## Custom Silicon for Low-Cost Information Dissemination among Illiterate People Groups

by

#### **ZhiYoong Foo**

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 2013

Doctoral Committee:

Professor David Blaauw, Chair Professor Peter Chen Assistant Professor James Cutler Assistant Professor Prabal Dutta

To my loving family.

## TABLE OF CONTENTS

| DEDICA  | ATION                                      | •                                                                                                                                                                                          | ii                                                                                                                     |

|---------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| LIST OF | F FIG                                      | URES                                                                                                                                                                                       | vi                                                                                                                     |

| LIST OF | F TAB                                      | LES                                                                                                                                                                                        | ix                                                                                                                     |

| CHAPT   | ERS                                        |                                                                                                                                                                                            |                                                                                                                        |

| 1       | Introdu<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5 | action       Thesis Scope       Thesis Scope         Information       Quality of Life       Thesis Overview         Impacts of Information, Literacy, and Education       Thesis Overview | $     \begin{array}{c}       1 \\       1 \\       2 \\       3 \\       3 \\       4     \end{array} $                |

|         | Develoy<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5 | Contemporary Dissemination Vehicles and their Limitations<br>Literacy Bridge's Talking Book                                                                                                | 8<br>8<br>10<br>15<br>20<br>26                                                                                         |

|         |                                            | ew of Literacy in Technology (LIT): A Low-Cost Custom Silicon Rural<br>Computer for Information Dissemination among Illiterate People Groups<br>Motivation                                 | <ol> <li>27</li> <li>29</li> <li>29</li> <li>30</li> <li>31</li> <li>32</li> <li>34</li> <li>35</li> <li>38</li> </ol> |

| 4 | On-Ch    | ip Integrated Power Management, Power Operational Modes and Wakeup    |          |

|---|----------|-----------------------------------------------------------------------|----------|

|   | Interru  | pt Controller                                                         | 39       |

|   | 4.1      | Introduction                                                          | 39       |

|   | 4.2      | LIT's On-Chip Integrated Power Management                             | 40       |

|   |          | 4.2.1 Overview                                                        | 40       |

|   |          | 4.2.2 LIT's 4 On-Chip LDOs and Unique Flexibility                     | 40       |

|   |          | 4.2.3 Voltage Doubler                                                 | 43       |

|   | 4.3      | Minimizing LIT's Energy Consumption                                   | 44       |

|   |          | 4.3.1 LIT's Carbon-Zinc Battery Direct Connect                        | 45       |

|   |          | 4.3.2 LIT's Power Operational Modes and Wakeup Interrupt Con-         |          |

|   |          | troller                                                               | 45       |

|   |          | 4.3.3 LIT's Variable Clock Frequency and Module Power Gating .        | 48       |

|   | 4.4      | LIT's Board Level Novel Configurable Pads                             | 50       |

|   | 4.5      | Summary                                                               | 51       |

|   |          |                                                                       |          |

| 5 | Hybrid   | l Switch Capacitor Network                                            | 53       |

|   | 5.1      | Overview                                                              | 53       |

|   | 5.2      | Prior Art in Voltage Converters                                       | 54       |

|   | 5.3      | Proposed Novel Hybrid Switch Capacitor Network                        | 56       |

|   | 5.4      | Detailed Operation                                                    | 58       |

|   | 5.5      | Results                                                               | 61       |

|   | 5.6      | Summary                                                               | 61       |

| C | Ъſ       | TT· 1                                                                 | <u> </u> |

| 6 |          | ry Hierarchy                                                          | 63       |

|   | 6.1      | Motivation                                                            | 63       |

|   | 6.2      | Commercially Available Microcontrollers, Memory Hierarchies and       | 0.4      |

|   | <u> </u> | their Cost                                                            | 64       |

|   | 6.3      | Memory Hierarchy                                                      | 67<br>70 |

|   | 6.4      | Memory Operation and Uniqueness of LIT's Memory Hierarchy             | 70       |

|   | 6.5      | Memory Hierarchy's Energy Consumption Results                         | 71       |

|   | 6.6      | Summary                                                               | 72       |

| 7 | Power-   | on-Reset / Brown-out-Detector with Lock-off for Carbon-Zinc Batteries | 74       |

| • | 7.1      | Introduction                                                          | 74       |

|   | 7.2      | Background and Unique Requirements for LIT Context                    | 74       |

|   | 7.3      | Prior Work in Power-on-Reset / Brown-out-Detectors                    | 76       |

|   | 7.4      | Proposed Novel On-Chip POR/BOD Circuit                                | 78       |

|   | 1.1      |                                                                       | 10       |

| 8 | Robus    | tness and Cost Sensitivity through Overloading PCB Traces             | 81       |

|   | 8.1      | Introduction                                                          | 81       |

|   | 8.2      | Human Input Interface Using Capacitance to Digital Converters (CDC)   |          |

|   |          | with PCB Traces as Buttons                                            | 82       |

|   | 8.3      | Information Transfer Using PCB Traces as Inductive Link Coil          | 86       |

|   | 8.4      | Summary and Novelty of Overloading PCB Traces                         | 88       |

|   |          | · · · · · · · · · · · · · · · · · · ·                                 |          |

| 9      | Results | of Literacy in Technology (LIT), a Low-Cost Custom Silicon Designed |

|--------|---------|---------------------------------------------------------------------|

|        | for Ru  | cal Audio Computers                                                 |

|        | 9.1     | LIT's Results                                                       |

|        | 9.2     | LIT's Cost                                                          |

|        | 9.3     | Results Summary 95                                                  |

| 10     | Conclu  | sion and Future Directions                                          |

|        | 10.1    | Conclusion                                                          |

|        | 10.2    | General Takeaways                                                   |

|        | 10.3    | Future Directions                                                   |

|        | 10.4    | Related Works                                                       |

| BIBLIC | GRAF    | PHY                                                                 |

## LIST OF FIGURES

## Figure

| 1.1  | 2013 Human Development Index World Map                                                                          | 3  |

|------|-----------------------------------------------------------------------------------------------------------------|----|

| 2.1  | Villagers gathered around a tree attending tutorial from a visiting NGO                                         | 11 |

| 2.2  | The world at night: Showing electricity penetration                                                             | 13 |

| 2.3  | Worldwide Literacy Rates: Percentage of illiterate people is decreasing, but                                    |    |

|      | total illiterate population is remaining constant                                                               | 14 |

| 2.4  | Global Map of Literacy Rates for Adults 2010 [1]                                                                | 15 |

| 2.5  | Typical radio available in developing regions                                                                   | 16 |

| 2.6  | Typical cassette player available in developing regions                                                         | 16 |

| 2.7  | Typical basic cellular phone available in developing regions                                                    | 18 |

| 2.8  | Global Recordings Network's Saber's handcrank allows end users to recharge                                      |    |

|      | its internal batteries.                                                                                         | 19 |

| 2.9  | The Talking Book: A state-of-the-art Rural Audio Computer designed specifi-                                     |    |

|      | cally for on-demand information access in developing regions. To access audio                                   |    |

|      | content, end users navigate through voice prompts using the small number of                                     | 01 |

| 0.10 | input buttons visible on the device.                                                                            | 21 |

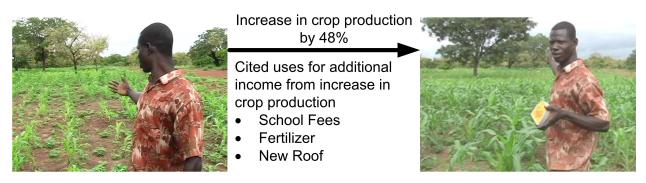

| 2.10 | Increase in crop production from a user applying information from the Talking<br>Book to his farming practices. | 21 |

| 2.11 | A nurse at a rural clinic inspecting the Talking Book for healthcare scenarios.                                 | 22 |

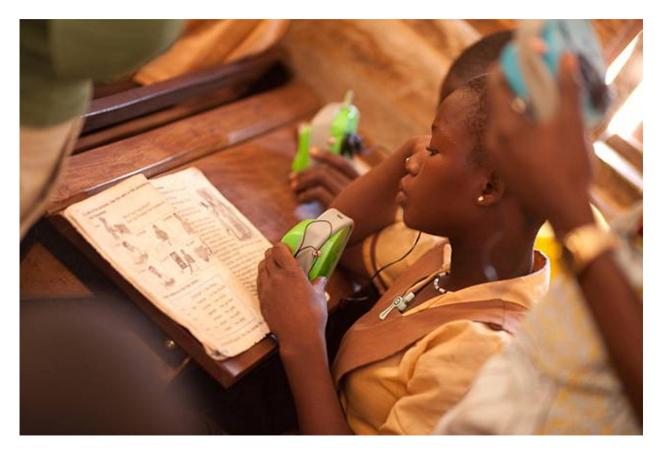

| 2.12 | Students in Ghana using the Talking Book in an educational setting                                              | 23 |

| 2.13 | Literacy Bridge's Talking Book with its 152 commercial off-the-shelf compo-                                     |    |

|      | nents (Front Side).                                                                                             | 24 |

| 2.14 | Literacy Bridge's Talking Book with its 152 commercial off-the-shelf compo-                                     |    |

|      | nents (Back Side)                                                                                               | 25 |

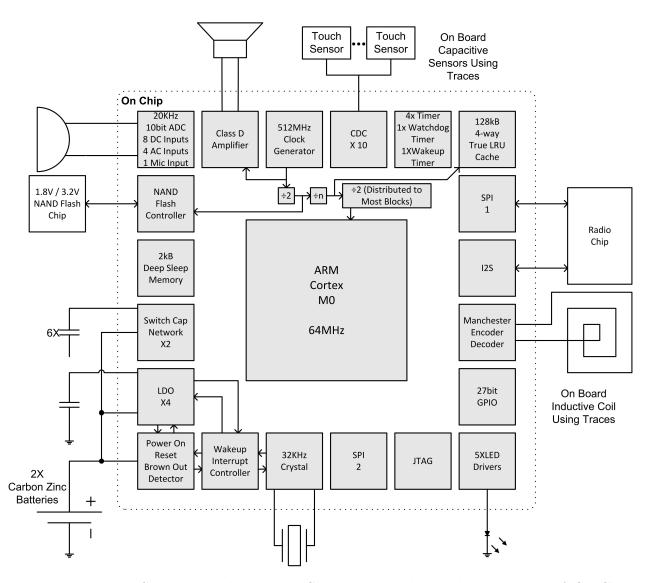

| 3.1  | LIT's System Level Diagram Showing a High Level Integration of On-Chip                                          |    |

|      | Components Resulting in a Low On-Board Component Count                                                          | 32 |

| 3.2  | Broken OLPC Push-Membrane Keyboard.                                                                             | 33 |

| 3.3  | Talking Book left outside in mud overnight by end users                                                         | 33 |

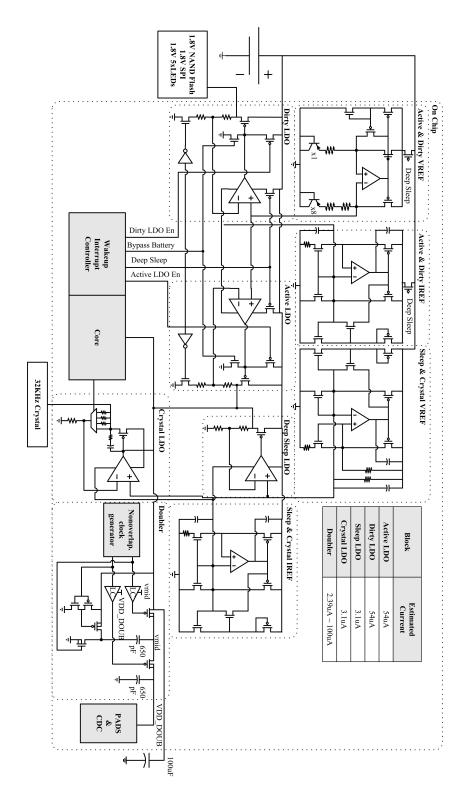

| 4.1  | LIT's power diagram showing LDOs, and on chip Voltage Doubler with their                                        |    |

|      | associated VREFs and IREFs and silicon measured linearity                                                       | 41 |

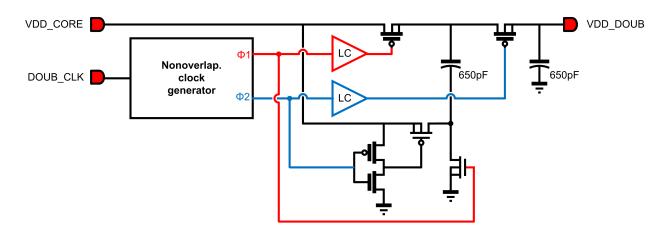

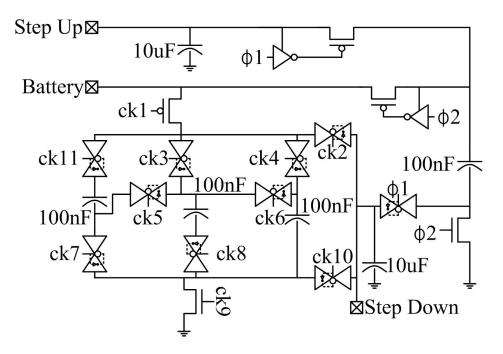

| 4.2  | LIT's Voltage Doubler's Circuit Level Diagram.                                                                  | 43 |

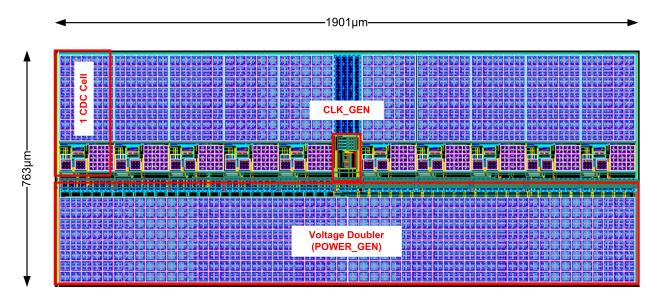

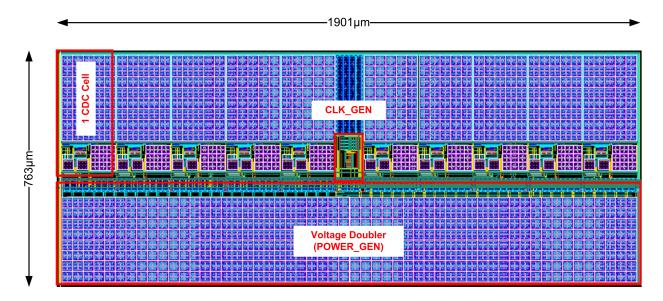

| 4.3  | LIT's Voltage Doubler's Layout Measuring 1.9mm X 0.35mm Occupying 3% of LIT's Area                                                                                                                                                                                                                  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

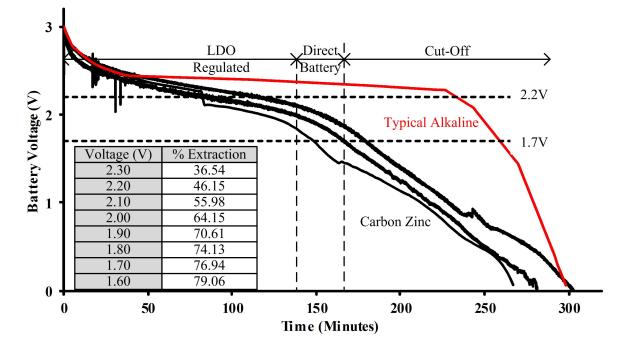

| 4.4  | Measurements of Ghana's Carbon-Zinc batteries versus typical Alkaline bat-<br>tery. By extending operational voltage from 2.2V to 1.7V, 30% more energy                                                                                                                                             |

|      | is extracted                                                                                                                                                                                                                                                                                        |

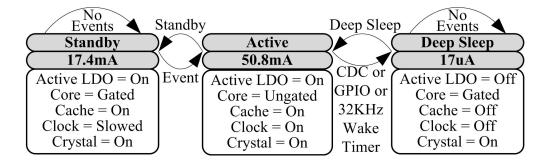

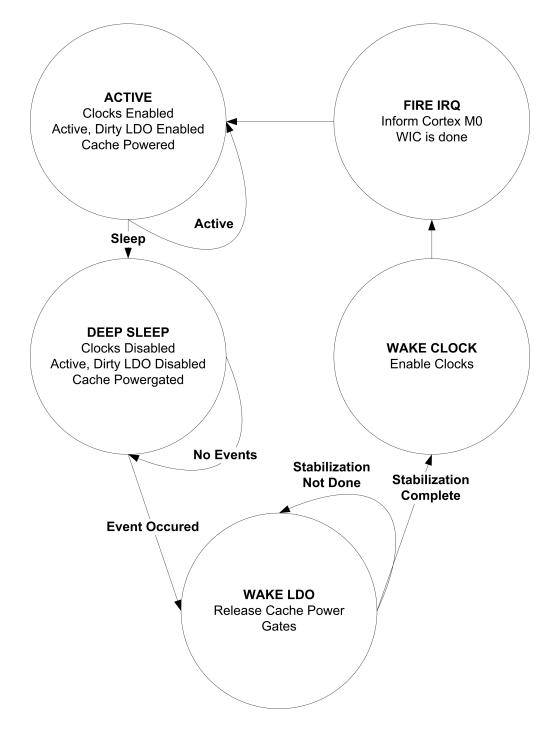

| 4.5  | LIT's Wakeup Interrupt Controller state diagram                                                                                                                                                                                                                                                     |

| 4.6  | LIT's Wakeup Interrupt Controller state diagram                                                                                                                                                                                                                                                     |

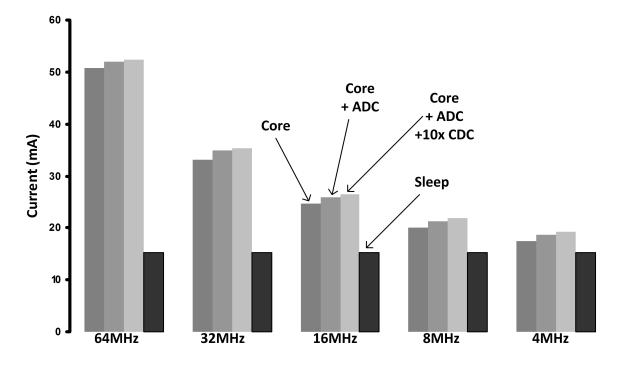

| 4.7  | LIT's silicon measured current draw for active mode with operational blocks<br>and Sleep mode at various frequencies                                                                                                                                                                                |

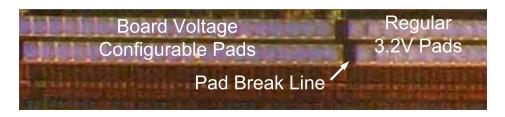

| 4.8  | LIT's I/O Pad Break for board voltage configurable pads                                                                                                                                                                                                                                             |

| 4.9  | LIT's System Power Diagram: The NAND Flash Controller I/O can be pow-<br>ered by either the Variable Charge Pump or the Dirty LDO depending on<br>whether a 3.2V or 1.8V NAND Flash chip is used. We accomplish this by<br>connecting the Variable Charge Pump or Dirty LDO to the PAD Dirty VDD. 5 |

| 5.1  | LIT's Off-Chip Component Operating Voltage Range                                                                                                                                                                                                                                                    |

| 5.2  | Typical Boost Converter Consisting of an Inductor, and Two Switches (Tran-                                                                                                                                                                                                                          |

| 0.2  | sistor and a Diode)                                                                                                                                                                                                                                                                                 |

| 5.3  | LIT's Hybrid Switch Capacitor Network Block Diagram                                                                                                                                                                                                                                                 |

| 5.4  | LIT's Hybrid Switch Capacitor Network                                                                                                                                                                                                                                                               |

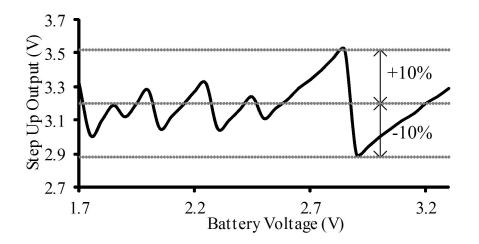

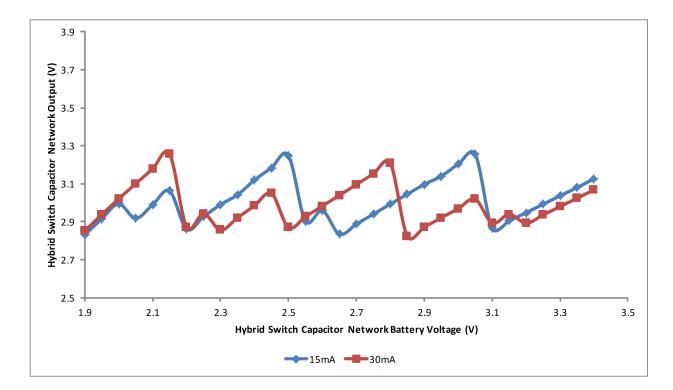

| 5.5  | Measured Output of LIT's Hybrid Switch Capacitor Network is shown to stay                                                                                                                                                                                                                           |

|      | within 10% of 3.2V across 3.3V - 1.7V battery voltage range                                                                                                                                                                                                                                         |

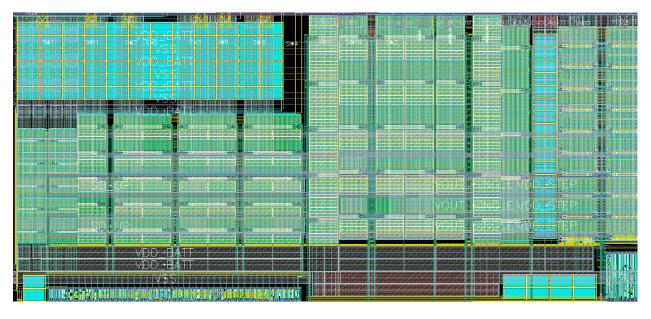

| 5.6  | 1.6mm X 0.7mm Hybrid Switch Capacitor Network Layout 6                                                                                                                                                                                                                                              |

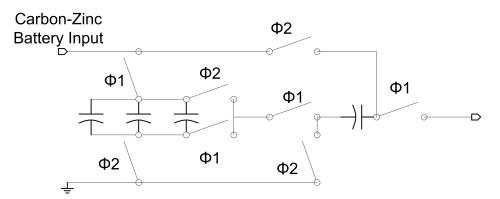

| 5.7  | LIT's Simplified Hybrid Switch Capacitor Network Topology for 50% Config-<br>uration                                                                                                                                                                                                                |

| 5.8  | LIT's Step Down Switch Capacitor Network Topology during $\Phi 1$ for 50% Configuration.                                                                                                                                                                                                            |

| 5.9  | LIT's Step Down Switch Capacitor Network Topology during $\Phi 2$ for 50%                                                                                                                                                                                                                           |

| 5 10 | Configuration                                                                                                                                                                                                                                                                                       |

|      |                                                                                                                                                                                                                                                                                                     |

|      | LIT's Hybrid Switch Capacitor Network's Load Regulation.6LIT's Hybrid Switch Capacitor Network's Line Regulation.6                                                                                                                                                                                  |

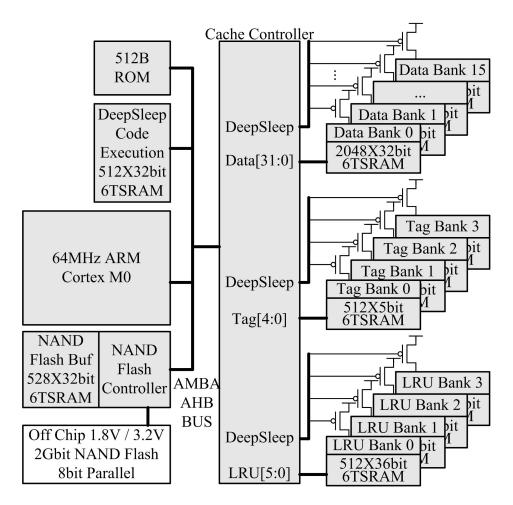

| 6.1  | LIT's memory system diagram.                                                                                                                                                                                                                                                                        |

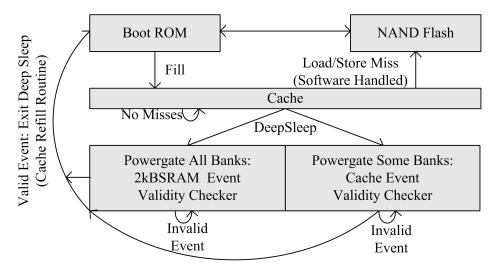

| 6.2  | LIT's memory operation from loading from boot, miss handling during Active                                                                                                                                                                                                                          |

| 0.2  | mode and Deep Sleep mode cache power gating options or using 2kB dedicated SRAM.                                                                                                                                                                                                                    |

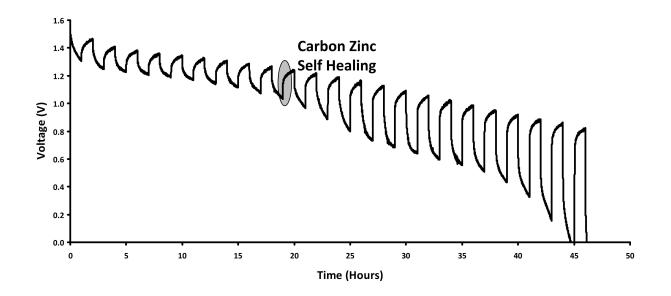

| 7.1  | Ghana's Carbon-Zinc batteries exhibiting its self healing property 7                                                                                                                                                                                                                                |

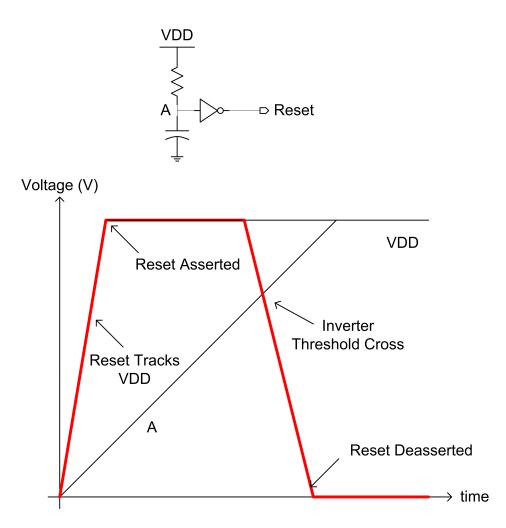

| 7.2  | Traditional Power-on-Reset Circuit.                                                                                                                                                                                                                                                                 |

| 7.3  | LIT's on-chip $1.7\mu$ A Power-on-Reset / Brown-out-Detector with "lock-off" for                                                                                                                                                                                                                    |

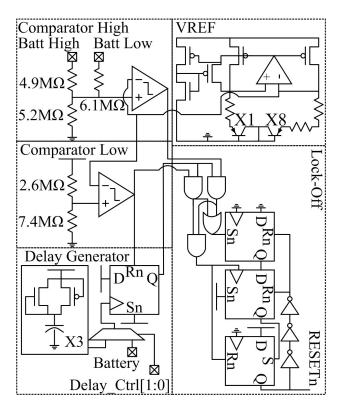

| 1.0  | Carbon-Zinc Batteries                                                                                                                                                                                                                                                                               |

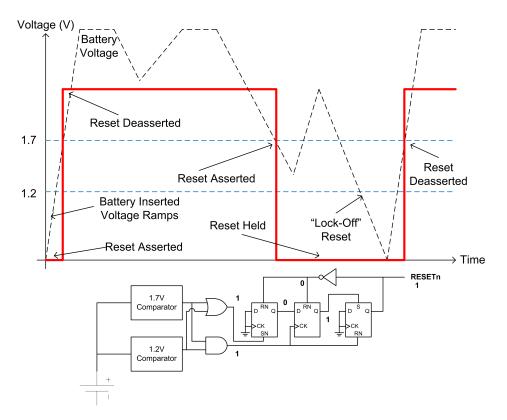

| 7.4  | LIT's on-chip $1.7\mu A$ Power-on-Reset / Brown-out-Detector with "lock-off"                                                                                                                                                                                                                        |

|      | operation                                                                                                                                                                                                                                                                                           |

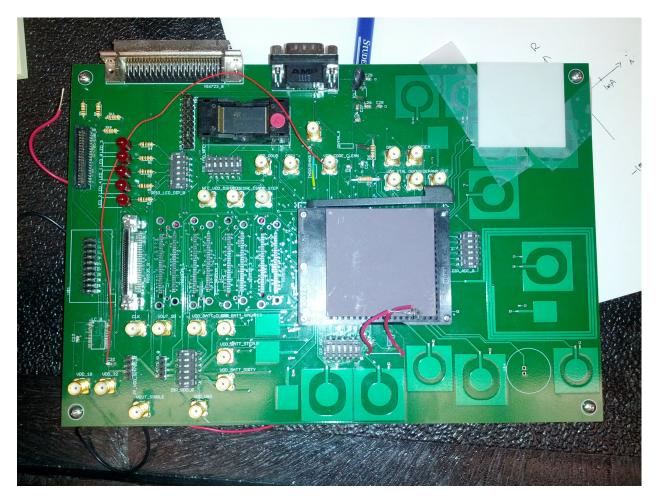

| 8.1  | LIT's PCB Showing Traces Used as Touch Sensor Human Input Interfaces                                                                                                                                                                                                                                |

|      | and as the coil for the inductive link                                                                                                                                                                                                                                                              |

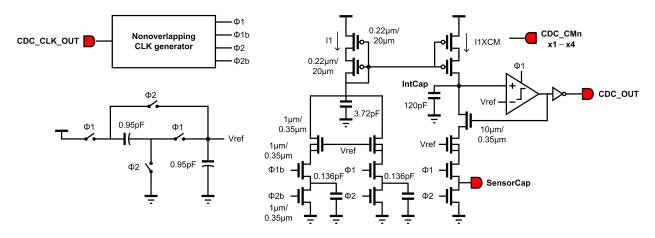

| 8.2 | LIT's 17-bit Sigma Delta Capacitance to Digital Converter Circuit Level Di- |    |

|-----|-----------------------------------------------------------------------------|----|

|     | agram Requiring only PCB Traces Buttons.                                    | 84 |

| 8.3 | LIT's 17-bit Sigma Delta Capacitance to Digital Converter Layout.           | 85 |

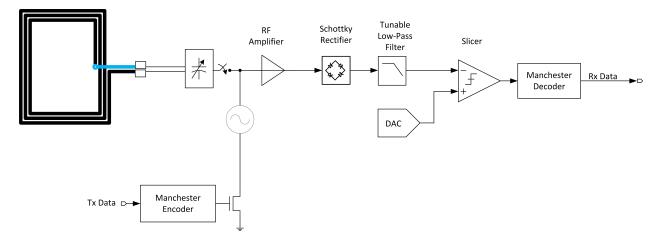

| 8.4 | LIT's Transceiver for PCB Inductive Link Coil Block Diagram                 | 88 |

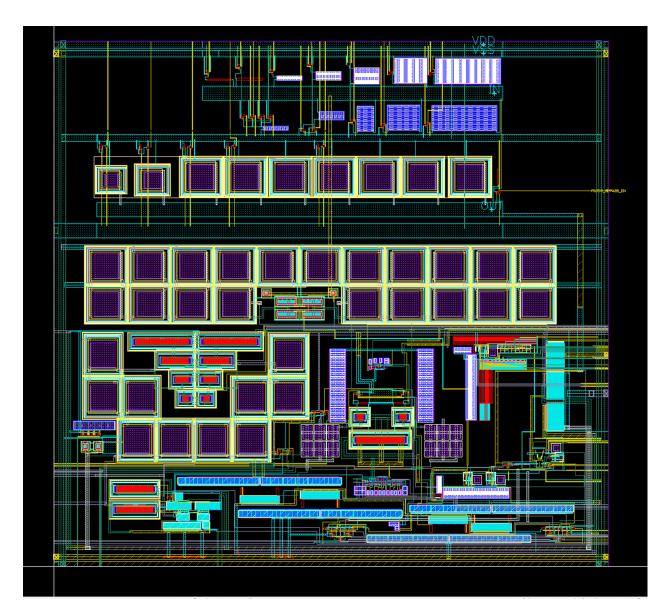

| 8.5 | LIT's Transceiver Layout for PCB Inductive Link Coil.                       | 89 |

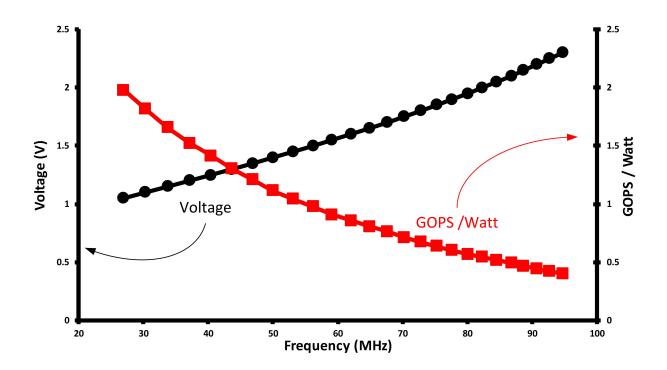

| 9.1 | LIT's Silicon Measured Core Clock frequency versus Voltage and Silicon Mea- |    |

|     | sure Core GOPS/Watt                                                         | 91 |

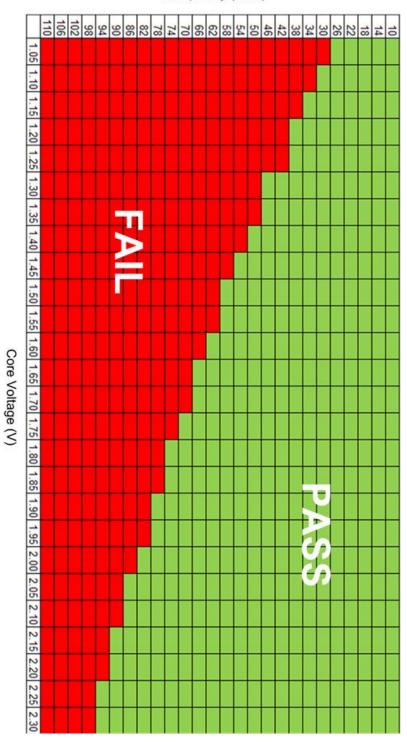

| 9.2 | LIT's Shmoo Plot.                                                           | 92 |

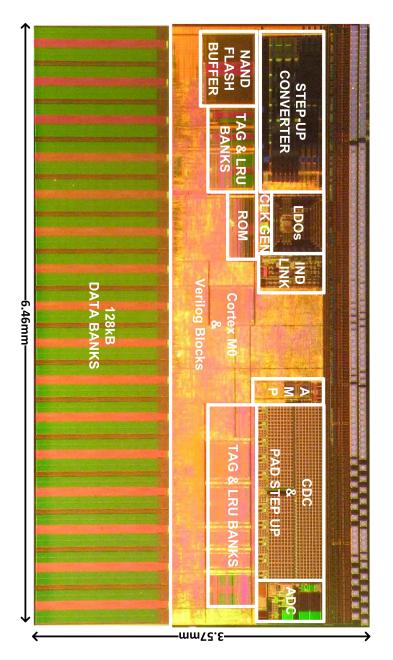

| 9.3 | LIT's Die Micrograph.                                                       | 93 |

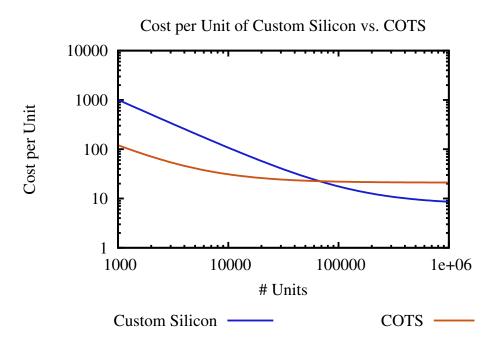

| 9.4 | Unit cost versus volume for custom silicon and a COTS component design      | 95 |

## LIST OF TABLES

#### Table

| 3.1 | LIT's Novel Design Decisions.                                                   | 37 |

|-----|---------------------------------------------------------------------------------|----|

| 4.1 | LIT's Deep Sleep mode current draw with event monitoring options selected.      | 48 |

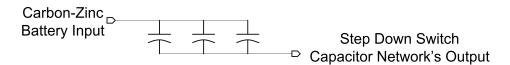

| 5.1 | Configurations for Step Down Switch Capacitor Network to achieve fractional     |    |

|     | battery voltages.                                                               | 58 |

| 6.1 | Currently available microcontrollers, their memory space, and cost              | 64 |

| 6.2 | Silicon measured current of LIT's cache during Deep Sleep mode.                 | 72 |

| 9.1 | LIT's design parameters and silicon measured results                            | 94 |

| 9.2 | LIT's Bill of Materials. Note that the fractional cent costs come from the high |    |

|     | volume pricing of components                                                    | 96 |

## CHAPTER 1

### Introduction

#### 1.1 Thesis Scope

In this thesis, we present the work done at the University of Michigan where the improvement of the quality of life of the poorest people in the world is attempted through Very Large Scale Integrated Chips (VLSI). The premise of the work was to see if we could build an ICT device that can be used to disseminate information to and among the poorest people in the world, identified to be subsistent farmers living in rural agrarian societies in developing regions. We first show how the benefits of timely, actionable information can improve the quality of lives. We then go on to show how current NGO solutions that attempt this have shortcomings and how current ICT solutions, while successful in some aspects, fall short in tackling all the unique problems in this setting: cost, power, connectivity, usability, robustness and illiteracy. We argue that even when an ICT solution is designed specifically to overcome the unique problems presented, that it falls short due to the high price and the low purchasing power of the target population.

We show that by designing custom silicon targeted to this application space, we can overcome the challenges presented. Literacy in Technology (LIT), developed at University of Michigan, tackles all the challenges through design decisions such as having a high level of integration to reduce the initial cost to a point that can be purchased by the target population. Other side effects of this design decision are a lowered Printed Circuit Board (PCB) footprint size due to the lowered count of passives and reducing the number of onboard chips to only 3. Furthermore we show how by reducing the costly DRAM or NOR Flash traditionally used for code storage in microcontrollers and leaving both code and data in an on-board NAND Flash further reduces the cost of the ICT solution. Other decisions such as removal of wires and open ports and using wireless delivery of content through radio updates or near field inductive communication improves the robustness of the solution. We also ensured that we designed LIT to consume as little energy as possible thus lowering the recurring costs of the end users. We also store information in an audio based format so that literacy is not a requirement for using the device. Other design decisions such as reusing traces that will be used during the PCB manufacturing for touch sensors and inductive coil increases the robustness of the design while reducing the cost as well. Through such design decisions, we show that LIT can overcome the unique problems presented.

### 1.2 Information

Information, knowledge that can be derived from study, experience or instruction, is widely available to most people in developed regions. From local libraries, to radios, televisions, and the internet, most people in developed regions can access information easily. Powered with information, people can be educated about basic rights, public services available to them, better healthcare, education, and work opportunities, all which can drastically improve their quality of life. Access to information is a resource that most people take for granted. However, a large number of the worldwide population suffers from difficulty in accessing information either due to reasons such as low purchasing power and illiteracy. Their low purchasing power means that they have limited capabilities in choices of how they can get access to information. Furthermore, literacy allows people to be independent in their means of access to and absorbing new information and passing of knowledge between groups through reading and writing in print. Once only restricted to a small elite group of people, literacy has been shown to have a large impact on people's livelihoods.

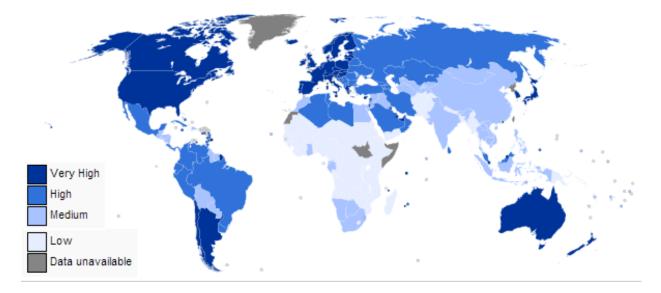

Figure 1.1: 2013 Human Development Index World Map

### 1.3 Quality of Life

The Human Development Index (HDI) is a composite statistic of life expectancy, education, and income used to rank countries and the quality of life of its citizens [2]. We can see from (Figure 1.1) that developing countries generally have low HDI scores. These developing countries have a high percentage of the population living in rural settlements where access to information is difficult. These populations rely on subsistence farming, a practice where farmers grow enough food for themselves and their families. Furthermore these population groups have a high number of illiterates making improving their quality of life through information difficult.

## **1.4** Impacts of Information, Literacy, and Education

Recent studies have illustrated the benefits of timely, actionable information on rural agrarian populations in developing regions. In the Avaaj Otalo project [3], a mobile phonebased, interactive voice forum enabled the "emergence of norms, persistent moderation, and a desire for...interaction with...authorities and open discussion with peers" in India. Users of the system found value in listening to questions and answers with 77% of interviewees citing this as the main reason they liked the forum. The Digital Green project [4], "seeks to disseminate targeted agricultural information to small and marginal farmers in India using digital video." A four month trial of the system showed a six to seven times increase in adoption of certain agricultural practices. The Talking Book project [5] deployed a custombuilt audio computer in rural Ghana to study "the impact of giving on-demand access to guidance created by local experts" and found that in a village with 90% illiteracy and no electricity, Talking Book users significantly increased crop production over farmers who did not use the devices.

Literacy and education have also been shown to correlate with issues ranging from poverty, to incarceration, to high health care costs [6] in the United States. For persons in developing regions, the same issues reign, while the consequences of illiteracy have also been linked to child mortality rates [7]. Children, whose mothers can read or write have a higher chance of surviving since they are more knowledgeable about health and nutritional practices and live in better situations. Child mortality has also been shown to reduce by an additional 8% for every year that a mother is educated [8]. These studies show how access to information can directly impact quality of life and is a motivator to finding means to supply information to those that need it the most: subsistence farmers living in rural agrarian populations that have a high number of illiterates.

#### 1.5 Thesis Overview

In the following chapters, we dive into the details of the work done for the thesis. Each chapter will highlight the motivation behind the work, talk about current solutions and present how LIT overcomes the challenges presented to achieve its target goals.

Chapter 2 explores the unique challenges of dissemination information amongst illiterate persons in developing regions. We show how current NGO solutions have limitations that can be overcome through ICT solutions. We then showcase some examples of current ICT solutions that attempt to tackle the problem and point out their shortcomings. By highlighting their shortcomings, we see that there is a real need to design a custom solution specifically tailored to fit the needs of the targeted end users. One such custom solution, the Talking Book, showed encouraging results from its pilot study, but it is still at a price point that is not viable for the end users that subsist on \$1 - \$2 a day. We show that in order to overcome all the complexities, custom silicon will yield a result that can cut the Gordian Knot that ties cost, power, connectivity, usability, robustness and illiteracy.

Chapter 3 introduces LIT and provides a quick overview of its unique capabilities. LIT shows how judicious design of silicon can improve upon previous ICT designs and can overcome the challenges — cost, power, connectivity, and robustness posited by the task of disseminating information among illiterate people. With its high-level of integration, novel circuit level, system level, and application specific level solutions and design decisions, they all work in unison towards the achieving the primary goal of reducing its initial cost and recurring cost to a point that can be purchased and used by the end users.

Chapter 4 highlights LIT's entirely On-Chip Integrated Power Management System. Resulting in a low off-chip component count that allows the final ICT solution to be priced at a point viable to the end users, we show how commercially available solutions do not have the level of integration that LIT achieves. This high level of integration differentiates LIT from current ICT solutions that are too expensive thanks to having a high number of off-chip components. Combined with LIT's Power Operational Modes, Active, Sleep, and Deep Sleep which results in LIT's 2 year lifetime. LIT's Board Level Configurable Pads allows LIT to be flexible in choice of either a 1.8V or 3.2V off-chip NAND Flash chip allowing LIT to be sensitive to market price volatility of the NAND Flash chips. This also results in a flexible low initial cost solution that other ICT solutions do not manage to achieve.

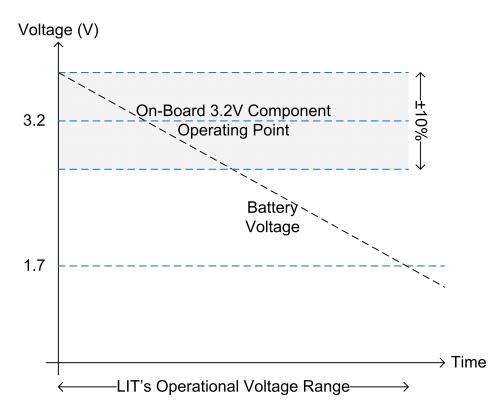

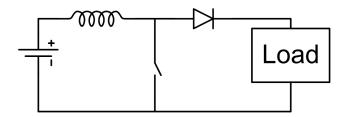

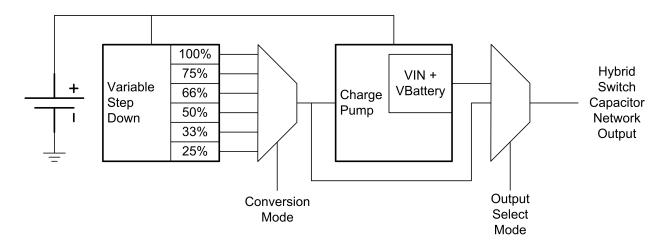

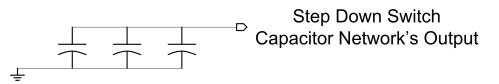

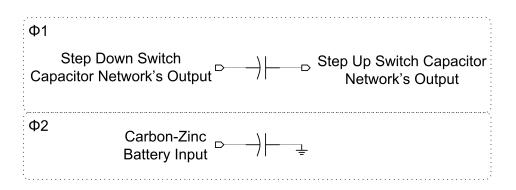

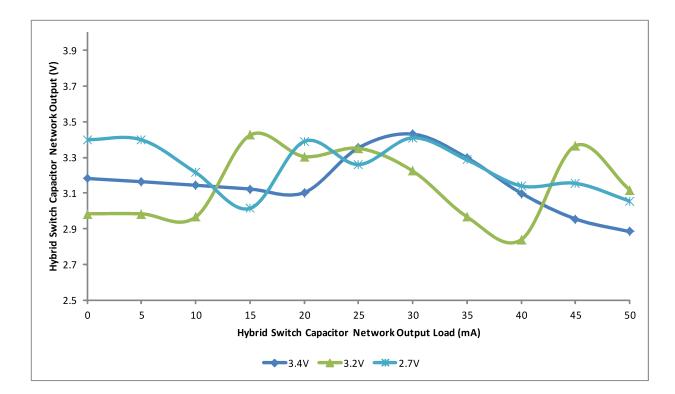

Given LIT's low-cost goal, Chapter 5 shows how LIT has to provide power to a whole system entirely from a single chip while maintaining a low off-chip component count which will result in a low-cost in order to power its off-chip components. We argue that inductors commonly used in Boost and Buck converters are not feasible, namely due to its cost and on-chip design complexity. Switch Capacitor Networks are the best solution due to the low cost of capacitors. However, they suffer from fixed conversion ratios and since LIT is designed to operate on a wide battery input voltage, we achieve generating the 3.2V through the design of a novel Hybrid Switch Capacitor Network that combines a Step Down Switch Capacitor Network that provides fractional values that gets fed into a Step Up Switch Capacitor Network. This allows us to achieve the 10% range of 3.2V in order to power the off-chip components while still maintaining LIT's design goal of a low-cost ICT device.

Chapter 6 talks about the investigative work behind currently available commercial microcontrollers and other possible memory solutions that led us to build LIT's memory hierarchy. We found that current microcontrollers are either too expensive as a one minimal solution system or severely lacks the capabilities that we require if we wanted to meet our target cost goals. Other possible memory solutions were either too expensive (MicroSD, NOR Flash, DRAM) or unfeasible to be implemented on chip (Embedded Flash). By using a 128kB 4-way True LRU cache backed by a large off-chip NAND Flash chip in conjunction with a low power, low cost small microcontroller, this allowed us to meet our target cost goal. However, this decision led to some complexities and obstacles that we managed to overcome. We also show how LIT's memory reduces its energy consumption through granular power gating that both allows us to maintain flexibility in the amount of code left awake for the event validity checker that reduces false wake ups.

Chapter 7 shows how LIT's novel robust Power-on-Reset / Brown-out-Detector with lock-off feature with dual comparators and hysteresis manages to overcome the oscillations due to the Carbon-Zinc batteries used in these developing regions that have a strong selfhealing property. By not allowing reset to deassert if LIT had already been in reset when the Carbon-Zinc battery voltage drops below 1.7V, we manage to not corrupt LIT's NAND Flash's contents. Furthermore by having the Power-on-Reset / Brown-out-Detector with lock-off only allowed to be reset past 1.2V, we ensure that with such a large margin of hysteresis, the self-healing properties of the Carbon-Zinc batteries will not cause LIT to oscillate between power-on and off.

Chapter 8 showcases how LIT is sensitive to robustness and cost through the overloading of PCB traces used as both a human input interface device and a component in data transmission between devices. By reusing the traces already available on PCBs during the PCB manufacturing process, LIT manages to keep cost down by not requiring additional components to implement the human input interface and data transmission off-chip. Furthermore, the traces improve the robustness of the system by removing the moving parts such as mechanical buttons found in the previous ICT solutions which are a failure point. It also removes the open ports, dongles and wires required to transfer data from device to device further improving upon previous ICT designs. Through the careful reusing of components already available during the manufacturing process, we show how LIT can achieve its goals of a low initial cost ICT solution.

Chapter 9 presents LIT's results attained from silicon testing with Core Frequency vs. Voltage, silicon measure core GOPS/WATT, Shmoo plot, design parameters and their associated measured results, the expected Bill of Materials table broken down into the total chip cost, board cost and system cost and its associated components along the way.

## CHAPTER 2

# A Case for Custom Silicon in Enabling Low-Cost Information Technology for Developing Regions

#### 2.1 Motivation

In Chapter 1, we highlighted the importance of information and the benefits of timely, actionable information through studies that show how access to information and literacy can improve not just economical status, but also healthcare. Given the importance and the impact of access to information on the livelihoods of the nearly 800 million who are illiterate and have difficulty accessing information, solutions must be identified to overcome it. Encouraged by results illustrating the benefits of timely, actionable information on rural agrarian populations in developing regions, the following sections explore the question of how to scale, and make economically viable and sustain, such technologies for the nearly 1.5 billion people who live without electricity, the nearly 800 million who are illiterate, the great majority of whom do not own mobile phones and live in rural areas with limited or no data connectivity [9][10].

First, we will explore the practical challenges for information dissemination in rural settings in Section 2.2. We show that the current method for transferring knowledge to persons in rural settings is inadequate and that a new methodology is required. We argue that cost is the most important factor that needs to be addressed in order for the new methodology to be adopted in a widespread, sustained deployment and be successful. Furthermore, we present the practical challenges faced by designers that are interested in tackling this problem from an Information and Communications Technology (ICT) perspective, specifically: cost, power, connectivity, usability, robustness and illiteracy.

In Section 2.3, we outline why existing devices, most notably mobile phones, have been unsuccessful in meeting this need. In particular, we show how smart phones fall significantly beyond the required cost bracket. Even inexpensive basic phones do not quite address the needs of this population. Basic phones, while approaching the required cost point, lack the data storage, offer no simple data transfer methods, and pose logistical issues in that they require "reflashing" (an operation highly-specific to each phone model). In addition, mobile phones have high power draw and poor speaker efficiency, which makes their ongoing cost of ownership significantly higher than the devices currently owned by these populations. Other currently available Information and Communications Technology (ICT) solutions all have significant shortcomings as well. Given the shortcomings of currently available solutions, we argue that developing a device designed to tackle the unique challenges presented is needed in this application space.

In Section 2.4, we introduce Literacy Bridge's Talking Book, a device that has been developed using commercial off-the-shelf (COTS) components to tackle the unique challenges presented in this application space. The Talking Book was specifically designed for information dissemination amongst illiterate persons and we cite its successes in its pilot study. However, the Talking Book is not without its shortcomings as well, and we argue that its disadvantages can be overcome with custom silicon instead of a COTS design.

Given the need for a custom device, in section 2.5, we present the Rural Audio Computer, a device tailored to the unique Information and Communications Technology (ICT) needs of rural developing regions and the system architecture that supports its operation. We then argue that custom silicon offers a way to cut the Gordian Knot that ties cost, power, connectivity, usability, robustness, and illiteracy. Through: (i) component integration, (ii) reduced power draw, (iii) application-specific design optimizations, and (iv) electronic-mechanical codesign, a custom silicon design for Rural Audio Computers offers dramatic cost reductions that can make information technology widely accessible.

# 2.2 Practical Challenges for Information Dissemination in Rural Settings

System designers using ICT targeted at developing regions face many different challenges than those that apply to more affluent markets. In this section, we outline some of these challenges and discuss contemporary mechanisms for information access. For the world's poorest 2.6 billion people that live on \$2 per day or less and make up approximately 40% of the earth's population that lack literacy, disseminating knowledge to them in a viable manner has many unique and practical challenges that need to be overcome.

Currently, the most efficient way to teach practices for reducing child mortality rates is often by driving a pickup truck over rough unpaved roads to a remote village that hasn't been visited recently. Upon arrival in a targeted village, the local health expert might gather anyone who is available and overwhelm them with numerous messages about disease prevention (Figure 2.1). Unfortunately, those who are able to attend will have difficulty recalling any specific guidance that they did not immediately apply — they are not able to replay the guidance on demand nor can they take notes due to lack of literacy. Furthermore, those who did not attend will suffer from the "telephone game" effect of having information spread through word-of-mouth from those who attended, diluting the guidance given. There needs to be a solution where they can retain the information being passed to them and access it, on demand, in a format that does not rely on literacy. This current method for transferring knowledge is clearly inadequate and we argue that ICTs can yield a solution.

Finding an ICT solution for this rather unique scenario has multiple challenges — cost, power, connectivity, usability, robustness, and illiteracy. We argue that cost is the least flexible challenge facing timely access to actionable information for illiterate persons. If cost were not a factor, one could conceivably provide audio information to illiterate persons using audio recordings on a smart mobile phone and simply recharge batteries using a solar panel or generator. One could use GPRS or EDGE, where available, for content downloading or use an integrated or external FM receiver to download content where GPRS or EDGE was not available, share content using WiFi in ad hoc mode, and offer graphical or voiceactivated user interaction. The technology for this is readily available, proven, and can be

Figure 2.1: Villagers gathered around a tree attending tutorial from a visiting NGO.

easily implemented if cost were not an issue. For designers of ICT products aimed at this population, cost is key. Designers must consider both the cash-flow challenges associated with initial purchase and the overall return on investment, which factors in all ongoing costs. The total cost of ownership (TCO) that designers must be aware of include both the upfront cost, and recurring cost.

That upfront cost is the dominant factor in widespread, sustained deployment is illustrated by two first-hand observations from a recent trip to remote villages in Ghana by members of our research team. First, these subsistence farmers (who grow enough food for their families with little or no surplus for cash income) tend to purchase a low-quality ax that costs \$10, but usually breaks quickly and needs to be replaced, rather than spend money on a high-quality ax that costs \$20 but will last a life time. This indicates that they tend to not be able to save the capital up to invest in something that will yield better returns. Second, the majority of electronics owned by these populations, again based on our investigations, typically cost less than \$10 and are almost never more than \$20, establishing the viable price points for typical consumers: economic viability requires a target price of approximately USD \$10.

The recurring cost, overhead of accessing information from the device, must also be considered. For example, consuming large amounts of energy to retrieve the information would make the device expensive to use by requiring end users to have to repeatedly recharge or buy new batteries. While lowering the energy consumption of the device is an overhead that designers must be aware of, access to content must also be considered. For instance, a basic mobile handset may cost between USD \$20-\$40, but listening to new content costs an additional \$0.10-\$0.30 per minute throughout most of Sub-Saharan Africa [11]. From our investigations, we also observed that the end users often prefer to listen to a recording several times. Given that, we can conclude that this recurring cost could quickly dominate the TCO making using the device not unfeasible.

While we argue that both upfront and recurring costs are the least flexible challenges, designers need to be aware of the other challenges as well — power, robustness, connectivity, usability, and illiteracy. Power is a concern since worldwide, 1.5 billion people have no access to electricity and, what's worse, is that the situation is not expected to improve much in

Figure 2.2: The world at night: Showing electricity penetration.

the next 20 years: by 2030, the International Energy Agency predicts the number to drop from 1.5 to 1.3 billion people Figure 2.2). Only 15% of rural households in Sub-Saharan Africa have access to grid electricity [12]. Therefore, any ICT product designed for the poorest people in the world cannot depend on grid electricity. Similarly, designing a device to include a built-in renewable power source will reduce the TCO in the long-run through power cost reduction, but the additional cash required to acquire the device may put it out of reach for this audience. For example, Global Recordings Network's Saber [13] and One Laptop Per Child [14] are such devices that allow the users to recharge them but puts a much higher burden on the upfront cost. Designers also need to ensure that the ICT solution is robust enough to be handled by the end users who may not be as careful with the device as typical users that are more accustomed to technology. Moving parts that are used to recharge the internal batteries will be prone to mechanical failure and will have to be designed to be more robust and thus burden cost even more.

Connectivity and usability are also challenges that need to be considered from this unique perspective. The human-computer interface needs of the end users are significantly different from literate users [15]. ICT designers should also consider efficient ways of delivering information to the end users through the device. Studies of constant pitch speed shifting of audio

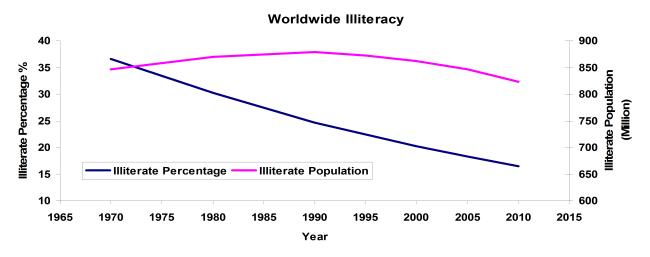

Figure 2.3: Worldwide Literacy Rates: Percentage of illiterate people is decreasing, but total illiterate population is remaining constant

have shown that listening to materials sped up at least twice is more effective than listening to it at normal speed [16]. Furthermore, constant pitch speed shifting allows users to slow down or, scan and skip sections in a manner similar to reading printed text. This helps with understanding the material since the end users can pace it an understandable rate [17].

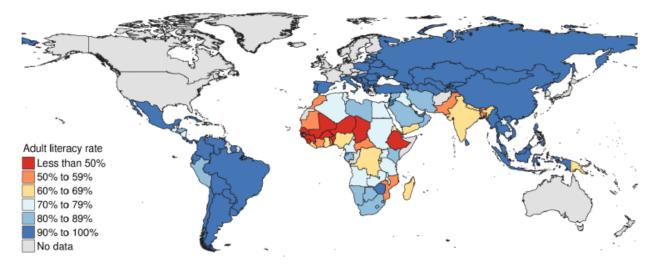

According to the UNESCO's Institute for Statistics, the total percentage of literate adults (adults defined as 15 years and older) in the world is 84% with 88.6% of the males and 80% of the females literate [1]. While the total percentage of illiterate persons have decreased over the years, the total number of illiterate persons has remained roughly constant (in part due to population growth) (Figure 2.3). 775 million adults, of which 64% are women, are unable to read or write. Literacy rates are the lowest in sub-Saharan Africa and in South and West Asia (Figure 2.4).

Across these regions, self-reported adult literacy rates are approximately 60% (these numbers are typically self-reported and have been shown to significantly underestimate the problem when follow up testing occurs). In many villages, the literacy rate may be as low as five to ten percent. Total youth (youth defined as ages 15 to 24 years) illiteracy is at 122 million. The nearly 800 million adults in the world that are illiterate have difficulty gathering information the way that the majority of the world's population can. This inability to gather information affects their ability to educate themselves and presents a unique problem to information access from an ICT solution perspective.

Figure 2.4: Global Map of Literacy Rates for Adults 2010 [1]

# 2.3 Contemporary Dissemination Vehicles and their Limitations

In this section, we showcase a few examples of current ICT solutions that attempt to meet the needs described in Section 2.2. From historical ICT solutions such as the radio, to state-of-the-art solutions such as mobile phones, we highlight how certain aspects of the current solutions work to solve the challenges. We also discuss their shortcomings that fail to make their widespread, sustained deployment successful.

**Radio** — Radios are widely used and available throughout rural developing regions and are at both an initial and recurring cost point that end users can afford. From our research team's observations in Ghana, a radio typically costs \$5. However, its limitations are that it does not allow end users to find the information they need, nor does it allow users to listen to a message several times at times convenient to them since they need to physically be there while the information is being transmitted. This is important since end users typically listen to a message multiple times based on our observations (Figure 2.5).

**Cassette Players** — Cassette Players are also available in rural developing regions and are at an initial cost point that end users can afford. However, with their electro-mechanical action, they are not energy efficient and add significant costs for content reproduction, distribution, and sharing with more than one device. Their electro-mechanical action also lowers

Figure 2.5: Typical radio available in developing regions.

Figure 2.6: Typical cassette player available in developing regions

their robustness as it will be prone to mechanical failure (Figure 2.6).

Cellular Phones — Cellular phones have become a necessity for nearly everyone in developed regions (Figure 2.7). The ability to have information at the touch of your fingers almost anywhere you go makes cellular phones a very tempting ICT solution. A cellular phone can download, store, and recall an audio recording which allows users to replay content as necessary, but there are many advantages and disadvantages to cellular phones which we will discuss. First, despite the cost of cellular phones dropping, cellular phones are still priced at roughly \$20, based on our research team's first hand observations in Ghana. This requires an initial investment that is just not possible for most of the poorest 40% of the world. Second, while only requiring power as the cost of access to the content stored on the phone, cellular phones need to be recharged, and some cellular phone owners will walk two or three hours to recharge their phone in a nearby town since their own town lacks the

running electricity as we have shown in 2.2. This scenario of crossing to other towns only work best when the phone is used for infrequent and brief calls. In fact, phone usage may be infrequent by necessity when network reception is too weak or not available in one's village (as applies to millions of mobile subscribers).

Connectivity is one of the challenges that a cellular phone, at first glance, might prove to be an advantageous ICT solution. Basic phones in Africa have a SMS cost between \$0.05 to \$0.21 [18] which is comparable to a 1 minute voice call [11]. SMS feedback is short and small compared to the data volume necessary to receive audio data and thus, SMS can provide a high-cost, low-bandwidth feedback channel. Another possibility of retrieving specific content on the phone is through the GSM data channel. The General Packet Radio Service (GPRS) or Enhanced Data rates for Global Evolution (EDGE) allow direct download of digital audio data over the Internet to a phone. However, these services are not available everywhere, and require an additional data plan. Access to the data modem of the phone is another issue that the solution would have to overcome: not all phones expose this capability to external devices, and there is no standard modem port on cellular phones. A further possibility for direct content dissemination is through the GSM voice channel. Recent work provided methods for transmitting digital data over the GSM voice channel [19][14] show that this is possible. While a cellular phone's connectivity basic phones and networks in the most impoverished areas often include SMS text capabilities, and sometimes even digital data services, there is a significant barrier for most potential users: illiteracy. Any ICT solution depending on text is not an option for the people who have the greatest need.

In each of these scenarios, a successful example of using mobile phones for communication does not necessarily translate into the ability to use the same tool for ongoing learning and on-demand reference. Some mobile phone-based ICT solutions have adopted interactive voice response (IVR) systems. The main challenge with such a system is usability, particularly on the input side (user selects an option). Those systems applying voice recognition are limited to the largest languages, which again excludes most of the potential beneficiaries of such a system. Those systems using keyed input face a usability challenge, particularly for people without numeracy skills or without exposure to any ICT beyond a radio. On the output side (prompts and status messages), graphical icons increase device cost and exclude

Figure 2.7: Typical basic cellular phone available in developing regions.

those with a visual disability; visual disability is twice as common in developing countries as developed countries — and yet Braille is much less available and not supported by cellular phones. Mid-range phones with FM radios and recording capability are still too expensive for one billion people living in extreme poverty; but more importantly, they are not designed as learning devices for people raised in oral cultures with little formal education.

Global Recordings Network's Saber — The Saber [13] does not require literacy to be operable and has a hand crank that can be used to recharge its internal batteries making it ideal from a recurring cost standpoint and ease in usability. However, data can only be updated through a computer, and furthermore, does not have a built-in microphone, meaning that end users have no way of including their own new information on the device. Furthermore, it is priced at a point (\$45-\$65) that is not affordable by the end users (Figure 2.8).

**Books of Hope's Speaking Books** — At a cost of \$10 for a minimum order quantity, Books of Hope's Speaking Books [20] are affordable but is limited to 5-10 minutes of data which cannot be updated. In fact, each new message requires a new Speaking Book to be developed. This causes giving out new information a difficult and costly task.

Given the current contemporary dissemination vehicles and their shortcomings, designing

Figure 2.8: Global Recordings Network's Saber's handcrank allows end users to recharge its internal batteries.

a custom ICT solution from the ground up to face these challenges will yield better results.

### 2.4 Literacy Bridge's Talking Book

Given the complexities and challenges that need to be overcome listed, in Section 2.2, and the limitations of current solutions from Section 2.3, we argue that developing a custom device is the right avenue to pursue. The Talking Book (Figure 2.9), developed by Literacy Bridge, is a Rural Audio Computer with an audio and tactile interface designed for the sole purpose of disseminating information to illiterate persons in developing regions [21]. Using only buttons, end users navigate through menus to access information and interact with the device. The device prompts the user through spoken instructions which are localized to the region. In January 2009, a pilot study was undertaken in a remote village, Ving Ving, Ghana, where 77% of the adult population had never attended school [5]. Ving Ving's population survives on subsistence agriculture and has no running electricity. In the pilot study, Talking Books were handed out to 20% of Ving Ving's population and were loaded with agricultural information such as instructions about fertilizers, soil preparation, planting and livestock handling. Healthcare practices, educational material, and general stories that had a focus on culture and tradition were also included.

The results of the pilot study, collected in January 2010, showed an increase in crop production by an average of 48% when compared to non end users decrease of 5%. 75% of the end users sold their surplus of crop, and the income from the production was used for health insurance, school fees, home improvements (new roofs), and further investments in their agriculture (seeds, livestock) (Figure 2.10).

The Talking Book can be used for scenarios other than just general agricultural information, such as health practices. For example, nurses in busy rural clinics can record health messages to teach patients about hygiene, infant care, and disease prevention. Treatment specific information can be reviewed at a later time at patients' pace and also be disseminated from a single user that comes back from the clinic to the entire village (Figure 2.11).

For educational purposes, Talking Books can be used to read back to children. This is a teaching practice that is common in developed nations, but impossible for illiterate parents.

Figure 2.9: The Talking Book: A state-of-the-art Rural Audio Computer designed specifically for on-demand information access in developing regions. To access audio content, end users navigate through voice prompts using the small number of input buttons visible on the device.

Figure 2.10: Increase in crop production from a user applying information from the Talking Book to his farming practices.

Figure 2.11: A nurse at a rural clinic inspecting the Talking Book for healthcare scenarios.

Figure 2.12: Students in Ghana using the Talking Book in an educational setting.

The Talking Book can also be used as a teaching supplement where questions and answers can be loaded onto the Talking Book and students can be quizzed on material learned (Figure 2.12). This breaks the cycle where illiteracy is commonly passed from parents to children since illiterate parents cannot help their children become literate.

Given the success of Talking Book's pilot study, its chief obstacle to widely distributing it is to make it economically viable. Its current initial cost of \$25 - \$35 is not affordable by end users, out of the price range that we have previously indicated to be in the \$10 -\$20 range. The chief contributor to the current cost of the Talking Books is its 152 off-theshelf components (Figures 2.13 & 2.14). The immediate problem is that the sheer number of COTS components carry significant cost themselves. Purchasing such a large variety of components from different vendors results in every component having some profit margin associated with it. However, there also exist a number of indirect costs associated with the number of components that are not obvious but are in fact, more significant. First, it

Figure 2.13: Literacy Bridge's Talking Book with its 152 commercial off-the-shelf components (Front Side).

increases the PCB size, the pick and place cost, the probability of failure, and the testing complexity. For instance, the larger device count of the current device requires a PCB area of 120mm X 120mm and a 4 layer board. Finally, the plastic housing, and the shipping costs due to its bulk are increased significantly and all directly translate to a more expensive device. Furthermore, the current Talking Book's high energy consumption requires two D batteries, which impacts its size as well and, again, leads to a costlier device and a form factor that cannot be transported easily by the end user in his/her pocket.

Figure 2.14: Literacy Bridge's Talking Book with its 152 commercial off-the-shelf components (Back Side).

# 2.5 Implications of Commercial Off-The-Shelf Components Versus Custom Silicon

The main disadvantage of the current COTS component based Talking Book is its cost. As we have outlined in Section 2.4, the Talking Book includes a 16-bit, 96 MHz system on a chip with 256 KB on-chip ROM, a 1 MB NOR Flash chip for program code, and a 256 MB MicroSD card for audio storage. Accounting for 20% of the total bill of materials, the MicroSD card is the most expensive component. The voltage regulator, DCDC converter, speaker amp, and more than 152 other components make up a relatively small portion of the cost but require PCB real estate accounting for 13% of the total cost. We argue that we should merge as many of the COTS components as possible onto a single chip. By doing so, not only can we reduce cost and supply risk, but we also allow for greater PCB flexibility. There are several reasons as to why custom silicon for the Rural Audio Computer would overcome the limitations of the current solutions and are listed as follows.

First, component integration reduces chip count and pin count, both of which reduce cost. Current systems developed from COTS components can consist of as many as 150 discrete components and six major chips [5]. This drives up cost through margin on each individual device and packaging due to high pin-out counts (which can be as high as 50% of the chip cost). By developing custom silicon, we show that the entire system can be integrated in a handful of devices. This saves costs directly through fewer devices and reduced packaging, but also indirectly by allowing a much smaller and simple PCB design (consisting of just 1 or 2 layers). Other indirect benefits also occur, such as lower cost of plastic packaging and reduced shipping costs resulting directly from a smaller PCB footprint.

Second, custom design provides extensive opportunity for a reduction in power draw which reduces TCO by increasing the lifetime on a pair of (disposable) batteries and lowers the recurring cost. Again, indirect benefits of lower power draw exist, such as smaller casing requirements due to smaller or fewer batteries leading to lower fabrication and shipping costs, which accrues to both lower upfront costs and lower recurring costs.

Third, custom integration allows for a design specifically targeted at the developing regions' market. Carbon zinc batteries, for instance, are almost the sole battery option for the target population. These batteries have significantly different discharge characteristics from alkaline batteries common in developed regions. The choice of battery chemistry, regulator architecture, conversion efficiency, and other factors all play into the design of a low-cost regulator. A custom converter better accommodates carbon-zinc discharge curves. The power supply design is mostly driven by the availability of energy sources in developing regions. From extensive first-hand observations in Ghana, we found that carbon zinc batteries are the most common way of powering electronics (sans mobile phones). The reason is that access to grid electricity to recharge batteries is few and far between, solar cells are uncommon and expensive, and carbon zinc batteries are cheap and have long shelf life. The two most common form factors available are the D and AA sizes. One D size carbon zinc battery holds almost 4X the charge of two AA batteries (8000 mAh vs. 2200 mAh) and costs approximately the same. However, the lower voltage of a single D battery requires that the processor and speaker amplifier operate from a boost converter, which incurs significant energy loss (60% efficient) and also adds cost from additional passive components. Furthermore, the smaller form factor of the AA battery shrinks the overall system size, which reduces cost of the casing and, indirectly, the cost of shipping and distribution. The smaller form factor also allowed easier transport and handling by the end users.

Finally, judiciously designed silicon not only reduces the number of electronic components, but also eliminates other mechanical components. For instance, custom silicon makes capacitive touch sensors economical which eliminates the need for membrane push button switches, which in turn increases reliability and decreases cost. Similarly, the coil necessary for inductive coupling-based, near-field communication (NFC) can be printed on the PCB, eliminating the need for a discrete antenna and additional radio chips. Furthermore, by designing the silicon to be used mostly with capacitors instead of costly inductors allows us to further reduce the cost of the on board passive components.

#### 2.6 Summary

While the statistics and impact of information and literacy on quality of life are well known, the current NGO solutions have significant drawbacks: overwhelming amount of information that gets lost due to inability to retain that information, and telephone game loss. We show how current commercially available ICT solutions, despite their best efforts, do not adequately solve the unique challenges for information dissemination to populations in rural settings. Some ICT solutions are out of the price range of the end users, while other ICT solutions do not take into account the lack of infrastructure, content delivery and replayability. Some ICT solutions while within the price range, are not robust given their electro-mechanical actions. Given the complexities needed to be overcome in this unique situation, we see that custom design is a logical choice to cut the Gordian Knot that ties cost, power, connectivity, usability, robustness, and illiteracy. However, as the Talking Book has shown, custom design even at the board level has been proven insufficient to put the device at a cost point to be purchased by end users. Hence, custom silicon is required.

# CHAPTER 3

# Overview of Literacy in Technology (LIT): A Low-Cost Custom Silicon Rural Audio Computer for Information Dissemination among Illiterate People Groups

# 3.1 Motivation

In Chapter 2, we discussed how current ICT solutions do not adequately overcome the challenges of disseminating information among illiterate people groups. We argued that the unique challenges — cost, power, connectivity, and robustness can be overcome through the design of custom silicon. As previously mentioned, the chief challenge to disseminating the ICT devices among this list is cost due to the low purchasing power of the end users that typically subsist on \$1-\$2 per day. Based on our analysis of electronic devices that are frequently purchased in the market places such as radios and cassette recorders as well as through discussions with various NGOs, we believe a total device cost must lie between \$10-\$15, which means that all the electronics, including PCB, speakers, microphone, radio, buttons, etc. must remain below \$6.

In order to meet this \$6 cost target, this thesis proposes an SOC which forms the heart of an audio computer for information dissemination among illiterate people groups. This people group has a currently untapped market size of \$10B [22]. In this chapter, we give a high-level overview of the features and components of the SOC, referred to as the Literacy Information Technology (LIT) chip. We also discuss at a high-level how these features help to meet the \$6 cost target as well as the other challenges of power, connectivity, and robustness in a novel way. We present each of the key features of the LIT chip in more detail in the following chapters.

# 3.2 Overview of LIT Chip and Approach to Reduce Cost

With the LIT SOC at its center, the audio computer allows users to navigate through menus using buttons enabling them to access information which is played back to them through a speaker. The audio computer's information can be updated either through an onboard FM chip that the SOC communicates with, through a microphone that is connected to an on-chip ADC, or through peer-to-peer distribution via its near-field radio link. Using audio feedback, the user can configure and operate the device in a similar way that made the Talking Book's pilot study a success.

In figure 3.1, we show the overall architecture and its subcomponents. LIT was implemented in 0.18um CMOS, measures 3.57mmX6.46mm (23.06mm<sup>2</sup>), has 8 million transistors, 265K gates, with an expected cost < \$1 in moderate volumes (Figure 3.1). LIT chip tackles cost in a number of ways. For example, a novel memory architecture with 128kB 4-way True LRU cache is directly backed by NAND Flash and removes the need for costly DRAM or NOR Flash commonly found in micro-controllers and processors.

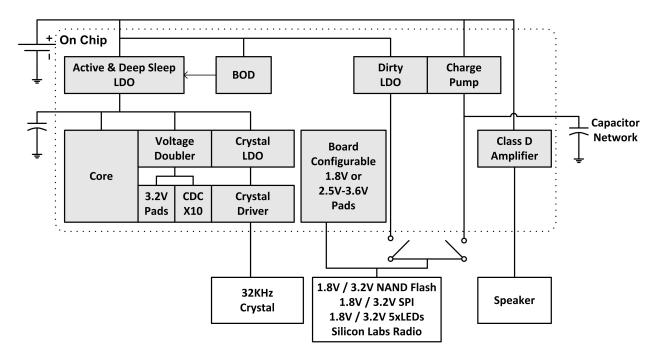

LIT also integrates all analog components in the system on-chip, including microphone amplifier and biasing circuits, an Analog-to-Digital Converter (ADC) [23], a class-D amplifier, 4 Low-Dropout Regulators (LDO)s, 2 voltage references, and a Hybrid Switch Capacitor regulator for DC-DC conversion. The high level of integration onto a single die reduces the total number of chips in the system to only 3: the LIT chip, a NAND Flash chip, and a radio chip. This saves cost and PCB size, which in turn reduces the plastic and handling costs (the previously mentioned indirect costs) of the final ICT solution.

There are current solutions that have a high level of integration [24] [25] [26] that meet some of the capabilities that fit the current ICT goals of information dissemination. Also, high levels of integration of SOC reuse has been known to save design complexity, product cycle time, and production cost [27] [28] [29] [30] [31]. However, LIT is the first custom chip designed specifically for disseminating information among low-income populations. Its high-level of integration results in a 9X reduction in components when compared to Talking Books [21] and other current ICT solutions available [13] [20] [32] which reduces both direct and indirect costs.

#### **3.2.1** Discrete Components

Even after integrating as many components on the LIT SOC as possible, there are still remaining discrete components. To reduce the cost of these components, we have also made design choices that directly reduce their cost. For example, instead of using a Step-Up Boost Converter with an expensive inductor for voltage boosting, we developed a new fine grain Hybrid Switch Capacitor Network which uses only capacitors. Since capacitors are one order of magnitude cheaper than inductors, this reduces overall system cost. Furthermore, peerto-peer information transfer is achieved through a coil that is directly traced on the PCB for a near-field inductive link for close range communication between devices instead of costly USB connectors/wires/antennas. This design also increases the robustness of the system by not requiring wires or connectors. In addition, 10 Capacitance-to-Digital Converters (CDCs) [33] were integrated on-chip to allow push-membrane buttons, which incur significant cost, to be replaced with capacitive sensors, also traced directly on the PCB. This overloading of PCB traces is unique in the field of ICT devices and results in a cheaper, more robust overall solution.

A side effect of the effort to reduce the number of components also results in a more robust device. Replacing the Talking Book's USB dongle (Figure 2.9) with the coil for peerto-peer transfer reduces the number of physical open ports, and the capacitive sensors on the board results in a longer lifetime of the buttons since push-button membranes will deteriorate with use (Figure 3.2). While robustness may not be as large a concern as cost, prior ICT devices have shown that end users are prone to disassembling the device and leaving it in the mud/rain indicating that end users may not be as careful with the device as typical users

Figure 3.1: LIT's System Level Diagram Showing a High Level Integration of On-Chip Components Resulting in a Low On-Board Component Count.

that are more accustomed to electronic technology (Figure 3.3).

### 3.2.2 Power Consumption

Lowering active and sleep energy consumptions are important goals for LIT since this reduces the end users' recurring costs, and many of LIT's design choices were made with lowering energy consumption in mind. Clock gating, power gating, and clock speed tuning, depending on workload and module activity, are software configurable and work in unison to lower energy consumption across the board. Furthermore, most of LIT's power hungry

Figure 3.2: Broken OLPC Push-Membrane Keyboard.

Figure 3.3: Talking Book left outside in mud overnight by end users.

components can be power gated individually depending on their use, thereby only using the minimal amount of energy required to do exactly what the device is doing at any point in time. LIT's low energy consumption allows it to be operated with only two AA batteries for up to two years in Deep Sleep mode, which improves its form factor to a point that makes it more easily transported by end users and lowers the recurring costs of purchasing new batteries for the device.

LIT's processor is an ARM Cortex-M0 which was chosen to balance power consumption with performance. The ARM Cortex-M0 uses only  $\sim$ 7000 gates from ARM's TSMC180 Standard Library, thereby requiring only modest chip area and contributes to the LIT chip's area by a minimal amount. The ARM Cortex-M0 has 32bit data operations and is powerful enough to decompress Speex audio, constant pitch speed shift audio using Synchronized Overlap-Add Fixed Synthesis (SOLAFS), and manage system overhead simultaneously at a clock speed of 64 MHz. Since the Cortex-M0 uses thumb code, consisting of 16-bit instructions as opposed to 32-bit instructions, it has high code density and minimizes system memory size. Its current draw of only 5mA during operation limits the recurring cost due to energy consumption.

# 3.3 Communication Capabilities

In Chapter 2 we showed that one of the drawbacks of current ICT devices is with their communication capabilities. LIT overcomes this through the integration of multiple communication modes with the inclusion of FM Radio, Peer-to-Peer communication, and mobile phone communications capabilities while maintaining a low cost. For wide-area dissemination, LIT uses an off-chip Silicon Labs FM radio receiver chip. A custom inductive link communication interface supports peer-to-peer communications, and connectivity over a mobile phone is possible by transferring data through the audio headset port [34]. We discuss each communications modalities briefly below, with the exception of the custom inductive link communication interface which is discussed in Chapter 8.