# VIRTUALIZING DATA PARALLEL SYSTEMS FOR PORTABILITY, PRODUCTIVITY, AND PERFORMANCE

by

Janghaeng Lee

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in the University of Michigan 2015

**Doctoral Committee:**

Professor Scott Mahlke, Chair Nathan Clark, Virtu Financial Associate Professor Kevin Pipe Assistant Professor Lingjia Tang Associate Professor Thomas Wenisch © Janghaeng Lee 2015

All Rights Reserved

To my family

### ACKNOWLEDGEMENTS

I would like to express my first and foremost gratitude to my research advisor, Professor Scott Mahlke, for his continuous support of this research. I consider myself truly lucky to have worked with him these past years. He has shown incredible patience, served as an excellent mentor from immense knowledges, encouraged me all the time, and guided pathways to success in this field.

My sincere gratitude also goes to my thesis committee, Prof. Thomas Wenisch, Prof. Kevin Pipe, Prof. Lingia Tang, and Nathan Clark for providing excellent comments and suggestions that helped me to make this work more valuable. I am grateful to Nathan Clark, the former advisor at Georgia Tech, who brought me to this area and enlightened me the first sight of research in this field. Also, I thank to Neungsoo Park who led me out into the graduate study in the United States.

It was very fortunate to be a member of Compilers Creating Custom Processors (CCCP) research group. I specially thank to Mehrzad Samadi, who is a great collaborator throughout years, providing significant helps in this work. It would not possible to have my thesis in the current shape without his support. I would also like thank a number of other students and alumni in the CCCP research group: Shantanu Gupta, Yongjun Park, Hyoun Kyu Cho, Ankit Sethia, Gaurav Chadha, Anoushe Jamshidi, Daya Khudia, Andrew Lukefahr, Shruti Padmanabha, Jason Jong Kyu Park, John Kloosterman, Babak Zamirai, and Jiecao Yu. All the people in the group are tightly bound together helping each other, and they made my PhD life much more enjoyable. In particular, Mehrzad, Ankit and Daya gave funnyand-stupid jokes all the time although I do not care, Jason Jong Kyu helped me when I encountered with math problems, and Shantanu played a great role as a mentor during my internship at Intel, giving me an opportunity to work on a great project.

My special thanks are extended to my Korean friends who made my time in Ann Arbor more enjoyable. Especially, I thank to Jason Jong Kyu Park and Eugene Kim as I could have tasty meals every dinner.

Finally and most importantly, my family deserves endless gratitude. My father, Jungsik Lee, and my mother, Sunmee Kim, always gave me the unconditional love and support. Whatever I am, I stand here because of them. I appreciate my brothers, Jihaeng and Jangwook. I have unforgettable childhood memories with them. They are always supportive and encouraging all the time.

# TABLE OF CONTENTS

| DEDICATION   |                                                                         | ii                    |

|--------------|-------------------------------------------------------------------------|-----------------------|

| ACKNOWLED    | GEMENTS                                                                 | ii                    |

| LIST OF FIGU | <b>RES</b>                                                              | ii                    |

| LIST OF TABL | ES                                                                      | ii                    |

| ABSTRACT     | xi                                                                      | ii                    |

| CHAPTER      |                                                                         |                       |

| I. Introd    | iction                                                                  | 1                     |

| 1.1<br>1.2   | Contributions       .         1.2.1       SKMD         1.2.2       VAST | 3<br>5<br>5<br>6<br>7 |

| II. Backg    | ound                                                                    | 9                     |

| III. SKMI    | : Single Kernel Execution on Multiple Devices 1                         | 2                     |

| 3.1          | Introduction                                                            | 2                     |

| 3.2          | 3.2.1Kernel Transformation13.2.2Buffer Management2                      | .7<br>.9<br>25<br>26  |

|              | 3.2.4 Transfer Cost and Performance Variation-Aware Parti-<br>tioning   | 29                    |

| 3.3          |                                                                         | 35<br>36              |

|           | 3.3.1 Results and Analysis                              | 40       |

|-----------|---------------------------------------------------------|----------|

|           |                                                         | -        |

|           | 3.3.2 Execution Time Break Down                         | 43       |

|           | 3.3.3 Performance Prediction Accuracy                   | 46       |

| 3.4       | Related Work                                            | 48       |

| 3.5       | Conclusion                                              | 51       |

| IV. VAST: | Virtualizing Address Space for Throughput Processors    | 52       |

| 4.1       | Introduction                                            | 52       |

| 4.2       | Motivation                                              | 56       |

| 4.3       | VAST System Overview                                    | 57       |

|           | 4.3.1 VAST System Execution Flow                        | 58       |

|           | 4.3.2 VAST Execution Timeline                           | 60       |

| 4.4       | Implementation                                          | 61       |

|           | 4.4.1 The Design of Page Accessed Set                   | 61       |

|           | 4.4.2 OpenCL Kernel Transformation                      | 63       |

|           | 4.4.3 Look-ahead Page Table Generation                  | 67       |

|           | 4.4.4 Forwarding Shared Pages                           | 69       |

| 4.5       | <b>8 1 1 1 1 1 1 1 1 1 1</b>                            | 09<br>71 |

| 4.3       | Further Optimization                                    |          |

|           | 4.5.1 Selective Transfer                                | 71       |

|           | 4.5.2 Zero Copy Memory                                  | 73       |

|           | 4.5.3 Double Buffering                                  | 74       |

| 4.6       | Evaluation                                              | 74       |

|           | 4.6.1 Results                                           | 77       |

|           | 4.6.2 Page Lookup Overhead                              | 81       |

| 4.7       | Related Work                                            | 83       |

| 4.8       | Conclusion                                              | 86       |

| V. MKM    | <b>D: Multiple Kernel Execution on Multiple Devices</b> | 88       |

| 5.1       | Introduction                                            | 88       |

| 5.2       | MKMD Overview                                           | 91       |

| 5.3       | Execution Time Modeling                                 | 93       |

| 5.4       | MKMD Scheduling                                         | 99       |

|           | 5.4.1 Kernel Graph Construction                         |          |

|           | 5.4.2 Coarse-grain Scheduling                           |          |

|           | 5.4.3 Fine-grain Multi-kernel Partitioning              |          |

|           | 5.4.4 Partitioning a Kernel to Time Slots               |          |

|           | 5.4.5 Overhead and Limitations                          |          |

| 5.5       | Evaluation                                              |          |

| 5.5       |                                                         |          |

|           | 5.5.1 Results                                           |          |

|           | 5.5.2 Sensitivity to Profiles                           |          |

|           | 5.5.3 Case Study                                        |          |

| 5.6       | RELATED WORK                                            |          |

| 5.7       | Conclusion                                              | 120      |

| VI. Conclu | <b>usion</b> |

|------------|--------------|

|            | Summary      |

|            | <b>IV</b>    |

## LIST OF FIGURES

## Figure

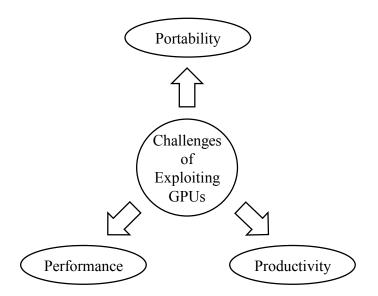

| 1.1  | Challenges in exploiting multiple GPUs for large data sets. Because the programming model exposes the hardware details, programmers must |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | consider portability, productivity, and performance when they write the                                                                  |    |

|      | data parallel kernels with large data on multiple devices.                                                                               | 2  |

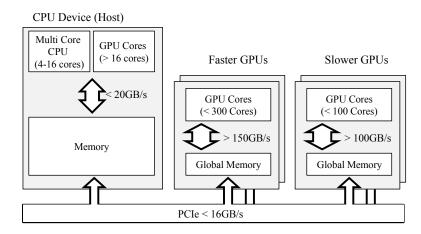

| 3.1  | Physical OpenCL computing devices with different performances, mem-                                                                      |    |

|      | ory spaces, and bandwidths.                                                                                                              | 14 |

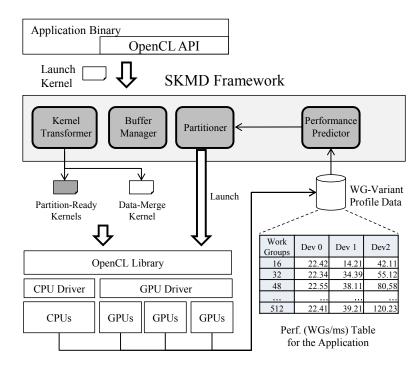

| 3.2  | The SKMD framework consisting of four units: Kernel Transformer,                                                                         |    |

|      | Buffer Manager, Partitioner, and Profile Database.                                                                                       | 16 |

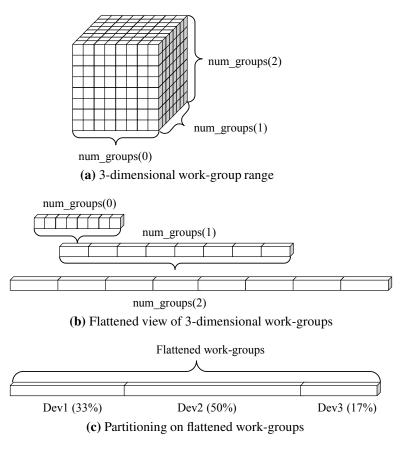

| 3.3  | OpenCL's N-Dimensional range                                                                                                             | 18 |

| 3.4  | Partition-ready Blackscholes kernel.                                                                                                     | 20 |

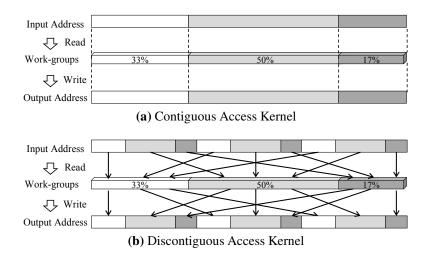

| 3.5  | Different memory access patterns of kernels                                                                                              | 21 |

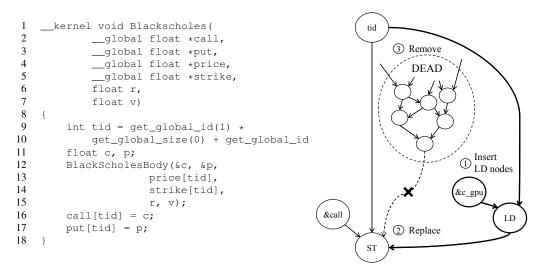

| 3.6  | Merge Kernel Transformation Process. Only global output parameters,                                                                      |    |

|      | call and put in (a), are marked for merging. Using data flow analysis,                                                                   |    |

|      | store values to global output parameters are replaced with GPU's partial                                                                 |    |

|      | results, and then proceed with dead code elimination (b). As a result, the                                                               |    |

|      | merge kernel does not have computational part (c).                                                                                       | 22 |

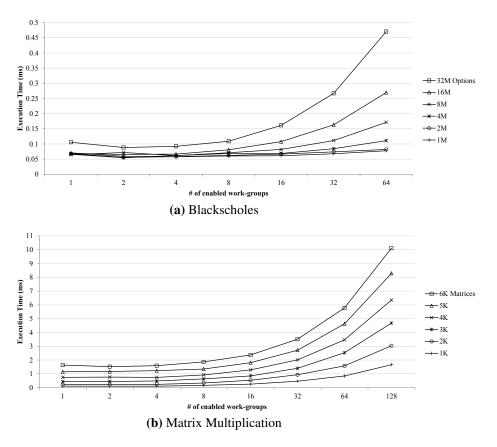

| 3.7  | Execution time varied by applications, input size, and the number of en-                                                                 |    |

|      | abled work-groups. Depending on the application and input size, the                                                                      |    |

|      | number of enabled work-groups impacts on the execution time differ-                                                                      |    |

|      | ently                                                                                                                                    | 27 |

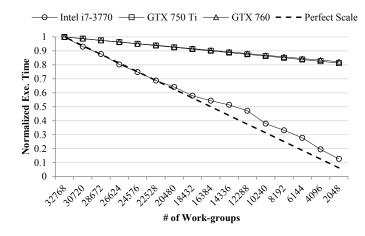

| 3.8  | Performance impact on VectorAdd varying the number of work-groups.                                                                       |    |

|      | The execution time of GPUs do not scale down in spite of reduced number                                                                  |    |

|      | of work-groups.                                                                                                                          | 29 |

| 3.9  | Comparison of linear partitioning and ideal partitioning                                                                                 | 31 |

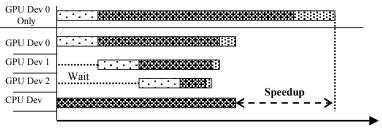

| 3.10 | Speedup and work-group distribution. Each benchmark has different                                                                        |    |

|      | baseline (a), as the fastest device differ by kernels. The fastest device                                                                |    |

|      | is determined with regard to the execution time and data transfer cost                                                                   | 41 |

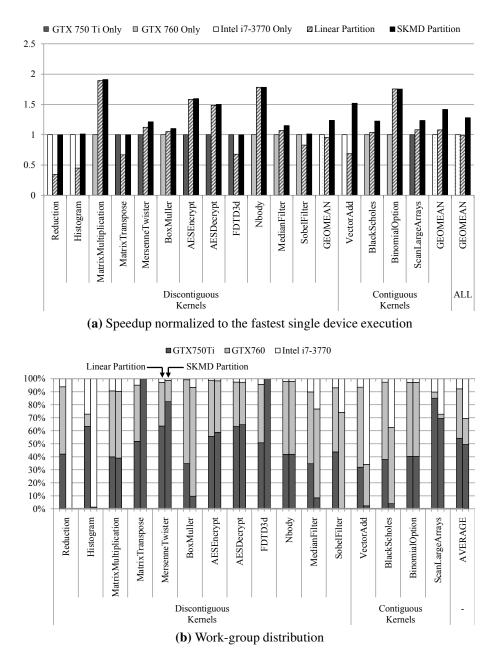

| 3.11 | Break down of the execution time on each device. The bars on the top                                                                     |    |

|      | is the baseline, which is the fastest single-device execution. SKMD con-                                                                 |    |

|      | siders the transfer cost, and offloads work-groups in order to balance the                                                               |    |

|      | workload among the three devices.                                                                                                        | 44 |

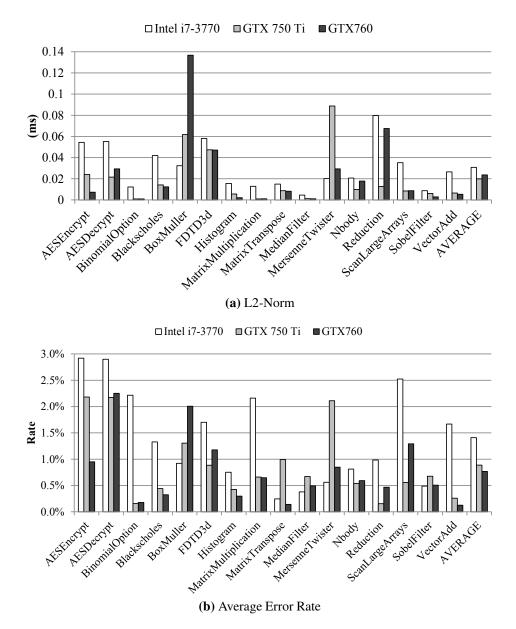

| 3.12 | Performance prediction accuracy. L2-Norm error (a) shows Euclidean distance between the real execution time and the predicted execution time in milliseconds. Average error rate (b) shows the average percentage of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|      | errors in predictions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 47       |

| 4.1  | The code transformation for partial execution of an OpenCL kernel. The kernel takes two additional arguments for the work-group range to execute, and grey backgrounded code is also inserted at the beginning of the kernel to check if the work-group is to be executed. The work-groups out of the range will terminate the execution immediately.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 56       |

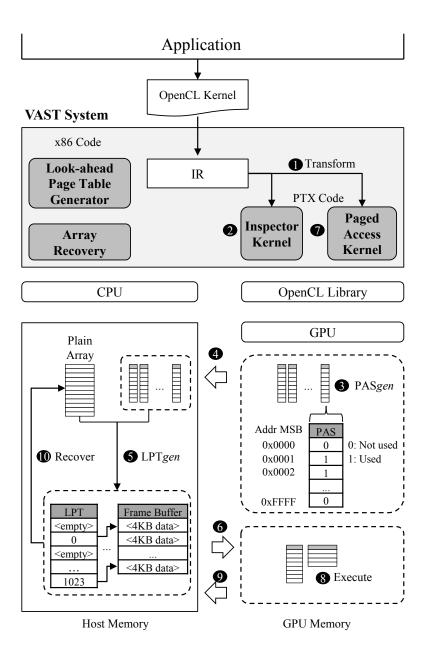

| 4.2  | The VAST system located between applications and OpenCL library.<br>VAST takes an OpenCL kernel and transforms it into the inspector kernel<br>and the paged access kernel. At kernel launch, the GPU generates PASs<br>(PASgen) by launching the inspector kernel, then transfers them to the<br>host to create LPT and frame buffer $(LPTgen)$ . Next, LPT and frame<br>buffer are transferred to the GPU in order to execute the paged access<br>kernel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 58       |

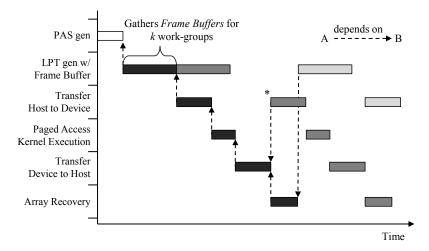

| 4.3  | Execution timeline for VAST system. Only PAS generation and the first LPT generation cost is exposed. Other LPT generations and array re-<br>coveries are overlapped from data transfer and kernel execution. With double buffering, the second LPT generation starts immediately after the first LPT generation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 60       |

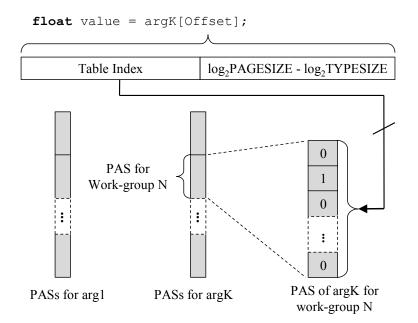

| 4.4  | The design of Page Accessed Set (PAS). Each work-group has its own PAS for each global argument. Each entry of PAS has a boolean value that represents whether corresponding page has been accessed by the work-group.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 62       |

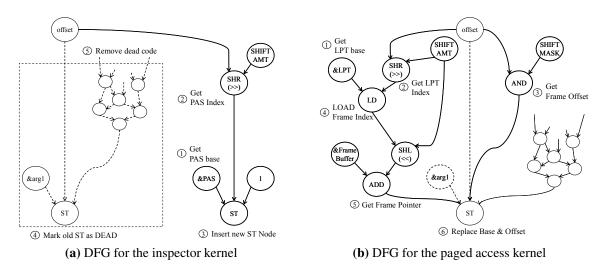

| 4.5  | Data flow graphs for the kernel transformation. In the inspector kernel<br>(a), all computational code are removed by dead code elimination. In<br>paged access kernel (b), the base and the offset are replaced with new<br>nodes for address translation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 64       |

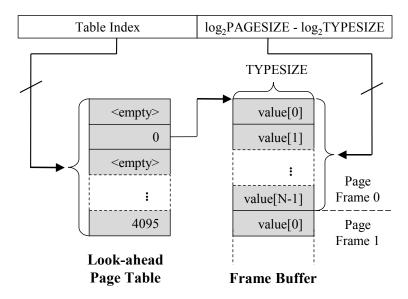

| 4.6  | The design of Look-ahead Page Table (LPT) and frame buffer. One pair of LPT and frame buffer corresponds to one global argument.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 65       |

| 4.7  | PAS generation for shared pages (shared PAS). Each reduced PAS is used<br>for a single sequence of partial execution. As the sequence of partial<br>execution increases, the number of logical operations increase for shared                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |

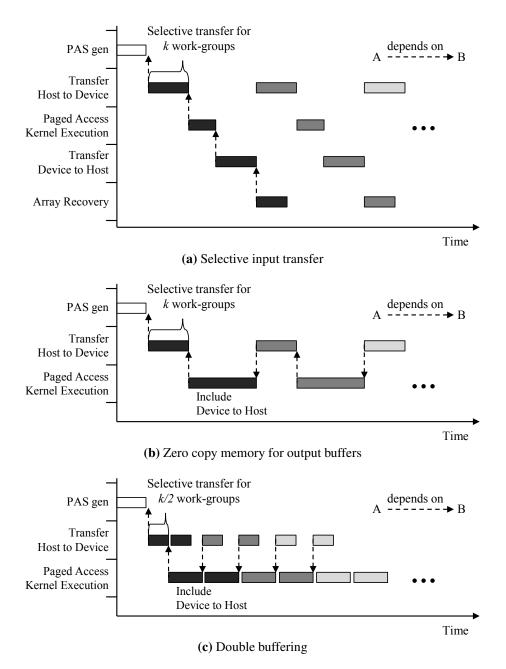

| 4.8  | PAS as VAST should check pages used in the previous sequences Execution timeline after optimizations. Selective input transfer removes the cost of frame generation (a). Zero copy memory for output buffer removes the cost of array recovery (b). Double buffering overlaps the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 69       |

| 4.9  | <ul><li>input transfer with kernel executioans (c).</li><li>Benchmark specifications. For the speedup over the CPU-baseline, data size more than GPU memory is used (a). For the comparison with normal GPU execution, data size less than GPU memory is used (b).</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 72<br>77 |

|      | $O_1 \cup C_2 \subset O_1 \cup C_2 \subset O_2 \cup O_2 $ | 11       |

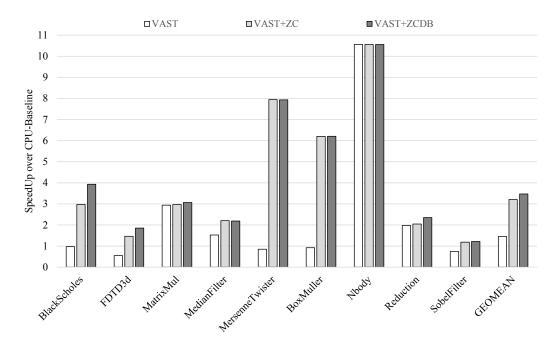

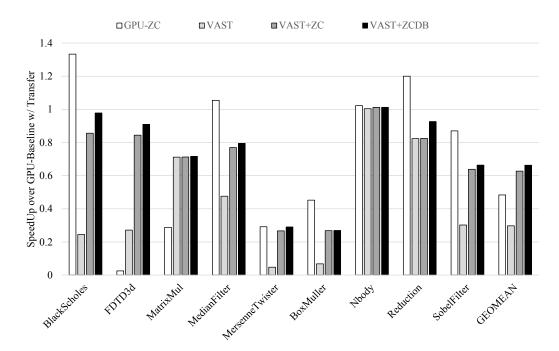

| 4.10       | Speedup of VAST over Intel OpenCL execution with 4 KB page frame size. VAST does selective transfers for input buffers. VAST+ZC uses              |       |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|            | selective transfers for input buffers and zero copy memory for output<br>buffers. VAST+ZCDB uses all optimization techniques discussed in Sec-    |       |

|            | tion 4.5.                                                                                                                                         | . 78  |

| 4.11       | Speedup of VAST over the GPU-baseline. The performance was mea-                                                                                   |       |

|            | sured using small workloads that fits into GPU memory. GPU-ZC is the                                                                              |       |

| 1.10       | execution using zero copy memory for all buffers.                                                                                                 | . 79  |

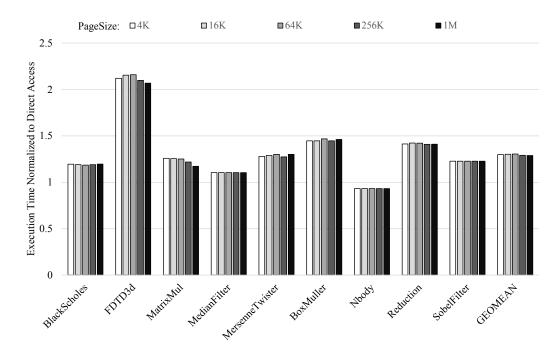

| 4.12       | Paged access kernel execution time normalized to the original kernel ex-<br>ecution time. Working set size for each benchmark is less than 2 GB.  |       |

|            | Paged-access kernel execution does not use zero copy memory.                                                                                      | . 81  |

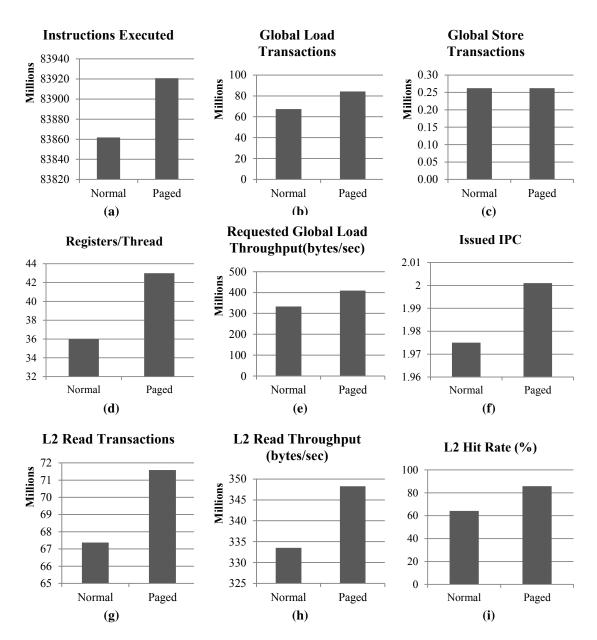

| 4.13       | Performance counters collected on N-body with 256K particles. Paged-                                                                              | . 01  |

|            | access kernel has approximately 60 million more instructions (a), and 20                                                                          |       |

|            | million more load transactions for page lookups (b). However, Paged-                                                                              |       |

|            | access kernel experiences higher IPC (f), because it gets more L2 hit rate                                                                        |       |

| <b>F</b> 1 | (i). $(1, 2, 2, 3, 3, 3, 3, 3, 3, 3, 3, 3, 3, 3, 3, 3,$                                                                                           | . 84  |

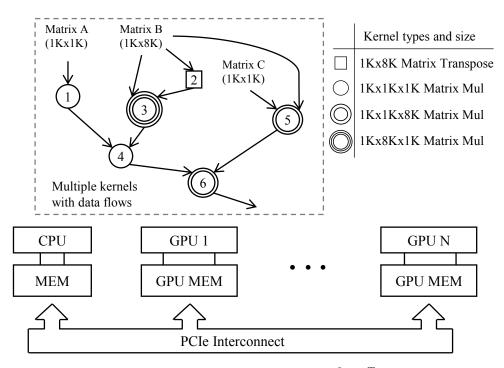

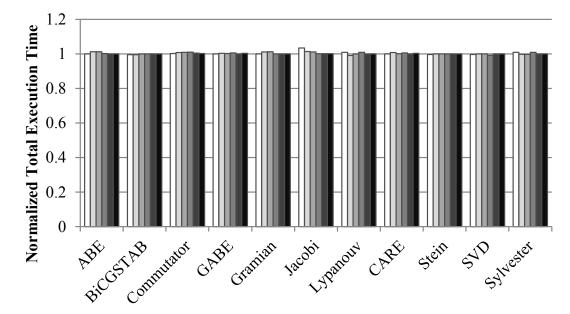

| 5.1        | A kernel graph for solving a matrix equation, $A^2BB^TCB$ , consisting of six kernels. The system is equipped with different computing devices    |       |

|            | with separated physical memory. Devices are connected through PCI                                                                                 |       |

|            | express (PCIe) interconnect. Each kernel has different amount of compu-                                                                           |       |

|            | tation, and each device has different performance.                                                                                                | . 89  |

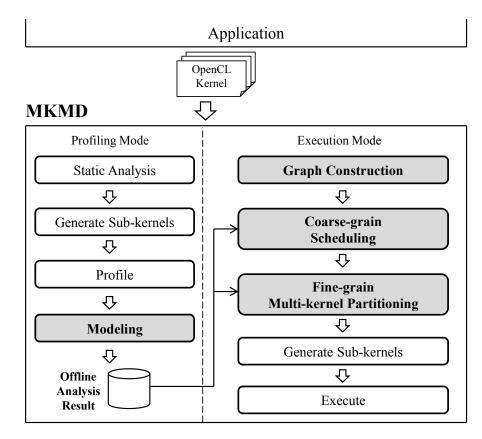

| 5.2        | MKMD workflow that operates in profiling mode and execution mode.                                                                                 |       |

|            | In profiling mode, MKMD builds a mathematical model with a set of                                                                                 |       |

|            | profile data for the execution time prediction. In execution mode, MKMD                                                                           |       |

|            | predicts the execution time of kernels on various input sizes using the model, and schedules kernels based on the predicted time.                 | . 92  |

| 5.3        | Upper bounds of trip count. The upper bounds are statically determined                                                                            | . )2  |

|            | as N for (a), and $\frac{N}{T}$ for (b)                                                                                                           | . 95  |

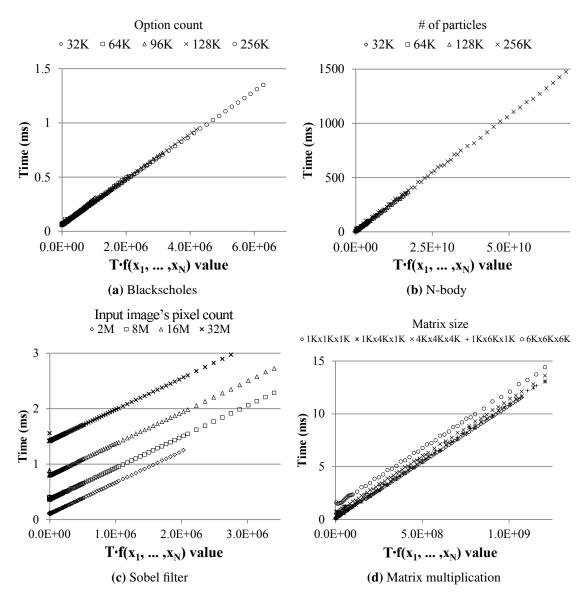

| 5.4        | Scalability of execution time on NVIDIA GTX760 varying input sizes                                                                                |       |

|            | and the number of enabled work-items $(T)$ . The execution time is linear                                                                         |       |

| <i>E E</i> | to the value of cost function $Tf(x_1,, x_N)$ .                                                                                                   | . 96  |

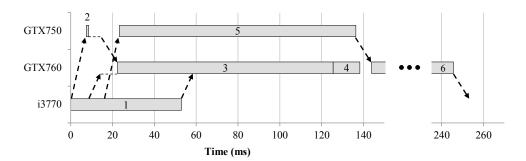

| 5.5        | Coarse-grain scheduling result on three heterogeneous devices. Dotted<br>arrows presents the buffer transfer between devices. PCI bus operates in |       |

|            | full-duplex, but GTX760 and i3770 experience input and output conges-                                                                             |       |

|            | tion respectively.                                                                                                                                | . 101 |

| 5.6        | Available compute-time slots (dotted-squares) for partitioning kernel 3.                                                                          |       |

|            | Because kernel 3 depends on kernel 2 (arrow), the lower bound and up-                                                                             |       |

|            | per bound of available time slots are the finish time of kernel 2 and 3                                                                           | 102   |

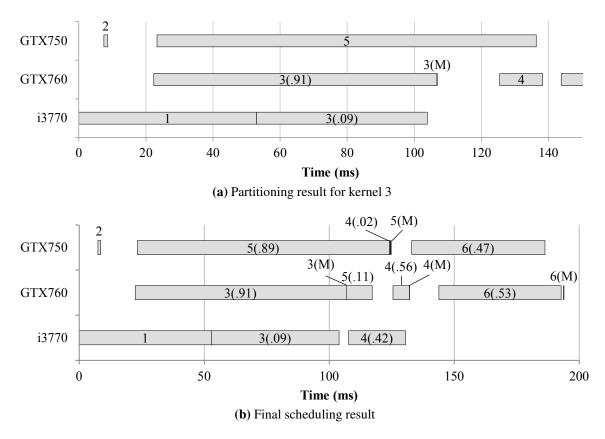

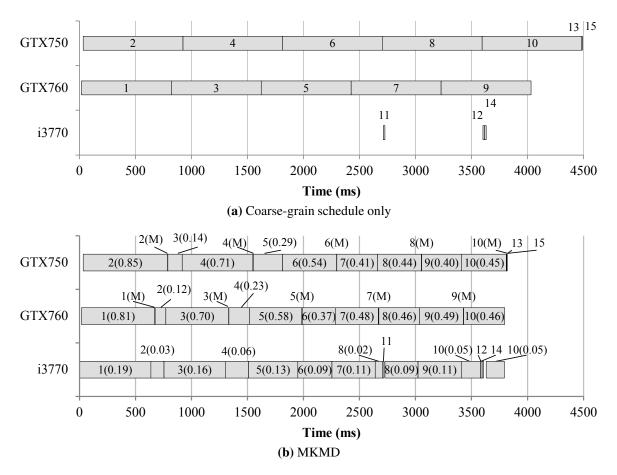

| 5.7        | respectively                                                                                                                                      | . 105 |

| 5.7        | the ratio of work-groups. The mark (M) is the cost for mering nonlinear                                                                           |       |

|            | outputs                                                                                                                                           | . 108 |

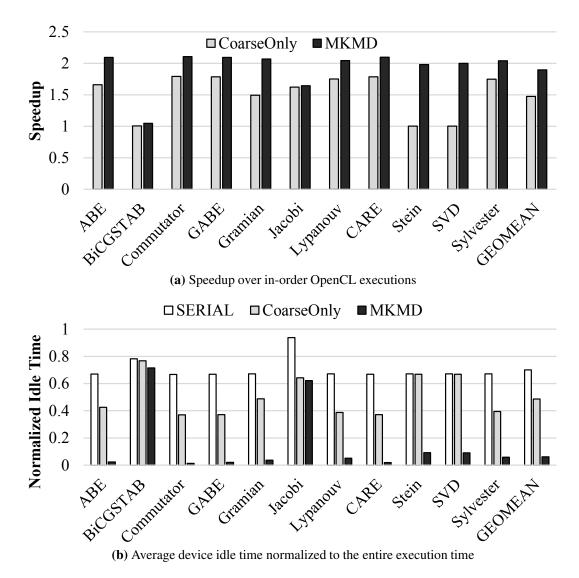

| 5.8        | (a) Speedup of MKMD over in-order executions, and (b) the average de-                                                                             |       |

|            | vice idle time normalized to the finish time.                                                                                                     |       |

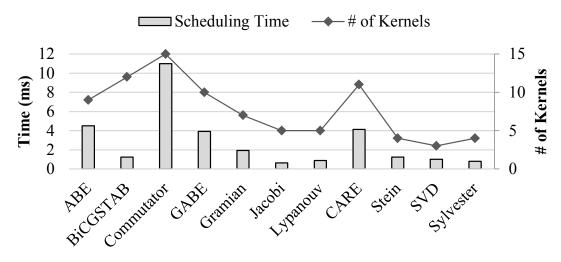

| 5.9        | MKMD scheduling overhead.                                                                                                                         | . 113 |

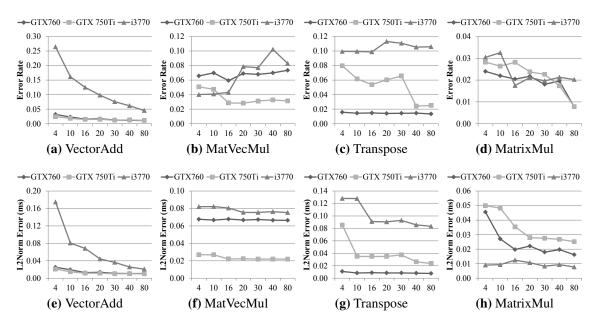

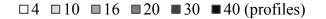

| 5.10 | Error rates and L2-norm error in milliseconds varying the number of pro-                                                                        |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | files for the execution time modeling. CPU has relatively high error rates                                                                      |    |

|      | on memory-intensive kernels as shown in (a), (b), and (c), but the execu-                                                                       |    |

|      | tion time of these kernels is trivial as they do not have much computation.                                                                     |    |

|      | As a result, the absolute error (L2-norm) in time is also small as illustrated                                                                  |    |

|      | in (d), (e), (f), and (g)                                                                                                                       | 5  |

| 5.11 | MKMD total execution time with different timing models varying the<br>number of profiles. The baseline is the execution time scheduled with the |    |

|      | model from 80 profiles. This result shows that the entire scheduling time                                                                       |    |

|      | is not sensitive to the number of profiles                                                                                                      | 6  |

| 5.12 | Kernel graph for triple commutator                                                                                                              | 17 |

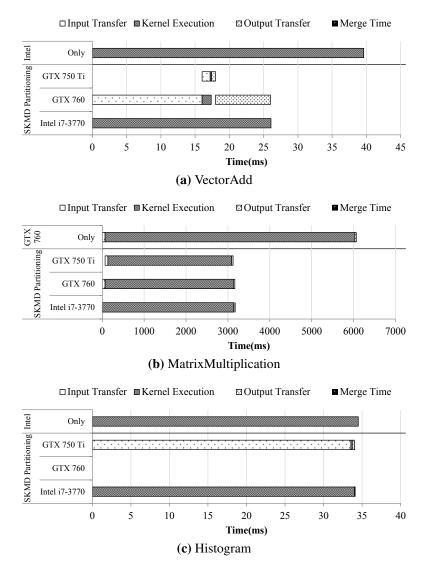

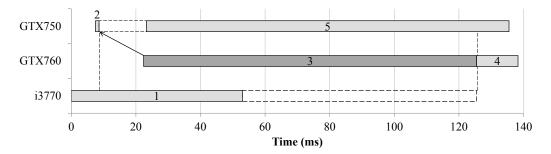

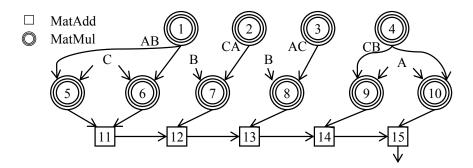

| 5.13 | Execution timeline for triple commutator. Because matrix computation                                                                            |    |

|      | is too expensive on i3770, (a) the coarse-grain scheduler does not sched-                                                                       |    |

|      | ule any matrix multiplication kernel on it while GPUs take more than 4                                                                          |    |

|      | kernels. With MKMD, (b) all devices are almost fully utilized 11                                                                                | 8  |

# LIST OF TABLES

### **Table**

| 3.1 | Experimental setup.                                                            | 36  |

|-----|--------------------------------------------------------------------------------|-----|

| 3.2 | Benchmark specification. VectorAdd, Blackscholes, BinomialOption, and          |     |

|     | ScanLargeArrays are classified as contiguous kernels, whereas others are       |     |

|     | defined as discontiguous kernels.                                              | 38  |

| 3.3 | Profile execution parameters and real execution parameters for evaluating      |     |

|     | performance prediction accuracy. For each profile, 16 profile data was         |     |

|     | collected varying the number of work-groups.                                   | 46  |

| 4.1 | Experimental Setup                                                             | 75  |

| 5.1 | Execution time estimation on NVIDIA GTX 760. The cost functions,               |     |

|     | $f(x_1,, x_N)$ , were statically analyzed. For example, $8^{th}Arg$ means that |     |

|     | the value of the $8^{th}$ argument is the trip count of a loop in the kernel.  |     |

|     | LocalSize(0) means the work-item count per work-group in the first di-         |     |

|     | mension, while the constant 1 means that a loop was not found in the           |     |

|     | kernel.                                                                        | 98  |

| 5.2 | Experimental Setup                                                             | 110 |

| 5.3 | Benchmark Specification                                                        | 111 |

|     |                                                                                |     |

### ABSTRACT

#### VIRTUALIZING DATA PARALLEL SYSTEMS FOR PORTABILITY, PRODUCTIVITY, AND PERFORMANCE

by

Janghaeng Lee

Chair: Scott Mahlke

Computer systems equipped with graphics processing units (GPUs) have become increasingly common over the last decade. In order to utilize the highly data parallel architecture of GPUs for general purpose applications, new programming models such as OpenCL and CUDA were introduced, showing that data parallel kernels on GPUs can achieve speedups by several orders of magnitude. With this success, applications from a variety of domains have been converted to use several complicated OpenCL/CUDA data parallel kernels to benefit from data parallel systems. Simultaneously, the software industry has experienced a massive growth in the amount of data to process, demanding more powerful workhorses for data parallel computation. Consequently, additional parallel computing devices such as extra GPUs and co-processors are attached to the system, expecting more performance and capability to process larger data.

However, these programming models expose hardware details to programmers, such as

the number of computing devices, interconnects, and physical memory size of each device. This degrades productivity in the software development process as programmers must manually split the workload with regard to hardware characteristics. This process is tedious and prone to errors, and most importantly, it is hard to maximize the performance at compile time as programmers do not know the runtime behaviors that can affect the performance such as input size and device availability. Therefore, applications lack portability as they may fail to run due to limited physical memory or experience suboptimal performance across different systems.

To cope with these challenges, this thesis proposes a dynamic compiler framework that provides the OpenCL applications with an abstraction layer for physical devices. This abstraction layer virtualizes physical devices and memory sub-systems, and transparently orchestrates the execution of multiple data parallel kernels on multiple computing devices. The framework significantly improves productivity as it provides hardware portability, allowing programmers to write an OpenCL program without being concerned of the target devices. Our framework also maximizes performance by balancing the data parallel workload considering factors like kernel dependencies, device performance variation on workloads of different sizes, the data transfer cost over the interconnect between devices, and physical memory limits on each device.

## **CHAPTER I**

# Introduction

Over the past decade, heterogeneous computer systems that combine multicore processors (CPUs) with graphics processing units (GPUs) have emerged as the dominant platform. The advent of new programming models such as OpenCL [37] and CUDA [58] makes it possible to utilize GPUs for processing massive data in parallel for general purpose applications. By leveraging these programming models, programmers can develop data parallel kernels for GPUs that achieve speedup of 100-300x in optimistic cases [55], and speedup of 2.5x in pessimistic cases [46].

As a result of these new ways to use massive data parallel hardware, applications from a variety of domains have been converted to OpenCL/CUDA programs. Meanwhile, the industry for large-scale data-intensive applications has grown rapidly, and now requires higher performance on data parallel processing of much larger sets of data [8, 59, 16]. Because hardware vendors cannot meet these demands with a single computing device (CPU or GPU including off-chip memories), they configured systems with additional GPUs, expecting applications to benefit from the additional devices.

Now the burden of improving performance and handling large data sets on increased

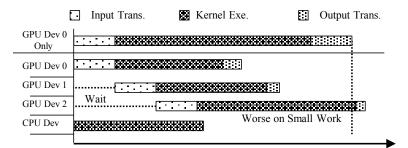

**Figure 1.1:** Challenges in exploiting multiple GPUs for large data sets. Because the programming model exposes the hardware details, programmers must consider portability, productivity, and performance when they write the data parallel kernels with large data on multiple devices.

computing devices must come from the software layers, e.g. applications, libraries, compilers and operating systems (OSs). In traditional software, the benefit from improved hardwares came for free as OSs virtualize underlying hardwares by providing the illusion of private computing resources to an application. Therefore, application programmers do not have to consider target hardware such as processor types and memory sub-systems for optimizing an application.

For data parallel software, although the OpenCL/CUDA programming model alleviated part of the complexity by providing unified processing interfaces, it still exposes hardware details to programmers, such as the number of processing elements, the size of off-chip memory, and interconnects between computing devices. Due to the absence of the virtualization layer between the hardware and OpenCL/CUDA program, we found three main challenges in using multiple GPUs: portability, productivity, and performance as shown in Figure 1.1.

#### **1.1** Challenges of Using Multiple GPUs

**Portability:** Different GPUs have different architectural specifications, e.g. the number of cores, the number of registers, maximum number of threads per processors, and the size of global memory. As a result, a data-parallel kernel optimized for a specific GPU is not guaranteed to be optimal for other GPUs. In the worst case, the execution may fail on other GPUs if there are not enough resources, such as physical memory. Most importantly, OpenCL/CUDA programming model exposes the computing devices of the system, so application programmers must write the code to list up available devices and pick a GPU to process data parallel kernels. Also, if a program is written to use a single GPU, simply attaching new additional GPUs does not bring any performance improvement.

**Productivity:** In order to make data parallel kernels with large data sets run on multiple GPUs, the programmer must restructure their code to operate within the limited physical memory space of a GPU by following several steps: 1) manually divide working sets to create a set of partial workloads; 2) change the kernel if the algorithm depends on the size of the working set; 3) transfer the working set back and forth between the application and GPUs; and, 4) merge the partial outputs from different GPUs into the application's memory address space. This process requires a deep analysis of the memory access pattern of the target kernel's working set, and substantial code is necessary to facilitate communication management between the application and GPU.

In addition to these efforts, if an application consists of multiple data parallel kernels, programmers must analyze the workload of each kernel to map kernels properly into the devices. During this process, they must also consider dependencies and communication cost between kernels.

This process is tedious and prone to errors and may fail if programmers are unable to statically determine the working set due to indirect array accesses.

**Performance:** To maximize the performance of data parallel kernels on multiple GPUs, statically determining where to execute or how much of the workload to assign to a device cannot be determined without knowing what resources will be available at the time of execution. For example, if the fastest GPUs are busy with another data parallel kernel, the application should select alternative GPUs as a computing device instead of waiting for the fastest GPU to be free. In addition, interconnects, such as Peripheral Component Interconnect Express (PCIe), must also be considered for the cost of data transfer because GPUs have separate memories that use different address spaces. If PCIe bus bandwidth is saturated by transferring another kernel's data, workload distribution over multiple GPUs must be different from the case where the bus is idle. With these dynamic behaviors, it is hard for programmers to statically decide a workload distribution that maximizes the performance.

Obviously, shifting all the burden of solving these issues on programmers is an unachievable goal. Instead, it is desirable to push as much of these responsibilities as possible to an additional abstraction layer of software that provides a seamless adaptation of application to hardware.

### **1.2** Contributions

In this thesis, we propose a dynamic compiler framework that significantly improves portability, productivity, and performance for multiple OpenCL kernels on multiple heterogeneous devices. This is accomplished by virtualizing computing units (CPU cores or GPU's streaming multi-processors), physical memory of GPUs, and the interconnect between devices. With the information of the underlying system, the framework takes multiple kernels from the applications, and schedules them on the physical devices considering kernel dependencies. The framework is fully transparent to OpenCL applications, thus the only responsibility for programmers is to write OpenCL kernels assuming that there is a single data parallel device.

The remainder of this chapter describes different frameworks that are specifically designed to virtualize multiple devices and physical memory space, and to schedule multiple kernels for improving portability, productivity, and performance.

#### 1.2.1 SKMD

In order to improve portability, productivity, and performance of OpenCL kernels on multiple devices, we propose *Single Kernel Multiple Device* (SKMD) [44], a dynamic system that transparently orchestrates the execution of a single kernel across asymmetric heterogeneous devices regardless of memory access pattern. SKMD transparently partitions an OpenCL kernel across multiple devices being aware of the transfer cost and performance variation on the workload, launches partitioned kernels for each devices, and merges the partial results into the final output automatically. For partitioning, performance for each device is predicted through a linear regression model which is trained offline. Using the performance prediction model, partitioning decision is made using *steepest ascent hill climbing heuristic* in order to minimize the execution time. SKMD is fully transparent to the applications, so it provides the illusion of a single device by virtualizing physical devices. As a result, SKMD not only eliminates the tedious process of re-engineering applications when the hardware changes, but also makes efficient partitioning decisions based on application characteristics, input sizes, and the underlying hardware. More details of SKMD are discussed in Chapter III.

#### 1.2.2 VAST

Although SKMD provides an abstraction layer for computing units and interconnects, it does not virtualize memory space of GPUs, exposing the physical memory of GPUs to the programmer. Without virtual address space on GPUs, SKMD cannot handle an application with large data that exceeds the physical memory of GPUs, so OpenCL applications are not fully portable to GPUs even with SKMD. For larger data sets, programmers must manually split the working set of the application to make data fit into physical memory, and manage the data transfer between the application and GPUs. This is still a huge burden for programmers. To increase the programming productivity, we present *Virtual Address Space for Throughput processors* (VAST) [43], a runtime system that provides programmers with an illusion of a virtual memory space for OpenCL devices. With VAST, the programmer can develop a data parallel kernel in OpenCL without concern for physical memory space limitations. In order to virtualize the memory space for GPUs, VAST uses a *inspector-executor* model, which inspects memory footprints of each thread before the real

execution, and efficiently extracts required working set of a subset of threads so as to not exceed the physical memory of GPUs. The extracted data is reorganized into contiguous memory space, and page tables are created for the address translation. Later, a subset of threads are executed accessing data through software address translation, and the execution of a subset of threads is repeated until all the threads finish their executions. Because VAST is able to process regardless of the type of kernels and fully transparent to the applications, it significantly improves portability and productivity of OpenCL applications. In Chapter IV, VAST is discussed in more detail.

#### 1.2.3 MKMD

As more applications are converted to utilize the highly data parallel architectures, applications are composed of several data parallel kernels communicating one another. Consequently, it is critical to map data parallel kernels properly onto multiple data parallel hardware in order to maximize the performance. However, it is difficult to manually map several data parallel kernels onto several computing devices because programmers must consider many factors like input size, type of data parallel kernels, kernel dependencies, the number of computing devices, and the interconnect between devices.

While SKMD and VAST virtualize computing resources and address space of GPUs, they focus only on a single kernel, so their executions can be suboptimal in terms of multiple data parallel kernels. For example, if there are two kernels that are independent each other, it could be better mapping kernels onto different devices separately rather than applying SKMD for each kernel.

To tackle this challenge, this thesis proposes Multiple Kernels on Multiple Device

(MKMD), a runtime system that does temporal scheduling of multiple kernels along with spatial partitioning across multiple devices. To achieve this goal, MKMD proposes a two-phase scheduling. The first phase builds a kernel graph and schedules at a kernel granularity maximizing the resource utilization. In this phase, an entire kenrel is executed by a single device. After than, the second phase reschedules kernels at the work-group granularity by spatially splitting kernels into sub-kernels considering temporal available computing resources. As a result of this phase, idle time slots on devices are removed. Further details of MKMD is described in Chapter V.

## **CHAPTER II**

## Background

The OpenCL programming model uses a single-instruction multiple thread (SIMT) model that enables implementation of general purpose programs on heterogeneous CPU/GPU systems. An OpenCL program consists of a host code segment that controls one or more OpenCL devices. Unlike the CUDA programming model, *devices* in OpenCL can refer only to both CPUs and GPUs whereas *devices* in CUDA usually refer to GPUs. The host code contains the sequential code sections of the program, which are run on the CPUs, and a parallel code is dynamically loaded into a program's segment. The parallel code section, i.e. *kernel*, can be compiled at runtime if the target device cannot be recognized at compile time, or if a kernel runs on multiple devices.

The OpenCL programming model assumes that underlying devices consist of multiple compute units (CUs) which are further divided into processing elements (PEs). The OpenCL execution model consists of a three level hierarchy. The basic unit of execution is a single *work-item*. A group of work-items executing the same code are stitched together to form a *work-group*. Once again, these work-groups are combined to form parallel segments called *NDRange*, *N-Dimensional Range*, where each NDRange is scheduled by a command queue. Work-items in a work-group are synchronized together through an explicit barrier operation. When executing a kernel, work-groups are mapped to CUs, and work-items are assigned to PEs. In real hardware, since the number of cores are limited, CUs and PEs are virtualized by the hardware scheduler or OpenCL drivers. For example, NVIDIA devices virtualize an unlimited number of CUs on physical streaming multi-processors (SMs) by quickly switching context of a work-group to another using a hardware scheduler.

For scheduling work-groups, devices do not have to consider the execution order of work-groups because the programming model relies on the relaxed memory consistency model. The OpenCL programming model uses relaxed memory consistency for *local* memory within a work-group and for *global* memory within a kernel's workspace, *NDRange*. Each work-item in the same work-group sees the same view of local memory only at a synchronization point where a *barrier* appears. Likewise, every work-group in the same kernel is guaranteed to see the same view of the global memory only at the end of kernel execution, which is another synchronization point. This means that the ordering of execution is not guaranteed across work-groups in a kernel, but only guaranteed across synchronization points.