# Vertical Integration of Germanium Nanowires on Silicon Substrates for Nanoelectronics

by

Lin Chen

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in the University of Michigan

2016

#### **Doctoral Committee:**

Associate Professor Wei Lu, Chair

Professor Cagliyan Kurdak

Assistant Professor Becky L. Peterson

Associate Professor Zhaohui Zhong

Copyright Lin Chen 2016

## Acknowledgements

First I would like to express my deepest appreciation and gratitude to my advisor, Prof. Wei Lu, for his patient guidance and mentorship from the day I applied for the PhD program, until the completion of this degree. This work would not have been possible without his unfailing inspiration and immense knowledge.

I would also like to thank my committee members, Prof. Cagliyan Kurdak, Prof. Peterson and Prof. Zhong, for their insightful comments and encouragement, which motivated me to improve this work from various perspectives.

I am also grateful to many current and former group members, including Jiantao Zhou, Chao Du, Ugo Otuonye, Wen Ma, Fuxi Cai, Dr. Wayne Fung, Dr. Siddharth Gaba, Dr. Patrick Sheridan, Dr. Yuchao Yang and Dr. Taeho Moon. In particular, I would like to thank Dr. Wayne Fung, who has been an excellent mentor and collaborator during my first two years in the program.

In addition, I would like to acknowledge the technical support of the Lurie Nanofabrication Facility (LNF) and the Electron Microbeam Analysis Laboratory (EMAL), especially the following staff members for their continuous assistance: Matt Oonk, Dennis Schweiger, Greg Allion, Shawn Wright, David Sebastian, Terre Briggs, Dr. Sandrine Martin, Dr. Nadine Wang, Dr. Vishva Ray and Dr. Kai Sun.

Last but not the least, my sincere thanks goes to my family and my friends, for their unconditional love and support throughout this PhD program and my life.

## **Table of Contents**

| Acknowledgements                                                   | ii   |

|--------------------------------------------------------------------|------|

| List of Tables                                                     | Vii  |

| List of Figures                                                    | viii |

| Abstract                                                           | xi   |

| Chapter 1 Overview                                                 | 1    |

| Chapter 2 Epitaxial growth of vertical Ge nanowire on Si substrate | 11   |

| 2.1 Introduction                                                   | 11   |

| 2.2 Overview of the nanowire growth process                        | 12   |

| 2.2.1 Vertical Ge nanowire growth                                  | 16   |

| 2.2.2 Si shell deposition                                          | 21   |

| 2.2.3 in situ Boron doping                                         | 22   |

| 2.2.4 Substrate chemistry and Au nanoparticle adhesion             | 26   |

| 2.3 Towards vertical device realization                            | 28   |

| 2.3.1 Selective area Ge nanowire growth                            | 29   |

| 2.3.2 Nanowire growth on Ge buffer layer                           | 32   |

| 2.4 Summary                                                        | 33   |

| Chapter 3 Characterization of Ge/Si heterojunction interface                   | 34 |

|--------------------------------------------------------------------------------|----|

| 3.1 Introduction                                                               | 34 |

| 3.2 Sample preparation                                                         | 35 |

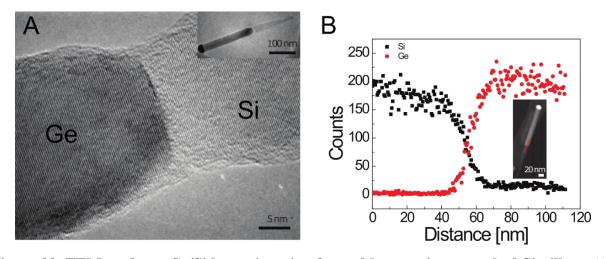

| 3.3 Microscopic study on Ge/Si heterojunction interface                        | 38 |

| 3.3.1 HRTEM                                                                    | 38 |

| 3.3.2 STEM/EDX line scan                                                       | 39 |

| 3.3.3 Additional notes                                                         | 40 |

| 3.4 Summary                                                                    | 43 |

| Chapter 4 Two terminal devices based on vertical Ge/Si heterojunctions         | 44 |

| 4.1 Introduction                                                               | 44 |

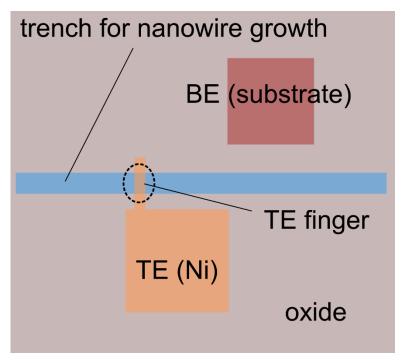

| 4.2 Fabrication of vertical two terminal heterodiode                           | 45 |

| 4.3 Regular PN diode based on Ge/Si p/n heterojunction                         | 49 |

| 4.4 Esaki diode based on Ge/Si p <sup>+</sup> /n <sup>+</sup> heterojunction   | 53 |

| 4.5 Non-ohmic contact based on Ge/Si p/p heterojunction                        | 56 |

| 4.6 Summary                                                                    | 61 |

| Chapter 5 Junctionless transistor based on vertical Ge/Si core/shell nanowires | 63 |

| 5.1 Introduction                                                               | 63 |

| 5.2 Fabrication of vertical junctionless transistors                           | 65 |

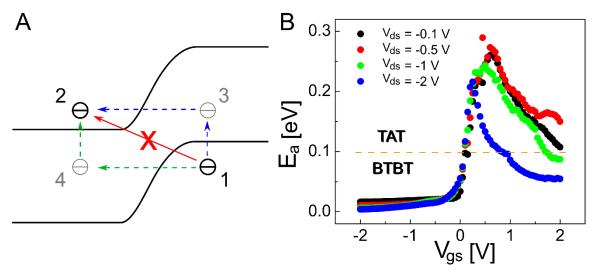

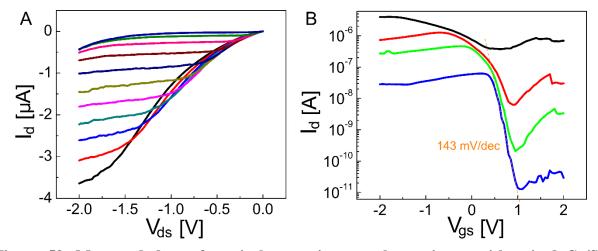

| 5.3 Vertical nanowire junctionless transistor performance                      | 69 |

| 5.3.1 Experimental characterization of nanowire junctionless transistors       | 69 |

|    | 5.3.2 Modeling nanowire junctionless transistors                         | 70  |

|----|--------------------------------------------------------------------------|-----|

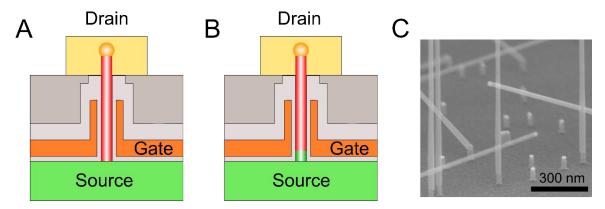

|    | 5.3.3 Gate length modulation and its impact                              | 78  |

|    | 5.4 All vertical nanowire junctionless transistor inverter               | 82  |

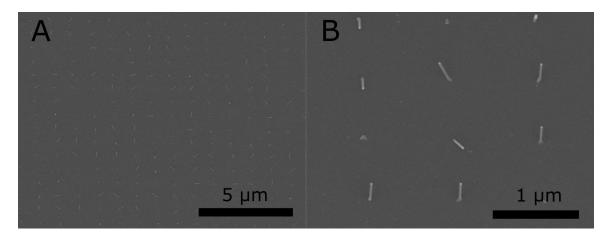

|    | 5.5 Summary                                                              | 85  |

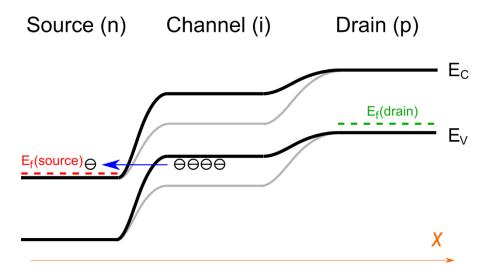

| Cl | napter 6 Tunnel transistor based on vertical Ge/Si core/shell nanowires  | 86  |

|    | 6.1 Introduction                                                         | 86  |

|    | 6.2 Tunnel transistor simulation                                         | 89  |

|    | 6.2.1 Overview of existing analytical TFET models                        | 90  |

|    | 6.2.2 Modeling tunnel transistors                                        | 93  |

|    | 6.2.3 Qualitative study on nanowire tunnel transistor performance        | 100 |

|    | 6.3 Experimental characterization of vertical nanowire tunnel transistor | 103 |

|    | 6.4 Summary                                                              | 110 |

| Cl | napter 7 Conclusion and future work                                      | 111 |

|    | 7.1 Vertical Nanowire growth on (111) Si substrate                       | 111 |

|    | 7.2 Characterization of Ge/Si heterojunction interfaces                  | 113 |

|    | 7.3 Two terminal devices based on vertical Ge/Si heterojunction          | 114 |

|    | 7.4 Vertical Ge/Si core/shell nanowire junctionless transistor           | 115 |

|    | 7.5 Tunnel transistors based on vertical Ge/Si core/shell nanowires      | 117 |

|    | 7.6 Some directions for future work                                      | 118 |

|    | 7.6.1 Deterministic site-control for nanowire integration                | 118 |

|      | 7.6.2 Optimization of tunnel transistor based on Ge/Si heterojunction | 120 |

|------|-----------------------------------------------------------------------|-----|

|      | 7.6.3 Vertical nanowire flash memory                                  | 120 |

| Refe | erences                                                               | 121 |

## **List of Tables**

| Table 1. Process parameters for boron-doped Ge nanowire growth          | 24 |

|-------------------------------------------------------------------------|----|

| Table 2. Parameters used in the simulation of junctionless transistors  | 77 |

| Table 3. Relation between PMMA concentration and resulting gate length. | 79 |

# **List of Figures**

| Figure 1. Overview of semiconductor nanowires and their applications                       | 3  |

|--------------------------------------------------------------------------------------------|----|

| Figure 2. Various gate structures for transistors.                                         | 5  |

| Figure 3. Power crisis in integrated circuits                                              | 6  |

| Figure 4. Schematic of supply voltage scaling and its effect on off-state current.         | 7  |

| Figure 5. Band diagram of TFET.                                                            | 7  |

| Figure 6. Schematic of 3-D integration of vertical nanowire transistors with CMOS circuits | 10 |

| Figure 7. VLS growth mechanism.                                                            | 13 |

| Figure 8. Ge nanowire growth with Au as catalysts.                                         | 17 |

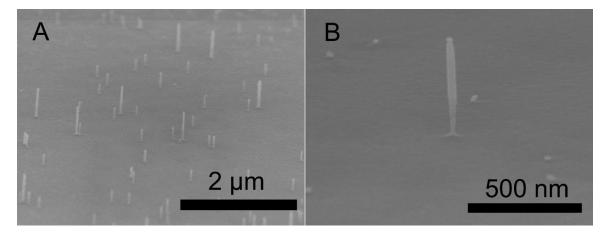

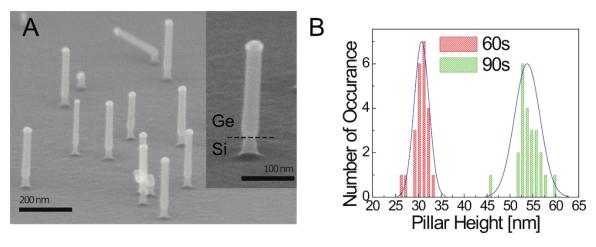

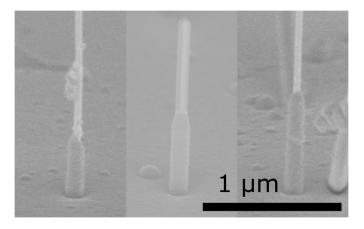

| Figure 9. SEM images of as-grown Ge nanowires.                                             | 20 |

| Figure 10. Heterostrcuture formation with VLS method.                                      | 21 |

| Figure 11. Ge nanowires grown with in situ Boron doping                                    | 25 |

| Figure 12. Effect of substrates on nanowire density                                        | 28 |

| Figure 13. Selective area growth of Ge nanwoires.                                          | 30 |

| Figure 14. Schematic of controlling nanowire location with post growth RIE.                | 31 |

| Figure 15. 75 degree tilted SEM images of vertical Ge nanowwires grown on Ge buffer layer. | 32 |

| Figure 16. Intrinsic Ge/Si band alignment.                                                 | 34 |

| Figure 17. 75 degree tilted SEM images of Ge nanowires on Si pillars after RIE.            | 36 |

| Figure 18. SEM image of Ge/Si heterojunctions transferred on TEM grid                      | 37 |

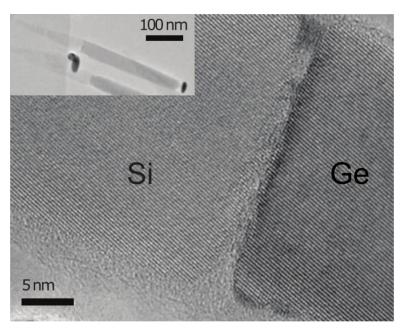

| Figure 19 HRTEM image of the nanowire heterostructure showing the Si/Ge interface.         | 38 |

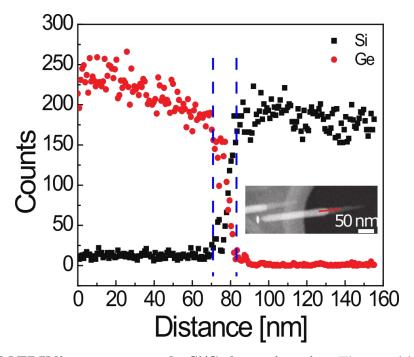

| Figure 20. STEM EDX line scan across the Si/Ge heterojunction.                        | 40 |

|---------------------------------------------------------------------------------------|----|

| Figure 21. The raised Si/Ge nanowire heterostructure.                                 | 41 |

| Figure 22. TEM study on Ge/Si heterojunction formed by growing on etched Si pillars   | 42 |

| Figure 23. SEM images of Al <sub>2</sub> O <sub>3</sub> removal process               | 46 |

| Figure 24. Schematic of the mask design for vertical heterodiodes.                    | 47 |

| Figure 25. Major steps for the vertical heterodiodes fabrication.                     | 47 |

| Figure 26. Vertical Si/Ge nanowire heterojunction devices.                            | 48 |

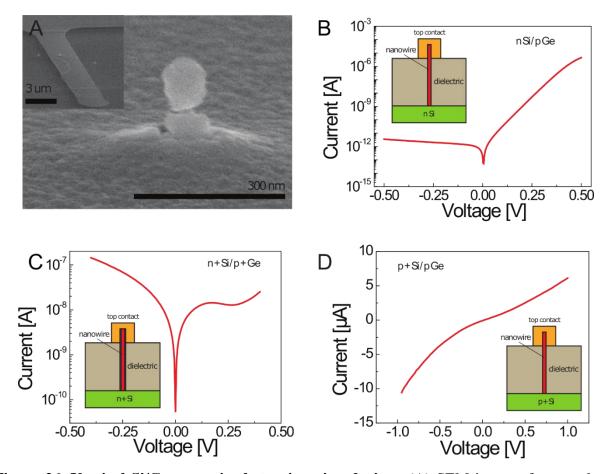

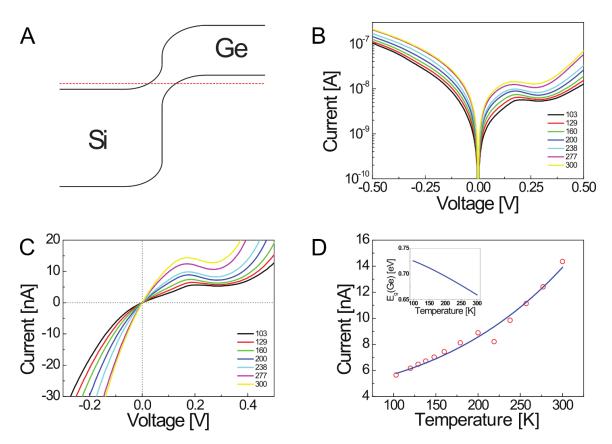

| Figure 27. Characteristics of the nSi/pGe diode.                                      | 50 |

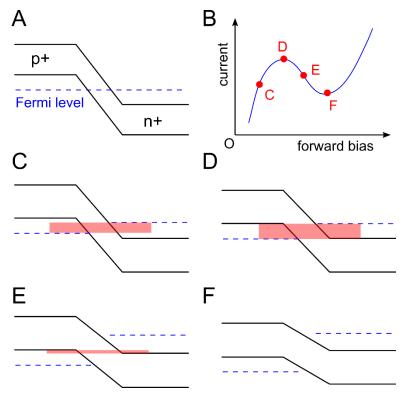

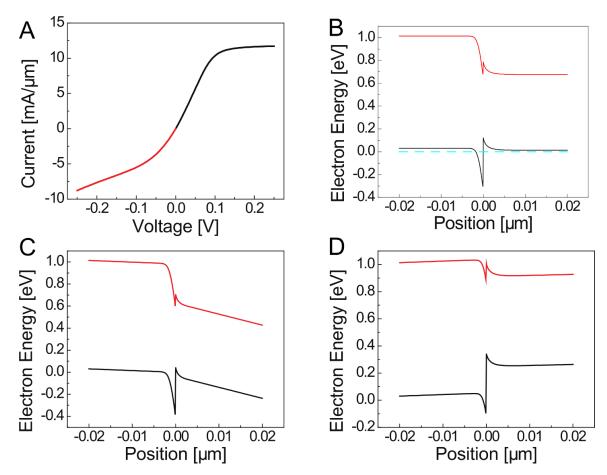

| Figure 28. Negative differential resistance in Esaki diodes.                          | 54 |

| Figure 29. Characteristics of the n+Si/p+Ge Esaki diode.                              | 55 |

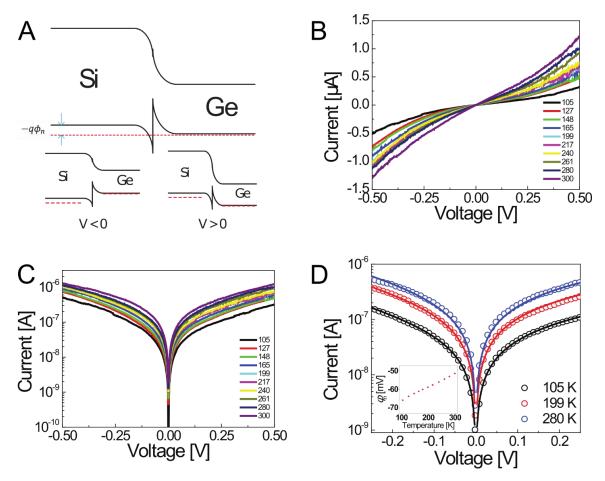

| Figure 30. Characteristics of the p+Si/pGe rectifying diode.                          | 57 |

| Figure 31. Numerical simulation results of the pSi/pGe structure using TCAD           | 59 |

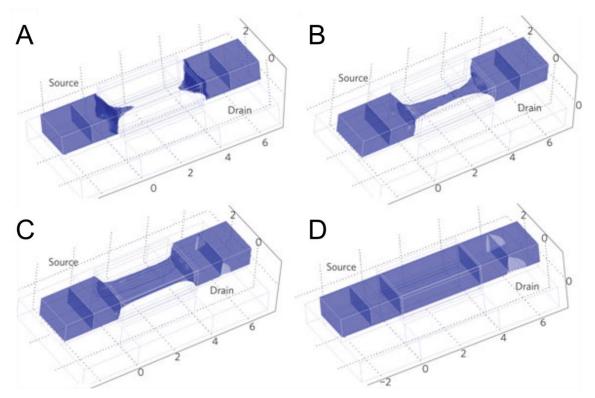

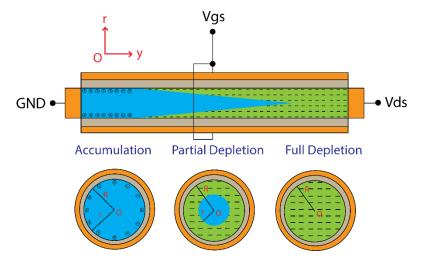

| Figure 32. Simulation of electron density for an n-type Si junctionless transistor    | 64 |

| Figure 33. Major steps for the vertical nanowire junctionless transistor fabrication  | 67 |

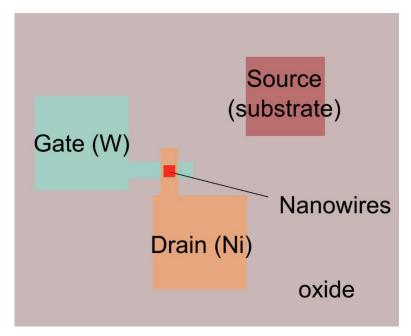

| Figure 34. Schematic of the mask design for vertical transistors.                     | 67 |

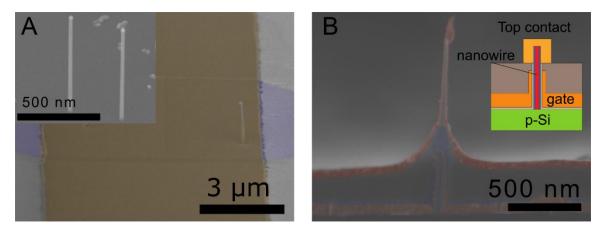

| Figure 35. SEM images of vertical nanowire junctionless transistor.                   | 68 |

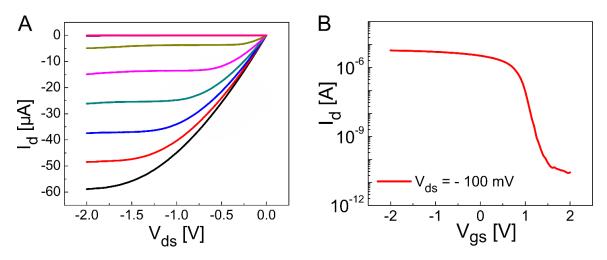

| Figure 36. Measurement results of vertical nanowire junctionless transistor           | 69 |

| Figure 37. Schematic of the simplified device structure used in modeling.             | 72 |

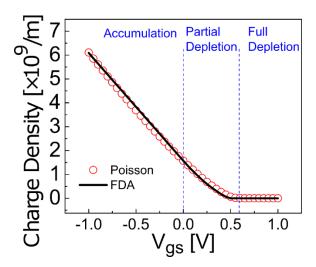

| Figure 38. Validation of the simplified equation using total charge density.          | 76 |

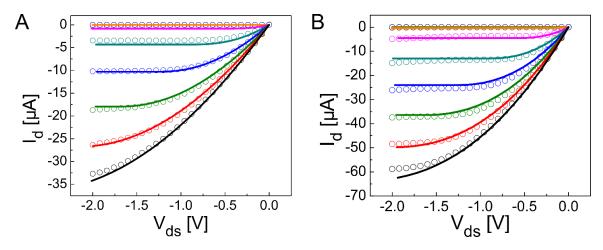

| Figure 39. Comparison of measurement results with simulation.                         | 77 |

| Figure 40. Controlling gate length by tuning the thickness of masking layer.          | 78 |

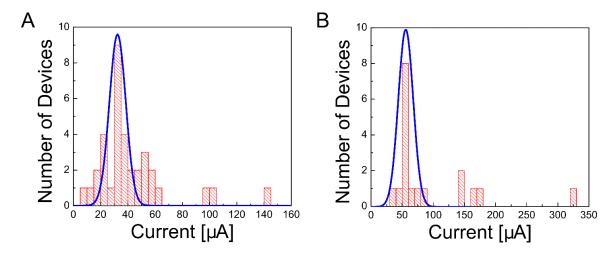

| Figure 41. Variation of device characteristics.                                       | 80 |

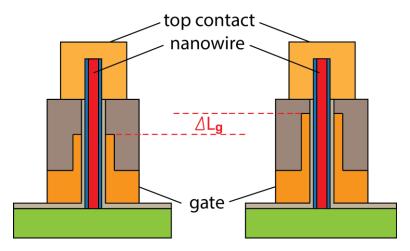

| Figure 42. Schematic of devices with the same total height but different gate lengths | 81 |

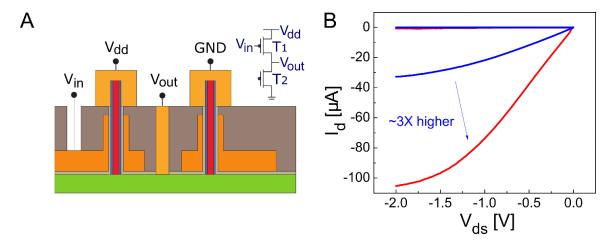

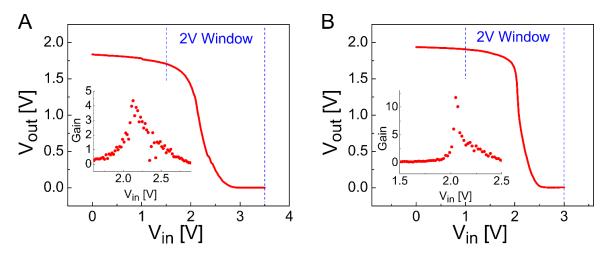

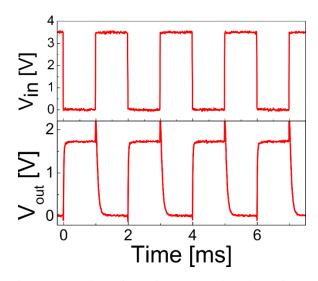

| Figure 43. Inverter consists of two vertical nanowire junctionless transistors                | 83  |

|-----------------------------------------------------------------------------------------------|-----|

| Figure 44. Voltage transfer characteristics of the inverter.                                  | 84  |

| Figure 45. Transient behavior of the inverter circuit at frequency of 500 Hz.                 | 85  |

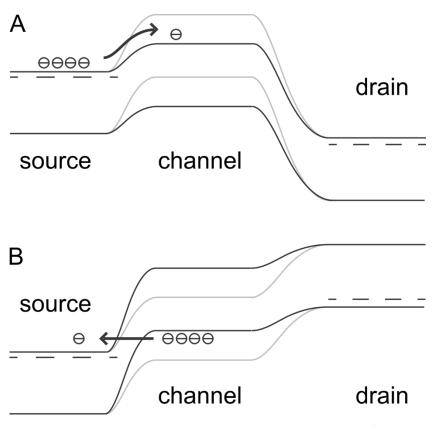

| Figure 46. Comparison of the operation principles between MOSFET and TFET                     | 87  |

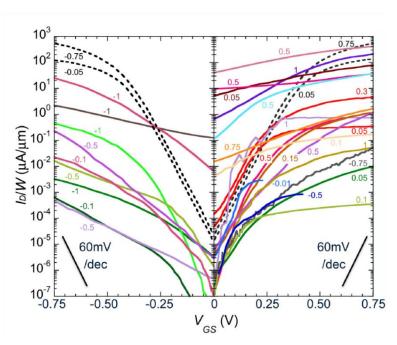

| Figure 47. Comparison of published TFET drain current density vs. gate voltage                | 88  |

| Figure 48. Schematic of the p-type TFET used in modeling.                                     | 93  |

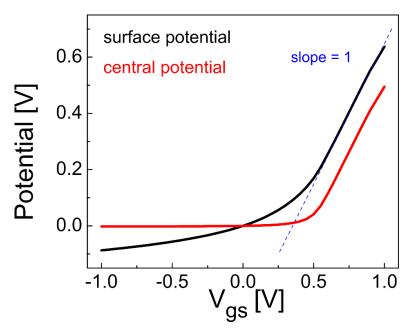

| Figure 49. Potential profile at different gate voltages                                       | 99  |

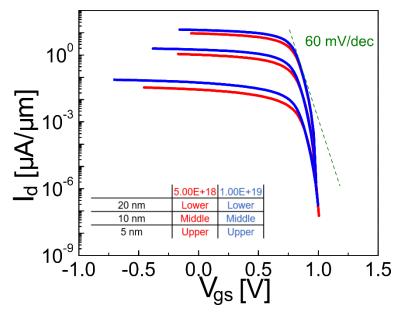

| Figure 50. Simulated TFET characteristics                                                     | .00 |

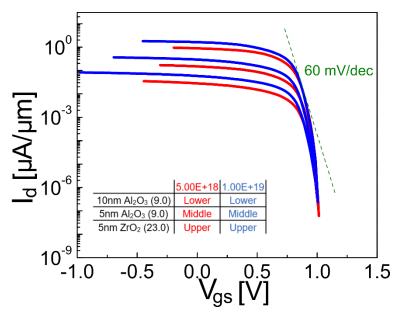

| Figure 51. Simulated tunnel transistor performance with various gate dielectric               | .01 |

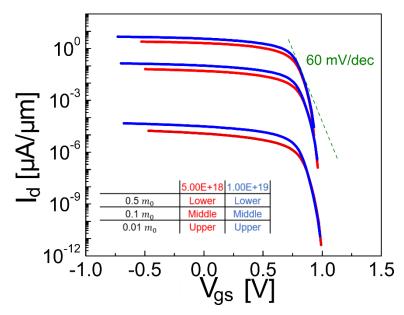

| Figure 52. Simulated tunnel transistor performance with various effective tunnel masses 1     | .02 |

| Figure 53. Simulated tunnel transistor performance with various nanowire diameters 1          | .02 |

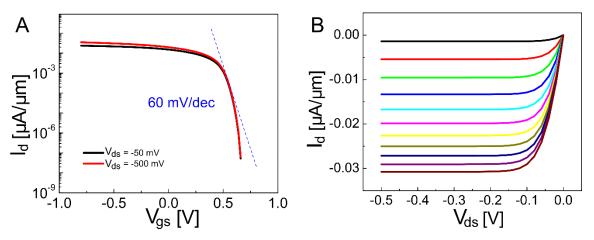

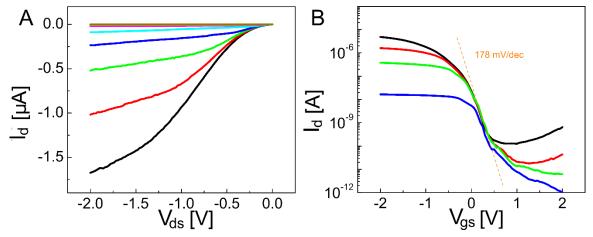

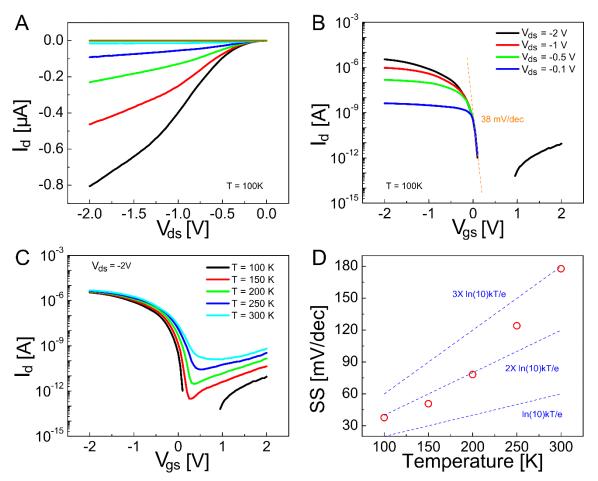

| Figure 54. Measured data of vertical nanowire tunnel transistors                              | .04 |

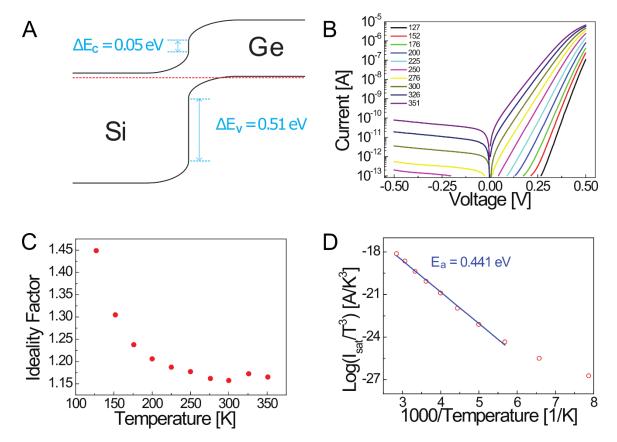

| Figure 55. Study of vertial nanowire tunnel transistos at various temperatures                | .05 |

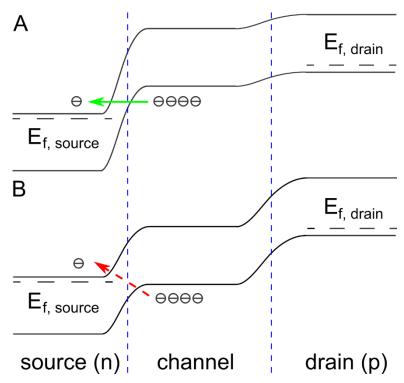

| Figure 56. Schematic of band diagrams of a TFET                                               | .06 |

| Figure 57. Trap assisted tunneling in TFET                                                    | .07 |

| Figure 58. Schematic of improved TFET design                                                  | .09 |

| Figure 59. Measured data of vertical nanowire tunnel transistors with raised Ge/Si junction 1 | .09 |

| Figure 60. SEM image of nanowires grown from an array of Au nanodots                          | 19  |

**Abstract**

**Vertical Integration of Germanium Nanowires**

on Silicon Substrates for Nanoelectronics

by

Lin Chen

Chair: Prof. Wei Lu

Rapid development of semiconductor industry in recent years has been primarily driven by

continuous scaling. As the size of the transistors approaches tens of nanometers, we are faced with

challenges due to technological and economic reasons. To this end, unconventional semiconductor

materials and novel device structures have attracted a lot of interests as promising candidates to

replace the Si-channel MOSFET and help extend Moore's law. In this dissertation, we focus on

chemically-synthesized germanium nanowires, and investigate their potential as electronic devices,

especially when vertically integrated on a Si substrate. The contributions of the work are as follows:

First, the Vapor-Liquid-Solid method for growing Ge nanowires on (111) Si substrates is

explored. In addition to the growth of vertical, taper-free, intrinsic Ge nanowires, strategies for

doping the nanowires, forming a radial heterojunction and controlling growth sites are also

discussed.

хi

Second, the Ge/Si heterojunction obtained via nanowire growth is examined by transmission electron microscopy. We confirm the epitaxial nature of the heterojunction despite the 4% lattice mismatch and determine the transition width to be 10-15 nm.

Vertical heterodiodes with independently-tuned doping profile in both Ge and Si are demonstrated. Different devices are obtained, including: (1) a rectifying diode with >10<sup>6</sup> on/off ratio and ideality factor of 1.16; (2) a tunnel diode with room temperature negative differential resistance, peak current density of 4.57 kA/cm<sup>2</sup> and reversed-bias tunnel current of 3.2  $\mu$ A/ $\mu$ m; (3) a non-ohmic contact due to large valence band offset between Ge and Si. All observed behaviors are very well supported by theoretical analysis of the devices.

In addition, a vertical junctionless transistor with Ge/Si core/shell nanowire channel and surrounding gate is demonstrated. High performance p-type transistor behavior with on state current density of 750  $\mu$ A/ $\mu$ m and mobility of 282 cm<sup>2</sup>/V·s is achieved. Moreover, an analytical model is developed to quantitatively explain the measured data and excellent agreement is obtained.

Finally, progress towards the realization of a nanowire tunnel transistor is reported. A physical model for nanowire tunnel transistors is proposed. Preliminary experimental results verified that the device concept works although further optimization is still required to boost its performance.

## Chapter 1

### Overview

Following the invention of the first transistor, the semiconductor industry has experienced tremendous growth over the past few decades. Although merely an observation when it was first proposed, Moore's law has been considered a roadmap and guided scientists and engineers working diligently to meet the rapid progress towards manufacturing integrated circuits with higher density and performance at a lower cost. Initially, this goal can be achieved through simply scaling the device dimensions. However, as the device size evolved from sub-micrometer and moved into nanometer range, scaling alone is not the solution anymore. In the past, there were a few times when Moore' law was seriously questioned, but every time, some innovative ideas were proposed to make the breakthrough the industry needed to keep up with the roadmap and continue pushing forward.

Looking back, the structure of a semiconductor transistor has undergone many changes to meet the continuously developing demands for performance and cost. Numerous improvements including strained Si (for improved mobility), high-k dielectric/metal gate (to suppress leakage current and provide higher gate capacitance) and carefully engineered doping profile (to prevent punch through) can be found in a modern transistor. Recent technological advances have allowed us to transform transistors from their original structure to the FinFET with tri-gate structure, marking the era of 3-D transistors. Now that the devices size has approached tens of nanometers, and we are faced with new obstacles that call for creative thinking again.

In large scale manufacturing, a top-down approach, where the critical dimension is lithographically defined and etched from a thin film, has been the mainstream since the very beginning. The top-down approach is capable of delivering precise size/location control, but its resolution is heavily dependent on the lithography and etching tools. A more fundament limit is posed by the wavelength of the photons used in the lithography tool. Without breakthroughs in advanced techniques such as e-beam and extreme ultraviolet (EUV) lithography, it will become more challenging and more importantly, less economical to define nanoscale features in modern devices using photolithography. In modern transistors, one or more dimensions is confined to the nanometer scale to gain various performance boosts. Ultimately, such aggressive scaling will evolve to nanowire channels in which carrier motion becomes largely one-dimensional. Aside from offering performance enhancement, nanowires are technologically promising since they can be fabricated through a bottom-up approach, in which they are chemically-synthesized, or grown. With this approach, critical dimensions such as diameter are controlled by process parameters, so that atomic resolution can be achieved without lithography.

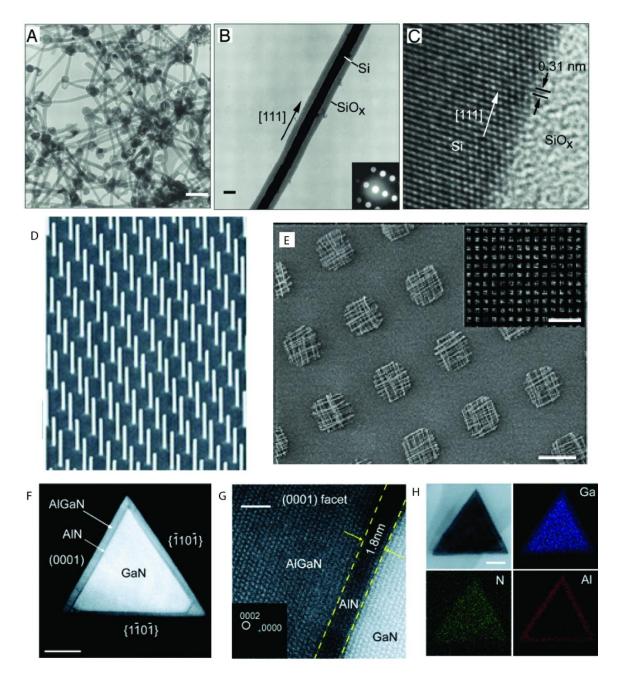

Being able to grow nanowires with different compositions, well controlled size, various crystal orientation and morphology plays an important role in recent developments of nanowire devices. The versatility of nanowires has been demonstrated in many applications where they are used as building block for electronics[1]–[11], photonics[12]–[23], solar cells[24]–[28], batteries[29]–[33], nanogenerators[34], [35] and biological/chemical sensors[36]–[43]. A wide range of materials can be synthesized in nanowire form, including but not limited to Si[44], Ge[45], III-V[16], [46]–[48], II-VI[49]–[51] and nitrides[52]. Different structures such as core/shell[53], [54], superlattice[16], [55] and branched nanowires[56], [57] can be realized and tailored to unique requirements. Figure 1 highlights a few notable applications for nanowire devices.[44], [58]–[60]

Not only are nanowires attractive for fundamental scientific research as they provide an excellent low dimension platform, they are promising candidates in future mass-produced electronics as well.

**Figure 1. Overview of semiconductor nanowires and their applications.** (A) TEM image of Si nanowires produced after ablation of a Si<sub>0.9</sub>Fe<sub>0.1</sub> target. Scale bar: 100 nm. (B) Diffraction contrast TEM image of a Si nanowire. Crystalline material (the Si core) appears darker than amorphous material (SiO<sub>x</sub> sheath) in this imaging mode. Scale bar: 10 nm. Inset: electron diffraction pattern recorded along the [211] zone axis perpendicular to the nanowire growth axis. (C) HRTEM image of the crystalline Si core and amorphous SiO<sub>x</sub> sheath. The (111) planes (black arrows) (spacing

0.31 nm) are oriented perpendicular to the growth direction (white arrow). (D) Tilted SEM image of a vertical InAs nanowire array grown on an InAs (111)B substrate. The spacing between nanowires is 0.5 μm. (E) SEM image of patterned crossed nanowire arrays. Scale bar: 10 μm. Inset: large area dark field optical microscopy image of the crossed arrays. Scale bar: 100 μm. (F) high-angle annular dark field scanning transmission electron microscopy (HAADF-STEM) image of the cross section of a GaN/AlN/AlGaN nanowire. Scale bar: 50 nm (G) lattice-resolved HAADF-STEM image recorded at the (0001) facet of the nanowire. Dashed lines highlight the heterointerfaces between layers. Scale bar: 2 nm. (H) bright field STEM image and corresponding EDS elemental mapping of the same nanowire, indicating spatial distribution of Ga (blue), Al (red) and N (green), recorded on a GaN/AlN/AlGaN nanowire cross section. Scale bar: 50 nm. From [44]. Reprinted with permission from AAAS. Adapted with permission from [58]–[60]. Copyright 2003, 2004, 2006 American Chemical Society.

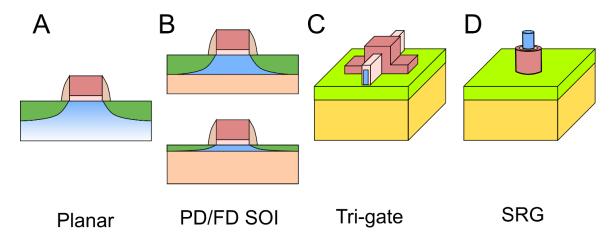

One major concern with continuous scaling is the need to suppress the short channel effect (SCE).[61] SCE such as drain induced barrier lowering (DIBL) starts to appear when gate gradually loses control over the channel in a scaled transistor. Essentially, as the channel length reduces, the gate capacitance needs to be enhanced proportionally to offer sufficient control over the underlying channel and ensure correct transistor operation. Usually this is achieved through scaling the gate oxide thickness along with other structural dimensions. However, this is not a sustainable approach as the gate leakage current grows exponentially with thinner oxides. It is found that the minimum channel length without incurring severe short channel effect is determined by factors such as channel thickness, oxide thickness, relative dielectric constant and gate structure.[62] By moving from planar transistors as shown in Figure 2A, to a partial/full depleted channel (Figure 2B), or 3-D FinFET (tri-gate, Figure 2C), gate control can be improved without reducing the oxide thickness. The best gate control is achieved when the whole channel is surrounded by gate dielectric (surrounding gate, or gate all around, GAA). However, GAA structures are technologically challenging to fabricate in a planar device, primarily due to difficulty of depositing material underneath the channel, which typically requires a sacrificial layer, a suspended channel and techniques like atomic layer deposition (ALD). To this end, nanowire devices can offer an interesting option to simplify the process by aligning the channel in the vertical

direction. As shown in Figure 2D, by depositing a thin metal film, surrounding gate can be readily achieved. Coupled with high-*k* dielectric, this may provide the boost needed for future high performance electronics.

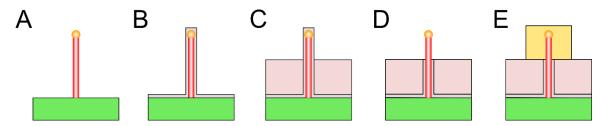

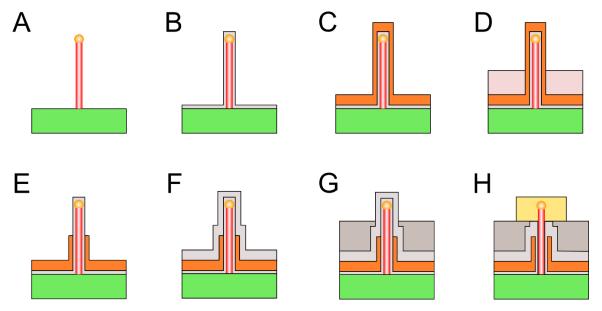

**Figure 2. Various gate structures for transistors.** (A) Planar channel. (B) Partially and fully depleted channel on SOI substrate. (C) FinFET, or Tri-gate. (D) Vertical nanowire with surrounding gate. Gate control is improved from (A) to (D).

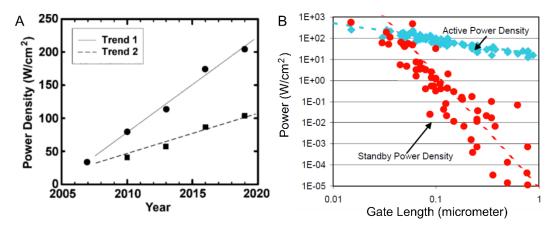

Another serious problem today's integrated circuit faces is increased power consumption. As shown in Figure 3A, with size reduction and the consequent increase in device density, power consumption per area increases at a fast pace.[63] Further increase in power consumption is not sustainable since the increased cost for associated packaging and cooling peripheral would render integrated circuits less economical. Power consumption in CMOS mainly consists of two components, active power  $P_{active} \propto V_{dd}^2$  when the device is switching and passive power  $P_{passive} = I_{off}V_{dd}$  when the device is idle. While it is obvious that scaling  $V_{dd}$  can reduce both active and passive power consumption, it requires  $V_{th}$  to be lowered proportionally to compensate for the reduction in  $I_{on}$ , because  $I_{on}$  must be proportional to  $(V_{dd} - V_{th})^2$  in first order approximation to maintain competitive circuit speed. The reduction in  $V_{th}$ , on the other hand, increases the passive power drastically due to the exponential dependence of  $I_{off}^{-1}$  on  $V_{th}$ . In actual circuits, the situation is somewhat better since normally threshold voltage is not scaled as

aggressively, but substantial increase in leakage current is still observed. For devices size above 100 nm, active power is the major contributor, as shown in Figure 3B. [64] Now that passive power takes the leading role, we have to seriously re-think our strategy in future circuit design.

**Figure 3. Power crisis in integrated circuits.** (A) Trend of power consumption per chip area. Trend 1 is calculated based on ITRS projected integration density and performance. Trend 2 is calculated based on increase chip size from year 2010. Adapted from [63]. © 2008 IEEE. (B) Comparison of active power and passive power as device scales. Adapted from [64].

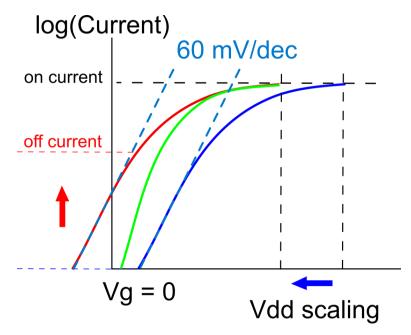

The increase of  $I_{off}$  poses a severe limit of MOSFET scaling. Physically, this effect is rooted in the finite subthreshold swing (SS), which is the inverse slope of the device transfer (*i.e.*,  $I_{ds}$  vs.  $V_{gs}$ ) characteristics. In essence, SS describes how much gate voltage is needed to turn the device off. It is limited to a minimum of 60 mV/dec at room temperature. This is due to the thermionic emission nature of the carriers in a MOSFET and originates from the tail in the Boltzmann distribution of electrons. Due to this fundamental limit, scaling of  $V_{dd}$  and  $V_{th}$  has essentially stopped while the device dimensions continue to be reduced, which raises additional problems such as device reliability, increased power dissipation and other high field effects. To address this problem, and to a broader content, the issue of power consumption, device characteristics similar to the green curve in Figure 4 are desired, which requires SS < 60 mV/dec to allow continued  $V_{dd}$  and  $V_{th}$  scaling. However, this means devices with a different operating mechanism must be developed.

Figure 4. Schematic of supply voltage scaling and its effect on off-state current. . The green curve represents an ideal device with sub-60 mV/dec switching so both high  $I_{on}$  and low  $I_{off}$  can be achieved simultaneously.

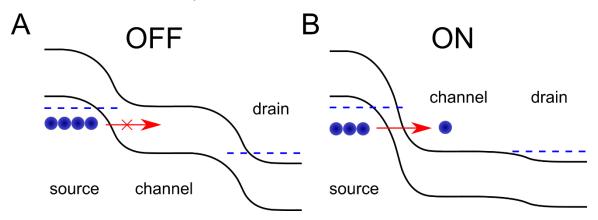

**Figure 5. Band diagram of TFET.** At OFF state, tunneling from source to channel is not allowed due to lackof available states in band gap. At ON state, band to band tunneling can occur between source and channel provided the electric field is sufficiently high.

For this reason, tunneling based devices have been an active research area in the search for an alternative, presumably low-power building block for integrated circuits. A tunneling field effect transistor (TFET) is essentially a reverse-biased p-i-n diode with a gate covering the intrinsic channel. The basic operation of an n-type TFET is schematically shown in Figure 5. When an overlap of the conduction band and valence band is achieved between the source and channel,

electrons in the valence band in the source can tunnel into the conduction band in the channel and get collected by the drain. Since in a TFET the carriers do not climb *over* a barrier, but tunnel *through* it instead, the turn-off rate is not limited by the Boltzmann distribution on the source side, and SS steeper than 60 mV/dec can potentially be obtained if the gate can change the tunnel junction width efficiently. To obtain a high  $I_{on}$  and a steep SS in a TFET, it is of paramount importance to create a high electric field (or equivalently thin tunnel barrier) and having efficient gate control to change the tunnel barrier thickness.

A number of studies have been performed to explore prototype TFET devices. So far, impressive off-currents and subthreshold slopes have been obtained.[65]–[74] In a TFET, the off state leakage current is governed by the thermionic current through a reverse biased p-i-n diode and can be suppressed to as low as  $0.12 \text{ pA/}\mu\text{m.}$ [69] Experimentally, several groups have achieved subthreshold slopes < 60 mV/dec in different materials and various device structures.[65], [66], [68] However, devices to date suffer from poor on-state performance due to a low band-to-band tunneling probability, which is exponentially dependent on the band gap and the thickness of the tunnel barrier. The highest  $I_{on}$  demonstrated to date is 12.1  $\mu$ A/um at 1 V (with SS < 60 mV/dec),[66] which is still two orders of magnitudes lower than that offered by state-of-the-art CMOS devices. Naturally, employing a narrow band gap material at the source/channel junction will provide improved on-state performance.[75] Additionally, heterostructures with staggered or even broken band alignment further reduces the effective tunneling barrier and could further improve the on-state performance.[76], [77]

In this dissertation, we focus on exploring Ge-nanowire based devices as a candidate for future nanoelectronics. Compared with other competitors such as III-V[8], [78], [79] and carbon based materials[80]–[82], Ge offers several unique advantages as a channel material. First, Ge can

offer both high electron mobility of 3900 cm<sup>2</sup>/Vs and hole mobility of 1900 cm<sup>2</sup>/Vs at room temperature.[83] Second, since Ge has been already introduced into semiconductor industry as a crucial component in strained Si, Ge is a proven CMOS compatible material more than the other alternatives.[84] Third, even though Ge has a relatively large lattice mismatch (4%) with Si, defect-free epitaxy of Ge nanostructures such as Ge nanowires on Si is possible due to coherent strain relaxation in the reduced volume.[11], [16], [85] Last but not least, with a smaller band gap (0.66 eV at room temperature, compared to 1.12 eV for Si) and lower effective mass for tunneling, Ge promises two orders of magnitude higher  $I_{on}$  at the same electric field compared with Si based TFETs.[86]–[88]

Ge nanowires used in this work are prepared via a bottom-up approach. We first focus on the techniques for Ge nanowire synthesis, in particular, engineering their morphology, orientation and composition. Then their potential for electronic devices is evaluated through a series of devices from the most basic pn diode to MOSFETs and TFETs. The goal is to fully understand their operation so we can gain insight for continued device optimization.

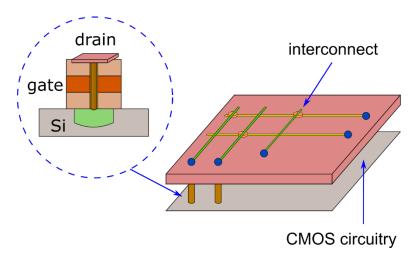

Another important field we would like to delve into in this dissertation is vertical integration of nanowire devices. Previous research on nanowire electronics has mostly focused on randomly deposited nanowires that are removed from the original growth substrate. The locations of the nanowires in these studies have to be learned from scanning electron microscopy (SEM) or atomic force microscopy (AFM) imaging and working devices have to be picked by hand.[1] As a result, these studies are limited to the proof-of-concept level, and the process are not sufficient for the fabrication of functional systems needed for real-world applications. Here we use an alternative scheme in which the vertical nanowire transistor structure can indeed provide an approach for nanowire circuit integration, as schematically illustrated in Figure 6. Ideally, vertical

nanowires can be grown on the same substrate with CMOS circuitry, either on the side or directly on top, eliminating the hassles of transferring and locating them after transfer. Since in our scheme the locations of the nanowires are determined by the growth process, full control of nanowire integration is possible. By designing appropriate interconnects, both nanowire/CMOS integration and the integration of different nanowire devices can be achieved for circuit applications.

Figure 6. Schematic of 3-D integration of vertical nanowire transistors with CMOS circuits.

The content of this dissertation is organized as follows. Chapter 2 discusses the synthesis of Ge nanowires on Si substrates and various techniques for the fabrication of Ge nanowire based devices. In chapter 3, we study the interface quality of the Ge/Si heterojunction, since device performance relies heavily on a clean, intrinsic interface. Several configurations of two terminal devices with independently tunable doping levels will be discussed in chapter 4, highlighting the flexibility of the Ge/Si system; In chapter 5, we demonstrate vertical Ge nanowire junctionless transistors and analyze their performance. In chapter 6, we propose an analytical model for the tunnel transistor and present some experimental progress towards vertical tunnel transistors based on Ge/Si core/shell nanowires. Finally, in chapter 7, we make some concluding remarks and discuss the future work that can be done after this dissertation.

## Chapter 2

## Epitaxial growth of vertical Ge nanowire on Si substrate

#### 2.1 Introduction

Semiconductor nanowires usually refer to crystal structures with diameters as small as few nanometers and lengths up to tens of micrometers or even millimeters. As mentioned in the previous chapter, the common techniques to acquire a particular structure in semiconductors can be roughly divided into two categories, a conventional "top-down" method where the shape is etched from a planar film, or "bottom-up" method where the structure is chemically grown, or synthesized. Nanowires are no different. So far, semiconductor nanowires have been demonstrated with both approaches.[10], [89]–[91] In a top-down process, the quality of the nanowires heavily depends on the starting material purity, although damages to crystalline structures are inevitable during size reduction steps such as dry etching, degrading its overall quality. The top-down approach also relies almost solely on the precision of the lithography/etching tools to produce nanoscale structures with good uniformity and consistency. With continuous device scaling, it has become more challenging and less cost-effective to do so. To the contrary, in a typical bottom-up process, the critical dimension of the nanowires (*i.e.*, diameter) is controlled by the chemical synthesis process and atomic resolution can be achieved with ease.

Synthesized nanowires offer many advantages such as small diameter, large surface-to-volume ratio, smooth surface and controlled material composition. For example, the large surface

area and small diameters allowed nanowire electrodes to outperform thin-film electrodes in battery applications with superior charging/discharging rate and better stability,[29] while the nearly-perfect material quality has enabled optical and electrical pumped nanowire lasers.[17], [19] Controlled nanowire growth has also enabled bio-sensors with integrated detectors and electrodes, all achieved in a single nanowire during growth.[41]–[43] Additionally, the suspended nanowire structure allows direct and *in situ* formation of heterostructures such as core/shell and axial heterostructures during growth, which can lead to improved electrical or optical properties tailored to specific applications.[6], [16], [53]–[55]

In this chapter, we discuss semiconductor nanowires fabricated via the bottom-up paradigm, in particular, Ge nanowires grown by Au catalyzed vapor-liquid-solid (VLS) process. In addition to exploring epitaxial integration of vertical Ge nanowires on Si substrates we will also discuss several techniques to either modify the Ge nanowire properties or provide more control over its location and morphology. These techniques are important since they pave the way for fabricating Ge nanowire based electronic devices and allow these devices to serve as building blocks in integrated circuits.

### 2.2 Overview of the nanowire growth process

The history of VLS growth can be traced back to the 1960s by Wagner who successfully employed this method to grow silicon microwires (whiskers).[92] Whisker research remained a productive field, however, the relatively large size (> 0.1 µm in diameter) of the whiskers produced in these early days offered few practical advantages compared with top-down fabricated structures. In fact, nanometer scale nanowires were not thought possible until the experimental demonstrations in 1998 by Morales *et al.*[44] The early demonstrations employed laser ablation to generate the source vapor needed for VLS growth to obtain single-crystalline Si and Ge nanowires.

Soon the process was expanded to more controllable methods such as chemical deposition (CVD) and VLS has become the dominant option for nanowire growth due to its simple realization yet flexible and excellent control over many aspects of the synthesis process.

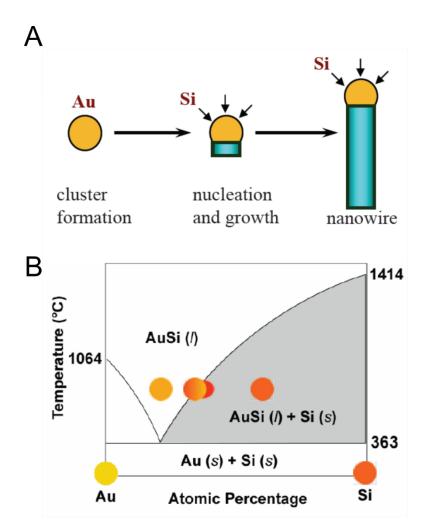

**Figure 7. VLS growth mechanism.** (A) Schematic of Au assisted VLS growth of Si nanowires. (B) Binary phase diagram of Au-Si system. © IOP Publishing. Reproduced with permission from [89]. All rights reserved.

In a typical VLS growth process, as schematically illustrated in Figure 7A, metal nanoparticles (either elemental particles such as Au, Ag, Cu, Al, Au or their alloys[93]) are employed as a catalyst to initiate and define nucleation, as well as facilitate activation/decomposition of the molecular reactants (if used). During the growth process, the metal nanoparticles are first heated up above the eutectic temperature for the target metal-semiconductor

system to create a liquid metal-semiconductor eutectic alloy. With the presence of the semiconductor source material in its vapor phase, the eutectic alloy will continue to incorporate the semiconductor material through the vapor/liquid interface, ultimately resulting in supersaturation of the semiconductor material in the eutectic alloy. Further addition of the semiconductor source material into the eutectic alloy will eventually result in a nucleation event whereby the semiconductor material precipitates and creates a liquid/solid interface, which is also referred as the growth interface. Nanowire growth is thus achieved via the transfer of the semiconductor material from the vapor source at the vapor/liquid interface into the eutectic alloy, followed by continued solid addition at the liquid/solid interface. In this manner, the name VLS growth accurately captures the essence of the growth process from the starting vapor source stage to the final solid crystal stage. It is also worth noting that as growth continues, the metal catalyst will remain at the tip as the nanowire elongates below the liquid/solid interface, as schematically illustrated in Figure 7A.[89]

The role of the metal nanoparticle is two-fold. First, it is used to form the eutectic alloy with the target semiconductor, and in doing so it also defines the diameter of a growing nanowire. The phase diagram of the Au/Si eutectic system is shown in Figure 7B, with a eutectic temperature of 363 °C with 19% Au in the alloy. This eutectic temperature is much lower than the melting temperature of either Au or Si so the VLS growth of Si nanowires can be carried out with Au catalysts in a low temperature system. Low-temperature growth can be advantageous, for example, by excluding impurities that might otherwise be trapped in growing Si at higher temperatures. Secondly, the metal nanoparticles normally serve as a catalyst that promotes the decomposition of the semiconductor gaseous precursor, thus selectively producing the semiconductor source material at the targeted growth sites. In the case of Si nanowire growth, SiH<sub>4</sub> and Au are normally

used as the precursor and catalyst, although other precursors such as Si<sub>2</sub>H<sub>6</sub>, SiH<sub>2</sub>Cl<sub>2</sub>, and SiCl<sub>4</sub> have also been employed.[93] The Au catalysts facilitate the decomposition of the precursor (*e.g.* SiH<sub>4</sub> into Si and H<sub>2</sub>) near the growth sites, as the Si atoms in turn incorporate into the Au nanoparticles to form the Au/Si eutectic alloy and eventually lead to VLS Si nanowire growth with Si atoms precipitate at the liquid/solid interface.

VLS nanowire growth is typically conducted in a chemical vapor deposition (CVD) chamber (including conventional hot-wall CVD, lamp-heated cold-wall CVD and metal organic CVD (MOCVD) systems) where the precursor materials are introduced in vapor phase. Precursor decompositions and nanowire growth take place at controlled temperatures and pressures. However, momentum and energy transfer methods such as pulsed laser ablation (PLA)[44] or molecular beam epitaxy (MBE)[94] can also be used to produce the vapor phase growth materials from solid targets, and VLS growth of nanowires using MBE and PLA have also been widely studied. The flexibility of the VLS method allows it to be used for the growth of a broad range of nanowire materials other than Si, covering other group IV materials such as Ge[45], group III-V (GaAs[46], GaP[16], InAs[48], InP[47], etc.), II-VI materials (ZnS[49], ZnSe[51], CdS[50], etc.) and nitrides[52]. This level of flexibility makes VLS the predominant method for semiconductor nanowire growth. In the case of compound material nanowires, the semiconductor reactants are usually provided by metal-organic chemical vapor deposition (MOCVD)[95] or PLA[96].

In a typical VLS-CVD process, the size of the nanowire is to a large extent determined by the size of the catalyst used. Wu *et al.* systematically studied the size distribution of Si nanowires synthesized using SiH<sub>4</sub>/H<sub>2</sub> and Au nanoclusters via the VLS method in well controlled conditions and reported that the sizes of the nanowires are consistently slightly larger than those of the catalyst used, which can be explained by the supersaturation of Si in Au which leads to the expansion of

the eutectic alloy volume compared to the starting pure Au nanoparticle.[97] Similar effects have also been reported in other VLS nanowire systems and verified through *in situ* imaging methods.[98] The excellent size control offered by VLS growth mediated with metal nanoparticles, which are commercially available at different specific diameters, offers a significant advantage over other methods such as laser ablation or thermal annealing of a thin metal film, and has become the dominating method of choice, and uniform nanowires with diameter down to a few nanometers can now be reliably obtained in a controlled fashion.

VLS growth is considered to be primarily thermodynamically driven since nanowires are synthesized mostly at near equilibrium conditions. The total free energy of the growth system includes the 'bulk' energy of the nanowire, the catalyst/nanowire (liquid/solid) interface energy, and the nanowire/vacuum (solid/vapor) interface energy and it is highly dependent on the nanowire orientation. As a result, usually a dominant nanowire orientation, determined by the minimum total free energy, can be observed. Note that this direction may also depends on other factors. For example, the preferred growth direction of Si nanowire was found to vary from <111> at larger diameters, to <112> at intermediate diameters (10-20 nm), to <110> at sizes below 10 nm.[97] The understanding and subsequent control of the preferred growth directions in turn allow the design and growth of epitaxial nanowire structures. While VLS growth on an amorphous substrate such as SiO<sub>2</sub> results in nanowires with random directions, epitaxial growth can occur with crystalline substrates, and more importantly, growth may occur along a certain direction that has low interface defect density.

#### 2.2.1 Vertical Ge nanowire growth

Ge nanowires used in this work were grown via the VLS method in a CVD tool (FirstNano Easytube 3000). Au nanoparticles with diameter of 20 nm (Ted Pella, Inc., part number: 15705-

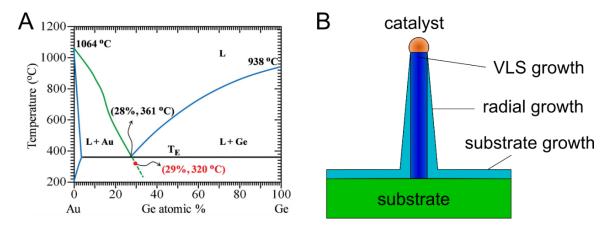

20) were typically used as catalysts while a mixture of GeH<sub>4</sub> and H<sub>2</sub> were used as processing gases. Figure 8A shows the phase diagram of the Au-Ge system where a eutectic temperature of 361 °C and 28% Au composition are indicated. It is worth noting that the low eutectic temperature of Au-Ge alloy allows for low-temperature synthesis of single crystalline materials, which can be particularly interesting for direct integration/growth of nanowire structures with existing CMOS circuits. It has been reported that the state of catalyst alloy depends on the thermal history and can be stabilized in liquid phase below eutectic point (*e.g.* 320 °C with 29% Au composition[99]), which makes low-temperature Ge nanowires attractive for thermally-sensitive substrates. During VLS growth, GeH<sub>4</sub> decomposes at the catalyst/vapor interface with the following reaction:

$$GeH_4 = Ge + 2H_2$$

which supplies Ge atoms throughout the process.

**Figure 8.** Ge nanowire growth with Au as catalysts. (A) Binary phase diagram of Au-Ge system. From [99]. Reprinted with permission from AAAS. (B) Schematic of different growth modes for the VLS process.

However, nanowire growth is not limited to one direction. As shown in Figure 8B, there are two competing processes in typical metal-catalyzed VLS growth: (1) catalyst-mediated precipitation through the liquid/solid interface which leads to axial elongation and (2) non-mediated direct vapor deposition on the existing nanowire sidewall surface. The latter process

results in radial thickening and eventually leads to tapering as the length of the nanowire increases. Deposition of thin film on the substrate is also possible, if the growth condition permits. Tapered nanowires are generally not preferable for most applications yet radial deposition can occur and may even dominate if growth conditions such as temperature and pressure are not optimized. In the example of Si nanowire growth, since deposition on the radial direction is not catalyzed by metal particles and thus requires a much higher activation energy, radial deposition can be suppressed at low growth temperatures, so the axial growth is the dominating process.[4] Similarly, a cold-wall CVD system with local, rapid heating, as opposed to a hot-wall tube furnace reactor, can promote nanowire growth with minimal tapering.[100]

Thus, a two-step growth recipe was developed to achieve Ge nanowire growth with uniform diameter. First Au nanoparticles were deposited on Si (or SiO<sub>2</sub>) substrate after it was properly cleaned (Piranha process followed by diluted-HF treatment). Commercial Au nanoparticles (Ted Pella Inc., part number: 15705-20) are stabilized and suspended in deionized water (DI). They are drop cast (in as received state) on the substrate following the application of surfactant such as Poly-L-lysine (Ted Pella Inc., part number: 18026). Typical application time for Poly-L-lysine is 3-5 min (drop cast on the growth substrate) before the sample is rinsed in DI water and dried with N<sub>2</sub>. Au nanoparticles were also rinsed in DI water and dried with N<sub>2</sub> before the sample was quickly transferred to CVD chamber. The first step was carried out at 360 °C, 45 Torr (0.9% GeH<sub>4</sub> in H<sub>2</sub>) for 1 min. The purpose of this step is to create the Au-Ge alloy with sufficient yield and help the nanowire nucleate. Thus high temperature is required. The duration was kept to 1 min and remained unchanged for all nanowire lengths, to prevent excessive sidewall deposition which would result in tapered wires at such high temperatures. The subsequent elongation step occurs at 300 °C with the same gas composition for 5-30 min depending on the length required.

The low temperature was key to suppress unnecessary GeH<sub>4</sub> decomposition at the nanowire sidewalls so that tapering can be minimized. A substrate heater was used throughout the process to ensure localized heating to mimic a cold-wall CVD system.

If an amorphous substrate such as SiO<sub>2</sub> is used, nanowires will grow with random orientations. It would be more useful if the growth can be confined to the vertical direction. In fact, vertical growth of Ge nanowires is possible on Si substrates having certain orientations. As explained previously, the VLS process has preferable growth directions due to thermodynamic reasons. In the case of Ge nanowire growth, <111> is the most favorable direction. For example, Jagannathan *et al.* observed that Ge nanowires grew predominately along the <111> direction on crystalline Si substrates.[101] Interestingly, epitaxial <111> Ge nanowire growth is always obtained regardless of the Si substrate orientation. For example, with a (111) Si substrate, most of the Ge nanowires will be vertical; while with a (100) or a (110) Si substrate, the Ge nanowires will instead grow at a tilted angle to maintain the <111> growth direction. For this reason, most of our growth experiments were carried out on (111) Si, to maximize the verticality of the resulting nanowires.

Though vertical growth of Ge nanowire on (111) Si substrate is thermodynamically favorable, good care still must be taken during sample preparation and growth to ensure vertical epitaxy. Similar to the CVD of thin films, high vacuum is generally key to achieve good epitaxy, as the formation of an interfacial native oxide layer will hinder the CVD process and cause degraded yield. It is also found that by adding 0.1M HF into the Au colloid solution (HF concentration is based on total volume) and transferring the sample to the CVD chamber immediately after catalyst dispersion, native oxide formation can be suppressed and high vertical growth yield can be obtained on (111) Si substrates.[45]

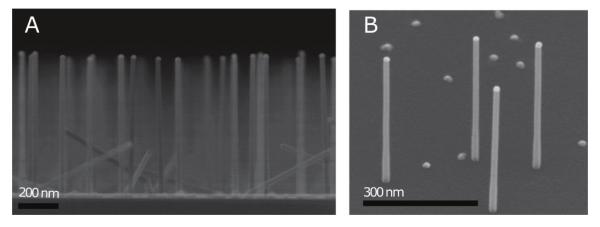

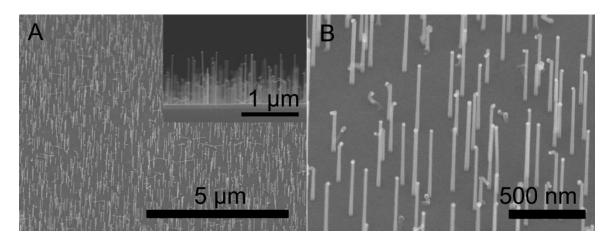

By carefully preparing the (111) Si substrate and catalyst solution to eliminate native oxidation, vertical Ge nanowire growth was achieved with a two-step recipe to suppress tapering. Figure 9 shows two scanning electron microscopy (SEM) images taken at 90 and 45 degree tilted angles after 1 min nucleation and 5 min elongation. The growth results showed good vertical yield and uniform height, which means that most of the nanowires were nucleated at roughly the same time. For those non-vertical nanowires, they tend to follow one of the three equivalent <111> directions, which has a fixed 35.3 ° angle with the substrate, indicating good epitaxy from the underlying (111) Si template. Nanowires grown via the two-step recipe indeed showed little tapering as expected. Most of the nanowires still have a slightly wider base, which was formed during the first nucleation step. With 20 nm Au nanoparticles, the diameter of the Ge nanowires obtained was  $20.2 \pm 1.1$  nm (measured near the top of nanowire from SEM). We can observe the remaining Au catalyst on top of the nanowire, with approximately the same diameter as the nanowires. The nucleation yield was not 100%, with un-nucleated catalyst particles scattered across the substrate. The nucleation yield can be improved with a longer nucleation step, which will lead to nanowires with a more tapered shape and more unevenly distributed lengths.

**Figure 9. SEM images of as-grown Ge nanowires.** SEM images taken from (A) 90 (B) 45 degree tilted angle showing vertical Ge nanowire growth. Adapted with permission from [102]. Copyright 2013 American Chemistry Society.

#### 2.2.2 Si shell deposition

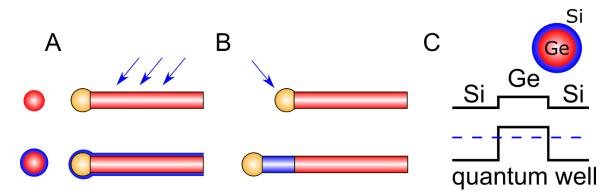

The VLS process can be readily adopted to create atomically sharp heterostructures in a controlled fashion. There are two main categories of nanowire heterostructures: axial heterostructures where segments of nanowires consist of different materials with the same diameter; and radial heterostructures in the form of core/shell or core/multi-shell structures. Similar to the tapering discussed earlier, there are usually two competing deposition processes during VLS heterostructure growth, *i.e.*, decomposition/deposition at the vapor/solid interface of the exposed nanowire sidewalls and precipitation at the liquid/solid interface of the nanowire growth front. The relative growth rates of these two processes determine whether an axial or radial heterostructure will be created: a radial heterostructure will be formed if the sidewall deposition dominates (Figure 10A); while an axial heterostructure can be obtained if reactants are exclusively deposited through the liquid/solid interface (Figure 10B). In the case of radial heterostructure, coating over the catalyst nanoparticle can be observed since sidewall deposition is conformal.

**Figure 10. Heterostreuture formation with VLS method.** Schematic of (A) radial and (B) axial heterostructure formation. (C) Band diagram of Ge/Si core/shell heterostructure and quantum well formed in Ge core.

Compared to a homogeneous nanowire, a core/shell nanowire heterostructure can be tailored through band structure engineering to provide better electrical and optical properties. For example, similar to the formation of two-dimensional electron and hole gases in high-electron

mobility transistors (HEMTs), one dimensional electron and hole gases can be obtained in core/shell nanowires by choosing the core and shell materials with appropriate band alignment. As shown in Figure 10C, with a thin Si shell grown epitaxially around a Ge core, a large valence band offset of *ca*. 500 meV between Ge and Si at the interface provides quantum confinement that leads to the accumulation of free holes in the Ge core channel when the Fermi level lies below the valence band of the Ge core. As a result, a Ge/Si core/shell nanowire will act as if it is heavily ptype doped even though both materials are not intentionally doped during the growth.[6] This can be particularly useful since the carriers in the Ge core exhibit a long mean free path and high mobility without dopants acting as scattering centers, making them ideally suited for applications such as high performance nanowire transistors[6] and low-temperature quantum electronics[103]–[105].

In our experiment, the Si shell was deposited *in situ* after vertical Ge nanowires were first grown. The Si deposition process was carried out at a higher temperature (465 °C) to enhance deposition at the vapor/solid interface. A mixture of SiH<sub>4</sub> and H<sub>2</sub>, where H<sub>2</sub> is the carrier gas was used (flow rates of SiH<sub>4</sub> and H<sub>2</sub> are 20 and 200 sccm, respectively). The total pressure was kept at 4.5 Torr throughout the shell deposition. It is found that approximately 2 nm of Si shell is conformally coated on a Ge nanowire with 3.5 min of shell deposition.

#### 2.2.3 *in situ* Boron doping

In integrated circuits, semiconductor nanowires can act as versatile building blocks for devices, particularly if different doping types are available with spatial control on an atomic level. The geometry of the nanowires, *i.e.*, high aspect ratio, makes conventional doping methods such as diffusion and ion implantation challenging. Instead, a more practical approach is through *in situ* doping of semiconductor nanowires during growth by adding dopant gaseous precursors to regular

processing gases. The basic principle is simple and both n-type and p-type doping have been realized in commonly used semiconductor nanowires, including Si, Ge, SiC, III-V, II-VI compound and metal oxides.[106]

The doping method is quite similar to VLS nanowire growth. As shown in Figure 8B, dopant atoms can be incorporated into the nanowires at the same time via two modes, namely, radial deposition and axial incorporation through the eutectic alloy. In axial incorporation, dopants enter nanowire through vapor/liquid and liquid/solid interface. The rate of dopant incorporation and final doping concentration are determined by the combined effect of dopant solubility in the liquid alloy and the segregation coefficient at the liquid/solid interface. On the other hand, dopants can enter nanowires radially through adsorption and capture at the vapor/solid interface. This mechanism can probably be described by thin film deposition theory.[106]

The addition of dopant species can also affect nanowire growth depending on the material added and the process conditions. Tapered nanowires due to the unintentional thin film deposition on nanowire sidewalls were usually observed. Such deposition can be minimized by proper tuning of the growth conditions, but enhanced side wall deposition is still often observed, especially in the presence of B<sub>2</sub>H<sub>6</sub>.[107] This is likely due to catalyzed decomposition of the semiconductor precursor with B<sub>2</sub>H<sub>6</sub>, a well-known effect in the deposition of Si thin films.[108] Unlike Si nanowires where *in situ* doping by PH<sub>3</sub> and B<sub>2</sub>H<sub>6</sub> with minimal morphology change has been demonstrated with optimized growth conditions,[109], [110] *in situ* doping of Ge nanowire often results in tapered nanowires.

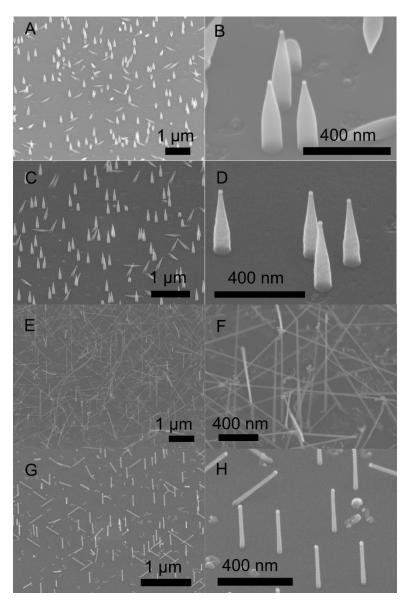

We studied the effect of  $B_2H_6$  by adding it to the processing gas with different atomic ratios during the nanowire elongation step. The growth results are shown in Figure 11A-F. The tuning of Ge:B ratio was achieved by replacing part of  $H_2$  carrier gas with  $B_2H_6$  while other process

parameters such as temperature, pressure and time were kept unchanged. Three different ratios were tested, from 100:3 (Figure 11A/B), to 4000:1 (Figure 11C/D) and 40000:1 (Figure 11E/F). The mass flow controller (MFC) that is installed in the CVD system has 200 sccm range with 2 sccm sensitivity. The B<sub>2</sub>H<sub>6</sub> (in H<sub>2</sub>) source available has B<sub>2</sub>H<sub>6</sub> concentration of 99 ppm. Therefore, 40000:1 is the maximum Ge:B ratio we can achieve in the experiment. The details of the growth condition are summarized in Table 1. Nanowires used in these studied were grown on (111) n+ Si substrate which was clean with the standard Piranha process and diluted HF treatment.

|                  | Temperature (°C) | Total<br>pressure<br>(Torr) | H <sub>2</sub> (sccm) | 10%<br>GeH <sub>4</sub><br>in H <sub>2</sub><br>(sccm) | 1%<br>B <sub>2</sub> H <sub>6</sub><br>in H <sub>2</sub><br>(sccm) | 99<br>ppm<br>B <sub>2</sub> H <sub>6</sub><br>in H <sub>2</sub><br>(sccm) | Time (min) | Ge:B<br>ratio |

|------------------|------------------|-----------------------------|-----------------------|--------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------|------------|---------------|

| (A-F) nucleation | 360              | 45                          | 200.0                 | 20                                                     | -                                                                  | -                                                                         | 1          | n/a           |

| (A-B) elongation | 300              | 45                          | 197.5                 | 20                                                     | 2.5                                                                | -                                                                         | 5          | 100:3         |

| (C-D) elongation | 300              | 45                          | 197.5                 | 20                                                     | -                                                                  | 2.5                                                                       | 5          | 4000:1        |

| (E-F) elongation | 300              | 45                          | 17.5                  | 200                                                    | -                                                                  | 2.5                                                                       | 5          | 40000:1       |

Table 1. Process parameters for boron-doped Ge nanowire growth.

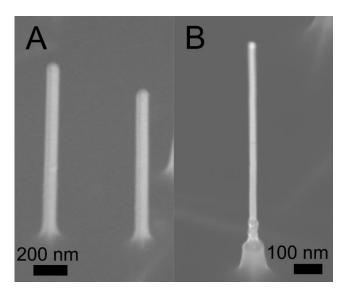

The difference in nanowire morphology is evident. Tapering is suppressed by decreasing Boron content. Nanowires shown in Figure 11A-D have a cylindrical base with a large diameter (~96 nm in Figure 11B and ~75 nm in Figure 11D) and cone-shaped body with a Au nanoparticle on top. We hypothesize that the cylindrical part was grown during nucleation while the cone-shaped body was grown during elongation as they are exposed to B<sub>2</sub>H<sub>6</sub> gas for different durations. The segment closer to the tip of the nanowire was grown later in the process. As a result, radial coating has a lesser effect on it. Comparing Figure 11B to Figure 11D, the base diameter was reduced for growth with a higher Ge:B ratio while the vertical yield and average nanowire height were almost the same. Nanowires grown in Figure 11E/F have very different morphology,

probably due to non-optimized process parameters since all gas flows were increased ten-fold to achieve 40000:1 ratio. Nevertheless, the nanowires in Figure 11E/F are almost free of tapering. They are much longer than the ones in Figure 11A-D, which were grown with the same duration. These results are consistent with the theory that the presence of  $B_2H_6$  can enhance non-selective decomposition of  $GeH_4$  on nanowire sidewalls.

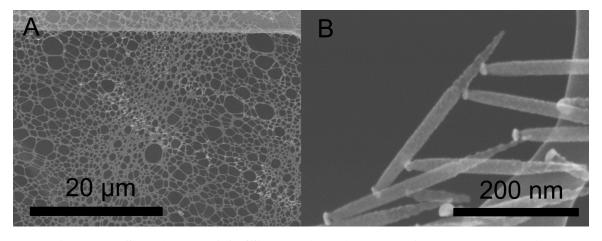

**Figure 11. Ge nanowires grown with** *in situ* **Boron doping.** (A-F) B doped NW with different Ge:B ratios of (A-B) 100:3 (C-D) 4000:1 and (E-F) 40000:1. (G-H) Ge nanowire grown with a surface doping layer.

An alternative route to achieve doping without incurring the tapered shape is to dope the nanowire surface without the GeH<sub>4</sub> precursor, eliminating the thin film deposition altogether. For example, Greytak *et al.* successfully doped Ge nanowires, after pure Ge nanowire elongation, with either PH<sub>3</sub> or B<sub>2</sub>H<sub>6</sub> in the absence of GeH<sub>4</sub> to produce a self-limiting layer of electrically activated dopant atoms.[100] This approach is verified using our growth chamber too. Figure 11G/H shows vertical taper-free Ge nanowires with B-rich surface on Si substrate. Surface doping was achieved via flowing B<sub>2</sub>H<sub>6</sub> (0.05% in H<sub>2</sub>) at 380 °C and total pressure of 5 Torr for 1 min *after* normal Ge nanowire growth. This method can be used to dope untapered Ge nanowires using PH<sub>3</sub> or B<sub>2</sub>H<sub>6</sub> for electronic devices applications.[100]

## 2.2.4 Substrate chemistry and Au nanoparticle adhesion

Another important aspect of nanowire growth is control of nanowire density. Since Ge nanowires are catalyzed by Au nanoparticles, a natural solution is to manipulate the Au nanoparticle density until the desired nanowire density is reached. In general, a higher nanowire density can be achieved by keeping Au colloids on the sample for a longer period of time between being drop cast and rinsed off. However, we consistently observed variations in Au nanoparticle density when the doping types of the underlying Si substrate changes, which leads us to consider the effect of substrate on Au nanoparticle adhesion.

Commercially available Au nanoparticle colloids are a very convenient way of acquiring catalysts with a desired size and concentration, but these citrate-stabilized gold colloids do not adhere to Si substrates in the as-received state. The purpose of citrate is to generate a net negative surface charge on the Au nanoparticles to prevent agglomeration. For this reason, a positive charged surfactant such as Poly-I-lysine (Ted Pella Inc. 0.1 % w/v aqueous solution) is often used to treat Si substrate for better Au nanoparticle adhesion.[45] Another and potentially better method

is to add 0.1 M HF into the Au colloid (HF concentration is based on total volume). Not only does the HF help improve vertical yield by preventing native oxide formation, but it can also promote Au nanoparticle adhesion by creating a hydrogen-terminated surface. HF converts the negatively charged citrate ions to neutral citric acid, thus Au colloid solution needs to be prepared immediately prior to use to prevent Au nanoparticles from agglomerating.[45]

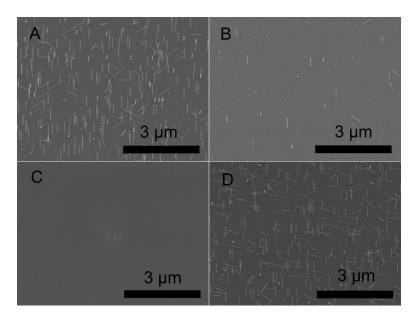

We conducted experiments to study the impact of the Si substrate on Au nanoparticle deposition. Four different (111) Si substrates were prepared, with n(p) doped bulk Si wafer and enhanced(reversed) doping at the surface. For fair comparison, undiluted Au colloid with 0.1 M HF added were prepared prior to growth and the Au colloids were kept on the substrates for 5 s for all four samples before rinsing in DI, dried with N<sub>2</sub> gun and transferred to the growth chamber. Growth was carried out following the regular two-step recipe with 1 min nucleation (360 °C at a total pressure of 45 Torr, with 20/200 sccm of GeH<sub>4</sub>/H<sub>2</sub>, where GeH<sub>4</sub> is diluted in H<sub>2</sub> carrier gas to 10%) and 3 min elongation (300 °C at a total pressure of 45 Torr, with 20/200 sccm of GeH<sub>4</sub>/H<sub>2</sub>, where GeH<sub>4</sub> is diluted in H<sub>2</sub> carrier gas to 10%).

The growth results are summarized in Figure 12, where SEM images for substrate/surface doping of (A) p/n+, (B) p/p+, (C) n/p+ and (D) n/n+ are shown. Interestingly, Figure 12A/D show very high nanowire density while Figure 12B/C showed the opposite. Thus we can conclude that the surface doping type is responsible for determining Au nanoparticle adhesion and n-type doping facilitates Au adhesion while p-type doping does not. Although we have not extensively studied the exact underlying mechanism, we suspect that the hydrogen-terminated Si substrate can be charged differently at the surface depending on the dopant type (negatively charged for p-type dopant and positively charged for n-type dopant), possibly due to the natural depletion region formed near the surface, which exposes the ionized dopant atoms to Au nanoparticles. The

positively (negatively) charged surface enhances (suppresses) Au particle deposition, since the Au particles are negatively charged due to the surfactants.

Figure 12. Effect of substrates on nanowire density. Different nanowire density for growth carried out on (A) p/n+, (B) p/p+, (C) n/p+, and (D) n/n+ (bulk/surface) doped substrates. All SEM images are taken with a 45 degree tilt angle.

Depending on the application, sometimes a lower density of nanowires is desired. In this case, simply shortening the Au nanoparticle dispersion time to very short time (e.g., 1-2 s) is not ideal as consistency is hard to maintain. An alternative solution is to dilute the Au colloid with DI water to achieve a lower Au count in the droplet. That way, the dispensing time can be kept at a relatively long time (e.g., > 10 s) for better repeatability and a wider process window.

### 2.3 Towards vertical device realization

One of the drawbacks of metal-assisted VLS growth is the random distribution of nanowire locations. Currently there is still no easy way to control the distribution of single nanoscale Au particles. Usually a large number of nanowires are grown simultaneously, and then individual ones grown at preferable locations are chosen for subsequent steps. For example, even though we are able to achieve good nucleation yield and desired nanowire density over a large area (typical size

of approximately 1 cm<sup>2</sup>), it is still very difficult to grow a single vertical nanowire at a precisely controlled location. While it is acceptable to pick one nanowire and build devices for fundamental studies, the future integration of nanowires with other devices/circuits often requires a more deterministic growth pattern.

### 2.3.1 Selective area Ge nanowire growth

Since nanowire growth is mediated by metal nanoparticles in the VLS process, it is natural to try to control the nanowire growth sites by controlling the original catalyst nanoparticle positions. For example, Sato *et al.* proposed to use a SiO<sub>2</sub> film as a patterning mask for defining the Au catalyst position in the growth of GaAs nanowhiskers as early as 1995.[111] The concept of patterned growth, or selective area growth has been adopted by several groups in recent years and the results reported are promising with the use of catalyst nanoparticles and advanced lithography techniques such as e-beam lithography.[59], [112] Some other approaches involve the use of nano-manipulation techniques such as atomic force microscopy[113], metal deposition through alumina templates[114], and nanosphere lithography (NSL)[115].

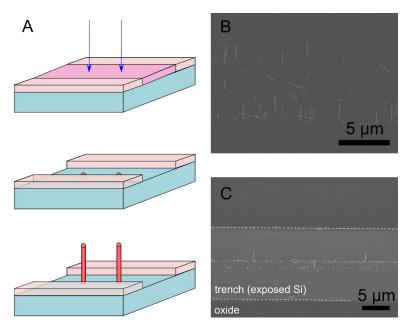

In our study, the goal is not to achieve 100% yield with a precisely designed number of nanowires in each patterned region, but to develop a fast, cost-efficient method to realize selective area growth. The schematic of one approach is illustrated in Figure 13A. First we deposited oxide ( $\sim$ 30 nm SiO<sub>2</sub> on top of 20 nm Al<sub>2</sub>O<sub>3</sub>, SiO<sub>2</sub> is deposited through 10% Spin-on-glass 700B from Filmtronics Inc. diluted in IPA) on (111) Si substrate, and then pattern a long stripe (length of  $\sim$  1 cm and width ranging between 2  $\mu$ m and 10  $\mu$ m) using photolithography. Wet etch by diluted HF was used to create the trench and expose the Si surface underneath. Dry etching techniques such as reactive ion etch (RIE) was intentionally avoided for fear of damaging the Si surface. Ideally a smooth surface is desired for epitaxy. The wet etch was followed immediately by drying with N<sub>2</sub>

gun and Au colloid deposition to mitigate native oxide formation. Since oxide has poor attraction to Au nanoparticles,[45] the majority of the catalysts can be found inside the trench. Then the sample was quickly transferred to the CVD chamber for normal Ge nanowire growth.

**Figure 13. Selective area growth of Ge nanwoires.** (A) Schematic of fabrication steps for selective area growth of Ge nanowire inside an oxide trench. (B-C) 45 degree tilted SEM images of patterned region with different nanowire densities.

Representative SEM images of nanowires grown in the trenches are shown in Figure 13B-C, with different densities achieved by changing the Au nanoparticle dispersion time (typical values range from 10 s to 2 min). It is observed that the spacing of nanowires along the length direction of the trench is quite uniform. By varying nanowire density, it is possible to design devices built on a portion of the trench that includes a single nanowire (or a fixed number of nanowires) with good fidelity. Because photolithography was used for oxide patterning, the throughput of this method can be high with a large number of patterns created in parallel. The size of the pattern is limited by the resolution of the lithography tool: trench widths down to 1 µm is achievable within the LNF capability (GCA AS200 AutoStep). The widening seen in Figure 13 was due to the isotropic nature of etching method and can be improved by using a thinner oxide

and a shorter etching time. A multi-step method with RIE first to thin the oxide in the trench down to ~10 nm followed by a short HF etch prior to growth can be potentially employed too. This way it may be possible to preserve a clean, smooth Si surface for nanowire growth while thicker field oxide can still be used. Thicker field oxide helps suppress leakage current in vertical nanowire devices.

Figure 14. Schematic of controlling nanowire location with post growth RIE.

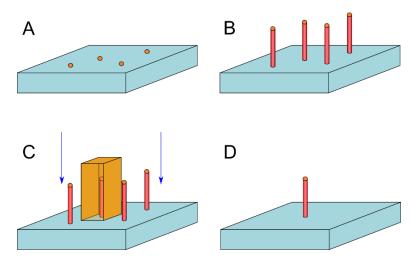

An alternative, "hybrid", strategy is to grow nanowires on the whole sample surface first, then selectively etch away the ones that are grown on unwanted portions of the Si substrate (Figure 14). Photoresist is generally sufficient to serve as a mask material since Ge can be etched fairly easily. Additional care need to be taken when stripping the mask material. Due to the high aspect ratio of nanowire structures, critical point drying is the preferable way to dry the samples while preventing them from being accidently knocked down by surface tension. Compared to the previous selective area growth method, this approach has fewer restrictions, since a dry etch can be utilized. It can potentially offer tighter location control since a smaller pattern size can be safely adopted. In contrast, we observed that it became more difficult for Au nanoparticles to deposit inside the oxide patterns as their size reduced (*i.e.*, using narrower trench, or 20×20 µm<sup>2</sup> instead of centimeter-long trench).

### 2.3.2 Nanowire growth on Ge buffer layer

In addition to site controlled growth, another step towards deterministic VLS growth for 3-D integration is to improve the vertical yield, which is at present in the range of 60-70% in a typical growth. One of the major obstacles to obtaining high vertical yield is native SiO<sub>2</sub> formation. Annealing in H<sub>2</sub> prior to growth can improve epitaxy by removing the native oxide on the surface,[116] but it is not an ideal solution due to the high temperature needed.

Figure 15. 75 degree tilted SEM images of vertical Ge nanowwires grown on Ge buffer layer. The inset of A is taken from 90-degree angle.

One simple method is to deposit a Ge buffer layer on the Si substrate and use this layer as the epitaxy template.[117] Since GeO<sub>x</sub> is much more volatile than SiO<sub>2</sub>, it can be readily removed by atomic hydrogen generated during the GeH<sub>4</sub> decomposition, promoting vertical yield. Figure 15 shows SEM images taken after nanowire growth on a Ge buffer layer (deposited for 1 min at 550 °C and 20 Torr, 1% GeH<sub>4</sub> in H<sub>2</sub>). Improved vertical yield (> 90%) was demonstrated. From the inset of Figure 15A, the thickness of Ge buffer was determined to be about 80 nm. Due to the relative low process temperature, this Ge buffer likely contained a high density of crystal defects. While it is not suitable for an active device, this Ge buffer layer can serve as a conducting electrode if doped to a high level (*e.g.*, with B<sub>2</sub>H<sub>6</sub> or PH<sub>3</sub>).

# 2.4 Summary

In summary, we have achieved VLS vertical Ge nanowire growth on (111) Si substrates with 20 nm Au nanoparticles as catalysts. A two-step temperature profile was adopted for nanowire growth with high nucleation yield, uniform height and suppressed tapering. Several growth modifications were explored and discussed in detail, including radial Ge/Si core/shell heterojunction formation, *in situ* boron doping and controlling nanowire density via Si substrate type. We have also showed progress towards more deterministic nanowire growth, such as controlling the nanowire location via a patterned oxide layer and improving vertical yield with the help of a Ge buffer layer. These results demonstrated that we were able to produce nanowires with the desired composition and morphology. Furthermore, the ability to define nanowire growth location can prove to be very useful in future device fabrication and integration.

# Chapter 3

# Characterization of Ge/Si heterojunction interface

### 3.1 Introduction

One of the motivations for this dissertation is the unique properties Ge can offer such as high mobility, low band gap and low tunneling effective mass. Moreover, there are various benefits for the nanowire body, including higher tolerance of lattice mismatch, quasi-1D channel and easier implementation of a surrounding gate geometry. In the previous chapter, we demonstrated the growth techniques for acquiring vertical Ge nanowires on (111) Si substrates. In fact, vertical Ge nanowires on Si substrates provides a very interesting material system that can be useful in many applications.

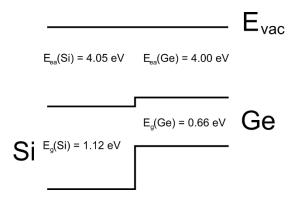

Figure 16. Intrinsic Ge/Si band alignment.

One of the unique properties of this Ge/Si system is the built-in heterojunction. As shown in Figure 16, Ge/Si has type II band alignment with 50 meV (0.56 eV) offset at the conduction (valence) band edges. One of the important applications for type II band alignment is tunneling

based devices, since the tunneling probability is enhanced by the lower effective tunnel barrier. For example, to move from the valence band in Ge to the conduction band in Si, an electron only needs to travel through a 0.61 eV tunnel barrier, lower than the band gap of either Si or Ge. Another important application is the creation of quantum wells, as mentioned in chapter 2. By growing radial Ge/Si core/shell heterostructures, a one dimensional hole gas is induced due to the large valence band offset, which provides carriers even though the nanowire is not intentionally doped.[6]

Considering that our goal is to build Ge nanowire based devices, it is critical to obtain an intrinsic, defect-free Ge/Si interface. For example, the effective tunnel barrier height depends heavily on the *actual* band alignment of the Ge/Si heterojunction, which can be easily distorted by interfacial defects. Thus it is important to characterize the Ge/Si heterojunction properties and ensure the cleanness of the junction before we move on to device level applications.