# Bio-inspired Hardware Architectures for Memory, Image Processing, and Control Applications

by

Yalcin Yilmaz

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 2017

Doctoral Committee:

Professor Pinaki Mazumder, Chair Assistant Professor Kira Barton Professor Yogesh Gianchandani Professor Semyon M. Meerkov Yalcin Yilmaz yalciny@umich.edu

## ORCID iD: 0000-0003-1524-4633

For my parents Birsen and Zafer Yilmaz

# TABLE OF CONTENTS

| DEDICATIO   | Ν                 |                                             | ii                                     |

|-------------|-------------------|---------------------------------------------|----------------------------------------|

| LIST OF FIG | URES .            |                                             | vi                                     |

| LIST OF TAI | BLES              |                                             | viii                                   |

| ABSTRACT    |                   |                                             | ix                                     |

| CHAPTER     |                   |                                             |                                        |

| I. Intro    | duction           |                                             | 1                                      |

| 1.1         | Variable          | Resistance Device Model                     | 3                                      |

| II. Multi   | -Level N          | Iemory Architecture                         | 6                                      |

| 2.1         | Introduc          |                                             | 6                                      |

| 2.2         | Multi-St<br>2.2.1 | ate Memory Architecture                     | $\begin{array}{c} 10\\ 10 \end{array}$ |

|             | 2.2.1<br>2.2.2    | Architecture                                | 10<br>12                               |

|             | 2.2.2<br>2.2.3    | Read/Write Circuitry                        | 12                                     |

|             | 2.2.3<br>2.2.4    | Read/Write Operations Flow                  | $15 \\ 15$                             |

|             | 2.2.4<br>2.2.5    | State Derivations                           | 18                                     |

| 2.3         | -                 | rite Operations                             | 20                                     |

| 2.0         | 2.3.1             | Read/Write Simulations                      | $\frac{20}{20}$                        |

|             | 2.3.2             | Read Disturbances to the Neighboring Cells  | $\frac{-6}{25}$                        |

| 2.4         | -                 | of Variations                               | $\frac{1}{27}$                         |

|             | 2.4.1             | Variations in Programming Voltage           | 27                                     |

|             | 2.4.2             | Variations in Series Resistance             | $\frac{-1}{29}$                        |

|             | 2.4.3             | Reduced-Impact Read Scheme                  | $\frac{-0}{30}$                        |

|             | 2.4.4             | Resistance Distributions after Array Writes | 32                                     |

| 2.5         | Conclusi          | on                                          | 34                                     |

| 0         |                   | sing by a Programmable Artificial Retina Com-<br>um Dots and Variable Resistance Devices | 35         |

|-----------|-------------------|------------------------------------------------------------------------------------------|------------|

| 3.1       | Introduc          | tion                                                                                     | 35         |

| 3.2       |                   | chitecture                                                                               | 37         |

| 0.2       | 3.2.1             | Resonant Tunneling Diode Model and Biasing                                               | 37         |

|           | 3.2.2             | Unit Cell Structure                                                                      | 39         |

| 3.3       | 0                 | ming Variable Resistance Connections                                                     | 41         |

| 3.4       | -                 | al Modeling                                                                              | 47         |

| 0.1       | 3.4.1             | Edge Detection                                                                           | 47         |

|           | 3.4.2             | Line Detection                                                                           | 50         |

| 3.5       | -                 | on Results                                                                               | 51         |

| 0.0       | 3.5.1             | Edge Detection                                                                           | 53         |

|           | 3.5.1<br>3.5.2    | Line Detection                                                                           | $55 \\ 57$ |

| 3.6       |                   | on                                                                                       | 58         |

| 5.0       | Concrusi          | 011                                                                                      | 90         |

| IV. Optin | nal Cont          | rol via Neural Network Approximators                                                     | 59         |

| 4.1       | Introduc          | tion                                                                                     | 59         |

| 4.2       | Optimal           | Control via Adaptive Dynamic Programming for Discrete                                    | <b>-</b> - |

|           | Time Sy           | stems                                                                                    | 62         |

|           | 4.2.1             | Control Optimization                                                                     | 62         |

|           | 4.2.2             | Bellman Equation                                                                         | 63         |

|           | 4.2.3             | The Discrete-Time Hamilton-Jacobi-Bellman (HJB)                                          |            |

|           |                   | Equation                                                                                 | 64         |

|           | 4.2.4             | Heuristic Dynamic Programming                                                            | 65         |

|           | 4.2.5             | Neural Network Approximation of HDP for Non-linear                                       |            |

|           |                   | Systems                                                                                  | 66         |

| 4.3       | Hardwar           | e Implementation of Action-Critic based ADP                                              | 66         |

| 1.0       | 4.3.1             | Actor-Critic Networks                                                                    | 66         |

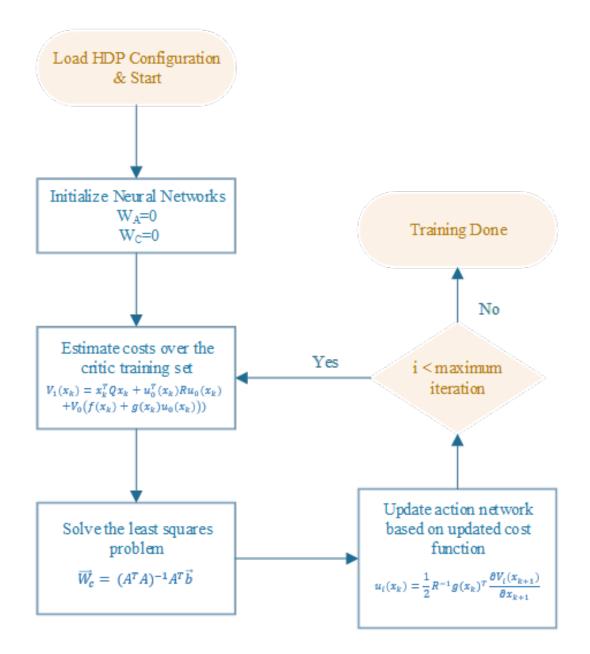

|           | 4.3.2             | Hardware HDP Algorithm                                                                   | 69         |

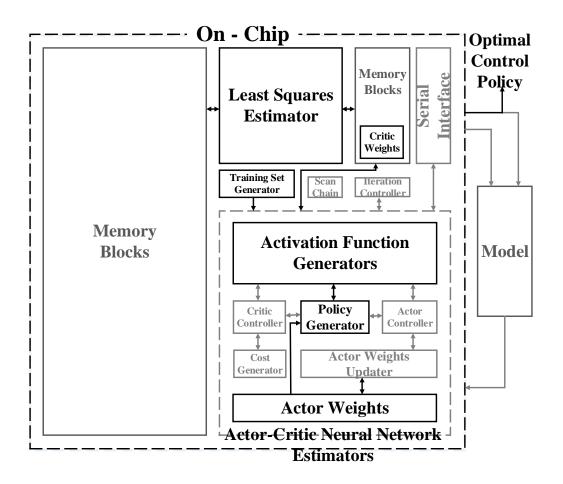

|           | 4.3.3             | Hardware Architecture and Specifications                                                 | 71         |

|           | 4.3.4             | Least Squares Regression Calculation                                                     | 74         |

| 4.4       |                   | on Results                                                                               | 76         |

| 1.1       | 4.4.1             | Simulation Setting                                                                       | 76         |

|           | 4.4.2             | Error Quantization                                                                       | 77         |

|           | 4.4.3             | Non-linear System Example                                                                | 78         |

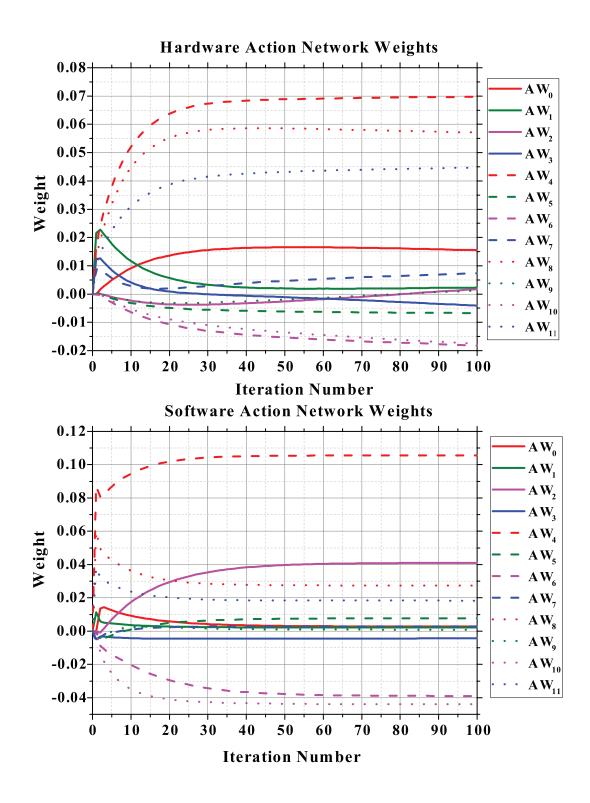

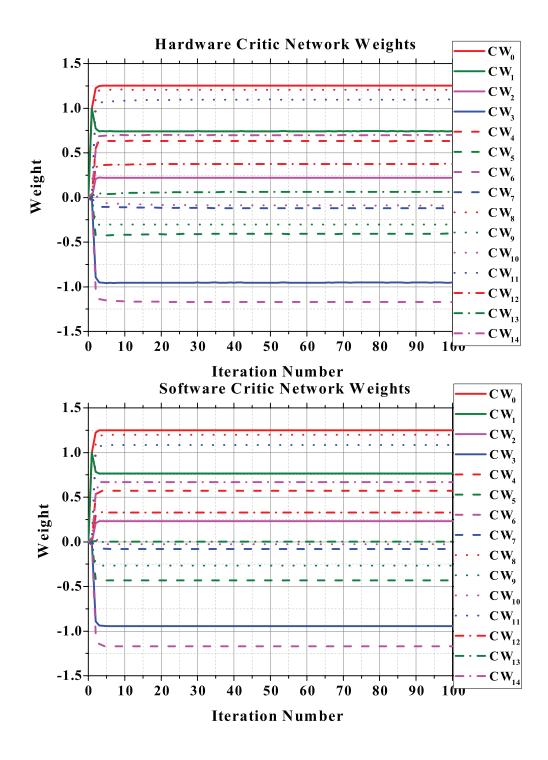

|           | 4.4.4             | Actor and Critic Network Weights during Training .                                       | 78         |

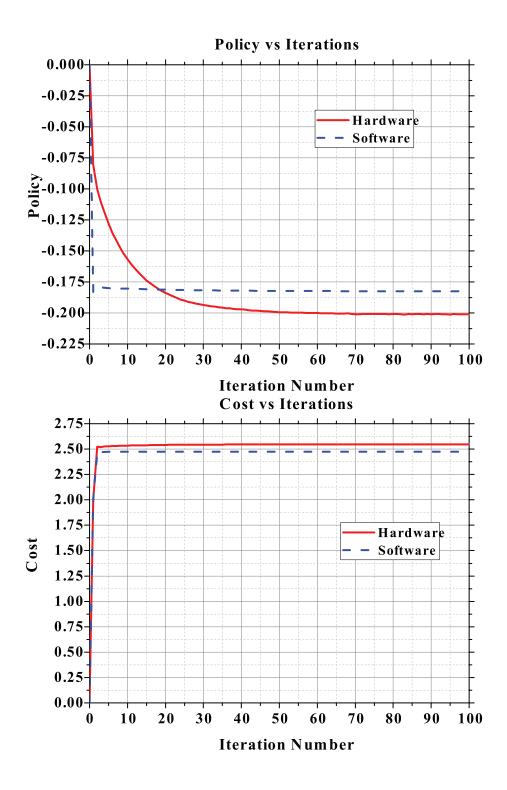

|           | 4.4.4<br>4.4.5    | Optimum Policy and Associated Cost during Training                                       | 81         |

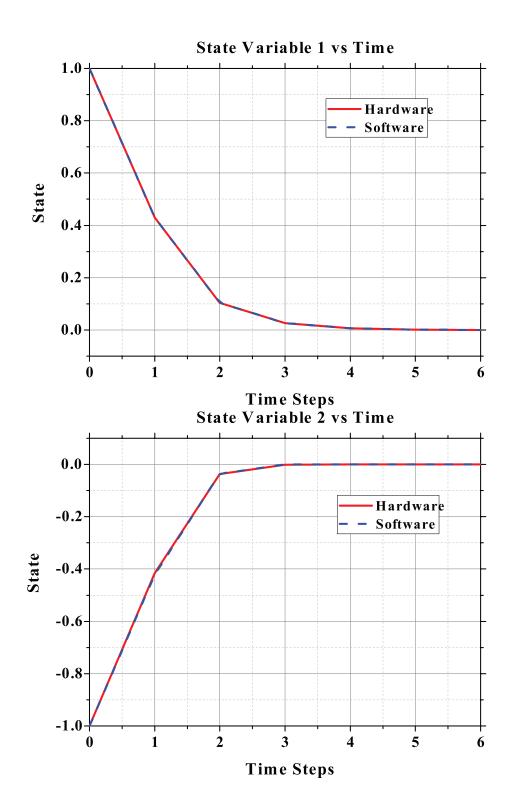

|           | 4.4.5<br>4.4.6    | Discrete Time System Response                                                            | 83         |

|           | 4.4.0<br>4.4.7    | v -                                                                                      | 03<br>83   |

| 4.5       | 4.4.7<br>Conclusi | The Proposed Hardware Layout                                                             | 89<br>89   |

| 4.0       | Conciusi          | 011                                                                                      | 09         |

| V. Conc   | lusions .         |                                                                                          | 90         |

## iv

| BIBLIOGRAPHY | • | • |  |  | • | • |  | • |  |  |  | • |  |  | • |  |  | • |  | ę | 92 |

|--------------|---|---|--|--|---|---|--|---|--|--|--|---|--|--|---|--|--|---|--|---|----|

|              |   |   |  |  |   |   |  |   |  |  |  |   |  |  |   |  |  |   |  |   |    |

# LIST OF FIGURES

## Figure

| 1.1  | Variable Resistance Device Structure                                               | 4  |

|------|------------------------------------------------------------------------------------|----|

| 2.1  | Multi-level RRAM architecture                                                      | 11 |

| 2.2  | Read interpreter circuitry block                                                   | 13 |

| 2.3  | Memory array biasing scheme                                                        | 14 |

| 2.4  | Flow chart explaining memory operations                                            | 17 |

| 2.5  | Array biasing levels during a write operation                                      | 21 |

| 2.6  | Interpreter operation during a write operation                                     | 22 |

| 2.7  | Writing of various values into the selected memory cell $\ldots \ldots \ldots$     | 24 |

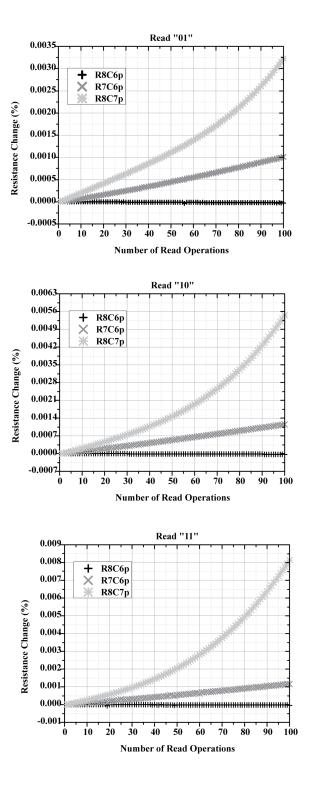

| 2.8  | Percent change of resistance in neighboring cells vs. number of read operations    | 26 |

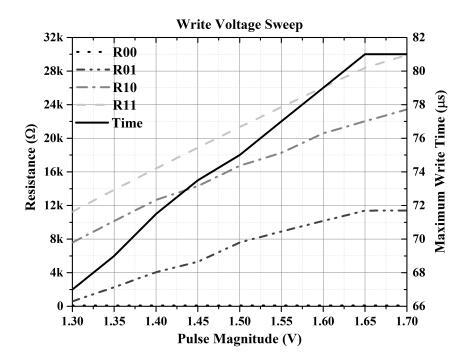

| 2.9  | Write voltage sweep                                                                | 27 |

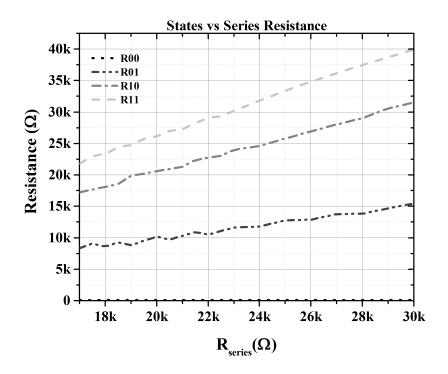

| 2.10 | Series Resistance Sweep                                                            | 29 |

| 2.11 | Resistance Distributions                                                           | 30 |

| 2.12 | Reduced impact read operation                                                      | 31 |

| 2.13 | Resistance distributions after programming                                         | 33 |

| 3.1  | RTD I-V curve                                                                      | 38 |

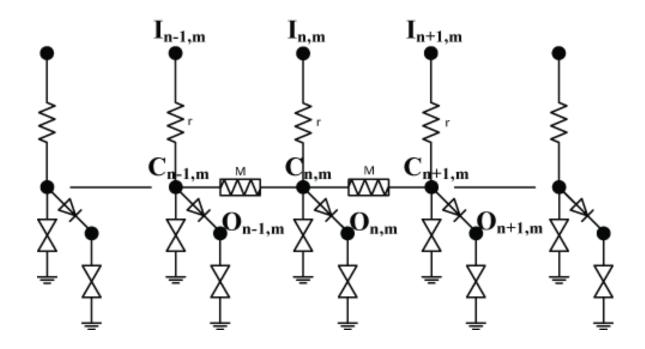

| 3.2  | Unit Cell                                                                          | 40 |

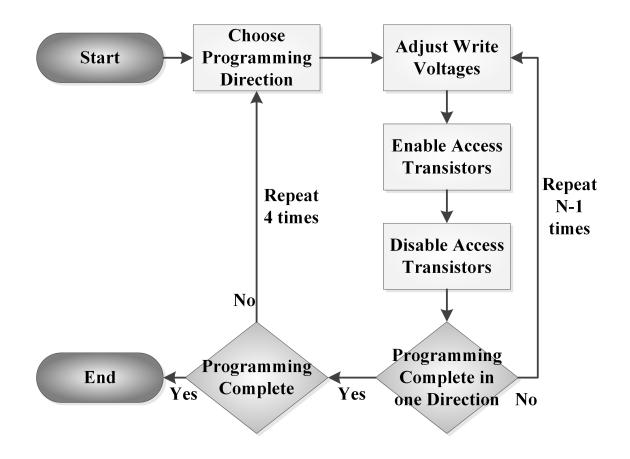

| 3.3  | Array programming flow                                                             | 42 |

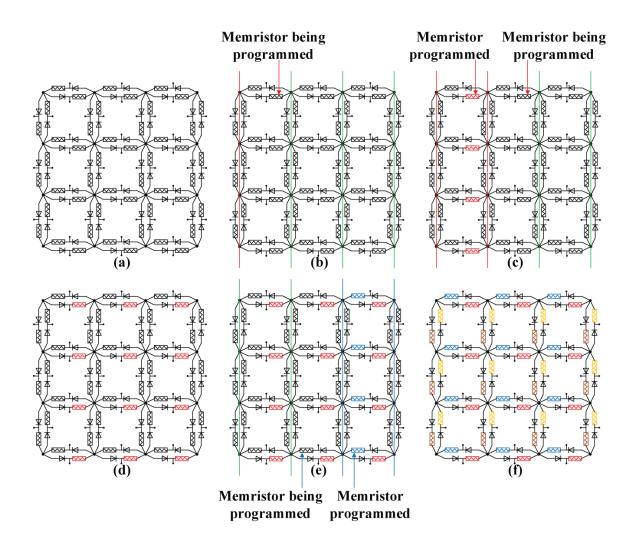

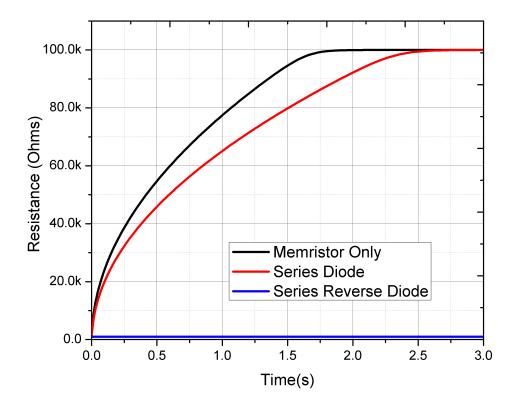

| 3.4  | Array programming in one direction                                                 | 44 |

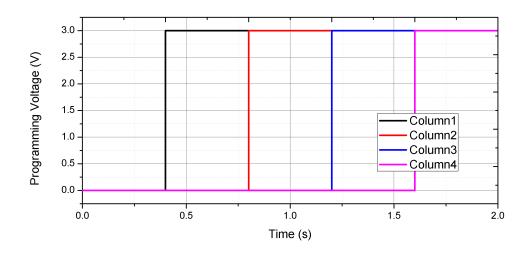

| 3.5  | Programming voltages in a 4 by 4 array                                             | 45 |

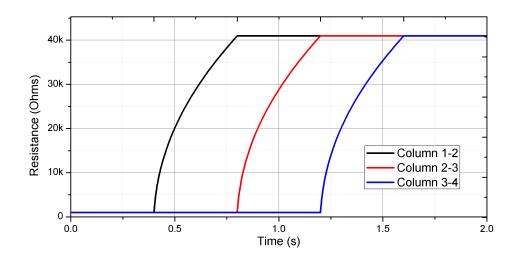

| 3.6  | Resistances in the same row in a 4 by 4 array                                      | 46 |

| 3.7  | Connections under different bias conditions                                        | 46 |

| 3.8  | CNN circuitry in 1D case                                                           | 48 |

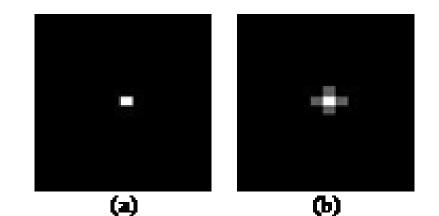

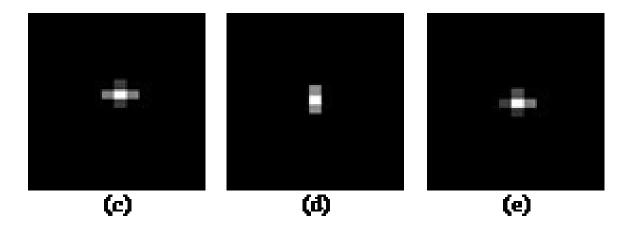

| 3.9  | Various diffusion characteristics that can be implemented in proposed architecture | 52 |

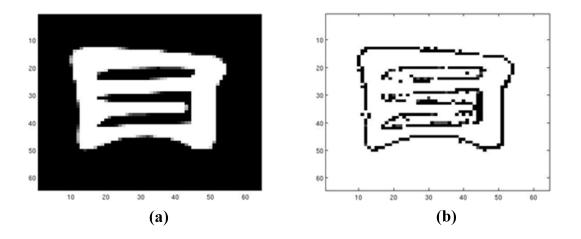

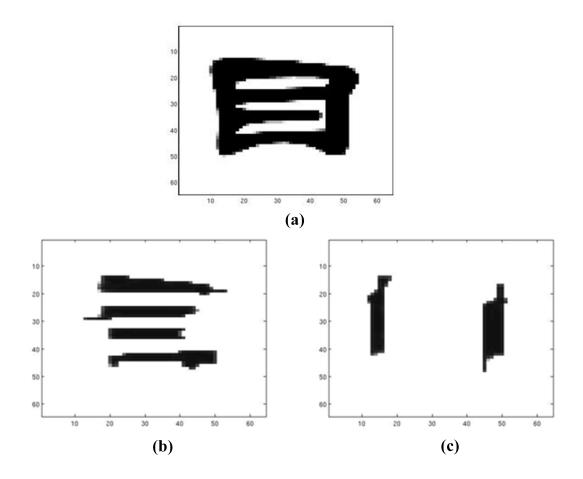

| 3.10 | Edge detection with irregular edges                                                | 53 |

| 3.11 | Edge detection with regular edges                                                                                                                                                                       | 54 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

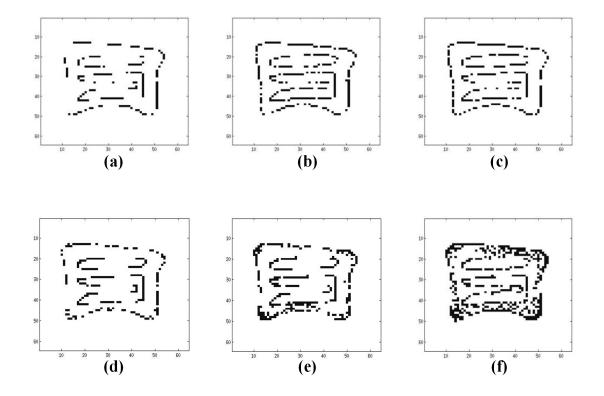

| 3.12 | Edge detection results with input resistance variation $\ldots \ldots \ldots$                                                                                                                           | 56 |

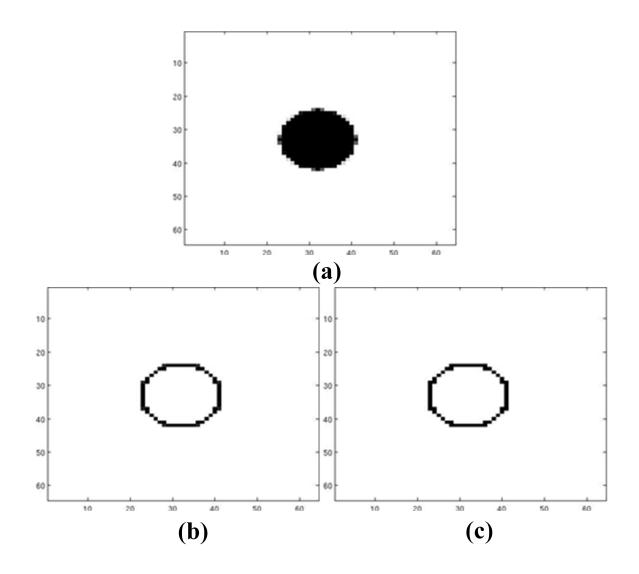

| 3.13 | Line detection results                                                                                                                                                                                  | 57 |

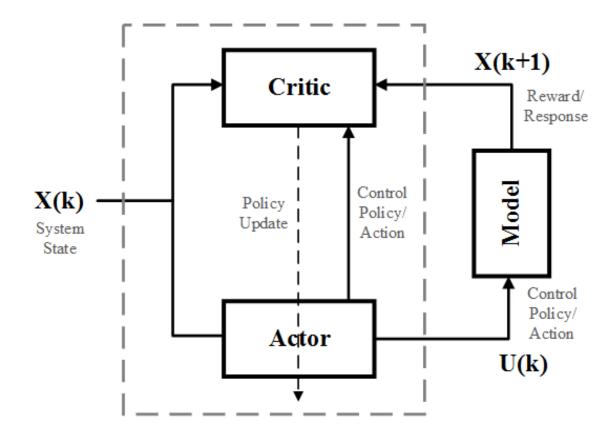

| 4.1  | Actor-Critic Network structure                                                                                                                                                                          | 67 |

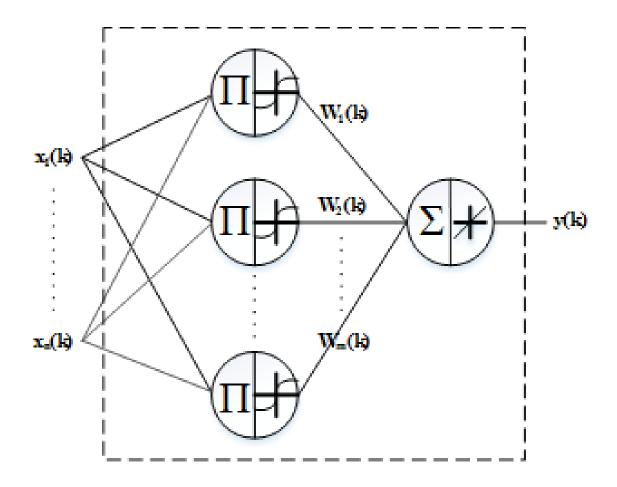

| 4.2  | The neural network structure. $x_1(k),, x_n(k)$ are neural network<br>inputs, $W_1(k),, W_m(k)$ are neural network weights, $y(k)$ is the<br>neural network output at discrete time step $k$            | 68 |

| 4.3  | Hardware heuristic dynamic programming algorithm flow                                                                                                                                                   | 70 |

| 4.4  | Block diagram showing the overall hardware architecture                                                                                                                                                 | 72 |

| 4.5  | Hardware vs software actor network weights over iterations                                                                                                                                              | 79 |

| 4.6  | Hardware vs software critic network weights over iterations                                                                                                                                             | 80 |

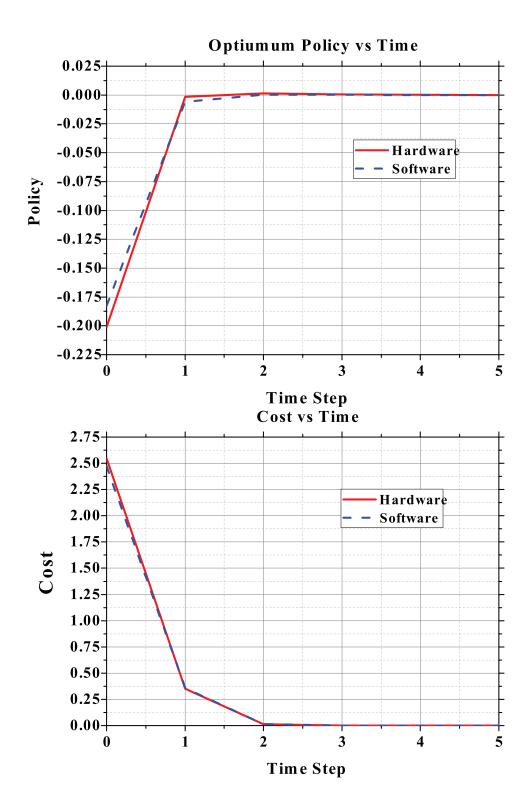

| 4.7  | Hardware vs software optimum policy and its cost over iterations. $% \mathcal{A}^{(n)}$ .                                                                                                               | 82 |

| 4.8  | Discrete time system response with hardware and software policies over time. The change in system state is plotted for both the hardware and software policies.                                         | 84 |

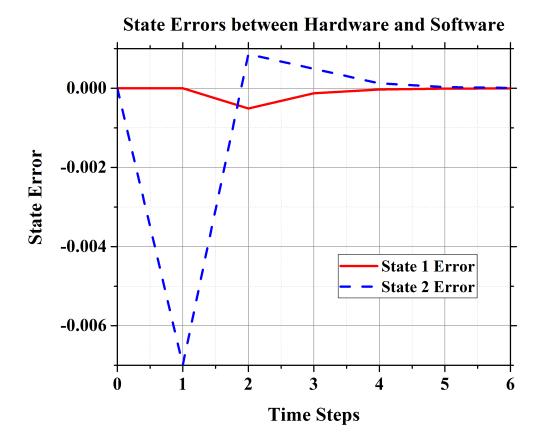

| 4.9  | The error in system states for the hardware policy compared to the software policy.                                                                                                                     | 85 |

| 4.10 | The hardware and software policies over time                                                                                                                                                            | 86 |

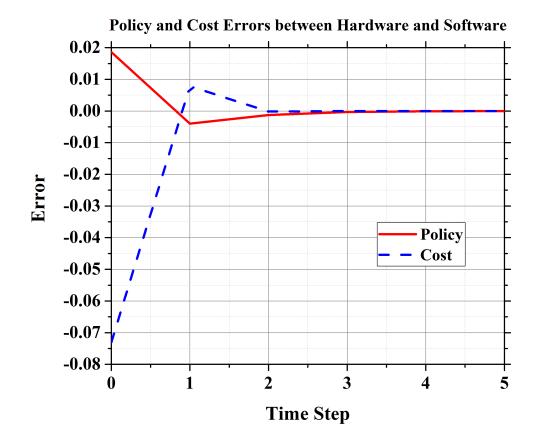

| 4.11 | The differences between the hardware policy and cost compared to the software counterparts.                                                                                                             | 87 |

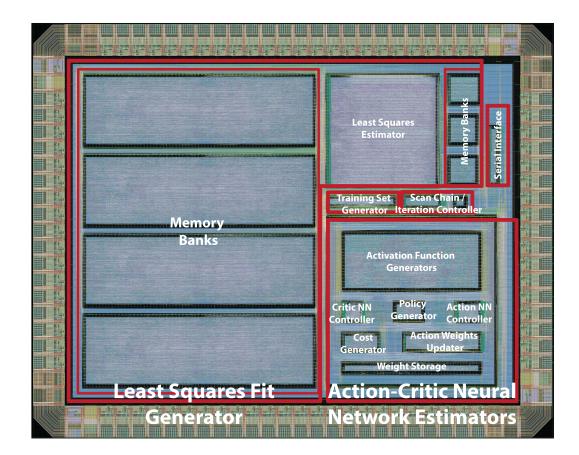

| 4.12 | Proposed heuristic dynamic programming (HDP) chip layout. The SoC dimensions are $1950\mu mx 1550\mu m$ in 65nm CMOS LP technology including the pads. The core dimensions are $1700\mu mx 1300\mu m$ . | 88 |

# LIST OF TABLES

### <u>Table</u>

| 2.1 | Calculated vs. Simulated Resistance Levels | 20 |

|-----|--------------------------------------------|----|

| 2.2 | Comparison of Resistive States             | 28 |

| 4.1 | Hardware Configurations                    | 73 |

| 4.2 | HDP SoC Summary                            | 89 |

### ABSTRACT

Bio-inspired Hardware Architectures for Memory, Image Processing, and Control Applications

by

Yalcin Yilmaz

Chair: Pinaki Mazumder

Emerging technologies are expected to partially replace and enhance CMOS systems as the end of transistor scaling approaches. A particular type of emerging technology of interest is the variable resistance devices due to their scalability, non-volatile nature, and CMOS process compatibility. The goal of this dissertation is to present circuit and system level applications of CMOS and variable resistance devices with bio-inspired computation paradigms as the main focus. The summary of the results offered per chapter is as follows:

In the first chapter of this thesis, an introduction to the work presented in the rest of this thesis and the model for the variable resistance device is provided.

In the second chapter of this thesis, a crossbar memory architecture that utilizes a reduced constraint read-monitored-write scheme is presented. Variable resistance based crossbar memories are prime candidates to succeed the Flash as the mainstream nonvolatile memory due to their density, scalability, and write endurance. The proposed scheme supports multi-bit storage per cell and utilizes reduced hardware, aiming to decrease the feedback complexity and latency while still operating with CMOS compatible voltages. Additionally, a read technique that can successfully distinguish resistive states under the existence of resistance drift due to read/write disturbances in the array is presented. Derivations of analytical relations are provided to set forth a design methodology in selecting peripheral device parameters.

In the third chapter of this thesis, an analog programmable resistive grid-based architecture mimicking the cellular connections of a biological retina in the most basic level, capable of performing various real time image processing tasks such as edge and line detections, is presented. Real time vision systems require computationally intensive tasks which often benefit greatly from fast and accurate feature extractions. Resistive grid-based analog structures have been shown to perform these tasks with high accuracy and added advantages of compact area, noise immunity, and lower power consumption compared to their digital counterparts. However, these are static structures that can only perform one type of image processing task. The proposed unit cell structure employs 3-D confined resonant tunneling diodes called quantum dots for signal amplification and latching, and these dots are interconnected between neighboring cells through non-volatile continuously variable resistive elements. A method to program connections is introduced and verified through circuit simulations. Various diffusion characteristics, edge detection, and line detection tasks have been demonstrated through simulations using a 2-D array of the proposed cell structure, and analytical models have been provided.

In the fourth chapter of this thesis, a bio-inspired hardware designed to solve the optimal control problem for general systems is presented. Adaptive Dynamic Programming algorithms provide means to approximate optimal control actions for linear and non-linear systems. Action-Critic Networks based approach is an efficient way to approximately evaluate the cost function and the optimal control actions. However, due to its computation intensiveness, this approach is usually implemented in high level programming languages run using general purpose processors. The presented hardware design is aimed at approximating the solution to the Bellman equation to find the optimal control action and to reduce the computation time and the hardware overhead by using the Heuristic Dynamic Programming algorithm which is a form of Adaptive Dynamic Programming. The proposed hardware operating at mere speed of 10 MHz yields 237 times faster learning rate in comparison to conventional software implementations running on fast processors such as the 1.2 GHz Intel Xeon processor. The proposed system-on-chip (SoC) integrated circuit is designed using 65 nm CMOS LP technology, and has a dimension of 1950  $\mu$ m × 1550  $\mu$ m while consuming 2.1 mW at 10 MHz operation frequency and 1.2 V supply voltage.

### CHAPTER I

## Introduction

CMOS scaling has been consistently providing increased density for the modern VLSI chips as predicted by the Moore's law, which dictates that the number of transistors in a semiconductor chip doubles approximately every two years. CMOS technology has facilitated Van Neumann architecture based computation paradigms to flourish and dominate the digital world for decades. However, as the transistor scaling is reaching its physical limits, and with the emergence of new technologies that provide interesting physical properties, alternative computation paradigms might need to be adopted in wide range of applications.

The nervous systems of living organisms perform many complex tasks with much more energy and computational efficiency than the current VLSI chips. For example, human brain can perform 10<sup>17</sup> FLOPS while dissipating around merely 15W. Therefore, bio-inspired neuromorphic computation paradigms have been attracting significant attention. Especially, mimicking neuron and synapse functionalities with CMOS circuitry has been the goal of many researchers in order to investigate if the computational efficiency of the biological systems can be attained on semiconductor chips.

The emerging technologies provide inherent advantages over the CMOS technology in some applications due to the fact that their operation principles are based on different physical properties. For example, such devices facilitate the mapping of certain computations directly to their physical properties which mean that a single device can realize a functionality that would otherwise require tens of CMOS transistors.

Among the emerging technologies, programmable variable resistance devices have recently attracted significant attention in various applications (bio-inspired and otherwise) after Hewlett-Packard research labs revealed that "memristance" can be observed in nano-scale thin film devices [1]. The significance of these devices arises from the fact that they can retain their resistive state even when power is turned off, displaying non-volatility and they might enable scaling beyond CMOS technology limits. The variable resistance characteristics of these devices are proposed to be utilized in ultra-dense crossbar memories [2], configurable logic applications and as synaptic connections in neuromorphic architectures [3]. They have also been used for carrying out image processing tasks which benefit from their non-linearity and adaptive characteristics [4]. Most of these applications could benefit from the use of these devices more if the devices show properties of long term stability of resistive states and little or no degradation of these states when the values stored in these devices are read. Fabrication results reported in [5] indicate the observation of diode-like behavior in amorphous Silicon (a-Si) devices which are undisturbed when the voltages across the devices are below a certain threshold and can retain their states more than 4 years at room temperature.

This thesis focuses on the circuit and system level applications of CMOS and variable resistance devices, bio-inspired computation paradigms being the main focus. The first application that will be presented is a non-volatile multi-level crossbar memory, capable of storing two or more bits per cell, facilitating the design of ultradense data storage. This application has the most potential for immediate adoption for commercialization as it provides increased memory density, reducing storage cost per bit. The following applications focus on the bio-inspired computation paradigms, one being the implementation of a programmable resistive grid acting as an artificial retina to realize various computer vision tasks such as edge and line detection. In fact, the structure can be programmed to implement different diffusion characteristics which can be extended to other image processing tasks. The final application that will be presented is the most significant contribution of this thesis, which provides a bio-inspired hardware to solve the optimal control problem for general systems. Living organisms interact with their environments and learn from their experiences to optimize their actions to get the best outcome. For example, they try to find the best food source, find the best path to avoid predators, etc. Inspired by this type of 'Reinforcement Learning', a neuromorphic hardware is proposed, which efficiently performs the objective minimization/maximization via on-chip learning mechanisms that is otherwise implemented in high level programming languages and run on general purpose processors with much less computation and energy efficiency.

Next subsection will provide information on the physical properties and modeling of the variable resistance devices (memristors) which comprise the main components presented in the next two chapters of this work.

#### 1.1 Variable Resistance Device Model

"Memristor" is the fourth fundamental circuit element which relates charge with magnetic flux as described by Leon Chua in [6]. HP research labs revealed in [1] that two terminal thin-film based devices can exhibit variable resistance behavior.

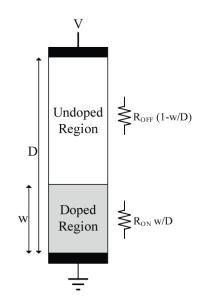

As laid out in [1], these devices can be modeled as a combination of two series variable resistors, with one of the resistors having a high dopant concentration, thus having low resistance and the other having a low dopant concentration, thus having high resistance. This model is visualized in Figure 1.1. Application of a voltage across the terminals of the device triggers dopant drift. Depending on the voltage polarity,

Figure 1.1: Variable Resistance Device Structure

the width of the doped region can increase or decrease. As the width of the doped region increases, conductance increases and as it decreases, conductance decreases.

Therefore the total resistance of the device can be expressed as:

$$R = \frac{w}{D}R_{ON} + (1 - \frac{w}{D})R_O FF \tag{1.1}$$

where w is the width of the doped region, D is the total length of the thin film,  $R_{ON}$ is the lowest resistance when w = D and  $R_{OFF}$  is the highest resistance when w = 0. When the current is passed through the device, the width of the doped region, wchanges. The rate of change of w with time is:

$$\frac{dw(t)}{dt} = \mu_v \frac{R_{ON}}{D} i(t) \tag{1.2}$$

where  $\mu_v$  is the dopant mobility and i(t) is the current passing through the device. The above model presented by HP labs is a linear model and does not account for the nonlinearities that are present in most fabricated devices due to second order boundary effects seen at thin film edges. The movement of the boundary between doped and undoped regions is greatly hindered when the width of the doped region approaches device limits (i.e., w = 0 or w = D) [7]. After including the boundary effects, the model expression becomes:

$$\frac{dw(t)}{dt} = \mu_v \frac{R_{ON}}{D} i(t) f(x) \tag{1.3}$$

where f(x) is the window function modeling the nonlinear dopant drift. This function is an estimation of nonlinearity and depends on the specific device behavior. A sample function is provided in [7].

The actual switching characteristics, namely switching delay, of the devices depend on material properties, device dimensions and biasing voltage.

There have been significant efforts in developing memristor SPICE models [8, 9, 10] and even SPICE-like simulators [11] to facilitate the design of hybrid memristor and CMOS circuits through conventional simulation tools that are familiar to circuit designers.

A SPICE model [8] based on this device model is adapted and implemented in Verilog-A to carry out circuit simulations in the following chapters.

### CHAPTER II

## Multi-Level Memory Architecture

## 2.1 Introduction

Nonvolatile memory technologies led by NAND Flash have been generating increased market revenues due to the increased usage of these devices, especially in portable consumer electronics and solid state drives (SSDs) [12]. The trend toward the cloud storage and computing is continually demanding enterprises to invest especially in SSD-based storages, as these provide higher performance compared to hard disk drives (HDDs) [13].

Flash memories have been providing solutions to the ever-increasing high- performance storage demands with continued feature scaling. However, flash scaling is reaching its limits due to the increased reliability problems such as aging of the oxide, charge leakage, retention problems, and the increased capacitive coupling between the floating gates of the neighboring cells [14].

The approaching end of the flash scaling has led researchers to look for alternative nonvolatile memory technologies that can sustain the scaling trend [15]. Many promising emerging technologies have been proposed, each with its own advantages and challenges. Magnetoresistive random-access memory (MRAM) [16], spin-transfer torque random-access memory (STT-RAM) [17], phase-change memory (PCRAM) [18] and resistive random-access memory (RRAM) [19], which is also commonly referred to as memristive crossbar memory, have been the major candidates to supersede the flash technology.

The successor technology has to be dense, has to be scalable, has to have high write endurance, and has to support multi-level cell structure as this has been the trend in flash. Variable resistance devices (memristors) as predicted by Chua in his 1971 paper [6] and realized by Hewlett-Packard Labs in [1] meet all these requirements with their CMOS compatibility, write endurance, data retention, multilevel storage capability, and scalability down to molecular dimensions [20].

Ever since the discovery of the missing variable resistance devices [1], they have attracted great interest not only due to their nonvolatile nature but also due to their hysteretic variable resistance characteristics which allowed for the realization of unconventional circuits and systems. They have found their applications in logic circuits [21, 22], neural computing [23, 24, 25], image processing [26], analog circuits [27, 28], field-programmable gate arrays (FPGAs) [29, 30] and nonvolatile memory [31, 32, 33]. However, among these, the most commercially promising application is the nonvolatile crossbar memory due to existing consumer market.

The crossbar memory has attracted more attention, due to its increased cell density compared to the other architectures that have been proposed, such as the unfolded architecture presented in [34], which requires more metal connections to be routed. In order to further increase the storage density, there has been much research effort in terms of achieving multi-bit storage per cell [33, 35] rather than single-bit. Multi-bit provides increased storage per unit area, reducing fabrication costs.

To achieve single or multi-bit storage per cell, various write schemes have been proposed. These schemes are split into two main categories: Pulse based schemes, where a predetermined duration and amplitude pulse is applied to the cell vs feedback based schemes, where the pulse duration depends on the feedback circuit, indicating if the cell has reached the desired state [36]. Feedback schemes are shown to have advantages over the pulse-based schemes, as they limit the resistive distributions of the programmed cells. In [37], it has been shown that a feedback-based scheme shows narrowing of the resistance distributions compared to a pulse-based scheme. However, the use of DAC, ADC [32, 33], or multi-stage comparisons [36] in feedback circuitry can introduce significant peripheral circuitry overhead, and can introduce latency in response time that can be significant when the memory device is highly non-linear. Thus, a more simplistic approach is required to reduce the circuit overhead, and to reduce latency to avoid over-programming.

Aside from the read/write techniques, another important factor that plays a role in the design of the resistive crossbar memory is the cell structure that is used in the memory array. There are three major types of cell structures that have been proposed: 1T1R, where a selection transistor is integrated in series with a resistive device [38], 1D1R structure, where a series diode is integrated with a resistive device [39] or the device itself shows diode-like behavior [40] and 1R structure [41], where a resistive device does not have any series selection device or diode-like behavior. Other device types are also proposed such as a 3-terminal resistive devices as in [42].

1T1R structure has density problem. With this structure, the memory density is dictated by the scaling of the series transistor, which has bigger feature size than the memristor cell itself. 1R structure has so called "sneak paths" problem which limit the array size due to the deterioration of sensing margins. In fact, relatively smaller-size arrays have been shown to provide enough margin for sensing [43]. In these structures, so called "half-selected cells" still see VDD/2 voltage levels across them [38] and their resistances can drift over time due to the read/write disturbances [44]. Although some methods claim the disturbance is not significant [36], it is more pronounced in 1R architectures as there is no selection device to reduce or eliminate the leakage through these cells. Some proposed methods such as grounding of unselected rows and columns can even cause the half-selected cells to see a higher voltage across them than the selected cell as shown in [45], significantly disturbing the half-selected cells.

Thus, it is believed that 1D1R structure is the most promising solution as it does not suffer from density issues like 1T1R and it does not suffer from the sneak paths problem as much as the 1R structure. Indeed, Crossbar Inc. recently presented a RRAM structure that utilizes series selector devices that provide programming thresholds [46], strengthening the belief that 1D1R structures will be widely adopted in RRAM designs. In order to realize these structures, there have been various approaches. The introduction of series diodes [39] or metal-insulator-metal (MIM) diodes [47, 48] and the engineering of the devices to integrate diode-like behavior [40, 49] in the device itself is presented in literature. Even with the series diode, cell-to-cell isolation is not perfect. Most works in literature fail to consider what happens to unselected or half- selected cells as the other cells are being programmed. In this work, how the programmed resistance distributions change as all the cells in the array are programmed is observed, and a read method that compensates for the expanded and shifted distributions is presented.

A read/write scheme where the voltage references are derived from the intermediate node via means of a combination of active and passive devices, such as diodes, diode-connected transistors, and resistors that generate distinct thresholds is put forward. The contributions presented in this chapter include a reduced-constraint read-monitored-write scheme which supports multi-bit storage per cell and utilizes reduced hardware, aiming to reduce the feedback complexity and latency while still operating with CMOS-compatible voltages, a read technique that provides enough margins for state detection while allowing certain amount of resistance drift in the array cells (thus reducing the need for frequent refresh operations), a relaxed array biasing scheme that aims to facilitate read/write operations while reducing cell disturbances, and derivations of analytical relations to pave the path for a design methodology in selecting peripheral device parameters. The outlined read/write methodology applies generally to 1D1R structures, but can be generalized to other structures with minor modifications.

In Section II, the approach adopted for modeling of the memory cells is presented. Section III details the memory architecture, our read/write methodology, and analytical expressions that guide the peripheral circuitry design. Section IV and V present our simulation results for read/write operations as well as the effects of variations on the programming voltages and the series resistance.

#### 2.2 Multi-State Memory Architecture

#### 2.2.1 Architecture

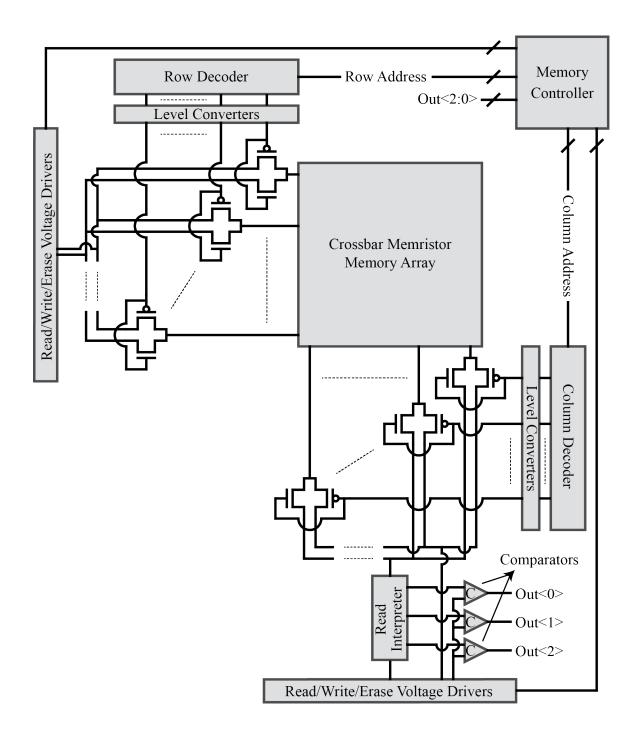

Proposed multi-level memory architecture is presented in Figure 2.1. The crossbar memory array is the main storage area that is composed of metal crossbars and resistive cells located at every intersection of these crossbars.

N-type and p-type access transistors enable the driving of the crossbars with adequate voltage levels. Row and column decoders activate the relevant access transistors depending on the location of the selected cell in the array. The voltage drivers provide various voltage levels to adequately bias the selected or unselected cells. The read interpreter circuitry is serially connected to the selected column through the access transistors, and is capable of actively monitoring the resistance of the selected cell. The interpretation results encoded in voltage levels are then fed into the comparators to detect whether the desired resistive state is reached. The memory controller is responsible for coordinating which memory operation to perform, and generates relevant control signals to activate peripheral blocks.

In this work we present the multiplexed read and write circuitries as parallel reads can introduce circuit overhead [50], however, our methodology can be modified

Figure 2.1: Multi-level RRAM architecture

to support parallel reading and writing of the cells on the selected row.

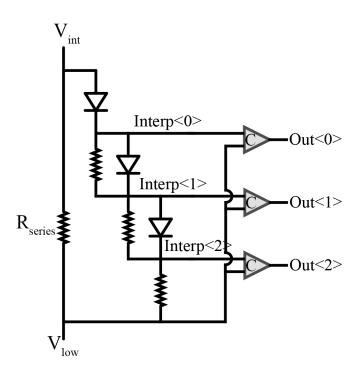

#### 2.2.2 Read/Write Circuitry

Figure 2.2 shows the read interpreter circuitry which actively monitors the resistance change in real time during a write operation, and detects the encoded state during a read operation. The read circuitry is composed of a voltage division stage employing diodes and resistors to interpret the voltage change across the series resistor, and a comparison state employing fast comparators to detect if a desired state is reached.  $R_{series}$  is the series resistor,  $V_{int}$  is the voltage level on the intermediate node that is the node connecting the read interpreter and the selected column through the selection circuitry, Interp(2:0)signals are the outputs generated by the voltage division stage, and Out(2:0)are the corresponding comparator outputs generated in the comparison stage.

The series diode in the voltage division stage provides a close-to-constant voltage reduction in the voltage to be interpreted by the circuitry, providing compaction of the resistive states. The interpreter circuitry can be expanded depending on the number of bits to be stored in the memory cell. For n-bit storage,  $2^n - 1$  diodes and comparators are needed. The resistors connected to the diode outputs have high resistances (1M  $\Omega$ ) in order to minimize the effect of the interpreter circuitry on the intermediate node voltage.

The Interp $\langle 2:0 \rangle$ signals are unique analog outputs, and their values decrease as the resistance of the cell increases. The read interpreter circuity ensures that the Interp $\langle 2 \rangle$ signal falls below the comparator threshold before the Interp $\langle 1 \rangle$ signal does, and Interp $\langle 1 \rangle$ signal falls below the threshold before the Interp $\langle 0 \rangle$ signal. Each Interp signal falling below the comparator threshold indicates that a particular resistive state is reached. We have adopted the convention such that the resistive states are '00', '01', '10' and '11'; where the states are listed in the order of increasing resistance.

Figure 2.2: Read interpreter circuitry block

However, the adoption of the reverse convention where the states are in the order of decreasing resistance is also possible.

#### 2.2.3 Array Voltage Bias Scheme

When performing a write operation, the voltage bias across the selected memory cell should exceed the cell threshold to achieve a fast write operation, whereas in order to minimize the resistance change of the unselected or half-selected cells, the voltage bias across these cells should be kept lower than the threshold of the memory cells.

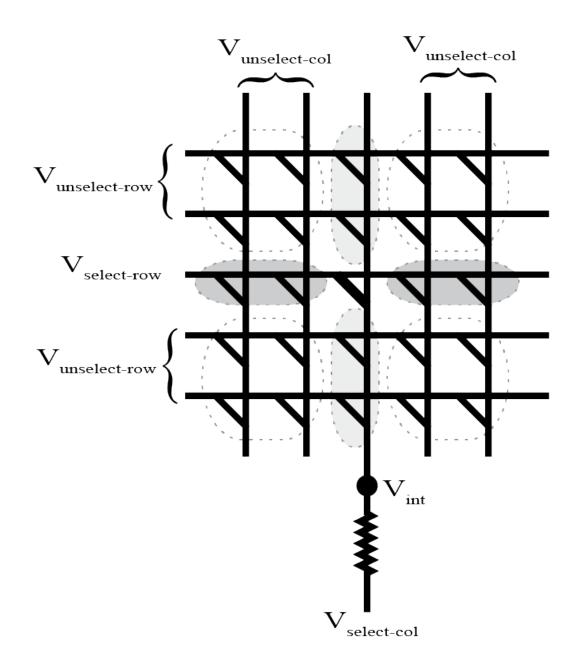

To achieve this goal, we bias the array with four different voltage levels as shown in Figure 2.3. The selected row is applied  $V_{select-row}$ , the unselected rows are applied  $V_{unselect-row}$ , the unselected columns are applied  $V_{unselect-col}$ , and the selected column is applied  $V_{select-col}$  through the interpreter circuitry which yields an applied voltage value of  $V_{int}$  on the intermediate node. These conditions are summarized as follows:

Figure 2.3: Memory array biasing scheme. The cells that lie in white regions see  $V_{unselect-row} - V_{unselect-col}$ , the cells that lie in light grey regions see  $V_{unselect-row} - V_{int}$ , the cells that lie in dark grey regions see  $V_{select-row} - V_{unselect-col}$  across them. The selected cell represented with a thick line sees  $V_{select-row} - V_{int}$  across it.

$$|V_{select-row} - V_{int}| > V_{mth}$$

(2.1a)

$$|V_{select-row} - V_{unselect-col}| < V_{mth}$$

(2.1b)

$$|V_{unselect-row} - V_{int}| < V_{mth} \tag{2.1c}$$

$$|V_{unselect-row} - V_{unselect-col}| < V_{mth}$$

(2.1d)

where  $V_{mth}$  is the memory cell threshold of the 1D1R cell. The above stated conditions can be satisfied by choosing voltage values that follow the following inequality:

$$V_{select-row} > V_{unselect-col} > V_{unselect-row} > V_{int} > V_{select-col}$$

(2.2)

Uneven biasing of the unselected rows and columns are also proposed in [51], where the array is biased with voltage levels that are VDD/3 apart. However, the scheme we propose does not have strict rules on the voltage levels, as long as the difference between the two consecutive voltage values is selected so that it is smaller than the magnitude of the memory cell threshold.

This biasing scheme yields four groups of cells that observe different voltage levels at their terminals as shown in Figure 2.3. Since  $V_{int}$  value changes during programming, the voltage difference at the terminals of the unselected cells connected to the same column as the selected cell is not constant. Therefore, it is important to pick the voltage levels such that the worst case voltage difference across these cells is below the cell threshold.

#### 2.2.4 Read/Write Operations Flow

At the beginning of the write operation, it is assumed that the selected cell in the array is at the erase state, which corresponds to the lowest resistive state ('00')

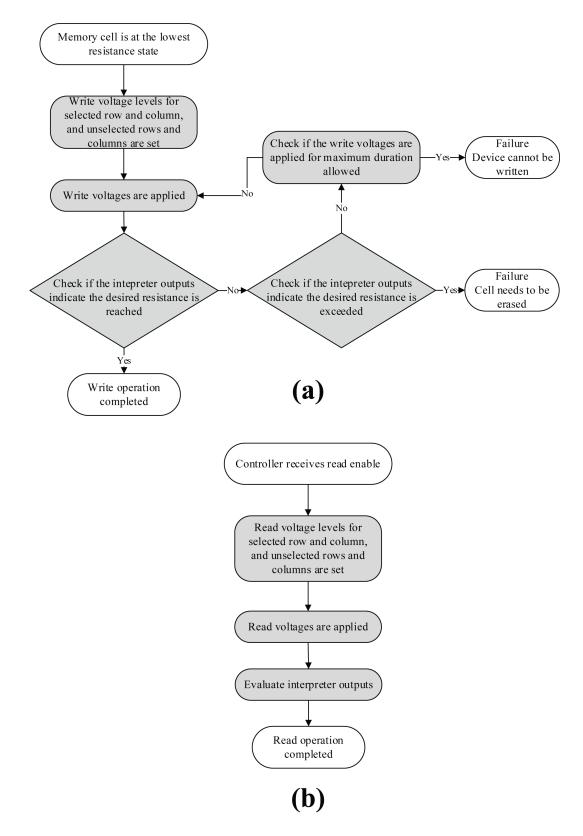

in our convention. After the controller is prompted to perform a write, it signals the voltage drivers to apply relevant voltage levels on the array, and enables the row and column decoders to facilitate the application of the voltages on the selected and unselected rows and columns. As the voltages are applied, the interpreter circuitry generates distinct analog voltage levels (Interp) that directly depend on the resistance of the selected memory cell. As the cell resistance increases, the Interp signal levels begin to decrease. As soon as one of these signals reaches the comparator threshold, the corresponding comparator output (Out) signal flips. The controller checks if the comparator outputs indicate that the desired state is reached. If the state is reached, the controller immediately terminates application of voltages; if not, the controller keeps enabling the application of the write voltages on the array. The flow chart visualizing these steps is shown in Figure 2.4a. The chart also includes the possible write protection and failed cell detection mechanisms that can be adopted similar to flash memories.

Figure 2.4b, shows the flow chart for the read operation. The read operation is similar to a write operation, except the voltage levels and the interpreter circuitry used can have different characteristics, as will be discussed in the following sections.

When the controller is prompted to perform a read, it signals the voltage drivers to apply read voltage levels on the array, and enables the row and column decoders to facilitate the application of the these voltages on the selected and unselected rows and columns. As the voltages are applied, the interpreter circuitry generates three distinct Interp signals that are dependent on the resistance of the memory cell. Interp signals are fed into the comparators. Out signals generated by the comparators indicate which resistive state the memory is in, and the read operation completes. Unlike the write operation, the read operation has a fixed duration, and this duration should be kept as short as possible to reduce the read disturbance which can cause the memory resistance to drift.

Figure 2.4: Flow chart explaining memory operations: a) Write Operation, b) Read Operation

#### 2.2.5 State Derivations

It is important to characterize the behavior of the read interpreter circuitry together with the array elements in order to understand how the component parameters should be selected.

First, we characterize the dependence of the resistive state of the memory cell on the intermediate node voltage. Then, we characterize the dependence of the intermediate node voltage on the series diode threshold based on the detection threshold requirements of the comparison stage and the current-voltage (IV) characteristics of the series diode in the interpreter circuitry.

The analog voltage levels in the intermediate node that correspond to the encoded resistive states can be characterized by the following equation:

$$V_{int} = V_{select-col} + \frac{R_{series}(V_{select-row} - V_{select-col} - V_{th_m})}{R_{parasitics} + R_{cell(s)} + R_{series}}$$

(2.3)

where  $R_{cell(s)}$  is the resistance of the selected cell at a given state and  $V_{th_m}$  is the cell threshold. Parasitic resistance sources represented by lumped  $R_{parasitics}$  term consist of the effective resistances of the n-type and p-type access transistors and the crossbar resistance seen by the interpreter circuitry. The read interpreter voltage division stage outputs meet the following equality when a particular memory state is being programmed:

$$V_{Interp_{3-k}} = V_{select-col} + \frac{(V_{int} - V_{diode_1} - V_{select-col})}{3}k = V_{c-res} + V_{select-col} \qquad (2.4)$$

where  $V_{Interp_{3-k}}$  represents the voltage level at the corresponding voltage division stage output (Interp), and k is the index of the corresponding voltage division stage output,  $V_{diode_1}$  is the threshold of the series diode in the interpreter circuitry and  $V_{c-res}$  is the comparator threshold. For analysis simplicity, the resistors connected to the outputs of diodes are assumed to have same resistances. However, it is possible to alter these resistances separately in order to tune the separation between resistive states of the memory cell. The decision on where to set the resistive states is highly dependent on the non-linear behavior of the device. The design decisions can also be made based on the trade-off between the programming time and the resistive margins.

Solving for  $V_{diode_1}$  in (2.4) yields:

$$V_{diode_1} = V_{int} - V_{select-col} - \frac{3}{k} V_{c-res}$$

$$\tag{2.5}$$

The above expression relates the intermediate node voltage with the series diode threshold. We need one more expression that relates the two in order to be able to numerically solve both to obtain  $V_{int}$  value, which we can plug in (2.3) to obtain corresponding resistive state level. The additional expression can be obtained using the diode current equation and solving for the diode threshold. The final expression is:

$$V_{diode_{1}} = 3I_{0}R_{h} + V_{int} - V_{select-col} - \frac{kT}{nq}LambertW[\frac{3e^{\frac{3I_{0}R_{h} + V_{int} - V_{select-col}}{kT/nq}}{I_{0}R_{h}}] \quad (2.6)$$

where LambertW is the lambert omega function,  $R_h$  is the magnitude of the resistances connected to the diode outputs,  $I_0$  is the reverse bias saturation current, n is the ideality factor, k is the Boltzmann constant, T is the absolute temperature and q is the magnitude of the charge of an electron.

Since  $I_0R_h$  term is extremely small, it can be omitted where it is an additive factor. The new simplified expression yields:

$$V_{diode_1} = V_{int} - V_{select-col} - \frac{kT}{nq} Lambert W[\frac{3e^{\frac{V_{int} - V_{select-col}}{kT/nq}}I_0R_h}{kT/nq}]$$

(2.7)

The expressions (2.5) and (2.7) form a pair of equations with two unknown pa-

rameters. They can be evaluated together numerically to obtain a unique pair of  $V_{int}$ and  $V_{diode_1}$  values which satisfy both. A unique pair is obtained for each resistive state since expression (2.5) depends on the state to be encoded. After obtaining unique pairs, the next step is to evaluate expression (2.3) to obtain corresponding resistive states.

|      | $\operatorname{Calculated}(\Omega)$ | Simulated( $\Omega$ ) | % Error |

|------|-------------------------------------|-----------------------|---------|

| '01' | 10064                               | 10166                 | 1.003   |

| '10' | 20227                               | 20590                 | 1.763   |

| '11' | 25653                               | 26067                 | 1.588   |

Table 2.1: Calculated vs. Simulated Resistance Levels

Table 2.1 lists the resistances calculated using expressions (2.3), (2.5) and (2.7) vs the results obtained through SPECTRE simulations of a 16x16 array. The percent error in calculations are also listed. The disagreement between the simulated and the calculated results are less than 2% for each programmed state. The leakage through the half-selected cells also contributes to the intermediate node voltage  $V_{int}$ ; however, the agreement between the simulated and calculated results indicate that this contribution to voltage mode reading is minimized especially owing to the 1D1R structure and the array biasing scheme used.

Another point to note is that the analytical models derived in this section are not dependent on the resistive device model used. The proposed circuitry behaves the same as long as the model meets the minimum and maximum resistances required for state encoding.

#### 2.3 Read/Write Operations

#### 2.3.1 Read/Write Simulations

Our simulations are performed on a 16x16 array with the adoption of distributed PI-model for the metal crossbars. The read interpreter circuitry is capable of per-

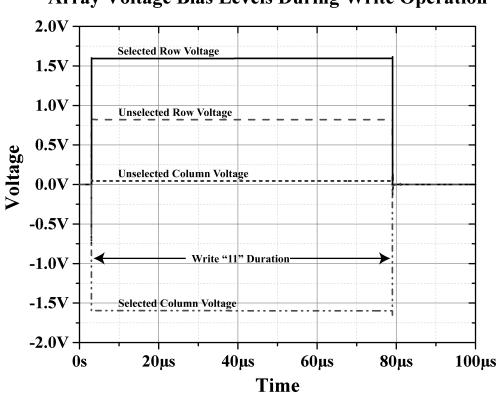

Array Voltage Bias Levels During Write Operation

Figure 2.5: Array biasing levels during a write operation

forming a read operation during a write operation by actively monitoring the voltage change across the series resistor connected to the selected column via the selection circuitry.

The bias voltages applied to the array during a write operation is shown in Figure 2.5. As explained earlier, this biasing scheme ensures that the disturbances to the unselected cells are minimized while the selected cell is exposed to a large voltage bias higher than the cell threshold. Example voltage levels shown in Figure 2.5 are:  $V_{select-row} = -V_{select-col} = 1.6V, V_{unselect-row} = 0.82V$  and  $V_{unselect-col} = 0.045V$ .

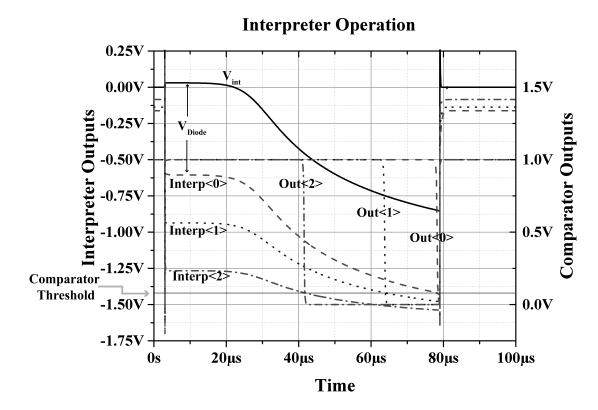

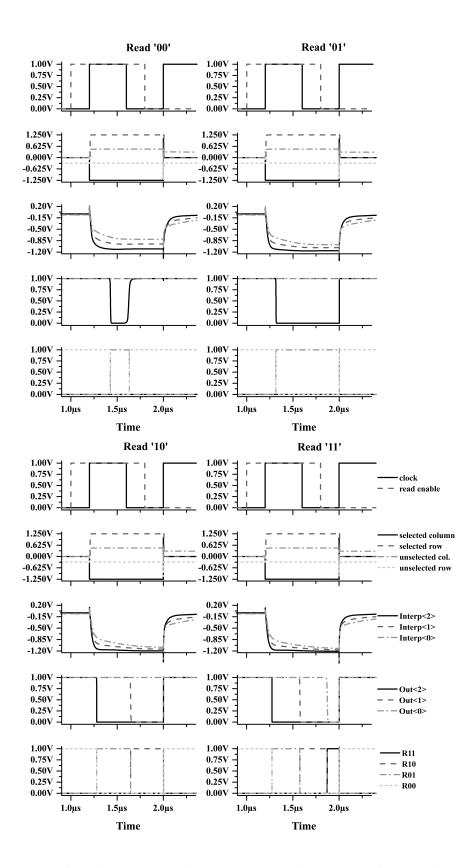

The operation of the interpreter circuitry is shown in Figure 2.6. The voltage division stage generates three distinct Interp signal levels which are then compared to the selection voltage that is also applied through the interpreter circuitry. Each Interp signal is connected to a comparator, and the comparator generates the corresponding Out signal that indicates if a certain state is reached. Interp signal levels

Figure 2.6: Interpreter operation during a write operation. The value being written is '11'

decrease as the resistance of the cell increases. Once the signal level reaches below the comparator threshold, the comparator output (Out) signal becomes low, signaling to the controller.

In our simulations  $Out\langle 2 \rangle$ ,  $Out\langle 1 \rangle$  and  $Out\langle 0 \rangle$  indicate that the states '01', '10' and '11' are reached, respectively. The series diode provides a close-to-constant voltage reduction of the intermediate voltage to be interpreted, allowing Interp signals to reach the comparator threshold more quickly; thus, reducing the write time and compacting the resistance levels.

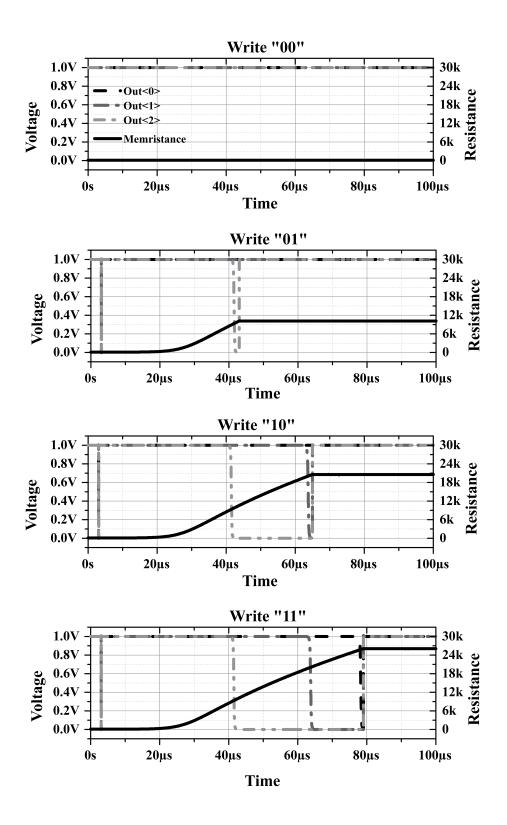

Figure 2.7 shows writing of states '00', '01', '10' and '11'. Since state '00' is the erase state of the cell, the controller does not apply any voltage to the array to change the state, and the Out signals remain high.

In '01', '10' and '11' cases, as the resistance of the cell increases, the Out signals start to become low. Once the desired resistances are reached, the controller stops applying write voltages to the array, and the Out signals become high again.

Since the read interpreter circuitry monitors the state of the cell as it is being written, the read operation can be implemented using the same biasing scheme as the write operation while keeping the pulse duration short to prevent significantly altering the resistive state of the memory. Since the write operation programs each cell to the point of detection, there is a significant read margin when the cell drifts toward a higher resistance; however, there is no margin if the cell drifts toward a lower resistance and a wrong value can be read. In order to mitigate this problem, modifications on the read scheme by reducing the pulse magnitudes used, and/or increasing the series resistance value during a read operation are proposed. The optimizations to the read operation will be discussed further in the following sections.

Figure 2.7: Writing of various values into the selected memory cell. Resistance change is overlapped with interpreter output signals.

#### 2.3.2 Read Disturbances to the Neighboring Cells

Even though each memory cell has a built-in threshold, a voltage bias below this value still induces a trivial resistance change in the cell. This means that the cell resistance can drift over time due to the repeated reading of the cell or due to the read and write operations performed on other cells in the array.

In order to quantify the effects of read disturbances in the presented architecture, the resistance drift of the neighboring cells to a selected cell is simulated while the selected cell is read repeatedly. Since the amount of drift is state dependent, the simulations for different values stored in the memory cell and its neighbors are performed. We have assumed the same voltage levels and the series resistance as used during a write operation to simulate the worst case drift. As any reduction in read voltage and increase in series resistance would yield better drift characteristics as shown in Figure 2.8.

The results indicate that for the cases of '01', '10' and '11', the greatest resistance drift is observed in the cells that are connected to the same column as the selected cell. The cells connected to the same row as the selected cell observe a drift that is less-however, still non-zero. The remaining cells observe a close-to-zero drift within the simulated 100 consecutive read operations. Among these three resistive states, the greatest change is observed when the selected cell is storing '11' due to the fact that the voltage bias across the unselected cells connected to the same column as the selected cell is highest.

In the case when the memory cell is storing '00', no meaningful change in resistance was observed, hence the results are not listed.

Figure 2.8: Percent change of resistance in neighboring cells vs. number of read operations. The cell located at the crossing of row 7 and column 7 (R7C7) is selected.

Figure 2.9: Write voltage sweep. How the resistive states change is shown with dashed and dotted lines. Maximum write time which corresponds to writing of state '11' is shown with straight line.

## 2.4 Effects of Variations

#### 2.4.1 Variations in Programming Voltage

As indicated by expressions (2.3), (2.5) and (2.7), the programmed states are dependent on the voltage levels used. If the voltage bias levels are scaled, the programmed states change accordingly as shown in Figure 2.9.

The selected row and column pulse magnitudes are kept equal and are listed in the x-axis while their signs are opposite. Although it is possible to scale the unselected row and column voltages separately, they were reduced or increased the same amount as the selected row and column voltage magnitudes. It was found that this scaling scheme provided more even scaling of the applied voltages to the unselected and half selected cells.

The results show that as the voltage levels are increased, the programmed resistance levels increase. This also results in increase in the programming time of the cell. As the resistance levels increase, the separation between the states increases, which can allow for better margin of detection.

Since a read operation is a write operation with an extremely short duration, the results reported in Figure 2.9 have important consequences in terms of improving the tolerance for resistance drift in both increasing and decreasing directions. If a cell is written at a pulse magnitude of 1.6V, it can still be read at, for example, 1.55V while allowing drift in its resistance. This can be further clarified by comparing the programmed resistances for both voltage levels as shown in Table 2.2.

|             | 1.6V           | $1.55\mathrm{V}$ | $MARGIN_{H}$    | $MARGIN_L$      |

|-------------|----------------|------------------|-----------------|-----------------|

| <b>'00'</b> | $100 \ \Omega$ | $100 \ \Omega$   | 8801 $\Omega$   | -               |

| <b>'01'</b> | 10166 $\Omega$ | 8901 $\Omega$    | $8099 \ \Omega$ | 1265 $\Omega$   |

| <b>'10'</b> | 20590 $\Omega$ | 18265 $\Omega$   | $3125 \ \Omega$ | $2325 \ \Omega$ |

| '11'        | 26067 $\Omega$ | 23715 $\Omega$   | 76285 $\Omega$  | $2352 \ \Omega$ |

Table 2.2: Comparison of Resistive States

The '11' state programmed at 1.6V has resistance of 26067  $\Omega$ . However, if this programmed resistance is read at 1.55V, it would yield a value of '11' since 26067  $\Omega$  is greater than the '11' value written at 1.55V which is 23715  $\Omega$ . In fact, reading at 1.55V allows the programmed resistance of 26067  $\Omega$  to drift up to the device maximum, which is assumed to be 100  $K\Omega$ , or down to the boundary of state '10', which is 23715  $\Omega$ .

Table 2.2 lists the high and low resistance margins that are the distances of the programmed resistances of the memory states at higher voltage level to the detection boundaries of the lower voltage reads. It is possible to optimize these margins by scaling the circuit parameters that contribute to the resistive states as characterized in Section 2.2.5.

Figure 2.10: Series Resistance Sweep. The change in programmed states vs the series resistance value is shown for fixed write voltage levels.

#### 2.4.2 Variations in Series Resistance

The programmed states are also dependent on the series resistance used, similar to the case of pulse magnitudes. The change in programmed resistances versus the series resistance is shown in Figure 2.10.

For fixed write pulse magnitude of 1.6V, the increase in series resistance results in increase in programmed resistances. The same trend as in the case of increased voltage levels is observed. The separation between the states increases with increased series resistance, which can allow for better margin of detection.

Similar to the case of voltage reduction, the reduction of series resistance when reading allows for generation of high and low margins, which in turn allows for drift in both increasing and decreasing directions. An example is not provided for this case in order to avoid repetition; however, similar results as in Table 2.2 can be deduced from values plotted in Figure 2.10.

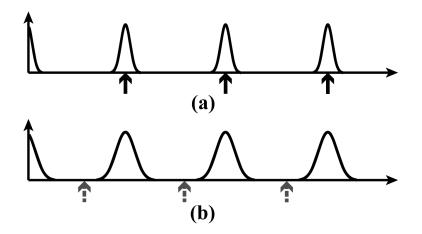

Figure 2.11: Resistance distributions when a single device is programmed in the whole array (a), after all the cells are programmed in the whole array (b). The black arrows indicate a sample cell resistances. The grey dashed arrows indicate where the lower boundaries of the resistive states shift when reduced-impact read scheme is used.

#### 2.4.3 Reduced-Impact Read Scheme

Even more powerful benefits can be obtained when both the read voltages and the series resistance are scaled simultaneously.

Figure 2.9 indicates that it is not possible to scale the read pulse magnitudes to 1.5V because the lower boundary for '11' state is 18891  $\Omega$  which is lower than the '10' boundary (20590  $\Omega$ ) for 1.6V writes. This means '10' written at 1.6V would be evaluated as '11' at 1.5V reads. However, the increase in series resistance shows the opposite trend as in the case of decrease in read voltage. Therefore, it is possible to perform reads even below 1.5V pulse magnitude with the help of increased series resistance.

The simulations indicated that it is possible to write the values at 1.6V with  $20K\Omega$  resistance, and then read at 1.5V pulse magnitude with  $25K\Omega$  series resistance or at 1.25V pulse magnitude with  $45K\Omega$  series resistance.

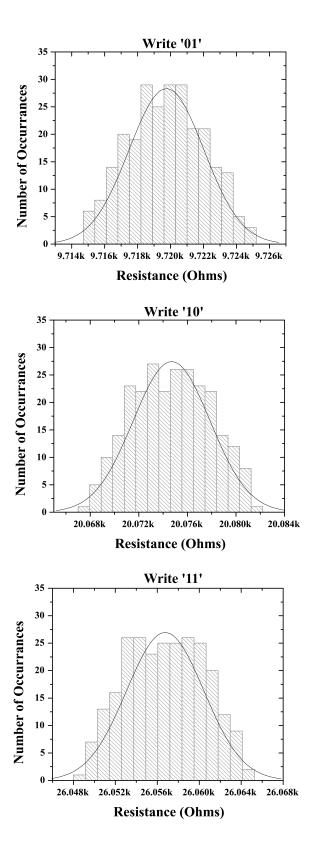

Figure 2.11 aims to visualize how the reduced-impact read scheme works together with the write scheme. When a single cell is programmed in the array, its resistance can land anywhere in the distributions shown in Figure 2.11a, depending on its loca-

Figure 2.12: Reduced impact read operation. Relevant signals are shown for each state.

tion in the array. In this case, the variation in resistances is due to the change in the lumped crossbar parasitic resistance seen by the interpreter circuitry, depending on the location of the memory cell in the array. As more cells are programmed in the array, the resistances of the previously-programmed cells start to drift due to write disturbances, causing the spreading of the resistance distributions as shown in Figure 2.11b. Most approaches in literature fail to address this spreading; however, write simulations on the whole array are performed sequentially to show the spreading and shifting of the states, and the results are presented in the next part of this section.

The reduced-impact scheme aims to shift the lower detection margins such that the new distributions fall completely within their intended resistive states.

Figure 2.12 shows the reduced-impact read operations performed on cells storing the four possible values. A cell located at the middle of the array is selected. The scheme uses 1.25V pulse magnitude with  $45K\Omega$  series resistance. In each case, when the controller receives the read enable signal, it facilitates the application of the bias voltages on the array. How Interp signals settle depending on the value that the cell is storing is shown. Interp signals settle in decreasing order, hence Out signals flip in the decreasing order as well. Signals R11, R10, R01 and R00 are the controller signals indicating whether a particular state is detected. The sequential flipping of Out signals also cause these signals to flip; however, the correct result is obtained at the end of the read operation.

#### 2.4.4 Resistance Distributions after Array Writes

The consecutive write operations on the neighboring cells cause the cell resistances to drift over time. Even though unselected and half selected cells are biased with low voltages, the leakages during the lengthy write durations add up and cause the array resistances to drift.

In order to quantify this drift, consecutive write operations are performed on every

Figure 2.13: Resistance distributions after programming the entire array with the same value.

cell of the array. The resulting resistance distributions are listed in Figure 2.13. The distributions include the effects of writes to the neighboring cells and the parasitic crossbar resistances as these values change depending on the location of the selected memory cell. The variations from the nominal value are within the margins that can be obtainable with the reduced-impact read scheme proposed in this section. Therefore, it is concluded that it is possible to write to the cells in the whole array, and then read the values using the presented read scheme while allowing margin for additional drift that can be caused by repeated read operations.

## 2.5 Conclusion

In this chapter a multi-level memristor memory architecture that incorporates a novel read-monitored-write scheme was presented. The architecture allows for programming of the cells to the detection thresholds with very tight state distributions. In addition, an analytical model for state derivations which can be utilized to decide on the component parameters to be used in the design was presented. Various read schemes where voltage reduction or series resistance increase or a combination of both can be used to evaluate the resistive state of the memory cell were also presented. Finally, the resistive distributions after the entire array is written were shown. These distributions fall within the detection margins of the proposed read methods.

## CHAPTER III

# Image Processing by a Programmable Artificial Retina Comprising Quantum Dots and Variable Resistance Devices

## 3.1 Introduction

Feature extraction is a fundamental task in vision systems as extracted features provide bases for correlation. In digital general purpose processors, many image processing applications require an immense number of operations per second, albeit these applications do not require floating point accuracy [52]. Use of fast, simple and relatively accurate extraction systems in vision machines directly reduces the processing time and required iterations. The main processor element can thereby rely on the reduced dataset that provides quality information on the extracted features for decision making.

Inherent parallel processing capabilities of Cellular Nonlinear Network (CNN) based architectures make them an efficient platform for various image processing tasks [53, 54]. Real time operation provides fast processing times, and local connections provide simplicity, scalability and power efficiency for VLSI implementations [55]. Therefore, much effort has been put into developing novel methods and finding adequate CNN templates to perform detail extraction tasks in vision systems, such as edge detection [56, 57, 58] which benefit greatly from immense parallelism and computational efficiency.

Resistive grid based architectures are shown to provide simple yet efficient ways to perform many image processing tasks and motion detection, and they are simple forms of CNNs [53]. Additional advantages including compact area, noise immunity and lower power consumption compared to digital computation structures, make them attractive for researchers. They are also relatively insensitive to mismatches in component values in VLSI chips [59]. However, most of the resistive grid based architectures in literature are static application specific structures and do not have the functional flexibility of their digital counterparts. Therefore, novel methods and devices should be introduced in these architectures to achieve functional versatility.

Resonant tunneling diodes (RTDs) have been employed in many applications including various CNN architectures due to their negative differential resistance (NDR) and fast switching characteristics. In [60] RTDs have been introduced as variable resistors to introduce versatility and compactness to CNN unit cells. In [61] a CNN architecture employing RTDs is investigated for its operation and it is shown that RTDs support fast settling times for various image processing applications.

In this chapter, a variable resistance grid-based architecture which improves the velocity tuned filter (VTF) architecture proposed by our group [62] is presented. It is demonstrated that when variable resistance connections are incorporated, various diffusion characteristics are obtained, and the developed architecture can be programmed for different image processing applications such as edge detection and line detection providing flexible analog processing environment that can perform various tasks. In addition RTDs are utilized to provide high speed signal detection and amplification. A method to program resistive connections in four directions is also demonstrated.

## 3.2 CNN Architecture

#### 3.2.1 Resonant Tunneling Diode Model and Biasing

RTDs have been employed in many circuit applications utilizing their fundamental characteristic of negative differential resistance (NDR). NDR implies that for certain range, the increase in applied voltage across an NDR device will result in decreased current through it, indicating increased resistance with increased voltage.

RTD conductance is determined by two mechanisms: The first mechanism is resonant tunneling, which provides the NDR characteristic, and the other mechanism is diode conduction.

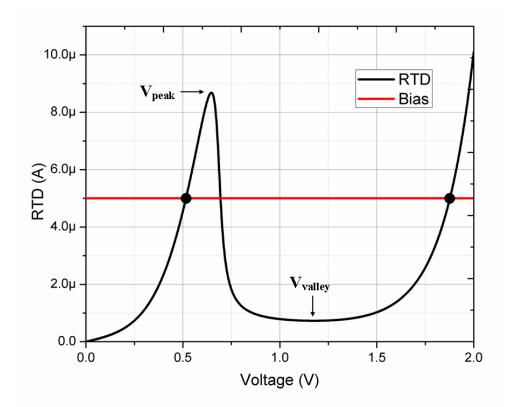

The NDR property of the RTD I-V characteristics is shown in Figure 3.1 utilizing the physics-based model laid out in [63]. The RTD current  $J_{RTD}(V)$  is given by:

$$J_1(V) = \frac{qm^*kT\Gamma}{4\pi^2\hbar^3} ln(\frac{1+e^{(E_F-E_r+n_1qV/2)/kT}}{1+e^{(E_F-E_r-n_1qV/2)/kT}}) * (\frac{\pi}{2} + \arctan(\frac{E_r-n_1qV/2}{\Gamma/2})) \quad (3.1a)$$

$$J_2(V) = H(e^{n_2 q V/kT} - 1)$$

(3.1b)

$$J_{RTD}(V) = J_1(V) + J_2(V)$$

(3.1c)

where  $J_1(V)$  is the current due to resonant tunneling and  $J_2(V)$  is the diode conduction current.  $E_F$  is the Fermi energy,  $E_r$  is the resonant level energy,  $\Gamma$  is the resonant width,  $n_1$  and  $n_2$  are empirical model parameters.  $q, m^*, k, T, \hbar$  are electron charge, effective mass, Boltzmann constant, absolute temperature, and reduced Planck constant respectively. V is the voltage across the device.

The main advantage of the NDR characteristic becomes apparent when RTD is biased with a static current source. If current magnitude of the source is selected such that it intersects RTD I-V curve in three places as shown in Figure 3.1, two stable voltage points are obtained. This result indicates that for the same amount

Figure 3.1: RTD I-V curve. The red line corresponds to the bias level. The intersections of the two lines represent the stable operating points.

of current passing through RTD, the voltage across it can take two stable values which correspond to the lowest and highest voltage intersection points. RTD does not stabilize in the middle intersection point, since any small disturbance causes it to switch to one of the outer intersection points.

The bistable characteristic of this structure can be utilized to build voltage level detectors since any voltage below switching threshold results in stabilizing in the low state, and any voltage above threshold results in stabilizing in high state. RTD switching threshold can be approximated as:

$$V_{th_{RTD}} = \frac{V_{peak} + V_{valley}}{2} \tag{3.2}$$

where  $V_{peak}$  and  $V_{valley}$  are the peak and the valley voltages of the RTD, respectively. When used in the detection mode, as the system starts all the RTDs are biased to the low voltage state, and a controlled disturbance toward a higher voltage results in the RTDs stabilizing at the higher stable level, allowing the detection and locking of the signal state.

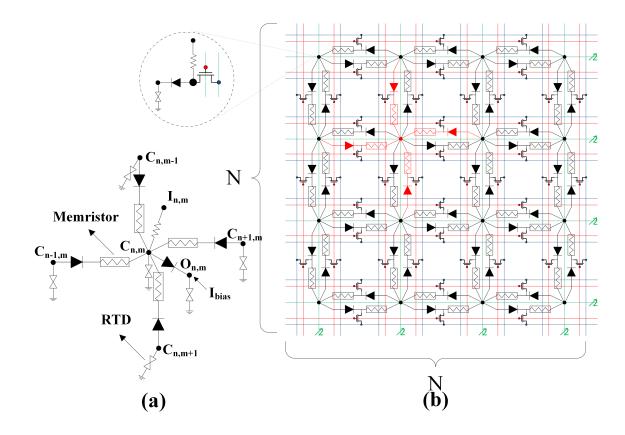

#### 3.2.2 Unit Cell Structure

Figure 3.2a shows the proposed unit cell structure. It is composed of variable resistance devices to provide resistive connections to neighboring cells, diodes to introduce unidirectionality to these connections, and RTDs to detect and latch signal levels. The proposed cell has an input node denoted by  $I_{n,m}$ , a center node  $C_{n,m}$ , and an output node  $O_{n,m}$ . The input is driven by voltage signals that correspond to the pixel intensity level which can be generated by a photo-detector. The connections employing variable resistance devices provide programmability for the realization of different characteristics including isotropic, anisotropic symmetrical and

Figure 3.2: (a) Variable resistance unit cell (b) Top view of the processing array. A unit cell is highlighted in red. Red and green lines denote programming connections to access transistors.

asymmetrical diffusion in grid architecture giving way to various spatiotemporal filter implementations.

Four variable resistors are connected to the center nodes of the unit cell and its neighbors, making the center node voltage a function of the center node voltages of the neighboring cells. Resistances of connections determine how much neighbors' center voltages contribute to the center voltage of the cell. Series diodes allow current in one direction separating how outputs of the two neighboring cells affect each other. The output node is isolated from the center node by a diode providing a voltage barrier equal to the diode threshold. RTDs enable detection and latching of output signals. When biased with a current source, RTDs initially settle at the lower stable voltage. When the voltage level on the center node goes above detection threshold, RTDs settle at the higher stable voltage. Two stable states provide a binary output. The detection threshold is equal to the sum of the diode threshold and the switching threshold of the RTD.

Figure 3.2b shows unit cells connected in a 2D array fashion. A top view for a 4x4 sample processing array is provided to show the neighboring connections. The unit cell shown in Figure 3.2a is highlighted in red. In order to program certain functionalities in the array, the resistances need to be altered. The Green lines in Figure 3.2b indicate the programming connections to the cells. Each green connection denotes programming-enable signal and voltage driver connections. Access transistors are used to isolate the connections during normal array operations. Programming connections can also be made to share the same connections as cell inputs, thus reducing number of access transistors if the input resistances are designed to be small at the expense of increased programming time or increased programming voltages due to voltage drop across the input resistor. Connections shown in red and blue as well as access transistors are needed during cell erase to bypass reverse biased diodes. During erase operation voltage polarity across the variable resistance device is reversed.

## 3.3 Programming Variable Resistance Connections

To be able to implement different processing tasks in the same array, we need a procedure to program the resistances of the resistive connections.

Figure 3.3 shows the programming flow for an N x N array. Programming is performed in four directions (left-to-right, right-to-left, top-to-bottom, and bottomto-top) one direction at a time. Programming of the whole array is completed in four passes across the array in different directions to change the resistances in these directions. While a pass is being made in one direction, the resistances are set in a column by column fashion. Programming in this fashion reduces the total required

Figure 3.3: Array programming flow

time significantly compared to programming every resistive cell in the array individually. The duration and voltage amplitude of the write pulses determine the resistance to be stored in the connections.

Within one direction, same voltage amplitudes and pulse durations are used. However, pulse characteristics can be changed in different directions to program different resistances, hence to program different functionalities to the array.

A sample programming operation in the left to right direction is shown in Figure 3.4. All the connections in the array are initially at the low resistance state. The programming begins by setting the first column write voltage to high (indicated with a red line) and the remaining columns (indicated with a green line) to low (0V in our implementation).

In this configuration the first column of connections observe a non-zero voltage difference across, whereas the remaining connections observe zero voltage difference. In the first column, only half of the connections are programmed due to the fact that half of the series diodes are forward-biased conducting high currents, and the other half are reverse-biased.

Once the resistances of the first column connections reach the desired level, the second column write voltage is set to high, making the voltage difference across these connections zero, thus stopping their programming. The rise of the voltage levels on the second column in turn causes the voltage difference across the next column connections to be non-zero. Once these connections reach the desired resistance, the next column's voltage is raised. This process is repeated until all the connections in the selected direction are programmed.

When programming in the selected direction is completed, another direction is selected and the same process is repeated in this new direction. The use of different voltages or change of voltage raise-durations result in programming of different resistances in this direction.

Figure 3.4: Programming in one direction. The green lines indicate the low voltage level (0V); other colors indicate altered high voltage levels. The different colors of variable resistance devices indicate different final resistances: a) Array in initial state, b) Programming started in left to right direction, c) Programming of first column completed in left to right direction, d) Programming of all connections completed in left to right direction, e) Programming of first column completed in right to left direction, f) Whole array after all connections are programmed in all directions

Figure 3.5: Programming in one direction in a 4 by 4 array: Programming voltages

Figure 3.5, sample left-to-right direction programming voltages to the array are shown. As described earlier, write voltages are applied per column basis. Voltage levels are increased with same time intervals.