# Attacking and Defending Emerging Computer Systems Using the Memory Remanence Effect

by

Amir Rahmati

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in The University of Michigan 2017

Doctoral Committee:

Professor Atul Prakash, Chair Professor J. Alex Halderman Professor Peter Honeyman Professor Vineet Kamat Amir Rahmati

rahmati@umich.edu

ORCID iD: 0000-0001-7361-1898

$\bigodot$  Amir Rahmati 2017

To my family,

for their unconditional love and support.

### ACKNOWLEDGEMENTS

It is said that every life is a story. If that is the case, my time as a graduate student will be definitely categorized as an adventure. I am in debt to many great people in it.

I thank my advisor, Atul Prakash, for believing and investing in me. His constant support was a definite factor in bringing this dissertation to its completion.

Matthew Hicks, a collaborator, mentor, and friend, whose support and guidance helped me through some of the toughest times in my Ph.D. career.

Members of my thesis committee, J. Alex Halderman, Peter Honeyman, and Vineet Kamat for their insightful suggestions, comments, and support.

I am grateful to Jaeyeon Jung whose deep understanding of the scientific method and problems and solutions in the IoT space taught me valuable lessons on how to conduct systems research. I am equally thankful to Harsha Madhyastha, who helped me expand my knowledge in Distributed Systems and intellectually challenged me to perfect my system designs. Morley Mao, Wayne Burleson, Jacob Sorber, and Dan Holcomb, whose scientific insights helped me throughout my research career.

This journey would have never been the same without my close friend and brotherin-arms, Earlence Fernandes, who always challenged me and pushed through project after project with me, and my labmate and friend, Kevin Eykholt, whose views added new dimensions to our work.

I thank Kevin Fu, who taught me the ABCs of research and helped me start my journey toward my Ph.D. My collaborator and friend Mastooreh Salajegheh, who mentored me on my first research projects, and all members of the SPQR lab whom I worked with: Benjamin Ransford, Shane Clark, Andres Molina-Markham, Denis Foo Kune, Shane Guineau, Joel Van Der Woude, Aravind Vadrevu, Michael Rushanan, Tim Trippel, Ofir Weisse, and Sai R. Gouravajhala.

I'm also grateful to my friends and colleagues Minghe Yu, Jie Song, Zhongjun Jin, Nikita Bhutani, Shichang Xu, Yunhan Jack Jia, Qi Alfred Chen, Shiqi Wang, and my fellow Iranians and friends at the University of Michigan and the University of Massachusetts Amherst. Some of them are, Ashkan Nikravesh, Mehrdad Moradi, Hamed Yousefi, Armin Sarabi, Mahdi Aghadjani, Hamed Soroush, Banafsheh Seyedaghazadeh, and Parya Pourazarm.

Finally, I thank my father, Abdolreza Rahmati, mother, Fariba Khashehchi, and brother, Ahmad for being the constant pillars of support in my life, my extended family, friends at Sharif and Allemeh Helli, and to my dear friends who helped me bring this adventure to its end.

> "Our revels now are ended. These our actors, As I foretold you, were all spirits and Are melted into air, into thin air: And, like the baseless fabric of this vision, The cloud-capp'd towers, the gorgeous palaces, The solemn temples, the great globe itself, Yea, all which it inherit, shall dissolve And, like this insubstantial pageant faded, Leave not a rack behind. We are such stuff As dreams are made on, and our little life Is rounded with a sleep." — William Shakespeare, The Tempest

# TABLE OF CONTENTS

| DEDICATION                                                                                                                                       | ii   |

|--------------------------------------------------------------------------------------------------------------------------------------------------|------|

| CKNOWLEDGEMENTS                                                                                                                                  | iii  |

| IST OF FIGURES                                                                                                                                   | viii |

| IST OF TABLES                                                                                                                                    | xii  |

| BSTRACT                                                                                                                                          | xiv  |

| CHAPTER                                                                                                                                          |      |

| I. Introduction                                                                                                                                  | 1    |

| 1.1 Contributions of This Dissertation                                                                                                           | 2    |

| 1.1.1 Probable Cause: Deanonymizing Effect of Approxi-<br>mate Memory                                                                            | 2    |

| 1.1.2 TARDIS: Providing a Notion of Time to Transiently<br>Powered Devices                                                                       | 3    |

| 1.1.3 DRV-Fingerprinting: Using Data Retention Voltage<br>for Chip Identification                                                                | 4    |

| II. Probable Cause: Deanonymizing Effect of Approximate Mem-<br>ory                                                                              | 5    |

| 2.1 Introduction                                                                                                                                 | 5    |

| 2.2 Background                                                                                                                                   | 8    |

| 2.3 Threat Model $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                | 10   |

| 2.4 Design of Probable Cause                                                                                                                     | 11   |

| 2.5 Mechanics of Probable Cause                                                                                                                  | 13   |

| 2.5.1 Characterization                                                                                                                           | 14   |

| $2.5.2  \text{Identification} \dots \dots$ | 15   |

| $2.5.3$ Clustering $\ldots$                                                                                                                      | 18   |

| 2.6 Experimental Setup                                                                                                                           | 18   |

|      | 2.7        | Evaluation                                                                                         |

|------|------------|----------------------------------------------------------------------------------------------------|

|      |            | 2.7.1 Uniqueness                                                                                   |

|      |            | 2.7.2 Consistency $\ldots \ldots 2$ |

|      |            | 2.7.3 Thermal effect                                                                               |

|      |            | 2.7.4 Order of failures                                                                            |

|      |            | 2.7.5 Accuracy versus privacy                                                                      |

|      |            | 2.7.6 Eavesdropping attacker evaluation                                                            |

|      | 2.8        | Discussion                                                                                         |

|      |            | 2.8.1 Effect of DRAM technology                                                                    |

|      |            | 2.8.2 Defenses against Probable Cause                                                              |

|      |            | 2.8.3 Error localization                                                                           |

|      | 2.9        | Related Work                                                                                       |

|      |            | 2.9.1 Analog artifacts in a digital World                                                          |

|      |            | 2.9.2 Approximate memory                                                                           |

|      | 2.10       | Conclusion                                                                                         |

|      |            |                                                                                                    |

| III. | TARI       | DIS: Providing a Notion of Time to Transiently Powered                                             |

|      | Embe       | dded Devices                                                                                       |

|      |            |                                                                                                    |

|      | 3.1        | Introduction                                                                                       |

|      | 3.2        | Intermittently Powered Devices: Background, Observations,                                          |

|      |            | and Challenges                                                                                     |

|      |            | 3.2.1 Threat Model and Assumptions 4                                                               |

|      | 3.3        | The TARDIS Algorithms                                                                              |

|      |            | 3.3.1 TARDIS Performance                                                                           |

|      | 3.4        | Securing Protocols with the TARDIS                                                                 |

|      |            | 3.4.1 Implementation and Evaluation 5                                                              |

|      | 3.5        | Security Analysis                                                                                  |

|      | 3.6        | Factors Affecting SRAM Decay                                                                       |

|      | 3.7        | Inside an SRAM Cell                                                                                |

|      |            | 3.7.1 Memory Decay Mechanisms 6                                                                    |

|      |            | 3.7.2 Choosing a State to Write 6                                                                  |

|      | 3.8        | Alternative Approaches                                                                             |

|      | 3.9        | Model of Decay Probabilities                                                                       |

|      | 3.10       | Related Work                                                                                       |

|      | 3.11       | Conclusions                                                                                        |

|      |            |                                                                                                    |

| IV.  |            | Fingerprinting: Using Data Retention Voltage of SRAM                                               |

|      | Cells      | for Chip Identification                                                                            |

|      | 4.1        | Introduction                                                                                       |

|      | 4.1        | Data Retention Voltage   7                                                                         |

|      | 4.2<br>4.3 | Characterizing the DRV of an SRAM Cell                                                             |

|      | 4.0        | 4.3.1 Experimental Setup                                                                           |

|      |            | 4.3.1 Experimental Setup                                                                           |

|      |            | 4.5.2 IIIOI IIIAIIOII COILEILI OI SKAWI CEIL DRV (                                                 |

|           | 4.3.3 Observations about Strong and Weak Cells  | 79  |

|-----------|-------------------------------------------------|-----|

|           | 4.3.4 Relation to Power-up State                | 80  |

| 4.4       | Fingerprint Matching                            | 82  |

|           | 4.4.1 Identification at Nominal Temperature     | 83  |

|           | 4.4.2 Impact of Temperature Variations          | 86  |

| 4.5       | Related Works                                   | 86  |

| 4.6       | Conclusions and Future Works                    | 87  |

| V. Surve  | y of Related Work                               | 93  |

| 5.1       | Physical Unclonable Functions                   | 93  |

| 5.2       | Approximate DRAM                                | 94  |

| 5.3       | DRAM Energy Saving Techniques                   | 95  |

| VI. Futur | e Work & Conclusion                             | 99  |

| 6.1       | Future Work                                     | 99  |

|           | 6.1.1 Security of Emerging IoT Platforms        | 99  |

|           | 6.1.2 Security of Approximate Computing Systems | 100 |

|           | 6.1.3 Trusted Execution Environments            | 100 |

| 6.2       | Concluding Remarks                              | 100 |

| BIBLIOGRA | РНҮ                                             | 102 |

# LIST OF FIGURES

## Figure

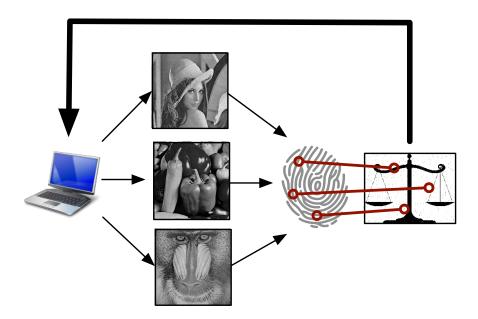

| 2.1 | Probable Cause creates a fingerprint of an approximate DRAM system                                                                 |     |

|-----|------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | by collecting approximate outputs and stitching together error pat-                                                                |     |

|     | terns in those outputs to form a fingerprint for the memory. Attackers                                                             |     |

|     | can then use this memory fingerprint to identify other approximate                                                                 |     |

|     | outputs as belonging to the system                                                                                                 | 6   |

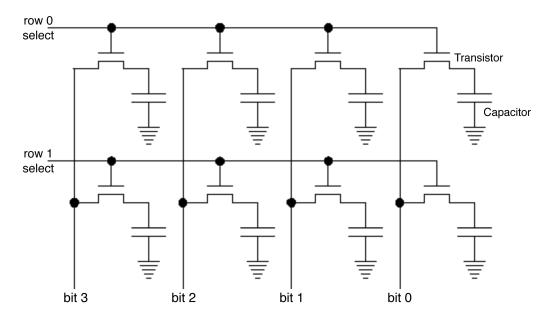

| 2.2 | A DRAM cell has a default low value that can be changed by charging                                                                |     |

|     | the capacitor. DRAM cells need to be constantly refreshed for the                                                                  |     |

|     | value to hold, otherwise capacitor leakage slowly reverts the cell to                                                              |     |

|     | its default value. All DRAM operations are done at row granularity.                                                                | 9   |

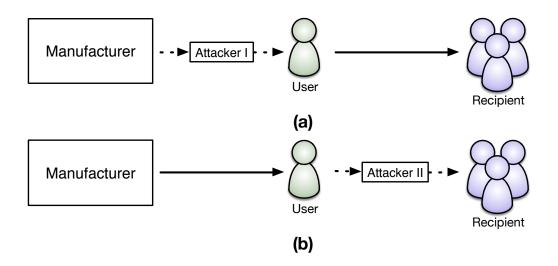

| 2.3 | Probable Cause tackles two attack scenarios: (a) the attacker inter-                                                               |     |

|     | cepts and fingerprints the entire memory (as a part of a system or a                                                               |     |

|     | standalone module) in the supply chain and (b) the attacker captures                                                               |     |

|     | approximate outputs from a deployed system to create a fingerprint.                                                                | 11  |

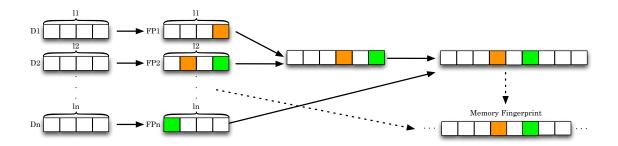

| 2.4 | Probable Cause constructs the whole-memory fingerprint by stitching                                                                |     |

|     | together fingerprints of overlapping approximate outputs. Pages of                                                                 |     |

|     | the same color are the same page and are matched by Probable Cause                                                                 | 10  |

| ~ ~ | using page fingerprints.                                                                                                           | 12  |

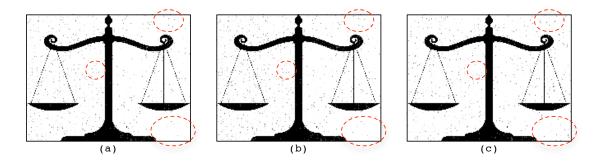

| 2.5 | Three identical images after storage in approximate memory. Image (c)                                                              |     |

|     | is stored in a different chip than (a) and (b). Simple visual inspection                                                           | 10  |

| ົງເ | reveals similar patterns of errors in results coming from the same chip.                                                           | 13  |

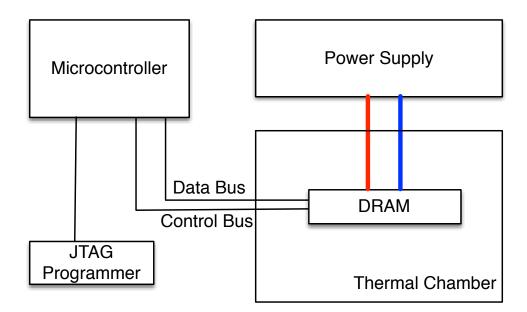

| 2.6 | Probable Cause experimental platform. The MSP430 microcontroller                                                                   |     |

|     | controls DRAM read/write functions. The target DRAM is placed<br>inside a thermal chamber to ensure environment consistency across |     |

|     | experiments. The JTAG programmer allows us to program the micro-                                                                   |     |

|     | controller and extract the results                                                                                                 | 20  |

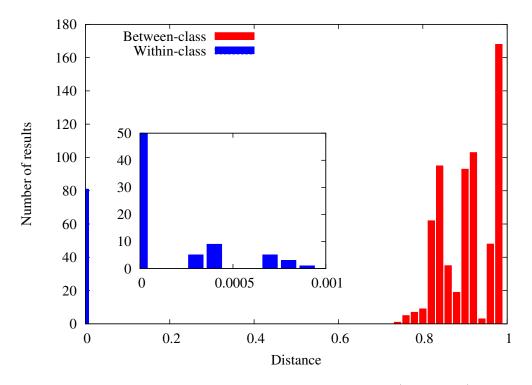

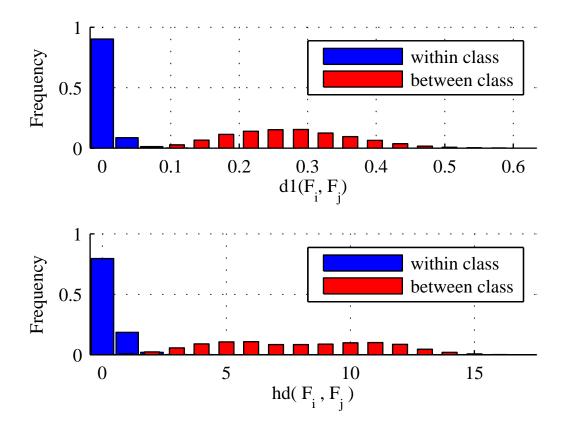

| 2.7 | Histogram of fingerprint distances for within-class (same chip) and                                                                | 20  |

| 2.1 | between-class (other chips) pairings                                                                                               | 22  |

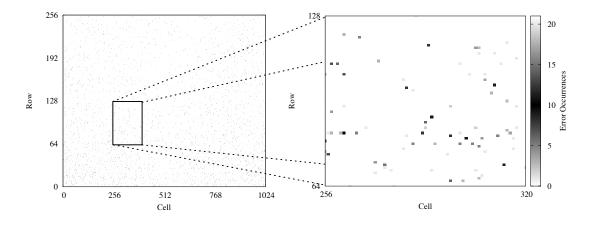

| 2.8 | Heatmap of cells unpredictability in a sample DRAM chip. Darker                                                                    |     |

| 2.0 | cells behave more like noise. More than 98% of cells behave reliably                                                               |     |

|     | across all 21 runs.                                                                                                                | 24  |

| 2.9 | Histogram of between-class (different chips) pair distances grouped                                                                | - 1 |

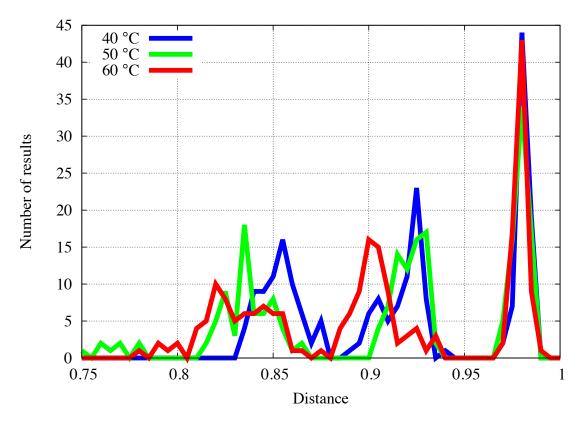

|     | by temperature. Temperature has no noticeable effect on distance.                                                                  | 25  |

|     | v                                                                                                                                  |     |

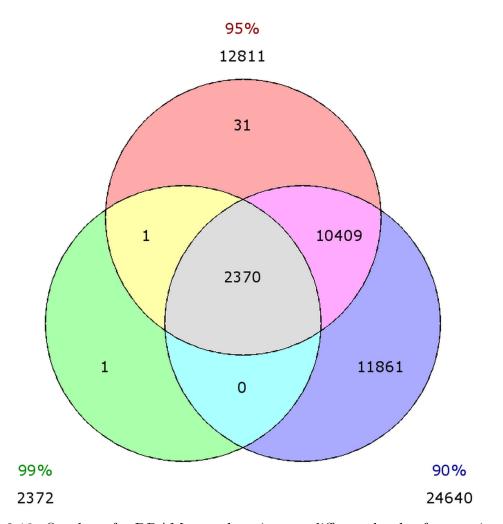

| 2.10 | Overlap of a DRAM error locations at different levels of approximation. The results support a rough subset relation $99\% \subset 95\% \subset 90\%$                                                    | 26 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

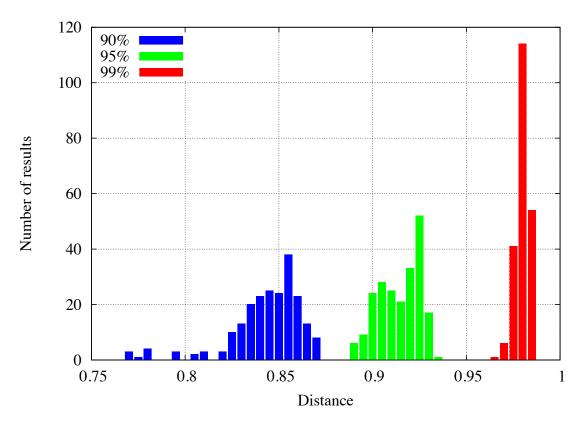

| 2.11 | Histogram of between-class chip distance grouped by approximate<br>memory accuracy. The increased chance of bit error overlap causes the                                                                | 20 |

|      | average distance to shrink with increases in approximation. Note that<br>these distances are still two orders larger than the largest within-class                                                      | 07 |

| 2.12 | distance                                                                                                                                                                                                | 27 |

|      | code used to evaluate Probable Cause.                                                                                                                                                                   | 29 |

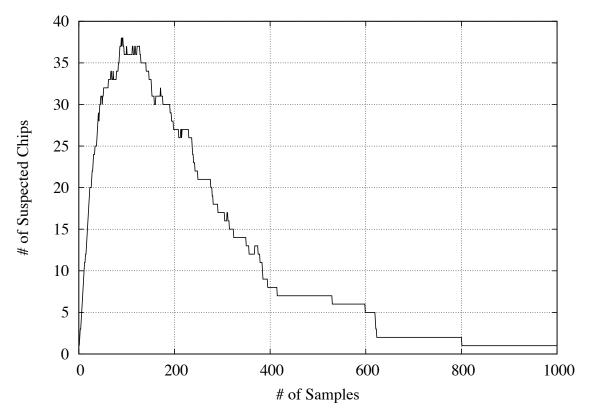

| 2.13 | Number of distinct fingerprints generated from a chip of size $1GB$ based on collected samples of size $10MB$ for our edge detection program. As the number of samples increase, Probable Cause is able |    |

|      | to connect different partial fingerprints together to create a single                                                                                                                                   | 20 |

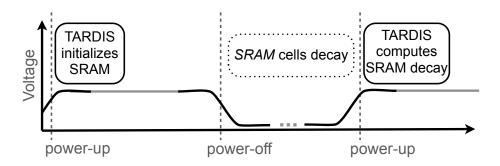

| 3.1  | system-level fingerprint                                                                                                                                                                                | 30 |

| J.1  | have a value of zero in power-up ( <i>computes SRAM decay</i> ). Initially,<br>a portion of SRAM cells are set to one ( <i>initializes SRAM</i> ) and their                                             |    |

|      | values decay during power-off. The dots in the power-off indicate the                                                                                                                                   |    |

|      | arbitrary and unpredictable duration of power-off                                                                                                                                                       | 39 |

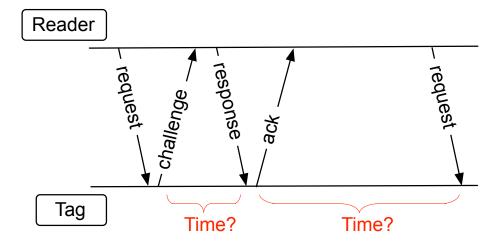

| 3.2  | The tag cannot determine the time between a challenge and a response                                                                                                                                    |    |

|      | or the time between two sessions. The reader could respond to the                                                                                                                                       | 10 |

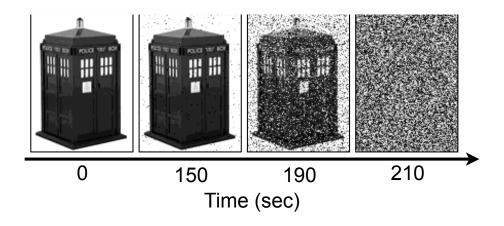

| 3.3  | tag as tardily as it likes or query the tag as quickly as it wants<br>Programs without access to a trustworthy clock can determine time                                                                 | 42 |

| 0.0  | elapsed during a power failure by observing the contents of unini-                                                                                                                                      |    |

|      | tialized SRAM. These bitmap images of the TARDIS [1] represent                                                                                                                                          |    |

|      | four separate trials of storing the bitmap in SRAM, creating an open                                                                                                                                    |    |

|      | circuit across the voltage supply for the specified time at $26^{\circ}C$ , then                                                                                                                        |    |

|      | immediately returning a normal voltage supply and reading unini-                                                                                                                                        |    |

|      | tialized SRAM upon reboot. The architecture of a contactless card                                                                                                                                       |    |

|      | is modeled using a 10 $\mu$ F capacitor and a diode in series with the                                                                                                                                  |    |

|      | MSP430 microcontroller's voltage supply pin. The degree of decay                                                                                                                                        |    |

|      | is a function of the duration of power failure, enabling hourglass-like                                                                                                                                 |    |

|      | timekeeping precision without power. No TARDIS was harmed or                                                                                                                                            |    |

|      | dematerialized in this experiment.                                                                                                                                                                      | 45 |

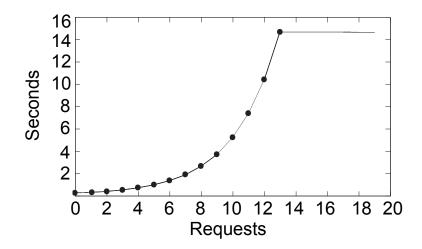

| 3.4  | Measured response time of a 2010-issued French passport [7]. The                                                                                                                                        |    |

|      | passport imposes up to 14 seconds of delay on its responses after                                                                                                                                       |    |

|      | unsuccessful execution. The delay will remain until a correct reading                                                                                                                                   |    |

|      | happens even if the passport were removed from the reader's field for                                                                                                                                   | 10 |

| 25   | a long time                                                                                                                                                                                             | 49 |

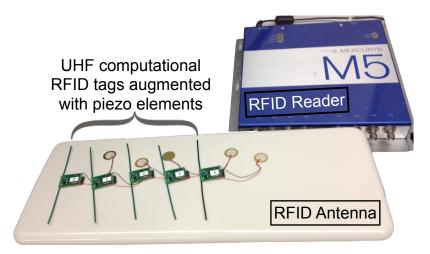

| 3.5  |                                                                                                                                                                                                         | 51 |

| 3.6  | and are remotely powered by a RFID reader (ThingMagic M5 [120]).<br>General circuit used during the experiments. The microcontroller is                                                                 | 01 |

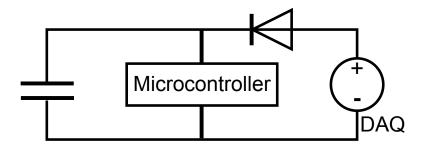

| 0.0  | held in an environmental chamber to ensure consistent temperature                                                                                                                                       |    |

|      | during the tests. The Data Acquisition (DAQ) unit both provides                                                                                                                                         |    |

|      | power to the microcontroller and records the voltage decay                                                                                                                                              | 55 |

|      | - 0 /                                                                                                                                                                                                   |    |

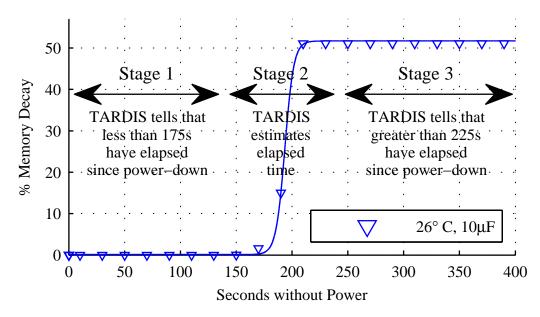

| 3.7  | The TARDIS presents a three-stage response pattern according to                      |     |

|------|--------------------------------------------------------------------------------------|-----|

|      | its amount of decay. Before 175 seconds, the percentage of bits that                 |     |

|      | retain their 1-value across a power-off is 100%. For times exceeding                 |     |

|      | 225 seconds, the TARDIS memory has fully decayed. The decay of                       |     |

|      | memory cells between these two thresholds can provide us with a                      |     |

|      | more accurate measurement of time during that period. This graph                     |     |

|      | presents our results measured on a TI MSP430F2131 with 256 B of                      |     |

| 0.0  | SRAM and a 10 $\mu F$ capacitor at 26°C.                                             | 57  |

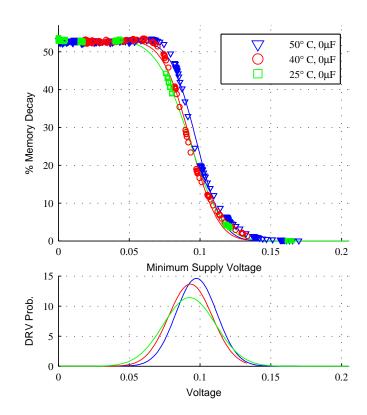

| 3.8  | Regardless of temperature, the amount of decay depends almost                        |     |

|      | entirely on the minimum supply voltage reached during a power-                       |     |

|      | down. The bottom graph shows the 3-parameter DRV probabilities                       |     |

|      | (Equation 3.4) that best predict the observed relationships between                  |     |

|      | decay and minimum supply voltage for each of the three temperatures.                 |     |

|      | The fit lines in the upper graph show the relationships between decay                |     |

|      | and minimum supply voltage that are predicted by these DRV models $(Section 2.0)$    | ۳O  |

| 3.9  | (Section 3.9)                                                                        | 58  |

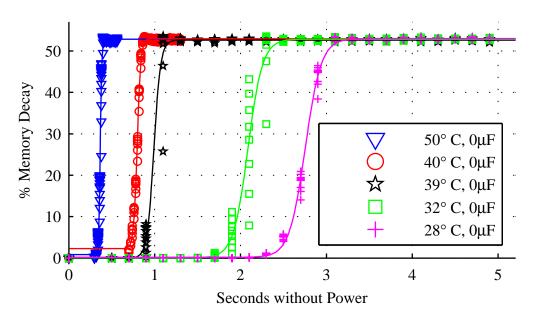

| 5.9  | when no capacitor is used. For any given temperature, the duration                   |     |

|      | of SRAM decay is consistent across trials. Increasing the temperature                |     |

|      | from $28^{\circ}C$ to $50^{\circ}C$ reduces the duration of both Stage 1 and Stage 2 |     |

|      | decay by approximately 80%.                                                          | 59  |

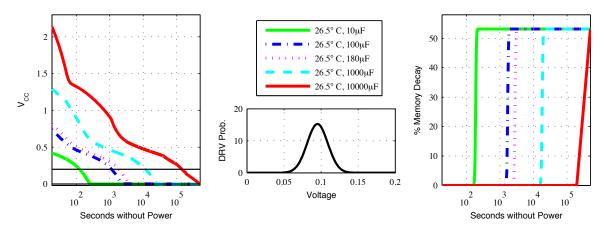

| 3.10 | For five different capacitor values, measured supply voltage traces                  | 00  |

| 0.10 | are combined with a pre-characterized DRV distribution to predict                    |     |

|      | decay as a function of time. The decaying supply voltages after                      |     |

|      | power is turned off are shown at left. The known DRV probabilities                   |     |

|      | (Equation 3.4) for $26.5^{\circ}C$ are shown at center. Equation 3.5 maps            |     |

|      | every supply voltage measurement to a predicted decay, thus creating                 |     |

|      | the memory-decay-vstime plots shown at right. The two horizontal                     |     |

|      | lines in the left image at approximately $150$ and $50$ mV are the voltages          |     |

|      | where the first and last bits of SRAM will respectively decay                        | 60  |

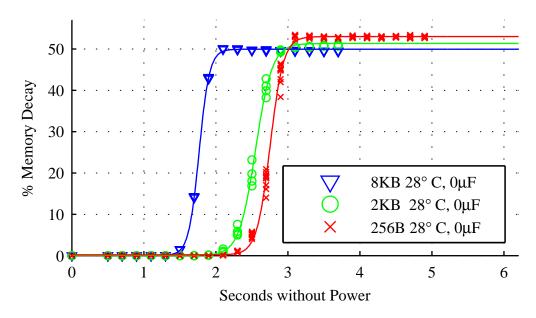

| 3.11 | Different microcontrollers within the TI MSP430 family with differ-                  |     |

|      | ent SRAM sizes exhibit different decay times, but follow the same                    |     |

|      | general trend. The $MSP430F2618$ , $MSP430F169$ , and $MSP430F2131$                  |     |

|      | respectively have 8 KB, 2 KB, and 256 B of SRAM                                      | 62  |

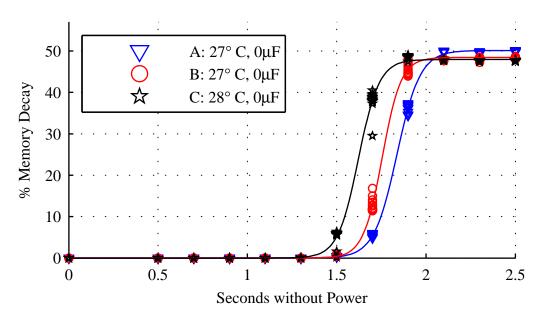

| 3.12 | Decay versus time in 3 different instances of the MSP430F2131 mi-                    |     |

|      | crocontroller at similar temperatures. The durations of Stage 1 and                  |     |

|      | Stage 2 decay match closely across instances                                         | 63  |

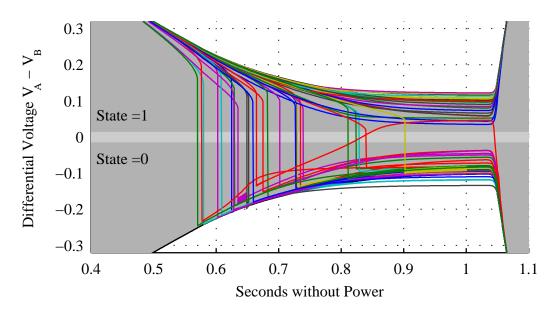

| 3.13 | The differential voltage of SRAM cells during decay. The envelope                    |     |

|      | of $\pm V_{CC}$ is shaded in grey. All cells are in the 1 state when power           |     |

|      | is first turned off. As $V_{CC}$ decays, some cells flip from 1 to 0. The            |     |

|      | cells stabilize when power is restored. The number of zeros after the                |     |

|      | restoration of power is used to estimate the duration of the power                   | ~   |

| 914  | The state holding mention of an CDAM call consists of two energy                     | 64  |

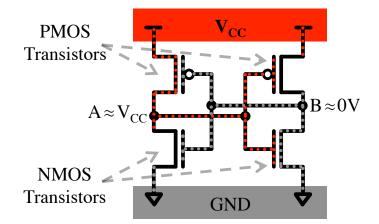

| 3.14 | The state-holding portion of an SRAM cell consists of two cross-                     | C A |

|      | coupled inverters tied to the chip's power and ground nodes. $\ldots$                | 64  |

х

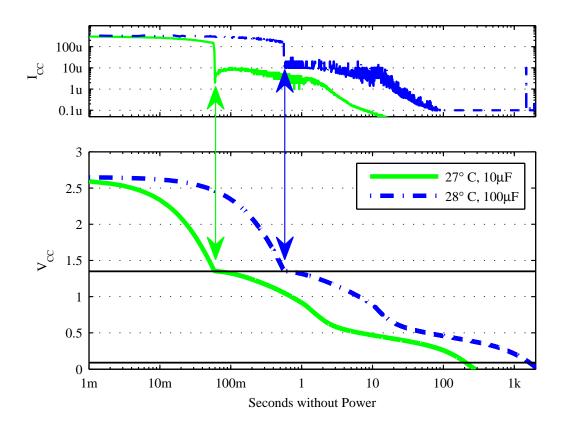

| 3.15 | Supply voltage and current during two power-down events with dif-<br>ferent capacitors. The voltage $V_{CC}$ is measured directly, and the<br>current $I_{CC}$ is calculated per Equation 3.1 using the measured $\frac{dV_{CC}}{dt}$<br>and known capacitor values. The voltage initially decays rapidly due<br>to the high current draw of the microcontroller. When $V_{CC}$ reaches<br>1.40V the microcontroller turns off and $I_{CC}$ drops by several orders<br>of magnitude, leading to a long and slow voltage decay. At the time<br>when $V_{CC}$ crosses the horizontal line at 0.09V, approximately half of<br>all eligible cells will have decayed | 66 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

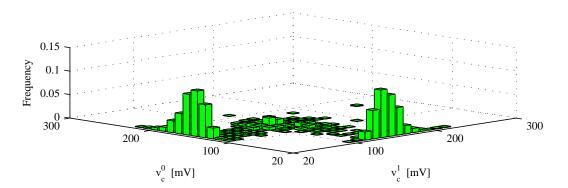

| 4.1  | The joint probability distribution function over all cells of the two<br>variables $(v_c^0 \text{ and } v_c^1)$ comprising a DRV characterization. The distribu-<br>tion is determined experimentally using Algorithm 9, and shows that<br>a large fraction of cells have the minimum possible value of 20mV for<br>either $v^0$ or $v^1$ , but none have the minimum value (or near-minimum<br>values) for both. A cell with a minimum value for $v^0$ or $v^1$ is a cell                                                                                                                                                                                      | 70 |

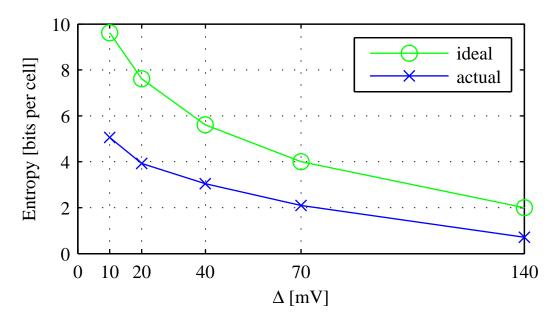

| 4.2  | that retains one written state across all test voltages. $\ldots$ $\ldots$ Sweeping $\Delta$ from 10mV to 140mV shows that a loss of measurement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 76 |

| 4.9  | precision reduces entropy of each cell's DRV characterization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 80 |

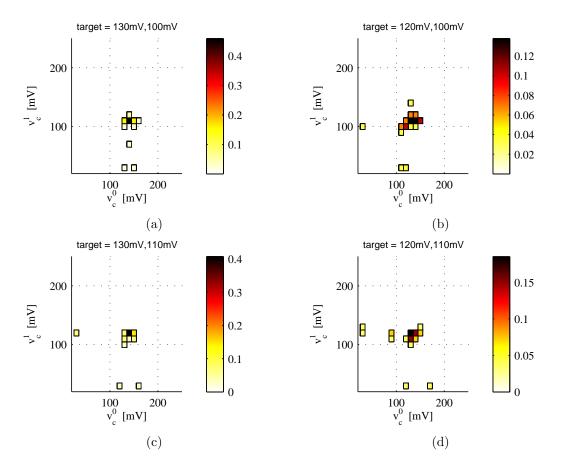

| 4.3  | For each of the 4 most frequently observed weak DRVs (see Ta-<br>ble 4.1(a)), the DRV in a second trial from a cell that produced the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|      | frequently observed DRV in a first trial                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 81 |

| 4.4  | For each of the 4 most frequently observed strong DRVs (see Ta-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

|      | ble. $4.1(b)$ , the DRV in a second trial from a cell that produced the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 00 |

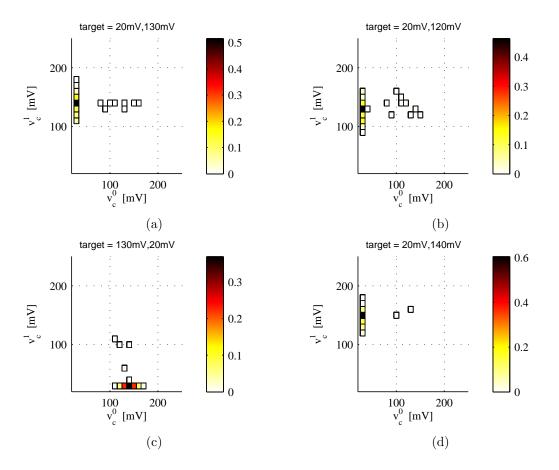

| 4.5  | frequently observed DRV in a first trial                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 82 |

| 1.0  | strongly 0 DRV reliably power-up to state 0, as observed by a mean                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|      | power-up state of 0. The plot at right shows that 95.1% of cells with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|      | strongly 1 DRVs reliably power-up to state 1. The DRV is from a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

|      | single trial of the cell, and the mean power-up state is measured over                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

| 4.0  | 28 power-up trials.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 89 |

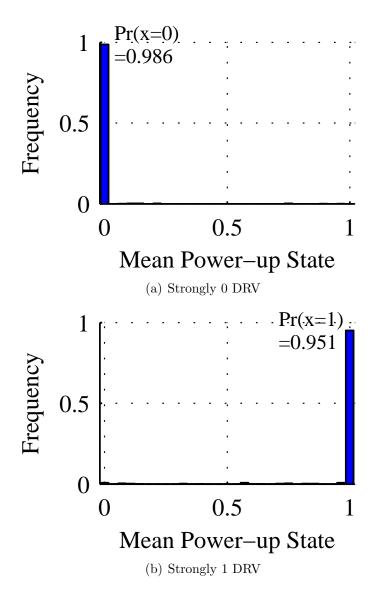

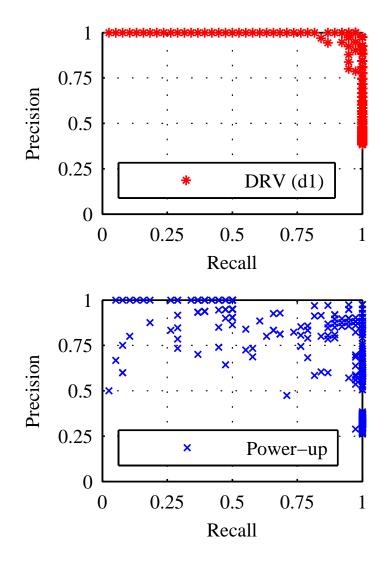

| 4.6  | Within-class and between-class distances of 16-bit fingerprints. The upper plot uses DRV fingerprints with distance metric $d1$ from Eq. 4.3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

|      | The lower plot uses power-up fingerprints with Hamming distance as                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|      | a metric.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 90 |

| 4.7  | Tradeoff points of precision and recall for trials of DRV fingerprints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|      | are generally closer to the ideal result of perfect precision and recall.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 91 |

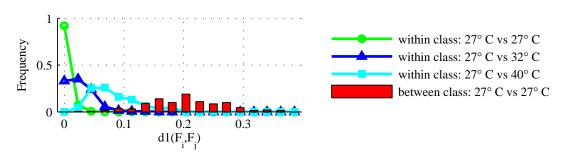

| 4.8  | The line plots show within-class distances when one fingerprint ob-<br>servation is made at $27^{\circ}C$ and the second at $27^{\circ}C$ , $32^{\circ}C$ , or $40^{\circ}C$ ;<br>within-class distances increase with temperature, implying a dimin-<br>ished reliability. The bar plot shows between-class distances of 16-bit<br>fingerprints taken at $27^{\circ}C$ . Because there does not exist a distance<br>threshold that can separate the two classes when temperature is varied,                                                                                                                                                                    |    |

|      | it may be necessary to use larger fingerprints for reliable identification.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 92 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

# LIST OF TABLES

## <u>Table</u>

| 1.1 | Summary of work                                                                                                                               | 2  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | Results for a page of memory                                                                                                                  | 23 |

| 2.2 | Chance of mismatching two pages of memory for different accuracies.                                                                           |    |

|     | Decreasing accuracy causes an exponential increase in fingerprint state                                                                       |    |

|     | space                                                                                                                                         | 28 |

| 3.1 | Practical attacks on intermittently powered devices. These attacks<br>require repeated interactions between the reader and the device. Throt- |    |

|     | tling the reader's attempts to query the device could mitigate the                                                                            |    |

|     | attacks.                                                                                                                                      | 38 |

| 3.2 | Because CPUs of embedded devices generally do not have on-chip                                                                                |    |

|     | DRAM, the TARDIS operates on SRAM. SRAM and DRAM differ                                                                                       |    |

|     | fundamentally in their manufacture, operation, intended use, and                                                                              |    |

|     | state of decay.                                                                                                                               | 41 |

| 3.3 | Overhead of TARDIS INIT and DECAY procedures measured for                                                                                     |    |

|     | TARDIS size of 256 bytes                                                                                                                      | 47 |

| 3.4 | Definition of the terms used to explain the behavior of SRAM decay                                                                            |    |

|     | and the theory behind it.                                                                                                                     | 56 |

| 3.5 | Estimated time in Stage 1 and Stage 2 of the TARDIS increases as                                                                              |    |

|     | capacitor size increases. The experiments are done on a $MSP430F2131$                                                                         |    |

|     | microcontroller at $26.5^{\circ}C$ and an SRAM size of 256 B. Stage 1 is the                                                                  |    |

|     | time after the power failure but before the SRAM decay. Stage $2$                                                                             |    |

|     | represents the duration of SRAM decay.                                                                                                        | 61 |

| 4.1 | The 4 most commonly observed weak and strong DRV characteriza-                                                                                |    |

|     | tions, and the probability of observing each in a randomly selected                                                                           |    |

|     | trial                                                                                                                                         | 79 |

| 4.2 | Probability of different pairwise outcomes when 2 DRV fingerprints are                                                                        |    |

|     | taken from a randomly chosen cell. Over the 5000 samples collected,                                                                           |    |

|     | no cell ever has a DRV that is strongly 1 in one trial and strongly $0$                                                                       |    |

|     | in another, but $5.6\%$ of outcomes have one strong and one weak DRV.                                                                         | 83 |

| Over 300 trials with a population of 240 16-bit fingerprints, DRV                                                                       |                                                                                                                                                                                                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| identification returns the fingerprint that correctly matches the target                                                                |                                                                                                                                                                                                                                                                                                 |

| more reliably than power-up state identification. Matching based on                                                                     |                                                                                                                                                                                                                                                                                                 |

| power-up state more frequently returns a misidentified fingerprint, or                                                                  |                                                                                                                                                                                                                                                                                                 |

| returns multiple fingerprints among which one is the correct match                                                                      |                                                                                                                                                                                                                                                                                                 |

| $(denoted "co-top"). \dots \dots$ | 84                                                                                                                                                                                                                                                                                              |

|                                                                                                                                         | identification returns the fingerprint that correctly matches the target<br>more reliably than power-up state identification. Matching based on<br>power-up state more frequently returns a misidentified fingerprint, or<br>returns multiple fingerprints among which one is the correct match |

## ABSTRACT

Attacking and Defending Emerging Computer Systems Using the Memory Remanence Effect

by

Amir Rahmati

Chair: Atul Prakash

In computer systems, manufacturing variances and hardware effects are typically abstracted away by the software layer. This dissertation explores how these effects, specifically memory remanence, can be used both as an attack vector and a tool to defend emerging computing systems. To achieve this, we show how time-keeping, anonymity, and authenticity can be affected by memory remanence. In terms of attacks, we explore the deanonymizing effect of approximate computing in the context of approximate memory in Probable Cause. We show how data passing through an approximate memory is watermarked with a device specific tag that points the attacker back to the device. In terms of defenses, we first present TARDIS: an approach to provide a notion of time for transiently powered embedded devices without requiring any hardware modification using remanence effect of SRAM. TARDIS allows these devices to keep a coarse-grained notion of time without the need for a running clock. Second, we propose data retention voltage of memory cells as a new type of physical unclonable function that allows for low-cost authentication and counterfeit resistance in computer systems.

## CHAPTER I

## Introduction

Memory remanence refers to the residual data or its traces that remain in memory after it is expected to be lost. In volatile memories where the integrity of the data relies on continuous access to a source of energy and/or refresh operations, memory remanence shows itself as the gradual decay of data after loss of power, or errors that may appear due to reduced input voltage or refresh rate in energy saving mechanism. A prominent example of memory remanence effect on security of computer systems was presented by Halderman et al. [42] where they used effect of memory remanence to extract secret cryptographic keys from DRAM memories.

This thesis focuses on security implications and potentials of memory remanence, exploring how various security primitives can be challenged or obtained using its effects. Table 1.1 provides an overview of this work. First, we look at Approximate Computing as an emerging field that seeks to trade computational accuracy for energy and performance, and show how use of approximation in memory can create a privacy risk by watermarking any data passing through the memory with a signature specific to that device. Second, we tackle the problem of time-keeping in transiently powered embedded devices in TARDIS. We show how limited access to energy makes these devices incapable of performing simple security functionalities such as rate-limiting and time-out and show how this capability can be regained in software by taking

| System             | Type    | Security Primitive | Contribution                                                                       |

|--------------------|---------|--------------------|------------------------------------------------------------------------------------|

| Probable Cause     | Attack  | Anonymity          | Showing that use of Approx-<br>imate Computing creates in-<br>herent privacy risks |

| TARDIS             | Defense | Time               | Providing a notion of time to<br>transiently powered devices                       |

| DRV-Fingerprinting | Defense | Authenticity       | Creating an unforgeable fin-<br>gerprint using data retention<br>voltage of memory |

Table 1.1: Summary of work

advantage of memory remanence in hardware.

In this dissertation, we take a principled approach to examine the effects of memory remanence and build attacks and security mechanisms that take advantage of its effects. We build open-source experimental platforms to implement attacks and security mechanisms. We use these platforms to evaluate these systems and to examine their robustness against physical and environmental factors. Finally, we prototype these systems in real-life scenarios to showcase their effectiveness.

### 1.1 Contributions of This Dissertation

### 1.1.1 Probable Cause: Deanonymizing Effect of Approximate Memory

Approximate computing research seeks to trade the accuracy of computation for increases in performance or reductions in power consumption. The observation driving approximate computing is that many applications tolerate small amounts of error which allows for an opportunistic relaxation of guard bands (*e.g.*, clock rate and voltage). Besides affecting performance and power, reducing guard bands exposes analog properties of traditionally digital components. For DRAM, one analog property exposed by approximation is the variability of memory cell decay times.

In Probable Cause, we show how the differing cell decay times of approximate

DRAM creates an error pattern that serves as a system identifying fingerprint. To validate this observation, we build an approximate memory platform and perform experiments that show that the fingerprint due to approximation is device dependent and resilient to changes in environment and level of approximation. To identify a DRAM chip given an approximate output, we develop a distance metric that yields a two-orders-of-magnitude difference in the distance between approximate results produced by the same DRAM chip and those produced by other DRAM chips. We use these results to create a mathematical model of approximate DRAM that we leverage to explore the end-to-end deanonymizing effects of approximate memory using a commodity system running an image manipulation program. The results from our experiment show that given less than 100 approximate outputs, the fingerprint for an approximate DRAM begins to converge to a single, machine identifying fingerprint.

# 1.1.2 TARDIS: Providing a Notion of Time to Transiently Powered Devices

Lack of a locally trustworthy clock makes security protocols challenging to implement on batteryless embedded devices such as contact smartcards, contactless smartcards, and RFID tags. A device that knows how much time has elapsed between queries from an untrusted reader can better protect against attacks that depend on the existence of a rate-unlimited encryption oracle.

The TARDIS (Time and Remanence Decay in SRAM) helps the system locally maintain a sense of time elapsed without power and without special-purpose hardware. The TARDIS software computes the expiration state of a timer by analyzing the decay of existing on-chip SRAM. The TARDIS enables coarse-grained, hourglass-like timers such that cryptographic software can more deliberately decide how to throttle its response rate. Our experiments demonstrate that the TARDIS can measure time ranging from seconds to several hours depending on hardware parameters. We address key challenges in implementing a practical TARDIS include compensating for temperature and handling variation across hardware.

Our contributions are (1) the algorithmic building blocks for computing elapsed time from SRAM decay; (2) characterizing TARDIS behavior under different temperatures, capacitors, SRAM sizes, and chips; and (3) three proof-of-concept implementations that use the TARDIS to enable privacy-preserving RFID tags, to deter double swiping of contactless credit cards, and to increase the difficulty of brute-force attacks against e-passports.

# 1.1.3 DRV-Fingerprinting: Using Data Retention Voltage for Chip Identification

Physical unclonable functions (PUFs) produce outputs that are a function of minute random physical variations. Promoted for low-cost authentication and resistance to counterfeiting, many varieties of PUFs have been used to enhance the security and privacy of embedded systems. To different extents, applications for both identification and authentication require a PUF to produce a consistent output over time. As the sensing of minute variations is a fundamentally noisy process, much effort is spent on error correction of PUF outputs. We propose a new variant of PUF that uses well-understood properties of common memory cells as a fingerprint. Our method of fingerprinting SRAM cells by their data retention voltage improves the success rate of identification by 28% over fingerprints based on power-up state.

## CHAPTER II

# Probable Cause: Deanonymizing Effect of Approximate Memory

## 2.1 Introduction

Secure system designers tend to focus on the anonymity of communication [86] and take for granted the hardware used to generate the data communicated. Attribution of data is usually done through communication meta-data [23]. While the use of encryption secures the communication against eavesdroppers, it is unable to hide the occurrence of communication. Anonymity systems such as Tor [26] try to provide this guarantee over the Internet. Even when software and communication channels are designed to preserve anonymity of users, devices can be deanonymized using intrusive measures such as espionage tools and Trojans [115] or non-intrusively using unique characteristics of analog hardware such as RF fingerprinting [17, 87], clock skew [57], or camera sensor noise [71]. The anonymity of digital computation has not been traditionally a concern since, in general, computer systems are deterministic machines that yield identical results to identical inputs.

The assumption of anonymous computation must be reconsidered with the emergence of approximate computing. The goal of approximate computing is to provide significant performance improvements and/or energy savings by sacrificing the accu-

Figure 2.1: Probable Cause creates a fingerprint of an approximate DRAM system by collecting approximate outputs and stitching together error patterns in those outputs to form a fingerprint for the memory. Attackers can then use this memory fingerprint to identify other approximate outputs as belonging to the system.

racy of computation or storage. In many cases, the error pattern due to approximation depends on hardware variations locked-in at manufacturing time. The dependency of computation result on hardware properties creates an opportunity for an attacker to deanonymize systems that produce approximate results.

Approximate computing adds accuracy as a third dimension to the conventional energy/performance trade-off. Many applications, such as computer vision, machine learning, and sensor networks, are naturally imprecise and thus accept a range of results, so expending extra time and energy to calculate an exact results is of no advantage. For example, any application that uses floating point numbers already accepts some inaccuracy.

As one of the main components of an approximate system, many works consider the trade off between accuracy and energy saving in Dynamic Random Access Memory (DRAM). Energy saving schemes targeted at DRAM work by lowering the input voltage [24] or by decreasing the refresh rate [67, 68, 125]. These techniques are a key component in future approximate computing systems, especially those that tolerate limited errors in data [28].

While much of the previous work has examined approximate DRAM's impact on correctness, performance, and energy, none of the existing approximate DRAM systems consider their impact on privacy. To this end, we introduce Probable Cause, to our knowledge, the first paper that explores the security implications of approximate DRAM. Probable Cause is an approach to uniquely identify approximate computing systems based on the error pattern imprinted in approximate outputs. Figure 2.1 provides an overview of how Probable Cause works. The insight driving Probable Cause is that the error pattern imprinted on data reveals the location of the most volatile cells in an approximate memory. Additionally, this volatility is chip-specific and due mainly to process variations locked-in during manufacturing.

To demonstrate the real-world implications of our observation, we implement Probable Cause. Probable Cause consists of an approximate memory system and set of approximate result classification algorithms. We show that Probable Cause reliably deanonymizes approximate results, even with changes in temperature and level of approximation. Additionally, we show that it is possible to dynamically construct a fingerprint for a DRAM by collecting arbitrary approximate results and stitching their individual fingerprints together to form a whole-memory fingerprint.

Our contributions are,

- We present the first work to highlight the privacy implications of approximate DRAM.

- We empirically evaluate the feasibility of our approach by deanonymizing DRAM devices based only on their approximate results.

- We present a mathematical model to quantify the end-to-end information leakage

of approximate DRAM, showing how many approximate results an attacker must gather to reliably identify a system.

### 2.2 Background

Dynamic Random Access Memory (DRAM) is a type of volatile memory that stores values by holding charge in a capacitor. Figure 2.2 presents a simplified DRAM structure. The storage capacitor in each DRAM cell has a default/uncharged state and a charged state. The uncharged state of a cell corresponds to either a logical '0' or a logical '1', depending on the DRAM mapping. For each cell, the logical value corresponding to an uncharged capacitor is denoted as the default value. Generally, all cells in the same row have the same default value, and the default value alternates every few rows. Writing a value opposite of the default value charges a cell's storage capacitor. The capacitor then begins to lose its charge. Eventually the capacitor voltage will drop below a detection threshold and return the cell to its default value. To prevent data loss in charged cells, DRAM must perform regular refresh operations. The JEDEC standard [53] specifies a refresh period of 64ms for operating temperatures below 85°C. Refreshes have row granularity (due to the architecture of DRAM). At the hardware level, a refresh operation is a read followed by a write. The write fully charges any data storage capacitors not in the default value.

DRAM cells decay at different rates, mainly due to their manufacturing variations. The distribution of how quickly DRAM cells decay follows a Gaussian distribution [90]. There are two types of manufacturing variation that influence the probability of state loss between refresh: (1) variation in the capacitance of the DRAM cell and (2) variation in the leakage current through the access transistor that drains the capacitor. It is possible that some variation in capacitance is mask-dependent, thus replicated across wafers produced in the same fabrication process. On the other hand, the variation in the leakage current is not mask-dependent, because it is caused by

Figure 2.2: A DRAM cell has a default low value that can be changed by charging the capacitor. DRAM cells need to be constantly refreshed for the value to hold, otherwise capacitor leakage slowly reverts the cell to its default value. All DRAM operations are done at row granularity.

threshold voltage variations due to random dopant fluctuations in the channel of the access transistor. Thus, we expect leakage current to be the dominant factor in DRAM cell retention time, *i.e.*, essentially mask independent.

In traditional/exact computing models, a DRAM requires frequent refreshes to prevent decay of the most volatile cells in the most extreme environmental conditions. This results in large overheads because, while some cells decay in less than a tenth of a second, the majority of the cells hold their value for tens of seconds. Additionally, most systems are not running in extreme environments.

Approximate computing systems take advantage of this opportunity either by lowering the supply voltage of memory or by decreasing the refresh rate. Both of these methods result in energy savings but cause errors in data. Given that the errors are mainly due to capacitor leakage, the ordering of cells that lose their charge is repeatable. This observation drives Probable Cause. In the remainder of this chapter, we experimentally show that these orderings are unique, stable given environmental changes, and stable given the amount of error.

## 2.3 Threat Model

Probable Cause's threat model assumes that a user has a system with approximate memory. The user wishes to publish data (e.g., post a picture on a forum) created on an approximate system while preserving his or her anonymity. We assume that the user takes all known precautions, such as removing identifying meta-data from the files they post and that they publish data using an anonymity-preserving communication channel (e.g., The Onion Router (Tor) [26]).

A key aspect of the threat model is a resource imbalance between the attacker and the victim: it assumes a sophisticated attacker with abundant resources (*i.e.*, a nation state) that seeks to identify a relatively small set of users (*e.g.*, a dissident) using only those users' approximate outputs. Figure 2.3 depicts two attack scenarios explored in this chapter:

- (a) The attacker inserts themselves in the supply chain between the manufacturer and the end user. This encompasses the attacker intercepting complete computer systems or just the DRAM modules themselves. The attacker fingerprints devices completely before they reach the user, thus Probable Cause can deanonymize any public approximate result generated by the system.

- (b) The attacker creates a database of all observed approximate outputs. The error patterns in the outputs are stitched together to form whole-system fingerprints. In this scenario, we assume that the attacker has access to the public data and can guess the positions of error in the approximate outputs. While this scenario is less intrusive, it requires collecting many approximate outputs from a system before Probable Cause is able to construct a reliable system-level fingerprint.

Figure 2.3: Probable Cause tackles two attack scenarios: (a) the attacker intercepts and fingerprints the entire memory (as a part of a system or a standalone module) in the supply chain and (b) the attacker captures approximate outputs from a deployed system to create a fingerprint.

Both the supply-chain attack and eavesdropping attack are feasible given real-world precedents [38].

### 2.4 Design of Probable Cause

The two scenarios described in Section 2.3 pose very different attack vectors for the adversary to deanonymize data generated by an approximate memory. Attacking the supply chain is the easier of the two attacks to implement. Giving the adversary physical access to the approximate memory guarantees complete and accurate fingerprinting of the memory. Section 2.7.1 covers how data only a few memory pages in length can produce a fingerprint powerful enough to differentiate outputs from one DRAM chip from another. The second attack scenario is more challenging since the attacker cannot control what data the victim gives him. This section shows that even with such limitations, Probable Cause still deanonymizes users based solely on user-provided approximate outputs.

For the post-deployment attack scenario, we assume the attacker has access to

Figure 2.4: Probable Cause constructs the whole-memory fingerprint by stitching together fingerprints of overlapping approximate outputs. Pages of the same color are the same page and are matched by Probable Cause using page fingerprints.

approximate outputs from the device, but does not know which page<sup>1</sup> of memory it emanates from. To formalize this, assume that we have approximate outputs  $D_1, D_2, ..., D_n$ . Without loss of generality, we assume that these pages are stored in physical memory pages  $s_1, s_2, ..., s_n$  and have length of  $l_1, l_2, ..., l_n$  consecutive pages. Note that this is not a strong assumption as even operating systems that utilize Address Space Layout Randomization (ASLR) [106] do *not* randomize the location of the pages that make up a file due to the added management overhead.

To create a holistic picture of memory, Probable Cause treats each output as a piece of a puzzle that it puts together to create a fingerprint of the entire memory. Figure 2.4 depicts how this process works: initially, Probable Cause creates a fingerprint for every page of data that it sees. Therefore, each approximate output will result in a contiguous series of page-size fingerprints  $FP_1, FP_2, ..., FP_n$  with length of  $l_1, l_2, ..., l_n$ pages, respectively. We will explain the process of fingerprinting in Section 2.5.2. Next Probable Cause tries to stitch these page-size fingerprints together into a system-level fingerprint by searching for overlap among the series of connected page fingerprints. This algorithm is explained in detail in Section 2.5.3. If the page fingerprints of two approximate outputs match, then there is a range of physical memory pages that held both outputs. Probable Cause uses the page fingerprints outside the overlap region

<sup>&</sup>lt;sup>1</sup>Our analysis focuses on 4 KB chunks of memory—called a page, because that is the smallest unit of contiguous memory that operating systems manage. Modern operating systems also use larger page sizes, which only makes our analysis easier.

to create a combined system-level fingerprint that encompasses the page fingerprints of each output. As the number of outputs increase, more fingerprints are stitched together. In Section 2.7.6 we show how, with large enough data and enough overlap, it is possible to create a system-level fingerprint comparable to the supply chain attack. In cases where the approximate outputs were *not* stored in any of the same physical memory pages, Probable Cause must assume that the outputs come from different systems.

Probable Cause stores system-level fingerprints in a database equal to the size of the fingerprinted region of memory. Although we do not imagine storage to be an issue for powerful attackers such as government agencies or Advanced Persistent Threats (APTs), it is possible to reduce the storage requirement by only tracking the fast decaying bits of memory (approximately, 1% of the bits in a memory).

### 2.5 Mechanics of Probable Cause

Figure 2.5: Three identical images after storage in approximate memory. Image (c) is stored in a different chip than (a) and (b). Simple visual inspection reveals similar patterns of errors in results coming from the same chip.

Probable Cause's goal is to identify the origin of approximate data based on the error pattern imprinted by approximate DRAM. Figure 2.5 presents three example outputs of two approximate DRAMs. For this example, a  $200 \times 154$  pixel black and white image is stored in two different DRAM chips refreshed at a rate that yields 1%

**Algorithm 1** Characterization Algorithm: Creates a fingerprint for a DRAM chip based on the errors from several approximate results.

CHARACTERIZE(approx[#ofResults][size], exact[size])

error with worst-case data. Figure 2.5.a and Figure 2.5.b show the image produced by the same chip, but at different temperatures, while Figure 2.5.c shows the output from a second chip.

Even from visual observation, it is possible to distinguish the results coming from a different chip as there are many similarities in the error patterns in Figures 2.5.a and 2.5.b, but no real similarity to Figure 2.5.c. We highlight regions with notable similarities and differences to ease the comparison.