## **Cross-point Circuits for**

# **Computation, Interconnects, Security and Storage**

by

Supreet Jeloka

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in the University of Michigan 2017

Doctoral Committee:

Professor David T. Blaauw, Chair Professor Jerome P. Lynch Professor Trevor N. Mudge Professor Dennis M. Sylvester To my family and friends

# **TABLE OF CONTENTS**

|                 | 5                                             |   |

|-----------------|-----------------------------------------------|---|

|                 | luction                                       |   |

|                 | e systems                                     |   |

| 1.2 Mobile sy   | stems with performance and energy constraints | 7 |

|                 | ns                                            |   |

| 1.4 Thesis or   | ganization                                    |   |

| CHAPTER 2 Hi-Ri | se: A high-radix switch for 3D integration    |   |

| 2.1 Introducti  | on                                            |   |

| 2.2 Backgrou    | nd: 2D switch                                 |   |

| 2.2.1           | The 2D swizzle-switch                         |   |

| 2.2.2           | Baseline 3D switch: A folded 2D switch        |   |

| 2.3 Hi-Rise 3   | D switch architecture: Datapath & arbitration |   |

| 2.3.1           | 3D switch datapath                            |   |

| 2.3.2           | 3D switch arbitration                         |   |

| 2.4 Implemen    | itation                                       |   |

| 2.4.1           | Basic cross-point design                      |   |

| 2.4.2           | Arbitration specific cross-point design       |   |

| 2.4.3           | Clocking of Hi-Rise switch                    |   |

| 2.4.4           | Physical implementation                       |   |

| 2.5 Methodol    | ogy                                           |   |

| 2.6 Results     |                                               |   |

| 2.6.1           | Analysis of 3D switch datapath parameters     |   |

| 2.6.2           | Analysis of 3D switch arbitration schemes     |   |

| 2.6.3           | TSV technology parameters                     |   |

| 2.6.4           | Application results                           |   |

| 2.6.5           | Discussion                                    |   |

| 2.7 Related w   | ork                                           |   |

| 2.8 Conclusio                                                                                                                                                                                                  | n                                                                                                                                                                                                                                   |                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| <b>CHAPTER 3</b> Config                                                                                                                                                                                        | gurable memory (TCAM/ BCAM / SRAM / logic-in-mem                                                                                                                                                                                    | ory) 54                                                                                                 |

| 3.1 Introducti                                                                                                                                                                                                 | on                                                                                                                                                                                                                                  |                                                                                                         |

| 3.2 Conventio                                                                                                                                                                                                  | onal CAM design                                                                                                                                                                                                                     | 55                                                                                                      |

| 3.3 Overview                                                                                                                                                                                                   | of proposed configurable memory circuit                                                                                                                                                                                             |                                                                                                         |

| 3.4 Configura                                                                                                                                                                                                  | ble memory: CAM circuit implementation                                                                                                                                                                                              | 60                                                                                                      |

| 3.4.1                                                                                                                                                                                                          | BCAM search operation                                                                                                                                                                                                               | 61                                                                                                      |

| 3.4.2                                                                                                                                                                                                          | Reconfigurable sense amplifier design                                                                                                                                                                                               |                                                                                                         |

| 3.4.3                                                                                                                                                                                                          | BCAM write operation                                                                                                                                                                                                                | 64                                                                                                      |

| 3.4.4                                                                                                                                                                                                          | BCAM search robustness                                                                                                                                                                                                              |                                                                                                         |

| 3.4.5                                                                                                                                                                                                          | TCAM mode operation                                                                                                                                                                                                                 |                                                                                                         |

| 3.5 SRAM m                                                                                                                                                                                                     | ode and logic in memory                                                                                                                                                                                                             | 71                                                                                                      |

| 3.5.1                                                                                                                                                                                                          | SRAM mode operation                                                                                                                                                                                                                 | 71                                                                                                      |

| 3.5.2                                                                                                                                                                                                          | Logic operations in memory                                                                                                                                                                                                          |                                                                                                         |

| 3.6 Test harns                                                                                                                                                                                                 | ess                                                                                                                                                                                                                                 |                                                                                                         |

| 3.7 Measured                                                                                                                                                                                                   | results                                                                                                                                                                                                                             | 77                                                                                                      |

| 3.8 Conclusio                                                                                                                                                                                                  | n                                                                                                                                                                                                                                   | 85                                                                                                      |

| 5.6 Conclusio                                                                                                                                                                                                  |                                                                                                                                                                                                                                     |                                                                                                         |

|                                                                                                                                                                                                                | nce dependent PUF                                                                                                                                                                                                                   |                                                                                                         |

| CHAPTER 4 Seque                                                                                                                                                                                                |                                                                                                                                                                                                                                     |                                                                                                         |

| <b>CHAPTER 4 Seque</b><br>4.1 Introducti                                                                                                                                                                       | nce dependent PUF                                                                                                                                                                                                                   | <b> 86</b><br>86                                                                                        |

| CHAPTER 4 Seque<br>4.1 Introducti<br>4.1.1                                                                                                                                                                     | nce dependent PUF                                                                                                                                                                                                                   | <b> 86</b><br>86<br>86                                                                                  |

| CHAPTER 4 Seque<br>4.1 Introducti<br>4.1.1<br>4.2 Proposed                                                                                                                                                     | nce dependent PUF<br>on<br>PUF concept                                                                                                                                                                                              | <b></b>                                                                                                 |

| CHAPTER 4 Seque<br>4.1 Introducti<br>4.1.1<br>4.2 Proposed<br>4.3 Measured                                                                                                                                     | nce dependent PUF<br>on<br>PUF concept<br>PUF design                                                                                                                                                                                | <b>86</b><br>86<br>86<br>86<br>87<br>92                                                                 |

| CHAPTER 4 Seque<br>4.1 Introducti<br>4.1.1<br>4.2 Proposed<br>4.3 Measured<br>4.4 Conclusio                                                                                                                    | nce dependent PUF<br>on<br>PUF concept<br>PUF design<br>results                                                                                                                                                                     | <b>86</b><br>86<br>86<br>87<br>92<br>96                                                                 |

| CHAPTER 4 Seque<br>4.1 Introducti<br>4.1.1<br>4.2 Proposed<br>4.3 Measured<br>4.4 Conclusion<br>CHAPTER 5 Low p                                                                                                | nce dependent PUF<br>on<br>PUF concept<br>PUF design<br>results<br>n                                                                                                                                                                | 86<br>86<br>86<br>87<br>92<br>96<br><b>97</b>                                                           |

| CHAPTER 4 Seque<br>4.1 Introducti<br>4.1.1<br>4.2 Proposed<br>4.3 Measured<br>4.4 Conclusion<br>CHAPTER 5 Low p<br>5.1 Introducti                                                                              | nce dependent PUF<br>on<br>PUF concept<br>PUF design<br>results<br>on<br>ower SONOS flash memory                                                                                                                                    | 86<br>86<br>86<br>87<br>92<br>92<br>96<br>97                                                            |

| CHAPTER 4 Seque<br>4.1 Introducti<br>4.1.1<br>4.2 Proposed<br>4.3 Measured<br>4.4 Conclusion<br>CHAPTER 5 Low p<br>5.1 Introducti                                                                              | nce dependent PUF<br>on<br>PUF concept<br>PUF design<br>results<br>on<br>ower SONOS flash memory<br>on                                                                                                                              | <b></b>                                                                                                 |

| CHAPTER 4 Seque<br>4.1 Introducti<br>4.1.1<br>4.2 Proposed<br>4.3 Measured<br>4.4 Conclusion<br>CHAPTER 5 Low p<br>5.1 Introducti<br>5.2 Proposed                                                              | nce dependent PUF<br>on<br>PUF concept<br>PUF design<br>results<br>on<br>ower SONOS flash memory<br>SONOS design                                                                                                                    | <b>86</b><br>86<br>86<br>87<br>92<br>92<br>96<br><b>97</b><br>97<br>98<br>98                            |

| CHAPTER 4 Seque<br>4.1 Introducti<br>4.1.1<br>4.2 Proposed<br>4.3 Measured<br>4.4 Conclusion<br>CHAPTER 5 Low p<br>5.1 Introducti<br>5.2 Proposed<br>5.2.1                                                     | nce dependent PUF<br>on                                                                                                                                                                                                             | <b>86</b><br>86<br>86<br>87<br>92<br>92<br>96<br><b>97</b><br>97<br>97<br>98<br>98<br>98<br>100         |

| CHAPTER 4 Seque<br>4.1 Introducti<br>4.1.1<br>4.2 Proposed<br>4.3 Measured<br>4.4 Conclusio<br>CHAPTER 5 Low p<br>5.1 Introducti<br>5.2 Proposed<br>5.2.1<br>5.2.2                                             | nce dependent PUF<br>on                                                                                                                                                                                                             | <b>86</b><br>86<br>86<br>87<br>92<br>92<br>96<br><b>97</b><br>97<br>97<br>98<br>98<br>100<br>101        |

| CHAPTER 4 Seque<br>4.1 Introducti<br>4.1.1<br>4.2 Proposed<br>4.3 Measured<br>4.4 Conclusio<br>CHAPTER 5 Low p<br>5.1 Introducti<br>5.2 Proposed<br>5.2.1<br>5.2.2<br>5.2.3                                    | nce dependent PUF<br>on<br>PUF concept<br>PUF design<br>results<br>on<br>ower SONOS flash memory<br>on<br>SONOS design<br>Overview of proposed design<br>Ultra-wide program<br>Transition pump: Charge sharing and charge recycling | <b>86</b><br>86<br>86<br>87<br>92<br>92<br>96<br><b>97</b><br>97<br>98<br>98<br>98<br>100<br>101<br>103 |

| CHAPTER 4 Seque<br>4.1 Introducti<br>4.1.1<br>4.2 Proposed<br>4.3 Measured<br>4.4 Conclusion<br>CHAPTER 5 Low p<br>5.1 Introducti<br>5.2 Proposed<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5                 | nce dependent PUF                                                                                                                                                                                                                   | 86      86      86      87      92      96      97      97      98      100      101      103      106  |

| CHAPTER 4 Seque<br>4.1 Introducti<br>4.1.1<br>4.2 Proposed<br>4.3 Measured<br>4.4 Conclusion<br>CHAPTER 5 Low F<br>5.1 Introducti<br>5.2 Proposed<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.3 Measured | nce dependent PUF<br>on<br>PUF concept<br>PUF design<br>results                                                                                                                                                                     | 86      86      86      87      92      96      97      97      98      100      101      103      108  |

| 6.1 Introducti         | on                                             |     |

|------------------------|------------------------------------------------|-----|

| 6.1.1                  | FRAM concept                                   |     |

| 6.2 Convention         | onal FRAM design                               |     |

| 6.3 Proposed           | FRAM adiabatic design                          |     |

| 6.3.1                  | PU/PD signal generation: Continuous comparator |     |

| 6.3.2                  | Reconfigurable to 2T-2C cell                   |     |

| 6.3.3                  | Other peripherals                              | 119 |

| 6.3.3                  | Simulation results                             |     |

| 6.4 Conclusio          | on                                             | 122 |

| <b>CHAPTER 7 Concl</b> | usion and future directions                    |     |

| 7.1 Contribut          | ions of this work                              | 123 |

| 7.2 Future din         | rections                                       |     |

| 7.3 Related p          | ublications                                    | 127 |

| BIBLIOGRAPHY.          |                                                |     |

# **LIST OF FIGURES**

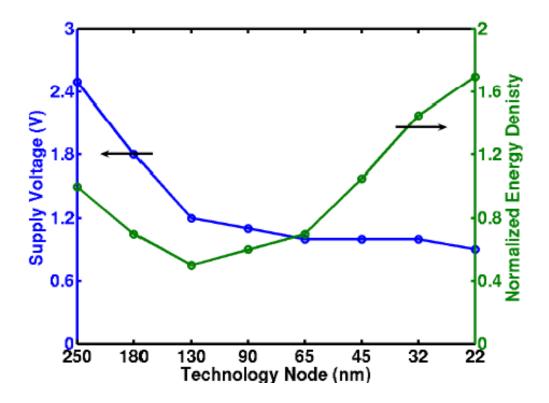

| Figure 1.1 Energy density and supply voltage scaling with technology node                  | 2    |

|--------------------------------------------------------------------------------------------|------|

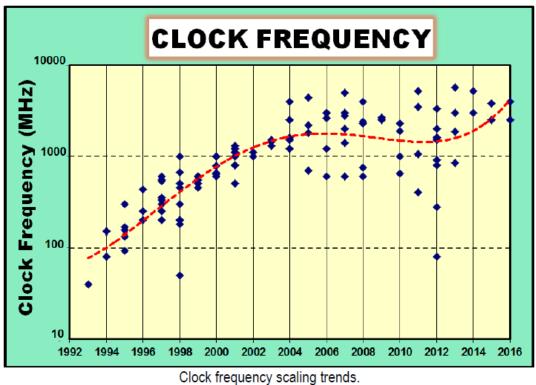

| Figure 1.2 Clock frequency trends                                                          |      |

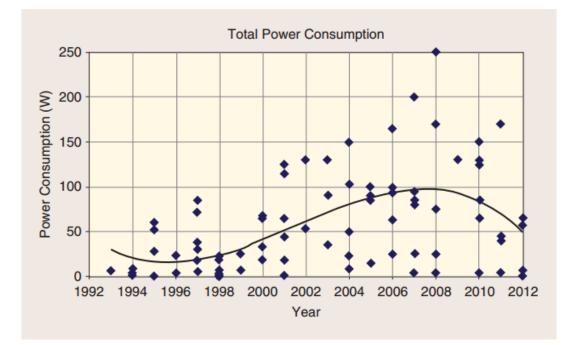

| Figure 1.3 Total power consumption trend                                                   | 3    |

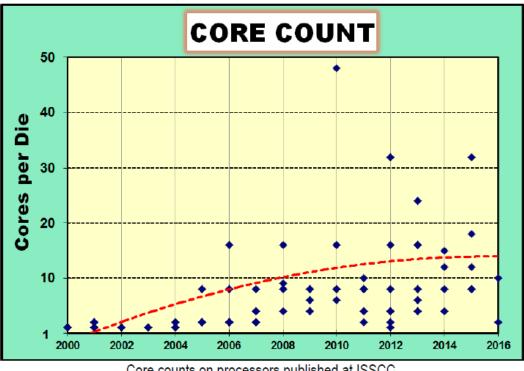

| Figure 1.4 Core count trends                                                               | 4    |

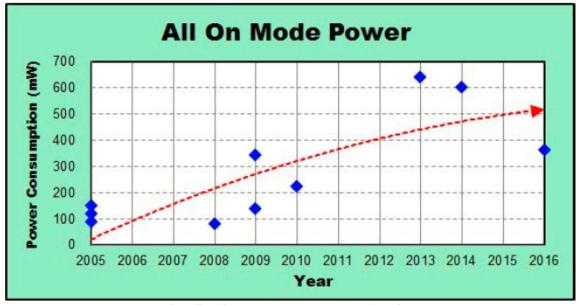

| Figure 1.5 All-on mode power for application processors                                    | 5    |

| Figure 1.6 Processor dynamic energy.                                                       | 8    |

| Figure 2.1 A 64-radix 3D folded switch                                                     | 19   |

| Figure 2.2 Conceptual view of <i>Hi-Rise</i> switch                                        | 20   |

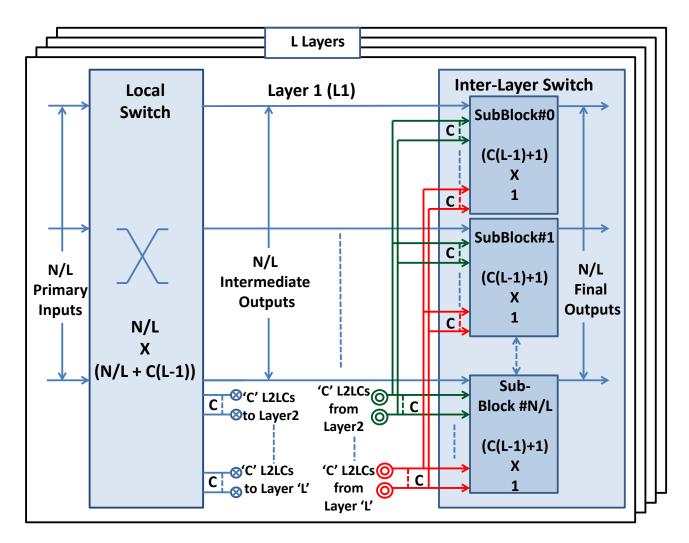

| Figure 2.3 One Layer of a generic NxN L-layered Hi-Rise with Channel Multiplicity of 'c    | ?    |

|                                                                                            |      |

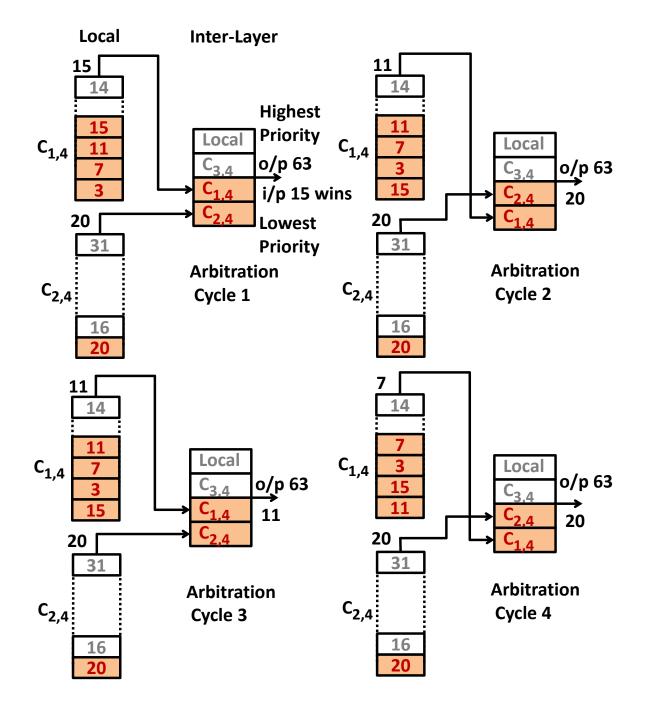

| Figure 2.4 Baseline Layer-to-Layer (L-2-L LRG) example                                     |      |

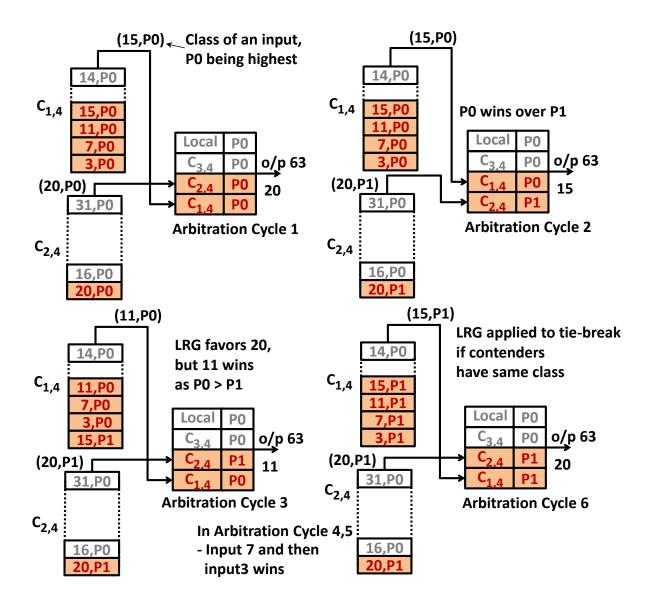

| Figure 2.5 Class-based Least Recently Granted (CLRG) arbitration example.                  | 30   |

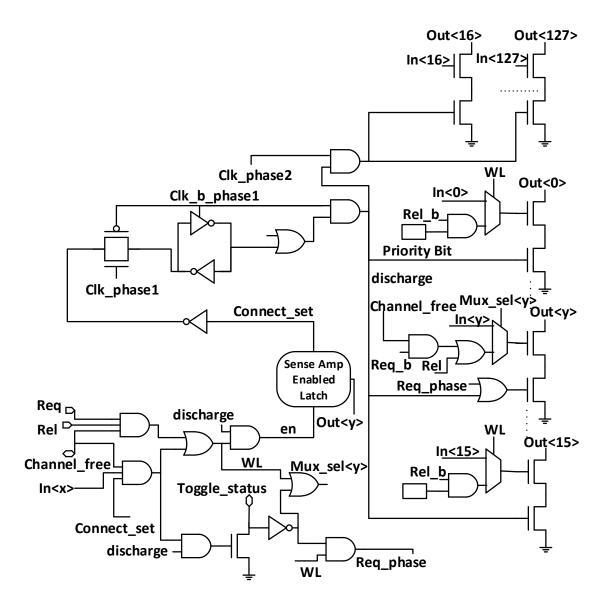

| Figure 2.6 Circuit schematic of local intermediate output cross-point                      |      |

| Figure 2.7 Conceptual view of a cross-point at inter-layer sub-block for CLRG arbitration  | . 33 |

| Figure 2.8 Phase-wise clocking of <i>Hi-Rise</i> switch.                                   |      |

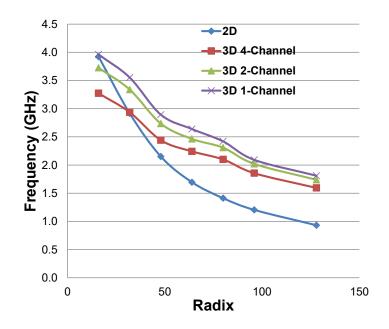

| Figure 2.9 Hi-Rise switch frequency vs radix                                               | 38   |

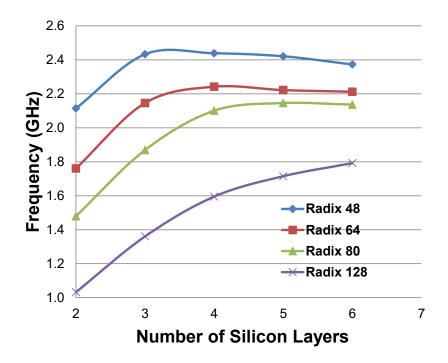

| Figure 2.10 Frequency vs number of silicon layers stacked                                  |      |

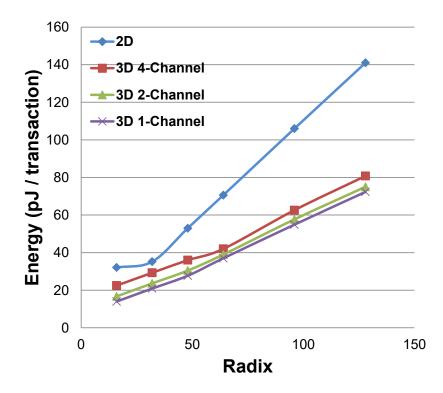

| Figure 2.11 Energy per transaction (128-bit) for 2D and 3D switch                          | 39   |

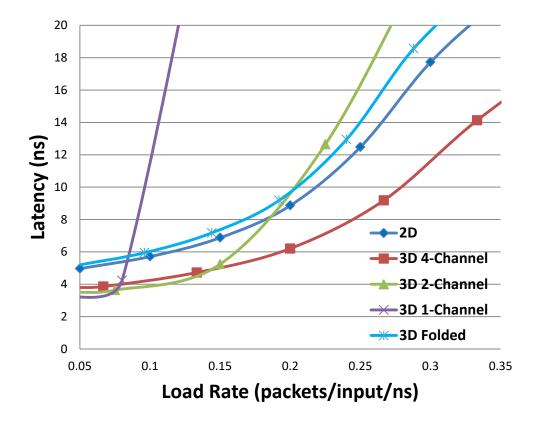

| Figure 2.12 Latency of 2D and 3D multi-channel configurations for UR traffic               |      |

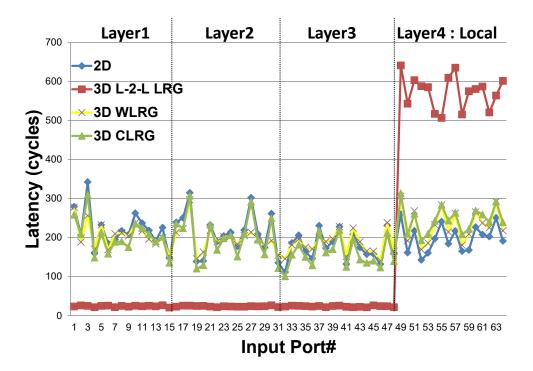

| Figure 2.13 Latency of each input for hotspot traffic                                      | 45   |

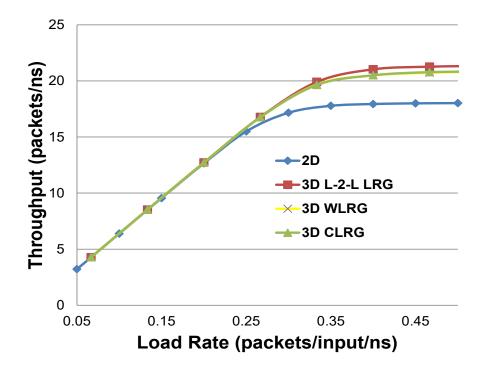

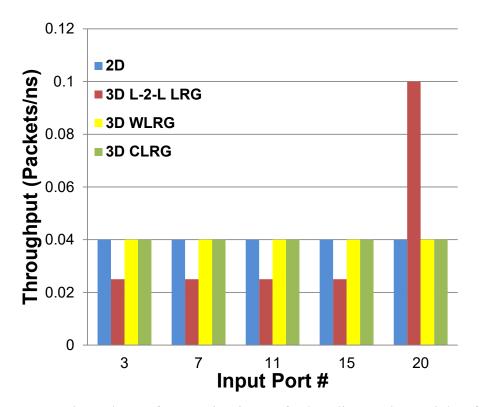

| Figure 2.14 Throughput of arbitration schemes for UR traffic                               | 45   |

| Figure 2.15 Throughput of requesting inputs for baseline's adversarial traffic             | 46   |

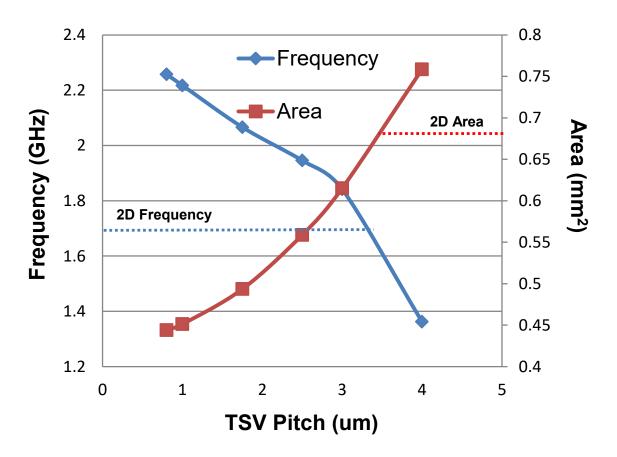

| Figure 2.16 Sensitivity of frequency and area to TSV pitch for Hi-Rise                     | 48   |

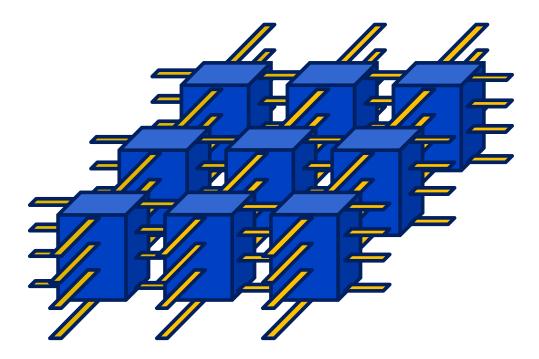

| Figure 2.17 A 2D mesh NoC topology composed of 3D Hi-Rise switches for 3D chips            |      |

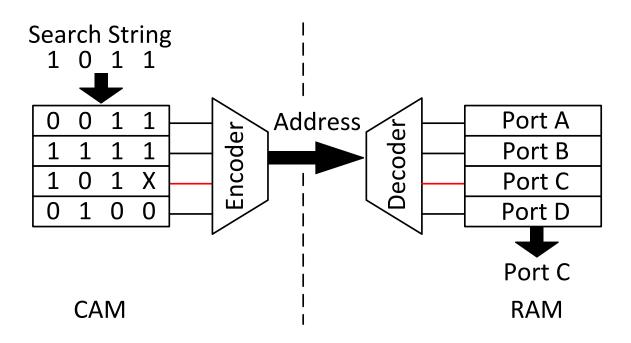

| Figure 3.1 CAM – A major component of IP router tables                                     | 56   |

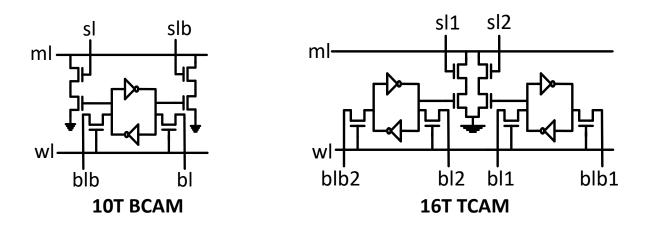

| Figure 3.2 Conventional bit cell design for BCAM and TCAM respectively                     | 57   |

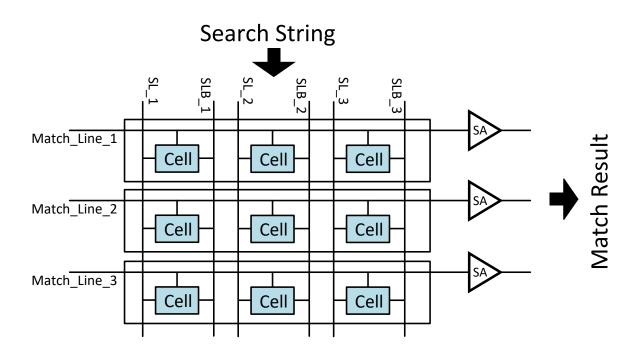

| Figure 3.3 Conventional CAM array organization.                                            | 58   |

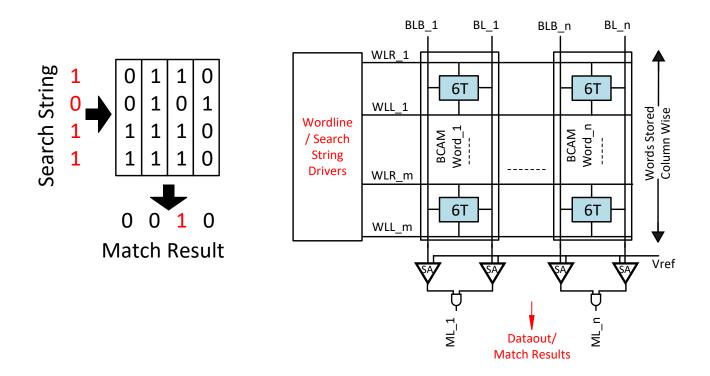

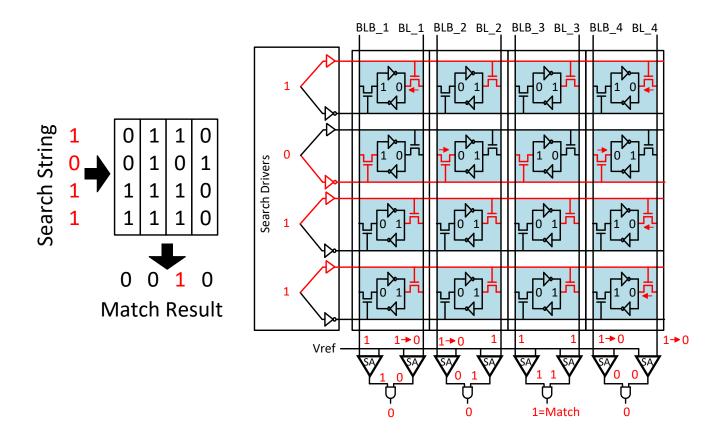

| Figure 3.4 Proposed CAM array organization.                                                | 59   |

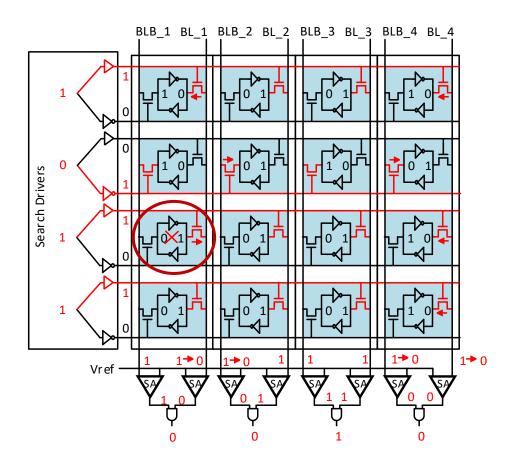

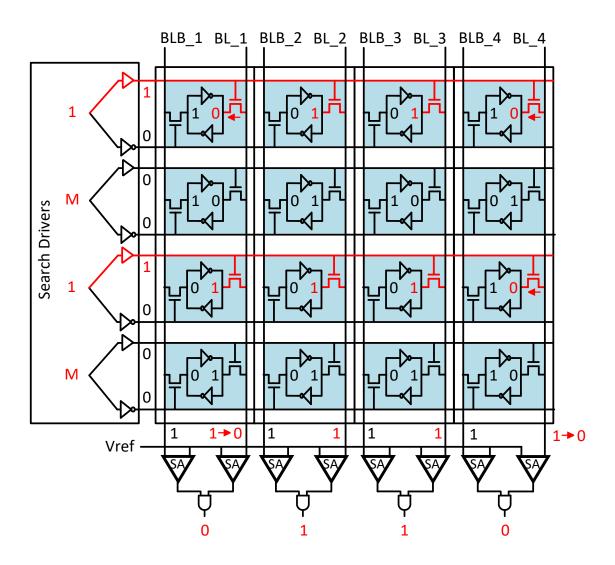

| Figure 3.5 BCAM search example. Only column 3 is a match.                                  |      |

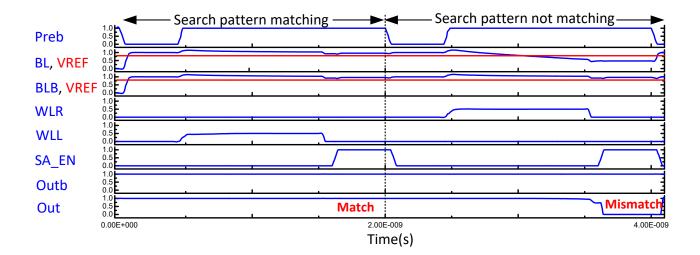

| Figure 3.6 Timing waveforms for BCAM search                                                |      |

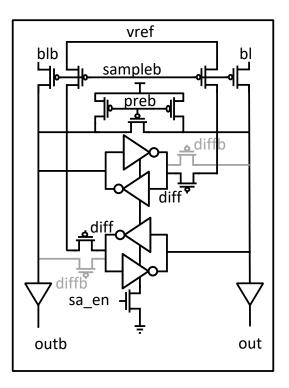

| Figure 3.7 Reconfigurable sense amplifier: 2-Single-ended amplifiers in CAM and logic mode | es   |

|                                                                                            |      |

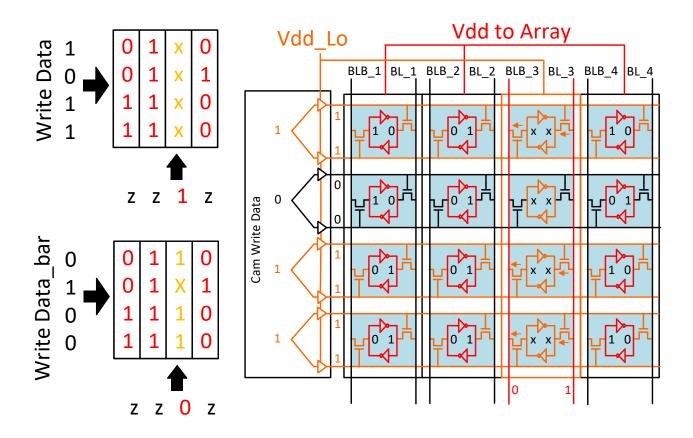

| Figure 3.8 Spice waveforms for reconfigurable sense amplifier in single-ended mode         |      |

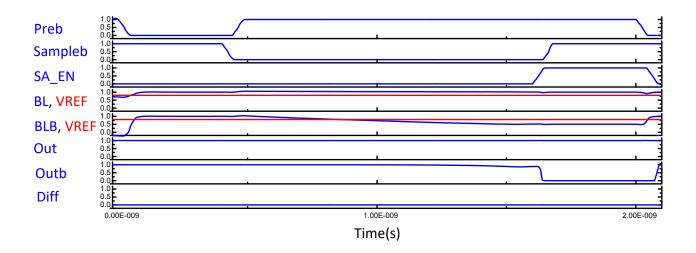

| Figure 3.9 BCAM column-wise write. In this example column 3 is being written               |      |

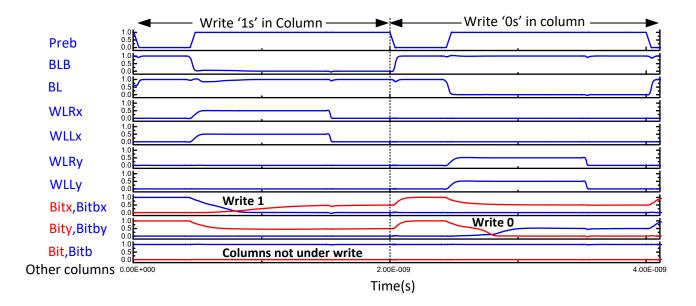

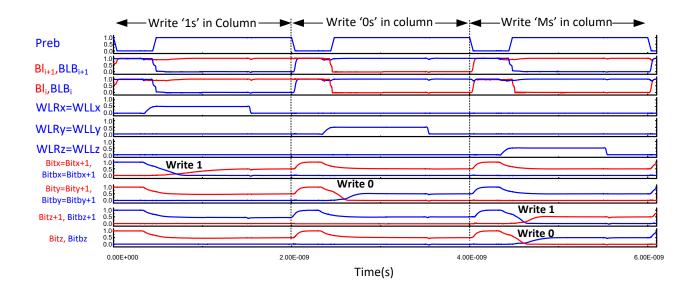

| Figure 3.10 Timing waveforms for 2-cycle BCAM write                                        |      |

| Figure 3.11 BCAM Search disturb: Pseudo write condition on encircled bit cell              |      |

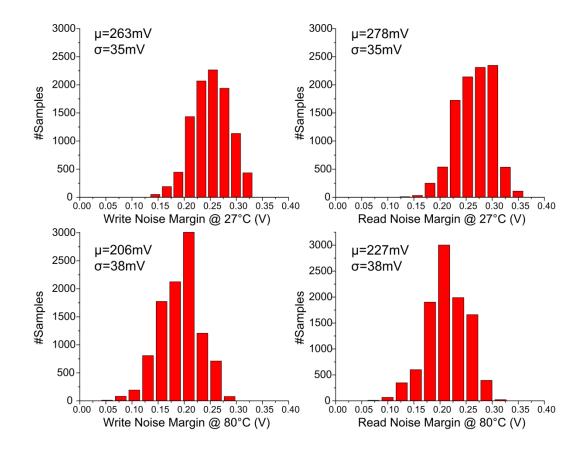

| Figure 3.12 Monte-carlo simulations for write and search (read) robustness in CAM modes    | 69   |

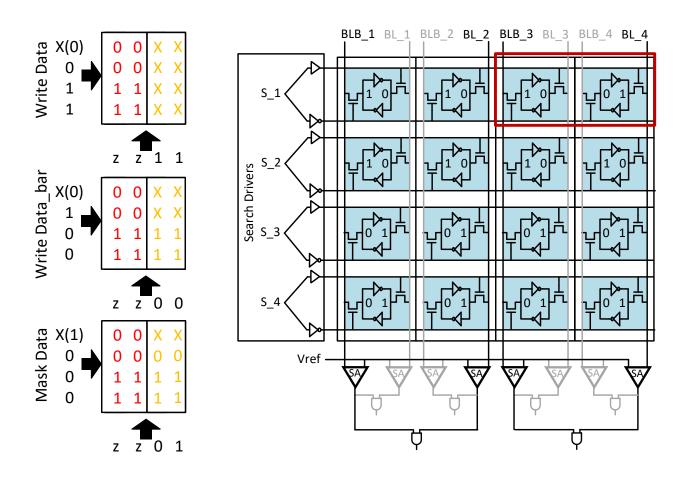

| Figure 3.13 TCAM mode organization. Two columns comprise one TCAM word70                         |

|--------------------------------------------------------------------------------------------------|

| Figure 3.14 Timing waveforms for 3-cycle TCAM write                                              |

| Figure 3.15 Logic operations in memory - 'AND' example                                           |

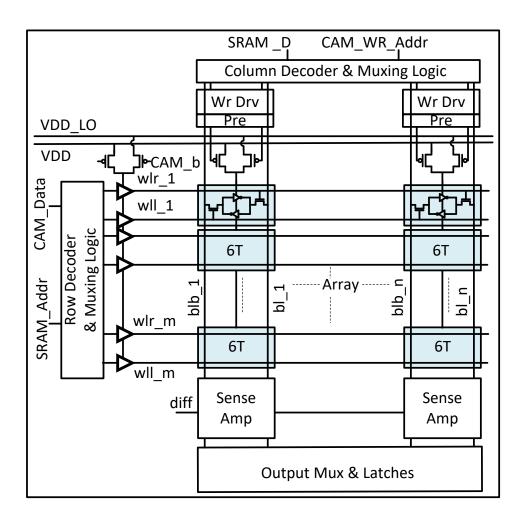

| Figure 3.16 Configurable memory organization                                                     |

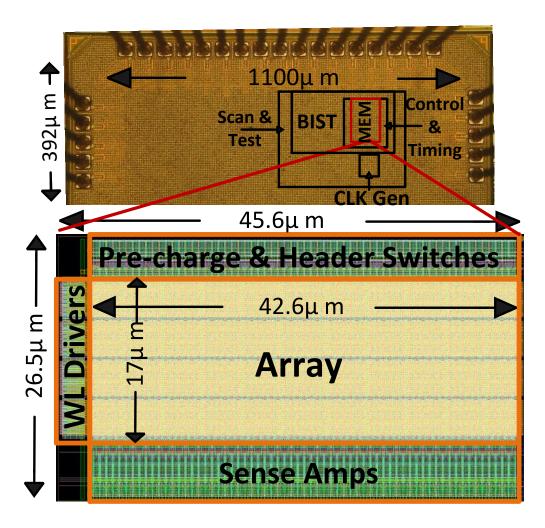

| Figure 3.17 Die photo and memory layout                                                          |

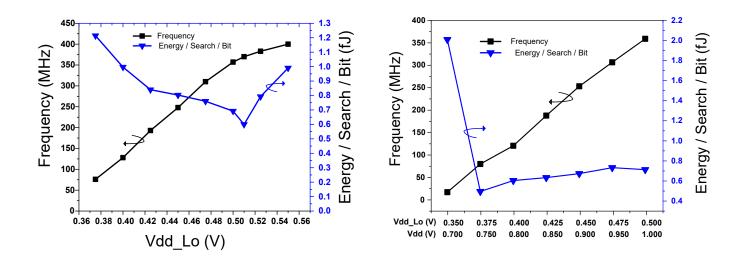

| Figure 3.18 (a) Measured frequency and energy in BCAM against Vdd Lo, with $Vdd = 1V$ .          |

| (b)Measured frequency and energy in BCAM against Vdd, with Vdd $Lo = 0.5*Vdd$                    |

|                                                                                                  |

| Figure 3.19 (a) Measured frequency and energy in TCAM against Vdd Lo, with $Vdd = 1V$ .          |

| (b)Measured frequency and energy in TCAM against Vdd, with Vdd $Lo = 0.5*Vdd$                    |

|                                                                                                  |

| Figure 3.20 Measured shmoo plot of Vdd_Lo vs VDD for BCAM. Numbers in box are                    |

| frequency in MHz                                                                                 |

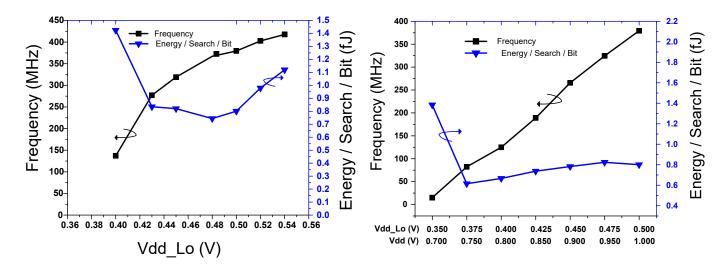

| Figure 3.21 Measured Vdd_Lo margin and max frequency across 10 chips                             |

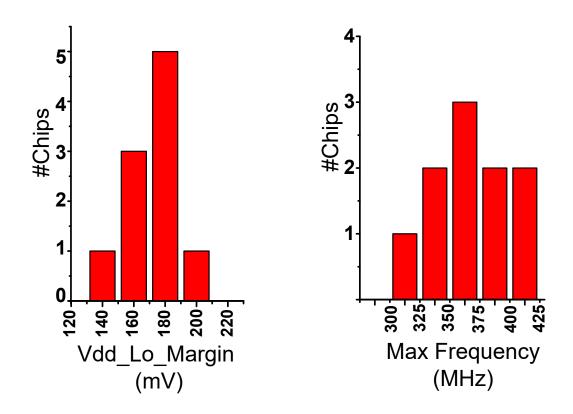

| Figure 3.22 Measured frequency for logic operation between two words in memory against           |

| Vdd_Lo, with fixed Vdd at room temperature                                                       |

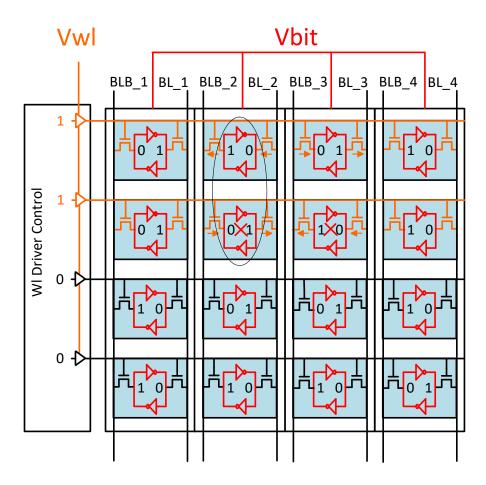

| Figure 4.1 Sequence based PUF with two word-lines enabled                                        |

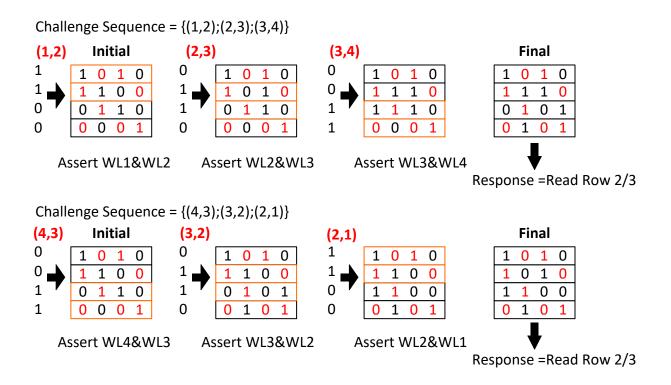

| Figure 4.2 Example of sequence dependence of proposed PUF                                        |

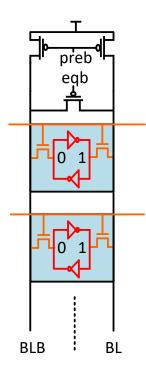

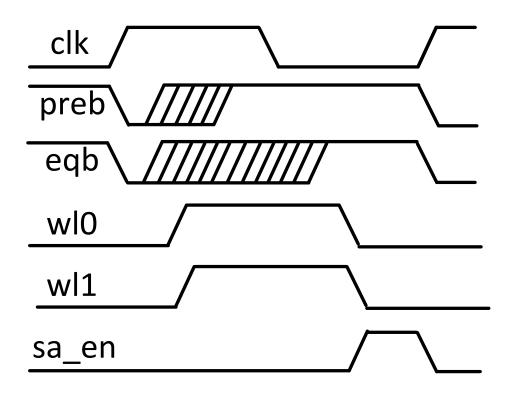

| Figure 4.3 Split equalizer signal in SRAM array column                                           |

| Figure 4.4 Timing waveform for proposed PUF                                                      |

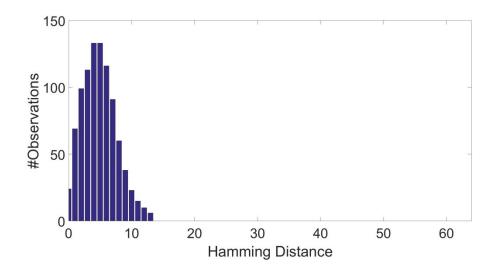

| Figure 4.5 Inter-sequence hamming distance distribution for 3-row cyclic                         |

| Figure 4.6 Inter-sequence hamming distance distribution for 3-row straight                       |

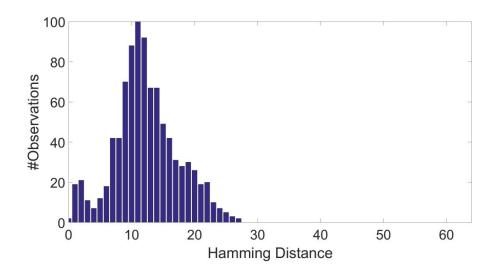

| Figure 4.7 Inter-sequence hamming distance distribution for 4-row straight                       |

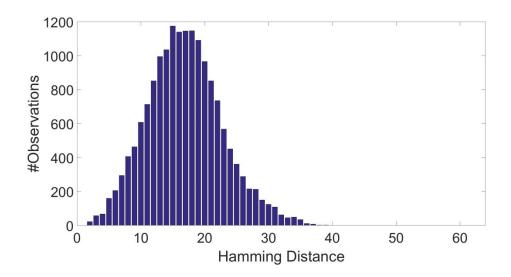

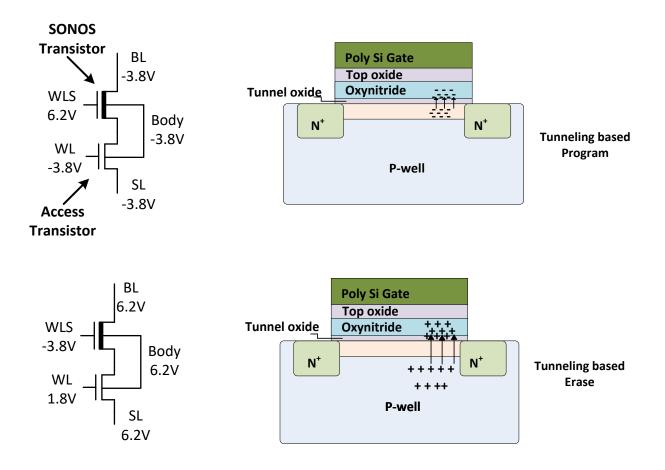

| Figure 5.1 Erase & program voltage for SONOS (Silicon-Oxide-Nitride-Oxide-Silicon) using FN      |

| tunneling                                                                                        |

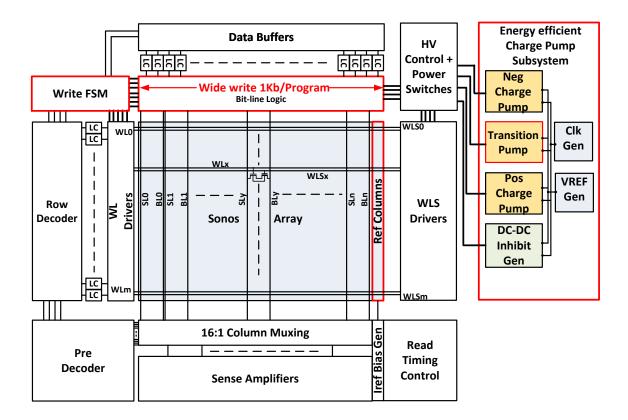

| Figure 5.2 Block diagram of proposed wide-write low power SONOS flash with transition pump       |

| for high current                                                                                 |

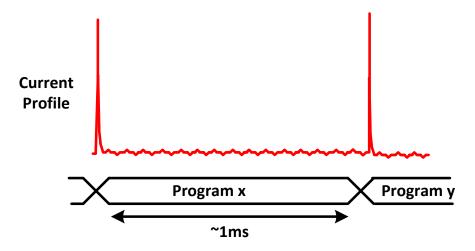

| Figure 5.3 Current profile for FN tunneling based program. Large transition current at beginning |

| of each program cycle100                                                                         |

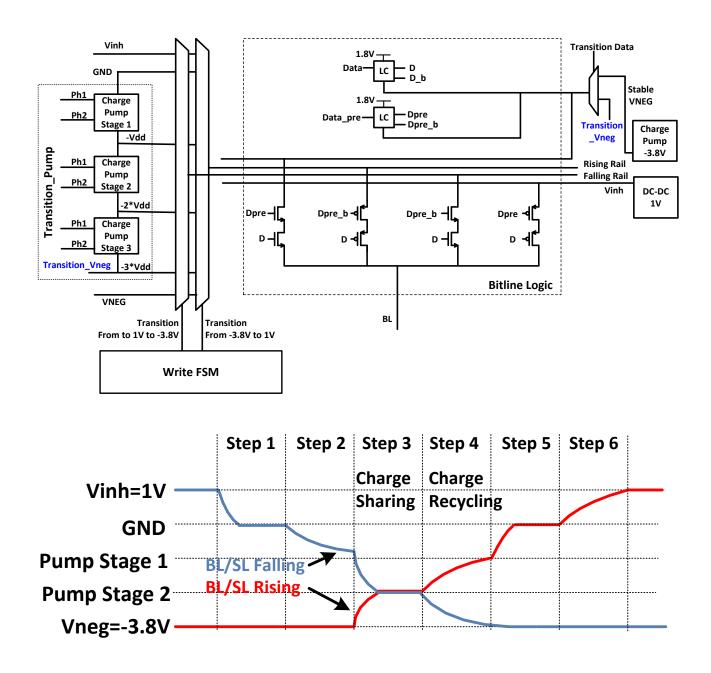

| Figure 5.4 Stepped-transition of 1K BL & SL using transition pump to reduce peak power,          |

| enabling wide write                                                                              |

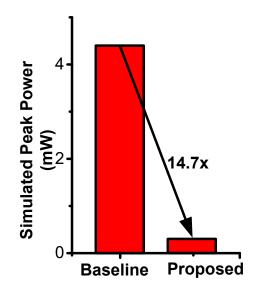

| Figure 5.5 Transition pump reduces peak power, enabling wide write                               |

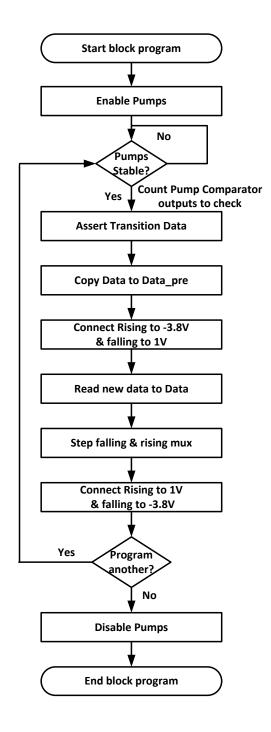

| Figure 5.6 Write flow chart implemented in the proposed SONOS program controller                 |

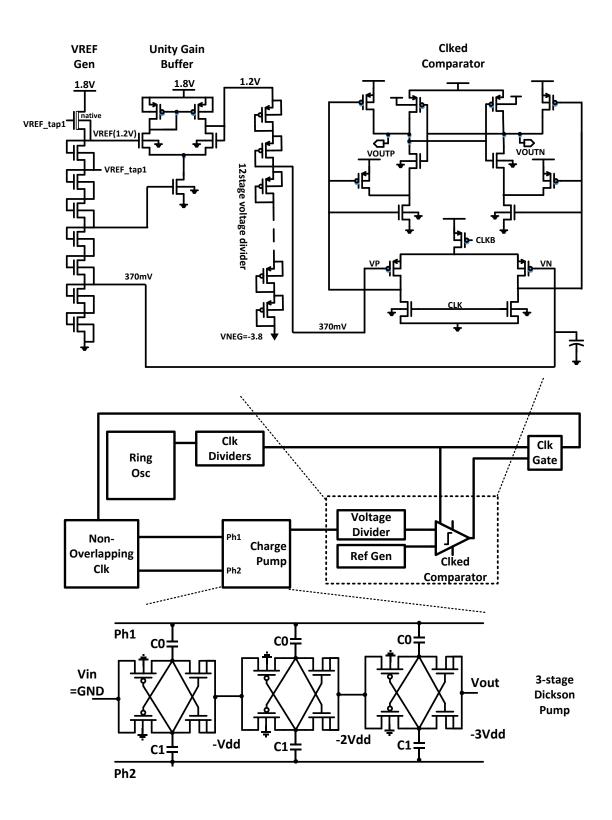

| Figure 5.7 Negative charge pump design with control loop                                         |

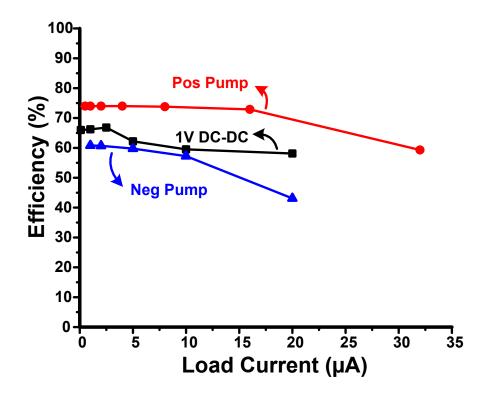

| Figure 5.8 Simulated efficiency over load current for negative and positive pumps and 1V DC-     |

| DC generator                                                                                     |

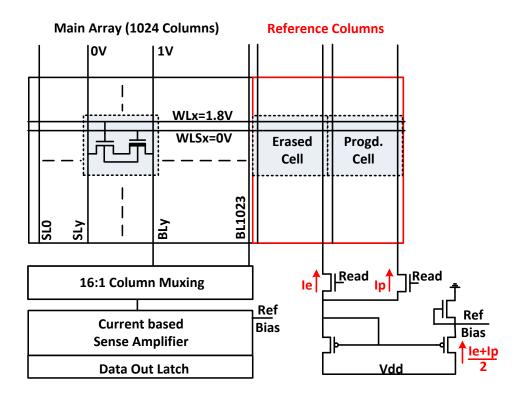

| Figure 5.9 Read reference current generation for proposed flash improves read margin by 23%      |

|                                                                                                  |

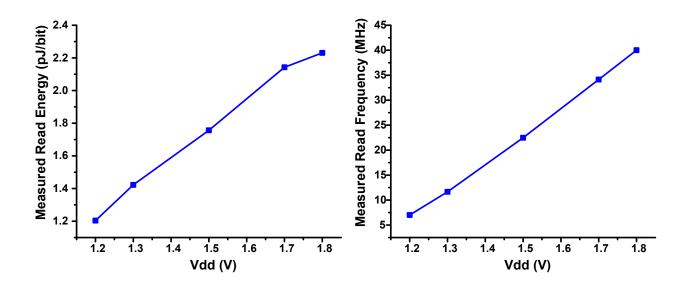

| Figure 5.10 Measured read energy and frequency over Vdd. Read Vddmin is 1.2V 108                 |

| Figure 5.11 Measured program energy across temperature (left). Program energy distribution is    |

| plotted for 21 chips (right)                                                                     |

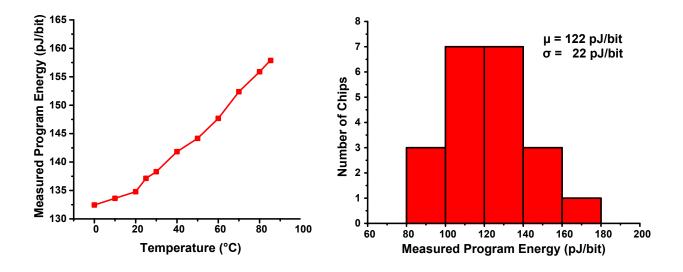

| Figure 5.12 Proposed SONOS flash die photo                                                       |

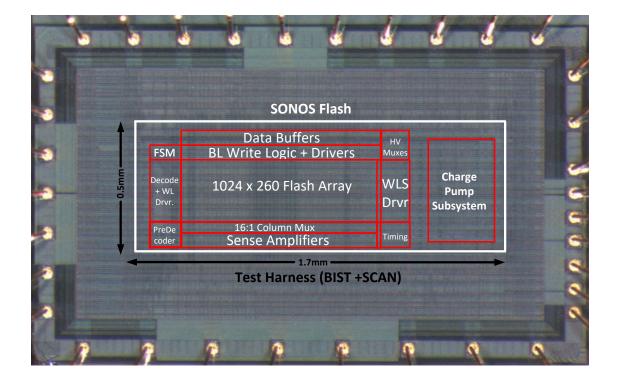

| Figure 6.1 FeCap based on Lead Zirconate Titanate                                                |

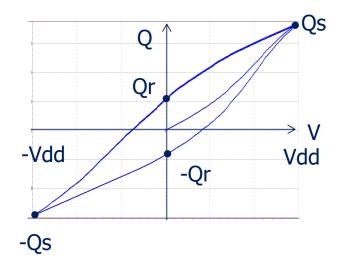

| Figure 6.2 FeCap hysteresis loop                                                                 |

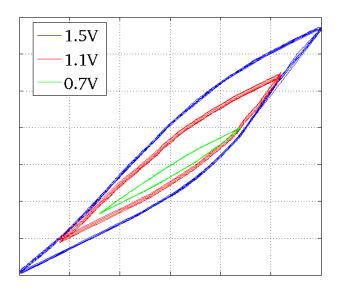

| Figure 6.3 FeCap hysteresis loop for different supply voltages                                   |

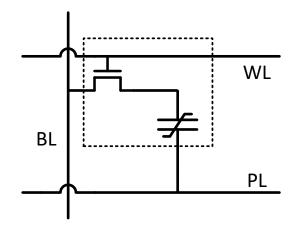

| Figure 6.4 A 1T1C FRAM bit cell 114                                                              |

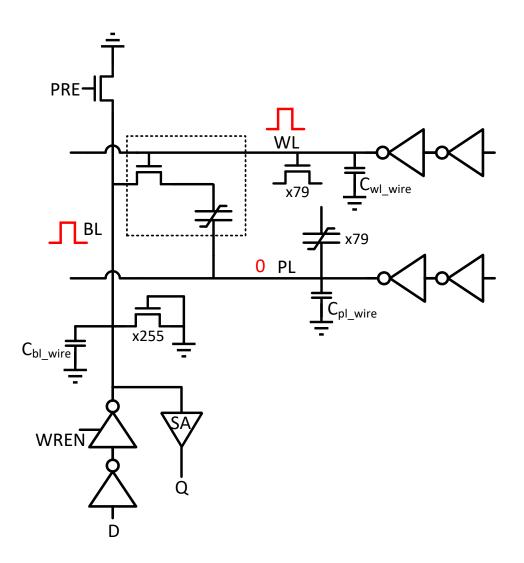

| Figure 6.5 Conventional 256x80 FRAM array model: Write '1' example                   | 115 |

|--------------------------------------------------------------------------------------|-----|

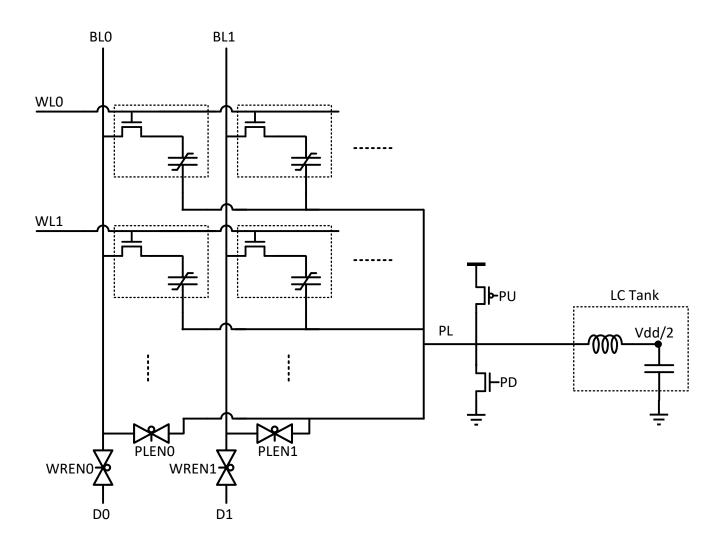

| Figure 6.6 Proposed FRAM adiabatic design                                            | 117 |

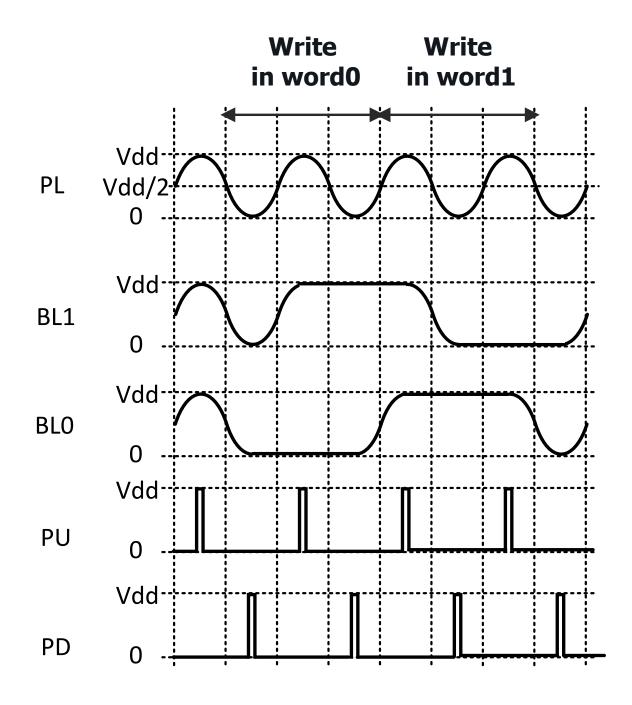

| Figure 6.7 Timing waveform for proposed FRAM adiabatic design                        | 118 |

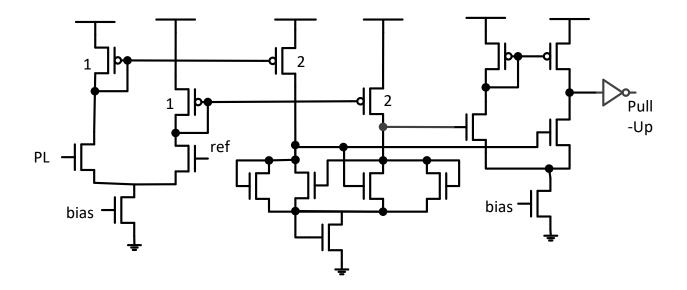

| Figure 6.8 Continuous comparator design for PU (Pull-up) signal                      | 119 |

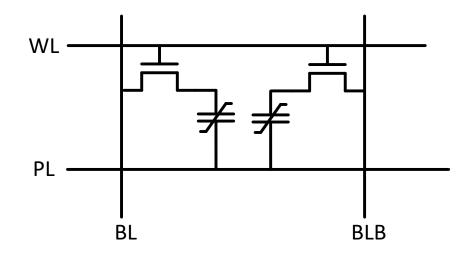

| Figure 6.9 A 2T-2C bit cell configuration                                            | 120 |

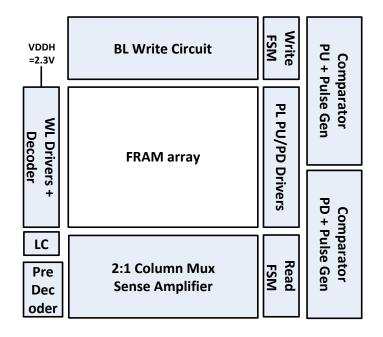

| Figure 6.10 Proposed FRAM block diagram                                              |     |

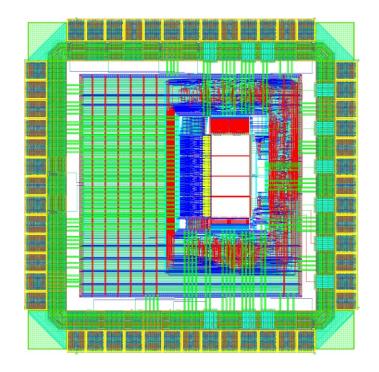

| Figure 6.11 FRAM prototype chip layout                                               |     |

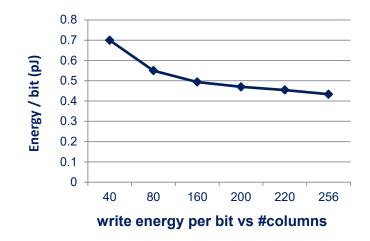

| Figure 6.12 Write energy per bit for proposed FRAM versus number of columns in array |     |

# LIST OF TABLES

| Table 2.1 Implementation cost of 2D versus 3D folded for 64-radix switch            | 20  |

|-------------------------------------------------------------------------------------|-----|

| Table 2.2 Spice condition and TSV parameters                                        | 36  |

| Table 2.3 Processor configuration for application workloads                         | 37  |

| Table 2.4 Implementation cost of different 64-radix switch implementations          | 41  |

| Table 2.5 Implementation cost of different switch arbitration variants for 64-Radix | 48  |

| Table 2.6 Benchmark speedup results for proposed switch for a 64-core processor     | 49  |

| Table 3.1 Logic operations supported in configurable memory                         | 72  |

| Table 3.2 Configurable memory – Mode configuration table.                           | 76  |

| Table 3.3 Comparison with previous BCAM works                                       | 83  |

| Table 3.4 Comparison with previous TCAM works                                       | 84  |

| Table 4.1 Two-row simple PUF measurement results                                    | 92  |

| Table 4.2 Two-row PUF: Initialization sensitivity measurements.                     | 93  |

| Table 4.3 Sequence based PUF measurement results                                    | 94  |

| Table 5.1 Comparison with previous flash works.                                     | 109 |

# **CHAPTER 1**

## Introduction

Technology scaling used to improve circuit performance with every technology node while keeping the power density (power dissipation per unit area) constant. Power density is an important parameter for modern chip design. Power density determines how quickly a system heats up, and has to be maintained within the limits of the thermal cooling capabilities of the system. As technology scaling geometrically shrinks circuit area, cooling becomes harder if power is not reduced proportionately.

For older technology generations, voltage scaling used to provide quadratic power reduction, while smaller capacitance for smaller transistors provided a linear reduction in power. These two factors combined more than offset the area reduction, and allowed a linear increase in the clock frequency of the system, while keeping the power density constant. This increase in clock frequency of the system implied more instructions being processed in the same wall clock time, and hence enhanced performance of the system.

However, in newer technology nodes, the supply voltage scaling has plateaued as seen in Figure 1.1 [56], and hence both energy density and power density are increasing. As the thermal cooling capabilities are bounded, system designers have had to limit the clock frequency. As a result frequency scaling came to an end around 2004, as seen in Figure 1.2. Also, to maintain the

power density as area continues to shrink, the maximum power has actually been reducing for processors, as seen in Figure 1.3. This total power consumption curve reiterates the limits created by power density, and consequently thermal cooling capabilities on system performance.

Figure 1.1 Energy density and supply voltage scaling with technology node [56]

As clock frequency stopped increasing, the performance stagnated because the processors can no longer be operated faster. The next logical step was to use this extra available area to add more cores in the system, and hence performing parallel processing to gain performance. Processor designs started using multiple cores, as can be seen from the trends in Figure 1.4, about the same time that clock frequencies stagnated.

Figure 1.2 Clock frequency trends [58]

Figure 1.3 Total power consumption trend [57]

Core counts on processors published at ISSCC.

Figure 1.4 Core count trends [58]

Multi-cores increase area linearly, but the slowing down of voltage scaling has a quadratic impact on power dissipation. This implies that multi-core processors only delayed reaching the thermal cooling capability limits, but could not avoid it.

This has led to development of several architectural and circuit-level techniques for low power. The general trend has been to replace power-hungry, high-voltage and high-speed complex cores with a number of more power-efficient simpler cores working in tandem. New techniques like heterogeneous cores use a mix of both simple and complex cores. Other techniques like Near-Threshold Computing (NTC) [56][70] in conjunction with many-core systems, try to reduce the supply voltage to achieve the most optimum energy-performance operating point. For performance intensive parts, such as servers, the number of cores has steadily increased. The same solution may not work for application specific processor, where the power profile is very different, and the 'all-on' mode power still shows an increasing trend in power, as seen in Figure 1.5. Notice the order of magnitudes lower total power than the power numbers shown in Figure 1.3. These applications still need more performance gains, but most are battery-operated and hence extremely energy sensitive.

Thus, with the current scaling trends, we need to apply different solutions for different application space. In this thesis we divide the design space into three categories, and propose solutions for improved energy-efficiency and the power-density problem for all three.

- i. Many core systems Performance intensive

- ii. Mobile Single / few-cores. Both performance and energy important

- iii. Internet of Things (IoT) Very low activity. Energy most important

Application processor power trends.

Figure 1.5 All-on mode power for application processors [58]

#### **1.1 Many-core systems**

Many-core systems are increasingly using power efficient simple cores. The performance of a single simple core is typically much lower than a power-hungry complex core, but by using a number of simple cores in parallel, and dividing the task into smaller parts, the overall performance of the system can be increased. The major challenge for many-core systems is the need to share data and hand-shaking signals between the cores working in parallel on the same task. As the simpler cores are more power-efficient, a majority of the energy is spent in moving the data from one core to the other, and back and forth from the memory.

As a result, many-core systems require low latency, area-energy efficient interconnect fabrics with extremely high band-width. Conventional interconnect topologies are optimized for few core systems, and hence are constructed out of low-radix switches such as a 2D-Mesh [1][2]. The radix of a switch is defined as the number of ports (nodes) that the switch connects. In a conventional 2D Mesh, each low-radix switch can only connect to four other nodes. For a fully connected many-core system comprising of several tens of cores, the low-radix switches will have to make connections (hops) through several intermediate nodes to transmit data from one core to the other. This leads to both high latency and high power consumption [3]. In addition, many-cores communicating together imply the interconnection fabric has to arbitrate more between competing requests from cores. Therefore, an interconnect fabric with efficiently designed high-radix switch and fair arbitration can be more optimal for many-core systems [4][5].

Concurrently, 3D integration has become an important means of improving performance as process scaling slows down. 3D integration allows the number of cores to be increased by stacking different layers [6], with short vertical connections between the layers. These short connections can be leveraged for speeding up inter-layer communication and building an efficient interconnect.

This thesis proposes a 3D cross-point based interconnect, *Hi-Rise* [67]. Hi-Rise is an efficient 3D high-radix switch. The proposed switch is a true 3D switch which connects inputs and outputs across different silicon layers. Hi-Rise adopts a hierarchical architecture with two internal switches per layer and dedicated layer-to-layer channels, to improve area efficiency, lower delay, and minimize the number of inter-layer vertical connections. Hi-Rise also provides built-in single-cycle arbitration across all inputs and outputs across different silicon layers. This improves both efficiency and scalability.

A new class based arbitration scheme is also proposed that is fully integrated into the switching fabric. This scheme makes the 3D hierarchical switch's fairness comparable to that of a flat 2D switch. The proposed switch extends scalability to radix 96 from that of the 64 radix supported by 2D switches at the same operating frequency, allowing for efficient integration of more cores.

### 1.2 Mobile systems with performance and energy constraints

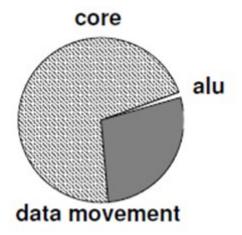

Current generation of mobile systems already use aggressive voltage-frequency scaling and other energy reduction techniques, to bring down the power of conventional architectures. As Figure 1.6 shows, the conventional Von Neumann architecture has an inherent issue, where orders of magnitude more energy is spent on data movement between the cores and the memory hierarchy, than on the actual computation in the Arithmetic Logic Unit (ALU). The data movement cost consists of fetching the operands from the cache or the main memory to the register file of the processor, computation in the ALU, and then finally writing back the result in the memory.

Figure 1.6 Processor dynamic energy

To improve the energy efficiency for such systems, the change required in the architecture is to move computation to where the data is stored. This shift in architecture will require storage that can inherently support computations. If the operands stored in the memory can be computed upon within the memory itself and then the result written back into the same memory, the data movement cost can be greatly reduced.

This thesis proposes a configurable memory that uses conventional SRAM bit cells, but can provide CAM (Content Addressable Memory) [36] capabilities for search applications and can also perform logical operations within the memory array. A Content Addressable Memory compares its search input data with every word stored in the memory, and returns the address location of the matching words. In addition, the configurable memory can perform bit-wise logical operations on two or more words stored within the array. Thus, the configurable memory with CAM [45] and logical functions capability [66] can be used to off-load specific computational operations to the memory, improving system performance and efficiency. Performing logical operations in memory also frees up the ALU for more involved calculations, and hence boosts performance [46][47][48][49]. Using logic-inmemory improved both performance ( $\sim$ 1.9×) and energy ( $\sim$ 2.4×) [71] for certain applications like string matching, and bit matrix multiplication. The configurable SRAM can therefore be used in accelerators for application specific design, as well as general purpose processors. The proposed configurable memory chip has been designed and fabricated in a 28nm technology node.

The configurable memory can also be repurposed as a PUF (Physically Unclonable Function), [62] [63] which is like a device fingerprint, typically used for hardware authentication. The proposed PUF is a modified design of the configurable memory discussed above, and has also been fabricated in the 28nm technology node. Unlike existing PUF circuits, where the response depends only on the current challenge (input) vector, the proposed PUF response is dependent on a sequence of inputs. Sequence dependence, combined with a larger number of possible challenge-response pairs makes the response from this PUF hard to predict and hence more secure.

### **1.3 IoT systems**

Unlike the server and mobile systems, IoT (Internet-of-Things) systems have an extremely small energy budget, and very low activity rate. They mainly consist of sensor nodes, which intermittently wake-up, log sensed data and go back to a very low-power or zero-power state.

For such IoT systems, the ability to power-off to save energy is vital. This is the reason for use of non-volatile memory in IoT systems for data logging. But, non-volatile memory may expend significant energy for write operations. To improve energy efficiency in IoT systems, this thesis proposes two non-volatile memory solutions with charge recycling techniques, to significantly reduce the write energy for the proposed non-volatile memory. The two nonvolatile memory solutions proposed are low power SONOS (Silicon-Oxide-Nitride-Oxide-Silicon) Flash [64][65] and adiabatic Ferroelectric RAM (FRAM). [59][60][61]

Unlike conventional flash which uses energy-intensive hot carrier injection based program (write) operation, both erase and program in a SONOS flash cell is based on tunneling. This makes SONOS inherently more energy efficient. This thesis proposes a SONOS flash with an ultra-wide 1Kb/program cycle, enabled by low tunneling program power and a dedicated, multi-output transition pump which uses charge sharing and charge recycling. Combined with energy efficient charge pumps, the proposed flash program energy is 122pJ/bit with a 1Mbps throughput. The proposed SONOS flash memory chip has been designed and fabricated in a 130nm technology node, and is able to match the throughput of a conventional floating gate flash with ~10× lower energy.

The second non-volatile memory (NVM) solution proposed in this thesis is an adiabatic (charge recycling) FRAM array. Compared to the more popular flash memory, FRAM has significantly faster write access time, lower write energy, and does not require high voltages to write. Flash on the other hand, has better density than FRAM, and is scaling better with technology. FRAM solutions are ideal for sensor nodes with small write-intensive arrays, as the density advantage of flash is offset by the area penalty for the high voltage circuits. The proposed FRAM chip is designed and fabricated in a 130nm technology node. The proposed

adiabatic FRAM design reduces the write energy by  $\sim 7 \times$  in simulations, compared to the baseline FRAM design.

## 1.4 Thesis organization

This dissertation proposes to solve the power density problem across systems, varying from very high performance systems to very low energy systems. It uses cross-point circuits for these solutions. Cross-point circuits are array based circuits, where the unit block is small, and can be easily optimized for both area and energy. These unit blocks are then tiled together to make much larger scalable circuits.

Chapter 2 proposes a cross-point based 3D high radix interconnect fabric, Hi-Rise, which is optimized for both throughput and arbitration fairness. At a radix of 64, Hi-Rise achieves an operating frequency of 2.2GHz, consumes only 44pJ of energy per 128-bit transaction and has an area of 0.451mm<sup>2</sup> in 32 nm technology. Hi-rise is therefore a fast, area-energy efficient interconnect for many-core systems.

Chapter 3 proposes a configurable memory that uses conventional SRAM bit cells, but can provide CAM capabilities for search applications and can also perform logical operations within the array between two or more words. Using memory for computation, reduces data movement costs, and greatly improves both energy-efficiency and performance of a processor. Using a standard push-rule 6T 28nm SRAM bit cell, the 64x64 (4kb) BCAM achieves 370 MHz at 1V and consumes 0.6fJ/search/bit. A logical operation between two 64-bit words achieves 787 MHz at 1V.

Chapter 4 proposes a cross-point based security block, based on the SRAM in Chapter 3. The proposed PUF response is dependent on both, the length and the order of the input challenge sequence. Therefore, the sequence dependent PUF can be run in many configurations and has a large challenge-response space.

Chapter 5 and Chapter 6 propose cross-point based non-volatile storage circuits optimized for write-intensive applications in IoT systems.

In Chapter 5, a low power SONOS flash memory is proposed. The proposed memory is a 130nm, 1024x260 SONOS flash which requires only 122pJ/bit program energy. It supports a wide program of 1Kbit per program cycle at a throughput of 1 Mbps. The proposed SONOS flash is  $\sim$ 10× lower program energy than conventional flash.

In Chapter 6, an adiabatic FRAM array is proposed. The proposed 130nm, 512x80 FRAM memory uses adiabatic techniques to reduce the write energy by  $\sim 7 \times$  compared to the non-adiabatic design in simulations, whereas the read with write back energy reduces by  $\sim 4 \times$ .

Concluding this dissertation is Chapter 7, which summarizes the contributions of this dissertation and discusses some possible future directions. At the end of Chapter 7, is a list of related publications generated from this work.

# **CHAPTER 2**

## Hi-Rise: A high-radix switch for 3D integration

### 2.1 Introduction

The number of cores on a single chip has seen a steady upward trend due to emerging parallel workloads and the need to meet performance goals within constrained power budgets. These many-core systems require low latency, area-energy efficient interconnects with extremely high bandwidth. Conventional interconnects constructed out of low-radix switches such as a 2D-Mesh [1][2] do not scale well because of the decreased performance resulting from larger hop counts and high power consumption [3]. Therefore, an interconnect fabric with efficiently designed high-radix switches is optimal for future many-core processors [4][5]. Concurrently, 3D integration has become an important means of improving performance as process scaling slows down. This technique allows the number of cores to be increased by stacking different layers [6], with short vertical connections between the layers. These short connections can be leveraged for speeding up inter-layer communication and building an efficient interconnect. Interconnects based on low-radix 3D switches [7][8][9][10] have been proposed in the past for 3D multi-core processors. However, as previously mentioned, low-radix and low bandwidth switches do not provide good scalability for a large number of cores.

3D high-radix switch design entails its own unique challenges. Unlike a flat 2D highradix switch [11], the inputs and outputs of a 3D switch are spread over multiple layers. A 3D high-radix switch requires both intra-layer connections and inter-layer connections. The interlayer vertical connections between silicon layers are made using Through-Silicon Vias (TSV). This leads to heterogeneity in the intra-layer and inter-layer connections. Consequently, a simple 3D high-radix [12] switch folded over silicon layers has lower performance than a flat 2D switch. A high-radix 3D switch design thus requires: 1) switch datapath optimized for this connection heterogeneity; 2) composable and fair arbitration scheme across inter-layer and intra-layer connections; 3) reduction in the number of expensive TSVs with minimal impact on the switch performance parameters, i.e., throughput, latency and fairness; and, 4) improved area and energy efficiency to offset the design and manufacturing cost.

This thesis proposes Hi-Rise, a high-radix 3D switch that achieves significant scalability and reduces the required number of TSVs by using a hierarchical architecture with dedicated layer-to-layer channels. The proposed Hi-Rise switch is divided into layers, each layer has two switches, a local switch and an inter-layer switch. The local switch connects local inputs to both intermediate outputs and vertical channels to other layers. The inter-layer switch connects both vertical channels from other layers and the intermediate outputs from the local switch to the final outputs on its layer. When combined, the two switches per layer result in a fully connected switch.

The hierarchical datapath of the switch is optimized for 3D connections. A key issue with the hierarchical switch datapath is that it can lead to unfairness as the arbitration is decomposed into two phases. To address this, a new arbitration scheme, Class-based Least Recently Granted (CLRG), which brings the fairness of a hierarchical 3D switch close to that of a flat 2D switch using LRG priority, is proposed. In this scheme, the inter-layer switch maintains a small counter for each input which signifies that input's output usage, and accordingly bins the requestors into different priority classes. Inputs in the same class use LRG to break ties. In contrast to CLRG, the implementation complexity of prior multi-stage arbiter designs [13][14], make them unattractive for high-radix switches. In addition, these arbiter designs are not optimized for 3D, and lead to high inter-layer traffic, unlike the proposed CLRG scheme. We demonstrate that the proposed class based arbitration allows for single cycle arbitration and full integration within the switch fabric, with no area and negligible performance overheads.

The proposed 3D switch is evaluated for various architectural and physical configurations. This thesis studies the proposed switch design through detailed circuit-level delay analysis, power modeling, and micro-architectural cycle accurate performance simulations. We study various synthetic traffic patterns, and also real application benchmarks. The 3D switch is analyzed for different radices, number of stacked layers, and different TSV technologies. A 64-radix, 128-bit, 4-layer Hi-Rise is evaluated in detail using a 32nm technology. It has a throughput of 10.65 Tbps for uniform random traffic, which marks a 15% improvement over a 2D design along with a 33% area reduction, 20% latency reduction, and 38% energy per transaction reduction. For application workloads evaluated on a 64-core processor, Hi-Rise switch improves overall performance by 8% on average over a 2D switch.

In summary, our key contributions are:

• Hi-Rise, an efficient 3D high-radix switch. The proposed switch is a true 3D switch which connects inputs and outputs across different silicon layers.

15

• Hi-Rise adopts a hierarchical architecture with two internal switches per layer and dedicated layer-to-layer channels, to improve area efficiency, lower delay, and minimize the number of inter-layer TSVs.

• Hi-Rise provides built-in single-cycle arbitration across all inputs and outputs across different silicon layers. This improves efficiency and scalability.

• This thesis proposes a new class based arbitration scheme that is fully integrated into the switching fabric. This scheme makes the 3D hierarchical switch's fairness comparable to that of a flat 2D switch.

• At a radix of 64, Hi-Rise achieves an operating frequency of 2.2GHz, consumes 44pJ of energy per 128-bit transaction and has an area of 0.451mm<sup>2</sup> in 32 nm technology. The proposed switch extends scalability to radix 96 from that of the 64 radix supported by 2D switches at the same operating frequency.

### 2.2 Background: 2D switch

#### 2.2.1 The 2D swizzle-switch

This section provides a brief background of a high-radix 2D Swizzle-Switch [11][15]. As discussed earlier, unlike a 2D flat switch, a high-radix 3D switch design connects inputs and outputs across multiple layers with both intra-layer and expensive vertical TSV inter-layer connections. The proposed Hi-Rise switch solves the design challenges of a 3D switch, while using the basic concepts of a 2D Swizzle-Switch for its internal switch structures.

A 2D Swizzle-Switch is a matrix type crossbar, with built-in arbitration, optimized for high radix switches. The input and outputs of the switch are placed in a grid fashion. The intersection of the horizontal input bus, with the vertical output bus is termed as a cross-point. A cross-point contains a connectivity bit, which if set, connects its input and output bus. The connectivity bit is set during the arbitration phase. The cross-point also stores a priority vector, containing priority information of its input with respect to all other inputs, for this output. The priority vector is updated based on LRG priority at the end of the arbitration phase.

The arbitration phase begins with each input requesting the outputs with which it wants to communicate. The input data lines are reused to index the outputs during arbitration. The output data lines are also reused as a priority bus during the arbitration phase. One advantage of reusing the output bus for priority lines during arbitration is that the same hardware used for data transfer (pre-charge, pull-down drivers and sense-amps) are reused during arbitration. This allows arbitration to be incorporated into the switch fabric without additional area overhead (since space underneath the cross-point is otherwise largely unused), and guarantees that the arbitration delay is identical to the datapath delay.

Thus, by embedding the logic-dominated arbitration into the wire-dominated crossbar, the 2D Swizzle-Switch allows a compact design and scaling of matrix crossbars to high radices.

#### 2.2.2 Baseline 3D switch: A folded 2D switch

A natural extension of the 2D switch to a 3D stacked implementation is to fold the 2D switch over multiple silicon layers. For this, the inputs and outputs will be redistributed across the layers.

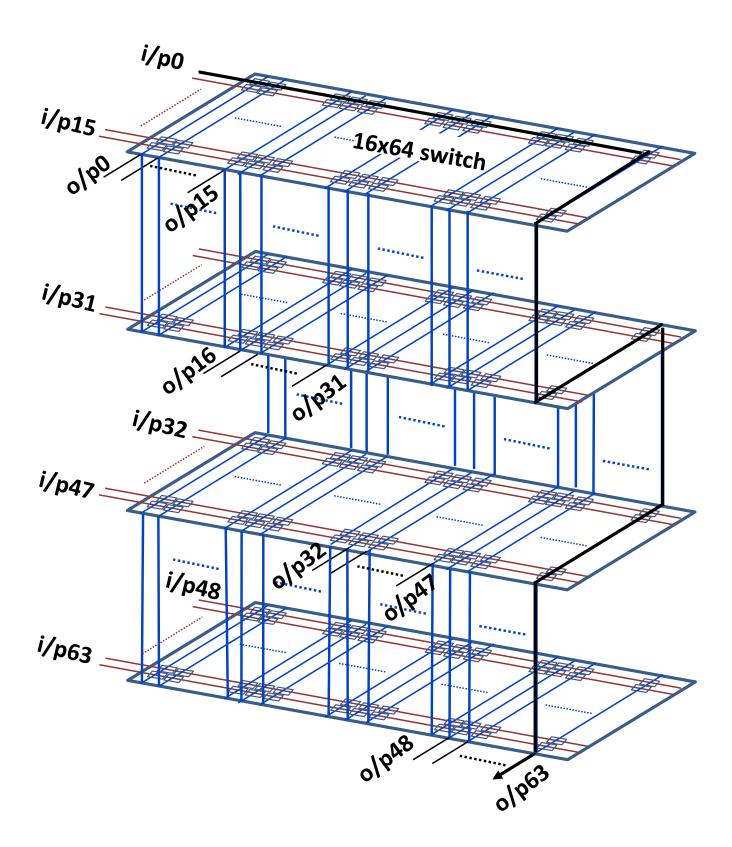

A  $64 \times 64$  2D switch evenly folded across four layers, will result in 16 inputs and 16 outputs on each layer. Since each input still needs to be able to communicate with all outputs, each layer will have a  $16 \times 64$  switch, with 16 outputs connected locally as shown in Figure 2.1. Note that there are still 64 output buses running from layer 1 through layer 4, and that each layer has a cross-point for all 64 outputs. Vertical TSVs go down from each layer to connect the 64

outputs lines between the layers. Essentially, the switch is a single  $64 \times 64$  switch that is folded in the y-dimension across the layers.

In this basic 3D switch design each layer in itself has some benefit in terms of compactness, as instead of 64 nodes each layer has only 16 nodes. This compactness is an inherent benefit of 3D stacking. However, the delay of the switch itself is increased, as shown in Table 2.1, because the wire and device capacitance in the switch remains the same after folding, while the addition of TSVs add to the total capacitance. Also, the number of TSVs required is very high as every output bus wire has to reach every layer.

Overall the folded switch configuration has higher implementation costs in terms of silicon area, delay, and energy over the 2D switch. The folded configuration was proposed and evaluated by Sewell et al. [12], however, their calculations incorrectly identified the number of TSVs required, and switch delay. Table 2.1 reflects the correct calculations. The folded baseline is still a single, radix-64 switch, which requires 64x64 cross-points, unlike the much leaner proposed Hi-Rise switch with hierarchical datapath. The arbitration in a 3D folded switch is identical to that of a 2D Swizzle-Switch, whereas the proposed Hi-Rise switch has a two phase class-based arbitration which composes fairly over inter-layer and intra-layer connections. Our goal is to realize a 3D switch with significantly improved efficiency that takes advantage of the potential that 3D integration affords.

#### 2.3 Hi-Rise 3D switch architecture: Datapath & arbitration

First we focus on the datapath of the proposed Hi-Rise switch followed by details of the arbitration mechanisms in Section 2.3.2.

Figure 2.1 A 64-radix 3D folded switch

Figure 2.2 Conceptual view of Hi-Rise switch

| Table 2.1 Implementation | cost of 2D versus 3D | folded for 64-radix switch |

|--------------------------|----------------------|----------------------------|

|--------------------------|----------------------|----------------------------|

| Design   | Configuration | Area     | Frequency | Energy/transaction | Throughput | #TSVs |

|----------|---------------|----------|-----------|--------------------|------------|-------|

|          |               | $(mm^2)$ | (GHz)     | (pJ/trans)         | (Tbps)     |       |

| 2D       | 64x64         | 0.672    | 1.69      | 71                 | 9.24       | 0     |

| 3DFolded | [16x64]x4     | 0.705    | 1.58      | 73                 | 8.86       | 8192  |

#### **2.3.1 3D switch datapath**

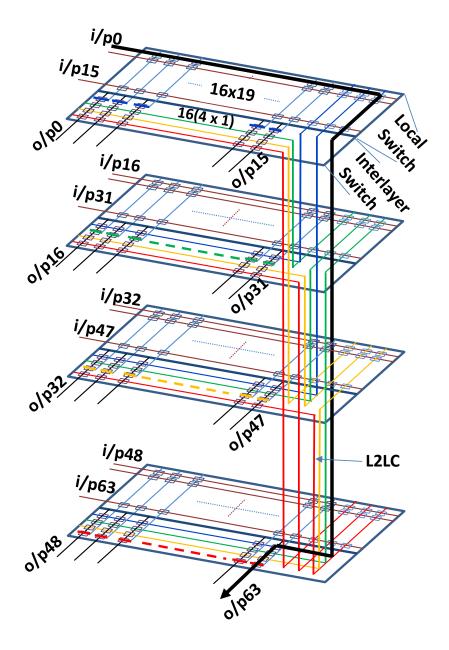

For a switch with radix N, the Hi-Rise switch divides the N inputs and N outputs equally amongst the L layers of stacking. Therefore, at each layer we have N/L inputs and N/L outputs. It provides one or more dedicated vertical layer-to-layer channels (L2LC) from each layer to all other L - 1 layers, as shown in Figure 2.2.

To create a fully connected switch, each input on any layer must be able to arbitrate for, and transmit data to all outputs i.e. outputs on the same layer, and also outputs on every other layer. For this, each layer has two blocks, as shown in Figure 2.3. The first block on a layer, referred to as the local switch, allows inputs to arbitrate for both local intermediate outputs on its layer, and outgoing vertical L2LCs to reach other layers. The second block, the inter-layer switch, is made up of several sub-blocks. Each inter-layer switch sub-block arbitrates between one particular incoming local intermediate output, and all the incoming vertical L2LCs from other layers, and forms the connection to one final output.

We define channel multiplicity as the number of L2LCs between any two layers, which we denote by the variable 'c'. The local switch, has N/L inputs, and both intermediate outputs (N/L) and vertical L2LC outputs (c·(L-1)). The local switch handles requests from all N/L inputs on a layer, and routes them to the desired layer, which may also be the current layer. The inter-layer switch on a layer has N/L sub-blocks. Each sub-block can connect a unique output to either one of the (c·(L - 1)) vertical channels coming in from other layers or to the unique intermediate output from the local switch on its own layer.

As an example, a 64-radix switch spread across 4 layers of silicon, will have 16 inputs and 16 outputs on each layer for the proposed 3D configuration. If c = 1, i.e. there is only one L2LC between any two layers, as shown in Figure 2.2, then the local switch is a 16×19 switch and the inter-layer switch has 16 sub-blocks of  $4 \times 1$ . In the inter-layer switch each final output can choose from 4 inputs—the three incoming L2LCs from the other three layers or the intermediate output bus from the local switch.

Figure 2.3 One Layer of a generic NxN L-layered Hi-Rise with Channel Multiplicity of 'c'

Suppose input 0 from layer 1 (L1) wants to communicate to output 63 on layer 4 (L4). Input 0 has to first win the dedicated L2LC from L1 to L4, by competing against all inputs from its own layer (L1) that want to communicate to L4. This arbitration happens on the local  $16 \times 19$  switch on L1. Upon winning this L2LC, input 0 gets access to the inter-layer switch on L4. It has to then contend against similar winners from L2 and L3 wanting to communicate with output 63, and also the local contender from within L4 on intermediate output 63. Once the connection has been setup, input 0 can transmit flits across the layer to output 63, using the L2LC.

In the previous example configuration, there was only one vertical L2LC between any two layers. This L2LC is required to service any request from the inputs on L1 to the outputs on L4. In the absence of a strong spatial locality the vertical L2LCs can limit inter-layer traffic, and become bottlenecks. This problem can be solved by increasing the channel multiplicity 'c'. However, the addition of more L2LCs, leads to increased size of both the local switch and the inter-layer switch. The outputs on the local switch grow by L-1 for every additional channel. The number of inputs on the inter-layer switch also grows similarly by L - 1. For the previous 64-radix example, a switch with c = 4 will have a  $16 \times 28$  local switch, and 16 sub-blocks of  $13 \times 1$  on the inter-layer switch. For channel multiplicity greater than one, rules are needed to allocate inputs to L2LCs. We discuss below a few possible channel allocation policies.

• Input binned: The inputs on a layer are given a fixed, uniform allocation to the L2LCs. In this case, in N radix with L layers and a channel multiplicity of c, each L2LC will service request from N/(L×c) pre-assigned inputs. These inputs are selected in an interleaved fashion to reduce spatial locality dependence.

• **Output binned:** Output binned is similar to input binning, except it is based on the output.

• **Priority based:** The above two methods of channel allocation may lead to under utilization of the critical vertical L2LCs under certain adversarial traffic as the assignments are fixed. A more efficient utilization can be done by using a priority mux to choose between all N/L

23

inputs. However this method incurs higher delay because arbitration across L2LCs is now serialized.

#### **2.3.2 3D switch arbitration**

In this section we discuss the arbitration mechanisms employed for the proposed Hi-Rise switch architecture. Both the local switch and the sub-blocks of the inter-layer switch can have different arbitration schemes that trade overall throughput and design complexity for fairness. The motivation of these schemes is to get as close as possible to the fairness of a 2D flat switch using a Least Recently Granted (LRG) scheme.

1) Baseline Layer-to-Layer (L-2-L) priority: This approach applies a simple, independent LRG policy on both the switches on a layer. For a 64-radix, 4-layered switch, the local switch has 16 inputs. The local switch thus maintains a 16-bit LRG priority vector at each cross-point, to arbitrate only between the local inputs to win a local intermediate output channel or an L2LC. Each sub-block on the inter-layer switch will get as inputs, the L2LCs from each of the other three layers as well as an intermediate output on its layer; hence it only needs a small priority vector. For a 4 layer switch with channel multiplicity of one, a 4:1 LRG arbitration is required on each of the inter-layer sub-blocks. The inter-layer switch follows the standard procedure; its priority is updated after every arbitration cycle. The priorities are updated at the local-switch only if it wins the final output. The local switch priority update is triggered by the winner at the inter-layer switch, and is back-propagated to the winner's local switch. This ensures that an input request always gets serviced, as its priority will rise on the inter-layer switch in subsequent arbitrations while remaining at the same priority on the local switch, thus, avoiding the possibility of starvation.

2) Unfairness with baseline L-2-L LRG priority: The baseline arbitration performs well for uniform random traffic. But, as the traffic requests to a particular output becomes more biased from a particular layer, the latency to service requests can become long.

Figure 2.4 Baseline Layer-to-Layer (L-2-L LRG) example.

We will illustrate this with the following example: a 1-channel 4-layer 64-radix configuration where 4 inputs, {3, 7, 11, 15} from the first layer (L1), and one input, {20} from the second layer (L2), are all requesting output 63 on layer four (L4). As shown in Figure 2.4, all four inputs requesting from L1 use the same L2LC going from L1 to L4, denoted as  $C_{1,4}$ . The four inputs compete with each other during arbitration at L1's local switch. On the other hand, input 20 is the only requester from L2, thus it always wins the local arbitration on its layer for  $C_{2,4}$ . At the sub-block of the inter-layer switch on L4 belonging to output 63, the winners of the local switch arbitrations compete for the final output.

Figure 2.4 walks through four cycles of arbitration for this example. The LRG priorities decrease from top to bottom. In arbitration cycle 1, input 15 wins  $C_{1,4}$  on the L1 local switch. Input 20, which is the lone contender for  $C_{2,4}$ , wins on the L2 local switch. The two local winners contend on the inter-layer switch of L4 where output 63 is being arbitrated. Input 15 wins as  $C_{1,4}$  has higher priority than  $C_{2,4}$ . This is followed by an LRG update at both the sub-block of the inter-layer switch L4, and at the local switch on L1.

In the subsequent arbitration cycle, input 11 and input 20 contend but input 20 wins, as  $C_{2,4}$  now has higher priority than  $C_{1,4}$ . The LRG of  $C_{1,4}$  remains unchanged as it did not win at the inter-layer switch. Thus, in the next arbitration cycle input 11 again gets to contend and wins against input20. The pattern continues, with one input amongst the four contenders on L1 winning, followed by the only contender from L2. The connection formed over time at output 63 is {15, 20, 11, 20, 7, 20, 3, 20, 15, 20 ...}. This pattern shows that the layer with the fewest number of contenders is able to access the output more frequently and the arbitration is unfair. In a 2D flat switch with LRG the output patter would be {20, 15, 11, 7, 3, 20, 15 ...}. The

observation is that the baseline L-2-L LRG arbitration will be unfair, whenever multiple L2LCs contending for a single output have disparate number of requestors.

3) Weighted LRG priority: To resolve the unfairness problem, the arbitration policy in the sub-blocks of the inter-layer switch needs to be modified. Weighted LRG (WLRG) arbitration scheme is a possible solution and is based on the intuition that L2LCs with higher traffic need to have higher priority. This can be achieved by freezing the LRG priorities for multiple cycles on the inter-layer switch sub-block when an L2LC has more than one requestor. The proportion of arbitration cycles for which the LRG is held, the weights, is determined by the number of requestors the L2LC represents.

Weights are generated by the local switch by counting the number of requestors. Weight information is then transmitted from the local switch to the inter-layer switch along with the request vector, and stored in a counter.

Calculating the number of requestors, involves counting the number of parallel requestors for an L2LC, which is hard to implement in hardware in a single-cycle. It makes the arbitration phase much longer, and hence slows down the cycle time for WLRG considerably. Furthermore, for a 3D switch the WLRG scheme becomes prohibitive due to the large amount of information (weights) that needs to be transmitted from the local switch to the interlayer switch over the L2LC.

4) Class-based Least Recently Granted (CLRG) priority: To improve the fairness over the baseline L-2-L LRG without having to compute and transmit weights to the inter-layer switch, CLRG priority scheme is proposed.

In this scheme, at the inter-layer switch a counter is maintained for each input-output pair. By keeping track of all inputs (across all layers) at the inter-layer sub-block cross-points,

27

the switch can be made fair. This counter tracks the number of times the specific primary input won the arbitration for a particular final output. The arbitration scheme at the inter-layer switch uses this count as a coarse priority, dividing the inputs into different subsets called classes. A bigger count value for an input signifies that the input has had a larger share of the bandwidth for this output, and it is relegated to a lower priority class. The inter-layer switch thus allows the contender with the least count to win. However, if input contenders belong to the same class, CLRG uses layer-to-layer LRG for tie-breaking.

To keep the counter based arbitration logic small, and to avoid cases where bursty traffic penalizes an input for a long time after the burst, the counter is kept short. The number of classes (counter length) required is a heuristic that needs to be tuned. Whenever any counter saturates in a sub-block on the inter-layer switch, all 64 input counters for that sub-block are divided by 2. This maintains the relative class ordering between inputs.

Revisiting the 1-channel example, the counters of all the inputs will be initialized to 0, placing them in the highest priority class 'P0' as shown in Figure 2.5. In arbitration cycle one, input 20 is the only contender from L2's local switch, and hence wins  $C_{2,4}$  (the L2LC to layer L4). The LRG at L1's local switch has input 15 as the highest priority requesting input, and hence input 15 wins the arbitration for $C_{1,4}$ . As both input 20 and input 15 are in priority class P0, LRG is used to tie-break. Input 20 wins, as  $C_{2,4}$  has higher LRG priority than  $C_{1,4}$ . On winning the arbitration, input 20 increments its counter and moves to the lower priority classP1. In arbitration cycle 2 input 15 again contends against input 20. This time input 15 has class P0 and input 20 has class P1, therefore the switch employs class-based priority to make input 15 the winner. Even though LRG is not used for this arbitration cycle, it is still updated.

In arbitration cycle three, input 11 and input 20 contend and input 11 wins by virtue of its class, even though input 20 has a higher LRG priority. This is followed by input 7and input 3 winning against input 20 as they are in class P0, while 20 is in P1. Now all requesting inputs have a count of 1, i.e., all are in class P1. In arbitration cycle 6, input 20 wins again on the basis of LRG tie-breaking. The sequence of winners for the class based arbitration will be {20, 15, 11, 7, 3, 20, ...}.

This is similar to the pattern that will be followed in a single flat 2D LRG switch. Therefore, this scheme is able to resolve the fairness issue of the baseline scheme and also has an efficient single cycle hardware implementation, as we will see in the next section.

## **2.4 Implementation**

To design a high-radix switch with area-energy efficiency, the local and inter-layer subblocks are designed similar to a Swizzle-Switch. Swizzle-Switch is implemented by tiling together cross-points. This section details the cross-point design for both the local switch, and the inter-layer sub-blocks. It also details how we integrate the proposed CLRG logic within a crosspoint.

#### 2.4.1 Basic cross-point design

Recall, a cross-point connects an input to an output port and each cross-point contains both the connectivity and the arbitration logic. A 2D switch of radix N contains  $N \times N$  crosspoints, where each cross-point has a N-bit priority vector. The proposed Hi-Rise switch has three types of cross-points, intermediate output cross-points on the local switch, L2LC output crosspoints on the local switch, and cross-points on the inter-layer sub-blocks.

Figure 2.5 Class-based Least Recently Granted (CLRG) arbitration example.

The underlying circuit for all three types of cross-points is similar to that of a 2Dswitch. The circuit schematic for the first type of cross-point, the intermediate output cross-point, is shown in Figure 2.6. The only difference from a 2D switch cross-point is that it has a N/L-bit priority vector, and two extra output bit-lines to transmit the request and the release signals to the inter-layer switch.

The second type of cross-point, L2LC output cross-point, builds upon the intermediate output cross-point. The L2LC cross-point differs from the intermediate output cross-point in two respects. First, the priority vector size is N/L in the intermediate output cross-point, whereas, it is only (N/(L \*c)) for the input binned L2LC cross-point. Second, the L2LCcross-point transmits the request vector of the input to the inter-layer switch during the arbitration phase, by setting high the L2LC wire with the requested output's index. This is because the L2LC output can request any of the N/L outputs on the destination inter-layer switch. On the other hand, the local intermediate output is dedicated to a single final output on the inter-layer switch.

The third type of cross-point, inter-layer sub-block cross-point, is discussed in the next section.

#### 2.4.2 Arbitration specific cross-point design

The inter-layer sub-block cross-point structure is dependent on the arbitration scheme employed. For the baseline L-2-L LRG, the inter-layer cross-point is very similar to the basic 2D cross-point with only the priority vector size changed. Below we discuss the implementation of the Class-based LRG cross-point.

CLRG cross-point design: The CLRG technique does not require any additional logic in the local switch cross-points. However, the inter-layer cross-point is modified to enable the classbased scheme.

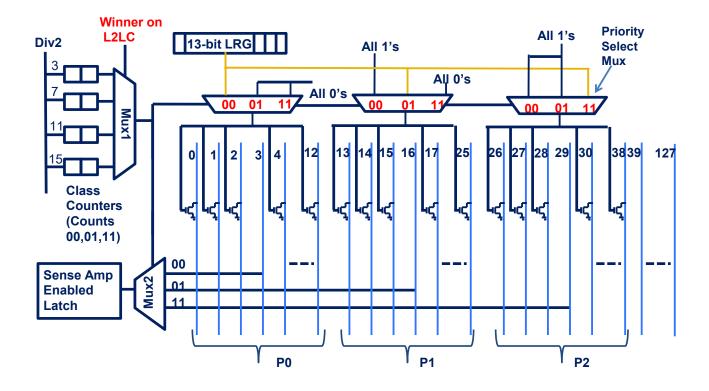

Figure 2.7 shows a single cross-point within an inter-layer switch for an input binned 4channel 4-layer 64-radix configuration. This configuration has 13 cross-points (corresponding to 12 L2LCs and a local input) in a sub-block.

31

Figure 2.6 Circuit schematic of local intermediate output cross-point

Each cross-point provides connectivity for an L2LC, which in turn is associated with four primary inputs. For each of these four primary inputs, a thermometer class counter is placed within the inter-layer switch cross-point. We find empirically that three classes provide reasonable fairness for a 64-radix Hi-Rise switch, hence we use a thermometer counter with the following sequence {00, 01, 11}.

Figure 2.7 Conceptual view of a cross-point at inter-layer sub-block for CLRG arbitration