# **Energy Efficient Pipeline ADCs Using Ring Amplifiers**

by

Yong Lim

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in the University of Michigan 2017

## **Doctoral Committee:**

Professor Michael P. Flynn, Chair Professor David Wehe Associate Professor David Wentzloff Associate Professor Zhengya Zhang

# Yong Lim

yonglim@umich.edu

ORCID iD: 0000-0002-1161-5671

© Yong Lim 2017

#### **ACKNOWLEDGEMENTS**

I would like to express my sincere gratitude to many people who have supported me during my Ph.D. study. My research wouldn't be successful without their support and help. First of all, I would like to thank my advisor Professor Michael P. Flynn for everything he has done for me. Starting from giving me this wonderful opportunity to study and research in this great university, he has guided me not only to be a great analog circuit designer but also has taught me how to be a great teacher, mentor, and boss by showing me great examples of himself while advising me and other students. I would also like to express my gratitude to my committee members Professor David Wehe, Professor David Wentzloff, and Professor Zhengya Zhang for their time and effort for reviewing my proposal and dissertation. They have offered me many valuable suggestions and feedback to better describe my research in this dissertation. In addition, I would like to thank Professor Un-Ku Moon at Oregon State University for his suggestions and supports for my research. He inspired me when he gave us a seminar talk about ring amplifier right after I joined the university and has given me advice and supports whenever I met him at conferences.

I would like to thank my advisor's administrative assistance Frances Doman for her help for my university life. Whenever I had administrative issues in the university, she was there to help me. Without her help, my life in the university wouldn't have been this smooth.

I also thank my EECS 413 (Monolithic Amplifier Circuits) class project group members, Michael Kines, Bowen Li, and Kyuseok Lee. My research topic started from the group project. I developed the idea of self-biased ring amplifier after the class project. If they didn't allow me to choose the ring amplifier as our project topic, I would have done completely different research, and I might have had hard time getting through it.

I was fortunate to study and research in the research group of diverse members. They are all great friends, and research and discussion partners. I thank all of former and current group members who were with me including Jorge Pernillo, Hyo Gyuem Rhew, Hyungil Chae, Jeffrey Fredenburg, Nicholas Collins, Jaehun Jeong, Chunyang Zhai, Batuhan Dayanik, Adam Mendrela, Aramis Alvarez, Fred Buhler, Daniel Weyer, Kyojin Choo, John Bell, Sunmin Jang, Peter Brown, Justin Correll, Rundao Lu, and Boyi Zheng. In particular, I thank Jorge Pernillo for teaching me the basis of ADC testing and measurement, and PCB design right after I joined the group while we were working on Geostar project. Also, I thank Jeffrey Fredenburg for teaching me detailed techniques for designing ADC throughout years. They were like my second advisors. I also want to thank my friends in the student office and many Korean friends in EECS department for making my university life colorful and enjoyable.

I also thank Samsung Electronics for Samsung Fellowship Program, which financially supported my study as an employee education program. Without the program, I wouldn't have dreamt of pursuing Ph.D. degree in the U.S.

Lastly, but most importantly, I want to say thank my beautiful wife Jihyeon Kim for everything she has done for me. She devoted five years of her life just for supporting my study. In addition, I am thankful for my adorable babies Jun and Yuna. Although I have been busy for taking care of them, they keep making me a better person and giving me joys.

# TABLE OF CONTENTS

| ACKNOWLEDGEMENTS                                                           | ii   |

|----------------------------------------------------------------------------|------|

| LIST OF FIGURES                                                            | vii  |

| LIST OF TABLES                                                             | xiii |

| ABSTRACT                                                                   | xiv  |

| CHAPTER 1 Introduction                                                     | 1    |

| 1.1 ADC Figure of Merits and Research Trend                                | 1    |

| 1.2 Pipeline ADC Research Trends                                           | 3    |

| 1.3 Research Contributions and Overview                                    | 7    |

| 1.4 Outline of the Dissertation                                            | 8    |

| CHAPTER 2 Review of Conventional Ring Amplifier                            | 9    |

| 2.1 Stabilized Three-Stage Inverter                                        | 9    |

| 2.2 Stability Requirements                                                 | 12   |

| 2.3 Ring Amplifier Gain Considerations                                     | 16   |

| 2.4 Benefits and Limitations of the Conventional Ring Amplifier            | 17   |

| CHAPTER 3 A Comparator-Less Pipeline ADC Using Self-Biased Ring Amplifiers | 19   |

| 3.1 Self-Biased Ring Amplifier                                             | 19   |

| 3.1.1 Introducing High Threshold Device for the Last Stage                 | 19   |

| 3.1.2 Ring Amplifier without Offset Biasing                                   | 20 |

|-------------------------------------------------------------------------------|----|

| 3.1.3 Dynamic Offset Using Resistor in the Second Stage Inverter              | 21 |

| 3.1.4 Noise and Power Optimization                                            | 23 |

| 3.2 Ring Amplifier Auto-Zero                                                  | 25 |

| 3.2.1 Stability during Auto-Zero                                              | 26 |

| 3.2.2 Improved Auto-Zero Switch to Eliminate Gain Error                       | 28 |

| 3.3 Comparator-Less Sub-ADC Using Ring Amplifier                              | 30 |

| 3.4 ADC Implementation and Measured Results                                   | 33 |

| 3.5 Conclusion                                                                | 42 |

| CHAPTER 4 A Fully-Differential Ring Amplifier Based SAR-Assisted Pipeline ADC | 43 |

| 4.1 Introduction                                                              | 43 |

| 4.2 Fully-Differential Ring Amplifier.                                        | 46 |

| 4.2.1 Conventional Ring Amplifiers Review                                     | 46 |

| 4.2.2 Fully-Differential Ring Amplifier.                                      | 48 |

| 4.3 Proposed ADC Architecture                                                 | 50 |

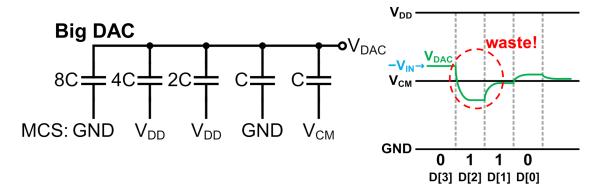

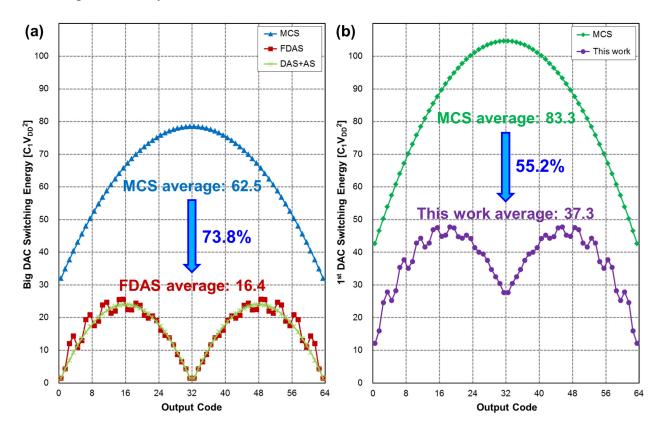

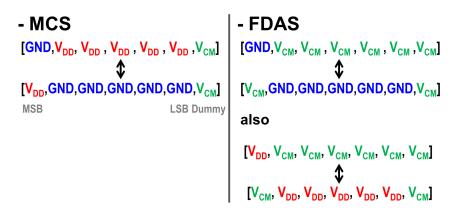

| 4.4 FDAS First-Stage CDAC Switching                                           | 54 |

| 4.4.1 Switching Energy Reduction                                              | 54 |

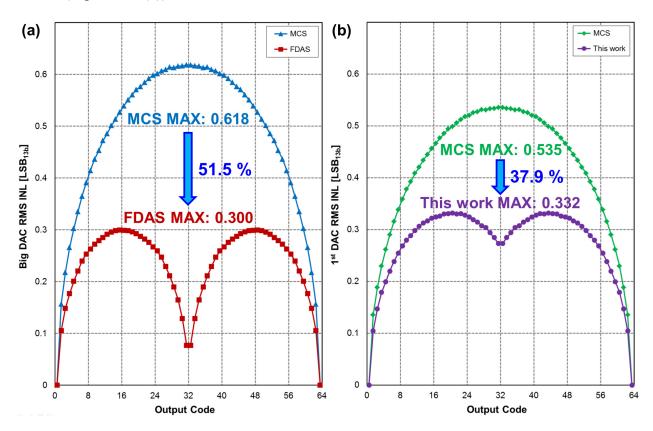

| 4.4.2 Linearity Improvement                                                   | 59 |

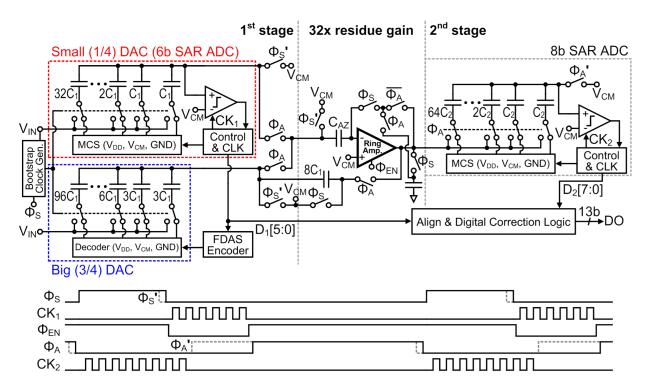

| 4.5 Detailed ADC Implementation                                               | 60 |

| 4.6 Measurement Results                                                       | 63 |

| 4.7 Conclusion                                                        | 71 |

|-----------------------------------------------------------------------|----|

| CHAPTER 5 A Four-Stage Ring Amplifier Based SAR-Assisted Pipeline ADC | 72 |

| 5.1 Introduction                                                      | 72 |

| 5.2 Four-Stage Fully-Differential Ring Amplifier                      | 73 |

| 5.2.1 Problems of a Straightforward Four-Stage Ring Amplifier         | 73 |

| 5.2.2 Auto-Zero with Second-Stage Auxiliary Amplifier                 | 75 |

| 5.2.3 Four-Stage Ring Amplifier                                       | 76 |

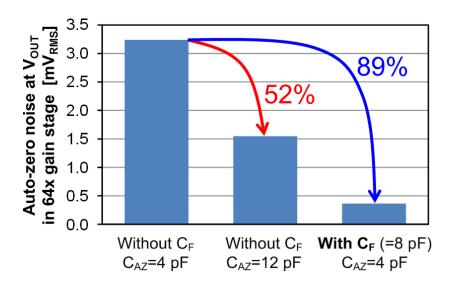

| 5.3 Auto-Zero Noise Reduction                                         | 78 |

| 5.3.1 Review of Auto-Zero                                             | 78 |

| 5.3.2 Auto-Zero Noise Filtering.                                      | 79 |

| 5.4 ADC Implementation                                                | 82 |

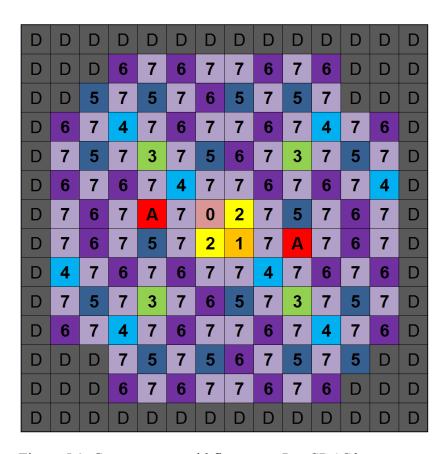

| 5.5 Systematic Mismatch Free SAR CDAC Layout                          | 84 |

| 5.6 Measured Results                                                  | 88 |

| 5.7 Conclusion                                                        | 93 |

| CHAPTER 6 Conclusion                                                  | 94 |

| BIBLOGRAPHY                                                           | 97 |

# LIST OF FIGURES

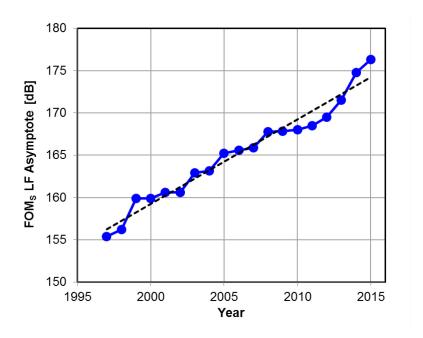

| Figure 1.1. FOM <sub>S</sub> trend over time (low-frequency asymptote). The fit line has a slope of about | 1   |

|-----------------------------------------------------------------------------------------------------------|-----|

| dB per year [6].                                                                                          | . 3 |

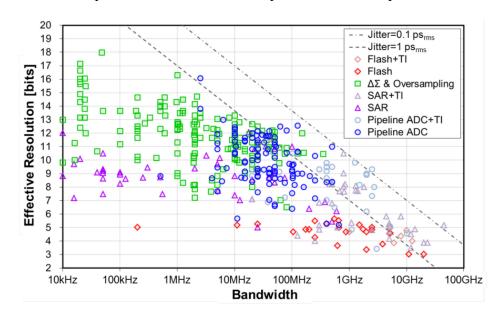

| Figure 1.2. Effective resolution vs. bandwidth ADC survey chart. [5]                                      | 4   |

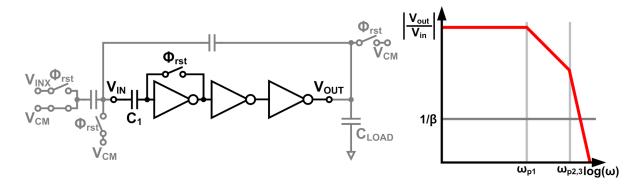

| Figure 2.1. An offset canceled three-stage inverter in a SC feedback amplifier configuration an           | nd  |

| its frequency response.                                                                                   | 9   |

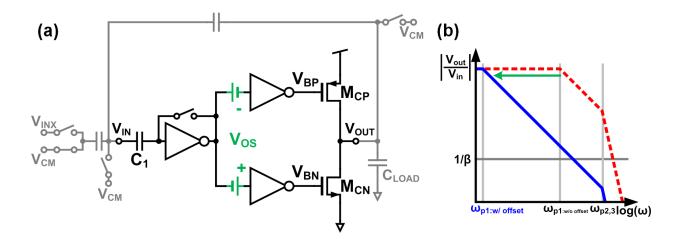

| Figure 2.2. Conceptual ring amplifier in a SC feedback amplifier configuration and its frequence          | су  |

| response                                                                                                  | 10  |

| Figure 2.3. Conventional ring amplifier1                                                                  | 11  |

| Figure 2.4. Simulated transient response of the ring amplifier of Figure 2.2. The ring amplifier          | er  |

| oscillates even with 73° of positive phase margin.                                                        | 12  |

| Figure 2.5. Stabilization of the ring amplifier from the simulation result of Figure 2.4 b                | эу  |

| reducing the first and second stage gain by half.                                                         | 14  |

| Figure 2.6. Stabilization of the ring amplifier from the simulation result of Figure 2.4 b                | эу  |

| reducing the slew rate by half                                                                            | 14  |

| Figure 2.7. Stabilization of the ring amplifier from the simulation result of Figure 2.4 b                | эу  |

| reducing the feedback factor by half                                                                      | 15  |

| Figure 2.8. Stabilization of the ring amplifier from the simulation result of Figure 2.4 b                | эу  |

| increasing the first and second stage bandwidth twice                                                     | 15  |

| Figure 2.9. Simulated ring amplifier small signal gain and the effective ring amplifier gain           |

|--------------------------------------------------------------------------------------------------------|

| calculated from the gain error of a gain stage with various embedded offset voltage                    |

| V <sub>OS</sub>                                                                                        |

| Figure 2.10. The third stage quiescent offset voltage range of the conventional ring amplifier 18      |

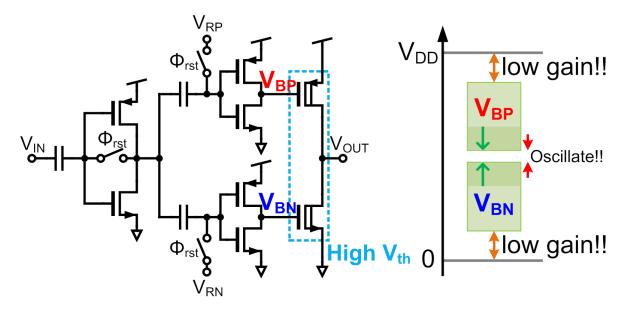

| Figure 3.1. Modified ring amplifier with high $V_{TH}$ last stage and the third stage quiescent offset |

| voltage range of the ring amplifier                                                                    |

| Figure 3.2. Offset-less ring amplifier. This can be stabilized when the sum of the last stage          |

| inverter transistors threshold voltage is higher than the power supply voltage 21                      |

| Figure 3.3. Ring amplifier with dynamic offset using a resistor R <sub>B</sub>                         |

| Figure 3.4. Dynamic offset DC response.                                                                |

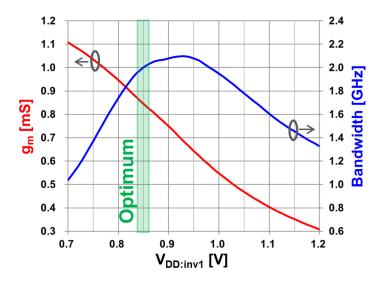

| Figure 3.5. Simulated first stage bandwidth and transconductance versus first stage power supply       |

| voltage (V <sub>DD:inv1</sub> ) with fixed stage current                                               |

| Figure 3.6. Self-biased ring amplifier. 25                                                             |

| Figure 3.7. Auto-zeroed flip-around 1.5b MDAC gain stage using a ring amplifier                        |

| Figure 3.8. Auto-zeroed flip-around 1.5b MDAC gain stage using a ring amplifier with                   |

| stabilization loading capacitor C <sub>LA</sub>                                                        |

| Figure 3.9. Gain error mechanism due to the parasitic capacitance of the auto-zero switch 29           |

| Figure 3.10. An improved auto-zero switch that is free from C <sub>SD</sub> related gain error         |

| Figure 3.11. Modification of the ring amplifier MDAC to use the amplification direction                |

| information                                                                                            |

| Figure 3.12. Amplification direction sampling circuit                                                  |

| Figure 3.13. Simulation of the MDAC gain stage in Figure 3.11 with the amplification direction         |

| sampling circuit in Figure 3.12 for various input voltages                                             |

| Figure 3.14. Amplification direction information to 1.5b sub-ADC result decode logic. $Q_{+}$ | and Q.   |

|-----------------------------------------------------------------------------------------------|----------|

| are from each side of the pseudo-differential ring amplifier MDAC gain stages                 | 33       |

| Figure 3.15. Prototype ADC structure.                                                         | 34       |

| Figure 3.16. Pseudo-differential ring amplified based flip-around sample and hold amplified   | er 35    |

| Figure 3.17. Pseudo-differential ring amplified based MDAC gain stage.                        | 35       |

| Figure 3.18. Die microphotograph of prototype ADC                                             | 37       |

| Figure 3.19. Measured DNL and INL at 10b level, 100 MSPS                                      | 38       |

| Figure 3.20. Measured spectrums for 10.08 MHz and 49.97 MHz inputs sampled at 10              | 0 MS/s   |

| (65536 point FFT)                                                                             | 38       |

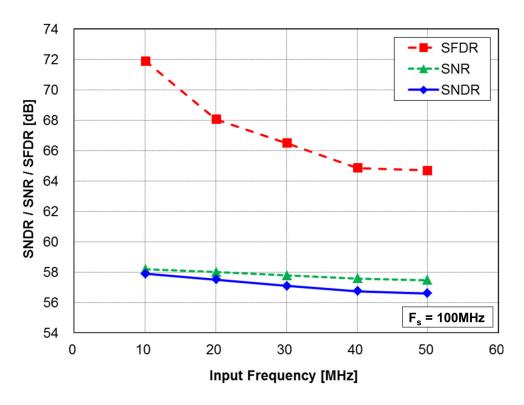

| Figure 3.21. Measured SFDR, SNR, and SNDR versus input frequency                              | 39       |

| Figure 3.22. Measured SNDR versus input amplitude.                                            | 39       |

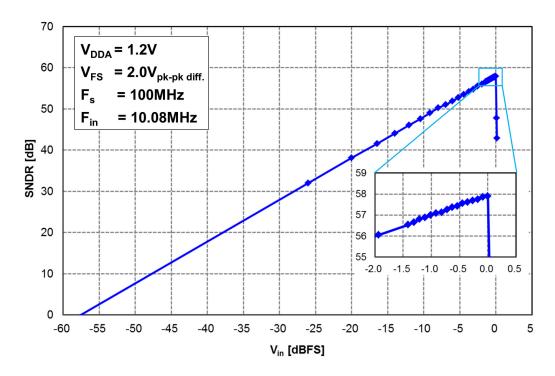

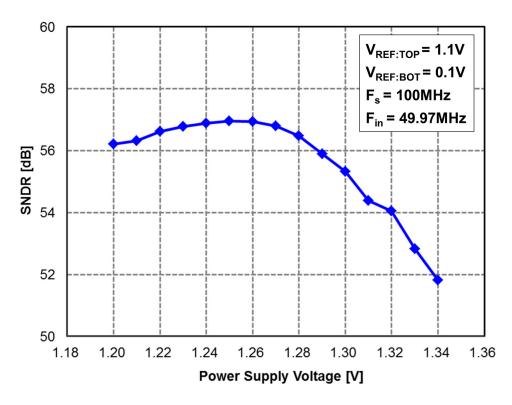

| Figure 3.23. Measured SNDR versus analog power supply.                                        | 40       |

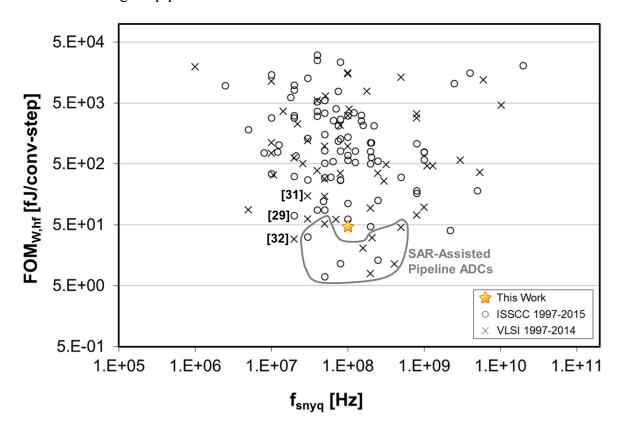

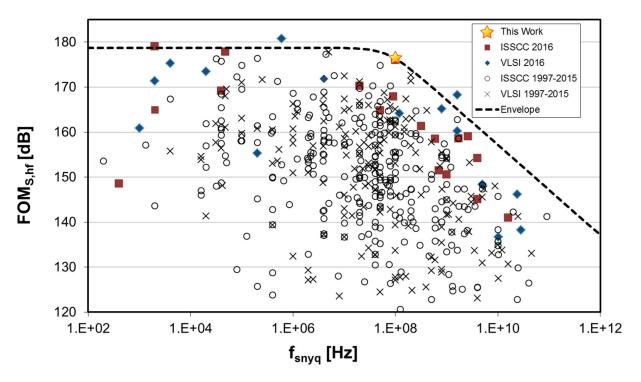

| Figure 3.24. FOM comparison with pipeline ADCs presented at ISSCC 1997-2015 and               | d VLSI   |

| 1997-2014 [5]                                                                                 | 41       |

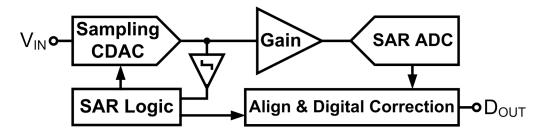

| Figure 4.1. SAR-assisted pipeline ADC block diagram.                                          | 43       |

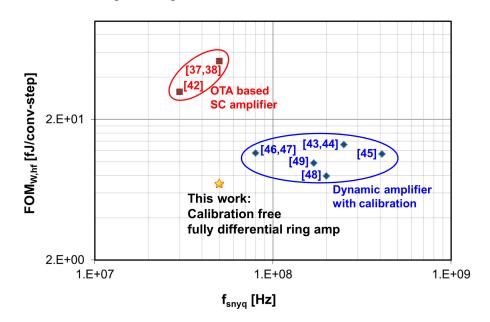

| Figure 4.2. Walden FOM comparison with conventional SAR-assisted pipeline ADCs                | 45       |

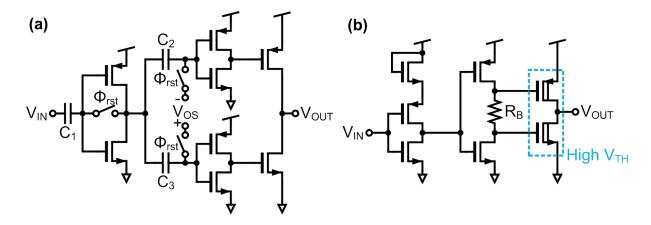

| Figure 4.3. Conventional ring amplifiers. (a) original ring amplifier [30], (b) self-bias     | sed ring |

| amplifier [34], [51]                                                                          | 47       |

| Figure 4.4. Pseudo-differential MDAC gain stage in [34], [51]                                 | 48       |

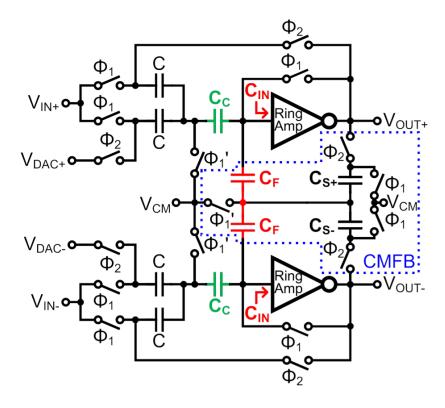

| Figure 4.5. Fully-differential ring amplifier, bias, and CMFB.                                | 49       |

| Figure 4.6. Proposed ADC architecture.                                                        | 51       |

| Figure 4.7. Residue gain stage structure. Actual implementation is fully differential         | 53       |

| Figure 4.8. Simplified ADC timing diagram.                                                    | 53       |

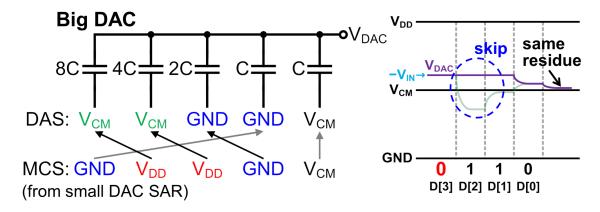

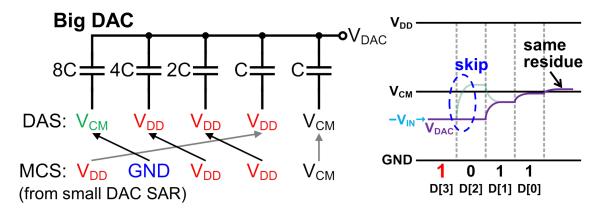

| Figure 4.9. MCS switching 4b <i>Big DAC</i> residue generation example. The bottom plates                 | are   |

|-----------------------------------------------------------------------------------------------------------|-------|

| switched to the final states.                                                                             | 56    |

| Figure 4.10. Detect-and-skip (DAS) switching 4b <i>Big DAC</i> residue generation example when            | ı the |

| MSB (D[3]) of Small DAC SAR is 0. The bottom plates are switched to the f                                 | final |

| states                                                                                                    | 56    |

| Figure 4.11. Detect-and-skip (DAS) switching 4b <i>Big DAC</i> residue generation example when            | ı the |

| MSB (D[3]) of Small DAC SAR is 1. The bottom plates are switched to the f                                 | final |

| states                                                                                                    | 56    |

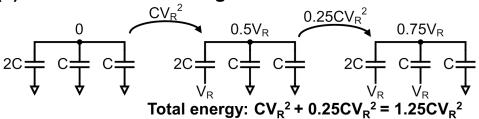

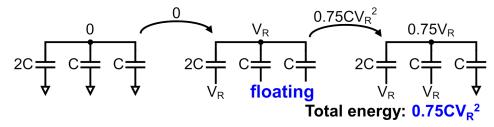

| Figure 4.12. 2b CDAC switching example. (a) successive switching, (b) floated detect-and-                 | skip  |

| switching.                                                                                                | 57    |

| Figure 4.13. Calculated 6b CDAC switching energy comparison. (a) <i>Big DAC</i> switching ene             | rgy,  |

| (b) the first-stage CDAC switching energy.                                                                | 58    |

| Figure 4.14. Worst case INL of 6b CDAC switching for MCS and FDAS                                         | 59    |

| Figure 4.15. Simulated RMS INL due to the first-stage CDAC mismatch with 10k iteration at                 | nd a  |

| one sigma C <sub>1</sub> mismatch of 0.3 %. (a) RMS INL due to Big DAC, (b) RMS INL du                    | ie to |

| the first-stage CDAC                                                                                      | 60    |

| Figure 4.16. Block diagram and timing of the prototype ADC (Actual implementation is f                    | fully |

| differential). $CK_1$ , $CK_2$ , and rising edges of $\Phi_{EN}$ , $\Phi_A$ and $\Phi_A$ ' are asynchrono | usly  |

| generated.                                                                                                | 61    |

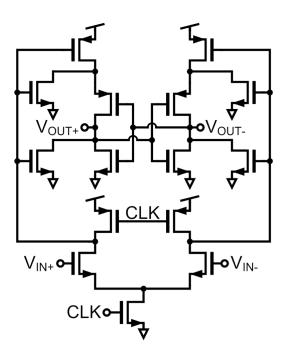

| Figure 4.17. Low noise single phase dynamic latched comparator [58].                                      | 62    |

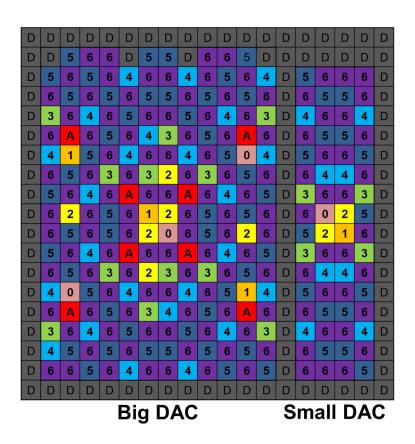

| Figure 4.18. Common centroid first-stage CDAC layout map.                                                 | 62    |

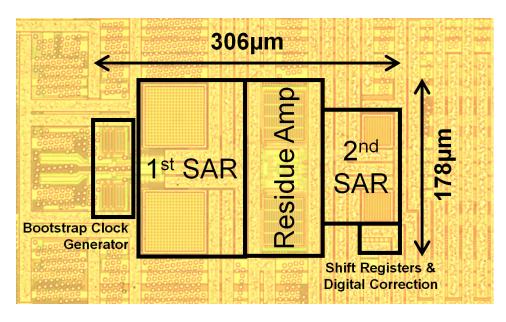

| Figure 4.19. Die microphotograph of prototype ADC                                                         | 64    |

| Figure 4.20. Measured DNL and INL at 50 MSPS (Decimated by 2)                                             | 65    |

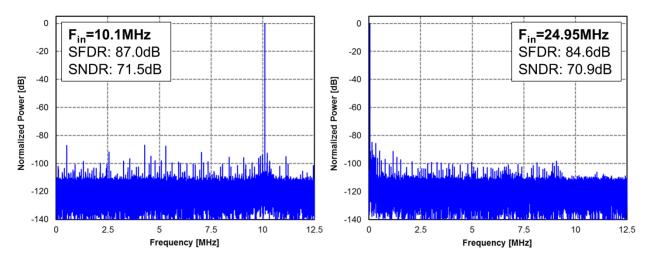

| Figure 4.21. Measured spectrums for 10.1 MHz and 24.95 MHz inputs sampled at 50 MS/s               |

|----------------------------------------------------------------------------------------------------|

| (Decimated by 2, 65536 point FFT)                                                                  |

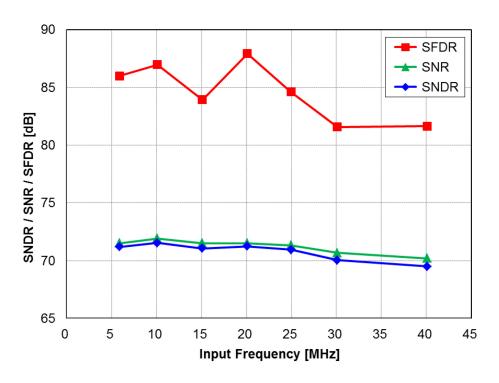

| Figure 4.22. Measured SFDR, SNR, and SNDR versus input frequency (Decimated by 2) 66               |

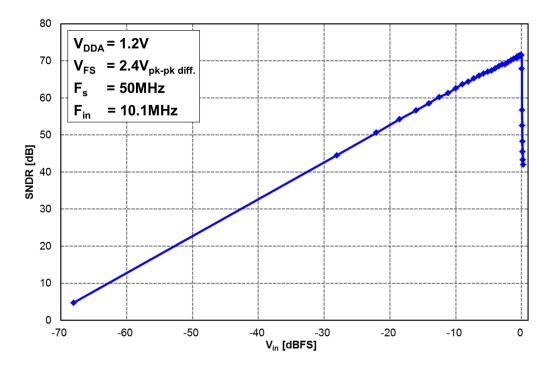

| Figure 4.23. Measured SNDR versus input amplitude (Decimated by 2)                                 |

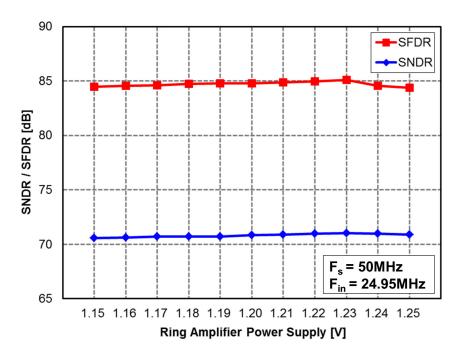

| Figure 4.24. Measured SNDR and SFDR versus ring amplifier power supply (Decimated by 2).           |

|                                                                                                    |

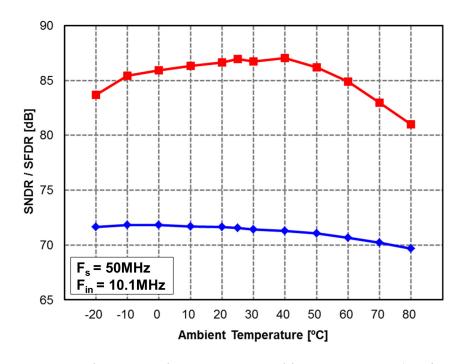

| Figure 4.25. Measured SNDR and SFDR versus ambient temperature (Decimated by 2) 68                 |

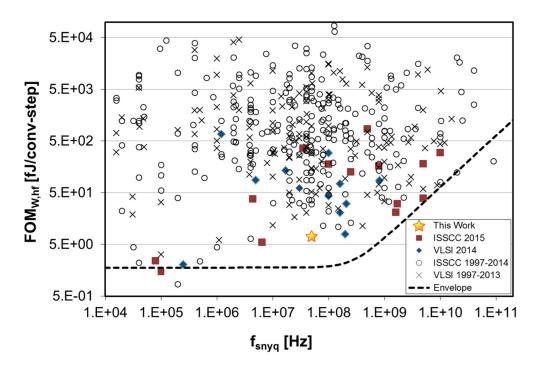

| Figure 4.26. Walden FOM comparison with ADCs presented at ISSCC 1997-2015 and VLSI                 |

| 1997-2014 [5]                                                                                      |

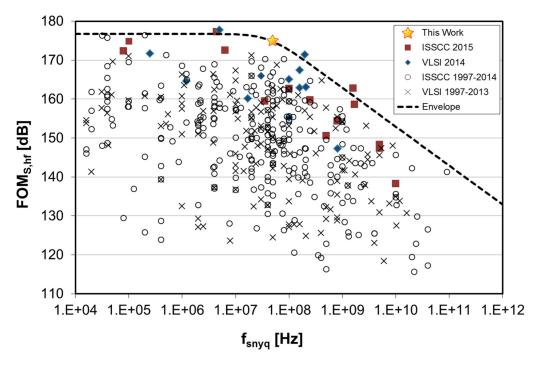

| Figure 4.27. Schreier FOM comparison with ADCs presented at ISSCC 1997-2015 and VLSI               |

| 1997-2014 [5]                                                                                      |

| Figure 5.1. A four-stage ring amplifier in a feedback network.                                     |

| Figure 5.2. A four-stage ring amplifier in a feedback network with an active CMFB                  |

| Figure 5.3. Proposed four-stage ring amplifier with second stage auxiliary amplifier auto-zero. 75 |

| Figure 5.4. Four-stage fully-differential ring amplifier and biasing.                              |

| Figure 5.5. Simplified four-stage ring amplifier in auto-zero configuration and timing diagram.80  |

| Figure 5.6. Auto-zero noise filtering transient noise simulation.                                  |

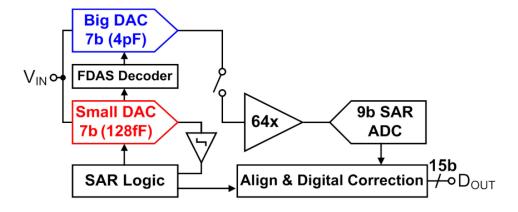

| Figure 5.7. Simplified ADC architecture.                                                           |

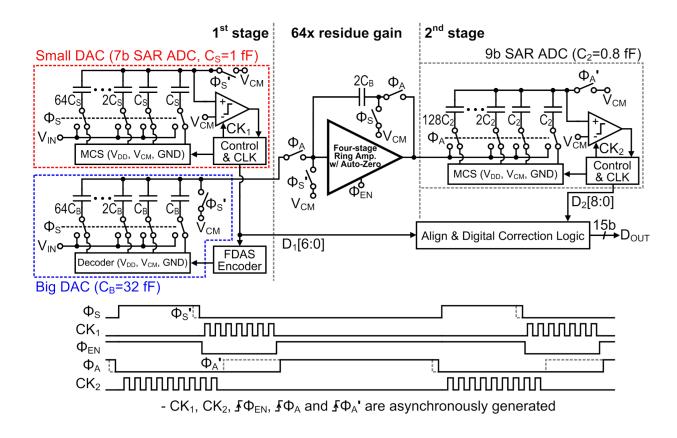

| Figure 5.8. Block diagram and timing of the ADC (Actual implementation is fully differential).     |

| 83                                                                                                 |

| Figure 5.9. Common centroid first-stage <i>Big CDAC</i> layout map                                 |

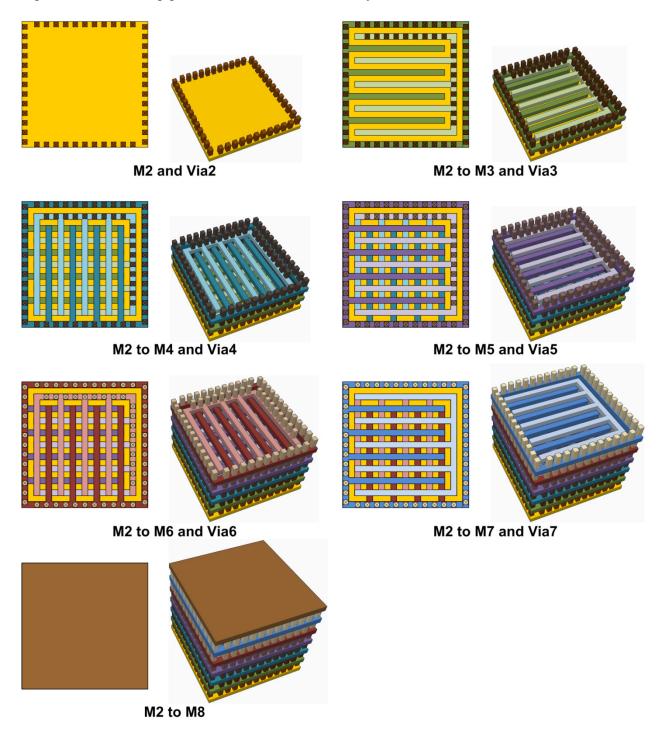

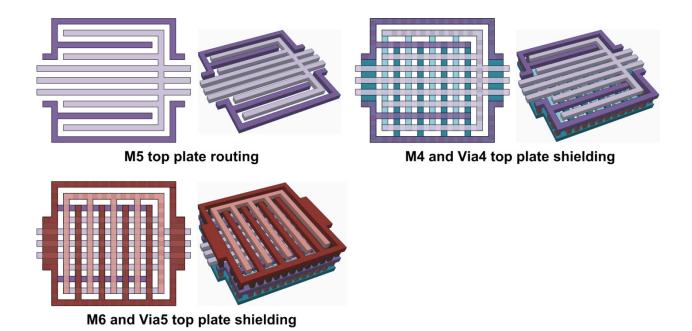

| Figure 5.10. Custom designed encapsulated MOM capacitor top and 3D view                            |

| Figure 5.11. Top plate routing and shielding top and 3D view.                                      |

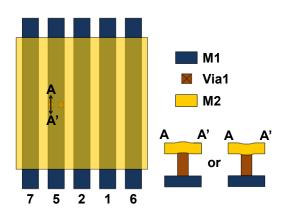

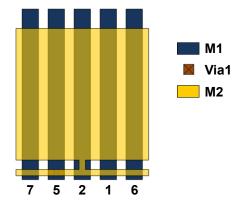

| Figure 5.12. Bottom plate routing with M1 strips and via1 connections under M2 bottom plate.87         |

|--------------------------------------------------------------------------------------------------------|

| Figure 5.13. Bottom plate routing via1 connections under an additional M2 tab                          |

| Figure 5.14. Partial Big CDAC common centroid layout                                                   |

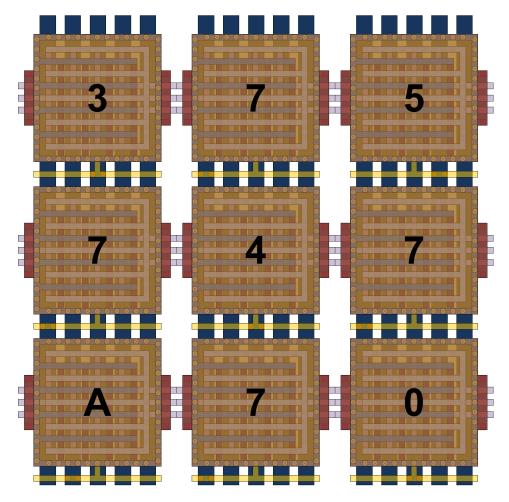

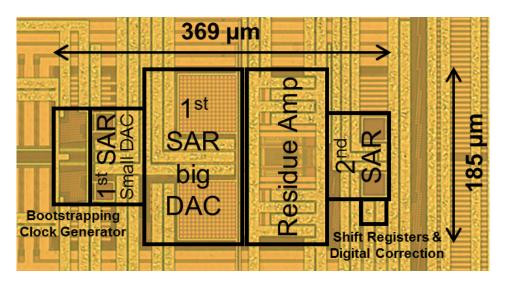

| Figure 5.15. Die microphotograph.                                                                      |

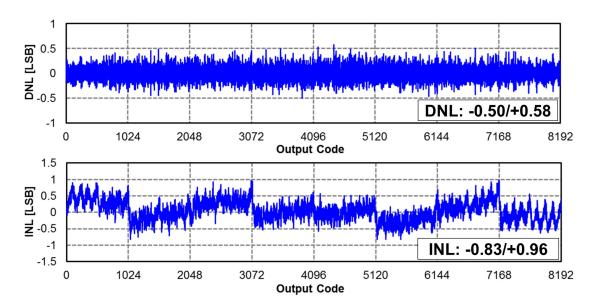

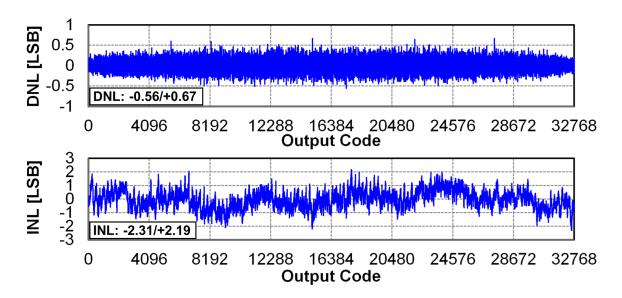

| Figure 5.16. Measured Linearity                                                                        |

| Figure 5.17. Measured spectrums for 5.9 MHz inputs sampled at 100 MS/s (Decimated by 2, 2 <sup>2</sup> |

| point FFT)90                                                                                           |

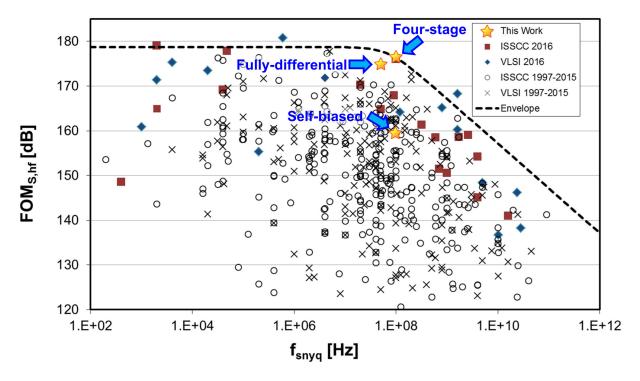

| Figure 5.18. Schreier FOM comparison with ADCs presented at ISSCC 1997-2016 and VLS                    |

| 1997-2016 [5]                                                                                          |

| Figure 6.1. Schreier FOM comparison with ADCs presented at ISSCC 1997-2016 and VLS                     |

| 1997-2016 [5]95                                                                                        |

# LIST OF TABLES

| Table 3-1. ADC performance summary                                                | 37 |

|-----------------------------------------------------------------------------------|----|

| Table 3-2. Performance comparison with the conventional ring amplifier based ADCs | 40 |

| Table 4-1. ADC performance summary                                                | 64 |

| Table 4-2. Performance comparison with the conventional SAR-assisted pipeline ADC | 69 |

| Table 5-1. ADC Performance Summary.                                               | 91 |

| Table 5-2. Performance comparison with the conventional two-stage SAR ADC         | 92 |

#### **ABSTRACT**

Pipeline ADCs require accurate amplification. Traditionally, an operational transconductance amplifier (OTA) configured as a switched-capacitor (SC) amplifier performs such amplification. However, traditional OTAs limit the power efficiency of ADCs since they require high quiescent current for slewing and bandwidth. In addition, it is difficult to design low-voltage OTAs in modern, scaled CMOS. The ring amplifier is an energy efficient and high output swing alternative to an OTA for SC circuits which is basically a three-stage inverter amplifier stabilized in a feedback configuration. However, the conventional ring amplifier requires external biases, which makes the ring amplifier less practical when we consider process, supply voltage, and temperature (PVT) variation. In this dissertation, three types of innovative ring amplifiers are presented and verified with state-of-the-art energy efficient pipeline ADCs. These new ring amplifiers overcome the limitations of the conventional ring amplifier and further improve energy efficiency.

The first topic of this dissertation is a self-biased ring amplifier that makes the ring amplifier more practical and power efficient, while maintaining the benefits of efficient slew-based charging and an almost rail-to-rail output swing. In addition, the ring amplifiers are also used as comparators in the 1.5b sub-ADCs by utilizing the unique characteristics of the ring amplifier. This removes the need for dedicated comparators in sub-ADCs, thus further reducing the power consumption of the ADC. The prototype 10.5b 100 MS/s comparator-less pipeline

ADC with the self-biased ring amplifiers has measured SNDR, SNR and SFDR of 56.6 dB (9.11b), 57.5 dB and 64.7 dB, respectively, and consumes 2.46 mW, which results in Walden Figure-of-Merit (FoM) of 46.1 fJ/conversion·step.

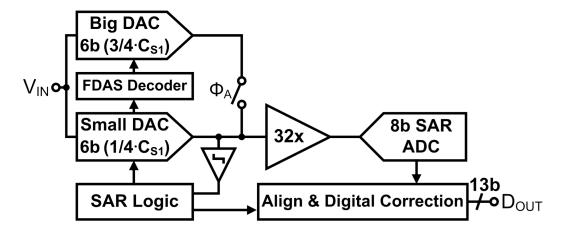

The second topic is a fully-differential ring amplifier, which solves the problems of single-ended ring amplifiers while maintaining the benefits of the single-ended ring amplifiers. This differential ring-amplifier is applied in a 13b 50 MS/s SAR-assisted pipeline ADC. Furthermore, an improved capacitive DAC switching method for the first stage SAR reduces the DAC linearity errors and switching energy. The prototype ADC achieves measured SNDR, SNR and SFDR of 70.9 dB (11.5b), 71.3 dB and 84.6 dB, respectively, and consumes 1 mW. This measured performance is equivalent to Walden and Schreier FoMs of 6.9 fJ/conversion-step and 174.9 dB, respectively.

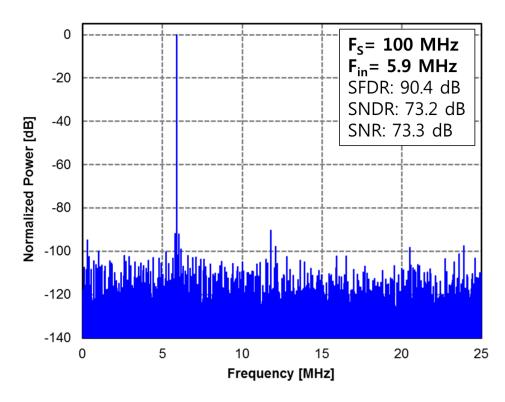

Finally, a four-stage fully-differential ring amplifier improves the small-signal gain to over 90 dB without compromising speed. In addition, a new auto-zero noise filtering method reduces noise without consuming additional power. This is more area efficient than the conventional auto-zero noise folding reduction technique. A systematic mismatch free SAR CDAC layout method is also presented. The prototype 15b 100 MS/s calibration-free SAR-assisted pipeline ADC using the four-stage ring amplifier achieves 73.2 dB SNDR (11.9b) and 90.4 dB SFDR with a 1.1 V supply. It consumes 2.3 mW resulting in Schreier FoM of 176.6 dB.

## **CHAPTER 1**

## Introduction

The analog to digital converter (ADC) is one of the most essential building blocks in electronic systems. Even though signal processing is nowadays mostly done in digital domain thanks to cost effective integration and energy efficient operation from the process scaling, the system still requires ADCs to convert real world analog signals to digital data. In other words, ADCs work as interfaces between the real analog signals such as images, sounds, various sensor (temperature, pressure, etc.) signals, and radio frequency signals for communications to the digital world. As the use of portable electronic devices greatly increases, to enhance battery lifetime, the energy efficiency becomes one of the most important specifications in ADC design. Therefore, researchers have been trying to find ways to improve energy efficiency of ADCs.

#### 1.1 ADC Figure of Merits and Research Trend

In order to fairly compare the energy efficiency of ADCs with different specifications, researchers have come up with figures of merit (FoM). ADC FoMs combine several performance metrics which directly affect the energy efficiency, such as power consumption, conversion speed, and effective resolution, into a single number for simple comparison. One of the most widely used FoMs is the Walden FoM (FoM<sub>W</sub>) [1] which is based on an empirical relationship

from extensive ADC performance survey data. Walden found a trend from his resolution vs. conversion rate survey that for every doubling conversion rate the resolution decreases by one bit. From this finding, he suggested  $FoM_W$  as the follows:

$$FoM_W = \frac{P}{f_{S} \cdot 2^{ENoB}} [\text{Joule/conversion·step}]$$

(1.1)

where, P is power consumption,  $f_S$  is conversion rate, and ENoB is effective number of bits. ENoB is derived from signal to noise and distortion ratio (SNDR) as the following equation.

$$ENoB = \frac{SNDR - 1.76}{6.02}$$

(1.2)

FoM<sub>W</sub> well represents the energy efficiency of low resolution ADCs (< 10b) ADCs. Therefore, it is commonly used for low resolution ADCs. However, for noise limited, moderate-to-high resolution ADCs, FoM<sub>W</sub> does not captures power and noise tradeoff, which typically requires a quadrupling of power to reduce noise voltage by half for every additional bit of effective resolution [2].

The Schreier FoM (FoM<sub>S</sub>), is a widely used FoM, that captures this quadrupling of power per bit tradeoff and formulates it in a logarithmic scale dB [3]. Schreier originally proposed FoM with dynamic range (DR) and bandwidth (BW) of oversampling delta-sigma ADCs as:

$$FoM_{S,DR} = DR (dB) + 10log \left(\frac{BW}{P}\right) [dB].$$

(1.3)

FoM<sub>S,DR</sub> well represents the one bit (6.02 dB) increase in dynamic range with a  $4\times$  increase in power, resulting in the same energy efficiency. The modified FoM<sub>S</sub> [4] is more widely used, which replaces DR with SNDR, and the bandwidth with half of the Nyquist sampling rate ( $f_s$ ), to compare high resolution Nyquist ADCs and oversampling delta-sigma ADCs.

$$FoM_S = SNDR (dB) + 10\log\left(\frac{f_S/2}{P}\right) [dB]$$

(1.4)

ADCs performance surveys based on these FoMs from two top international circuit design conferences (i.e. International Solid-State Circuit Conference, and Symposium on VLSI Circuits) [5], [6] show that energy efficiency is clearly improving. For almost two decades, FoM<sub>S</sub> of leading edge energy efficient ADCs has improved by about 1dB per year (Figure 1.1). In other words, there has been an energy efficiency improvement of 26% per year. This improvement is achieved through research innovation and engineering optimization.

Figure 1.1. FOM<sub>s</sub> trend over time (low-frequency asymptote).

The fit line has a slope of about 1 dB per year [6].

## 1.2 Pipeline ADC Research Trends

Among the various types of ADCs such as flash, pipeline, algorithmic, successive approximation register (SAR), counting or slope, and delta-sigma, the pipeline ADC is a popular architecture since it covers a resolution range from moderate to high resolution (6 to 16b) with wide range of conversion rate (1 MHz to 10 GHz) as shown in the ADC survey chart in Figure 1.2 [5]. This specification range is adequate for many applications including wireless

communications (i.e. CDMA, WCDMA, LTE/4G, and WiFi), digital cameras, camcorders, and ultrasound imaging. Several pipeline ADCs are usually employed in a smart phone. However, the use of operational transconductance amplifiers (OTAs) for switched-capacitor (SC) residue amplification limits energy efficiency since they require high quiescent current for suppressing noise, and satisfying slewing and bandwidth requirements. This dissertation focuses on novel energy efficient OTA replacements for switched-capacitor residue amplifiers.

Figure 1.2. Effective resolution vs. bandwidth ADC survey chart. [5]

In order to improve the energy efficiency of pipeline ADCs, researchers have optimized the power consumption of the OTAs in each pipeline stage [7]. Since the noise requirement of a stage is reduced by gain of the previous stage, the power consumption of the OTAs as well as the size of sampling capacitors in a pipeline ADC can be scaled down along the pipeline. In addition, researchers have also optimized the architecture of pipeline ADCs by reducing the number of OTAs used in a pipeline ADC by increasing stage resolution [8], [9]. Increasing stage resolution, especially increasing the resolution of the first stage also reduces non-linearity caused by capacitor mismatch in subsequent stages capacitive digital to analog converter (CDAC).

However, these optimization techniques have limited ability for improving the energy efficiency because they still require a large power consumption for the first stage OTA and there is limit in the scaling power consumption of OTAs in subsequent stages.

Further energy efficiency improvements in pipeline ADC have been made with the switched OTA technique [10], [11] and OTA sharing technique [12]–[15]. These techniques use the fact that the OTA in a pipeline stage has an idle period during the sampling phase of the stage. The switched OTA technique turns off the OTA during the idle phase. However, this technique has the drawback of reduced operating speed since the OTA requires an additional start-up time during every amplification phase. This reduced operating speed can be alleviated by partially turning off the output stage in a multi-stage OTA [11], but this technique trades off the speed and power consumption of the first stage of the OTA during the idle phase. The OTA sharing technique shares an OTA for two or more stages, by using the fact that the pipeline stages work during alternate clock cycles; when even numbered stages are in amplification phase, odd numbered stages are in sampling phase, and vice versa. In other words, one OTA serves as the residue amplifier in two stages during two different clock phases. OTA sharing reduces the number of OTAs by half. However, since an idle period is needed to cancel offset of the OTA by auto-zeroing [16], these techniques can be applied only if the OTA offset is tolerable.

The above energy efficiency improvement techniques depend on conventional OTA SC circuits. However, designing conventional OTAs is getting more difficult with process scaling, since process scaling tends to be more favorable for digital circuits than analog circuits [17]. Process scaling reduces both supply voltage and intrinsic device gain. This means it is getting harder to achieve sufficiently high gain to meet the accuracy requirement of residue generation. The reduced supply voltage makes it hard to use cascode gain boosting since this significantly

reduces the output dynamic range. Multi-stage OTAs can enhance overall OTA gain, but these further increase power, and also require complex compensation schemes [18].

Several alternative approaches have been proposed to overcome the problems of conventional OTA-based SC circuits, including inverter-based SC circuits [19], [20], and zero-crossing-based circuits [21]–[28]. Inverter-based SC circuits have limited accuracy, due to the limited gain of a single inverter, so the application of the inverter-based SC circuits is usually limited to delta-sigma ADCs, which have a relaxed OTA gain requirement. Zero-crossing-based circuits replace the OTA with a comparator (or zero-crossing detector) and current sources, and have the benefit of slew-based charging. Although, the concept of the zero-crossing-based circuit [21] is simple, the non-idealities of the building blocks and the open loop nature of its operation limit gain accuracy. Various techniques tackle these limitations [24]–[28], but these techniques make the zero-crossing more complex and limit efficiency.

Another attractive alternative is the ring amplifier [29]–[32]. The ring amplifier is essentially a stabilized offset-canceled three-stage inverter which has the benefit of slew-based charging. In addition, ring amplifiers have a near rail-to-rail output swing because the output stage is a simple inverter that operates in sub-threshold in steady state. Ring-amplifier-based SC circuits use feedback just as conventional OTA based SC circuits do, and therefore the accuracy depends on the gain of the ring amplifier. The required gain can be relatively easily achieved from three gain stages. Although, the simple structure of the ring amplifier is attractive, the requirement for external bias voltages limits the practicality when we consider PVT variation.

#### 1.3 Research Contributions and Overview

This research presents three novel ring amplifiers, which improve energy efficiency and practicality compared to conventional ring amplifier. Three prototype pipeline ADCs based on the novel ring amplifiers achieve state-of-the-art energy efficiencies. The first novel ring amplifier is a self-biased ring amplifier which makes the ring amplifier simpler, more energy efficient, and more robust to PVT variation by removing the need for external bias voltages, and improving energy efficiency of the first stage inverter. In addition, a comparator-less sub-ADC exploits a unique characteristic of ring amplifiers.

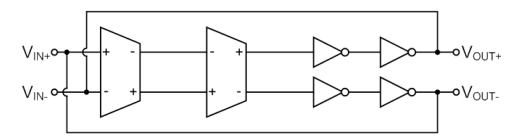

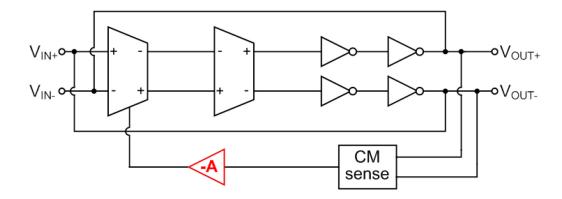

The conventional ring amplifier and the self-biased ring amplifier use a single-ended architecture which suffers from even order harmonics and is susceptible to common mode and supply voltage variation. The use of a pseudo-differential architecture and pseudo-differential common mode feedback (CMFB) can somewhat alleviate these problems; however, the pseudo-differential CMFB reduces effective gain of ring amplifiers. The second novel ring amplifier is a fully-differential ring amplifier which solves the problems of the single-ended and pseudo-differential architectures.

The last novel ring amplifier is a four-stage fully-differential ring amplifier which achieves even higher gain for high resolution pipeline ADCs in deep sub-micron CMOS processes. Furthermore, the noise of a SC residue amplifier is further improved without burning additional power by filtering out the dominant noise source during an auto-zeroing phase.

#### 1.4 Outline of the Dissertation

The rest of this dissertation is organized as follows. Chapter 2 reviews the conventional ring amplifier in depth, and discusses its benefits and limitations. Our approach to the conventional ring amplifier in this chapter is somewhat different to that in the original ring amplifier paper [30] which analyzes it as a zero-crossing based circuit. Chapter 2 analyzes the ring amplifier as a regular amplifier and verifies this analysis with various simulations.

Chapter 3 introduces the self-bias ring amplifier and explains its benefits over the conventional ring amplifier. In addition, an improved auto-zero scheme, and comparator-less sub-ADC technique are also presented. A 10.5b, 100 MS/s prototype pipeline ADC demonstrates the effectiveness of these new techniques.

Chapter 4 introduces the fully-differential ring amplifier and the implementation of a 13b, 50 MS/s SAR-assisted pipeline ADC using it. Furthermore, an improved first-stage SAR CDAC switching technique is presented which improves both the CDAC switching energy efficiency and linearity.

The four-stage fully-differential ring amplifier is presented in Chapter 5, as well as a 15b, 100 MS/s SAR assisted pipeline ADC implementation using it. An auto-zero noise filtering method for the four-stage ring amplifier is also presented for further noise reduction. This does not consume extra power, and is more area efficient than conventional auto-noise reduction techniques. In addition, a systematic mismatch free SAR CDAC layout method is presented. Finally, Chapter 6 summarizes the research contributions.

## **CHAPTER 2**

# **Review of Conventional Ring Amplifier**

## 2.1 Stabilized Three-Stage Inverter

The ring amplifier is an energy efficient and high output swing alternative to an OTA for use in SC amplifiers [29]–[32]. The ring amplifier is based on an offset-canceled three-inverter stage amplifier as shown in Figure 2.1. A capacitor,  $C_1$  stores the voltage difference between a desired common mode voltage  $V_{CM}$  and the trip point voltage of the first inverter. This voltage on  $C_1$  is refreshed during a reset phase. Although a cascade of three inverter stages can achieve high gain, a three-stage inverter amplifier is not stable in a feedback network, such as the SC amplifier shown in Figure 2.1. This is because this amplifier has three poles close in frequency resulting a negative phase margin.

Figure 2.1. An offset canceled three-stage inverter in a SC feedback amplifier configuration and its frequency response.

Figure 2.2. Conceptual ring amplifier in a SC feedback amplifier configuration and its frequency response.

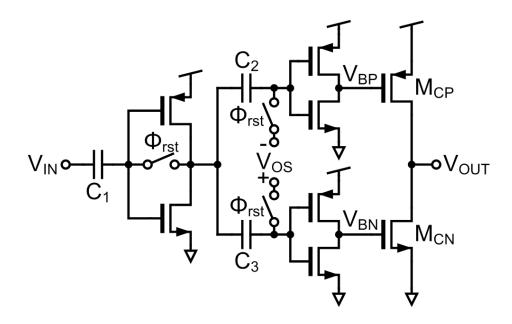

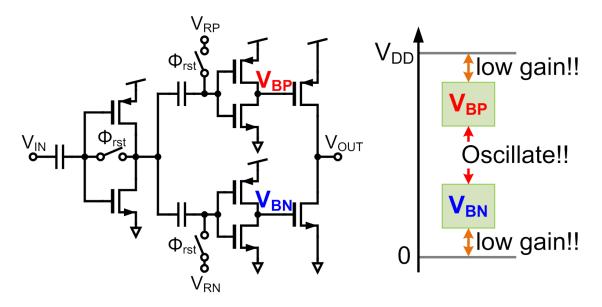

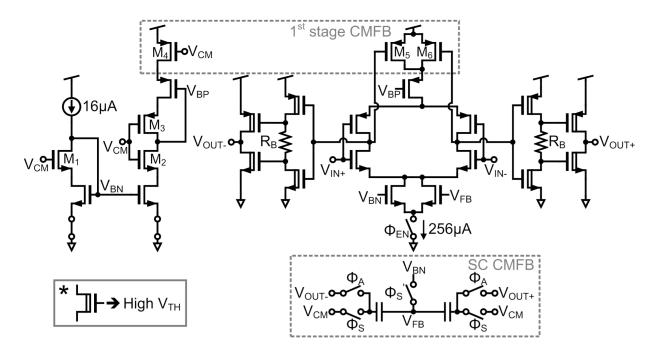

In order to stabilize the three inverter stage amplifier, [29]–[31] split the second stage of the amplifier into two separate inverter gain paths, and apply an offset voltage,  $V_{OS}$ , at the inputs of these two second stage inverters<sup>1</sup> as shown in the conceptual ring amplifier of Figure 2.2(a). One second-stage inverter drives the gate of the PMOS transistor of the third stage ( $V_{BP}$ ) while the other drives the gate of the NMOS transistor ( $V_{BN}$ ). The offset voltages of the two second stage inverters are tuned to bias the third stage transistors,  $M_{CP}$  and  $M_{CN}$ , in sub-threshold as  $V_{IN}$  approaches  $V_{CM}$ :

$$V_{RP} > V_{DD} - |V_{th \cdot P}|, V_{RN} < V_{th \cdot N}$$

(2.1)

In this way, as  $V_{IN}$  approaches  $V_{CM}$ , the output resistance of the third stage dramatically increases, forming a dominant pole that stabilizes the overall amplifier (Figure 2.2(b)). While settling, this ring amplifier has a high output slewing current. However, when it is settled the

10

<sup>&</sup>lt;sup>1</sup> [32] introduces a fine ring amplifier which applies an offset voltage at the output of the second stage inverter, without splitting the second stage inverter, to more precisely control the output stage overdrive voltage. This fine ring amplifier offers a higher gain but a reduced slew rate. The reduced slew rate is overcome by using the ring amplifier in [29]–[31] in parallel with the fine ring amplifier.

current from the output stage, operating in sub-threshold, is negligible. Figure 2.3 shows the conventional, practical implementation of a ring amplifier [29]–[32]. The capacitors,  $C_2$  and  $C_3$ , act as the floating bias offset voltage sources in Figure 2.2. An external bias voltage,  $V_{OS}$ , sets these capacitor voltages during a reset period.

Figure 2.3. Conventional ring amplifier.

## 2.2 Stability Requirements

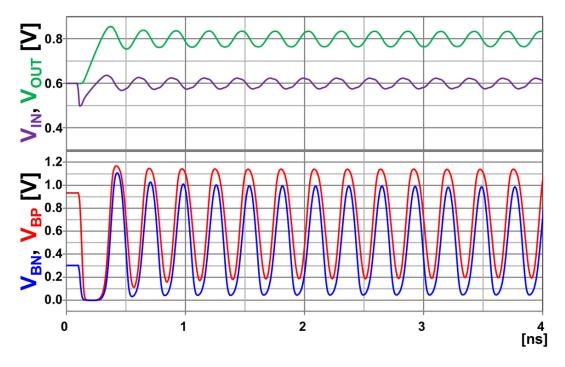

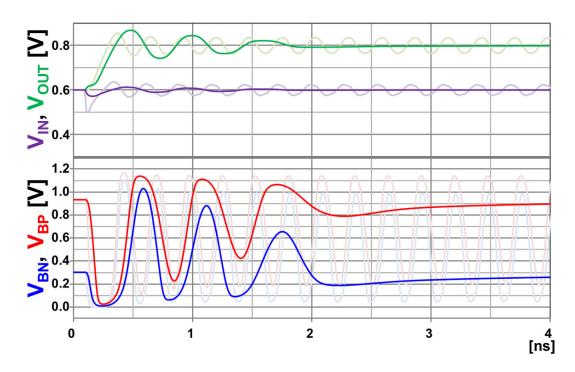

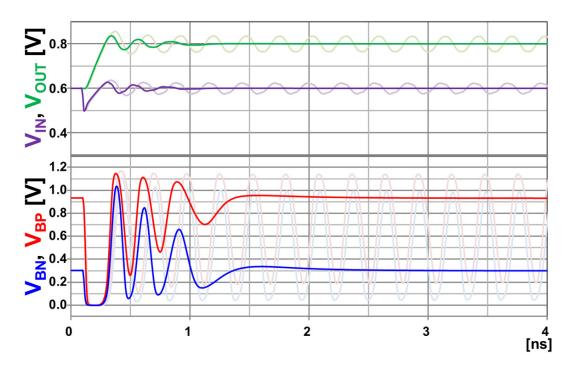

A positive small-signal phase margin is a necessary but insufficient condition for stability of the ring amplifier. In fact, a ring amplifier can become unstable due to large signal effects even if there is a positive phase margin. This is because the current of the last stage transistors changes dramatically around the target settling point, making the large signal behavior of the ring amplifier highly nonlinear. As an example, Figure 2.4 shows the simulated large signal behavior of the ring amplifier in the SC amplifier configuration<sup>2</sup>, shown in Figure 2.2. In this example, the ring amplifier has phase margin of  $73^{\circ}$  when  $V_{IN}$  is at  $V_{CM}$ , but is still unstable.

Figure 2.4. Simulated transient response of the ring amplifier of Figure 2.2.

The ring amplifier oscillates even with 73° of positive phase margin.

12

<sup>&</sup>lt;sup>2</sup> Ideal switches without charge injection or clock feed-through are used in this simulation for clarity.

The simulation shown in Figure 2.4 begins as the amplifier emerges from the reset phase. If the overall SC amplifier input,  $V_{INX}$ , is higher than  $V_{CM}$ , the ring amplifier input,  $V_{IN}$ , initially falls at the beginning of the amplification phase and the gain of the first and the second inverter stages causes the gate voltages,  $V_{BP}$  and  $V_{BN}$ , of the last stage PMOS and NMOS transistors to hit ground. In this condition, the PMOS transistor of the last stage strongly conducts so that the output of the ring amplifier,  $V_{OUT}$ , slews towards  $V_{DD}$  (i.e. 1.2 V in this example). Ideally, this slewing should stop as  $V_{IN}$  reaches  $V_{CM}$  (i.e. 0.6 V), but here slewing continues and  $V_{IN}$  overshoots  $V_{CM}$  because the inverters and the feedback path have a finite response time. This  $V_{IN}$  overshoot causes  $V_{BN}$  and  $V_{BP}$  to reach  $V_{DD}$ , strongly turning on the NMOS of the last stage and causing  $V_{OUT}$  to start slewing down towards ground. If this falling slew rate is similar to the previous rising slew rate, then slewing and overshoot repeat in alternate directions, leading to sustained oscillation.

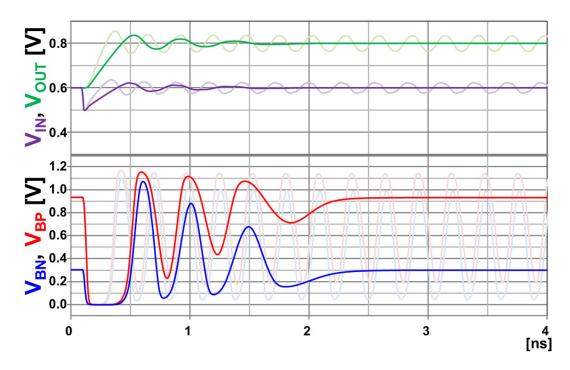

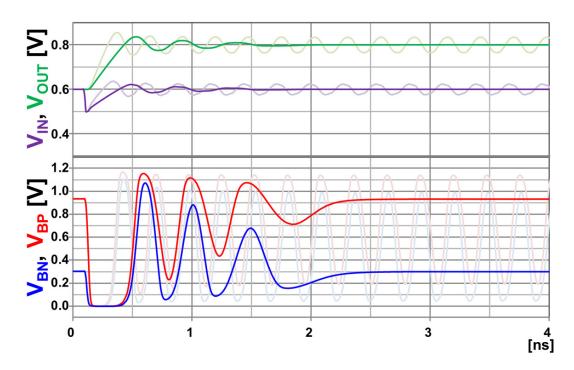

As seen in this example, the ring amplifier can still oscillate even if there is a substantial positive phase margin. In order to prevent this sustained oscillation, we must configure the circuit so that the overshoot decreases each successive oscillation. The overshoot is proportional to the gain of the three stages, the slew rate, the feedback factor, and the response time. Therefore, reducing the gain of the three stages (Figure 2.5), or reducing the slew rate (Figure 2.6), or reducing the feedback factor (Figure 2.7) can reduce overshoot. Reducing the response time by increasing the bandwidth of the first and the second inverters (Figure 2.8) also reduces the overshoot<sup>3</sup>. The gain and the feedback factor are usually determined by the target application, thus this tuning is best done by reducing the slew rate and increasing the first and second inverter bandwidths. Tuning is a tradeoff between the speed needed for the application and the power consumption.

\_

<sup>&</sup>lt;sup>3</sup> These observations agree well the equation (8) in [30].

Figure 2.5. Stabilization of the ring amplifier from the simulation result of Figure 2.4 by reducing the first and second stage gain by half.

Figure 2.6. Stabilization of the ring amplifier from the simulation result of Figure 2.4 by reducing the slew rate by half.

Figure 2.7. Stabilization of the ring amplifier from the simulation result of Figure 2.4 by reducing the feedback factor by half.

Figure 2.8. Stabilization of the ring amplifier from the simulation result of Figure 2.4 by increasing the first and second stage bandwidth twice.

#### 2.3 Ring Amplifier Gain Considerations

The ring amplifier has high gain, thanks to its three stages. One might argue that the dead-zone voltage ( $V_{OS}$  in this chapter) determines the gain of the ring amplifier. Indeed, [30] analyzes the accuracy of the virtual ground (i.e. the inverse of the ring amplifier gain) is defined as  $|V_{OS}/A_1|$ , where  $A_1$  is the gain of the first stage inverter. The dead-zone approximation is based on the assumption that the last stage transistors become ideal on/off current sources. In practice, all three stages contribute to the gain of the ring amplifier because the last stage still conducts sub-threshold current in steady-state condition and acts as inverter having low bandwidth.

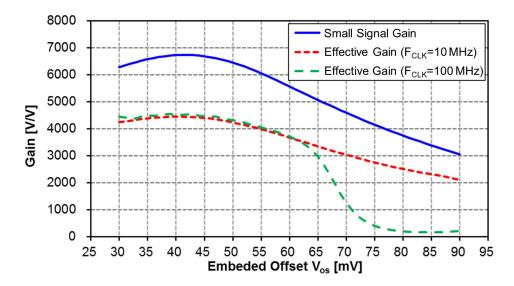

Figure 2.9 plots the simulated ring amplifier small signal gain and effective gain from a SC amplifier configuration versus the embedded offset, V<sub>OS</sub>. The conceptual ring amplifier in Figure 2.2 (with entire three stage offset cancelation) is used for this simulation. The effective ring amplifier gain is back calculated from the gain error of a SC amplifier. The effective gain is simulated at two different clock frequencies of 10 MHz and 100 MHz to separate the insufficient settling time caused gain error from the gain error due to the finite ring amplifier gain.

As shown in Figure 2.9, the effective gain of the ring amplifier tracks the small signal gain of the ring amplifier when there is a sufficient settling time (i.e. with a slow clock frequency, 10 MHz for this simulation). Here, the gain reduction between the small signal gain and the effective gain is caused by capacitive divider formed by the offset storage capacitor,  $C_C$ , and the first stage input capacitance and the common mode feedback capacitor. With a faster clock frequency (100 MHz), the effective gain of the ring amplifier drops steeply as  $V_{OS}$  increases when  $V_{OS}$  is higher than 65 mV. This drop in effective gain is because the bandwidth of the ring amplifier is not sufficient to settle for the given operating frequency, and not because the accuracy is inversely proportional to  $V_{OS}$ . The gain of the ring amplifier falls if  $V_{OS}$  is increased

over 40 mV because the gain of second stage inverter falls as one of the transistors in the second stage inverter starts operating in the triode region.

Figure 2.9. Simulated ring amplifier small signal gain and the effective ring amplifier gain calculated from the gain error of a gain stage with various embedded offset voltage  $V_{OS}$ .

## 2.4 Benefits and Limitations of the Conventional Ring Amplifier

The ring amplifier delivers high gain from its three gain stages without the need for complicated gain enhancement techniques. Furthermore, the ring amplifier can slew very efficiently because the third stage inverter acts as a pair of digital switches during slewing. However, the conventional ring amplifier circuit has drawbacks because it depends on the external offset voltage, Vos. The quiescent voltages of VBP and VBN, when VIN=VCM, must be set within narrow voltage windows as illustrated in Figure 2.10. If the quiescent overdrive voltages of the last stage are set too high then the ring amplifier can oscillate because the output resistance of the third inverter stage is never sufficiently large to create a sufficient phase margin. On the other hand, if the quiescent overdrive voltage is too low, the bandwidth of the last stage is

reduced and the ring amplifier might not settle fully within the given settling time. With a low quiescent overdrive voltage, even if the ring amplifier settles in the given settling time, the second stage inverters operate in the triode region resulting in a low overall three-stage gain<sup>4</sup>. Setting V<sub>OS</sub> for these narrow V<sub>BP</sub> and V<sub>BN</sub> voltage windows is difficult when we consider PVT variation of the second and third stage inverters. Furthermore, the common mode of V<sub>OS</sub> also determines the output common mode voltage of the ring amplifier. The common mode of V<sub>OS</sub> is amplified by gains of the second and third stages to set the output common mode voltage. This is also affected by PVT variation making it difficult to set the output common mode within a certain range. Some of the PVT variation issue can be solved by using on-chip biases that track PVT variation [16]. However we still need to consider the device to device variation which can cause large output common mode variation. The device to device variation is particularly problematic since the ring amplifier uses almost minimum sized transistors [31].

Figure 2.10. The third stage quiescent offset voltage range of the conventional ring amplifier.

\_

<sup>&</sup>lt;sup>4</sup> This low second stage gain can be avoided by applying the offset voltage at the output of the second stage inverter without using two second-stage inverters [32]. However this reduces the offset voltage setting accuracy since the sampled offset leaks through parasitic diodes of the switches because the voltages of offset sampling capacitors exceed the rails during slewing - the amount of leakage depends on slewing time.

## **CHAPTER 3**

# A Comparator-Less Pipeline ADC Using Self-Biased Ring Amplifiers

## 3.1 Self-Biased Ring Amplifier

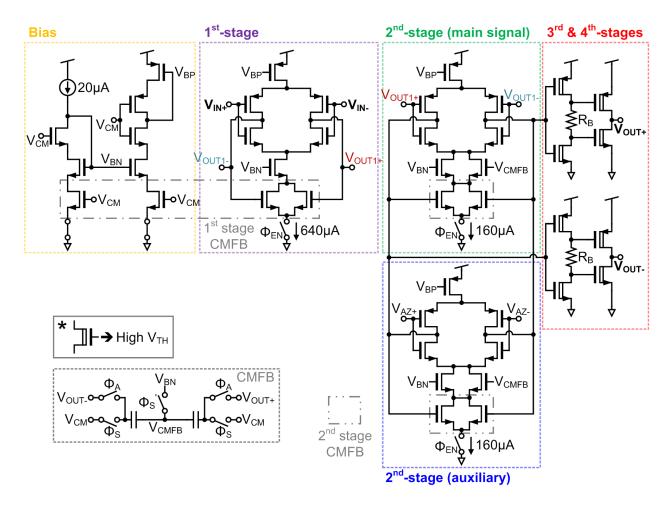

In this section, we introduce the new self-biased ring amplifier and explain its benefits. We adopt high threshold devices for the last stage inverter to extend the stable offset  $(V_{OS})$  range. We also eliminate the external biases and the split second stage inverter. We dynamically apply an offset using a resistor in the second stage to make the ring amplifier more practical and power efficient.

## 3.1.1 Introducing High Threshold Device for the Last Stage

We introduce high threshold devices in the third stage of the ring amplifier to take advantage of their higher output resistance. Because we can get orders of magnitude higher output resistance from the high threshold voltage device inverter<sup>5</sup>, we can extend the  $V_{OS}$  range

<sup>&</sup>lt;sup>5</sup> This also reduces the slewing current of the ring amplifier. However, for same sized last stage transistors, the output resistance in steady state is two to three orders of magnitude higher while the slewing current is reduced by a half to a quarter. Therefore, the use of high threshold voltage devices for the last stage is beneficial although we need to increase the size of the last stage to make the slewing current the same.

(or the range quiescent overdrive voltages  $V_{BP}$  and  $V_{BN}$ ) as illustrated in Figure 3.1. This extended  $V_{OS}$  range increases the robustness of the ring amplifier to PVT variation.

Figure 3.1. Modified ring amplifier with high  $V_{TH}$  last stage and the third stage quiescent offset voltage range of the ring amplifier.

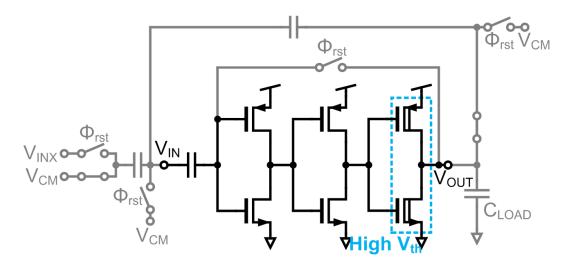

#### 3.1.2 Ring Amplifier without Offset Biasing

Adopting high threshold devices for the last stage allows us to stabilize a three-inverter stage amplifier without the split second stage and offsets, as shown in Figure 3.2. When the sum of threshold voltages of transistors in the third stage inverter is higher than the power supply voltage (i.e.  $V_{TH:N}+|V_{TH:P}| > V_{DD}$ ), then third stage operates in the sub-threshold region. The three-stage inverter is stabilized since the third stage forms a dominant pole due to the significantly higher output resistance from the sub-threshold operation. This simple three-stage ring amplifier has two advantages compared to the conventional ring amplifier. Firstly, the reduced number of second stage inverters, together with the removal of the offset capacitors and the switches, reduces the loading on the first stage, allowing us to reduce the power consumption of the first inverter while maintaining the same first stage bandwidth. Secondly, we can auto-zero

the entire three inverter stages as in Figure 3.2 and this gives us a more stable output common mode even with PVT variation, and the device to device variation. However, this simplified offset-less ring amplifier is not practical because the power supply voltage condition  $(V_{TH:N}+|V_{TH:P}|>V_{DD})$  is not always true.

Figure 3.2. Offset-less ring amplifier. This can be stabilized when the sum of the last stage inverter transistors threshold voltage is higher than the power supply voltage.

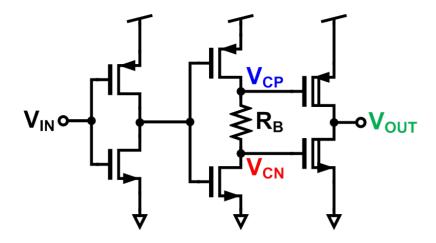

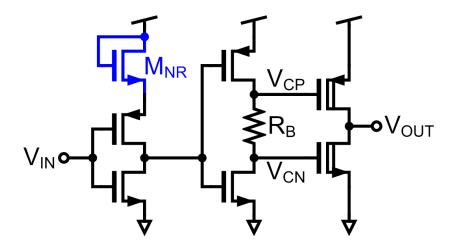

### 3.1.3 Dynamic Offset Using Resistor in the Second Stage Inverter

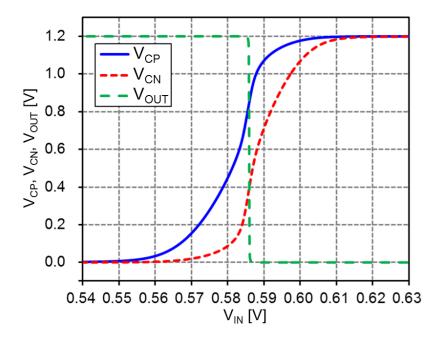

In order to avoid these constraints on the power supply voltage, while keeping the advantages of a single inverter-based second stage without external biases, we embed a polysilicon resistor,  $R_B$ , between the drains of the NMOS and PMOS transistors of the second-stage inverter, as shown in Figure 3.3. The resistor  $R_B$  dynamically applies an offset to gate voltages,  $V_{CP}$  and  $V_{CN}$ , of the third stage inverter transistor thanks to the IR drop due to the inverter short circuit current. There is now a voltage offset between the gates of the last stage PMOS and NMOS transistors when  $V_{in}$  is close to the virtual ground. As we can see in Figure 3.4, the second inverter still drives the last stage rail-to-rail when the ring amplifier input,  $V_{in}$ , is away from the virtual ground. The offset voltage variation caused by the  $R_B$  resistance variation

and the second inverter short circuit current variation is acceptable as long as it is within the stable  $V_{OS}$  range. As explained in sub-section 3.1.1, the acceptable  $V_{OS}$  range is extended by using high threshold device in the last stage. This increases the design margin for offset voltage variation.

Figure 3.3. Ring amplifier with dynamic offset using a resistor  $R_{\rm B}$ .

Figure 3.4. Dynamic offset DC response.

This resistor based dynamic offset ring amplifier has another benefit. Since the offset depends on the short circuit current of the second stage inverter, this offset tracks the power supply voltage. This means the ring amplifier with dynamic offset biasing can operate over a wider  $V_{DD}$  range. The short circuit current of the second-stage inverter can be calculated from the NMOS saturation region square law equation:

$$I_D = \frac{1}{2} \mu_n C_{ox} \frac{W_n}{L_n} \left( \frac{V_{DD}}{2} - V_{TH:N} \right)^2$$

(3.1)

This assumes that the second inverter is balanced so that the trip point of the second inverter is  $V_{DD}/2$ . As shown in equation (3.1), the inverter current increases quadratically as  $V_{DD}$  increases and therefore the voltage across  $R_B$  also increases quadratically. Ideally, the offset voltage should linearly track<sup>6</sup>  $V_{DD}$  to maintain the same overdrive voltage on the last stage transistors regardless of  $V_{DD}$ . Nevertheless, the increase in IR drop with  $V_{DD}$  along with the extended offset range facilitated by the high threshold voltages of the last stage ensures a wide  $V_{DD}$  operating range.

### 3.1.4 Noise and Power Optimization

We optimize the noise and the power consumption of the first stage inverter. The first stage inverter is the dominant noise source of the dynamic offset ring amplifier in Figure 3.3. Although flicker noise is mostly removed by the auto-zeroing [16], thermal noise cannot be cancelled. Since the thermal noise of an inverter is inversely proportional to the  $g_m$  of the inverter, we must increase  $g_m$  to reduce the thermal noise. For a given length and for a fixed gain, the only way to increase the  $g_m$  of an inverter is to increase the width of the inverter. However, increasing the width also increases the power consumption.

\_

<sup>&</sup>lt;sup>6</sup> This can be achieved by using triode mode N/PMOS resistors instead of a poly resistor. However the use of triode mode transistors also increases the loading capacitance of the second stage and therefore also the power consumption of the ring amplifier.

If we also adjust the power supply voltage of the first inverter then we do not have to significantly increase power consumption to reduce the thermal noise. In fact, we can get a higher  $g_m$  for a given quiescent current,  $I_D$ , from an inverter when we reduce the power supply voltage. Since the  $g_m$  of a MOS transistor is  $2I_D/(V_{GS}-V_{TH})$  when we assume strong inversion operation, then assuming the trip point of the inverter is  $V_{DD}/2$ , we get  $g_m/I_D$  of an inverter as:

$$\frac{g_m}{I_D} = \frac{2}{\left(\frac{V_{DD}}{2} - V_{TH:N}\right)} + \frac{2}{\left(\frac{V_{DD}}{2} - |V_{TH:P}|\right)}.$$

(3.2)

Equation (3.2) shows that  $g_m/I_D$  of an inverter increases as we decrease  $V_{DD}$ .

Figure 3.5 shows the simulated  $g_m$  and bandwidth of the first stage inverter at the trip point versus the first stage inverter  $V_{DD}$  ( $V_{DD:inv1}$ ). The short circuit current of the first stage inverter is fixed in this simulation by changing the width of the inverter. We can get a close to maximum bandwidth with about 2.8 times higher  $g_m$  compared with the default power supply (1.2 V) when  $V_{DD:inv1}$  is around 0.85 V. As we see from the simulation, we can get optimum  $g_m$  and bandwidth with a lower  $V_{DD:inv1}$  which allows us to reduce the thermal noise of the first stage inverter without significantly increasing power consumption.

Figure 3.5. Simulated first stage bandwidth and transconductance versus first stage power supply voltage  $(V_{DD:invl})$  with fixed stage current.

Instead of using an external voltage, we lower  $V_{DD:inv1}$  using a diode-connected NMOS  $(M_{NR})$  as shown in Figure 3.6. The diode connected  $M_{NR}$  works as an internal regulator and effectively lowers the power supply voltage of the first stage inverter without additional power consumption. The size of  $M_{NR}$  needs to be large to reduce the regulated voltage variation. Figure 3.6 shows the final structure of the self-biased ring amplifier.

Figure 3.6. Self-biased ring amplifier.

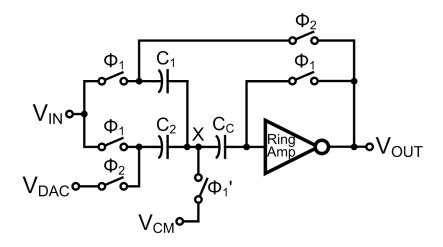

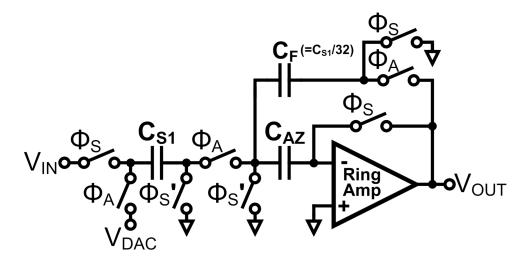

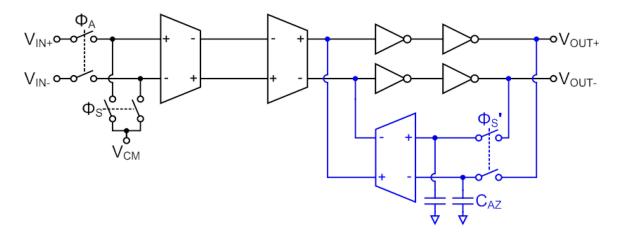

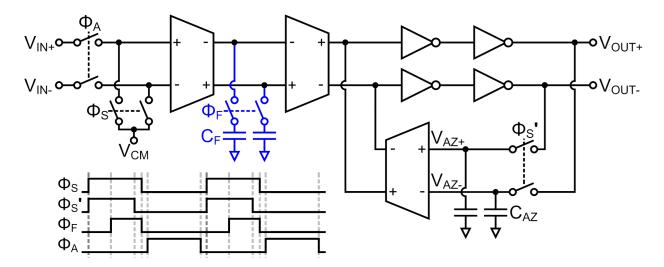

## 3.2 Ring Amplifier Auto-Zero

As discussed in the previous section, unlike the conventional ring amplifier, which only cancels the offset of the first stage, we auto-zero the entire input offset of the self-biased ring amplifier. The auto-zeroing is required to cancel the difference between V<sub>CM</sub> and the input common voltage of the ring amplifier. This also removes the output offset of the ring amplifier, unlike the conventional ring amplifiers [29]–[32], and this helps maximize the usable dynamic range of the output swing. In this section, we explain the problems of auto-zeroing the ring amplifier in a flip-around 1.5b multiplying digital to analog converter (MDAC) gain stage (Figure 3.7), and introduce a new scheme that overcomes these problems.

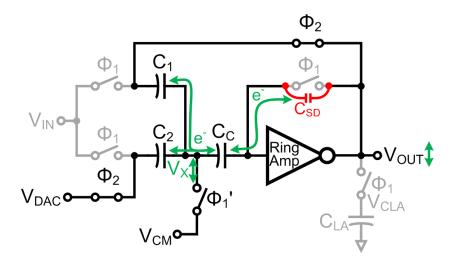

Figure 3.7. Auto-zeroed flip-around 1.5b MDAC gain stage using a ring amplifier.

### 3.2.1 Stability during Auto-Zero

We first consider stability during the auto-zero. When  $\Phi_1$  is high (i.e. the sampling/auto-zeroing phase) the MDAC stage in Figure 3.7 samples the input,  $V_{in}$ , onto the sampling capacitors  $C_1$  and  $C_2$ , and at the same time samples the offset of the ring amplifier on the offset sampling capacitor,  $C_C$ . Then, when  $\Phi_2$  is high (the amplification phase), the MDAC stage amplifies the sampled voltage by transferring the sampled input charge to  $C_1$  capacitor. During the amplification phase, the ring amplifier sees the sampling capacitors of the next pipeline stage as the load capacitance. In addition, the feedback factor during the amplification phase is about a half. However, during the sampling/auto-zeroing phase, the offset sampling capacitor,  $C_C$ , is the only load, and also the feedback factor increases to about one. The increased feedback factor and the reduced load capacitance (i.e. assuming  $C_C < C_1 + C_2$ ) during the auto-zero phase make the ring amplifier hard to stabilize because these reduce the phase margin. It is possible to design a ring amplifier that is stable during auto-zeroing with this condition, but this requires higher power consumption than that required for the amplification phase. If  $C_C$  is equal to  $C_1$  and  $C_2$ , then to stabilize the ring amplifier during the auto-zero phase, the second and third poles of the

ring amplifier need to be four times higher than that required to stabilize it during the amplification phase. This requires at least four times higher power for the first and second inverters.

One approach to improving stability during the sampling/auto-zeroing phase without using more power is to increase the  $C_C$  capacitance, but this is not desirable for moderate resolution ADCs where the auto-zero related noise is not dominant. In order to stabilize the ring amplifier during auto-zero, and considering the twice larger feedback factor,  $C_C$  needs to be at least twice as large as sampling capacitance of the next stage  $(C_C > 2(C_1 + C_2))$ . However, that would require a large area since  $C_C$  should be a floating capacitor and floating capacitors such as metal-insulator-metal (MIM) or metal-oxide-metal (MOM) have a relatively low per unit area capacitance. A high density MOS capacitor can be used for  $C_C$ , but a MOS capacitor has a relative large bottom plate parasitic capacitance. The large bottom plate parasitic capacitance of  $C_C$  on the virtual ground node X increases the gain error during the amplification [33] because the bottom plate capacitance of  $C_C$  steals some of the sampled signal charge due to the imperfect virtual ground.

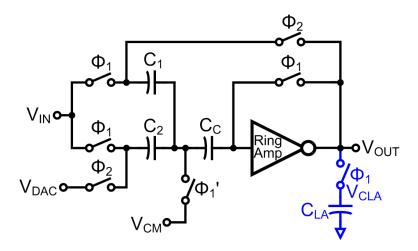

Instead of using a large  $C_C$ , we periodically add a loading capacitor  $C_{LA}$ , as shown in Figure 3.8.  $C_{LA}$  is connected to the output of the ring amplifier during the auto-zero phase, but not during the amplification phase. The sum of  $C_C$  and  $C_{LA}$  needs to be at least twice as large as the next stage sampling capacitors (i.e.  $C_C + C_{LA} > 2(C_1 + C_2)$ ). However, the use of a large  $C_{LA}$  does not require much area because we can use a high per unit area capacitance MOS capacitor, since one terminal of  $C_{LA}$  is always connected to ground. In addition, the addition of  $C_{LA}$  does not increase power consumption since the sampled offset voltage on  $C_{LA}$  stays constant in every cycle.

Figure 3.8. Auto-zeroed flip-around 1.5b MDAC gain stage using a ring amplifier with stabilization loading capacitor  $C_{LA}$ .

### 3.2.2 Improved Auto-Zero Switch to Eliminate Gain Error

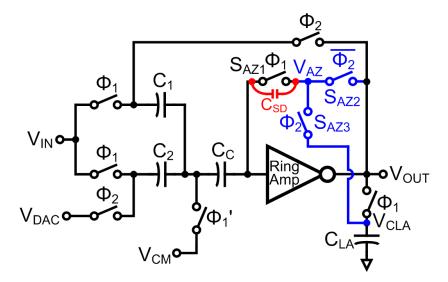

Another important consideration is the gain error due to the parasitic capacitance across the auto-zero switch. As shown in Figure 3.9, the source-drain parasitic capacitance,  $C_{SD}$ , of a conventional auto-zero switch scheme causes a gain error during the amplification phase. As the ring amplifier output voltage,  $V_{OUT}$ , moves during the amplification phase,  $C_{SD}$  steals (or injects) charge from (or to) the  $C_C$  capacitor and this also changes the sampled input charge in the sampling capacitors,  $C_1$  and  $C_2$ . In addition, the change in charge on  $C_C$  also moves the virtual ground voltage,  $V_X$ , from  $V_{CM}$ , which also causes a gain error. The gain of the MDAC gain stage in Figure 3.9 including the gain error caused by  $C_{SD}$  can be calculated as:

$$\frac{V_{OUT}}{V_{IN}} = \frac{2}{1 + \left(\frac{1}{c} + \frac{2}{c_C}\right)c_{SD}}.$$

(3.3)

where  $C_1$  and  $C_2$  have the same value C,  $V_{DAC}$  is equal to  $V_{CM}$ , and we assume the ring amplifier has infinite gain and zero offset for simplicity. As we can see from the equation,  $C_{SD}$  is problematic for gain accuracy.

Figure 3.9. Gain error mechanism due to the parasitic capacitance of the auto-zero switch.

One way to reduce this gain error is to minimize  $C_{SD}$  using layout techniques. For example, we can minimize  $C_{SD}$  by extending the distance between the source and drain of the auto-zero switch, or by adding a shield in between. However, we cannot completely eliminate this gain error because  $C_{SD}$  still exists due to the electrical field in the substrate and we cannot completely shield over the gate poly.

We introduce an improved auto-zero switch, as shown in Figure 3.10, to eliminate the  $C_{SD}$  related gain error. This improved auto-zero scheme makes use of the sampled ring amplifier offset voltage,  $V_{CLA}$ , stored on  $C_{LA}$ , which we already use to stabilize the ring amplifier during the auto-zero phase. During the auto-zero phase, the scheme works in the same way as a conventional auto-zero by turning on the switches  $S_{AZ1}$  and  $S_{AZ2}$ , and turning off the switch  $S_{AZ3}$ . During the amplification phase,  $S_{AZ1}$  and  $S_{AZ2}$  are turned off and  $S_{AZ3}$  connects the intermediate auto-zero switch voltage,  $V_{AZ}$ , to the sampled offset voltage,  $V_{CLA}$ , which effectively grounds  $C_{SD}$  to  $V_{CLA}$ . In this way,  $C_{SD}$  no longer affects the charge on the other capacitors, even as  $V_{OUT}$  moves.

Figure 3.10. An improved auto-zero switch that is free from C<sub>SD</sub> related gain error.

### 3.3 Comparator-Less Sub-ADC Using Ring Amplifier

We introduce a comparator-less MDAC stage that uses the self-biased ring amplifiers as comparators by exploiting a unique characteristic of the ring amplifier. As discussed in CHAPTER 2, during the amplification phase, the second stage outputs reach ground when the ring amplifier output slews up, and the second stage outputs reach V<sub>DD</sub> when the ring amplifier output slews down. In other words, the second stage output voltage indicates the amplification direction during ring amplifier output slewing. In fact, the first two stages of the ring amplifier work as an offset canceled continuous time comparator at the beginning of the amplification as a byproduct of the slow response of the last stage. We can use this amplification direction information as the next stage MDAC sub-ADC decision. This allows us to further reduce the power consumption of a ring amplifier based pipeline ADC by eliminating dedicated clocked comparators for the sub-ADCs.

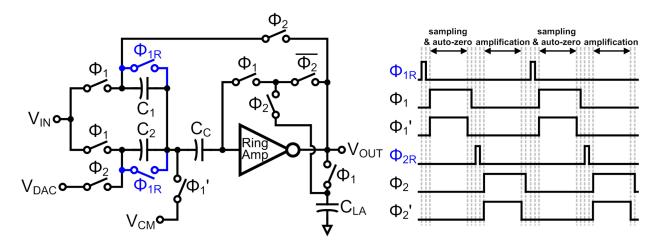

In order to properly use this direction information from the ring amplifier, we first ensure the amplification always starts from  $V_{CM}$ . To ensure this, we reset the sampling capacitors  $C_1$  and

$C_2$  using a short pulse  $\Phi_{1R}$  before the sampling phase, as shown in Figure 3.11. This resetting operation also reduces the maximum slew requirement by half, which allows us to further reduce the ring amplifier power consumption for the same operating speed.

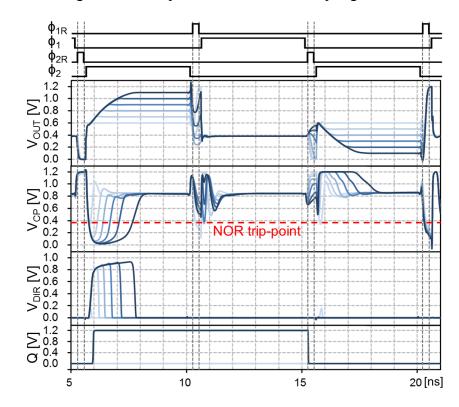

Figure 3.11. Modification of the ring amplifier MDAC to use the amplification direction information.

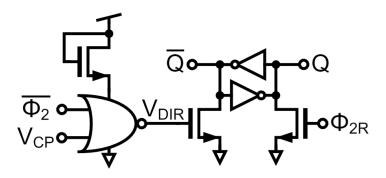

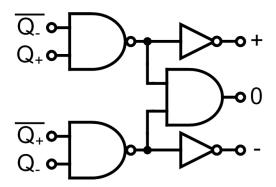

We can sample the amplification direction from the second stage output  $V_{CP}$  of the self-biased ring amplifier (Figure 3.6) by using a minimum sized NOR gate and a set-reset (SR) latch as in Figure 3.12. The latch consists of weak back-to-back inverters, and pull-down set-reset NMOS transistors. The latch can be set or reset by turning on only one of the pull down transistors. Figure 3.13 shows a simulation of the MDAC gain stage (Figure 3.11) with the direction sampling circuit for various input voltages. The NOR gate inverts  $V_{CP}$  during the amplification phase and outputs 0 during the sampling phase. The supply voltage of the NOR gate is reduced by a diode connected NMOS transistor in order to reduce the logic threshold voltage of the gate. This helps to get the correct NOR trip-point for the direction sampling and prevents unwanted short circuit current after the ring amplifier slewing due to the lower than  $V_{DD}$  quiescent voltage of  $V_{CP}$ . The SR latch is reset right before the amplification phase and samples

the amplified direction information from the NOR gate output  $V_{DIR}$ . We can use the latch output, Q, as the next MDAC stage sub-ADC result. A similar circuit samples the opposite direction information from the opposite side of the MDAC pseudo-differential stage. The simple decoding circuit in Figure 3.14 decodes the two direction information bits (Q+ and Q-) to provide the 1.5b sub-ADC result for the next stage.

Figure 3.12. Amplification direction sampling circuit.

Figure 3.13. Simulation of the MDAC gain stage in Figure 3.11 with the amplification direction sampling circuit in Figure 3.12 for various input voltages.

Figure 3.14. Amplification direction information to 1.5b sub-ADC result decode logic. Q<sub>+</sub> and Q<sub>-</sub> are from each side of the pseudo-differential ring amplifier MDAC gain stages.

The auto-zero ensures the correct amplification direction even with PVT variation, while the NOR trip-point and the ring amplifier slew rate define the threshold of the direction sampling. The direction sampling threshold voltage tends to be close to  $V_{CM}$  because  $V_{CP}$  drops near ground for even slightly positive  $V_{OUT}$  slewing and the slew is tuned to be slow (about half of amplification period for maximum swing) for better power efficiency. Therefore, even with some PVT variation, the thresholds are well within the redundancy ( $\pm 1/2V_{ref}$ ) of the 1.5b/stage pipeline ADC.

### 3.4 ADC Implementation and Measured Results

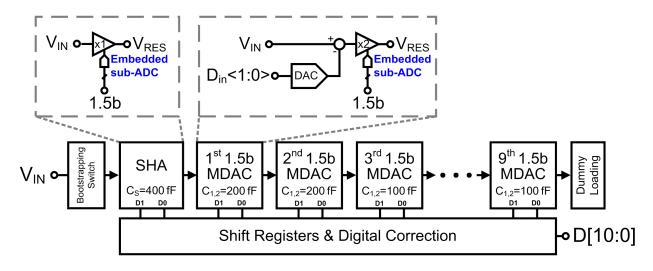

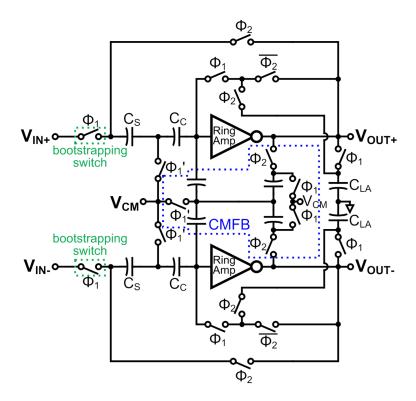

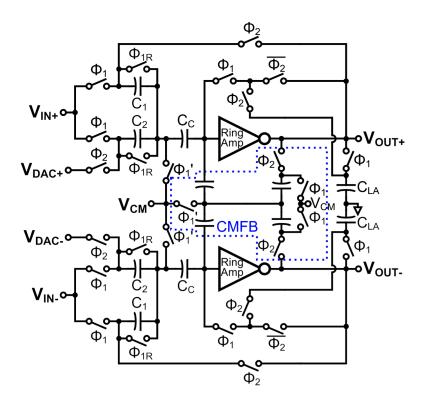

A 100 MS/s, 1.5b/stage 10.5b pipeline ADC [34] is implemented as a proof of the concept prototype to demonstrate the effectiveness of the self-biased ring amplifier. As shown in Figure 3.15, the ADC is composed of a flip-around sample and hold amplifier (SHA) [9], [35] with the bootstrapping input switches [36], nine 1.5b flip-around MDAC stages, and dummy loading for the last stage. Figure 3.16 and Figure 3.17 show the pseudo-differential ring amplifier based flip-around SHA and MDAC gain stage used in the ADC. The pseudo-differential CMFB in [29] is

implemented for all stages. The SHA also works as the first MDAC 1.5b sub-ADC<sup>7</sup>. To further optimize the power efficiency, the seven last MDAC stages are scaled down by half compared to the first two MDAC stages. Identical self-biased ring amplifiers are used for the SHA and for the first two MDACs. The SHA uses a sampling capacitance ( $C_S$ ) of 400 fF and the first two MDAC stages use sampling capacitors ( $C_1$ ,  $C_2$ ) of 200 fF. The SHA and the first two MDAC stages use 200 fF offset storage capacitors ( $C_C$ ). The ring amplifiers used in the seven last MDAC stages use half width transistors and a doubled resistance  $R_B$  when compared with the ring amplifier of the first two MDAC stages.  $R_B$  is doubled to generate the same bias voltages,  $V_{CP}$  and  $V_{CN}$ , as the first two stages with half the inverter short-circuit current.

Figure 3.15. Prototype ADC structure.

<sup>&</sup>lt;sup>7</sup> We implement the SHA in this ADC to demonstrate a completely comparator-less pipeline ADC. We can eliminate SHA as in [31] if we use a conventional flash ADC for the first stage sub-ADC. The elimination of SHA also improves SNR and power efficiency of the ADC since the SHA adds noise to the sampled input signal without providing amplification. From a power consumption point of view, it is better to use this ring amplifier based comparator-less MDAC for all stages except the first stage sub-ADC for better energy efficiency.

Figure 3.16. Pseudo-differential ring amplified based flip-around sample and hold amplifier.

Figure 3.17. Pseudo-differential ring amplified based MDAC gain stage.

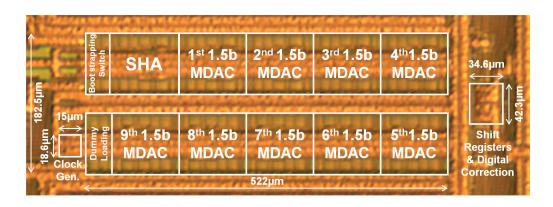

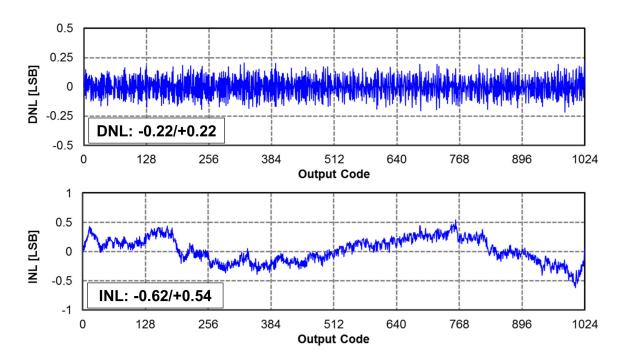

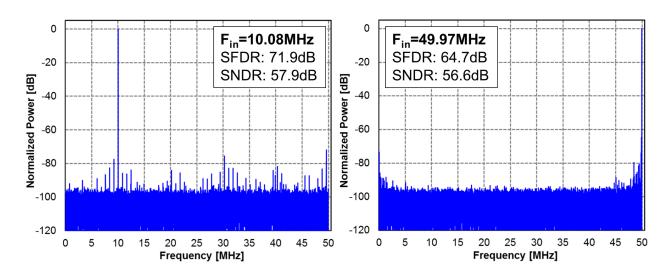

The prototype ADC is fabricated in a single poly nine metal (1P9M) 1.2 V 65 nm CMOS process. The ADC core fits within a small area of 0.097 mm<sup>2</sup>, as shown in the die microphotograph in Figure 3.18. A summary of performance is shown in Table 3-18. The top and bottom references are set at 1.1 V and 0.1 V thanks to the wide swing of the ring amplifier which results a full-scale differential input signal of 2 V<sub>pk-pk</sub>. Linearity plots (Figure 3.19) measured at 10b and at a full conversion rate of 100 MS/s, show that the measured DNL and INL are within ±0.22 LSB and -0.62/+0.54 LSB, respectively. As shown in the measured spectrums (Figure 3.20), at a 100 MHz sampling rate the ADC achieves 57.9 dB SNDR, 58.2 dB SNR, and 71.9 dB SFDR with a 10.08 MHz input, and 56.6 dB SNDR, 57.5 dB SNR, and 64.7 dB SFDR with a Nyquist frequency input. Figure 3.21 summarizes the measured SFDR, SNR, and SNDR versus input frequency. The ADC has a quite flat SNR response while SFDR (also SNDR affected by SFDR) is degraded at higher input frequency due to imperfect bootstrapping sampling switch design. The ADC has linear SNDR response up to the full-scale (Figure 3.22). For a 2 V<sub>pk-pk</sub> input swing, the SNDR with a Nyquist input frequency remains higher than 56 dB over an analog power supply voltage range from 1.2 V to 1.28 V (Figure 3.23). This proves that the dynamic bias using a resistor, R<sub>B</sub>, effectively tracks the power supply voltage variation. The SNDR increases as the supply voltage increases up to 1.26 V because the  $g_{m}$  of the first stage inverter increases as the supply voltage increases, and the increased g<sub>m</sub> reduces thermal noise of the ring amplifiers. However, the SNDR drops when the supply voltage is higher than 1.26 V because the quiescent offset voltage across R<sub>B</sub> increases faster than the supply voltage, and this causes the second stage to operate in the triode region resulting a lower overall three-stage gain. This reduced overall gain gives us a lower SFDR and thus also a reduced SNDR.

^

<sup>&</sup>lt;sup>8</sup> The ADC measurements have been updated since those reported in [34]. The measurements in [34] were degraded by digital output I/O related supply noise. The ADC and the test board were revised to achieve better isolation between the ADC core and the digital output I/O.

Figure 3.18. Die microphotograph of prototype ADC.

Table 3-1. ADC performance summary.

| Resolution          | 10.5 bit                                |                            |  |  |

|---------------------|-----------------------------------------|----------------------------|--|--|

| Supply              | 1.2 V (Analog, Clock),                  |                            |  |  |

|                     | 0.75 V (Digital)                        |                            |  |  |

| Sampling Rate       | 100 MS/s                                |                            |  |  |

| Technology          | 65 nm 1P9M CMOS                         |                            |  |  |

| Active Area         | 0.097 mm <sup>2</sup>                   |                            |  |  |

| Input Range         | 2.0 V <sub>pk-pk</sub> differential     |                            |  |  |

| <b>DNL</b> (10 bit) | -0.22/+0.22 LSB                         |                            |  |  |

| INL (10 bit)        | -0.54/+0.62 LSB                         |                            |  |  |

| Power               | 2.46 mW Total: 2.33 mW (Analog +        |                            |  |  |

| Consumption         | CLK), 61.6 μW (Ref.), 65.4 μW (Digital) |                            |  |  |

|                     | F <sub>in</sub> =10.08 MHz              | F <sub>in</sub> =49.97 MHz |  |  |

| SNDR                | 57.9 dB                                 | 56.6 dB                    |  |  |

| SNR                 | 58.2 dB                                 | 57.5 dB                    |  |  |

| SFDR                | 71.9 dB 64.7 dB                         |                            |  |  |

| ENOB                | 9.33 bit 9.11 bit                       |                            |  |  |

| $FoM_W$             | 38.4 fJ/conv-step                       | 44.5 fJ/conv-step          |  |  |