## Investigation of the Performance of Photon Counting Arrays Based on Polycrystalline Silicon Thin-Film Transistors

by

Albert KJ Liang

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Biomedical Engineering) in the University of Michigan 2018

Doctoral Committee:

Professor Larry E. Antonuk, Chair Professor Jeffrey A. Fessler Professor Mitchell Goodsitt Professor Kwok Lam Albert K. Liang

akliang@umich.edu

ORCID iD: 0000-0002-9146-5633

© Albert K. Liang 2018

#### Acknowledgements

First and foremost, I must extend by sincerest gratitude to my academic advisor, Dr. Larry Antonuk. Your scientific guidance and constant support helped make all this possible. Thank you for being patient and giving me the academic freedom to explore. I am constantly impressed by your perceptiveness and ability to break down seemingly colossal problems into sensible milestones. Thank you for supporting me through my personal difficulties outside of the Argus building as well. I greatly appreciate the amount of time and effort you gave me so that I could reach this step of my academic career.

In addition, I would not have reached this point without the support, advice, and guidance from Martin Koniczek, Dr. Youcef El-Mohri, and Dr. Qihua Zhao. The knowledge and understanding I have gained through our countless hours of discussion and debate is invaluable. Some of the most colorful memories of my Ph.D. are the road trips and conferences we all attended together. In particular, I could not have accomplished the things I did without the technical and personal support of Martin. Working closely with him has helped me learn a wide breadth of new things – from

computer programming principles to circuit design and fabrication. Several of the SPC1 prototype array designs would not exist without the circuit design experience he brought to the project.

I would also like to thank all the other members of our lab – Dr. Gechuan Liu, Dr. Hao Jiang, Mike Yeakey, Charles Martelli, Alan Young and John McDonald. Without their academic and technical contributions, none of my research would have been possible. I still thinking naming our simulation cluster "Skynet" is a bad idea – but it's been, without a doubt, an invaluable tool for my research.

Furthermore, I am grateful for the discussions with and knowledge transfer provided by the members of the Palo Alto Research Center prototyping group – Dr. Robert Street and Dr. Jeng Ping Lu. Thank you for patiently answering my numerous questions so I could understand how semiconductor fabrication works. Thank you for lending me your vast knowledge of layout and circuit design when creating the SPC1 prototypes. And thank you for literally making the prototype arrays a reality.

The saying "it takes a village to raise a child" also applies to a Ph.D. student. Without the humor and joy provided by my peers and friends – Dr. Jerry Wang, Dr. Eric Yu, Dr. Franke Hsu, Anna Chen, Kevin Cheng, Frank Gu, Dr. Andrew Liu, Wise Ongg, PJ Liu, Wen Cui, Yuching Lin, Greg Wu, Jimmy Chen, Kristan Hoffman, Patrick Tien, John Ding, Kevin Ly, and Jonathan Barker – and the endorphins provided by my volleyball teammates and coaches – Xia Xi, Yong Sun, Shuqi Cheng, Wenbing Hu, Sabor Hou, Ruiyang Li, Dani Knoefler, Bo Brandt, Ariel Wang, Grace Liu, Brian Liu, Ryan Wang, Carlen Zhang, Lindy Zhang, Mike Lee, Hai Hoang, Robinson Seda, Steve Maiser, Jay Lin, Eren Ural, Alejandro Arconada, and Karen Draves – I probably would've gone crazy by now. Thanks for all the adventures, the memories, and the chance to try new things.

Finally, none of this would be possible without the support of my family and wife. Mom and Dad, thanks for always being willing to listen without judging and for helping to solve whatever problems came my way. I'm so lucky to have your perspective whenever I get stuck on a scientific problem or reach a professional crossroad. Thank you for being willing to financially support me so I could pursue what I really want. To my sister Amy, you're definitely braver than me since you jumped straight into industry after graduating. Now, I'm lucky that I can count on you for career advice! Also, thanks for being a catch-all and letting me vent my frustrations from graduate student life. To my wife, Fei Zhao – thank you for waiting for me and being patient, even though that meant earning two Master degrees and then working at two different companies. For as long as you have known me, I've always been a Ph.D. student. Having reached this major milestone, we can now start a new chapter of our lives and go explore the "real" world together.

## **Table of Contents**

| Acknowledgements                                                                        | ii   |

|-----------------------------------------------------------------------------------------|------|

| List of Figures                                                                         | viii |

| List of Tables                                                                          | xiii |

| Abstract                                                                                | xv   |

| Chapter 1: Introduction                                                                 | 1    |

| Chapter 2: Design and Development of Poly-Si Photon Counting Arrays                     | 12   |

| I. Introduction                                                                         | 12   |

| II. Overview of the SPC1 designs                                                        | 14   |

| III. Amplifier circuit design                                                           | 16   |

| IV. Comparator circuit design                                                           | 19   |

| V. Clock generator circuit design                                                       | 22   |

| VI. Counter circuit design                                                              | 25   |

| VII. SPC1 prototype array design                                                        | 29   |

| VIII. Summary and discussion                                                            | 31   |

| Appendix 2.A – SPC1 test circuits and helper circuit elements                           | 33   |

| <b>Appendix 2.B</b> – Conversion of radiographic exposure to counts/sec/mm <sup>2</sup> | 38   |

| Chapter 3: Performance of In-Pixel Circuits for PCAs Based on Poly-Si TFTs              |      |

| I. Introduction                                                               |         |

|-------------------------------------------------------------------------------|---------|

| II. Methods                                                                   |         |

| IIa. Methods - Transistor parameters and noise characteristics                | 41      |

| IIb. Methods - Amplifier performance simulations                              | 43      |

| IIc. Methods – Comparator+clock generator performance simulations             | 46      |

| IId. Methods - Counter performance simulations                                | 48      |

| IIe. Methods – Minimum pixel pitch calculations                               | 49      |

| III. Results                                                                  | 52      |

| IIIa. Results - Transistor parameters and noise characteristics               | 52      |

| IIIb. Results – Amplifier performance simulations                             | 54      |

| IIIc. Results – Comparator+clock generator performance simulations            | 57      |

| IIId. Results - Counter performance simulations                               | 60      |

| IIIe. Results - Minimum pixel pitch calculations                              | 62      |

| IV. Discussion                                                                | 63      |

| Chapter 4: Count Rate Capabilities of In-Pixel Amplifiers for PCAs Based on 1 | Polv-Si |

| TFTs                                                                          | -       |

| I. Introduction                                                               | 67      |

| II. Methods                                                                   |         |

| IIa. Overview                                                                 |         |

| IIb. Determination of Energy Resolution                                       | 69      |

| IIc. Determination of Count Rate                                              |         |

| III. Results                                                                  |         |

| IIIa. Amplifier Designs                                                       |         |

| IIIb. Simulation Results for Performance Metrics                              |         |

| IIIc. Simulation Results Related to Count Rate                                |         |

| IV. Discussion                                                                      | 84 |

|-------------------------------------------------------------------------------------|----|

| Appendix 4.A – Estimates of the relative contribution of TFT thermal noise based on |    |

| analytic calculations                                                               | 88 |

| Chapter 5: Summary and Conclusion                                                   | 92 |

| References                                                                          | 99 |

# List of Figures

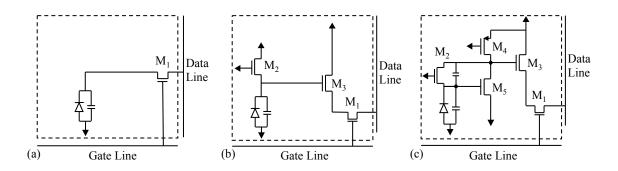

| <b>Figure 1.1.</b> Circuit diagrams for (a) a typical AMFPI pixel, (b) an active pixel with a one-stage amplifier, and (c) an active pixel with a two-stage amplifier. In each diagram, the circuit elements labeled with "M" are transistors, the dotted box represents the pixel boundary, the empty-triangle-and-line symbol is a photodiode, and the black triangles indicate connections to externally supplied voltages.                                                                                                                              |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6  |

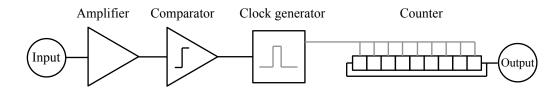

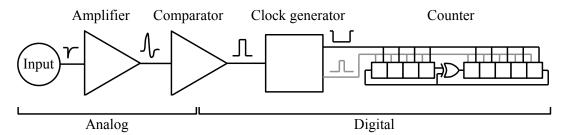

| Figure 1.2. Schematic diagram of the four circuit components of a photon counting pixel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10 |

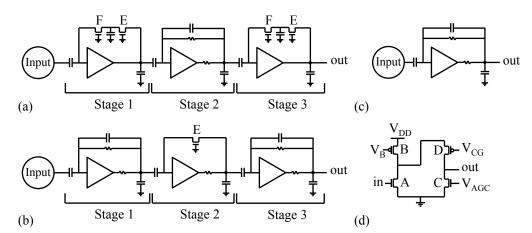

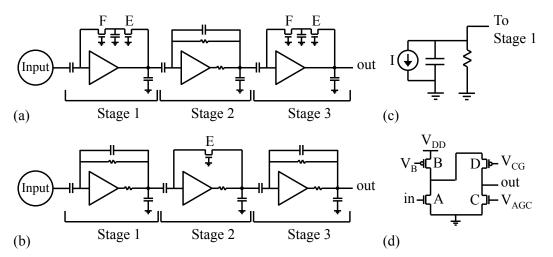

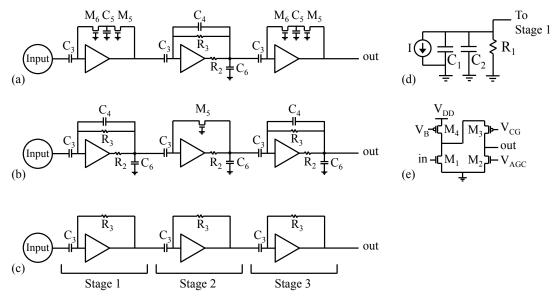

| <b>Figure 2.1.</b> Circuit diagrams for the three amplifier circuit variations: (a) 3-stage, 1 <sup>st</sup> order bandpass, (b) 3-stage, 2 <sup>nd</sup> order bandpass, and (c) 1-stage, 1 <sup>st</sup> order bandpass. In each diagram, the triangle is a folded cascode circuit, shown in (d) and the letters A-F denote transistors.                                                                                                                                                                                                                  | 18 |

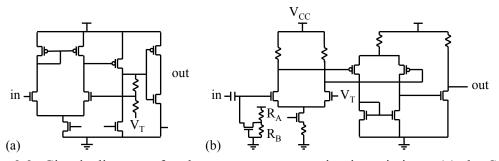

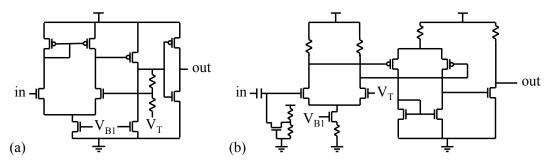

| <b>Figure 2.2.</b> Circuit diagrams for the two comparator circuit variations: (a) the Schmitt trigger and (b) the differential pair circuit. The symbol $V_T$ denotes where the threshold voltage should be applied. See text for details regarding the power rail $V_{CC}$ and resistors $R_A$ and $R_B$ .                                                                                                                                                                                                                                                | 19 |

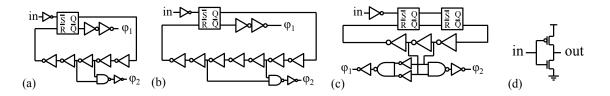

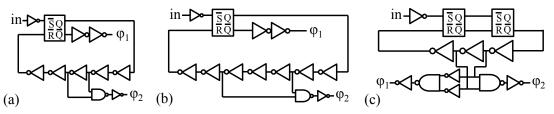

| <b>Figure 2.3.</b> Circuit diagrams for the four clock generator circuit variations: (a) the 1SR-5inv design (with two configurations referred to as 1SR-5inv-long and 1SR-5inv-short), (b) the 1SR-7inv design, and (c) the 2SR-3inv design. In each diagram, the triangle-and-bubble symbol represents an inverter circuit, shown in (d), the combined plug-shape-and-bubble symbol represents a NAND gate, the rectangle represents an SR (i.e., set-reset) latch based on 2 NAND gates, and $\varphi_1$ and $\varphi_2$ denote the output clock pulses. | 23 |

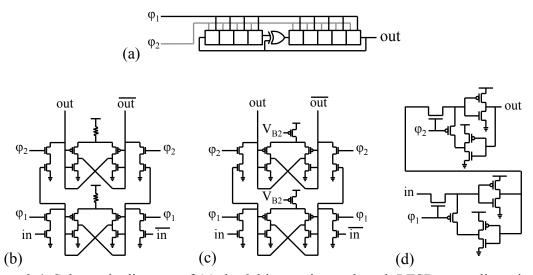

| <b>Figure 2.4.</b> Schematic diagram of (a) the 9-bit, maximum-length LFSR, as well as circuit diagrams for one bit of each counter component circuit variation: (b) the resistor-biased differential pair, (c) the transistor-                                                                                                                                                                                                                                                                                                                             |    |

| biased differential pair, and (d) the gated CMOS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 26 |

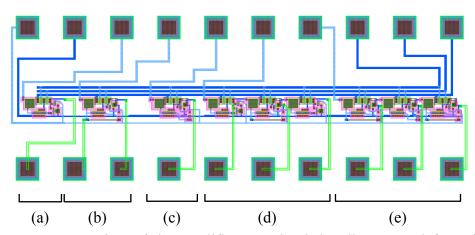

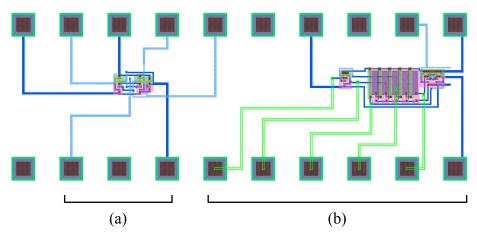

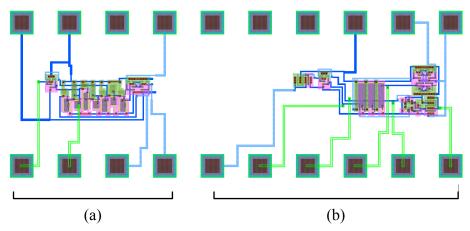

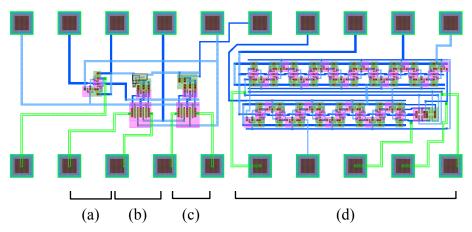

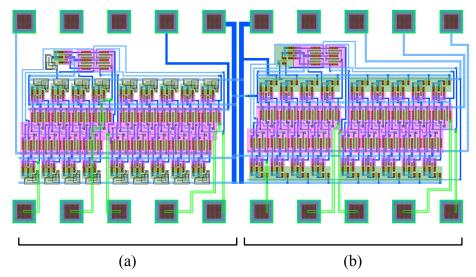

| <b>Figure 2A.1.</b> Layout view of the amplifier test circuit bundle. From left to right, the circuits are: (a) a single cutoff stage [named 2T-amp], (b) a single bandpass stage [named 2R-amp], (c) another single cutoff stage [named 1T1R-amp], (d) a 3-stage, 1 <sup>st</sup> order bandpass [named 3st-1bw-amp], and (e) a 3-stage, 2 <sup>nd</sup> order bandpass [named 3st-2bw-amp].                                                                                                                                                                                                           | 34 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

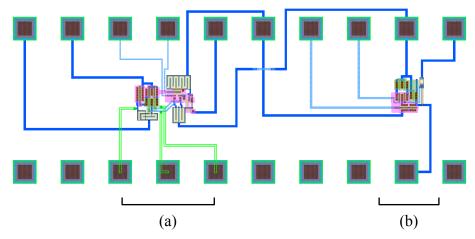

| <b>Figure 2A.2.</b> Layout view of the comparator test circuit bundle. From left to right, the circuits are: (a) a differential-pair comparator [named diff-comp] and (b) a Schmitt-trigger comparator [named Schmitt-comp].                                                                                                                                                                                                                                                                                                                                                                            | 35 |

| <b>Figure 2A.3.</b> Layout view of the first clock generator test circuit bundle.<br>From left to right, the circuits are: (a) a tri-state buffer [named tri-<br>buffer] and (b) a 1SR-5inv-long circuit [named 1SR-5inv-long].                                                                                                                                                                                                                                                                                                                                                                         | 35 |

| <b>Figure 2A.4.</b> Layout view of the second clock generator test circuit bundle. From left to right, the circuits are: (a) a 1SR-7inv circuit [named 1SR-7inv] and (b) a 2SR-3inv circuit [named 2SR-3inv].                                                                                                                                                                                                                                                                                                                                                                                           | 36 |

| <b>Figure 2A.5.</b> Layout view of the first counter test circuit bundle. From left to right, the circuits are: (a) one bit of the gated CMOS design [named gated-cmos-bit], (b) one bit of the resistor-biased differential pair design [named diff-res-bit], (c) one bit of the transistor-biased differential pair design [named diff-tft-bit], and (d) a 9-bit LFSR based on gated CMOS bits [named gated-cmos-lfsr].                                                                                                                                                                               | 36 |

| <b>Figure 2A.6.</b> Layout view of the second counter test circuit bundle. From left to right, the circuits are: (a) a 9-bit LFSR based on resistor-biased differential pair bits [named diff-res-lfsr] and (b) a 9-bit LFSR based on transistor-biased differential pair bits [named diff-tft-lfsr].                                                                                                                                                                                                                                                                                                   | 37 |

| <b>Figure 3.1.</b> Diagram of the four main circuit components of the prototype photon counting pixels: an amplifier, a comparator, a clock generator, and a counter. The waveforms between components schematically illustrate the shape of the signals at that point in the design. The clock generator component has two outputs, denoted by black and grey lines.                                                                                                                                                                                                                                   | 40 |

| <b>Figure 3.2.</b> Circuit diagrams for the amplifier designs considered in this study: (a) a 3-stage, 1 <sup>st</sup> order bandpass filter design, and (b) a 3-stage, 2 <sup>nd</sup> order bandpass filter design. In these figures: the circles labeled "Input" represent the circuit shown in (c); the triangles are folded cascode circuits, the diagram of which is shown in (d); and the stages are labeled as Stage 1, Stage 2, and Stage 3. Transistors in the folded cascode circuit are labeled A through D, and transistors not related to the folded cascode circuit are labeled E and F. | 45 |

- Figure 3.3. Circuit diagrams for the comparator designs considered in this study: (a) a Schmitt trigger design, and (b) a differential pair design. For both designs, two adjustable nodes,  $V_{B1}$  (bias) and  $V_T$  (threshold), are labeled.

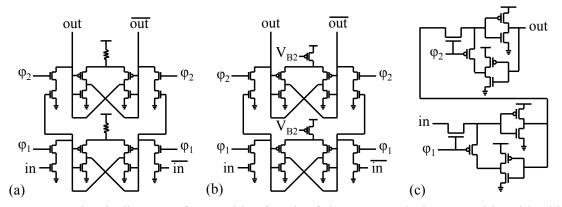

- **Figure 3.4.** Circuit diagrams for the clock generator designs considered in this study: (a) a 1 SR + 5-inverter design (corresponding to two configurations: long-delay and short-delay), (b) a 1 SR + 7-inverter design, and (c) a 2 SR + 3-inverter design. In the diagram, the rectangles represent 2-NAND-gate-based SR (i.e., set-reset) latches; the combined triangle-and-bubble symbols represent inverter stages; and the combined plug-shape-and-bubble symbols represent NAND gates. The outputs of the clock generator are denoted as  $\varphi_1$  and  $\varphi_2$ .

- **Figure 3.5.** Circuit diagrams for one bit of each of the counter designs considered in this study: (a) a differential-pair with resistive load design (referred to as Differential-Res), (b) a differential-pair with transistor load design (referred to as Differential-TFT), and (c) a gated-CMOS design. The symbols  $\varphi_1$  and  $\varphi_2$  indicate inputs provided by the preceding clock generator component. The bias voltage  $V_{B2}$  was set to 4 V.

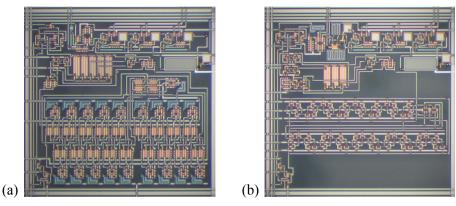

- Figure 3.6. Microphotographs of a single pixel from (a) the Pxl3 array with 229 transistors, 9 capacitors, and 26 resistors and (b) the Pxl5 array with 197 transistors, 11 capacitors, and 12 resistors.

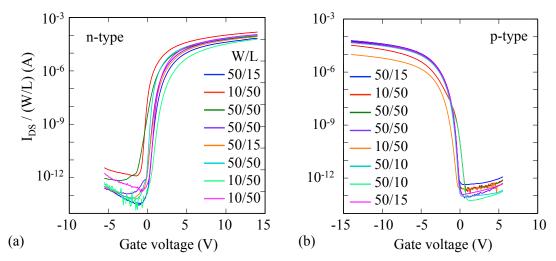

- **Figure 3.7.** Normalized transfer characteristics measured from (a) 8 n-type and (b) 8 p-type poly-Si TFTs. The legend indicates the dimensions of W and L, in µm, for the individual transistors.

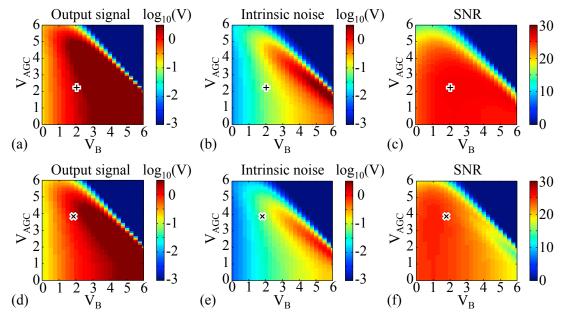

- **Figure 3.8.** Results for (a) output signal, (b) intrinsic noise, and (c) SNR for the 3-stage,  $1^{st}$  order bandpass amplifier plotted as a function of  $V_{AGC}$  and  $V_B$  with the best combination indicated by the superimposed "plus" symbol. (d), (e), and (f) show the corresponding signal, noise, and SNR results for the 3-stage,  $2^{nd}$  order bandpass amplifier with the best combination indicated by the "cross" symbol. For each plot, the color bar to the right denotes the scale. Note that output signal and intrinsic noise are plotted on a logarithmic scale while SNR is plotted on a linear scale.

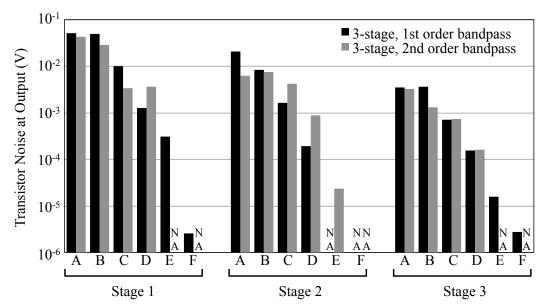

- **Figure 3.9.** Noise values, referred to the output of the amplifier, for each transistor in the 3-stage, 1<sup>st</sup> order bandpass and 3-stage, 2<sup>nd</sup> order bandpass amplifier designs, indicated by the black and grey bars, respectively. The transistor results are grouped by stage. In each stage, the letters A through F correspond to the transistors appearing in Fig. 3.2. Finally, the use of the notation "NA" in place of a black

47

48

52

49

53

or grey bar indicates the absence of that transistor in a given stage of a design.

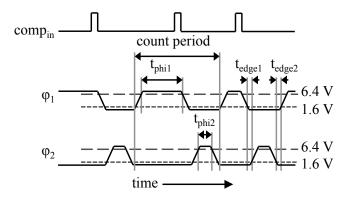

- **Figure 3.10.** Illustrations of the waveforms input to the comparator component (comp<sub>in</sub>) and output from the clock generator component ( $\varphi_1$  and  $\varphi_2$ ). Each pulse appearing in the comp<sub>in</sub> waveform corresponds to an event triggered by one X ray interacting with the detector. In the simulation, the input pulses swing between ground (0 V) and V<sub>DD</sub> (8 V). The short-dashed and long-dashed horizontal lines represent 20% (1.6 V) and 80% (6.4 V) of V<sub>DD</sub>, respectively, and are used to evaluate the  $\varphi_1$  and  $\varphi_2$  waveforms. Superimposed on the figure are labels for the timing parameters (t<sub>phi1</sub>, t<sub>phi2</sub>, t<sub>edge1</sub>, and t<sub>edge2</sub>) and count period used for evaluation of the variations.

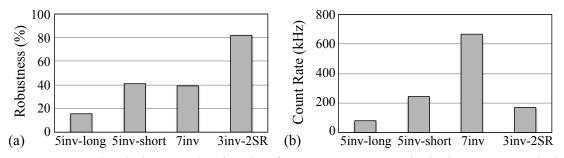

- Figure 3.11. Simulation results for the four comparator and clock generator design combinations listed in Table 3.1: (a) robustness, and (b) maximum count rate obtained for each design. See text for further details.

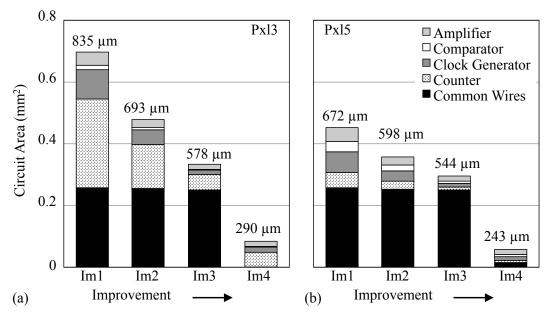

- Figure 3.12. Bar graph illustrating the total circuit area for the circuit designs of the (a) Pxl3 and (b) Pxl5 prototypes as a function of progressive improvement in the layout and fabrication of these designs as detailed in the main text. For each bar, the areas occupied by the amplifier, comparator, clock generator, and counter components, as well as the common wires, are indicated by different shadings. The number appearing above each bar is the pixel pitch corresponding to the total circuit area.

- **Figure 4.1.** Circuit diagrams for the amplifier circuit designs described in Table 4.1: (a) SPC1-amp1, (b) SPC1-amp2, and (c) New-amp-a and New-amp-b. In these diagrams, transistors are labeled  $M_1$  to  $M_6$ , capacitors are labeled  $C_1$  to  $C_6$ , and resistors are labeled  $R_1$  to  $R_3$ . Other circuits depicted in the figure include: (d) the circuit corresponding to the circle symbol at the input to each amplifier; and (e) a folded cascode circuit corresponding to the triangle symbols in each of the designs. Note that  $C_1$  is the capacitance of the CZT detector,  $C_2$  is a parasitic capacitance,  $V_{AGC}$ ,  $V_B$  and  $V_{CG}$  are bias voltages, and  $V_{DD}$  is a power rail (which is set to 8 V in the study).

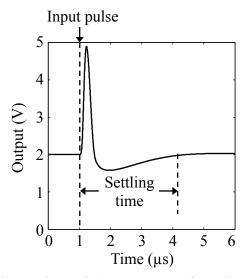

- **Figure 4.2.** Schematic illustration of the concept of settling time. The solid curve represents the amplifier output response to an input pulse corresponding to an interacting X ray. Note that the dashed vertical line on the left corresponds to the introduction of an input pulse. See main text for further details.

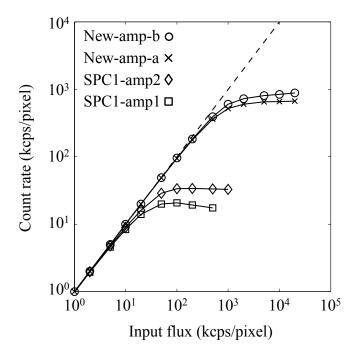

- Figure 4.3. Count rate as a function of input flux for the four amplifier circuit designs. For each design, results are plotted up to that value of

56

58

59

63

input flux beyond which less than 2% of the flux is resolved. The solid lines are drawn to guide the eye while the dashed line corresponds to the ideal of a 1-to-1 correlation between count rate and input flux.

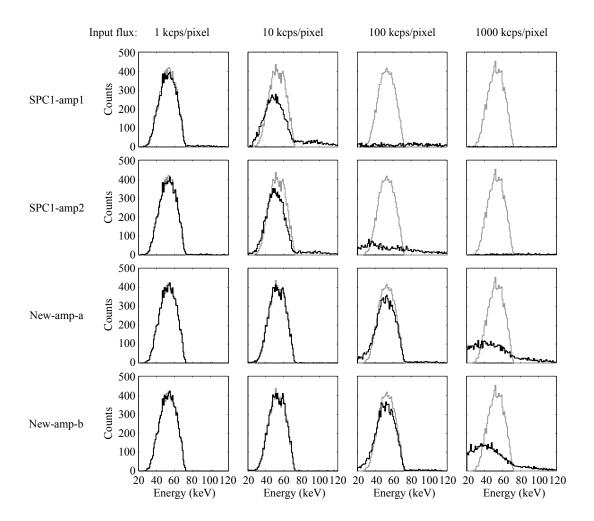

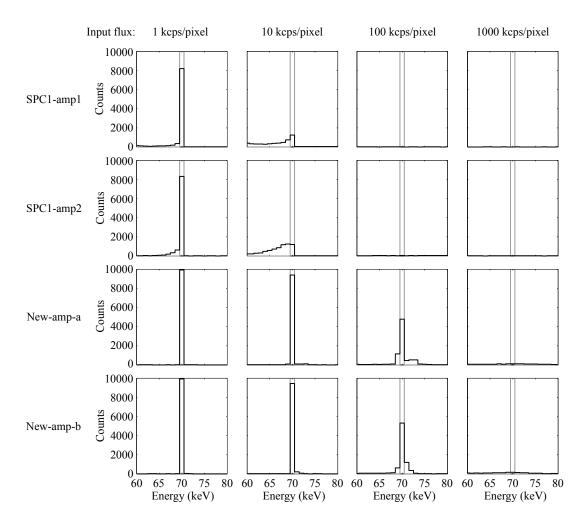

- **Figure 4.4.** Energy response profiles for the four amplifier circuit designs. For each design, results are shown for input flux values ranging from 1 to 1000 kcps/pixel. For a given design and flux, the grey and black lines in a graph represent the input energy distribution (corresponding to the RQA5 spectrum) and the resulting energy response profile, respectively. Note that counts are plotted for a bin size of 1 keV. See main text for further details.

- **Figure 4.5.** Energy response profiles for the four amplifier circuit designs following the same conventions used in Fig. 4.4 but where the input energy distribution corresponds to 70 keV monoenergetic X rays.

83

### List of Tables

| <b>Table 2.1.</b> Summary of the identifier codes (column 1) and circuit variations chosen for each component of the 11 prototype array designs. In the identifier codes, the letter "n" denotes the absence of a photodiode, the "s" denotes a sparse configuration and the "p" denotes a design with an extra probe pad connected to the input of the                          |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| amplifier. See text for further details.                                                                                                                                                                                                                                                                                                                                         | 30 |

| <b>Table 3.1.</b> Combinations of comparator and clock generator designsexamined in the study.Each design pair is employed in thecorresponding SPC1 arrays (described in more detail in reference 36)                                                                                                                                                                            |    |

| indicated in the last column.                                                                                                                                                                                                                                                                                                                                                    | 47 |

| <b>Table 3.2.</b> Minimum and maximum mobility $(\mu_{00})$ and threshold voltage $(V_{t0})$ values for the 8 n-type and 8 p-type transistor model cards. The                                                                                                                                                                                                                    | 50 |

| values for the standard transistor model cards are also shown.                                                                                                                                                                                                                                                                                                                   | 53 |

| <b>Table 3.3.</b> Simulation results for output signal, total intrinsic noise, SNR, equivalent noise, and energy resolution corresponding to a 70 keV incident photon for each amplifier design using the best combination of $V_{AGC}$ and $V_B$ indicated in Fig. 3.8. Note that, for each design, the intrinsic noise values correspond to the sum in quadrature of the noise |    |

| values of the individual transistors given in Fig. 3.9.                                                                                                                                                                                                                                                                                                                          | 57 |

| Table 3.4. Robustness results from simulation of the three counter designs                                                                                                                                                                                                                                                                                                       |    |

| shown in Fig. 3.5 as a function of count rate.                                                                                                                                                                                                                                                                                                                                   | 61 |

| <b>Table 4.1:</b> Design name, circuit description and pixel pitch for each of the amplifier circuit designs examined in this study.                                                                                                                                                                                                                                             | 72 |

| <b>Table 4.2.</b> Transistor width/length dimensions, as well as the resistance and capacitance of the other circuit elements, for the various amplifier circuit designs examined in this study. The symbols for the circuit elements listed in the table correspond to those appearing in Fig. 4.1.                                                                             |    |

| Note that the design specifications for New-amp-a and New-amp-b are identical, except for the value of the input detector capacitance $C_1$ .                                                                                                        | 74 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| <b>Table 4.3.</b> Summary of the values for the optimal operating conditions (columns 2 to 4) identified for each amplifier circuit design examined in this study – along with the values of the corresponding performance metrics (columns 5 to 8). | 76 |

| <b>Table 4.4.</b> Results for the three measures of count rate ( $CR_{max}$ , $CR_{30}$ and $CR_{10}$ ) for each amplifier circuit design. See text for further details.                                                                             | 79 |

#### Abstract

Projection x-ray imaging is commonly employed to visualize internal human anatomy and used to produce diagnostic images. Modern projection imaging is typically performed using an active matrix, flat panel imager that is comprised of a converter layer overlying a pixelated array. The images are formed by converting x-ray photons into electrical signals, and then integrating those signals over a frame time – a method referred to as fluence integration.

Recently, imagers employing a second method for creating x-ray images – referred to as photon counting – have been developed and used to perform mammographic imaging (a form of projection imaging). Photon counting involves measuring the energy of each interacting x-ray photon and storing digital counts of the number of photons exceeding one or more energy thresholds. Because the imaging information is stored digitally, photon counting imagers are less susceptible to noise than fluence-integrating imagers – which improves image quality and/or decreases the amount of radiation required to acquire an image.

Current photon counting mammographic imagers are based on crystalline silicon and are limited in detection area. In order to produce an image, the array is moved in a scanning motion across the object of interest. A photon counting imager with larger detection area would benefit other projection imaging modalities – such as radiography (which produces, for example, chest x-ray images) or fluoroscopy (which is used for noninvasively inserting stents and other medical devices). However, techniques to increase detection area, such as tiling multiple arrays, result in increased imager complexity or cost. For this reason, our group has been exploring the possibility of creating photon counting arrays using a different semiconductor material, referred to as polycrystalline silicon (poly-Si). This material is fabricated using a thin-film process, which allows the economic manufacture of monolithic, large-area arrays and has favorable material properties for creating complex, high speed circuits.

Using poly-Si, a set of prototype arrays have been designed and fabricated. The design of the arrays consists of four components: an amplifier, a comparator, a clock generator, and a counter. Several circuit variations were created for each component, and circuit simulations were performed in order to determine energy resolution and count rate values for each variation of each component.

For the amplifier component, all circuit variations were determined to have an energy resolution of  $\sim 10\%$  when presented with a 70 keV input x-ray photon (a typical photon energy level used in diagnostic imaging). This energy resolution value is

xvi

comparable to those reported for photon counting imagers fabricated using crystalline silicon. In addition, while count rate values for the amplifier component were roughly one order of magnitude too low for radiographic and fluoroscopic applications (which require count rates on the order of 1 million counts per second per square millimeter [cps/mm2]), a hypothetical amplifier circuit variation with count rate capabilities suitable for these applications (while preserving the same ~10% energy resolution) was designed. In addition, the count rate values for the various comparator, clock generator, and counter circuit variations ranged from 100 to 3000 kcps/mm2. Finally, due to improvements in the poly-Si fabrication process (driven largely by the display industry), future photon counting arrays employing this material can have pixel pitches as small as 250 um – a size approaching that suitable for radiographic and fluoroscopic imaging.

#### Chapter 1:

#### Introduction

Over 120 years after their discovery, X rays continue to play a variety of crucial roles in modern medicine, including visualization of human anatomy. Such visualization takes the form of projection (i.e., two-dimensional) imaging and volumetric (i.e., three-dimensional) imaging. Projection imaging can be divided into static imaging (involving the production of a single image, such as for radiography and mammography) and dynamic/fluoroscopic imaging (where a series of images is produced at video rates and visualized in real time).

Considerable innovation has been applied to the development of x-ray detector technologies used to perform projection imaging. For the purpose of this dissertation, some detectors can be considered to have an identifiable component (referred to as a *backplane*) that captures the image. For static imaging, backplanes initially took the form of glass plates (and, later, plastic sheets) coated with an emulsion such as silver halide. Exposure of the emulsion to X rays forms a latent image which, after chemical development, results in a viewable image on the "film". To increase the fraction of

incident X rays that interact with the detector (referred to as x-ray quantum efficiency), as well as to amplify the amount of signal generated per X ray (referred to as x-ray sensitivity), a layer of photoluminescent material (referred to as an intensifying screen) is positioned in front of and/or behind the film. Such screen-film systems remained a dominant, ubiquitous backplane technology for static imaging for many decades.

In early forms of dynamic imaging, physicians viewed images in real time by directly observing light output from a phosphor screen positioned in line with the x-ray source and placed between the physician and the patient. However, due to the relatively low light level of images produced by such screens, physicians needed to dark adapt before viewing. The development of x-ray image intensifiers (XRIIs) overcame this limitation by amplifying the image signal by several orders of magnitude. XRIIs are comprised of an input phosphor screen, a photocathode, a high-voltage tube, an output phosphor screen and a camera. The energies of incident X rays are first converted into light photons by the input screen, and then into electrons by the photocathode. Electrons emitted from the photocathode are then accelerated in the high-voltage tube and strike the output screen – producing a signal that is captured by the (typically CCD) camera. Compared to the signal produced by the input screen, the signal presented to the camera is amplified by a factor of ~1000 or more.<sup>1</sup> XRIIs allow a wide variety of interventional procedures to be performed safely and relatively easily - such as inserting ports for chemotherapy or stents for vascular procedures.

In the latter part of the 20th century, a new technology for static imaging called computed radiography (CR) was successfully introduced into the clinic. CR backplanes incorporate a photostimulable phosphor that converts the energy of incident X rays into trapped signal, resulting in the storage of a latent image.<sup>2</sup> That image is later "read out" by using a laser to stimulate the phosphor and release the stored energy in the form of light. That released light is converted to an electrical signal, then amplified, digitized and stored in a computer for subsequent processing, viewing and archiving.

In the late 1980s, active matrix flat panel imagers (AMFPIs) were conceived and their development began.<sup>3-5</sup> An AMFPI is made up of an x-ray converter material positioned over a backplane taking the form of a two-dimensional pixelated array fabricated on a glass substrate. For indirect-detection AMFPIs, the converter is a phosphor screen (such as thallium-activated cesium iodide, CsI:Tl) in which the energy of incident X rays is transformed into optical light. For direct-detection AMFPIs, the converter is a photoconductor (such as amorphous selenium, a-Se) in which x-ray energy is transformed into electron-hole pairs. Both types of detection result in imaging signal that is captured by, and stored in, the pixels of the array. Each AMFPI pixel is comprised of a storage capacitor that retains the signal, coupled to a single thin-film transistor (TFT) that functions as an addressing switch. (In indirect-detection AMFPIs, the storage capacitor takes the form of a photosensitive element, usually a PIN photodiode.) The gate nodes of all the TFTs in a given row of pixels are connected to a common wire referred to as a *gate line*. The source nodes of all the TFTs in a given column of pixels are connected to a common wire referred to as a *data line*. Peripheral electronics are used to "read out" the image by sequentially activating one gate line at a time in order to transfer the signals stored in the pixels along that row onto the orthogonal data lines. The signals are conveyed by the data lines to pre-amplifiers located on the periphery of the array where they are magnified before being digitized and stored in a computer. AMFPIs are versatile devices and are used to perform static and dynamic/fluoroscopic imaging, as well as volumetric imaging.

The TFTs in AMFPI pixels (and photodiodes in indirect-detection AMFPIs) are fabricated using hydrogenated amorphous silicon (a-Si:H), a semiconductor material which allows the creation of large area, monolithic imaging arrays with dimensions commensurate with human anatomy – currently as large as ~43×43 cm<sup>2</sup>. In addition, a-Si:H TFTs and photodiodes are highly resistant to the effects of radiation.<sup>6, 7</sup> These desirable characteristics (i.e., large area and radiation damage resistance), together with real-time, digital imaging capabilities as well as high image quality under many conditions, have allowed AMFPIs to increasingly replace film, XRIIs and CR. However, under conditions of low x-ray exposure per frame (such as is encountered in fluoroscopy), the signal-to-noise performance of AMFPIs suffers due to the relatively high electronic readout noise of the peripheral electronics compared to the imaging signal.<sup>8</sup>

Given that prospects for reducing electronic readout noise in AMFPIs are poor, a variety of methods for increasing signal are being investigated. One method is to increase x-ray sensitivity by substituting a-Se with an alternative photoconductive material such as mercuric iodide (HgI<sub>2</sub>), lead iodide (PbI<sub>2</sub>) or lead oxide (PbO).<sup>9-16</sup>

Another method is to magnify the signal stored in the pixel before readout by introducing an amplifier circuit into each pixel – a concept referred to as active pixel. Active pixel detectors created using crystalline silicon (c-Si, a common semiconductor material) are currently employed in mammographic imaging (such as the GE Senographe Crystal) and for interventional radiology and cardiology (such as the Siemens Artis Q.zen). The high electron and hole mobilities of c-Si – on the order of 1000 cm<sup>2</sup>/V-s – allow the creation of highly-performing active pixel circuits. However, unlike a-Si:H, c-Si is not well-suited to the economic manufacture of monolithic, large-area arrays and is typically not radiation resistant. While active pixel arrays based on a-Si:H have been explored,<sup>17, 18</sup> the rather low electron and hole mobilities of c-Si, respectively) make it difficult to design highly-performing circuits.

In this context, a promising, alternative, thin-film semiconductor material is polycrystalline silicon (poly-Si). Like a-Si:H, poly-Si allows the creation of monolithic, large-area arrays, but exhibits much higher electron and hole mobilities – within an order of magnitude of that offered by c-Si. Poly-Si TFTs also demonstrate good radiation resistance.<sup>19</sup> Active pixel arrays created using this material are currently being explored by our group.<sup>20-22</sup>

Figure 1.1 shows the circuit diagram for a typical AMFPI pixel, as well as for two active pixel circuit designs created using poly-Si. In the figure, compared to the single-transistor AMFPI pixel circuit shown in Fig. 1.1a, the active pixel circuit shown in Fig. 1.1b has a one-stage amplifier with three transistors, and the active pixel circuit shown in Fig. 1.1c has a two-stage amplifier with five transistors. Early prototypes of these one-and two-stage pixel amplifiers provide nominal signal gains of ~10 and 20, respectively,<sup>21</sup> which offer the potential of greatly improving the signal-to-noise ratio.

**Figure 1.1.** Circuit diagrams for (a) a typical AMFPI pixel, (b) an active pixel with a one-stage amplifier, and (c) an active pixel with a two-stage amplifier. In each diagram, the circuit elements labeled with "M" are transistors, the dotted box represents the pixel boundary, the empty-triangle-and-line symbol is a photodiode, and the black triangles indicate connections to externally supplied voltages.

For the x-ray detector technologies described above, images are formed by integrating the signal created by X rays interacting with the converter – a method of imaging that can be regarded as fluence integration. This fluence is typically generated by conventional x-ray sources which produce X rays with a spectrum of energies that are tailored to a given medical application through selection of suitable materials for the target and filter of the x-ray tube. However, fluence integration results in the loss of

spectral information which could be used to improve image quality. For example, since higher-energy X rays are more likely to penetrate denser objects than lower-energy X rays, the ability to selectively view images formed only from higher-energy X rays would allow improved visualization of higher-density anatomical features with less interference from lower-density objects. To some degree, such density separation can be achieved with fluence-integrating detectors and conventional x-ray sources by acquiring and subtracting two images: one taken at a low x-ray energy and one taken at a higher x-ray energy. However, this results in increased dose to the patient, increased time to acquire the images, and registration problems if the patient moves between acquisition of the two images.

In comparison to fluence-integrating detectors, photon counting detectors can perform density separation imaging using a single image acquisition. A photon counting detector measures the energy of each interacting X ray individually and records this information digitally. Because the imaging signal information is stored digitally within each pixel, photon counting detectors are not susceptible to electronic readout noise. In addition, photon counting detectors can potentially eliminate Swank noise (i.e., variation in the amount of converted signal for each interacting X ray).<sup>23</sup> For those reasons, photon counting detectors offer the prospect of improved image quality and, potentially, decreased radiation dose.

Photon counting detectors based on c-Si have been employed for mammographic imaging.<sup>24, 25</sup> Those devices take the form of a linear array of silicon strip detectors

coupled to readout electronics. To form an image, the array moves in a sweeping motion across the field of view during irradiation to form a 2D image –providing, for example, a  $26 \times 24 \text{ cm}^2$  image with an acquisition time on the order of 1 second.<sup>24</sup> The detector has a pitch of 50 µm and employs two energy thresholds <sup>26</sup> set to 10 keV (to remove background noise) and 18-22 keV (to separate low- and high-energy photons)<sup>27</sup>. Mammographic imaging using such photon counting detectors has been reported to reduce radiation dose by much as ~67%.<sup>28</sup>

Photon counting detectors in the form of 2D pixelated arrays based on c-Si are also being explored.<sup>29-34</sup> Reported prototype arrays have pixel pitches ranging from 55 up to 1000  $\mu$ m,<sup>35</sup> and employ up to 8 energy thresholds.<sup>29</sup> Some prototypes have capabilities which enable neighboring pixels to combine information to more accurately resolve the energy of an X ray whose signal was spread across two or more pixels.<sup>29</sup> (Since this dissertation is concerned with large-area detectors, the specialized photon counting detector modules under development and use for fan-beam computed tomography [CT] are not discussed.)

However, these photon counting prototypes are limited in detection area due to their c-Si-based backplane arrays. This detection area can be increased by joining multiple arrays together (commonly referred to as tiling), but this increases detector complexity and complicates assembly. In addition, the areas where arrays are joined together may not be sensitive to X rays. For these reasons, our group has been exploring the possibility of creating photon counting backplanes (referred to as photon counting arrays, PCAs) using poly-Si and an initial set of prototype PCAs named SPC1 have been created.<sup>36</sup> In contrast to the ~3 to 5 transistors used to create active pixel circuits, our initial prototype PCA pixels contain several hundred transistors. This increase in transistor count is necessary in order to create the various circuit components needed to perform photon counting. Although each pixel has a very high number of transistors, this does not affect the fill factor (i.e., the percentage of pixel area that is used to collect signal) since the photodiode (for indirect detection) or storage capacitor (for direct detection) would be manufactured out-of-plane (i.e., on top of the circuits).

The schematic diagram in Fig. 1.2 shows the four components of the SPC1 photon counting pixel circuits: an amplifier, a comparator, a clock generator and a counter – similar to how other photon counting circuits are generally organized. The input to the amplifier component is an electrical signal produced by an overlying x-ray converter, such as cadmium zinc telluride (CZT) – a material with signal properties that lend itself to photon counting. That signal is amplified (by the first component) and compared (by the second component) to a user-defined energy threshold. If the signal exceeds this threshold, the comparator component will generate an output pulse. That pulse activates the clock generator component, which produces clock signals suitable for incrementing the counter component. Following image capture, the information stored in the counter is read out to external electronics, one row of pixels at a time – parallel to the readout operation of AMFPIs or active pixel imagers.

Figure 1.2. Schematic diagram of the four circuit components of a photon counting pixel.

The organization of the remainder of this dissertation is as follows. Chapter 2 presents a description of the SPC1 prototype arrays and their pixel circuit designs, along with a summary of the considerations behind those designs. While this dissertation is focused on a theoretical examination of the performance of the pixel circuits, the information presented in Chapter 2 is provided in the spirit of giving context for the simulation studies reported in Chapters 3 and 4. In addition, this information also serves as documentation to assist future empirical studies of the SPC1 arrays.

While the SPC1 prototype designs presented in Chapter 2 resulted from collaborative efforts between members of our group (including myself) and scientists at the Palo Alto Research Center, the latter chapters document my efforts to characterize the performance of those prototype designs. The results of those simulation efforts have been reported in first-author publications that have already been accepted (and presented in Chapter 3) or are under review (and presented in Chapter 4). The work has also been reported in 2 conference proceedings,<sup>36, 37</sup> 2 oral presentations, and 1 poster presentation.

Chapter 3 presents theoretical performance results for the pixel circuit designs of the four components of the SPC1 prototypes, as well as an estimate of the minimum achievable pixel pitch for future poly-Si-based photon counting arrays. The components are divided into analog (i.e., the amplifier) and digital (i.e., the comparator, clock generator, and counter) components. For the analog component, a circuit simulation framework was used to determine amplifier output response and energy resolution. For the digital components, a different simulation framework was used to determine amplifier output response and energy resolution. For the digital components, a different simulation framework was used to determine robustness (employing a metric that predicts how reliably a given circuit will perform) and an estimate of count rate (employing a metric related to how quickly a circuit can resolve x-ray photons). Finally, potential improvements in the poly-Si manufacturing process that may lead to reduced pixel pitch are discussed. The work presented in Chapter 3 has been adapted from a peer-reviewed article.<sup>38</sup>

Chapter 4 presents a study performed to explore the count rate capabilities of the analog amplifier component. A circuit simulation framework capable of determining detailed count rate metrics for poly-Si-based amplifier circuits was developed and used to estimate the count rate of the pixel circuit designs of the amplifier component. In addition, using this framework, a hypothetical amplifier circuit with improved count rate was identified and its capabilities explored. The work presented in Chapter 4 has been adapted from a manuscript recently submitted for publication.<sup>39</sup>

Finally, the summary and conclusions for this dissertation are presented in Chapter 5.

### Chapter 2:

#### **Design and Development of Poly-Si Photon Counting Arrays**

#### I. Introduction

The design of SPC1 prototype arrays was the result of a 14 month long collaborative effort involving myself and other members of our research group and two scientists at the Palo Alto Research Center (PARC). During that time, numerous material- and circuit-specific considerations were discussed and the final circuit designs of the SPC1 prototypes reflect many of those considerations. This chapter serves to document the history of the SPC1 prototypes in the spirit of providing a guide for future design efforts.

The fabrication of the SPC1 prototype arrays involved the use of low-temperature, polycrystalline silicon semiconductor material to create thin-film transistors (TFTs) for the pixel circuits. Low-temperature polycrystalline silicon is created by depositing a thin film of amorphous silicon (a-Si:H) on a quartz substrate followed by recrystallization of the a-Si:H using an excimer laser. The use of this form of polycrystalline silicon in the creation of photon counting arrays introduces a number of material-specific

characteristics that must be considered in circuit design. Compared to transistors fabricated using crystalline silicon (c-Si), TFTs created using polycrystalline silicon (poly-Si) cannot be manufactured as uniformly, resulting in variations in transistor properties and changes in circuit performance. In addition, poly-Si TFTs cannot be manufactured as small as c-Si transistors – leading to decreased circuit density and/or larger pixel pitch. While c-Si transistors currently have a minimum feature size (i.e., a value that describes the smallest structure that can be created) as small as 10 nm, the minimum feature size for poly-Si was in the range of 3-6  $\mu$ m at the time that the SPC1 designs were under development. For the SPC1 prototypes, a minimum feature size of 6  $\mu$ m was chosen so as to maximize fabrication yield.

In addition to these material-specific characteristics, circuit designs also have to account for process limitations imposed by the fabrication facility – which, for the SPC1 prototype arrays, was a poly-Si prototyping line at PARC. For example, the PARC prototyping line allows up to 4 metal layers for signal routing and bias voltages. Two of those layers are reserved for contacting the top and bottom of a photoconductive x-ray converter or a photodiode, leaving only 2 layers available for photon counting circuitry. Furthermore, the PARC line employs resistors created using doped a-Si:H. This material has an estimated sheet resistance of 10 M $\Omega$ /square – generally limiting resistance values to a range of 0.5 to 200 M $\Omega$ .

In order to design circuits that accounted for these characteristics and limitations, circuit simulations based on the Eldo SPICE circuit simulator (Mentor Graphics, OR)

employing version 2 of the RPI poly-Si TFT model <sup>40</sup> were used. To make the simulation results representative of the poly-Si semiconductor material produced by PARC, empirical measurements of individual poly-Si TFTs were performed and transistor parameters derived from those measurements were employed. (Those TFTs were previously fabricated by PARC in connection with active pixel array development – a related area of research in our lab.) Simulation frameworks were developed to determine photon counting performance metrics and simulation results were used to identify designs that were more tolerant to TFT variations, required fewer and/or smaller circuit elements, and met PARC process limitations.

#### II. Overview of the SPC1 designs

The SPC1 prototype arrays encompass 11 different array designs that share a number of common specifications – such as the pixel pitch, the method of signal routing, the method of signal input and the form of signal-chain architecture.

The pixel pitch of the arrays was set to 1 mm to ensure that there would be sufficient space within the pixel for the circuit elements (including ~200 TFTs) needed to create the photon counting circuits, as well as for wires that provided power and signal routing. In addition, using a common pitch allowed those wires to be organized in a nearly identical manner for each array design – greatly reducing the overall design effort, as well as making it possible for a single set of external data acquisition electronics to operate all of the arrays. Note that empirical evaluation of the prototypes is not a part of this dissertation.

Signal input considerations included selecting the type of x-ray converter material that the pixel circuits should be designed to accept input from. Ideally, a fast converter material should be employed – such as cadmium zinc telluride (CZT) – so as to maximize the count rate capabilities of the imaging system. However, as it was unknown at the time of the design of the prototypes whether it would be practical to deposit CZT on the arrays, a number of alternative approaches for signal input were developed. First, in order to allow the arrays to be tested with signal generated by x-ray radiation, some arrays were designed with a discrete a-Si:H photodiode in each pixel - which would require a scintillator such as cesium iodide (CsI:Tl) to first convert x-ray photons into However, because a-Si:H photodiodes are inherently slow, the optical photons. maximum count rate of those arrays would be limited by the photodiodes – even though the circuits of the SPC1 prototype arrays were designed to operate faster. In order to operate the SPC1 prototypes faster, all arrays include test input pads connected to each pixel. Those pads can be used to directly inject an electronically generated signal to a pixel circuit – thereby providing input pulses of any shape, magnitude, or rate.

Finally, the prototype arrays also employed a common signal-chain architecture consisting of 4 components: an amplifier, a comparator, a clock generator, and a counter. For each of those components, a number of circuit designs, called *variations*, were identified through simulation studies. The 11 unique prototype array designs consist of different combinations of these circuit variations. In the remaining sections of this

chapter, the circuit variations are described and the reason for including certain combinations of those variations in the prototypes is discussed.

#### III. Amplifier circuit design

The amplifier component is responsible for magnifying the input signal generated by the converter material. For the design of this component, the most important considerations were signal gain and bandwidth. The gain of the amplifier needs to be large enough to enable the next component (i.e., the comparator) to operate properly, while the bandwidth of the amplifier has implications for count rate and noise.

Assuming the comparator component required an input of ~1 V, the gain of the amplifier was designed to be on the order of 1000 – based on an estimated ~1 mV input corresponding to the amount of signal generated by a 70 keV x-ray photon interacting with a CsI:Tl converter and collected by a  $100 \times 100 \ \mu\text{m}^2$  a-Si photodiode. (This corresponds to the size of the photodiode located in the same plane as the pixel circuits in several of the SPC1 array designs.) However, an empirical measurement performed by PARC on one of their earlier single-stage poly-Si amplifiers demonstrated a gain of only ~10 to 100. As a result, it was determined that multiple amplifier stages would be required to achieve a gain of 1000. For most of the prototypes, a 3-stage architecture, with each stage providing a gain of ~10, was chosen.

The second important consideration was amplifier bandwidth – defined as the operational frequency range of the circuit between a low-frequency 3 dB point and a

high-frequency 3 dB point. (A 3 dB point is the frequency value at which the gain of the amplifier is equal to  $1/\sqrt{2}$  of the maximum gain.) For the prototypes, the main concern regarding bandwidth was noise. Specifically, flicker noise (or 1/f noise) was the only noise source considered since this type of noise is dominant at low frequencies. Flicker noise for a given transistor can be calculated using the following equation:<sup>41, 42</sup>

$$S_{V-flick} = \frac{k_f}{C_{ox}^2 W L f} \,. \tag{2.1}$$

In the equation,  $k_f$  is a fabrication- and bias-dependent constant of the transistor,  $C_{ox}$  is the gate oxide capacitance (which depends on processing parameters and material properties, and was estimated to be 0.345 fF/ $\mu$ m<sup>2</sup> for the TFTs fabricated on the PARC line), W and L are the width and length, respectively, of the gate of the transistor and *f* is frequency (in Hertz). The integral of Eq. 2.1 over frequency yields an equation which shows that flicker noise is proportional to bandwidth. Thus, decreasing the bandwidth will decrease flicker noise. (While flicker noise can also be decreased by maximizing the W and L dimensions of the transistor, that has the undesirable effect of increasing gate capacitance – which generally reduces the efficiency of signal transfer through the circuit.) For the prototype arrays, a target bandwidth extending from ~50 to 100 kHz was chosen. The upper limit corresponds to the high-frequency 3 dB point empirically determined by PARC in the characterization of their single-stage poly-Si amplifier, while the lower limit was chosen somewhat arbitrarily – keeping in mind the effect of bandwidth on flicker noise.

With these design targets in mind (i.e., the number of stages and signal gain, as well as the frequency bandwidth), a total of three amplifier circuit variations were created. The first two variations are three-stage designs, as shown in Figs. 2.1a and 2.1b. Comparing the two variations, the variation shown in Fig. 2.1a consists of two cutoff stages and one bandpass stage (forming a  $1^{st}$  order bandpass), while the variation shown in Fig. 2.1b consists of one cutoff stage and two bandpass stages (forming a  $2^{nd}$  order bandpass). Note that the cutoff stages are different for the two designs – also an arbitrary choice. Between each stage is an AC-coupling capacitor – which allows each stage to set its own DC bias. A value of 500 fF was chosen for this capacitor. Smaller capacitor values were found to attenuate the signal too much, and values larger than 500 fF did not provide significantly better AC-coupling performance.

**Figure 2.1.** Circuit diagrams for the three amplifier circuit variations: (a) 3-stage,  $1^{st}$  order bandpass, (b) 3-stage,  $2^{nd}$  order bandpass, and (c) 1-stage,  $1^{st}$  order bandpass. In each diagram, the triangle is a folded cascode circuit, shown in (d) and the letters A-F denote transistors.

The third amplifier variation, shown in Fig. 2.1c, is a single-stage design consisting of the same bandpass stage used for the other variations – forming a  $1^{st}$  order bandpass. Due to its lower gain, this design is capable of accepting a larger input signal, while still producing an output response that is ~1 V. A larger input signal can be

produced by irradiating an array with higher energy X rays, or by directly injecting signal into the test input pads. The advantage of providing a larger input signal would be to overcome any potential noise that is present at the input of the amplifier (which would be amplified along with the input signal). Since, at the time the prototypes were created, it was unclear what the magnitude of the input noise would actually be, this single-stage design would allow empirical characterization of some prototype arrays even if the magnitude of this noise turned out to be large.

### IV. Comparator circuit design

The comparator component produces an output pulse if the input signal provided by the amplifier component exceeds a user-defined threshold level. For this component, two circuit variations were created for the SPC1 prototypes – one based on a Schmitt trigger and another based on a differential pair circuit.

**Figure 2.2.** Circuit diagrams for the two comparator circuit variations: (a) the Schmitt trigger and (b) the differential pair circuit. The symbol  $V_T$  denotes where the threshold voltage should be applied. See text for details regarding the power rail  $V_{CC}$  and resistors  $R_A$  and  $R_B$ .

The comparator circuit shown in Fig. 2.2a is the Schmitt trigger variation. A key feature of a Schmitt trigger is *hysteresis* – a change in the behavior of a circuit due to something that happened in the past. Specifically, after an input signal exceeds the threshold voltage and the circuit produces an output pulse, the comparator will be unable to produce another output pulse until the input has fallen a certain amount below the threshold level. For the SPC1 prototypes, that amount was chosen to be ~500 mV. The advantage of having hysteresis in the comparator component is that noise in the input signal will not trigger multiple output pulses (assuming the noise is smaller than 500 mV).

However, the Schmitt trigger circuit variation presents a number of challenges. Most importantly, the DC bias level of the Schmitt trigger is directly tied to that of the amplifier – resulting in an unpredictable threshold level. Specifically, due to TFT variations, the DC level of the amplifier can vary from pixel to pixel – requiring, in principle, a different threshold level for every pixel.

A second challenge with the Schmitt trigger circuit is its power consumption profile. When idle, the Schmitt trigger draws very little current from the power rail, but, in order to generate an output pulse, the circuit requires a large amount of current in a very short period of time. This current "spike" can propagate through the power rails and affect the performance of other circuits. Digital components (such as the clock generator and counter) are less susceptible to such spikes, but analog components (such as the amplifier) are very sensitive to power rail spikes. In order to protect the analog components, the prototype arrays employ two power rails – one for analog components and one for digital components. Since the comparator component converts the analog output of the amplifier into a digital output pulse, the comparator can be considered to be both analog and digital. Simulations of the Schmitt trigger circuit showed that energy resolution is greatly affected when the circuit is connected to the digital power rail. As a result, it was decided that this circuit should be connected to the analog power rail – at the cost of possibly affecting the performance of the amplifier component.

In order to overcome this power rail dilemma, the second variation of the comparator component based on a differential pair circuit (shown in Fig. 2.2b) was designed. This circuit splits the "comparing" function and the "output pulse generating" function into two sub-circuits – allowing the more sensitive comparing sub-circuit to be connected to the analog rail while the generating sub-circuit is connected to the digital rail. In addition, the input to the circuit includes an AC-coupling capacitor – which separates the DC bias level of this comparator circuit from that of the amplifier component. The resistors  $R_A$  and  $R_B$  (shown in Fig. 2.2b) ensure that the DC bias level at the input of this circuit is always 2 V (when the power rail,  $V_{CC}$ , is set to 8 V) – which allows the threshold level to be set uniformly for all pixels in an array. However, this circuit lacks hysteresis and may produce erratic output pulses – a problem that was not addressed in the SPC1 prototype designs.

# V. Clock generator circuit design

The clock generator component is responsible for creating a pair of clock pulses suitable for operating the next component (i.e., the counter). Since the preceding component (i.e., the comparator) outputs a single pulse, one requirement of the clock generator is to split this signal into two non-overlapping clock pulses. In addition, the clock generator must guarantee a minimum pulse width for each clock pulse in order for the counter to operate properly – regardless of the width of the input pulse provided by the comparator. Due to the nature of the comparator, the width of the comparator output pulse can vary – depending on the energy of the x-ray photon or due to pulse pile-up when multiple pulses are spaced too closely in time and manifest themselves as a single pulse.

A circuit architecture commonly employed to create pulses with a fixed width is a monostable multivibrator (MSMV). The clock generator component of the prototype arrays is very similar to an MSMV, except it outputs 2 clock pulses (whereas an MSMV typically only outputs a single pulse). For the clock generator component, a total of 4 circuit variations, shown in Figs. 2.3a to 2.3c, were created for the SPC1 prototypes. Note that Fig. 2.3a represents two circuit variations that only differ by the transistor dimensions employed in the circuit.

**Figure 2.3.** Circuit diagrams for the four clock generator circuit variations: (a) the 1SR-5inv design (with two configurations referred to as 1SR-5inv-long and 1SR-5inv-short), (b) the 1SR-7inv design, and (c) the 2SR-3inv design. In each diagram, the triangle-andbubble symbol represents an inverter circuit, shown in (d), the combined plug-shape-andbubble symbol represents a NAND gate, the rectangle represents an SR (i.e., set-reset) latch based on 2 NAND gates, and  $\varphi_1$  and  $\varphi_2$  denote the output clock pulses.

As seen in the figure, all circuit variations employ one or more set-reset (SR) latches. An SR latch outputs a digital "high" signal if the set input (labeled S-bar) is triggered, and will continue to output this signal until the reset input (labeled R-bar) is triggered – at which time, it changes to and continues to output a digital "low" signal. By connecting the output labeled Q (or, in the case of 2SR-3inv, Q-bar) to the reset input, the circuit will automatically reset itself after being triggered – resulting in a fixed-width output pulse. The width of the pulse can be adjusted by introducing delay elements between Q and R-bar. For the prototype arrays, these delay elements took the form of an inverter circuit (shown in Fig. 2.3d). Decreasing the W/L ratio of the transistors in that circuit, as well as increasing the number of inverters, increases the delay.

For the clock generator circuit variations involving a single SR latch (shown in Figs. 2.3a and 2.3b), the  $\varphi_1$  clock pulse is generated by the output labeled Q-bar. Note that the two inverter circuits before the  $\varphi_1$  label are intended as buffers, not delay elements. The  $\varphi_2$  clock pulse is generated by attaching a NAND gate to the chain of delay-generating inverters. Note that the number of inverters straddled by the NAND

gate (and also the W/L ratio of those inverters) controls the width of the  $\varphi_2$  pulse, and that the NAND gate must span an odd number of inverters.

For the remaining circuit variation shown in Fig. 2.3c, the  $\varphi_1$  and  $\varphi_2$  clock pulses are generated in a different manner – by tapping the 3-inverter chain. The  $\varphi_1$  pulse is generated when S-bar is triggered, and the  $\varphi_2$  pulse is generated when R-bar is triggered. Again, the inverter circuit before the  $\varphi_1$  and  $\varphi_2$  outputs are buffers.

The four clock generator circuit variations described above were created in the spirit of addressing a "flaw" discovered in the circuit behavior during the design process. For the single-SR-latch configuration, input pulses with a very specific spacing in time can cause the clock generator to produce clock pulses that are overlapping and/or do not have the required minimum pulse width. Either of these conditions would invalidate the value stored in the counter component, as explained in more detail in Sec. VI of this chapter. This problem, referred to as racing, was first discovered in the 1SR-5inv-long design, and the 1SR-5inv-short design was created to try to make the probability of encountering the problem less likely. Specifically, the "short" variant employs transistors with shorter gates, which decreases the amount of delay produced by the inverter chain. Due to this modification, racing will only occur if the input pulses are spaced closer together. For the 1SR-7inv design, even closer input pulse spacing is required for racing to occur. Unlike the "short" variant, the 1SR-7inv design does not rely on further shortening of the transistor gates. Due to minimum feature size limitations, the length of the gates could not be fabricated shorter than those specified for the "short" variant, and thus the 1SR-7inv design employs carefully selected transistor dimensions for the inverters in order to "shape" the pulse as it propagates through the inverter chain in an attempt to suppress racing.

However, none of these three circuit variations are immune to racing. Due to the statistical nature of x-ray photon generation, the flux rate reported for a given imaging modality represents only an average rate (e.g., on the order of 10<sup>6</sup> to 10<sup>7</sup> counts per second per mm<sup>2</sup> for radiography [see Appendix 2.B])<sup>43</sup>. Thus, there is always the possibility of encountering input pulses spaced any arbitrary distance apart. The fourth variation, the 2SR-3inv design shown in Fig. 2.3c, circumvents the design flaw entirely by adding a second SR latch to the input of the circuit. This SR latch acts as an enable flag for the clock generator. When an input pulse arrives, this additional latch will produce an "enable" signal that allows the rest of the clock generator circuit to operate. If additional input pulses arrive while the enable signal is active, they are ignored. The enable signal will be deactivated after the circuit has finished generating the two clock pulses, at which time the circuit is ready for another input pulse.

## VI. Counter circuit design

The counter is the final component in the signal chain and stores the number of counts detected by the pixel circuit. The number of counts is stored in a binary format in *bits*. For the prototype arrays, a 9-bit, maximum-length linear feedback shift register (LFSR) architecture was employed. The 9-bit length chosen for the prototype arrays was

arbitrary. A clinically useful imager would likely require more bits. A schematic diagram of the LFSR is shown in Fig. 2.4a.

**Figure 2.4.** Schematic diagram of (a) the 9-bit, maximum-length LFSR, as well as circuit diagrams for one bit of each counter component circuit variation: (b) the resistor-biased differential pair, (c) the transistor-biased differential pair, and (d) the gated CMOS.

For the counter component, three circuit variations were created for the SPC1 prototypes. For a given circuit variation, the bits are identical and the circuit diagram for one bit of each variation is shown in Figs. 2.4b to 2.4d. Note that, for the circuit of a given bit, the "out" node is connected to the "in" node of the next bit – and the out node of the last bit is connected to the in node of the first bit. Similarly, where applicable, the "out-bar" node of one bit connects to the "in-bar" node of the next bit – and the out-bar node of the last bit is connected to the in-bar node of the first bit. All circuit variations have a maximum count of 511 (i.e.,  $2^9 - 1$ ) since the LFSR circuit has an invalid state when all bits are zero. This invalid state can occur randomly when the array is connected to be

very low (approximately 1 in 512 for a 9-bit counter, assuming an equal probability of a bit powering up in either a high "1" or low "0" state). While methods for preventing this invalid state (such as introducing logic that would force a bit to a high state upon power up) were considered, no solutions were implemented in the prototype arrays.

The differential pair bit designs, one resistor-biased and one transistor-biased (shown in Figs. 2.4b and 2.4c, respectively), were the first two circuit variations created. Compared to the transistor-biased variation, the resistor-biased variation has the advantage of requiring one less wire, which simplifies wire routing. On the other hand, the transistor-biased variation allows for user-controlled fine-tuning of the bias – which may be necessary if TFT variations cause the bits to perform poorly.

During the design process, it was discovered that both differential-pair-based circuit designs are sensitive to TFT variations – specifically, variations in electron and hole mobility. The differential bits employ a self-reinforcing loop to store a value. In order to change the value in the bit, a large amount of current is required to overcome the self-reinforcing loop. If the transistors of the self-reinforcing loop have very high mobility or if the transistors responsible for changing the value of the bit have very low mobility, the current will not be sufficient to override the self-reinforcing loop and change the value.