## Bridging the Scalability Gap by Exploiting Error Tolerance for Emerging Applications

by

Parker Hill

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in The University of Michigan 2018

#### **Doctoral Committee:**

Assistant Professor Lingjia Tang, Co-Chair Assistant Professor Jason Mars, Co-Chair Assistant Professor Hun Seok Kim Professor Scott Mahlke

## Parker Hill

parkerhh@umich.edu

ORCID iD: 0000-0002-6114-6033

© Parker Hill 2018

#### ACKNOWLEDGEMENTS

I thank my dissertation committee – Lingjia Tang, Jason Mars, Scott Mahlke, and Hun Seok Kim – for their feedback while writing this dissertation. I particularly appreciate the guidance and support I have received by having Lingjia, Jason, and Scott as co-advisors. My dissertation would not be nearly as exciting or robust if not for Jason's ability to make a compelling case for seemingly every research direction that I've pursued and Lingjia's ability to pinpoint key questions throughout my research. In addition to those in formal advisory roles, I thank Michael Laurenzano for always being available and helping refine every aspect of my research.

I am grateful to all of the members of Clarity Lab. Their contagious work ethic and ambition provided me with the motivation to conduct my work with equally high determination and standards. Specifically, I owe Animesh Jain gratitude for invaluable collaboration and enduring countless practice talks.

I thank my parents, Brent and Caroline, for their love and support before and throughout this process. Architecting the foundation of a computer architecture researcher is certainly more difficult than being one. You truly instilled the characteristics in me that make me a happy and productive researcher. Finally, I express gratitude towards my brothers – Spencer, Mason, and Connor – for the innumerable discussions and debates, providing me with the fortitude to thrive in graduate school.

## TABLE OF CONTENTS

| ACKNOWLE    | DGEMENTS                                                                                                                                                                                                                                                                                                                | ii               |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| LIST OF FIG | URES                                                                                                                                                                                                                                                                                                                    | vi               |

| LIST OF TAI | BLES                                                                                                                                                                                                                                                                                                                    | xi               |

| ABSTRACT    |                                                                                                                                                                                                                                                                                                                         | xii              |

| CHAPTER     |                                                                                                                                                                                                                                                                                                                         |                  |

| I. Introd   | luction                                                                                                                                                                                                                                                                                                                 | 1                |

| 1.1         | Motivation  1.1.1 Output Quality Guarantees  1.1.2 Removing Insignificant Computation  Exploiting Error Tolerance  1.2.1 NinjaProx: Achieving Accuracy Guarantees for Approximate Computing  1.2.2 DeftNN: Addressing Bottlenecks for DNN Execution on GPUs via Synapse Vector Elimination and Nearcompute Data Fission | 3<br>3<br>5<br>9 |

| 1.3         | 1.2.3 Rethinking Numerical Representations for DNNs Summary of Contributions                                                                                                                                                                                                                                            | 11<br>13         |

| II. Backş   | ground and Related Work                                                                                                                                                                                                                                                                                                 | 15               |

| 2.1<br>2.2  | Output Quality Guarantees                                                                                                                                                                                                                                                                                               | 15<br>17         |

|      | 2.3    | Customized Hardware                                 | 18 |

|------|--------|-----------------------------------------------------|----|

| III. | Realiz | ing Service Level Agreements on Result Accuracy for |    |

|      | Appro  | oximate Data-parallel Programs                      | 19 |

|      | 3.1    | Accuracy SLAs                                       | 21 |

|      |        | 3.1.1 Motivation                                    | 21 |

|      |        | 3.1.2 Defintion                                     | 22 |

|      |        | 3.1.3 ASLA Specification                            | 23 |

|      | 3.2    | NinjaProx Overview                                  | 23 |

|      |        | 3.2.1 Programming Interface                         | 24 |

|      |        | 3.2.2 Compilation                                   | 25 |

|      |        | 3.2.3 Runtime Support                               | 26 |

|      | 3.3    | Guarantee Enforcement                               | 27 |

|      |        | 3.3.1 Map-based Model                               | 27 |

|      |        | 3.3.2 Guarantee Engine Overview                     | 30 |

|      |        | 3.3.3 Computing an Accuracy Distribution            | 31 |

|      |        | 3.3.4 Deriving an Accuracy Guarantee                | 32 |

|      | 3.4    | Evaluation                                          | 40 |

|      |        | 3.4.1 Experimental Methodology                      | 40 |

|      |        | 3.4.2 Accuracy Guarantees                           | 44 |

|      |        | 3.4.3 End-to-end Approximation System               | 48 |

|      |        | 3.4.4 Runtime Analysis                              | 51 |

|      |        | 3.4.5 Comparison to Static Oracle                   | 51 |

|      | 3.5    | Summary                                             | 53 |

| IV.  | DeftN  | N: Addressing Bottlenecks for DNN Execution on GPUs |    |

|      |        | napse Vector Elimination and Near-compute Data Fis- |    |

|      | ·      |                                                     | 55 |

|      |        |                                                     |    |

|      | 4.1    | Challenges                                          | 56 |

|      |        | 4.1.1 Computation Elimination                       | 56 |

|      |        | 4.1.2 On-chip Memory Bandwidth                      | 60 |

|      | 4.2    | System Overview                                     | 62 |

|      | 4.3    | Optimization Techniques                             | 64 |

|      |        | 4.3.1 Synapse Vector Elimination                    | 64 |

|      |        | 4.3.2 Near-compute Data Fission                     | 74 |

|      | 1.1    | Evaluation                                          | 70 |

|           | 4.4.1                                                | Methodology                                                                                                                    |

|-----------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

|           | 4.4.2                                                | Overall DeftNN System                                                                                                          |

|           | 4.4.3                                                | Synapse Vector Elimination 81                                                                                                  |

|           | 4.4.4                                                | Near-compute Data Fission                                                                                                      |

|           | 4.4.5                                                | Hardware-accelerated Data Fission                                                                                              |

|           | 4.4.6                                                | Performance-Accuracy Tradeoffs 87                                                                                              |

|           | 4.4.7                                                | cuDNN with DeftNN Optimization 90                                                                                              |

|           | 4.4.8                                                | Comparison to Prior Work 90                                                                                                    |

| 4.5 S     | ummar                                                | y                                                                                                                              |

| . Rethink | king Nı                                              | imerical Representations for Deep Neural Net-                                                                                  |

| works .   |                                                      |                                                                                                                                |

| 5.1 C     | Customi                                              | zed Precision Hardware                                                                                                         |

|           | 5.1.1                                                | Design Space                                                                                                                   |

|           | 5.1.2                                                | Customized Precision Types 96                                                                                                  |

|           | 5.1.3                                                | Hardware Implications                                                                                                          |

| 5.2 N     | Aethodo                                              | ology                                                                                                                          |

|           | F 0 1                                                | Accuracy                                                                                                                       |

|           | 5.2.1                                                | V                                                                                                                              |

|           | 5.2.1 $5.2.2$                                        | Efficiency                                                                                                                     |

|           |                                                      | v .                                                                                                                            |

|           | 5.2.2                                                | Efficiency                                                                                                                     |

|           | 5.2.2<br>5.2.3                                       | Efficiency                                                                                                                     |

|           | 5.2.2<br>5.2.3<br>5.2.4                              | Efficiency                                                                                                                     |

|           | 5.2.2<br>5.2.3<br>5.2.4<br>Experim                   | Efficiency       100         Training       101         Efficient Customized Precision Search       102         ents       103 |

|           | 5.2.2<br>5.2.3<br>5.2.4<br>Experim<br>5.3.1          | Efficiency                                                                                                                     |

|           | 5.2.2<br>5.2.3<br>5.2.4<br>Experim<br>5.3.1<br>5.3.2 | Efficiency                                                                                                                     |

## LIST OF FIGURES

## Figure

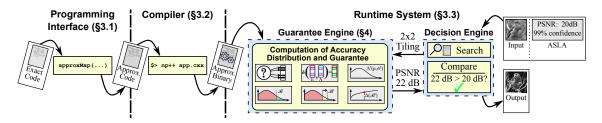

| 3.1 | End-to-end NinjaProx: after compiling an approximation-amenable application written using the NinjaProx programming interface, the runtime system searches the set of approximations based on the accuracy guarantees supplied by the guarantee engine to select an approximation.                                                                                                                              | 20 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Original implementation of binarize, an application that segments pixels based on intensity.                                                                                                                                                                                                                                                                                                                    | 26 |

| 3.3 | Example of NinjaProx applied to a binarize implementation. The ninjaprox::approxMap function writes a value to each element in the output, after automatically finding the approximation param-                                                                                                                                                                                                                 |    |

| 9 / | eters that fit the ASLA                                                                                                                                                                                                                                                                                                                                                                                         | 28 |

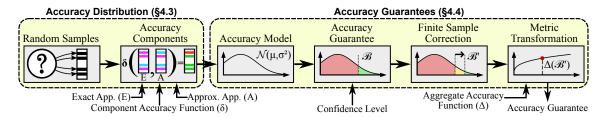

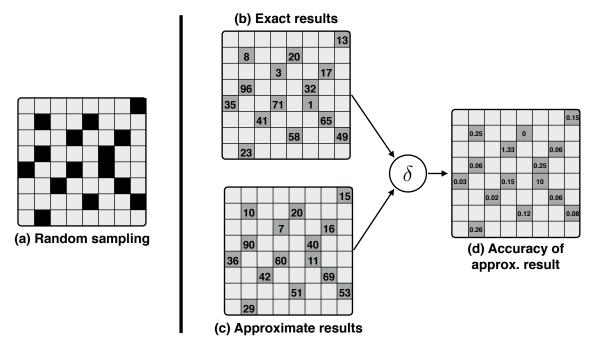

| 3.4 | Guarantee engine overview comprised of two steps: accuracy inference and guarantee generation                                                                                                                                                                                                                                                                                                                   | 28 |

| 2.5 |                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

| 3.5 | Example accuracy distribution derivation.                                                                                                                                                                                                                                                                                                                                                                       | 29 |

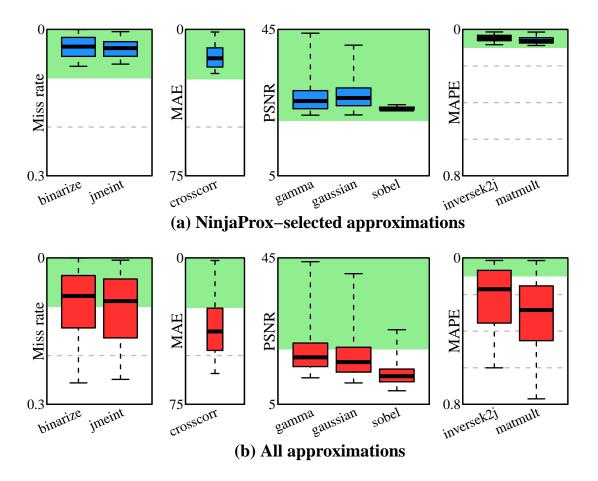

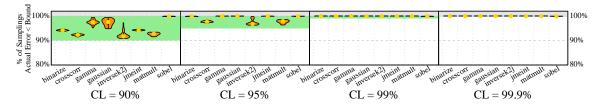

| 3.6 | A comparison between the accuracy resulting from approximations that pass the NinjaProx guarantee engine (CL=90%) to the accuracy of all approximations, showing that the guarantee engine catches all                                                                                                                                                                                                          |    |

|     | approximations that do not conform to the specified ASLA                                                                                                                                                                                                                                                                                                                                                        | 43 |

| 3.7 | Distributions of how frequently the accuracy guarantee meets the accuracy target across all applications, inputs and approximations and 4 confidence levels of 90%, 95%, 99% and 99.9%. By observing that all such experiments are above the specified CL (i.e., that the entire violin is within the shaded region), we can verify that the statistical guarantees made by the NinjaProx guarantee engine work |    |

|     | as expected                                                                                                                                                                                                                                                                                                                                                                                                     | 44 |

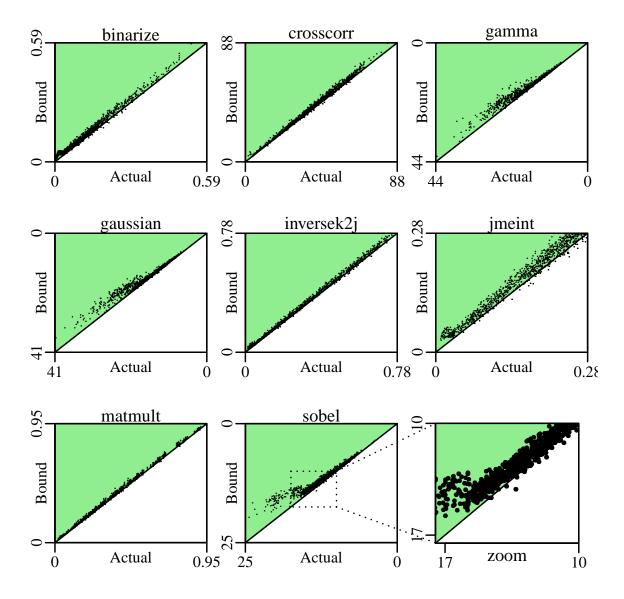

| 3.8  | Scatter plots comparing actual accuracy (x-axis) to guarantee accuracy (y-axis) for a confidence level of 90%. A point in the green         |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | shaded region indicates a guarantee that achieves more accuracy                                                                             |    |

|      | than the target. The white regions should, and do, contain less than                                                                        |    |

|      | 10% of the points in each plot, representing a maximum of 10% out-                                                                          |    |

|      | side of the CL=90% confidence interval. The accuracy guarantees                                                                             |    |

|      | heavily skew toward the shaded region and closely track the actual                                                                          |    |

|      | accuracy                                                                                                                                    | 46 |

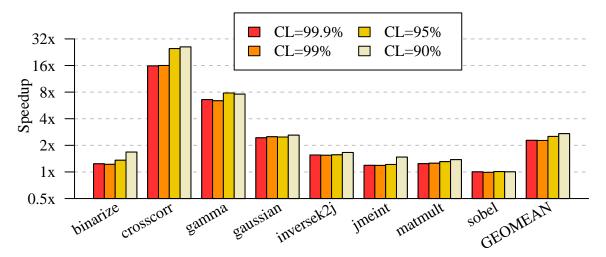

| 3.9  | Speedup achieved per application across all inputs for the NinjaProx runtime system with $CL = \{90\%, 95\%, 99\%, 99.9\%\}$ , showing that |    |

|      | less strict ASLAs allow for higher performance                                                                                              | 49 |

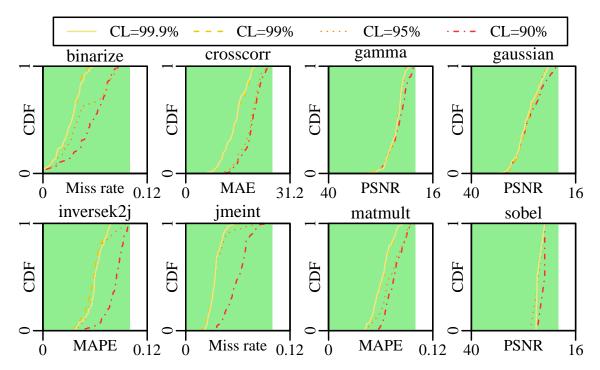

| 3.10 | CDFs of accuracy achieved for all application inputs when allowing                                                                          | 45 |

|      | NinjaProx to choose approximations, showing that accuracy targets                                                                           |    |

|      | are always met and that the accuracy approaches the target output                                                                           |    |

|      | quality limit as a less strict confidence level is used in the ASLA                                                                         | 50 |

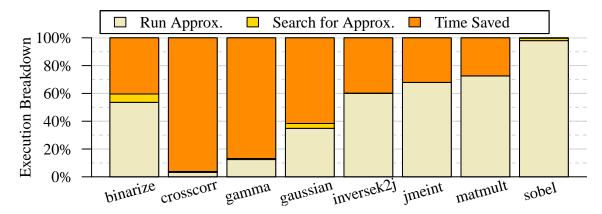

| 3.11 | Time breakdown of the NinjaProx runtime system, showing very                                                                                |    |

|      | low overhead for selecting approximations and significant time-to-                                                                          |    |

|      | solution improvements                                                                                                                       | 52 |

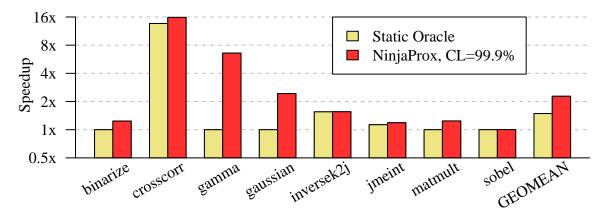

| 3.12 | Speedup achieved by NinjaProx for $CL = 99.9\%$ compared to a static                                                                        |    |

|      | oracle, showing that NinjaProx outperforms the static oracle. The                                                                           |    |

|      | accuracy is above the target accuracy in all cases for both techniques.                                                                     | 53 |

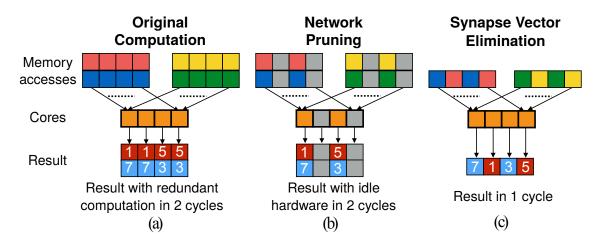

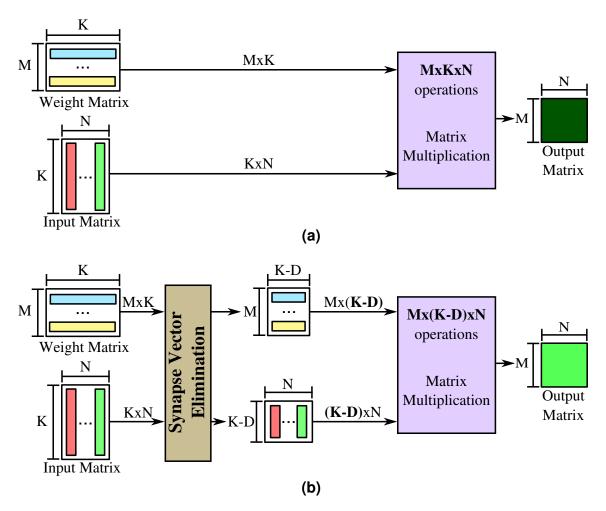

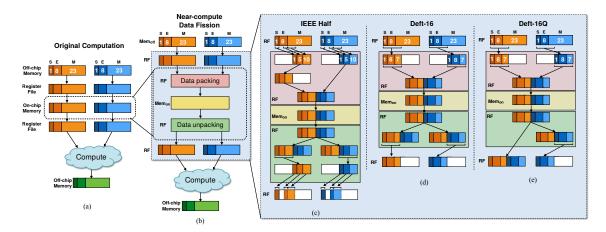

| 4.1  | (a) Original DNN computation resulting in redundant computation,                                                                            |    |

|      | (b) network pruning [40,41] resulting in underutilized hardware, and                                                                        |    |

|      | (c) synapse vector elimination showing efficient use of resources                                                                           | 57 |

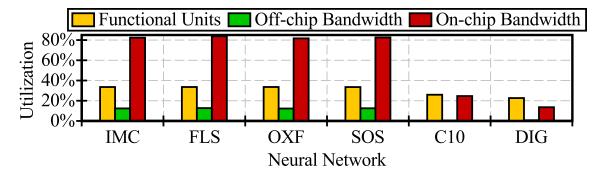

| 4.2  | GPU utilization when processing DNNs, showing the on-chip mem-                                                                              |    |

|      | ory bandwidth bottleneck                                                                                                                    | 59 |

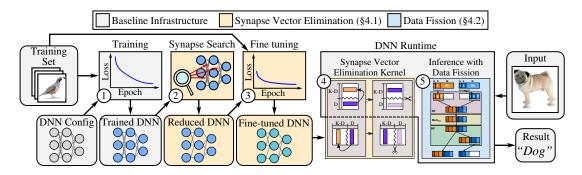

| 4.3  | Overview of the DeftNN framework                                                                                                            | 59 |

| 4.4  | High-level view of synapse vector elimination, showing that (a) the                                                                         |    |

|      | exact computation is an $M \times K$ by $K \times N$ matrix multiplication,                                                                 |    |

|      | while (b) synapse vector elimination preprocesses the input to make                                                                         |    |

|      | the computation an $M \times (K-D)$ by $(K-D) \times N$ matrix multiplication.                                                              | 65 |

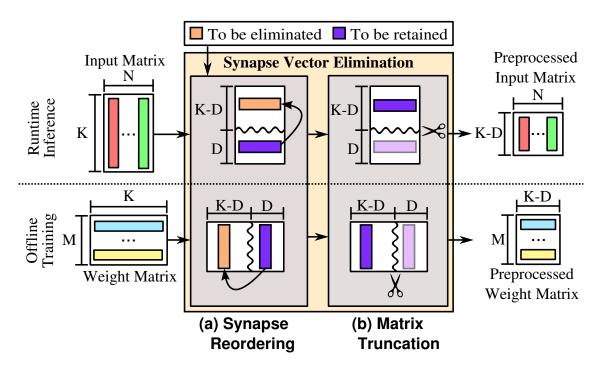

| 4.5  | Internal workings of synapse vector elimination, showing compacting                                                                         |    |

|      | retained synapses so that the matrix can be trivially resized                                                                               | 66 |

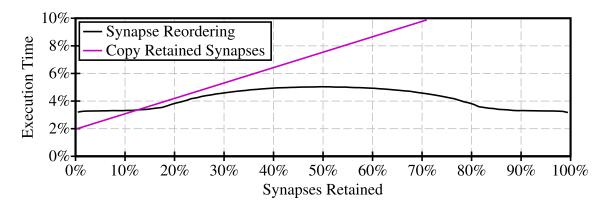

| 4.6  | Overhead from synapse reordering compared to copying all retained                                                                           |    |

|      | synapses, showing that DeftNN substantially reduces the overhead of                                                                         |    |

|      | input transformation by reordering synapses at useful design points                                                                         |    |

|      | (;50% retained)                                                                                                                             | 69 |

|      |                                                                                                                                             |    |

| 4.7          | (a) The original design, (b) high level view of a design with near-compute data fission, (c) fission using the IEEE 754 single precision |     |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------|-----|

|              | floating-point to the half precision variant, (d) fission using the Deft-                                                                |     |

|              | 16 floating-point format, and (e) fission using the optimized Deft-                                                                      |     |

|              | 16Q floating-point conversion format                                                                                                     | 71  |

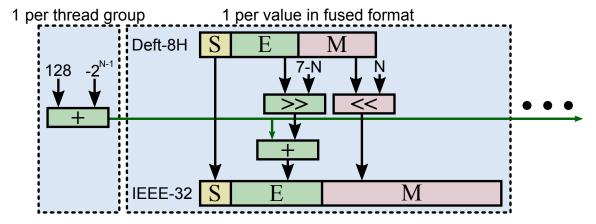

| 4.8          | Fission in the DFU, showing hardware to apply fission to an 8-bit,                                                                       |     |

|              | variable exponent length (N) floating-point value to an IEEE single-                                                                     |     |

|              | precision value.                                                                                                                         | 77  |

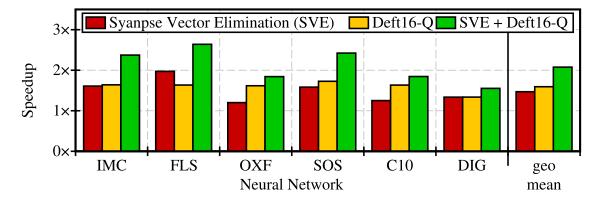

| 4.9          | Speedup achieved by DeftNN when applying synapse vector discard-                                                                         |     |

|              | ing, data fission, and the combination of the two, showing the sig-                                                                      |     |

|              | nificant benefits of each technique and their efficacy when applied in                                                                   | 0.1 |

| 1.10         | concert.                                                                                                                                 | 81  |

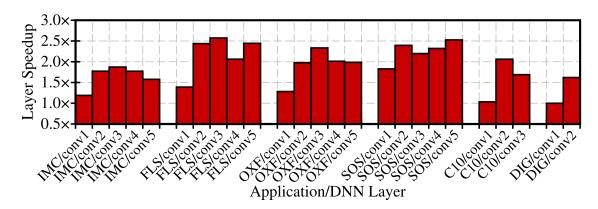

| 4.10         | Per-layer speedup when applying synapse vector elimination, show-                                                                        |     |

|              | ing large performance improvements, particularly for the large DNNs (IMC, FLS, OXF, and SOS)                                             | 82  |

| 4.11         | (IMC, FLS, OXF, and SOS)                                                                                                                 | 02  |

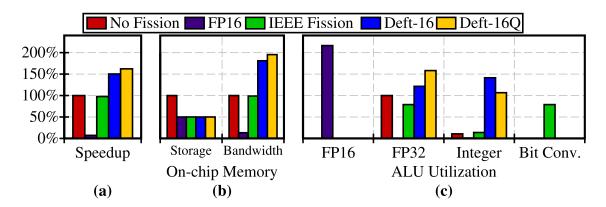

| 4.11         | different formats (IEEE Fission, Deft-16, and Deft-16Q) compared                                                                         |     |

|              | to 32-bit storage and computation (No Fission) along with (b,c) per-                                                                     |     |

|              | tinent profiling metrics, showing that Deft-16Q, achieves the highest                                                                    |     |

|              | performance because of improved effective on-chip memory band-                                                                           |     |

|              | width.                                                                                                                                   | 83  |

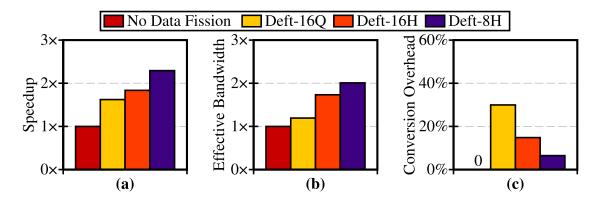

| 4.12         | Comparison of no near-compute data fission, software-only fission                                                                        |     |

|              | (Deft-16Q), and hardware accelerated 16-bit (Deft-16H) and 8-bit                                                                         |     |

|              | (Deft-8H) fission, showing that (a) performance is improved as (b) ef-                                                                   |     |

|              | fective on-chip bandwidth is increased with smaller representations,                                                                     |     |

|              | without (c) restrictive conversion overhead                                                                                              | 84  |

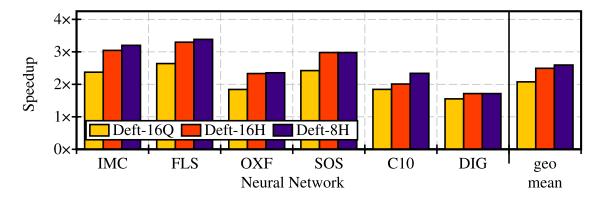

| 4.13         | DeftNN runtime performance achieved by employing software-only                                                                           |     |

|              | (Deft-16Q) and hardware-accelerated (Deft-16H/8H) fission, show-                                                                         |     |

|              | ing substantial speedup via hardware-accelerated DeftNN                                                                                  | 86  |

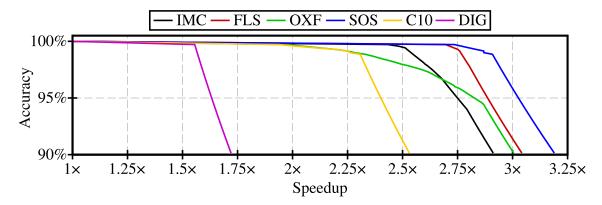

| 4.14         | DeftNN Pareto frontiers, showing a range of advantageous operating                                                                       |     |

|              | points as the accuracy target is tuned                                                                                                   | 88  |

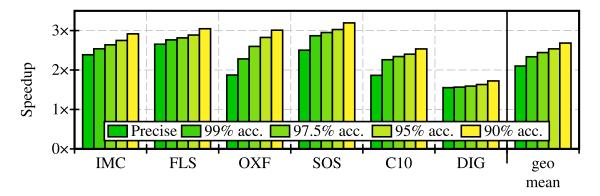

| 4.15         | Speedup achieved by DeftNN at particular accuracy levels, showing                                                                        |     |

|              | that DeftNN exposes a range of useful design points for approximate                                                                      | 0.0 |

| 1 1 <i>G</i> | computing                                                                                                                                | 88  |

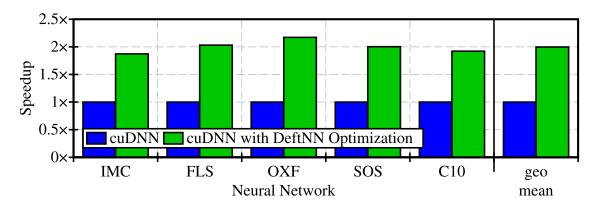

| 4.16         | Speedup of cuDNN [20] with DeftNN optimizations, showing DeftNN provides similar speedup for cuDNN as it provides for MAGMA              | 89  |

|              | Drovides SHIHIAL SDEEDHD TOLCHDININ AS IL DROVIDES TOLIVIACTIVIA                                                                         | 0.5 |

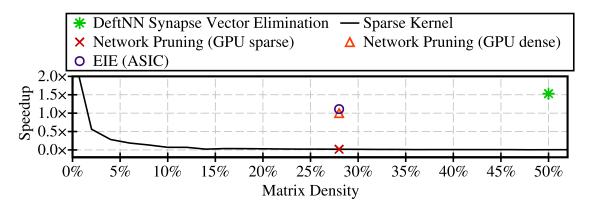

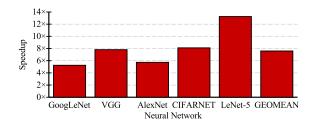

| 4.17 | End-to-end speedup of DeftNN synapse vector elimination, software executed network pruning [41], and EIE [39] hardware-accelerated                                                                   |     |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | network pruning                                                                                                                                                                                      | 92  |

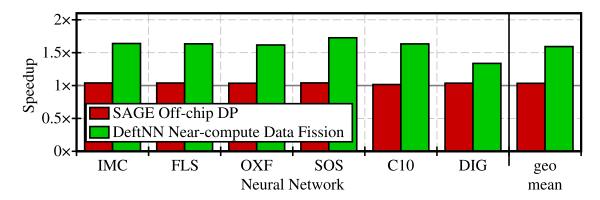

| 4.18 | Comparison of DeftNN data fission to off-chip data packing [98].                                                                                                                                     | 93  |

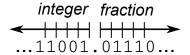

| 5.1  | A fixed-point representation. Hardware parameters include the total number of bits and the position of the radix point                                                                               | 95  |

| 5.2  | A floating-point representation. Hardware parameters include the                                                                                                                                     |     |

|      | number of mantissa and exponent bits, and the bias                                                                                                                                                   | 95  |

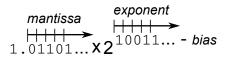

| 5.3  | Floating point multiply-accumulate (MAC) unit with various levels of detail: (a) the high level mathematical operation, (b) the modules                                                              |     |

|      | that form a floating point MAC, and (c) the signal propagation of                                                                                                                                    |     |

|      | the unit.                                                                                                                                                                                            | 97  |

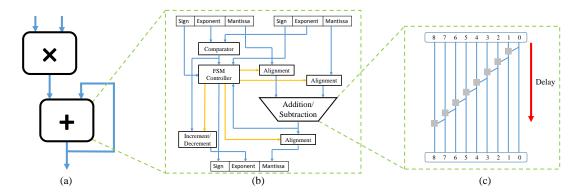

| 5.4  | Delay and area implications of mantissa width, normalized to a 32-                                                                                                                                   |     |

|      | bit Single Precision MAC with 23 mantissa bits                                                                                                                                                       | 99  |

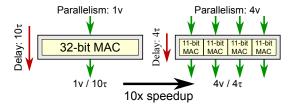

| 5.5  | Speedup calculation with a fixed area budget. The speedup exploits                                                                                                                                   |     |

|      | the improved function delay and parallelism                                                                                                                                                          | 99  |

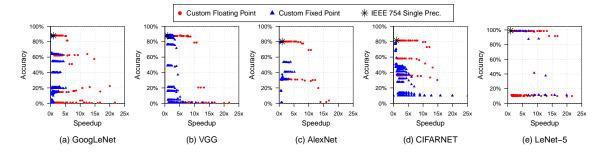

| 5.6  | The inference accuracy versus speedup design space for each of the neural networks, showing substantial computational performance improvements for minimal accuracy degradation when customized pre- |     |

|      | - · · · · · · · · · · · · · · · · · · ·                                                                                                                                                              | 104 |

| 5.7  | The speedup and energy savings as the two parameters are adjusted                                                                                                                                    | 104 |

| 5.1  | for the custom floating point and fixed-point representations. The                                                                                                                                   |     |

|      | marked area denotes configurations where the total loss in AlexNet                                                                                                                                   |     |

|      | <u>e</u>                                                                                                                                                                                             | 106 |

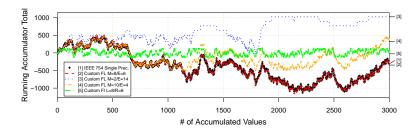

| 5.8  | The accumulation of weighted neuron inputs for a specific neuron                                                                                                                                     | 100 |

|      | with various customized precision DNNs as well as the IEEE 754                                                                                                                                       |     |

|      | single precision floating point configuration for reference. FL and FI                                                                                                                               |     |

|      | are used to abbreviate floating point and fixed-point, respectively.                                                                                                                                 |     |

|      | The format parameters are as follows: M=mantissa, E=exponent,                                                                                                                                        |     |

|      | , , ,                                                                                                                                                                                                | 107 |

| 5.9  | The linear fit from the correlation between normalized accuracy and                                                                                                                                  |     |

|      | last layer activations of the exact and customized precision DNNs                                                                                                                                    | 107 |

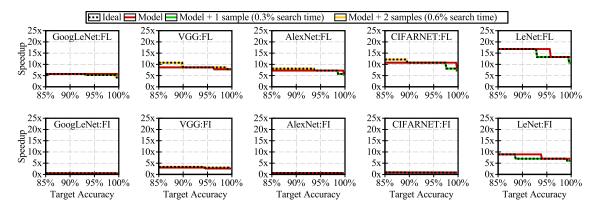

| 5.10 | The speedup achieved by selecting the customized precision using       |     |

|------|------------------------------------------------------------------------|-----|

|      | an exhaustive search (i.e. the ideal design) and prediction using      |     |

|      | the accuracy model with accuracy evaluated for some number of          |     |

|      | configurations (model + X samples). The floating-point (FL) and        |     |

|      | fixed-point (FI) results are shown in the top and bottom rows, re-     |     |

|      | spectively. The model with two evaluated designs produces the same     |     |

|      | configurations, but requires <0.6\% of the search time                 | 109 |

| 5.11 | The speedup resulting from searching for the fastest setting with less |     |

|      | than 1% inference accuracy degradation. All selected customized pre-   |     |

|      | cision DNNs meet this accuracy constraint                              | 112 |

## LIST OF TABLES

| <u>Table</u> |                                                    |    |

|--------------|----------------------------------------------------|----|

| 3.1          | Applications and input sets used in the evaluation | 37 |

| 4.1          | The set of benchmarks used to evaluate DeftNN      | 79 |

#### ABSTRACT

In recent years, there has been a surge in demand for intelligent applications. These emerging applications are powered by algorithms from domains such as computer vision, image processing, pattern recognition, and machine learning. Across these algorithms, there exist two key computational characteristics. First, the computational demands they place on computing infrastructure is large, with the potential to substantially outstrip existing compute resources. Second, they are necessarily resilient to errors due to their inputs and outputs being inherently noisy and imprecise.

Despite the staggering computational requirements and resilience of intelligent applications, current infrastructure uses conventional software and hardware methodologies. These systems needlessly consume resources for every bit of precision and arithmetic. To address this inefficiency and help bridge the performance gap caused by intelligent applications, this dissertation investigates exploiting error tolerance across the hardware-software stack. Specifically, we propose (1) statistical machinery to guarantee that accuracy is not compromised when removing work or precision, (2) a GPU optimization framework for work skipping and bottleneck mitigation, and (3) exploration of unconventional numerical representations to steer future hardware designs.

## CHAPTER I

## Introduction

In the past few years, there has been a surge demand for intelligent applications, as companies like Apple, Google, Microsoft and Amazon devise increasingly wide-reaching and sophisticated software offerings [3, 5, 37, 73]. Underlying these applications are algorithms from domains such as computer vision, image processing, pattern recognition and machine learning. Two characteristics of these domains have become evident in recent years. First, the computational demands they place on computing infrastructure are large, with the potential to outstrip available compute resources by a large margin [45]. Second, their inputs and outputs are inherently noisy and imprecise. Despite these staggering computational requirements and imprecise inputs and outputs, current infrastructure uses conventional methodologies resulting in redundant computations and overly precise arithmetic. However, to remove insignificant work and precision three key challenges must be addressed.

First, developers and service operators do not trust that accuracy will not be compromised when computation and precision is removed. To build trust in these approaches, new runtime systems must be designed that can guarantee consistent output quality. Second, the architecture must be considered in order to exploit error tolerance to improve performance. For example, cutting raw computation (e.g., dynamic floating-point instructions) does not directly map to performance on commodity accelerators due to the wide vector units present in the architecture. To improve performance, the microarchitectural nuances of such accelerators must be carefully considered. Finally, to improve performance by developing customized accelerators for these emerging application, we must explore a large trade-off space between performance and accuracy. Specifically, the accelerator's underlying numerical representation, a critical factor in performance, has not been investigated due to the difficultly in simulating all of these representations.

This dissertation addresses these challenges to promote the widespread use of exploiting error tolerance. In the first chapter, it proposes a runtime system that provides statistical output quality guarantees, allowing approximated computations to be trusted in deployment. We achieve this by casting the problem of finding an accurate approximation to a statistical one and design a framework around robust statistical methods to guarantee output quality. In the next chapter, this dissertation introduces techniques to efficiently exploit error tolerance for DNNs being executed on GPUs. It does this by tailoring work skipping and memory compression to the GPU architecture, requiring (1) skipping work in a very structured manner to fully utilized GPU vector units and (2) decompressing values with very little overhead to avoid undermining the benefits of mitigating the on-chip memory bandwidth architectural bottleneck. Finally, this dissertation proposes exploring the numerical

representation design space to achieve even higher performance benefits for custom DNN accelerators.

#### 1.1 Motivation

In this section, we motivate the need of runtime systems and approximation techniques that exploit error tolerance in emerging applications.

#### 1.1.1 Output Quality Guarantees

There has recently been a surge of popularity in intelligent webservices, as companies like Apple, Google, Microsoft and Amazon devise increasingly wide-reaching and sophisticated software offerings [3,5,37,73]. The underlying computational components that are central to such services are often computations that are amenable to approximation from domains that include computer vision, image processing, pattern recognition and machine learning. Two characteristics of these domains have become evident in recent years. First, the computational demands they place on computing infrastructure are large, with the potential to outstrip available compute resources by a large margin [45]. Second, their inputs and outputs are inherently noisy and imprecise.

The confluence of these two characteristics make such applications prime candidates for approximate computing, where small, often imperceptible degradations in output quality can be traded for large improvements in performance or energy. While there are a number of techniques that have been devised for both hardware and software to make this tradeoff [4,46,51,63,98,99], one of the key challenges that remains

in this area and holds back the adoption of approximate computing lies in providing guarantees as to how much accuracy will be lost when applying approximation.

Conventional approximation systems use empirical demonstrations to validate that their approaches to steering approximation provide the accuracy levels intended by the designers, often based on devising training sets resembling the input sets that will be seen in production [29,51,72,102], a notoriously difficult problem to solve [26]. Other systems leverage training-free quality control mechanisms [63, 97, 98], often by assuming that recent inputs will resemble future inputs and adjusting the level of approximation accordingly. In all cases, however, this class of systems cannot provide guarantees of result quality on difficult cases that the system is not trained or designed to handle.

Prior works have taken steps to address the more fundamental problem of providing analytical or statistical guarantees of result quality. These works fall into two classes:

- Static Analysis This class of techniques uses formal static analysis to reason about program accuracy under approximation [10,11,16,74,76], an approach that has two limitations. First, it is difficult to scale such approaches to problems beyond a limited level of complexity (dozens of lines of code). They can be applied to simple programs, for particular kinds of approximation techniques, but have difficulty scaling beyond these narrow cases. Second, these approaches are driven by the worst-case accuracy, and typically leave significant untapped performance opportunities on the table when the worst case fails to materialize.

- Customized Solutions This class of techniques leverage quality guarantee

mechanisms that are specific to a set of assumptions around the application(s) or approximation technique(s), such as database aggregation operations [15] or reductions in a MapReduce framework [36,84]. Such techniques are important, but cannot be applied beyond the scope of applications and approximation techniques they are designed to cover.

Instead of designing application-specific techniques, this paper begins with the observation that many applications amenable to approximation have similar computational patterns, coming from the domains of machine learning, pattern recognition, computer vision, image processing and data mining. Exploiting this commonality, we describe a solution that provides statistical accuracy guarantees when applying approximation to a broad class of applications characterized with the property we describe as map-based. We describe an application as being map-based if parts of the application can be executed in parallel, and can also be executed out-of-order and incrementally. We leverage these properties to first compute a randomly-selected subset of the application output both with and without approximation applied. The fact that random sampling can be applied to the problem allows us to leverage statistical techniques to build statistical guarantees about the accuracy of the output when applying approximation.

## 1.1.2 Removing Insignificant Computation

This section motivates the use of exploiting error tolerance in emerging applications, specifically deep neural networks. In the following two subsections, we find this need for both commodity and customized hardware.

#### 1.1.2.1 Commodity Hardware

As user demand for state-of-the-art technologies in the domains of computer vision, speech recognition, and natural language processing (NLP) continues to increase, system designers are tasked with supporting increasingly sophisticated machine learning capabilities [44,45]. An important trend that impacts the design of current and future intelligent systems is the convergence of industry toward deep learning as the computational engine providing these services. Large companies, including Google [104], Facebook [33], and Microsoft [89], among others [65], are using deep neural networks (DNNs) as the primary technique underpinning machine learning for vision, speech, and NLP tasks.

With an increasing number of queries requiring DNN computation on the critical path, a significant challenge emerges vis-à-vis the large gap between the amount of computation required to process a DNN-based query relative to a traditional browser centric query such as web search [45].

This work is driven by key insight that, much like biological neural networks, DNNs are intrinsically resilient to both minor numerical adjustments [27, 53, 92, 120] and eliding spurious neurons and synapses [40, 41]. This characteristic can be leveraged to achieve performance improvement. However, as we show later in the paper, reduction of computation and data movement does not directly translate to performance improvement. Techniques from prior work either create a mismatch between the algorithm and underlying architecture, or are not designed to address the real hardware bottlenecks, leaving two open challenges in the way of realizing performance benefits:

- Limitation 1: Irregular Computation Network pruning [40,41], a state-of-theart machine learning technique that reduces the DNN topology focuses on reducing the memory footprint. However, their methodology fails to realize performance benefits on GPUs. Although this technique significantly reduces the amount of raw computation (i.e. floating-point operations), we show that the hardwareinefficient irregular DNN topology outweighs the benefits and results in substantial slowdown (up to 61×) due to increased branch divergence and uncoalesced memory access on GPUs. We present details on this limitation in §4.1.1. To achieve performance benefits, the challenge of reducing computation while aligning the reduced computation with underlying hardware must be addressed.

- Limitation 2: Not Optimized for Bottleneck Our investigation identifies onchip memory bandwidth to be the key bottleneck for DNN execution on GPUs. However, prior works focus on improving off-chip memory bandwidth using compression [98], removing non-contributing bits to increase the effective bandwidth. This technique, however, fails to provide significant speedups for DNNs (details in §4.1.2). We evaluate off-chip data packing and observe a speedup of less than 4%. On the other hand, compared to off-chip techniques, it is more challenging to perform on-chip compression because frequently reformatting data is difficult to achieve without introducing significant overhead.

#### 1.1.2.2 Customized Hardware

Recently, deep neural networks (DNNs) have yielded state-of-the-art performance on a wide array of AI tasks, including image classification [60], speech recognition [42], and language understanding [114]. In addition to algorithmic innovations [79, 113, 116], a key driver behind these successes are advances in computing infrastructure that enable large-scale deep learning—the training and inference of large DNN models on massive datasets [24, 30]. Indeed, highly efficient GPU implementations of DNNs played a key role in the first breakthrough of deep learning for image classification [60]. Given the ever growing amount of data available for indexing, analysis, and training, and the increasing prevalence of ever-larger DNNs as key building blocks for AI applications, it is critical to design computing platforms to support faster, more resource-efficient DNN computation.

A set of core design decisions are common to the design of these infrastructures. One such critical choice is the numerical representation and precision used in the implementation of underlying storage and computation. Several recent works have investigated the numerical representation for DNNs [12,19,27,78]. One recent work found that substantially lower precision can be used for training when the correct numerical rounding method is employed [38]. Their work resulted in the design of a very energy-efficient DNN platform.

This work and other previous numerical representation studies for DNNs have either limited themselves to a small subset of the customized precision design space or drew conclusions using only small neural networks. For example, the work from Gupta et al. 2015 evaluates 16-bit fixed-point and wider computational precision on LeNet-5 [66] and CIFARNET [58]. The fixed-point representation (Figure 5.1) is only one of many possible numeric representations. Exploring a limited customized precision design space inevitably results in designs lacking in energy efficiency and com-

putational performance. Evaluating customized precision accuracy based on small neural networks requires the assumption that much larger, production-grade neural networks would operate comparably when subjected to the same customized precision.

## 1.2 Exploiting Error Tolerance

In this section, we outline the proposed techniques for exploiting error tolerance for emerging in this work.

## 1.2.1 NinjaProx: Achieving Accuracy Guarantees for Approximate Computing

Central to our approach of maintaining output quality is a guarantee engine for efficiently providing accuracy guarantees when applying approximation to map-based applications. Our approach leverages the well-known central limit theorem (CLT) as the starting point for generating an accuracy guarantee. However, as its name implies, the CLT provides guarantees that hold only in the limit (that is, with infinite samples). However, taking infinite (or even very large numbers of) samples is impractical, particularly when the goal is to improve time-to-solution with approximation. Instead, we leverage recent advances in the Berry-Esseen theorem [107, 108, 119] — a framework for adjusting the results of the CLT in the face of finite numbers of samples — to produce accuracy guarantees that are robust to arbitrary inputs that have not been anticipated or already seen by the system.

Our approach is in contrast to standard practice in approximate computing which

is to use heuristics to drive their approximation strategies [4, 6, 29, 51, 63, 72, 97, 98, 102, 109, 112]. Central to these approaches are intangible accuracy constraints that lack completely defined and enforceable semantics. Such accuracy constraints take the form of statements such as "The accuracy target is 99%", including no requirements about how often or on what inputs the accuracy target will be met. Accuracy constraints of this form lead to systems that produce acceptably-accurate approximations in the common case, but cannot provide robust guarantees of accuracy for any particular input or set of inputs. Instead, this work introduces the Accuracy Service Level Agreement (ASLA), a contract between the programmer or end-user of an application and the runtime system that computation accuracy will meet a well-defined set of constraints. Intuitively, these constraints take the form of "Accuracy must be above 99% with 95% confidence", which will be met by the runtime system regardless of the characteristics of the input, the desired accuracy level, and the confidence level specified. This work defines, specifies semantics for, and shows runtime support for ASLAs.

## 1.2.2 DeftNN: Addressing Bottlenecks for DNN Execution on GPUs via Synapse Vector Elimination and Near-compute Data Fission

This work introduces *DeftNN*, a GPU DNN execution framework that leverages error tolerance of DNN executions by tailoring the removal of precision and work to the GPU architecture. Firstly, *synapse vector elimination* reduces the total problem size by automatically locating and discarding non-contributing synapses in the DNN – those synapses having negligible impact on the output results – to improve perfor-

mance. To address the limitation of irregular computation, our insight is that it is necessary to preserve existing architectural optimizations in original GPU-efficient applications. Utilizing this insight, synapse vector elimination applies a novel transformation to the DNN data layout, producing computations that efficiently leverage GPU hardware.

The second optimization, near-compute data fission, mitigates the GPU on-chip memory bandwidth bottleneck by optimizing the utilization of integer units during DNN execution. To address the prior work's limitation of providing only off-chip bandwidth optimization [98], as on-chip memory is closer to the functional units, we design novel techniques that can support low-overhead very fine-grained data conversion. The key insight that makes near-compute data fission feasible is that the focus of data conversion must be shifted from high compression ratio to low decompression overhead. In addition to the benefits achieved by our carefully optimized near-compute data fission technique on commodity hardware, we describe a small additional unit called the Data Fission Unit (DFU) that can be added to existing GPU hardware to obviate data fission overhead to realize additional benefits on future generations of GPU hardware.

#### 1.2.3 Rethinking Numerical Representations for DNNs

In this work, we propose exploring the accuracy-efficiency trade-off made available via specialized custom-precision hardware for inference and present a method to efficiently traverse this large design space to find an optimal design. Specifically, we propose evaluating the impact of a wide spectrum of customized precision settings for fixed-point and floating-point representations on accuracy and computational performance. We propose evaluating these customized precision configurations on large, state-of-the-art neural networks. By evaluating the full computational precision design space on a spectrum of these production-grade DNNs, we want to determine:

- 1. Whether precision requirements generalize across all neural networks or not. The answer to this question could prompt designers of future DNN infrastructures to carefully consider the applications that will be executed on their platforms, contrary to works that design for large networks and evaluate accuracy on small networks [12, 19].

- 2. Whether many large-scale DNNs require more precision for arithmetic than previously found from small-scale evaluations [12,19,27]. For example, it is unclear if a large network such as GoogLeNet requires the same number of bits as opposed to small networks such as LeNet-5.

- 3. Whether floating-point representations are more or less efficient than fixed-point representations when selecting optimal precision settings. For example, a lower precision floating-point representation may be acceptable, when compared to a fixed-point representation. Current platform designers may need to reconsider the use of the floating-point representations for DNN computations in place of the commonly used fixed-point representations [12, 19, 27, 78].

To make the answers to these questions of customized precision readily actionable for DNN infrastructure designers, we propose designing a technique to quickly search the large customized precision design space. This technique should leverage critical values in the computation to capture the propagation of numerical error to build a model to predict accuracy. Using such a method on deployable DNNs, should provide infrastructure designers a near-optimal customized precision, without requiring an exhaustive search of all inputs and configurations.

## 1.3 Summary of Contributions

This work proposes runtime systems and techniques for exploiting error tolerance in emerging applications. The specific contributions are as follows:

- Accuracy Service Level Agreements this work introduces the concept of the Accuracy Service Level Agreement (ASLA). We describe the specification and enforcement mechanisms for making use of ASLAs in approximate computing (described in §3.1).

- End-to-end Approximation we introduce NinjaProx, an end-to-end system for ASLA-enabled approximate computing. NinjaProx presents the user with a flexible set of knobs to trade off performance and accuracy while providing statistical accuracy guarantees (§3.2). Through a thorough evaluation that covers 8 map-based applications employing 4 approximation techniques proposed in the literature, we show that it is the first system to provide both high performance approximation and robust guarantees of accuracy.

- Robust Accuracy Guarantees we enable ASLAs for approximate map-based applications using a set of robust statistical techniques for generating accuracy

guarantees (§3.3). These techniques use no offline training or assumptions about the distribution of input or output data. Nor do they require reasoning about the semantics of the approximation or the exact computation, allowing them to easily be leveraged on complex applications for a wide range of approximation techniques and accuracy metrics.

- **DeftNN.** We introduce DeftNN, a state-of-the-art GPU DNN execution framework. This framework automatically applies synapse vector elimination and near-compute data fission optimizations to existing DNN software applications to dramatically improve performance on today's GPUs.

- Synapse Vector Elimination. We introduce a DNN optimization technique for GPUs, synapse vector elimination, that shrinks the topology of the neural network. This method is guided by the insight that network pruning techniques in DNN systems must have computational regularity to achieve significant speedups. Our experiments show that synapse vector elimination achieves 1.5× average end-to-end speedups on a set of 6 state-of-the-art DNNs on real GPU hardware.

- Near-compute Data Fission. We introduce near-compute data fission, which improves performance by efficiently packing on-chip memory. To realize speedup, we find that the focus must be shifted from minimizing data size to minimizing unpacking overhead. We find that near-compute data fission provides 1.6× end-to-end speedup on a set of 6 DNNs on real GPU hardware available today by performing unpacking in software. We also introduce a lightweight hardware extension (<0.25% area overhead) to facilitate efficient unpacking, achieving an additional 1.4× speedup over software-only near-compute data fission.

## CHAPTER II

## Background and Related Work

This chapter presents and compares work related to this dissertation. First, we examine prior work that investigates runtime systems for parameterizing approximation techniques. Next, we present prior work that has optimized DNNs on platforms other than the GPU, which is not directly applicable to GPU acceleration due to not considering the architecture. Finally, we look at prior work for optimizing DNN execution with customized numerical representations.

## 2.1 Output Quality Guarantees

Many approaches have been proposed in prior work to trade accuracy for improvements in execution time or energy, ranging from modifying the underlying hardware [100,121], the ISA [28], compiler [47,97,98], programming language [4,8,9,101], database [1], runtime system [6,95] or multiple layers of the hardware/software stack [29,46,71,77,99].

Various techniques have been proposed to develop models of approximation ac-

curacy. Offline training and profiling has been used extensively to guide the choice of how aggressively to approximate [4, 47, 48, 75, 109, 112]. NinjaProx uses no training phase, instead building accuracy guarantees dynamically for each input to an application. Dynamic approaches to maintaining high approximation accuracy have also been proposed in the literature. IRA [63] dynamically tunes the parameters to software-based approximations based on input, while others tune these parameters using intermittent accuracy checks [6, 97, 98]. Uncertain<T> [8] takes advantage of Bayesian networks and sampling to propagate uncertainty through calculations. Unlike NinjaProx, such approaches make no guarantee of runtime accuracy. Mayhap [101] is a tool to validate that a probabilistic property exists in a program by sampling Bayesian networks, but does not impact how approximation is applied to a program.

ApproxHadoop [36] and other recent works [15,84] devise techniques to bound the error propagated to the single output value when applying a particular set of reduction operators in approximate MapReduce computations. These techniques are applicable to specific reduction operators – sum, count, average, ratio, minimum, and maximum – and are difficult to extend to more complex scenarios. Instead, NinjaProx provides accuracy guarantees for a host of common error metrics when approximating arbitrary map-based computations.

Static analysis of application and approximation semantics has been used to reason about approximation accuracy [10, 11, 16, 103, 111, 124]. Specifically, some have used semantic analysis to reason about the accuracy of perforated programs [76,94]. Unlike static analysis, NinjaProx uses no semantic analysis of the computation or as-

sumptions about the distribution of the input, instead focusing directly on the results of the computation, which allows it to be applied to applications and approximations that have complex semantics.

## 2.2 Commodity Hardware

The computational requirements and applicability of deep neural networks [62] and convolutional neural networks [66] have prompted researchers to design novel DNN hardware [2, 13, 14, 31, 39, 56, 69, 90, 105, 117]. Some of these hardware designs specifically target memory bandwidth [17, 19]. Although these works can provide substantial speedup upon fabrication, our techniques can operate on current commodity hardware.

On the software side, there has been a lot of effort to efficiently implement DNNs on GPUs [20, 52, 61, 64, 82]. In addition to optimizing for GPUs, some work has looked at optimizing DNNs at the cluster level [21, 24, 42, 44, 45, 54, 91]. Further software approaches consider using different types of neural networks to improve performance [35]. Optimized algorithms can be applied in concert with our optimization techniques.

Many prior works improve performance by exploiting reduced precision [27, 53, 68, 92, 120]. Reducing precision is possible for both floating-point and fixed-point formats [22, 38]. These works all require substantial hardware modifications to operate. ACME [50], although requiring less modifications to hardware by design, still requires substantial overhead when applied to a high-throughput accelerator such as a GPU. The DFU in DeftNN requires [0.25% overhead to continuously provide the

functional units with data, while scaling ACME to the same number of units would require over 19% overhead.

#### 2.3 Customized Hardware

To the best of our knowledge, our work is the first to examine the impact of numeric representations on the accuracy-efficiency trade-offs on large-scale, deployed DNNs with over half a million neurons (GoogLeNet, VGG, AlexNet), whereas prior work has only reported results on much smaller networks such as CIFARNET and LeNet-5 [12,19,23,27,38,78]. Many of these works focused on fixed-point computation due to the fixed-point representation working well on small-scale neural networks. We find very different conclusions when considering production-ready DNNs.

Other recent works have looked at alternative neural network implementations such as spiking neural networks for more efficient hardware implementation [21,25]. This is a very different computational model that requires redevelopment of standard DNNs, unlike our proposed methodologies. Other works have proposed several approaches to improve performance and reduce energy consumption of deep neural networks by taking advantage of the fact that DNNs usually contain redundancies [18,32].

## **CHAPTER III**

# Realizing Service Level Agreements on Result Accuracy for Approximate Data-parallel Programs

A major challenge in approximate computing lies in providing guarantees of result quality on arbitrary inputs that have not been anticipated or already seen by the system. It is widely believed that this is one of the key obstacles that has prevented the adoption of approximate computing in commercial and production environments.

This chapter presents an approach to this challenging problem for a broad class of computational problems, developing the statistical machinery to provide accuracy guarantees when approximating applications regardless of the input content and desired accuracy level. This mechanism builds on the insight that the computation in applications that are amenable to approximation can be performed both out-of-order and incrementally. We leverage this fact to (1) cheaply sample the application output with and without approximation, then (2) dynamically build a statistical description of the accuracy characteristics, leveraging statistical methods to generate accuracy guarantees on the approximation.

Figure 3.1: End-to-end NinjaProx: after compiling an approximation-amenable application written using the NinjaProx programming interface, the runtime system searches the set of approximations based on the accuracy guarantees supplied by the guarantee engine to select an approximation.

Building on this mechanism, we introduce and describe enforcement techniques for a new class of service level agreement (SLA) called an Accuracy SLA (ASLA). Like an SLA on tail latency that bounds the likelihood of a computation falling below some latency target, an ASLA is a bound on the likelihood of computational accuracy falling below some target accuracy. We describe NinjaProx, a language, compiler, and runtime for enforcing ASLAs in approximate computing. We evaluate NinjaProx, applying 4 approximation techniques from the recent literature to 8 applications in the domains of machine learning, image processing, and data mining. Among thousands of individual experiments leveraging ASLAs that cover a number of common accuracy metrics and a range of confidence levels, we find that, in practice with representative approximate applications, NinjaProx never fails to meet the specified ASLA and achieves speedups that average 2.5×.

## 3.1 Accuracy SLAs

We begin by introducing the concept of the Accuracy Service Level Agreement (ASLA), motivating their use and defining their semantics.

#### 3.1.1 Motivation

A conventional webservice Service Level Agreement (SLA) is an agreement specifying a set of constraints on performance. A common approach in specifying such SLAs is to describe constraints on the latency, such as "the latency of 99% of queries is under 50ms." This performance constraint on tail latency has two components — a performance target and a point in the tail of the latency distribution. Tail latency is a common metric because it reflects one of the realities of webservice operation — users observing long latency in their requests may leave for the competition and never return — thus constraining tail latency minimizes the likelihood of this event.

Similarly, users of an approximate application may seek alternatives if they are presented with results that are unsatisfactorily poor, and thus a convention similar to the conventional SLA is needed in dealing with approximation accuracy. There is a wealth of prior work in approximate computing that demonstrates satisfactory result accuracy by example, showing on a set of benchmarks that result accuracy usually satisfies some accuracy target(s) [4,46,51,63,98,99]. These approaches have resulted in useful systems for enacting approximation, but they do not solve the more fundamental problem, providing no assurances on result accuracy for difficult cases that may not have been envisioned by the system designers.

#### 3.1.2 Defintion

The simplest form of an ASLA is shown in Equation 3.1.

$$P[A \ge T] \ge CL \tag{3.1}$$

This expression says that for an approximate application, the result accuracy A must not fall below the target accuracy T with probability of at least CL. Note that exact execution of the application (i.e. 100% accuracy with 100% confidence) can be expressed as an instance of this style of probabilistic guarantee, taking the form  $P[A \ge 100\%] \ge 1.0$ . Multiple simple ASLAs can be composed to form a compound ASLA. Consider the k-statement compound ASLA in Equation 3.2, which would require that all k expressions are satisfied.

$$P[A \ge T_0] \ge CL_0$$

$$P[A \ge T_1] \ge CL_1$$

$$\cdots$$

$$P[A \ge T_k] \ge CL_k$$

(3.2)

A compound ASLA may be useful, for example, in expressing a willingness to drop to 90% accuracy nearly all the time alongside a strict requirement to rarely drop below 80% accuracy. Such a requirement could be expressed as the 2-clause compound ASLA shown in Equation 3.3.

$$P[A \ge 90\%] \ge 95\%$$

$P[A \ge 80\%] \ge 99.999\%$  (3.3)

## 3.1.3 ASLA Specification

The ASLA definitions described above are probabilistic constraints. In contrast to prior work that has focused on validating probabilistic assertions [101], an ASLA is not a stopping condition of the program, but is instead a set of constraints that must be met when computing approximate results.

For an ASLA clause with target accuracy T and confidence level  $\alpha$ , an accuracy metric M that gives meaning to the accuracy constraint must also be specified. Our current implementation provides turnkey support for a variety of common accuracy metrics that include mean absolute percentage, mean absolute error, mean square error and peak signal-to-noise ratio (PSNR), as well as the ability to supply additional customized metrics. We describe these accuracy metrics and how they are supported in detail in §3.3.4.2.

## 3.2 NinjaProx Overview

This section introduces NinjaProx, a language, compiler and runtime system for enforcing ASLAs in map-based applications. An overview of NinjaProx is presented in Figure 3.1. NinjaProx has two main components: an offline component to compile support for approximation and the ASLA into the application, and a runtime to

select how to approximate in a way that meets the ASLA.

## 3.2.1 Programming Interface

NinjaProx provides a simple interface that allows programmers to employ accuracy guarantees in map-based applications. The programmer defines an ASLA, a map-based computational kernel, and the dimensions of the problem being solved to utilize NinjaProx. We use binarize, an application that segments an image based on pixel intensity, as an example of the programming interface. For comparison, the original implementation is provided in Figure 3.2, while the NinjaProx implementation is found in Figure 3.3. NinjaProx currently supports C++11, used in the example code, but the NinjaProx statistical framework is language independent.

First (lines 5-6 of Figure 3.3), the programmer defines an ASLA, comprising an accuracy metric, the target accuracy level, and a statistical confidence level. The example code shows a concrete specification of the target accuracy level (0.90) and confidence level (0.99), however we envision that a typical NinjaProx deployment will defer the specification of one or both parameters until runtime. In the example, a simple 1-statement ASLA is defined. However, an array of ASLA objects can used together to build a compound ASLA as described in §3.1.2. Next (lines 8-10), an approximation parameter space is specified. This denotes the set of approximation parameters that NinjaProx should investigate, when it searches for an optimal approximation strategy.

The subsequent code (lines 12-22) is written specifically for the binarize application. Approximated binarize is made compatible with NinjaProx by refactoring

the code so that each output is computed independently. In code, the operation is defined by the programmer by using a closure that produces a single output from loop indices (mapIdx) and approximation parameters (apxParam) (lines 18-22). Using the defined application kernel, output array, output dimensions, ASLA, and approximation parameter space, the programmer calls the mapNinjaProx function (lines 24-27). This function searches the approximation parameter space for the fastest approximation that meets the ASLA for the application, and then, using this approximation, writes an approximated value for each element in the output array.

## 3.2.2 Compilation

The NinjaProx compiler allows assumptions about the computational kernel to be checked and mitigates overhead introduced by the high-level programming model. For example, the NinjaProx compiler checks that the map-based computation provided to mapNinjaProx is pure, since NinjaProx will execute the map-based operation many times and in random order during its search for an optimal approximation strategy. When the map-based function is not pure, the compiler does not apply approximation and produces a warning.

To improve search runtime performance, the NinjaProx compiler orders the approximation parameters by how fast they are. This ordering is usually an obvious consequence of the nature of the approximation. For example, in skipping loop iterations for loop perforation [47], the technique becomes faster and less accurate as more iterations are skipped. The NinjaProx compiler applies another key optimization that benefits approximations that skip work by reusing output values, as in

```

//Input declarations (initialization omitted)

int width, height, threshold;

uint8_t input[width*height];

//Original binarize kernel

uint8_t output[width*height];

for(int x = 0; x < width; x++) {

for(int y = 0; y < height; y++) {

output[x+y*width] =

input[x+y*width] > threshold ? 255 : 0;

}

```

Figure 3.2: Original implementation of binarize, an application that segments pixels based on intensity.

tiling approximation [97]. In this case, the NinjaProx compiler identifies that multiple output values derive from identical computation, splitting the computation of the final approximate result into two phases: a first phase to compute each unique element in the output, and a second phase to copy those results to the remainder of the output.

#### 3.2.3 Runtime Support