# Hardware Mechanisms for Efficient Memory System Security

by

Salessawi Ferede Yitbarek

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in The University of Michigan 2018

Doctoral Committee: Professor Todd M. Austin, Chair Assistant Professor Reetuparna Das Professor Scott Mahlke Professor Dennis M. Sylvester Salessawi Ferede Yitbarek

salessaf@umich.edu

ORCID iD: 0000-0003-1420-7937

© Salessawi Ferede Yitbarek 2018

In loving memory of Haileleul Mulugeta Haile.

## Acknowledgements

This thesis would not have been possible without the support of numerous people.

I have been extremely fortunate to have Professor Todd Austin as an advisor. Todd has taught me a great deal about doing research, crafting effective presentations, leading projects, and more. He has been an incredibly supportive advisor who consistently took time out of his busy schedule to mentor me on subjects beyond our research.

I would also like to thank my thesis committee members, Professors Reetuparna Das, Scott Mahlke, and Dennis Sylvester for their valuable feedback. I had the pleasure of collaborating with Reetuparna on multiple projects as well, and her rigorous approach to research has deeply shaped me. Professor Valeria Bertacco has also been an excellent source of wisdom on numerous subjects ranging from communicating my research to surviving graduate school and navigating the academic world.

I have benefited a great deal from all the graduate students I have worked and interacted with. Misiker Aga and David Williams did a lot of heavy-lifting for the infrastructure used for the DDR3 scrambler analysis in Chapter 3. Doowon Lee has kindly shared his expertise with me while I was setting up the experiments and writing this document. My work has also greatly benefited from discussions and feedbacks from Shazeen Aga. Thank you to Lauren Biernacki, Zelalem Birhanu, William Ehrett, Mark Gallagher, Vidushi Goyal, Colton Holoday, Abraham Lamesgin, Timothy Linscott, Andrew McCrabb, Hiwot Tadese, Tarunesh Verma, and Brendan West, for all their valuable feedbacks, and for being a constant source of fun around the lab. I have been fortunate to collaborate on various projects outside of this dissertation and learn from an outstanding set of students, including Zelalem Birhanu, Mark Gallagher, Lauren Biernacki, Tao Yang, Evan Chavis, Kegan Thorrez, Kartik Joshi, and Walter Zarate. Thank you to Rawan Abdel Khalek and Ritesh Parikh for giving me valuable direction as I was starting out. Thank you to William Arthur, who guided me as I was settling and finding my way in the A-Lab. Thank you to Patipan Prasertsom, Ram Srivatsa, Thomas Zachariah, and Animesh Jain for the loads of fun memories and labor we shared. Thank you to Sai Gouravajhala for being a fantastic companion during all the stressful semesters. I would especially like to thank my friend Biruk Wendimagegn, who has supported me in numerous ways since day one, from helping me settle in Ann Arbor to helping me gain my footing as a Ph.D. student to consulting me as I try to make post-graduation plans. It would be impossible to list all the students I have been enriched by during my stay at the University of Michigan.

I would also like to thank administrative staff members Ashley Andreae, Christine Boltz, Alice Melloni, Alexis Santa Cruz, Karen Liska, Denise Duprie, Stephen Reger, Jamie Goldsmith, Dawn Freysinger, Lauri Johnson-Rafalski, and Laura Pasek for tirelessly assisting me with all the administrative processes I needed to go through.

Thank you to Kidus Ayalneh, Misiker Tadesse, Zelalem Birhanu, Abraham Lamesgin, Helen Arefayne, Hiwot Tadese, Abeselom Fanta, Zerihun Bekele, Abdi Zeynu, Yodit Beyene, and Leul Beyene for the fun, friendship, and support. I have also been immensely blessed by my friendships with Daniel McCarter, Jazmine and Stephen Xu, Ciara Reyes, Carole and Derek Metzger, Carmen Lee, Joel Perry, and Gee Zhu. Thank you to Meseret Tadesse, the Mekonene's (Michael, Tsedey, Hanna, Selamawit, and Mekonnen), Meshesha Mengesha, Genet Girma, Girma Moges, and Bethlehem Yikono for all they have done to make me feel at home. I am also grateful for the many years of continued companionship and emotional support from my closest friends back home: Abisa Girma, Sara Abdella, Mistere Mamo, Lensa Teklu, Sara Teklu, and Besufekad Mamo.

I am indebted to my parents, Adamwork and Ferede, who have always gone out of their way to support me and enable me to follow my interests. Thank you to Zemen Ferede, Ewnetu Ferede, and Meron Mekonen for always looking out for me and for their unwavering support. I am grateful my brother Ewnetu introduced me to programming and encouraged me to pursue my curiosities. Thank you to Haileluel Mulugeta who always encouraged me to pursue a graduate degree and supported me as I was moving to the U.S. to work on my Ph.D. I have looked up to him ever since I got to know him, and I will dearly miss him. Thank you to Abeba Beyene and Dejene Shewaye for their emotional support. I cannot thank my beloved Bethlehem enough for being an unending source of optimism, encouragement, and support, and for making this journey delightful.

# **Table of Contents**

| Dedicat   | ion                                                   | ii   |

|-----------|-------------------------------------------------------|------|

| Acknow    | ledgements                                            | iii  |

| List of F | igures                                                | viii |

| List of T | ables                                                 | х    |

| Abstrac   | t                                                     | xi   |

| Chapter   | 1 Introduction                                        | 1    |

| 1.1       | Preventing Physical Attacks on Memory Systems         | 2    |

| 1.2       | Safeguarding the Operating System's Code              |      |

|           | and Data                                              | 6    |

| 1.3       | Summary of Contributions                              | 10   |

| Part I: E | Efficient Physical Memory Security                    | 13   |

| Chapter   | 2 Physical Memory Security                            | 14   |

| 2.1       | Data Remanence and Cold Boot Attacks                  | 14   |

|           | 2.1.1 Cold Boot Attack Mitigation Measures            | 15   |

|           | 2.1.2 Cold Boot Attacks and Memory Scramblers         | 16   |

| 2.2       | Bus Snooping and Replay Attacks                       | 17   |

| 2.3       |                                                       | 18   |

| 2.4       |                                                       | 22   |

| Chapter   | 3 Cold Boot Attacks on Scrambled DDR3 and DDR4 Memory | 24   |

| 3.1       | Overview of Memory Scramblers                         | 25   |

|           | 3.1.1 Memory Scramblers and Cold Boot Attacks                       | 27       |

|-----------|---------------------------------------------------------------------|----------|

| 3.2       | Analysis Framework                                                  | 28       |

| 3.3       | Analysis of DDR3 Scramblers                                         | 31       |

|           | 3.3.1 Seeding the Scrambler                                         | 31       |

|           | 3.3.2 Memory Scrambler Properties                                   | 33       |

|           | 3.3.3 Effects of Descrambling on a Separate Machine                 | 37       |

| 3.4       | Analysis of a DDR4 Scrambler                                        | 38       |

|           | 3.4.1 Disk Encryption Key Recovery from a DDR4 Memory               | 41       |

|           | 3.4.2 Physical Characteristics of DDR4 DRAM                         | 45       |

| 3.5       | Replacing Scramblers with Strong Ciphers                            | 46       |

|           | 3.5.1 Low Overhead Memory Encryption                                | 46       |

|           | 3.5.2 Results and Discussion                                        | 51       |

| 3.6       | Summary                                                             | 55       |

| <b>01</b> |                                                                     | 1        |

| _         | r 4 Leveraging ECC DIMMs for Reducing the Overhead of Authenticated |          |

|           | nory Encryption                                                     | 57       |

| 4.1       | Merging ECC and Integrity Checking                                  | 58<br>59 |

| 4.2       | On the Security of SGX's 56-bit MAC Tags                            |          |

| 4.3       | MACs for Error Detection                                            | 59       |

| 4.4       | MACs for Error Correction                                           | 61       |

| 4.5       | Attacks Versus Hardware Faults                                      | 64       |

| 4.6       | Evaluation                                                          | 64       |

|           | 4.6.1 Experimental Setup                                            | 65       |

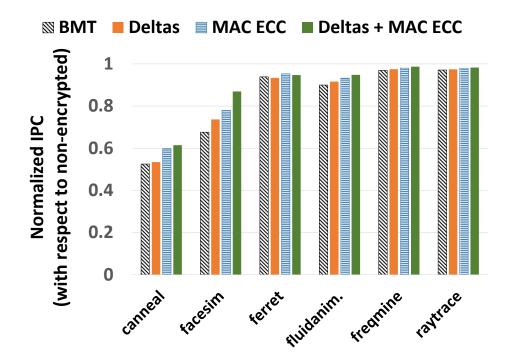

|           | 4.6.2 Results                                                       | 66       |

| Chapte    | r 5 Reducing Counter Storage Overhead Using Delta Encoding          | 67       |

| 5.1       | Delta Encoding                                                      | 68       |

| 5.2       | Counter Updates and Re-Encryptions                                  | 70       |

| 5.3       | Minimizing Overflow                                                 | 71       |

| 5.4       | Putting it All Together: Delta Encoding                             |          |

|           | Implementation                                                      | 73       |

| 5.5       | Evaluation                                                          | 75       |

|           | 5.5.1 Results                                                       |          |

|           |                                                                     |          |

|           | A Lightweight Hardware Extension for Enforcing Operating System     |          |

| Inte      | grity                                                               | 79       |

| Chapte    | r 6 Operating System Kernel Security                                | 80       |

|           | Kernel-Mode Execution and Rootkits                                  | 80       |

|           |                                                                     |          |

|         | 6.1.1   | Rootkit Stealth Techniques82                               |

|---------|---------|------------------------------------------------------------|

| 6.2     | Shield  | ing the Operating System from Attacks                      |

|         | 6.2.1   | Secure Boot                                                |

|         | 6.2.2   | Driver Signing                                             |

|         | 6.2.3   | Supervisor Mode Access/Execution Prevention 84             |

|         | 6.2.4   | Kernel Integrity Monitoring and Enforcement 85             |

|         | 6.2.5   | Hardware Mechanisms for Kernel Integrity                   |

|         | 6.2.6   | Limitations of Existing Defenses: A Summary 88             |

| Chapter | r7 Ne   | verland: A Lightweight Hardware Extension for Safeguarding |

| -       |         | System Integrity                                           |

| 7.1     |         | Model                                                      |

| 7.2     |         | and Implementation Overview                                |

| 7.3     | Hardw   | vare Requirements                                          |

|         | 7.3.1   | Eliminating Additional Memory Latency                      |

| 7.4     | Suppor  | rting Loadable Kernel Modules                              |

| 7.5     | Restric | tions on Kernel Features                                   |

| 7.6     | Securi  | ty Analysis                                                |

| 7.7     | Evalua  | tion                                                       |

|         | 7.7.1   | Hardware Overhead                                          |

|         | 7.7.2   | Performance Overhead 109                                   |

| Chapter | r8 Co   | nclusion                                                   |

| -       |         | Research Directions 111                                    |

| Append  | lix     |                                                            |

| Bibliog | raphy . |                                                            |

# **List of Figures**

## Figure

| 1.1<br>1.2                      | Storage Overheads of ECC & Authenticated Memory Encryption Linux Kernel Vulnerabilities.                                                                                                                                                                                      | 5<br>7                           |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 2.1                             | Counter mode encryption                                                                                                                                                                                                                                                       | 19                               |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5 | High-level View of Memory Scrambling.An Example Linear Feedback Shift RegisterFPGA Used for Initializing DDR3 DRAM with ZerosCold Boot Attack on DDR4 DRAM.Visual Comparison of DDR3 and DDR4 Scramblers on Single Channel                                                    | 26<br>27<br>30<br>31             |

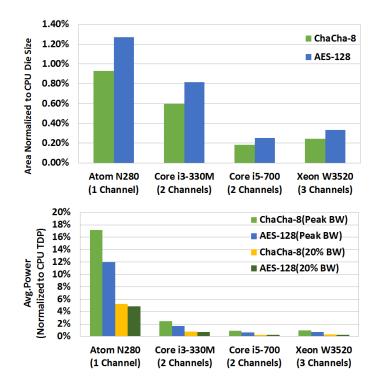

| 3.6<br>3.7<br>3.8<br>3.9        | Machines       Machines         A Model Representing Scrambler Logic       Scanning Memory for AES Round Keys         Minimizing Decryption Overhead       Decryption Latency of Different Ciphers.         Power and Area Overhead.       Scanning Memory for AES Round Keys | 32<br>36<br>43<br>47<br>52<br>54 |

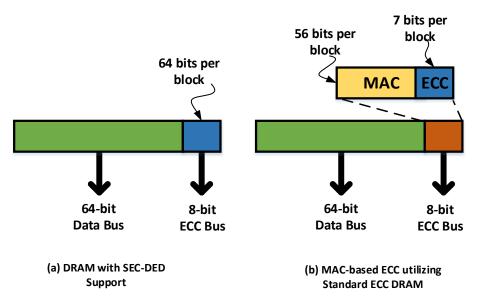

| 4.1<br>4.2<br>4.3               | MAC-based ECC Using ECC DRAM DIMMs                                                                                                                                                                                                                                            | 60<br>62<br>66                   |

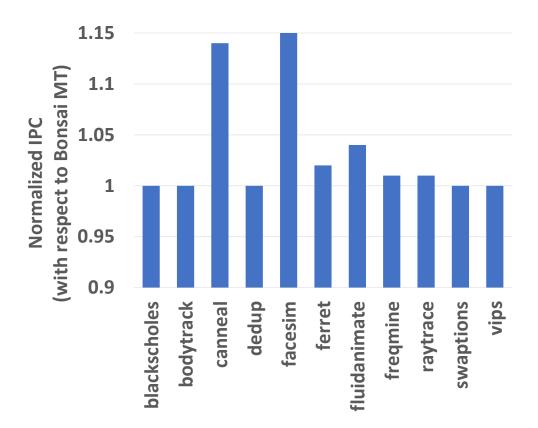

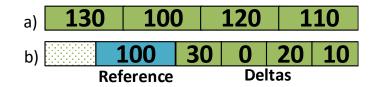

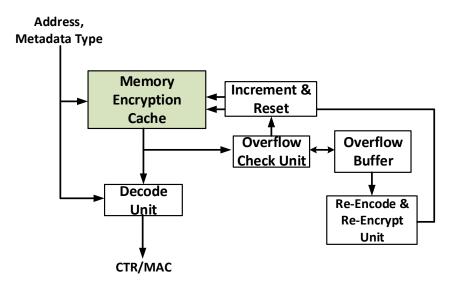

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5 | Frame-of-Reference Delta EncodingDelta Encoding CountersDual Length Delta EncodingImplementation of Delta EncodingPerformance Impact of Authenticated Memory Encryption                                                                                                       | 67<br>69<br>71<br>74<br>77       |

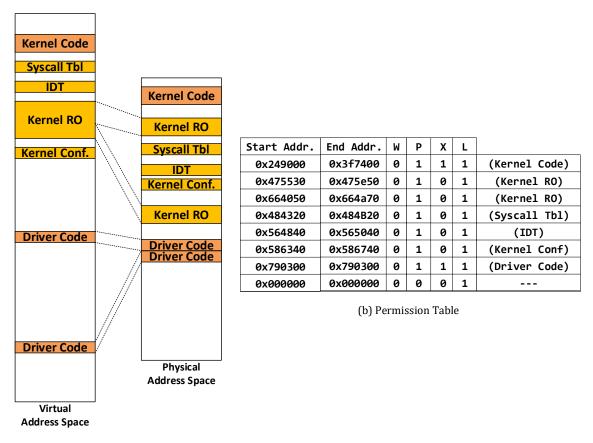

| 7.1 | Example Memory Layout and Physical Memory Permissions     | 92  |

|-----|-----------------------------------------------------------|-----|

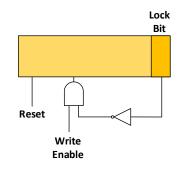

| 7.2 | Register Locking                                          | 98  |

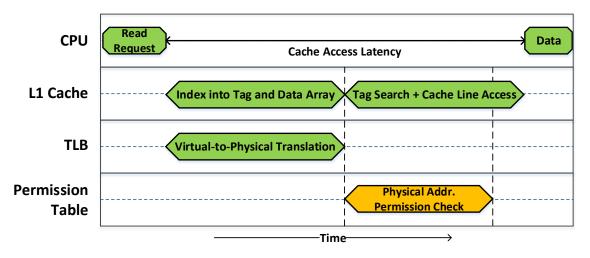

| 7.3 | Performing Permission Check in Parallel with Cache Access | 99  |

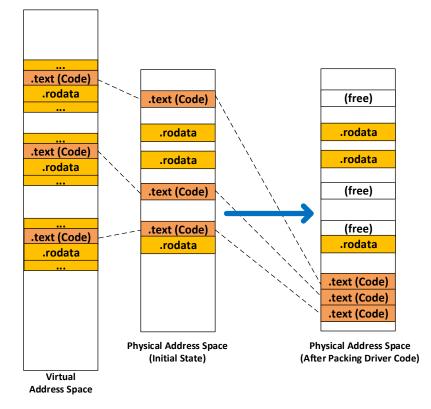

| 7.4 | "Defragmenting" Kernel Module Code                        | 102 |

| A.1 | Scrambler Seed Generator Logic                            | 116 |

# List of Tables

#### Table

|     | CPU Models of Tested Machines                                                                                                                   |     |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | MAC-based ECC Using ECC DRAM DIMMs                                                                                                              |     |

| 5.1 | Average Number of Re-Encryptions                                                                                                                | 76  |

| 6.1 | Existing OS Kernel Protections and their Limitations/Drawbacks                                                                                  | 89  |

| 7.2 | Effectiveness of Neverland's Protections1Power and Area Overhead of Permission Tables1Module Load Latency Overhead Incurred by Defragmentation1 | 109 |

## Abstract

The security of a computer system hinges on the trustworthiness of the operating system and the hardware, as applications rely on them to protect code and data. As a result, multiple protections for safeguarding the hardware and OS from attacks are being continuously proposed and deployed. These defenses, however, are far from ideal as they only provide partial protection, require complex hardware and software stacks, or incur high overheads. This dissertation presents hardware mechanisms for *efficiently* providing *strong* protections against an array of attacks on the memory hardware and the operating system's code and data.

In the first part of this dissertation, we analyze and optimize protections targeted at defending memory hardware from physical attacks. We begin by showing that, contrary to popular belief, current DDR3 and DDR4 memory systems that employ memory scrambling are still susceptible to cold boot attacks (where the DRAM is frozen to give it sufficient retention time and is then re-read by an attacker after reboot to extract sensitive data). We then describe how memory scramblers in modern memory controllers can be transparently replaced by strong stream ciphers without impacting performance.

We also demonstrate how the large storage overheads associated with authenticated memory encryption schemes (which enable tamper-proof storage in off-chip memories) can be reduced by leveraging compact integer encodings and error-correcting code (ECC) DRAMs – without forgoing the error detection and correction capabilities of ECC DRAMs.

The second part of this dissertation presents Neverland: a low-overhead, hardwareassisted, memory protection scheme that safeguards the operating system from rootkits and kernel-mode malware. Once the system is done booting, Neverland's hardware takes away the operating system's ability to overwrite certain configuration registers, as well as portions of its own physical address space that contain kernel code and security-critical data. Furthermore, it prohibits the CPU from fetching privileged code from any memory region lying outside the physical addresses assigned to the OS kernel and drivers. This combination of protections makes it extremely hard for an attacker to tamper with the kernel or introduce new privileged code into the system – even in the presence of software vulnerabilities. Neverland enables operating systems to reduce their attack surface without having to rely on complex integrity monitoring software or hardware.

The hardware mechanisms we present in this dissertation provide building blocks for constructing a secure computing base while incurring lower overheads than existing protections.

# Chapter 1 Introduction

The security of a computer system hinges on the trustworthiness of the operating system and the hardware, as applications rely on them to protect code and data. As a result, modern systems employ multiple layers of hardware-level and software-level defenses to ensure the integrity of the hardware and the kernel. Today's CPUs, for example, provide protections against hardware-level bus snooping and memory tampering attacks, can prevent the execution of arbitrary code in kernel-mode, and allow execution of software components in a hardware-isolated environment. Operating systems are also being shipped with increasingly sophisticated attack mitigations. For example, it is becoming a common practice to deploy an operating system alongside a separate integrity checking kernel.

These defenses have significantly improved the security of computer systems. Reliably mounting an attack on a modern, well-protected hardware or operating system is harder than ever. These defenses, however, are far from ideal. Existing protections against hardware-level attacks on memory systems, for example, either provide partial protection or incur high overheads. Similarly, defenses targeted at enforcing the integrity of OS kernels require complex and high overhead software stacks (such as a hypervisor and/or a separate trusted kernel), and are still prone to attacks in the presence of software bugs.

In this dissertation, we present hardware mechanisms for providing *strong* protections against an array of attacks on the memory hardware and the operating system's code and data, while incurring lower overheads compared to existing mechanisms. This chapter highlights these protections and optimizations proposed in this dissertation.

## 1.1 Preventing Physical Attacks on Memory Systems

Data stored in a CPU's registers and caches is extremely hard to physically probe or modify. Modern CPUs have complex layouts with multiple metal layers. As a result, it is extremely expensive, if at all possible, for an attacker to physically access on-chip storage units.

On the other hand, data stored in off-chip memory (DRAM or non-volatile memory) can be physically extracted much more easily. An attacker with physical access to a machine can probe a data bus [44], or dump memory contents through a cold boot attack [37]. For this reason, critical secrets are considered at-risk if they are stored on an off-chip memory, and applications such as disk encryption software immediately wipe out encryption keys from memory once they are no longer necessary.

#### **Cold Boot Attacks**

Even if DRAMs are expected to lose their content immediately after the system is powered off, studies have shown that they retain data for several seconds after power loss – with only a fraction of data being lost. Such data retention in DRAMs has been shown to be a security risk [107, 8, 37], as systems that rely on disk encryption and passwords often store sensitive data in DRAM under the assumption that a reboot or removal of the DRAM will destroy the data. However, in 2008, a team of researchers demonstrated that disk encryption keys could be recovered from DDR and DDR2 DRAMs by dumping out the contents of a locked computer's DRAM [37]. The contents of the DRAM can be recovered by either rebooting the locked machine into a custom OS, or by transferring the DRAM to another machine. Since charge decay in capacitors slows down significantly at lower temperatures, they cooled the DRAMs using off-the-shelf compressed air spray cans before transferring them to another machine or rebooting the locked machine. This technique came to be known as a *cold boot attack*.

**Data Extraction from Non-Volatile Main Memory (NVMM).** With the imminent introduction of non-volatile main memory technologies such as the Intel 3DXPoint,

extracting data from main memory is going to become significantly easier [50]. As the name implies, these technologies do not lose their content upon power loss. Furthermore, due to their increased storage capacity, NVMMs will expose more data if their content is unencrypted. Since these devices are attached to the CPU via memory buses and are accessed directly with load and store instructions, simply enabling disc encryption will not protect them.

**Memory Scrambling.** In recent years it has become more challenging to execute cold boot attacks due to the introduction of *memory scramblers*. Modern processors scramble data by XOR'ing it with a pseudo-random number before writing it to DRAM [63, 79]. These scramblers were introduced to mitigate the effects of excessive current fluctuations on bus lines by ensuring bits on the memory bus transition nearly 50% of the time.

Scramblers in many modern processors (*e.g.*, Intel's Skylake) have incorporated extra features that obfuscate data. Since these data obfuscation features are not necessary to mitigate the electrical problems that motivated the use of scramblers in the first place, we surmise they were added as the first line of defense against cold boot attacks.

Since the details of these scramblers remain undisclosed, it has become challenging to extract and analyze DDR3 and DDR4 DRAM contents. Although multiple attempts to replicate cold boot attacks on scrambled memory failed in the past [35, 106], recent work has demonstrated a cold boot attack that bypasses DDR3 DRAM scramblers on  $2^{nd}$  generation Intel Core (SandyBridge) CPUs [14].

**Cold Boot Attack on Scrambled Memory.** The study we present in Chapter 3 of this dissertation reveals that DDR4 memory scramblers have been redesigned in Intel's 6<sup>th</sup> generation CPUs in a manner that provides enhanced data obfuscation over previous generation DDR3-based scramblers. While this enhanced design is resistant to attacks that have been demonstrated in the past, we will show that it is certainly not impenetrable. In this dissertation, we reveal details of the first cold boot attack that is able to successfully extract AES keys from a scrambled DDR4 DRAM. We demonstrate this attack by extracting VeraCrypt/TrueCrypt master keys.

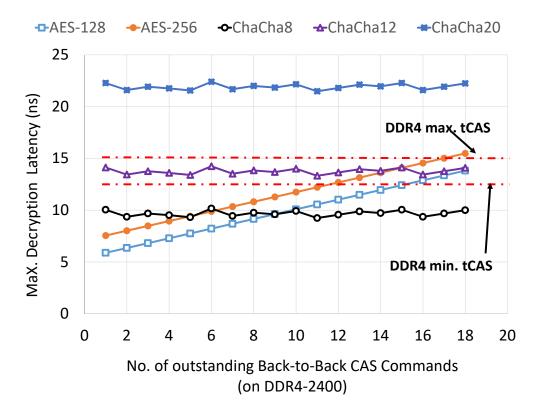

Low-Overhead Memory Encryption. Confidentiality of data stored in memory can be ensured by employing strong encryption. When employing memory encryption, however, we need to ensure that we do not adversely affect memory latency or bandwidth. In Chapter 3, we present analysis that shows modern high-throughput stream ciphers (e.g., ChaCha8) coupled with high-speed ASIC implementations make it practical to create strongly encrypted memories without incurring any performance penalty. We detail latency, area, and power trade-offs of memory encryption engine designs based on RTL simulation and synthesis results. As future-generation systems will utilize dense non-volatile memories, it is becoming increasingly crucial to employ strong encryption to safeguard memory contents.

#### **Bus-Snooping Attacks**

In addition to dumping memory content, attackers could probe memory buses as well. This is a more powerful attack as it makes it possible to observe values change over time. This ability to observe multiple versions of a single data can be used to defeat certain encryption schemes (e.g., stream ciphers that do not generate a unique nonce for each memory write operation). Furthermore, an attacker with the capability to modify bits on the bus can change or reset memory contents as they are being written and read.

Authenticated Memory Encryption. Stream ciphers alone are not sufficient to protect contents from tampering. To ensure data integrity, we need to use an authenticated encryption scheme that stores a message authentication code (MAC) along with the encrypted data. A MAC function is a one-way function that takes a block of data and a secret key, and produces a hash value. An attacker cannot generate a new MAC value after modifying data, as a secret key is required for generating a valid MAC.

Even if attackers cannot create MAC values for arbitrary data, they can still reset data blocks and MACs to an older value – a process commonly referred to as a replay attack. Replay attacks cannot be prevented unless we have a mechanism for detecting changes to the MACs. Such protection is provided by constructing integrity trees (discussed in the next chapter).

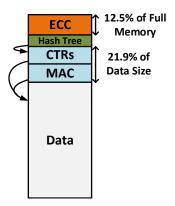

**Figure 1.1 Storage Overheads of ECC & Authenticated Memory Encryption.** Authenticated memory encryption requires storage of MACs and counters. Each of these incur an 11% storage overhead. The counters themselves are then protected with a hash tree. Furthermore, if the system has ECC support, an additional 12.5% storage overhead is incurred by parity bits.

Employing these cryptographic primitives in the context of memory encryption, however, results in high storage overheads as shown in Figure 1.1. Strong encryption requires that we provide a unique, one-time (non-reusable) input commonly referred to as a cryptographic nonce. Counter-mode encryption, the most widely used mode of memory encryption, uses a growing counter value as a nonce. Counters/nonces used to encrypt each memory block need to be stored as they are necessary to decrypt the data when it is read back. SGX (Intel's implementation), for example, stores a 56-bit counter for each 64-byte block, resulting in an  $\sim$ 11% overhead. In addition to counter values, MACs also need to be stored for each memory block. Again, SGX uses 56-bit MACs - incurring an additional  $\sim$ 11% storage overhead.

Memory read latency is also impacted as reading a protected block requires we fetch the corresponding counter and MAC values, perform decryption, and check the integrity of the data. Additional overhead arises from the fact that the counters and MACs themselves need to be protected by an integrity tree. Overall, strong memory encryption incurs more than 22% storage overhead.

**Reducing the Overhead of Authenticated Memory Encryption.** In Chapters 4 and 5, we propose optimizations for reducing the storage overheads discussed above. The

optimizations we present also reduce the performance overhead of authenticated memory encryption.

We make the observation that MAC bits, along with 7 parity bits, can be used for error detection and correction. As a result, the MAC storage overhead on systems with ECC memory can be reduced to zero – without forgoing security guarantees or error detection and correction capabilities. Furthermore, ECC memory has wider buses that enable the CPU to read error detection/correction bits in parallel with a memory block. Hence, this approach enables us to read MAC values in parallel with the data block – reducing the extra latency associated with reading security metadata.

We also show how delta encoding can be used to represent counters with fewer bits. Delta encoding is a data representation scheme that stores the difference (deltas) between two values, instead of storing the full values themselves. To apply this scheme, we first group multiple memory blocks into a logical group. Each block-group shares a single reference value. The counters for each block in a group are then represented as deltas to this common reference value. Since the delta values will be smaller than the actual values themselves, they can be represented with fewer bits – resulting in lower storage overhead.

# 1.2 Safeguarding the Operating System's Code and Data

The second part of this dissertation explores memory protection techniques for enhancing the OS kernel's security. Security mechanisms on a computer system heavily rely on the proper functioning of the OS kernel. If the kernel is compromised, other protections built on top of it can be bypassed.

Today's systems commonly employ a secure boot mechanism to prevent the system from booting into a tampered kernel. However, once the boot process is completed, attackers could exploit software vulnerabilities to perform malicious actions such as overwriting kernel memory, executing malware in kernel-mode, or disabling driver integrity checks (example attacks can be seen in [120, 19, 31, 84, 116, 101, 91, 87]).

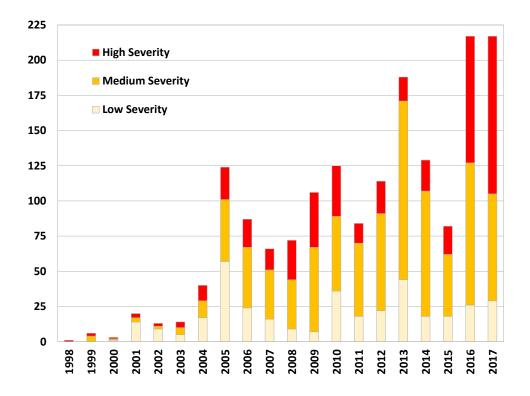

**Figure 1.2** Linux Kernel Vulnerabilities. New kernel vulnerabilities continue to be reported each year (data based on the National Vulnerability Database).

Completely eliminating vulnerabilities from today's large and complex kernels remains impractical. This is illustrated by the data in Figure 1.2, which shows Linux kernel vulnerabilities disclosed since 1998 (based on the data from the National Vulnerability Database<sup>1</sup>). Clearly, today's operating systems have a large attack surface as a result of their size and complexity. Furthermore, kernel modules (drivers) introduce additional attack surface, as they have full access to the kernel's address space.

#### **Ongoing Challenges of Protecting the Kernel**

Recognizing their vast attack surface, a growing number of operating systems are deployed along with a continuous kernel integrity monitoring/enforcement mechanism.

<sup>&</sup>lt;sup>1</sup>https://nvd.nist.gov/. Vendor: "linux", Product:"linux\_kernel", Keyword: "linux kernel"

Android distributions from major mobile vendors and recent versions of Microsoft Windows are two notable operating systems that have adopted this approach [126, 16, 12].

These integrity checking mechanisms typically monitor kernel memory and CPU configuration registers to prevent malicious modifications. Furthermore, they impose additional restrictions on the system, such as disallowing writable code pages in the kernel's address space. Continuous integrity monitoring makes compromising the kernel quite challenging – even in the presence of software vulnerabilities.

**Guarding the Guardians.** If the integrity enforcement mechanisms run at the same privilege level as the kernel they are meant to protect, then vulnerabilities in the kernel could be exploited to subvert the integrity enforcement mechanism itself. For example, a kernel bug has previously been exploited to bypass Microsoft's Kernel Patch Protection (KPP) feature [6].

To shield these protection mechanisms from a compromised kernel, numerous previous works have proposed leveraging virtualization support available in today's systems [32, 47, 67, 114, 102, 94, 23]. With this approach, the main OS runs on top of a hypervisor, while kernel protections are implemented in a hypervisor or another *separate* virtualized operating system. This provides additional protection as the hypervisor and the virtualized operating systems are isolated by the hardware. Microsoft Windows 10 has adopted this approach to protect its driver and kernel integrity enforcement mechanisms [126].

Alternatively, it is possible to leverage the TrustZone execution environment which is available on ARM CPUs. Programs that run under TrustZone are isolated and protected from the rest of the system at the hardware level [73]. Android devices commonly take advantage of TrustZone to protect the kernel integrity mechanisms from the main kernel [12, 16].

Even with the extra hardware-level isolation, software vulnerabilities in the kernel integrity enforcement mechanisms themselves remain exploitable. For instance, attacks against multiple generations of TrustZone-based kernel protections have been shown [85, 16]. In addition, virtualization-based security relies on hypervisors, which

themselves have a large attack surface – as proven by serious vulnerabilities that continue to be discovered in hypervisors [86, 88, 89, 90]. Furthermore, running operating systems on top of a restrictive hypervisor incurs performance overheads [118, 53]

#### Hardware Mechanisms for Safeguarding Kernel Integrity

In the second part of this dissertation, we present an efficient hardware-based protection, dubbed Neverland, which can be used to harden the operating system against kernelmode malware and rootkits. Neverland does not rely on a complex (and potentially vulnerable) kernel integrity monitoring software and incurs zero runtime performance overhead.

Once the kernel boots, Neverland's hardware irreversibly takes away the operating system's ability to overwrite certain configuration registers and portions of the physical address space. More specifically, we "lock" the kernel's code and read-only sections, security-critical configurations (e.g., driver signing configuration flags, system call table), and CPU configuration registers that store kernel entry points. These locked registers and memory regions can only be modified after rebooting the system. Neverland also prohibits the CPU from fetching kernel-mode code from any memory region lying outside the physical addresses assigned to the OS kernel and drivers.

Note that the code, data, and registers mentioned above are guarded or periodically scanned by a typical kernel integrity monitor. Locking these components at the hardware-level obviates the need to continuously run an integrity monitoring software.

We use a **hardware permission table** to mark portions of the physical address space as read-only, executable, privileged, and locked. On every instruction fetch and load/store, the CPU checks the permission table to determine the legality of the memory operations.

A number of embedded CPU architectures specify a form of (optional) physical memory permission tables (e.g., ARM MPU and RISC-V PMP specifications). These ISA extensions are normally used to implement a lightweight memory protection scheme in low-resource microcontrollers that do not have virtual memory support [11, 24].

CPUs with virtual memory support do not generally implement these physical memory permission schemes. The hardware support required by Neverland is a variation of such permission tables. We leverage immutable hardware tables to provide low-overhead operating system protections – without requiring complex integrity monitoring software that rely on hypervisors or trusted execution environments. In addition, we also introduce the notion of "locked" CPU configuration registers to prevent interrupt and system call hijacking.

Maintaining a separate physical address permission table has advantages over existing hardware-level privilege escalation defenses such as Intel Supervisor Mode Execution and Access Prevention (SMEP and SMAP) and ARM Privileged-eXecute-Never (PXN). SMEP/SMAP and PXN are under the total control of the operating system and can be disabled if the kernel is compromised. Neverland side-steps this issue by stripping away the operating system's ability to overwrite the permission table entries once the boot process is complete. Furthermore, since the physical address permission tables do not rely on virtual page permissions, attacks that manipulate the page table entries [84] are prevented.

We validated the efficacy of these protections by prototyping the hardware extensions in Spike (the official RISC-V emulator) and running a minimally modified version of the Linux kernel on the emulator. Our evaluations based on RTL simulation and synthesis show that the hardware extensions required by Neverland incur minimal silicon and energy cost, and that integrating the proposed protections does not incur any performance overhead beyond the 10s of milliseconds that are required to setup permissions at boot time.

### **1.3 Summary of Contributions**

We make the following contributions towards understanding and overcoming the threat of cold boot attacks on modern memory systems:

• We demonstrate DDR interfaces continue to be vulnerable to cold boot attacks despite the introduction of increasingly advanced memory scramblers. We

demonstrate data recovery from scrambled DDR3 and DDR4 DRAMs and show how encryption keys can be extracted by descrambling memory (Chapter 3, [124]).

• We demonstrate memory scramblers in DDR4 controllers can be replaced with strong ciphers (such as ChaCha8) without introducing any performance overheads (Chapter 3, [124]).

We make the following contributions towards reducing the overhead of authenticated memory encryption schemes (which prevent bus snooping and memory tampering):

- We show how the extra memory chips and buses available in ECC DRAM can be leveraged to eliminate the message authentication code (MAC) storage overheads

without forgoing error correction or integrity checking capabilities. In addition to reducing storage overheads, this approach has the added benefit of reducing the performance impact of authenticated memory encryption by up to 15% as MACs are read in parallel with the data through the ECC bus (Chapter 4, [125]).

- We present a data encoding scheme that can reduce counter storage overhead incurred by counter-mode encryption by a factor of 7, while still enhancing encryption performance by up to 10% (as a result of reductions in off-chip memory access) (Chapter 5, [125]).

We make the following contributions towards safeguarding the operating system's memory (code/data) from kernel-mode malware and rootkits:

- We present a hardware-based memory protection scheme that can protect an operating system from kernel-mode malware and rootkits. The protection works by stripping away some of the kernel's powers once the boot process is done. We show how this protection can be applied without incurring any runtime performance overhead (Chapter 7).

- We demonstrate the practicability of the approach by integrating the proposed protections into an emulated RISC-V CPU, and by making minimal changes to the

Linux kernel to take advantage of these hardware protections. We also show the hardware and energy overheads of the additional hardware (a permission table) are minimal (Chapter 7).

**Dissertation Organization.** This dissertation is organized into two parts. The first part (Chapters 2 - 5) focuses on hardware-level attacks and defenses on memory systems, while the second part (Chapters 6 and 7) focuses on operating system security and our low-overhead kernel memory protection scheme. Chapter 2 and Chapter 6 provide background material for Part 1 and Part 2 of the dissertation respectively.

Part I: Efficient Physical Memory Security

# Chapter 2 Physical Memory Security

Data stored in an off-chip memory, such as DRAM or non-volatile main memory, can potentially be extracted or tampered with by an attacker with physical access to a device. In the first part of this dissertation, we will focus on mechanisms for defending against such physical attacks.

This chapter provides a primer on bus snooping and cold boot attacks (two techniques that can be used to physically extract data out of main memory), and motivates the need for protecting the confidentiality and integrity of data stored in off-chip memory. We also summarize the state-of-the-art on memory encryption and authentication techniques that are employed for preventing such physical attacks.

### 2.1 Data Remanence and Cold Boot Attacks

DRAMs store bits by storing charge in bit cell capacitors. Due to substrate leakage, these capacitors can lose their charge in 10s of milliseconds unless the system refreshes the bit cell. For this reason, DRAMs are conventionally expected to lose their content once a system loses power. However, contrary to conventional wisdom, studies have shown that DRAM modules can maintain a large fraction of their content after being powered down. It has also been demonstrated that the bit cell capacitors can retain their charge for significantly longer periods of time (up to minutes) when the DRAM chips are super-cooled [107, 37].

This long-term retention of DRAM content poses security risks since an attacker

with physical possession of a device can move the DRAM module from a locked system to an attacker-owned machine, and extract sensitive data stored in the DRAM. In 2008, Halderman *et.al.* demonstrated that DDR and DDR2 modules can retain 99.9% of the data stored in them for minutes when they are cooled down to  $-50^{\circ}C$  using an off-the-shelf can of compressed air [37]. They exploited this fact to extract sensitive data such as disk encryption keys from locked and suspended computers – an attack vector now popularly known as a "cold boot attack".

After the demonstration of cold boot attacks, other studies have replicated the attack on additional platforms, including Android devices [65]. Another work reproduced the results from [37] and also demonstrated the feasibility of cold boot attacks on DDR3based systems that do *not* employ any form of memory scrambling [56]. Today, many CPUs employ some form of memory scrambling that XORs data with keys generated during system boot-up. As a result, cold boot attacks have become more challenging.

#### 2.1.1 Cold Boot Attack Mitigation Measures

To prevent extraction of encryption keys via cold boot attacks, disk encryption tools typically erase keys stored in memory immediately after a disk is unmounted. This approach can be applied on partitions other than the one the operating system is running on. While this approach reduces the attack surface, it will fail to protect disk encryption keys if a device is acquired by an attacker while disks are still mounted and the key is resident in DRAM (*e.g.*, if the machine is in sleep mode while the attacker acquires it). It should be noted that even disk encryption tools such as BitLocker that store encryption keys within trusted platform modules (TPMs) are still susceptible to cold boot attacks as the expanded keys for mounted volumes are cached in DRAM until the drive is unmounted or until the system is cleanly shutdown [98].

Solutions that store encryption keys exclusively in CPU registers have also been proposed [105, 64]. Loop-Amnesia [105] stores encryption keys in model-specific registers that are typically used by performance counters. Similarly, Tensor [64] leverages x86 debug registers for storing keys. These solutions require a patched operating system to prevent user-space access to these otherwise freely accessible

registers, as they are now storing sensitive keys. Such approaches are capable of protecting disk encryption keys, but they typically suffer performance impacts since round keys must be generated before any encryption operation and subsequently erased. Previous work has shown that expanded round keys greatly simplify the task of identifying keys in memory [37], and thus, they should not reside in memory. However, due to the lack of protected on-chip storage and the limited size of registers, a large amount of sensitive data still remains in main memory, at least for a limited time, unprotected.

Full memory encryption techniques, both in hardware and software, have been suggested [40, 122]. Furthermore, the new Intel Software Guard Extension (SGX) includes hardware support for maintaining confidentiality and integrity of data stored in DRAM by employing strong encryption (AES) and message authentication codes (MACs). Unfortunately, SGX has been shown to incur significant performance overheads [10, 117]. This makes such high-security solutions undesirable for latency-sensitive and bandwidth-intensive applications. The design of a memory encryption scheme that provides integrity at low overhead is still an open problem. Recent AMD CPUs also provide full-memory AES encryption (without integrity checking) [50].

Finally, newer machines with compact form factors come with their DRAM chips either directly soldered on the motherboard or packaged with the CPU chip together. While this can make attacks more cumbersome, it does not fully deter them. A determined attacker can still carefully desolder the DRAM modules or boot from external media (potentially after flashing the BIOS to enable boot from external media).

#### 2.1.2 Cold Boot Attacks and Memory Scramblers

In older DDR and DDR2 systems, the CPU stores data in memory in plaintext form. This made capturing memory contents straightforward: simply transfer the DRAM to another system and read the full contents of the DRAM. With the introduction of high-speed buses, however, the scrambling of DRAM data was introduced to improve signal integrity and reduce power supply noise [63].

DRAM traffic is not random, and long successions of 1s or 0s can be observed on the

data bus under normal workloads. As a result, energy can potentially be concentrated at certain frequencies or all the data lines can switch in parallel resulting in high di/dt(current fluctuations). The noise created by these phenomena can affect signal integrity and power delivery. The Intel Core processor datasheets [80, 78, 79] state that by randomizing the DRAM data, potentially dangerous di/dt harmonics are eliminated. Consequently, the overall power demand of the bus becomes largely uniform.

Over time, however, these scramblers have been adapted to also provide data obfuscation, in particular with the introduction of scrambler seeds that change after each reboot. Another Intel product datasheet [77] states that its integrated memory controller has a "DDR Data Scrambler to reduce power supply noise, improve signal integrity and to encrypt/protect the contents of memory." These data obfuscation features thwart straightforward cold boot attacks. In Chapter 3 we will present a detailed analysis that shows that modern scramblers, despite their increasing complexity, cannot prevent more advanced cold boot attacks.

## 2.2 Bus Snooping and Replay Attacks

A cold boot attack provides the attacker a static snapshot of the memory system. A more powerful attacker can track all DRAM read and write transactions and analyze how the data changes over time. If a memory encryption scheme does not address this threat model (e.g. a strong stream cipher used with a fixed key and nonce), the attacker can easily recover the plaintext of a specific block after collecting multiple ciphertext samples.

**Data Tampering and Replay.** An active attacker may also attempt to manipulate execution by flipping bits stored in memory. Such attacks cannot be prevented by solely encrypting data and require message authentication codes to be effectively prevented (discussed in the next section). An even more powerful attack involves resetting a memory block to an older version – a process commonly referred to as a "replay" attack. Replay attacks cannot be protected by simply tracking MACs as the attacker can reset

both the encrypted block and its associated MAC value. As we will detail in the next section, preventing replay attacks requires a more complex defense.

## 2.3 Authenticated Memory Encryption

In this section, we provide an overview of the state-of-the-art in authenticated memory encryption and the associated overheads.

**Threat Model.** Authenticated memory encryption aims to protect a system from an attacker that has physical access to a device. An attacker with physical access to a device can either snoop data as it is being transferred over the memory bus, or extract data directly out of DRAM modules. Authenticated memory encryption ensures confidentiality and integrity of data, but does not prevent information leakage through memory access patterns [59, 93, 109].

#### Early Work in Memory Encryption and Integrity Checking

Execute-Only Memory (XOM) [55] is one of the earliest efforts to design an architecture for creating tamper and copy-proof software. Under XOM, software that is to run on a specific target CPU is encrypted using the target CPU's public key. Since only the target CPU has the private key, no external entity can examine, execute, or modify the program code. As public key encryption is slow, the scheme used a symmetric cipher to encrypt the code, after which the symmetric key itself is encrypted using the public key and embedded in the program's header.

XOM's protection mechanisms do not fully prevent replay attacks – where an attacker resets contents of data in external memory to an earlier state. **Hash-tree** based memory verification was proposed to address this vulnerability [33] (detailed below). AEGIS [111] improves upon XOM by leveraging advances made in cryptography and memory integrity checking. AEGIS is resilient to replay attacks, and also reduces decryption latency through the use of **counter mode encryption** (discussed below).

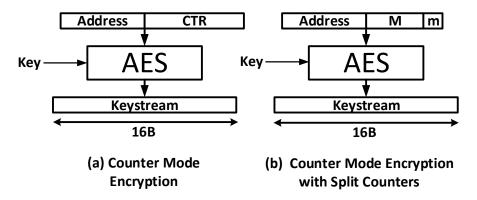

**Figure 2.1 Counter (CTR) Mode Encryption.** CTR mode encryption generates a keystream by encrypting a counter value with a block cipher such as AES. The counter is incremented after each encryption to avoid keystream reuse. The counter value is concatenated with the physical address of the block being encrypted to generate a unique keystream for each memory block. The generated keystream is XOR'd with the data to be encrypted/decrypted. The split counter scheme reduces storage space by storing a small (e.g., 8-bit) counter (m) per block and sharing a larger (e.g., 64 bit) counter (M) among multiple blocks.

#### **Counter Mode Encryption.**

High-performance memory encryption implementations use a block cipher (mainly AES) in counter mode. In counter mode memory encryption, a distinct counter value is associated with each 64-byte memory block. We generate a keystream for a memory block by encrypting the corresponding counter value using a block cipher such as AES. The generated keystream is then XOR'd with the data to be encrypted/decrypted (Figure 2.1a). To make the keystream unique across different memory blocks, the physical address of the memory block being encrypted is concatenated with the counter value as shown in Figure 2.1a.

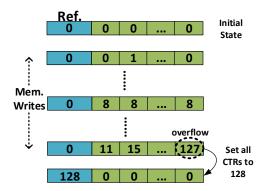

To get the maximum security guarantees from CTR mode encryption, a counter value must be incremented whenever the corresponding memory block is updated. If the counters are incremented during each write, then identical values written to the same memory location at different times will appear as different ciphertexts. These counters themselves are then stored in the off-chip memory in plaintext. **Counter Storage Overhead.** The size of the counters needs to be large enough to ensure they do not overflow and wrap around to 0. An overflow would result in keystream reuse – which compromises the security of the system. To prevent overflow, counters that are 64-bit or 56-bit wide are typically employed. Such large counters would not overflow for the lifetime of any machine. Using large counters, however, results in a significant storage overhead. With a 56-bit counter per 64-byte block, the counter storage overhead will be  $\sim 11\%$  (Figure 1.1).

#### **Data Integrity**

Securing data using counter-mode encryption alone, however, cannot prevent an attacker from modifying or resetting data. We need to provide an additional mechanism to ensure *data integrity*. Ensuring data integrity requires us to compute and store distinct message authentication codes (MACs) for each memory block. A MAC is computed using a secret key that is not known by the attacker. Similar to encryption keys, the key used to compute a MAC is securely stored in an on-chip SRAM or register.

As a DDR memory block is read/written at a 64-byte memory block granularity, MAC values are also computed and stored for each 64-byte memory block. As a result, protecting large chunks of memory results in significant storage overheads. For example, Intel SGX computes 56-bit MACs for each memory block. This results in an  $\sim 11\%$  overhead – in addition to the 11% counter storage overhead discussed above (Figure 1.1).

#### **Integrity Trees**

When protecting large chunks of memory, the MAC values will require more storage than what is normally feasible on-chip. For example, protecting just 128MBs of memory would require 14MBs for MAC storage (assuming 56-bit MACs per block). As a result, we need to store the MAC values in an off-chip memory.

However, when storing the MACs off-chip, we need to prevent the attacker from tampering with the MAC values themselves. If the integrity of the MAC values is not

enforced, an attacker can "replay" old values by concurrently resetting the counter, MAC, and data to an older value.

MAC values are stored off-chip in a tamper-proof manner by using **integrity trees** [33, 95, 36]. As already discussed, all data that is stored in an off-chip DRAM is not trusted. On the other hand, the amount of storage that is available on-chip is limited. The main aim of integrity trees is to protect the integrity of a large off-chip memory using a small amount of on-chip metadata storage.

**Constructing an Integrity Tree.** To build an integrity tree, we begin by computing a MAC value for all the data blocks that we need to protect. These MAC values ( $M_0$ ) form the leaf nodes of the integrity tree. The size of the MAC bits is only a fraction of the data blocks. For example, an 8-byte (64-bit) MAC can be used to protect a 64-byte block (Intel SGX uses just 56-bit MACs [81]). We then proceed to chunk multiple MAC values together into a single memory block. If our MACs are 8 bytes, we can chunk 8 of them together and store them in a single memory block.

To protect  $M_0$  from tampering, we compute yet another set of MACs  $(M_1)$  over the memory blocks that are storing  $M_0$ . The  $M_1$  MACs form the second level of the tree. Note that  $M_1$  will be smaller than  $M_0$ . We repeat this process recursively until we reach a level where the MACs can fit in an allocated on-chip memory. Since the top level is stored in an on-chip memory, it cannot be easily tampered with.

**Reading/Writing Protected Data.** When reading a memory block, its MAC value is computed and checked against the value stored in its parent node. This check is then recursively applied until we reach the root node. Since the attacker cannot tamper with the root node (which is stored on-chip), any changes made to the nodes of the tree can be detected during the final check made against the root node. Similarly, when a data block in memory is modified, all of its parent nodes need to be updated.

## 2.4 Previously Proposed Optimizations

Multiple optimizations have been proposed to reduce the performance and storage overhead associated with encryption and integrity checking. In this section, we highlight prior optimizations that are relevant to our work [33, 95, 121].

**Counter and MAC Caches.** Verifying data integrity by recursively reading nodes from the integrity tree requires extra memory reads. To reduce the overhead incurred by these extra reads, Gassend et al. cache the integrity tree on an on-chip cache [33]. Just like conventional CPU caches, these caches reduce the latency for reading MACs and counters – especially when the accesses exhibit spatial and temporal locality. Intel's SGX implementation has a dedicated cache for MACs and counters [36, 81].

**Bonsai Merkel Trees.** The work by Rogers et al. [95] made notable enhancements to tree-based integrity checking. They made the observation that it is possible to ensure the integrity of data blocks by only protecting the integrity of counters. Since the size of counters is significantly smaller than the size of data blocks, protecting the counters (instead of the data) results in a significantly smaller tree – which the authors call a Bonsai Merkle tree.

Their technique requires the counters used for encryption to also be used as an additional input when computing MAC tags for the data blocks. With this modification, if an attacker changes the data or MAC values in memory without changing the counter value, the integrity checks will fail. In short, modifying data without detection requires modifying the protected counters as well. Intel SGX uses this optimized tree structure [36, 81]. We also use Bonsai Merkel trees as the baseline in our evaluations and apply our proposed optimization over them.

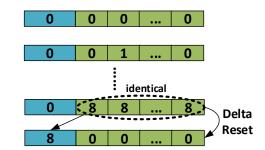

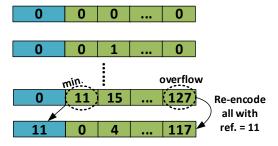

**Split-Counters.** Yan et al. [121] proposed **split counters** – a compact counter storage scheme (Figure 2.1b). Split counters reduce the overall size of counters by storing small (8-bit or less) minor counters (m) per memory block. However, an 8-bit counter would easily overflow, resulting in nonce re-use after just hundreds of writes to the

same memory block. Re-encrypting the entire memory with a new key when a single counter overflows would be extremely expensive.

The authors address this issue by coupling minor counters with a 64-bit major counter (M) – which would not overflow for millennia. A single major counter is shared by multiple consecutive blocks, incurring significantly less storage overhead compared to storing a 64-bit counter for every block. The consecutive blocks that share a major counter form a block-group  $^1$  – which is typically a few kilobytes. When a block is accessed, it's minor counter is concatenated with its major counter to obtain the full counter value (Figure 2.1b). When a minor counter overflows, the entire block-group is re-encrypted using a new major counter. This enables the technique to avoid re-encrypting the entire memory.

Split counters can reduce the counter storage overhead by a factor of 8 compared to storing a 64-bit counter for each memory block. However, this counter compaction scheme requires frequent re-encryption of block-groups on memory intensive applications. In Chapter 5, we present a counter encoding and storage scheme that results in a significantly lower rate of re-encryption while maintaining the compactness of split counters.

<sup>&</sup>lt;sup>1</sup>The original paper refers to block-groups as "pages". We avoid using that terminology throughout this dissertation to avoid confusion with OS pages.

# **Chapter 3**

# Cold Boot Attacks on Scrambled DDR3 and DDR4 Memory

As we have described in the previous chapter, previous work has demonstrated that systems with unencrypted DRAM interfaces are susceptible to cold boot attacks [37, 65, 14]. This method has been shown to be an effective attack vector for extracting disk encryption keys out of locked devices.

However, most modern systems incorporate some form of data scrambling into their DRAM interfaces [14, 76] making cold boot attacks challenging. While first added as a measure to improve signal integrity and reduce power supply noise, these scramblers today serve the added purpose of obscuring the DRAM contents. As a result, multiple attempts to perform cold boot attacks on systems with scrambled DRAM have failed in the past due to lack of detailed information about the scrambler design [35, 106]. This has led some to conclude that scrambled memory systems are not susceptible to cold boot attacks [35, 38].

In this chapter, we will begin by presenting an empirical analysis of the data obfuscation features found in (older) Intel DDR3 memory scramblers and then investigate enhancements that have been introduced in the newer DDR4 memory scramblers. Our study reveals that DDR4 memory scramblers have been redesigned in Intel's 6<sup>th</sup> generation Core (Skylake) processors in a manner that provides enhanced data obfuscation over previous generation DDR3-based scramblers. While this enhanced design is resistant to attacks that have been demonstrated in the past, it is certainly not impenetrable. In this work, we reveal details of our DDR4-based cold boot attack that is

able to successfully extract AES keys from a DDR4 DRAM connected to an Intel Skylake processor. We demonstrate this attack by extracting VeraCrypt/TrueCrypt master keys.

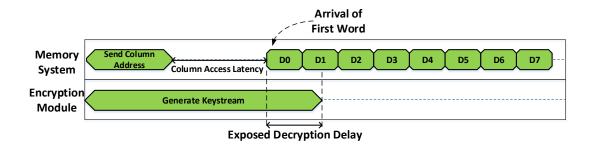

The limitations of memory scramblers we point out in this chapter motivate the need for strong, yet low-overhead full-memory encryption schemes that can transparently replace scramblers. Existing schemes such as Intel's SGX can effectively prevent such attacks, but have overheads that may not be acceptable for performance-sensitive applications [10, 117]. To that end, we present analyses that confirm modern stream ciphers such as ChaCha8 are sufficiently fast that it is now possible to completely overlap keystream generation with DRAM row buffer access, thereby enabling the creation of strongly encrypted DRAMs with zero exposed latency. Adopting such low-overhead measures in future generation of products can effectively shut down cold boot attacks in systems where the overhead of existing memory encryption schemes is unacceptable. Furthermore, the emergence of non-volatile DIMMs that fit into DDR4 buses is going to exacerbate the risk of cold boot attacks. Hence, strong full memory encryption is going to be even more crucial on such systems.

Our goal in this work is not to criticize the state of memory scramblers, but to make two important observations: *i*) DRAM (including DDR4) continues to be susceptible to cold boot attacks as the scramblers do not provide sufficient confidentiality guarantees, and *ii*) modern high-throughput stream ciphers (*e.g.*, ChaCha8, CTR mode AES-128) coupled with high-speed ASIC implementations make it practical to create strongly encrypted memories that are impervious to cold boot attacks without incurring any performance penalty.

### **3.1** Overview of Memory Scramblers

In older DDR and DDR2 systems, the CPU stores data in memory in plaintext form. This made capturing memory contents straightforward. With the introduction of high-speed buses however, the scrambling of DRAM data was introduced to improve signal integrity and reduce power supply noise [63].

DRAM traffic is not random and successive 1s and 0s can be observed on the data

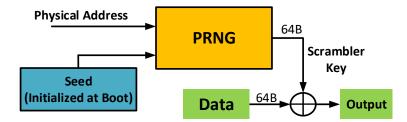

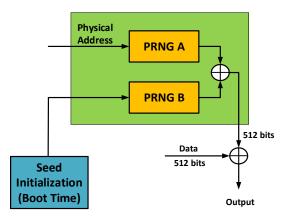

**Figure 3.1 High-level View of Memory Scrambling.** Data is scrambled by XOR'ing it with a pseudo-random number. The scramble/descramble process is symmetric and a seed (generated at boot time) and portions of the physical address bits are used by the pseudo-random number generator (PRNG) to generate 64-byte keys.

bus under normal workloads. As a result, energy can potentially be concentrated at certain frequencies or all the data lines can switch in parallel resulting in high di/dt (current fluctuations). The noise created by these phenomenon can affect signal integrity and power delivery. The Intel Core processor datasheets [80, 78, 79] state that by randomizing the DRAM data, potentially dangerous di/dt harmonics are eliminated. Consequently, the overall power demand of the bus becomes largely uniform.

Over time, however, these scramblers have been adapted to also provide data obfuscation, in particular with the introduction of scrambler seeds that change after each reboot. Another Intel product datasheet [77] states that its integrated memory controller has a "DDR Data Scrambler to reduce power supply noise, improve signal integrity and to encrypt/protect the contents of memory." These data obfuscation features thwart straightforward cold boot attacks.

Figure 3.1 provides a high level model of a data scrambling unit. It is very similar to a symmetric encryption scheme. Before data leaves the CPU, it is XOR'd with pseudo-random numbers. When data is read back from DRAM, it is XOR'd with the same pseudo-random number to recover the original data. The pseudo random number generater (PRNG) can potentially be initialized using a certain initial seed.

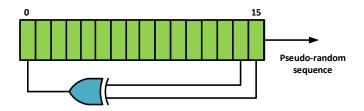

While Intel's datasheets do not provide any additional details about their data scrambler architecture, their 2011 publication [63] discloses that Linear Feedback Shift Registers (LFSRs) are used as pseudo-random number generators (PRNGs) by

Figure 3.2 An Example Linear Feedback Shift Register

the scrambler implemented in the Westmere microarchitecture. An LFSR is a simple hardware component commonly used to generate pseudo-random numbers. It consists of a shift register and a feedback function that sets the leftmost bit of the shift register. The feedback function is conventionally an XOR of some of the bits of the shift register. Figure 3.2 shows an example PRNG constructed out of an LFSR. The specific design shown in the figure is the standard LFSR used to scramble data on one of the buses on a hybrid memory cube [76]. Different random number sequences can be generated by varying the initial state of the LFSR, register width, and the bits that are XOR'd together. The Intel publication [63] also discloses that the LFSRs are seeded using a portion of the address bits. This reduces correlations between memory blocks containing the same data values.

#### 3.1.1 Memory Scramblers and Cold Boot Attacks

The information presented so far gives us a high-level understanding of the inner workings of memory scramblers. However, this information is not sufficient to analyze to what extent scramblers can defend against cold boot attacks. In the rest of this chapter, we will present an empirical analysis of multiple generations of memory and show that these interfaces continue to be vulnerable to cold boot attacks.

| CPU Model             | Microarchitecture | Launch Date |

|-----------------------|-------------------|-------------|

| Intel i5-2540M (DDR3) | SandyBridge       | Q1, 2011    |

| Intel i5-2430M (DDR3) | SandyBridge       | Q4, 2011    |

| Intel i7-3540M (DDR3) | IvyBridge         | Q1, 2013    |

| Intel i5-6400 (DDR4)  | Skylake           | Q3, 2015    |

| Intel i5-6600K (DDR4) | Skylake           | Q3, 2015    |

Table 3.1CPU Models of Tested Machines. In this work, we analyzed the DDR3 and DDR4memory scramblers of the listed processors.

### 3.2 Analysis Framework

Since the scramblers implemented in modern CPUs are not publicly documented, we needed to empirically analyze the data transformations applied by the memory controller before attempting to identify its limitations. For this study, we analyzed data stored by the DDR4 memory controllers integrated in Intel's 6<sup>th</sup> Generation Core Processors. For comparison purposes, we also analyzed older scramblers found in multiple generations of DDR3 controllers. We performed this analysis on multiple laptop and desktop computers. The CPUs we have analyzed are given in Table 3.1.

All data that is eventually written to DRAM passes through the scrambler. Similarly, all data that is read by software is first passed through the descrambler and regular software cannot see the raw scrambled data. This scrambling/descrambling algorithm is implemented inside the memory controller, which cannot be directly accessed. Hence, we needed to devise a mechanism for capturing and observing the raw output of the memory scrambler. We did this using two approaches.

For the DDR4 DRAMs, we relied on a motherboard that enabled us to switch the scramblers on and off through the BIOS configuration menus. However, the DDR3-based systems we used for comparative analysis do not expose a mechanism for controlling the scrambler. Hence, we relied on an external FPGA-based system to directly access the DDR3 memory's contents. On the FPGA board we can read and write any raw (unscrambled) data. For our experiments, we used the Xilinx VC709 board with Virtex-7 FPGA to write unscrambled data to the DRAM (Figure 3.3).

To extract the scrambler keys, we implemented a "reverse cold boot attack" on

a memory filled with all zeros. We use the mechanisms we just described to write *unscrambled* zeros to a DRAM module. Given that the final step of scrambling is XOR'ing the scramble key with the data, we can discover the keys by initially filling all memory with *unscrambled* zeros and then re-reading the data with the scrambler turned-on. In this case note that when the zeros are read back through the descrambler, it will attempt to descramble the data using the scrambler keys and we are actually reading the scrambler keys themselves (*i.e.*,  $0 \oplus key$ ). Based on this approach, we extract the scrambler keys using the following steps:

- 1. On a system where scrambling is disabled, we fill the entire memory with raw (unscrambled) zeros.

- 2. We freeze the DRAM and transfer it onto the motherboard of the system we are analyzing.

- 3. We boot scrambled system and read the raw zero values from memory using our custom GRUB module that runs on the bare hardware.

The resulting memory image retrieved by the program (a GRUB module) is filled with scrambler keys (since a scrambler key XOR'd with zero yields the key). The program we run to extract the memory dump has no operating system or virtual memory manager running underneath it. Hence, we have full view of DRAM contents while introducing minimal pollution to the memory contents. Note that this procedure is the reverse of a cold boot attack, since in this situation we want to inject known data *into* a scrambled system.

Instead of filling the DRAM with zeros, we can alternatively begin by allowing the DRAM to fully decay to its ground state. We can then read out the value each DRAM block assumes at this ground state *with the scrambler turned off*. Note that portions of the DRAM cells decay to a zero while others decay to a one. After this initial "profiling" stage, we can boot into a scrambled system with the fully decayed DRAM and read out this known data (*i.e.*, the ground state values) through the scrambler. Unlike the technique where we fill the memory with zeros, we do *not* have to worry about bit decay that might occur in midst of the experiment.

Figure 3.3 FPGA Used for Initializing DDR3 DRAM with Zeros.

Later in our research, we acquired a DDR4-based motherboard that allowed us to reboot an initially scrambled machine with the memory scramblers turned off – without destroying the scrambled DRAM contents from the previous boot cycle. Hence we were able to study the data transformations made by the scrambler by simply writing scrambled data to memory and reading it back out on the next boot cycle with the scrambler turned off. It should be noted that this setup was used to speed up our analysis, and the cold boot attacks detailed later in this section were indeed tested by transporting a frozen DDR4 DRAM across two machines. Figure 3.4 shows the frozen DDR4 DRAM on the scrambled machine's motherboard, prior to being pulled out and re-socketed into the motherboard of a machine with a disabled scrambler.

**Figure 3.4** Cold Boot Attack on DDR4 DRAM. This photo shows the DRAM in one of our DDR4-based systems. The DRAM is filled with data scrambled by the memory interface of an Intel Skylake-based CPU. The memory has been cooled to  $-25^{\circ}C$ , and it will next be moved to a separate system where its contents will be descrambled.

# 3.3 Analysis of DDR3 Scramblers

In this section, we present an empirical analysis of DDR3 scramblers based on the experimental setup we described in the previous section  $^{1}$ .

#### 3.3.1 Seeding the Scrambler

One property that can be seen by observing the list of keys used for scrambling is that the keys change every time the system reboots. Keys extracted for one boot session cannot be used to descramble memory contents on future boot sessions. This make cold boot attacks more challenging.

When studying the BIOS firmware for an Intel SandyBridge machine [2], we observed

<sup>&</sup>lt;sup>1</sup>A concurrent work by Bauer et al. [14] also analyzes Intel's DDR3 scramblers. The analysis in dissertation extends into the more advanced DDR4 scramblers as well.

(a) Original Image

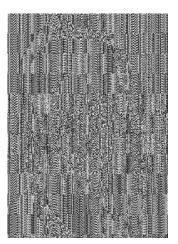

(b) Scrambled DDR3 Data

(c) Scrambled DDR3 Data Read Back After Reboot

(e) Scrambled DDR4 Data Read Back After Reboot

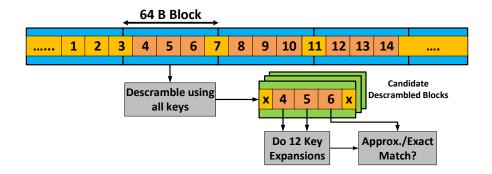

**Figure 3.5 Visual Comparison of DDR3 and DDR4 Scramblers on Single Channel Machines.** Due to the larger key pool used in the Skylake DDR4 scramblers, repeated data in memory reveal fewer correlations compared to DDR3 (compare (b) and (d)). Additionally, unlike DDR3, portions of the key are not factored out in the DDR4 scramblers when data is loaded back using a different seed (compare (c) and (e)). Overall, DDR4 memory achieves better data obfuscation.

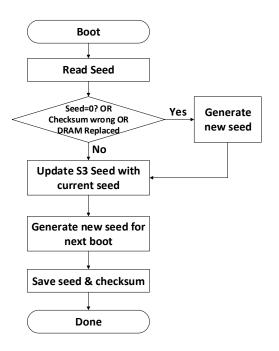

the memory scrambler is initialized with a 32-bit random seed during the boot process. The BIOS can change this seed on each reboot. This seed is used by the scrambler's psedudo-random number generator. Details on the seed generation process for the particular firmware we analyzed can be found in the Appendix.

#### 3.3.2 Memory Scrambler Properties

The aforementioned 32-bit random seed is not directly used to scrambler memory blocks. On DDR3 and DDR4 systems, data is read in blocks of 64 bytes. Therefore, the 32-bit seed must be "expanded" into a 64-byte random number that can be XOR'd with the entire memory block (see Figure 3.1). Using the techniques we described in Section 3.2, we extracted the 64-byte scrambler keys that are directly XOR'd with the data. Our observations on these 64-byte scrambler keys can be summarized as follows:

- 1. A limited number of scrambler keys are **reused multiple times** to scramble the whole memory. We observed a total of 16 scrambler keys per memory channel.

- 2. On a reboot, all scrambler keys change based on the new seed.

- 3. The mapping of which memory blocks share the same scrambler key is fixed and does not change after reboot.

- 4. Each memory channel has its own set of distinct 16 scrambler keys

The fact that addresses from different channels are scrambled using keys specific to that channel suggests that the scrambler's output also depends on a portion of the address bits. This is consistent with a disclosure from Intel [63].

Figure 3.5(b) illustrates how the raw data shown on 3.5(a) is scrambled and stored by the DDR3 controller. While the image in Figure 3.5(b) is obscured due to scrambling, features of the original image are still present. This correlation resulted from the scramblers reuse of a single key multiple times. Clearly, this reuse of keys can be leveraged to descramble data in a straight forward manner. **Key Idea:** A limited number of keys are reused multiple times to scramble a large memory space. The assignment of which memory blocks use the same keys is fixed and does not change after reboot.

#### **Reading Data After Reboot**

As mentioned above, the scrambler keys are changed after every reboot. As a result, we will not get the original data written to DRAM if we try to re-read it after a cold-reboot.

To get additional insights into the scrambler's characteristics, we analyzed how data re-read after system reboot differs from the original one. Figure 3.5(c) illustrate how the original data in Figure 3.5(a) would appear when we read it back after reboot. Perhaps surprisingly, when the original data is read back after reboot, it will appear as though the data that has been scrambled using just a single key per channel! In other words, every memory block in a channel can be descrambled by XOR'ing them with a single, fixed 64-byte value. Note that a total of 16 scrambler keys (per channel) are used to originally scramble the data. However, simply rebooting the system and re-reading the data will make it appear as though a single scrambler key was used for each channel.

To understand what is happening, suppose data  $D_1$  is stored at address  $A_1$  after being scrambled using key  $K_1$ . Similarly, assume data  $D_2$  at address  $A_2$  is scrambled using key  $K_2$ . The memory content at the two addresses will be:

- $A_1: D_1 \oplus K_1$

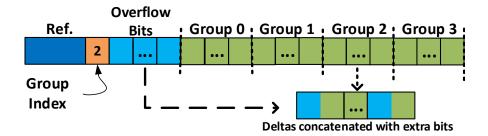

- $A_2: D_2 \oplus K_2$