# Interconnect and Memory Design for Intelligent Mobile System

by

Jingcheng Wang

A dissertation submitted in fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical and Computer Engineering) in The University of Michigan 2020

Doctoral Committee:

Professor Dennis Sylvester, Chair Professor David Blaauw Professor Reetuparna Das Professor Hun-Seok Kim Jingcheng Wang jiwang@umich.edu ORCID iD: 0000-0001-5831-9063 © Jingcheng Wang 2020 To my family and friends

# TABLE OF CONTENTS

| DEDICATIO   | Ν                                                                                                    | ii   |

|-------------|------------------------------------------------------------------------------------------------------|------|

| LIST OF FIG | URES                                                                                                 | V    |

| LIST OF TAI | BLES                                                                                                 | viii |

| ABSTRACT    |                                                                                                      | ix   |

| CHAPTER     |                                                                                                      |      |

| I. Introd   | luction                                                                                              | 1    |

| 1.1         | Technology Scaling and Intelligent Mobile System                                                     | 1    |

| 1.2         | Challenges for Intelligent Mobile System                                                             | 3    |

|             | 1.2.1 Slow and High Energy Interconnect                                                              | 4    |

|             | 1.2.2 Large On-Chip Memory                                                                           | 6    |

| 1.3         | Contribution of This Work                                                                            | 9    |

|             | figurable Self-Timed Regenerators for Wide-Range Volt-<br>caled Interconnect                         | 12   |

| 2.1         | Introduction                                                                                         | 12   |

| 2.2         | Proposed Approach                                                                                    | 14   |

| 2.3         | Measurements and Results                                                                             | 19   |

| 2.4         | Summary                                                                                              | 21   |

|             | nm Compute SRAM with Bit-Serial Arithmetic Oper-<br>s for Programmable In-Memory Vector Acceleration | 24   |

| 3.1         | Introduction                                                                                         | 24   |

| 3.2         | Overview of Bit-serial Arithmetic and CRAM Architecture                                              | 28   |

|             | 3.2.1 Bit-serial Arithmetic                                                                          | 28   |

|             | 3.2.2 CRAM Architecture                                                                              | 29   |

| 3.3         | CRAM Circuitry                                                                                       | 31   |

|           | 3.3.1 8T transposable bit cell                                                                                      | 31 |

|-----------|---------------------------------------------------------------------------------------------------------------------|----|

|           | 3.3.2 Computing Peripherals                                                                                         | 33 |

| 3.4       | Multi-cycle Arithmetic                                                                                              | 35 |

|           | 3.4.1 Integer Addition and Subtraction                                                                              | 36 |

|           | 3.4.2 Unsigned Integer Multiplication                                                                               | 37 |

|           | 3.4.3 Unsigned Integer Division                                                                                     | 38 |

|           | 3.4.4 Comparison and Search                                                                                         | 38 |

|           | 3.4.5 Floating-point Arithmetic                                                                                     | 39 |

| 3.5       | Measurements and Results                                                                                            | 41 |

| 3.6       | Summary                                                                                                             | 44 |

| Powe      | W Deep-Learning Accelerator with 270KB Custom Low<br>r SRAM and Non-Uniform Memory Hierarchy for Mo-<br>ntelligence | 47 |

| 4.1       | Introduction                                                                                                        | 47 |

| 4.2       | Deep Learning Algorithm and Processor                                                                               | 50 |

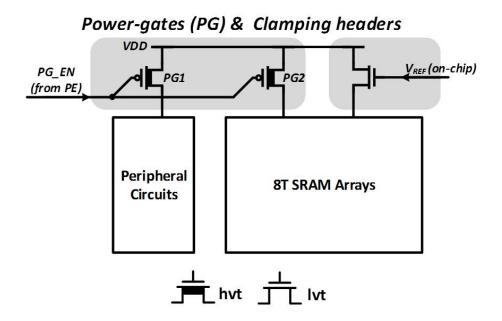

| 4.3       | Non-Uniform Memory Access Architecture                                                                              | 54 |

| 4.4       | Low Power Custom SRAM                                                                                               | 57 |

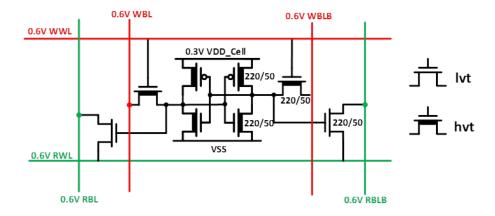

|           | 4.4.1 8T HVT Bit-cell and Noise Margin                                                                              | 57 |

|           | 4.4.2 Active Power Reduction Techniques                                                                             | 59 |

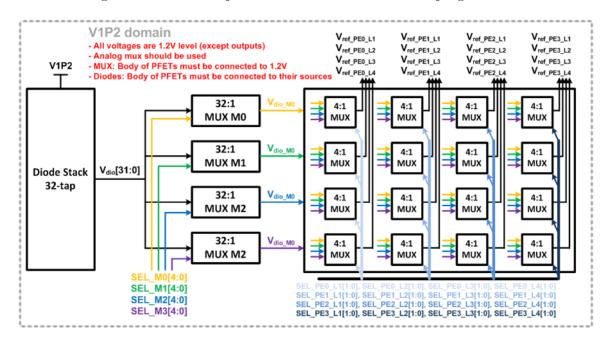

|           | 4.4.3 Leakage Power Reduction Techniques                                                                            | 62 |

| 4.5       | Measurements and Results                                                                                            | 63 |

| 4.6       | Summary                                                                                                             | 65 |

| -         | W/bit Ultra-low Leakage Voltage-Stacked SRAM for igent Edge Processors                                              | 67 |

| 5.1       | Introduction                                                                                                        | 67 |

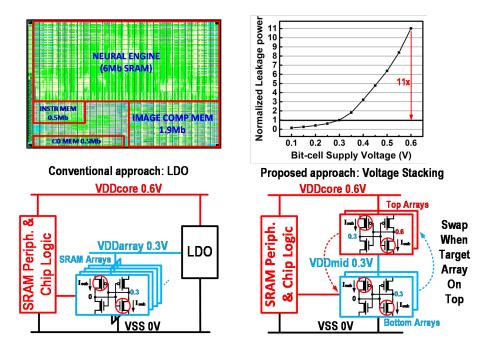

| 5.2       | Ultra Low Leakage SRAM for Low Power ISP                                                                            | 67 |

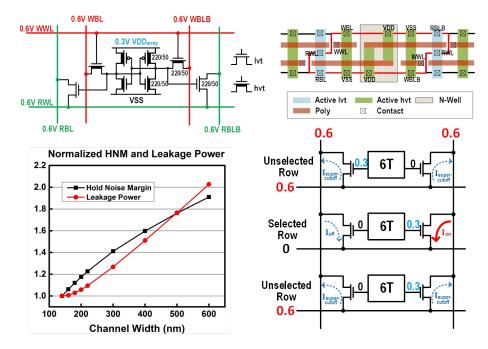

|           | 5.2.1 Differential 8T Bit-cell                                                                                      | 69 |

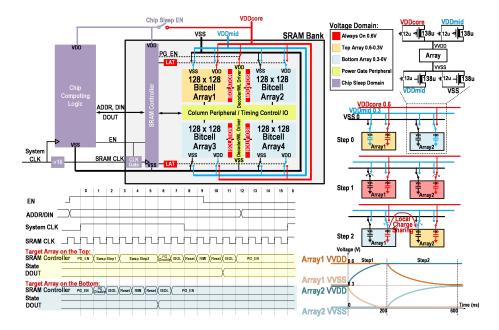

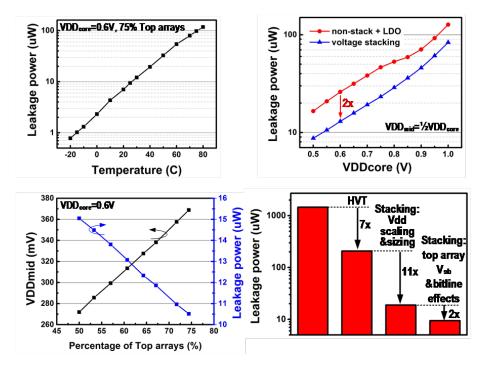

|           | 5.2.2 Stacked SRAM Array                                                                                            | 71 |

| BIBLIOGRA | РНҮ                                                                                                                 | 78 |

# LIST OF FIGURES

# Figure

| 1.1 | Bell's Law on scaling of computing platforms                                                         | 2  |

|-----|------------------------------------------------------------------------------------------------------|----|

| 1.2 | Apple A12 SoC with 8-Core Neural Engine (top-left), Google Edge                                      |    |

|     | TPU ASIC (top-right), KAIST 3D-stacked gaze-activated object-                                        |    |

|     | recognition system (bottom).                                                                         | 3  |

| 1.3 | Processor power scales exponentially (Moore, ISSCC Keynote, 2003)                                    | 4  |

| 1.4 | Delay scaling trend of logic and interconnect without (left) and with                                |    |

|     | repeater (right) $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$             | 5  |

| 1.5 | Energy scaling trend of logic, SRAM, and interconnect                                                | 5  |

| 1.6 | Die photo of 45nm 8-core Enterprise Xeon Processor (left and top-                                    |    |

|     | right) and power breakdown of an 8 core server chip (bottom-right)                                   | 6  |

| 1.7 | Energy and latency breakdown of a conventional FCNN accelerator                                      | 7  |

| 1.8 | Energy costs for various operations in $45$ nm at $0.9$ V $\ldots$ $\ldots$ $\ldots$                 | 7  |

| 1.9 | SRAM takes $93\%$ of total area of the Efficient Inference Engine (EIE)                              |    |

|     | for Deep Compressed Network                                                                          | 8  |

| 2.1 | Differing optimal repeater designs for high and low supply voltages                                  |    |

|     | lead to sub-optimality in wide-range voltage scaled systems. $\ldots$ .                              | 13 |

| 2.2 | RSTR schematic with transistor sizing. Transistors with unlabeled                                    |    |

|     | sizes are minimum width (152nm). Enable signal and header/footer                                     |    |

|     | transistors provide reconfigurability                                                                | 16 |

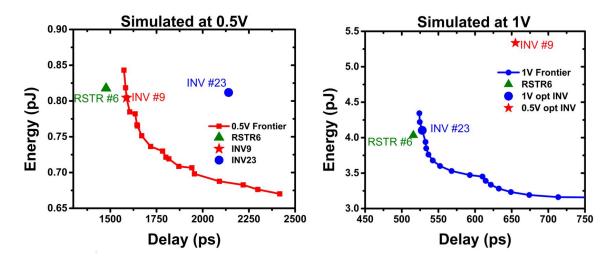

| 2.3 | Simulated energy versus delay curves for RSTR. Optimal inverter                                      |    |

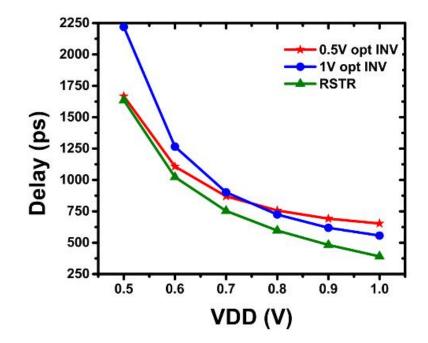

|     | and RSTR designs are chosen from the frontier curves at each voltage.                                | 18 |

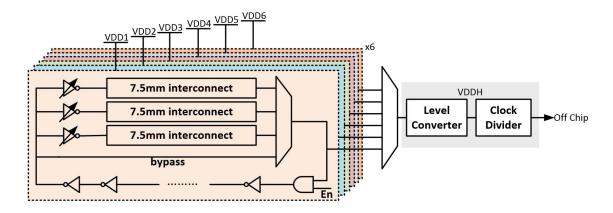

| 2.4 | Reported delays are measured based on the frequency of a ring os-                                    |    |

|     | cillator structure. Each interconnect design is in a separate voltage                                |    |

|     | domain to measure energy. Each interconnect under test has adjacent                                  |    |

|     | neighbors with 140nm spacing $(1 \times \text{min.})$                                                | 19 |

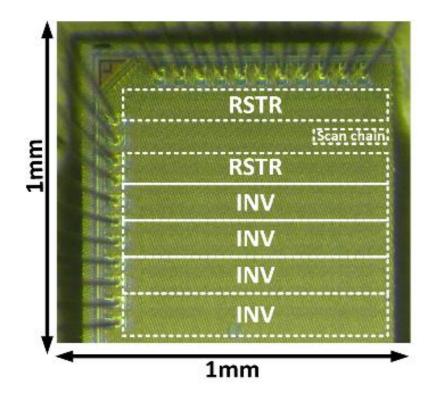

| 2.5 | Die photo of 45nm SOI test chip. The 7.5mm interconnect is folded                                    |    |

|     | ten times. $\ldots$ | 20 |

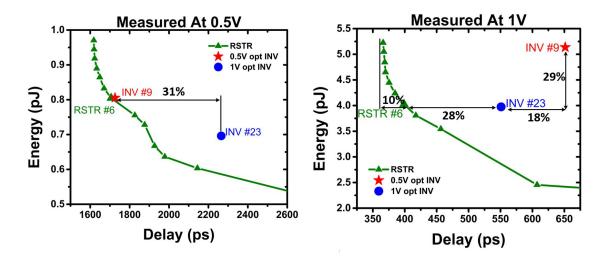

| 2.6 | Measured energy versus delay curves showing RSTR and repeater                                        |    |

|     | performance. Green triangles represents different RSTR configura-                                    |    |

|     | tions (i.e., different number of RSTR enabled)                                                       | 21 |

| 2.7 | Simulated energy versus delay curves for RSTR. Optimal inverter                                      |    |

|     | and RSTR designs are chosen from the frontier curves at each voltage.                                | 22 |

| 2.8            | RSTR speed scales more similarly to digital logic than inverter-based repeated wires.                | 22                                     |

|----------------|------------------------------------------------------------------------------------------------------|----------------------------------------|

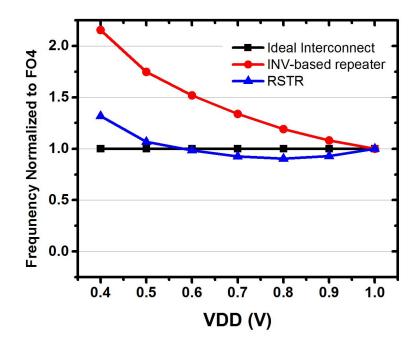

| 3.1            | Bottlenecks in conventional von Neumann architecture: (a) low on-                                    |                                        |

| 0.1            | chip network bandwidth and (b) high data movement energy                                             | 26                                     |

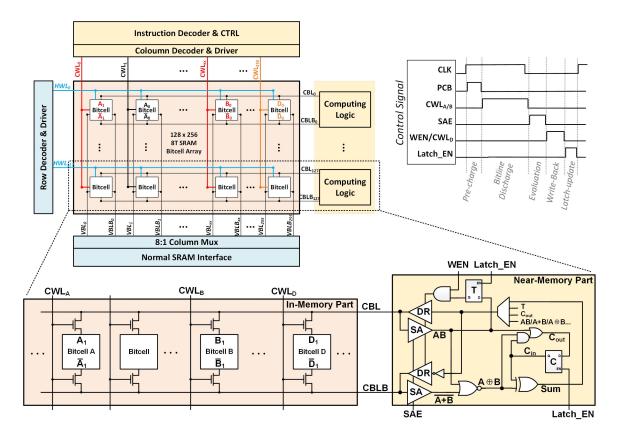

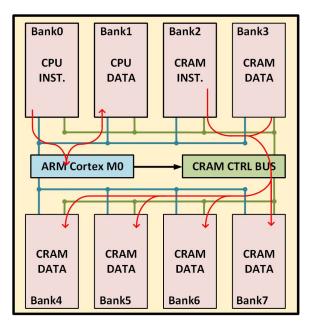

| 3.2            | Proposed CRAM Architecture                                                                           | $\frac{20}{30}$                        |

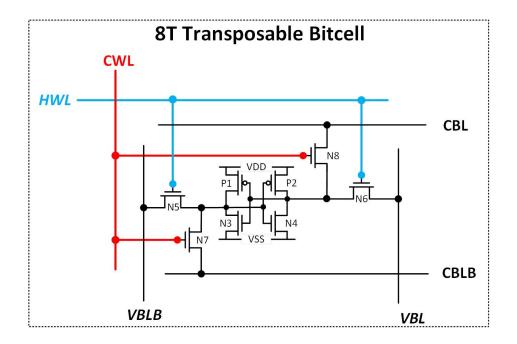

| 3.3            | Schematic and layout of 8T transposable bit cell                                                     | $30 \\ 32$                             |

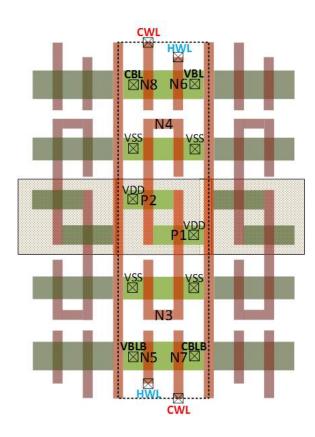

| 3.4            | CRAM Array Architecture (Top-left), computation control signal                                       | 52                                     |

| 0.4            | timing diagram (Top-right), and in/near-memory computing periph-                                     |                                        |

|                | erals (Bottom).                                                                                      | 34                                     |

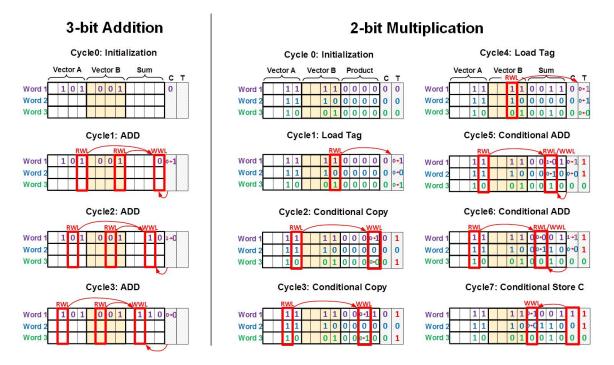

| 3.5            | 3-bit Addition Cycle-by-Cycle Demonstration (left), 2-bit Multipli-                                  | 94                                     |

| 0.0            | cation Cycle-by-Cycle Demonstration (right)                                                          | 37                                     |

| 3.6            | Test chip architecture with sample memory bank configuration                                         | 41                                     |

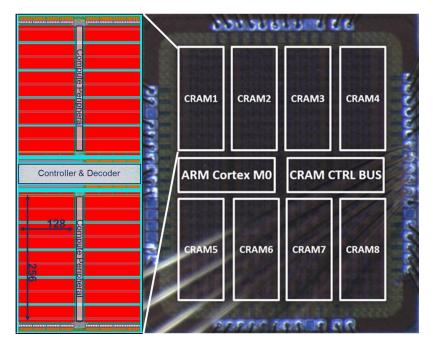

| 3.7            | Layout of CRAM bank and die photo                                                                    | 42                                     |

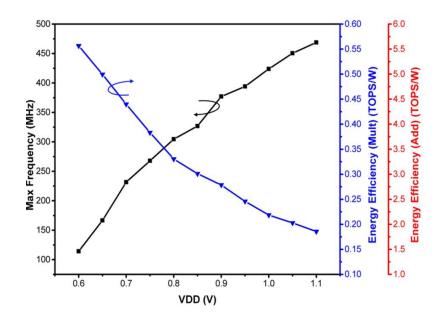

| 3.8            | Frequency and energy efficiency of 8-bit multiplication and addition                                 | 12                                     |

| 0.0            | at different VDD                                                                                     | 43                                     |

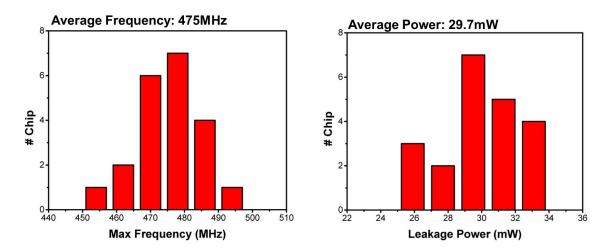

| 3.9            | Maximum frequency and leakage power distribution of 21 dies at 1.1V.                                 | 44                                     |

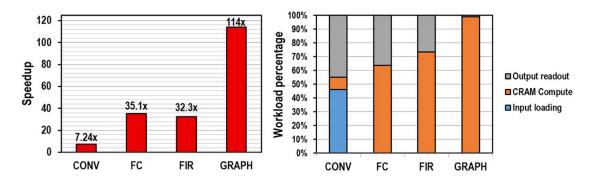

| 3.10           | Performance comparison between CRAM and baseline scenario (top),                                     |                                        |

|                | workload breakdown (bottom)                                                                          | 45                                     |

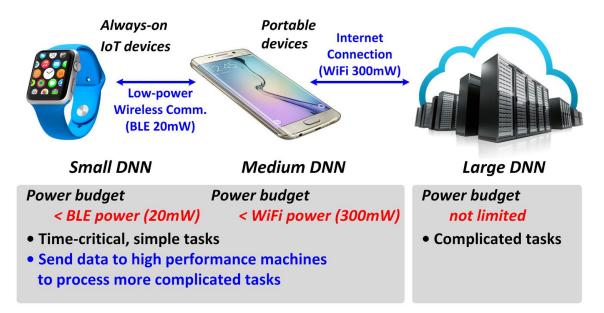

| 4.1            | Hierachical deep neural network                                                                      | 48                                     |

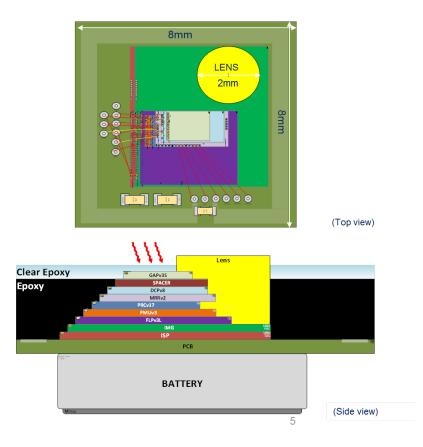

| 4.2            | $1mm^3$ die-stacked sensing platform                                                                 | 49                                     |

| 4.3            | Minimum bit-width in different layers and networks for error toler-                                  |                                        |

|                | ance between $1\%$ and $10\%$ . (I: integer bits; F: fractional bits)                                | 51                                     |

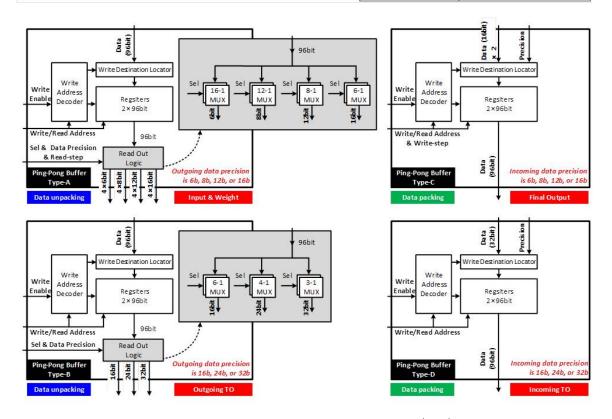

| 4.4            | Available precisions for different data types (top) and programmable                                 |                                        |

|                | ping-pong buffer to unpack and pack data (bottom)                                                    | 52                                     |

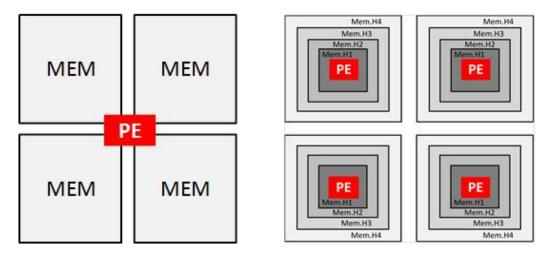

| 4.5            | One big PE and memory (left), four PE surrounded by its own mem-                                     |                                        |

|                | ory sector to exploit spatial locality (right)                                                       | 53                                     |

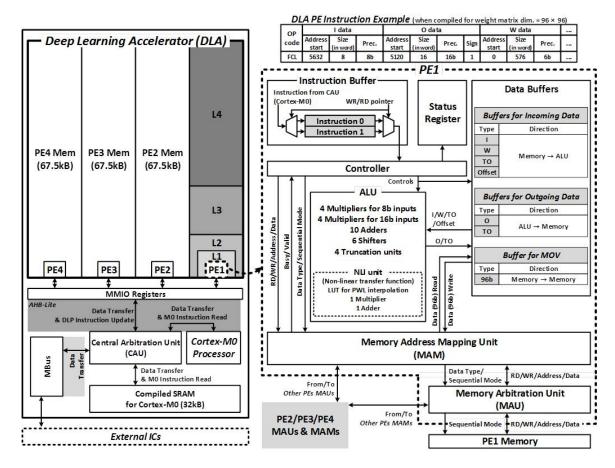

| 4.6            | Top-level diagram of proposed deep learning accelerator $(DLA)$ (left).                              |                                        |

|                | DLA PE instruction example (top). DLA PE block diagram (right).                                      | 54                                     |

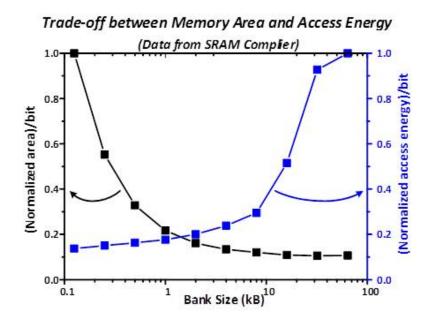

| 4.7            | Trends in SRAM density and access energy with different bank size.                                   | 55                                     |

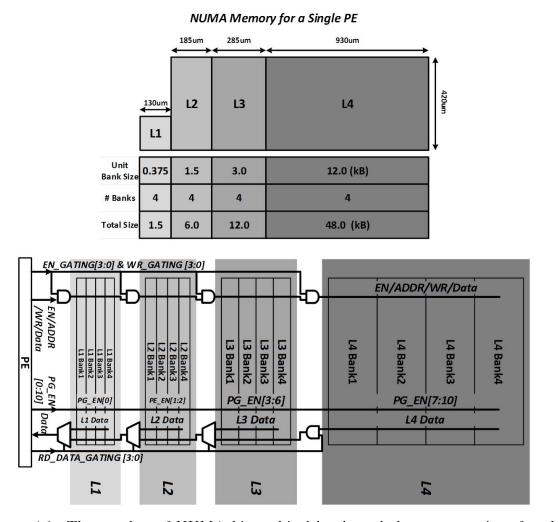

| 4.8            | The number of NUMA hierarchical levels and the memory size of                                        |                                        |

|                | each hierarchy (top), and signal gating circuit to unnecessary signal                                |                                        |

|                | switching (bottom).                                                                                  | 56                                     |

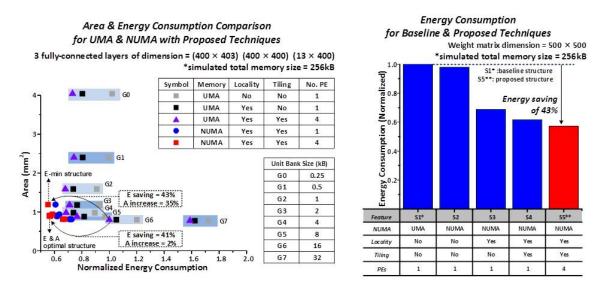

| 4.9            | Area and energy comparison with UMA & NUMA and proposed tech-                                        |                                        |

|                | niques.                                                                                              | 57                                     |

| 4.10           | Compiler 6T push-rule bit-cell (top-left), 8T HVT bit-cell schematic                                 | ~0                                     |

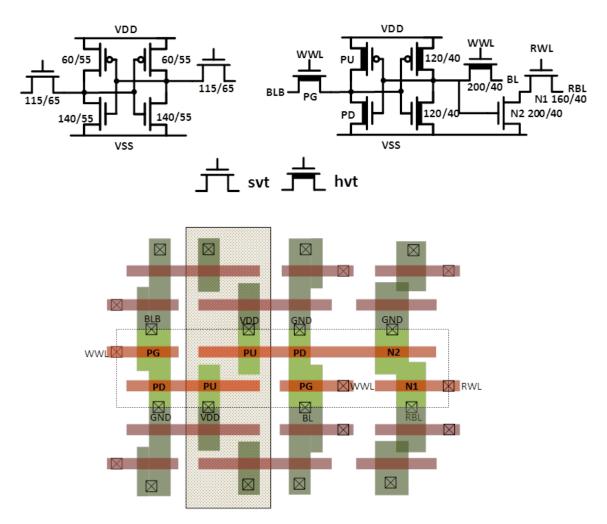

| 4              | (top-right) and layout (bottom)                                                                      | 58                                     |

| 4.11           | Active and leakage power breakdown of a SRAM array.                                                  | 59                                     |

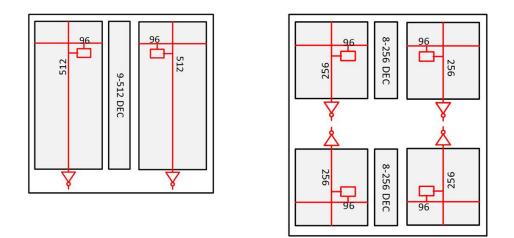

| 4.12           | Long bit-line length of a dual-array bank (left) versus short bit-line                               | co                                     |

| 4 1 9          | length of a qual-array bank (right).                                                                 | 60                                     |

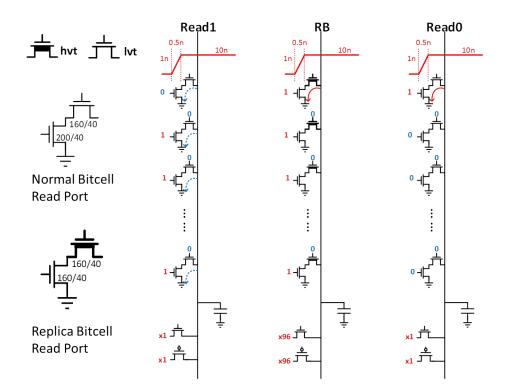

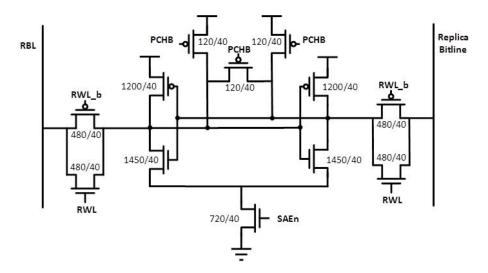

| 4.13           | Replica bit-cell and bit-line to provide the reference voltage for dif-<br>ferential sense amplifier | 60                                     |

| 4.14           | ferential sense amplifier.                                                                           | $\begin{array}{c} 60\\ 61 \end{array}$ |

| $4.14 \\ 4.15$ | Differential Sense Amplifier Schematic                                                               | 01                                     |

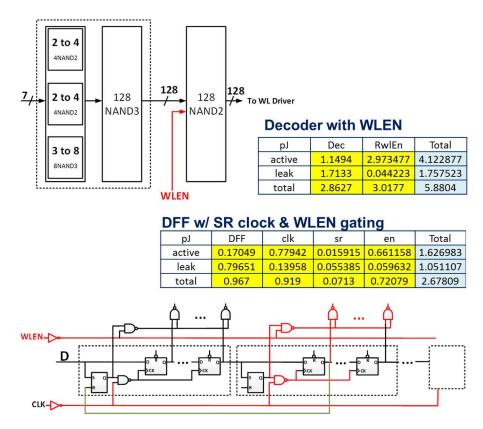

| 4.10           | tial decoder (bottom).                                                                               | 62                                     |

| 4.16           | PMOS power header and NMOS clamping headers.                                                         | 63                                     |

| <b></b>        | THE PERCENCENCE AND THE THE POINT HOUSEDED FOR THE FORMED PERCENCE                                   | 00                                     |

| 4.17 | Diode stack for on-chip reference voltage generation                                                                                    | 63 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------|----|

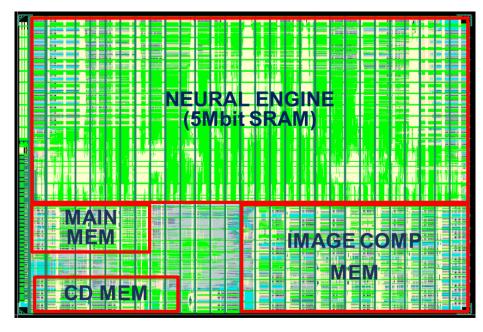

| 4.18 | Die photo of Deep Learning Processor.                                                                                                   | 64 |

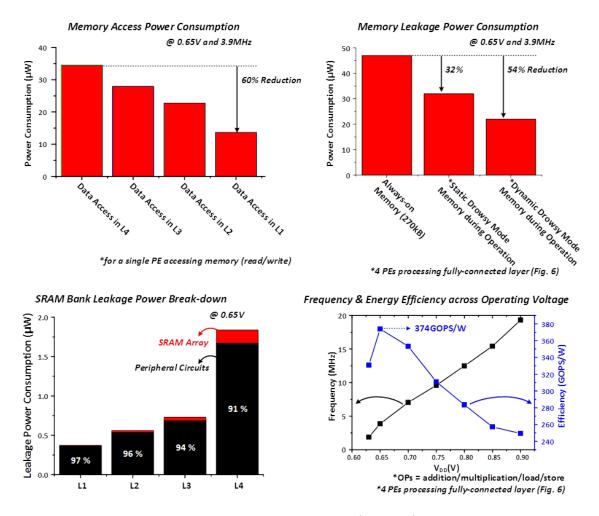

| 4.19 | Memory access power consumption (top left). Memory leakage power                                                                        |    |

|      | comparison (top right). SRAM bank leakage break-down (bottom                                                                            |    |

|      | left). Performance and efficiency across voltage (bottom right)                                                                         | 65 |

| 4.20 | Performance summary for neural networks with a variety of layer                                                                         |    |

|      | specification (top). Comparison table (bottom).                                                                                         | 66 |

| 5.1  | 3D-stacked smart sensor system with low power imager, radio, flash,                                                                     |    |

|      | and ISP                                                                                                                                 | 68 |

| 5.2  | ISP Chip Layout shows that $90\%$ area is memory                                                                                        | 68 |

| 5.3  | Bit-cell hold noise margin at different channel width and supply voltage.                                                               | 70 |

| 5.4  | Schematic of the differential 8T bit-cell                                                                                               | 70 |

| 5.5  | SRAMs on an image processing IoT chip (top-left), leakage power                                                                         |    |

|      | across voltage (top-right), proposed array stacking and swapping                                                                        |    |

|      | $technique (bottom). \dots \dots$ | 72 |

| 5.6  | Bitcell schematic and layout (top), hold noise margin (HNM) and                                                                         |    |

|      | leakage versus bitcell sizing (bottom-left), currents on the bitline dur-                                                               |    |

|      | ing read operation (bottom-right)                                                                                                       | 74 |

| 5.7  | SRAM bank architecture and timing diagram (left), array swapping                                                                        |    |

|      | algorithm (right).                                                                                                                      | 75 |

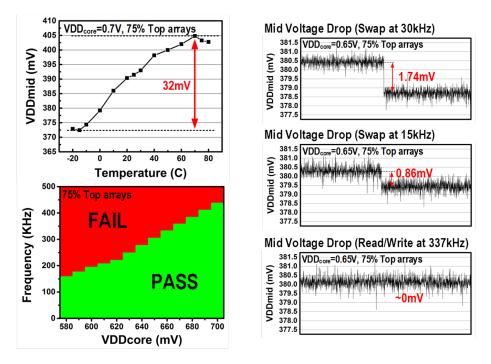

| 5.8  | Leakage across temperature and voltage (top), Mid-rail voltage and                                                                      |    |

|      | leakage with temperature (bottom-left), leakage reduction effects.                                                                      |    |

|      | (bottom-right)                                                                                                                          | 76 |

| 5.9  | Mid-rail variation with temperature (top-left), voltage drop due to                                                                     |    |

|      | various memory activities (right), shmoo plot (bottom-left)                                                                             | 76 |

| 5.10 | Comparison table and design space landscape. $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                        | 77 |

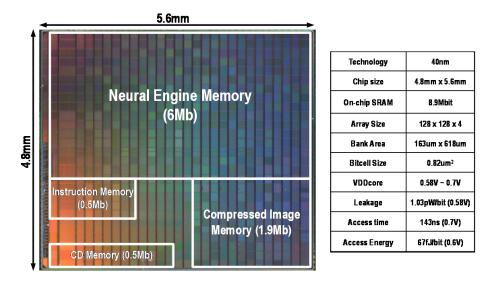

| 5.11 | Die photograph in 40nm CMOS                                                                                                             | 77 |

# LIST OF TABLES

# <u>Table</u>

| 2.1 | Simulated optimal repeater design.                 | 15 |

|-----|----------------------------------------------------|----|

| 3.1 | CRAM Instruction Set                               | 35 |

| 3.2 | Sample of supported operations and cycle counts.   | 36 |

| 3.3 | Pseudo-code: Unsigned Integer Division.            | 39 |

| 3.4 | Pseudo-code: Floating Point Addition.              | 40 |

| 3.5 | Performance of Test Chip at 475MHz.                | 45 |

| 3.6 | Comparison with Previous In-memory Computing Work. | 46 |

## ABSTRACT

Technology scaling has driven the transistor to a smaller area, higher performance and lower power consuming which leads us into the mobile and edge computing era. However, the benefits of technology scaling are diminishing today, as the wire delay and energy scales far behind that of the logics, which makes communication more expensive than computation. Moreover, emerging data centric algorithms like deep learning have a growing demand on SRAM capacity and bandwidth. High access energy and huge leakage of the large on-chip SRAM have become the main limiter of realizing an energy efficient low power smart sensor platform.

This thesis presents several architecture and circuit solutions to enable intelligent mobile systems, including voltage scalable interconnect scheme, Compute-In-Memory (CIM), low power memory system from edge deep learning processor and an ultra-low leakage stacked voltage domain SRAM for low power smart image signal processor (ISP).

Four prototypes are implemented for demonstration and verification. The first two seek the solutions to the slow and high energy global on-chip interconnect: the first prototype proposes a reconfigurable self-timed regenerator based global interconnect scheme to achieve higher performance and energy-efficiency in wide voltage range, while the second one presents a non Von Neumann architecture, a hybrid in-/near-memory Compute SRAM (CRAM), to address the locality issue. The next two works focus on low-power low-leakage SRAM design for Intelligent sensors. The third prototype is a low power memory design for a deep learning processor with 270KB custom SRAM and Non-Uniform Memory Access architecture. The fourth prototype is an ultra-low leakage SRAM for motion-triggered low power smart imager sensor system with voltage domain stacking and a novel array swapping mechanism. The work presented in this dissertation exploits various optimizations in both architecture level (exploiting temporal and spatial locality) and circuit customization to overcome the main challenges in making extremely energy-efficient battery-powered intelligent mobile devices. The impact of the work is significant in the era of Internet-of-Things (IoT) and the age of AI when the mobile computing systems get ubiquitous, intelligent and longer battery life, powered by these proposed solutions.

# CHAPTER I

# Introduction

## 1.1 Technology Scaling and Intelligent Mobile System

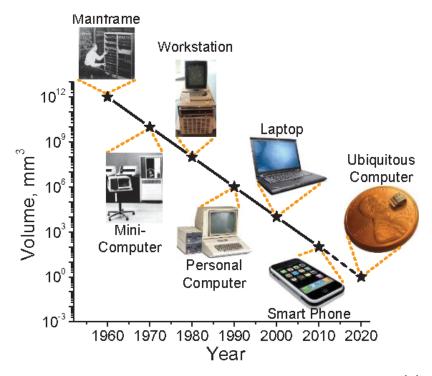

Guided by the Moore's Law [1], the minimum feature size of transistor keeps shrinking and the number of transistors on chip increases exponentially. As predicted by the Bell's Law [2], in the first two decades of the 21st century, we have witnessed a shifted from the PC era to the smart phone and ubiquitous computer era (Figure 1.1). Now we all get used to the convenience of fast wireless communication and excellent computing power brought by these battery-powered mobile systems. Tablet is as powerful as a PC with a touch-screen which allows us to continue the work even on the feet. Smart phone has become a indispensable part of our life, a personal assistant and a second brain. Smart watch and other wearable device monitor our health data and offload many frequently used functions to a smaller screen. Besides the ever growing demand in the handheld devices, many foresee the coming of Internet-of-Things (IoT) driven by the faster 5G communication and the advances in low power techniques. Wireless sensor nodes will get a large-scale deployment in many areas of life. For example, an interocular pressure sensor can be implanted in human eyes to prevent glaucoma [3], and infrastructure monitoring sensor can measure vibrations and material conditions in buildings, bridges and historical monuments to prevent accidents. The number of smart sensors is estimated to increase by 3X and reaches 1

trillion by 2023 [4].

Figure 1.1: Bell's Law on scaling of computing platforms [5].

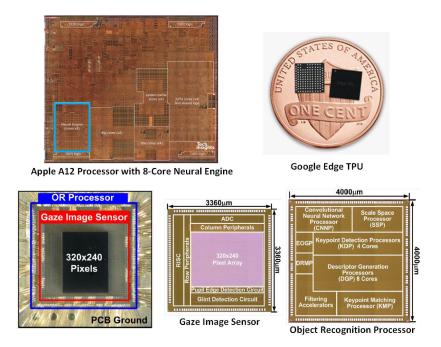

At the same time, benefiting from the high performance computing and "Big Data" driven by the technology scaling, artificial intelligence has embraced the "Second Wave" as described by DARPA's John Launchbury [6]: a shift from Handcrafted Knowledge to Statistical Learning. The recent advance in deep learning has led to many revolutionary improvements in various application domains, including computer vision, speech recognition, and nature language processing. Nowadays, AI has become the most promising and popular applications to both consumers and enterprises. With the explosive growth in demand, AI empowered intelligent system has become the hottest research and development topic (Figure 1.2), from the 8-Core neural engine in Apple's high performance System on Chip (SoC) [7] to the Edge TPU in Google's purpose-built ASIC [8], and the heterogeneous integrations of image sensor and object recognition processor [9].

Figure 1.2: Apple A12 SoC with 8-Core Neural Engine (top-left), Google Edge TPU ASIC (top-right), KAIST 3D-stacked gaze-activated object-recognition system (bot-tom).

## 1.2 Challenges for Intelligent Mobile System

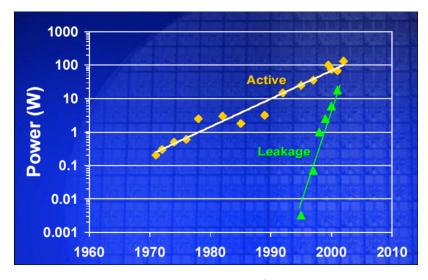

Thanks to technology scaling, more transistors can be integrated into a smaller chip area with increased performance, which helps the development of a more powerful and smaller battery-operated intelligent system. However, even though the minimum feature size of the transistor continues decreasing, today a number of factors have made the benefits of technology scaling diminishing. The first barrier we hit is the "Power Wall". To combat the sub-threshold leakage, the scaling of threshold voltage and supply voltage has been greatly slowed down, but the number of transistors continue to scale exponentially with a constant die size, resulting in an exponential increase in both active and leakage power [10], as shown in Figure 1.3. The small form factor of the mobile devices limits the size of the battery, but many AI applications like keyword spotting and face ID requires part of the system to be always-on. To extend the battery life, ultra-low power and energy-efficient circuits needs to be specially

optimized for the intelligent mobile system.

Figure 1.3: Processor power scales exponentially (Moore, ISSCC Keynote, 2003) [10].

#### 1.2.1 Slow and High Energy Interconnect

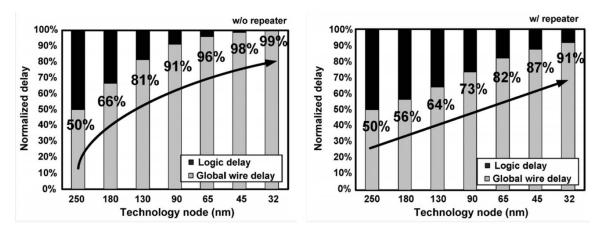

The first challenge comes from the slow and high energy global interconnect. Even though technology scaling improves the driving strength and reduces the parasitic capacitance of the transistor, which generally results in higher performance and lower energy cost, the delay and energy scaling of interconnect fall far behind that of the logic. The reducing minimum width and pitches increase the wire resistance and inter-wire capacitance. Even with the deployment of low-K dielectric materials, unit length resistance and capacitance of wire doesn't scale much with the technology nodes. Therefore, the RC delay dominates the logic delay and becomes the main bottleneck of high-speed circuit, as shown in Figure 1.4. Technology scaling also non-uniformly improves the energy efficiency of computation and communication. As shown in Figure 1.5, the energy of a standard-cell-based double-precision fusedmultiply-and-add (DFMA) is reduced from 50pJ in 40nm to 8.7pJ in 10nm, while the energy of 10mm 256-bit bus only scales from 310pJ to 200pJ. The cost of accessing 256 bits of operands from a distant memory is 6 times greater than the cost of computing in 40nm. This ratio goes up to 23 times in 10nm. Scaling makes locality even more important, since fetching the operands is getting much more expensive than computing it. One solution to this challenge is to find a interconnect scheme that improves both the delay and energy-efficiency of communication, which will be introduced in Chapter II. Another solution is to exploit locality and reduce the amount of data movement per operation as much as possible, which leads to the proposal of a non Von Neumann Architecture, Compute-in-Memory (CIM), introduced in Chapter III.

Figure 1.4: Delay scaling trend of logic and interconnect without (left) and with repeater (right) [11].

|                                                      | 2010                                   | 2017                     |                       |  |

|------------------------------------------------------|----------------------------------------|--------------------------|-----------------------|--|

| Process technology                                   | 40 nm                                  | 10 nm, high<br>frequency | 10 nm,<br>Iow voltage |  |

| $V_{\rm DD}$ (nominal)                               | 0.9 V                                  | 0.75 V                   | 0.65 V                |  |

| Frequency target                                     | 1.6 GHz                                | 2.5 GHz                  | 2 GHz                 |  |

| Double-precision fused-multiply<br>add (DFMA) energy | 50 picojoules (pJ)                     | 8.7 pJ                   | 6.5 pJ                |  |

| 64-bit read from an 8-Kbyte static RAM (SRAM)        | 14 pJ                                  | 2.4 pJ                   | 1.8 pJ                |  |

| Wire energy (per transition)                         | 240 femtojoules (fJ)<br>per bit per mm | 150 fJ/bit/mm            | 115 fJ/bit/mm         |  |

| Wire energy (256 bits, 10 mm)                        | 310 pJ                                 | 200 pJ                   | 150 pJ                |  |

Figure 1.5: Energy scaling trend of logic, SRAM, and interconnect [12].

#### 1.2.2 Large On-Chip Memory

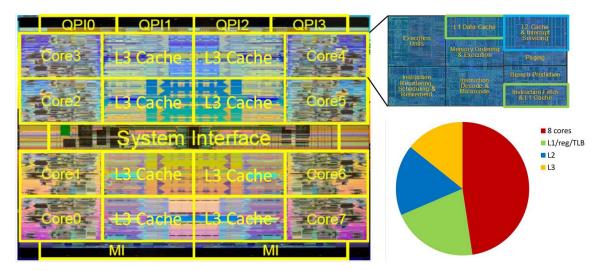

The growing size and power of on-chip memory has become one of the biggest challenges for low power Machine Learning and modern DSP chip design. Static random access memory (SRAM) is an indispensable part of Very-Large-Scale Integration (VLSI) system since it dominates most chip area and power consumption. Figure 1.6 shows that in the 45nm 8-core Enterprise Xeon Processor, more than 60% of the chip area is occupied by L1/2/3 cache [13]. And the power breakdown of a recent 40nm, 8-core server processor shows that over 50% of the active energy is dissipated in the caches and register files. What's more, the leakage power of a modern last-level cache (LLC) can be comparable to the active power of one simple core running in full speed [14].

Figure 1.6: Die photo of 45nm 8-core Enterprise Xeon Processor (left and top-right) and power breakdown of an 8 core server chip (bottom-right) [13, 14].

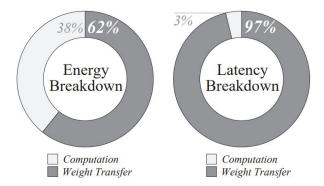

This problem is exacerbated by deep learning algorithm. Since the complex training part of the neural network is usually done off-line in the cloud, hardware accelerator in the mobile SoC is only responsible for real-time inference. Compared to many traditional DSP algorithms, the core arithmetic computation of deep learning inference is very simple, mostly just matrix multiplication and accumulation (MAC) operation on 8-bit precision data. In contrast to the low requirement of computation, deep neural networks requires huge amount of parameters/weights storage. For example, AlexNet, that won the ImageNet competition in 2012, has 60 Million parameters, around 240MB of memory storage [15]. Even a keyword spotting network has 2.1 Million parameters, around 8.4MB of memory [16]. Many studies have shown that most of the energy and latency in the neural network accelerator is consumed by the data transfer. For example, in a conventional fully connected neural network (FCNN) accelerator, 62% of the energy and 97% of the latency is due to weight transfer, as shown in Figure 1.7 [17]. One of the reason is that memory access energy is way higher than arithmetic operation energy. In 45nm, DRAM access energy is 5000 times higher than a 8-bit MAC operation and SRAM access energy of a small 8KB bank is still 40 times higher (Figure 1.8).

Figure 1.7: Energy and latency breakdown of a conventional FCNN accelerator [17].

| Integer |        | FP     |       | Memory |          |

|---------|--------|--------|-------|--------|----------|

| Add     |        | FAdd   |       | Cache  | (64bit)  |

| 8 bit   | 0.03pJ | 16 bit | 0.4pJ | 8KB    | 10pJ     |

| 32 bit  | 0.1pJ  | 32 bit | 0.9pJ | 32KB   | 20pJ     |

| Mult    |        | FMult  |       | 1MB    | 100pJ    |

| 8 bit   | 0.2pJ  | 16 bit | 1.1pJ | DRAM   | 1.3-2.6n |

| 32 bit  | 3.1pJ  | 32 bit | 3.7pJ |        |          |

Figure 1.8: Energy costs for various operations in 45nm at 0.9V [14].

Since edge devices can't afford to have high power off-chip DRAM, people try

to squeeze all the weights into on-chip SRAM by pruning the network and compress the weights. Still a deep learning accelerator requires hundreds of Kilo-bytes of memory. A good example is Standford's Efficient Inference Engine (EIE) for "Deep Compressed" network. The layout photo in Figure 1.9 shows that 162KB SRAM takes 93% of the total area [18].

|               | /lat      |                              |

|---------------|-----------|------------------------------|

| Ptr_Even Arit | hm Ptr_Oo | Total                        |

|               | /lat      | combinational<br>filler cell |

|               | Power<br>(mW) | (%)      | Area $(\mu m^2)$ | (%)      |

|---------------|---------------|----------|------------------|----------|

| Total         | 9.157         |          | 638,024          |          |

| memory        | 5.416         | (59.15%) | 594,786          | (93.22%) |

| clock network | 1.874         | (20.46%) | 866              | (0.14%)  |

| register      | 1.026         | (11.20%) | 9,465            | (1.48%)  |

| combinational | 0.841         | (9.18%)  | 8,946            | (1.40%)  |

| filler cell   |               |          | 23,961           | (3.76%)  |

Figure 1.9: SRAM takes 93% of total area of the Efficient Inference Engine (EIE) for Deep Compressed Network [18].

However, huge amount of on-chip SRAM brings another two challenges: low leakage and high yield. Customized low leakage SRAM become more crucial in neural network based intelligent sensor. Usually a battery-powered sensor node can frequently shut down the supply during sleep mode to extend battery life. However, since neural network requires all the weights to be retained after sleep, SRAM, now the largest portion of the system, has to stay on in standby mode. Due to the extremely low activity ration of a sensor-based system, the leakage power can even be higher than active power. Low voltage operation is one of the most effective ways to reduce both active power, due to its quadratic relationship with supply voltage, and leakage power, due to the Drain-Induced-Barrier-Lowering (DIBL) effect. However, low supply voltage greatly compromises the stability of SRAM operations. What's more, technology scaling makes it even harder to design robust SRAM, since process variation like Random Dopant Fluctuation (RDF) [19] and Line Edge Roughness (LER) [20] gets worse with reduced bitcell size. In Chapter IV and V, we are going to focus on the issues in low power SRAM design for intelligent sensor nodes.

## **1.3** Contribution of This Work

This work contributes some solutions to the interconnect and memory challenges in development of intelligent mobile and edge devices. This proposal presents four works in detail.

Dynamic Voltage and Frequency Scaling (DVFS) is a frequently used low power technique in many mobile systems. The supply voltage may drop to near-threshold when the chip is in low workload and suddenly rise to full VDD when a burst of high workload appears. To make the slow RC delay of global interconnect go linear instead of quadratic with the wire length, repeater is usually inserted with carefully designed number and size based on the wire and repeater delay properties. However, the relative delay between wire and repeater is greatly affected by the voltage causing the optimal number and size of the repeaters at one voltage become sub-optimal at another voltage. In Chapter II, this proposal presents a reconfigurable self-timed regenerator based global interconnect scheme which enables graceful degradation of performance and power in wide range dynamic voltage/frequency scaled systems. A test chip demonstrates up to 40% and 25% better performance scaling than a traditional repeater based interconnect at 1V and 0.5V, respectively, in 45nm SOI CMOS. This work resulted in publications in ASSCC'15[21].

Conventional Von Neumann architecture involves frequently data transfer between memory and computation unit incurring significant energy and latency cost. This problem is amplified by technology scaling and "Data Centric" application like deep learning. In Chapter III, this proposal presents a non Von Neumann architecture —a hybrid in-/near-memory Compute SRAM (CRAM) that uses 8T transposable bit-cell and vector-based, bit-serial arithmetic to accomplish a wide range of operations with flexible bit-width. The proposed design was implemented in a small IoT processor in 28-nm CMOS consisting of a Cortex-M0 CPU and 8 CRAM banks of 16 kB each (128 kB total). The system achieves 475 MHz operation at 1.1 V and, with all CRAMs active, produces 30 GOPS or 1.4 GFLOPS on 32-bit operands. It achieves the energy efficiency of 0.56 TOPS/W for 8-bit multiplication and 5.27 TOPS/W for 8-bit addition at 0.6 V and 114 MHz. This work resulted in publications in ISCA'18[22], ISSCC'19[23], MICRO'19[24] and JSSC'19 (to appear).

In Chapter IV, this proposal presents a Deep Learning Accelerator (DLA) with all weights stored in 270KB custom low power SRAM and non-uniform memory architecture for intelligent edge computing, like keyword spotting and face detection. Implemented in 40nm CMOS, the DLA achieves 288µW power consumption of and 374 GOPS/W energy efficiency with the following techniques: 1) Flexible and compact memory storage for highly truncated fixed-point network weights ranging from 6–32 bit precision via programmable control; 2) All weights stored in 270KB on-chip SRAMs with four processing elements (PEs) located amidst them, minimizing data movement energy; 3) A non-uniform memory architecture provides optimal energydensity trade-off between small, low power memory banks for frequently used data (e.g., input neurons) and large, high density banks for the large amount of infrequently accessed data (e.g., synaptic weights); 4) A 0.6V custom 8T SRAM with both active power reduction techniques like low-swing bit-line and sequential decoder, and leakage reduction techniques like peripheral power-gating, array voltage clamping and bank-by-bank drowsy mode. This work resulted in publications in SiPS'15[25], ISSCC'17[26] and JSPS'18[27].

In Chapter V, this proposal presents an ultra-low leakage SRAM in a smart image signal processor (ISP) for an energy-efficient low-noise CMOS image sensor [28]. The system is designed for motion-triggered IoT applications empowered by change detection and three dedicated neural networks to do human detection, face detection, and face recognition respectively. Including main memory, frame buffer, and memory for neural network weights, the system requires 6.4 Mbit of on chip SRAM in total. With a special designed differential 8T bitcell, we are able to bring down total leakage power of SRAM array to 2uW by retaining the data at 0.3V, and still achieve a good stability. What's more, 0.3V supply is generated directly on chip using a novel stacking array technique instead of a DC-DC converter. The proposed design is taped-out using TSMC 40nm Low Power technology in April 2019.

# CHAPTER II

# Reconfigurable Self-Timed Regenerators for Wide-Range Voltage Scaled Interconnect

# 2.1 Introduction

Near-threshold (NT) operation has been shown to provide a reasonable balance between energy efficiency and performance demands for a wide range of applications [29, 30], particularly in the mobile space. However, even with the recent focus on energy efficiency, high single-thread performance demands still dictate nominal voltage operation at times. Wide-range dynamic voltage and frequency scaling (DVFS) enables operation across the energy/performance design space, but requires underlying circuits to scale across voltage in a robust and predictable manner. Without this, the ability to adapt to dynamic runtime constraints will be limited.

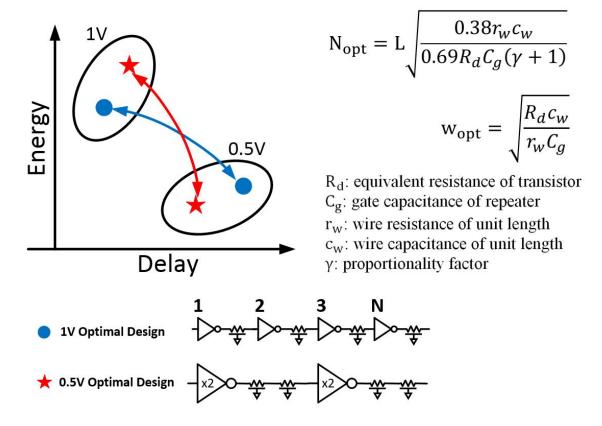

Recent work has shown how to optimize logic [31, 32] and memory [33] across both near-threshold and full voltage regimes. However, little work has addressed interconnect optimization across this wide voltage range. Unlike logic delay, which changes dramatically with supply voltage, interconnect RC delay is insensitive to voltage scaling. This leads to different optimization approaches in comparison to logic and memory. As designs are limited by their critical path, interconnections that are poorly optimized for certain voltage modes cause the entire design to suffer. Optimal repeater insertion for a long interconnect differs significantly at full and near-threshold (NT) voltages. The optimal repeater count N<sub>opt</sub> and size w<sub>opt</sub> are given by the well-known equations [34] in Fig. 2.1. As supply voltage reduces, the effective repeater driver resistance R<sub>d</sub> increases relative to the interconnect resistance  $r_w$ , which remains constant. Wire capacitance  $c_w$  and gate capacitance C<sub>g</sub> also remain constant as voltage scales. Therefore, N<sub>opt</sub>  $\propto 1/\sqrt{R_d(1+\gamma)}$  and w<sub>opt</sub>  $\propto \sqrt{R_d}$ , such that at low VDD fewer, yet larger, repeaters are optimal.

Figure 2.1: Differing optimal repeater designs for high and low supply voltages lead to sub-optimality in wide-range voltage scaled systems.

For the 45nm SOI technology used in this work, nominal voltage is 1V while 0.5V can be considered near threshold, hence we consider this range during optimization. In this technology,  $R_d$  increases by roughly 4× from 1V to 0.5V, therefore an optimized interconnect at 0.5V uses half as many repeaters of twice the size as an in-

terconnect optimized for 1V. Operating repeated interconnects at a voltage they were not targeted for leads to large sub-optimality in energy and delay, shown conceptually in Fig. 2.1.

On-chip interconnect has been studied in-depth by the circuit community with many specialized designs, such as low-swing transceivers, being proposed to save energy and increase throughput. However, within circuit blocks, long wires are repeated with inverters and buffers by commercial place and route tools. While specialized transceivers are desirable for well-defined interconnections spanning long distances, we propose using regenerators for shorter, within-block, wired interconnects in voltage scaled systems when simplicity, low overhead, and ease of integration into a design is valued over absolute performance and energy improvements. This proposed technique does not replace specialized interconnect techniques, but instead is meant to replace repeaters for general purpose use.

# 2.2 Proposed Approach

The poor voltage scalability of repeater-based interconnect currently forces the designer to choose between a design that is optimal at either full or NT voltages, but not both. Furthermore, the interconnect delay does not track the fanout-of-4 (FO4) inverter delay, characteristic of how digital circuits scale with voltage, and hence the interconnect will become performance-limiting for the entire design during either full or NT operation if traditional design methodologies are followed. SPECTRE simulations of industrial wire and device models provided by a 45nm foundry are shown in Table 2.1 with results matching the analytical predictions of Figure 2.1. The baseline repeaters were inverters in this simulation. As expected, NT favored fewer, larger repeaters as compared to nominal voltage.

An obvious approach to overcome the  $N_{opt}$  discrepancy between VDD and NT operation is to selectively disable repeaters along an interconnect. However, this

| VDD (V)    | Optimal<br>Delay (ps/mm) | Optimal Size<br>w <sub>opt</sub> (μm) | Optimal #<br>N <sub>opt</sub> |

|------------|--------------------------|---------------------------------------|-------------------------------|

| 0.5 (NT)   | 1680                     | 12.6                                  | 35                            |

| 1.0 (Nom.) | 740                      | 6.3                                   | 49                            |

\*Interconnect configuration: 10mm length with minimum width and spacing.

Table 2.1: Simulated optimal repeater design.

only shifts the problem from drivability of the repeater to drivability of the bypass devices, amounting to a zero sum game. For instance, if transmission gates are used to bypass repeaters then they suffer similar Rd degradation to that of the repeater, unless driven by a separate nominal voltage supply, which incurs considerable level shifting and power delivery overheads.

We propose using single-ended regenerators based on [35, 36] which, unlike conventional repeaters, are single-ended gates attached along a wire. Instead of discrete input and output pins, regenerators rely on detection circuits to sense partial transitions along the wire, triggering a temporary regenerative drive of the wire until it has fully transitioned to a new value. Regenerators have the unique property of not partitioning a long interconnect into separate wire segments. If a regenerator is enabled, it acts as a repeater passively monitoring the interconnect and then actively driving it to transition. Disabling the regenerator in effect extends the repeated distance, as the inactive regenerator does not change the characteristics of the wire other than added parasitic capacitance. Using regenerators addresses the scalability of the number of inserted repeaters, but to address repeater size we also add regenerators in parallel and selectively enable them.

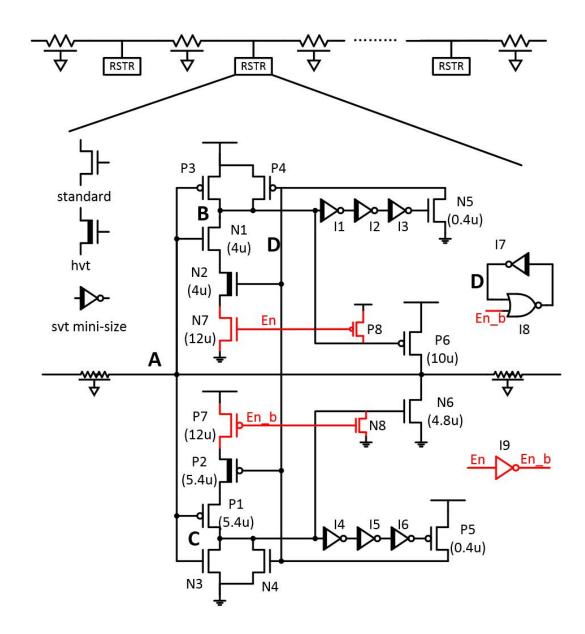

Fig. 2.2 shows a circuit schematic for our proposed regenerator, named Reconfigurable Self-Timed Regenerator (RSTR), which is based on [35] but with extensions for reconfiguration. The new reconfigurable components are highlighted in red.

Figure 2.2: RSTR schematic with transistor sizing. Transistors with unlabeled sizes are minimum width (152nm). Enable signal and header/footer transistors provide reconfigurability.

The circuit operates by early detection of a transition along the interconnect wire at point A. The transition is then aided by turning on either the PMOS or NMOS driving transistor, P6 and N6, to supply additional current in driving the wire. To avoid global control signals a self-timed delay chain (I1-3 and I4-6) turns off the driving transistors and awaits the next transition. The regenerator is enabled through the En signal that, when asserted, activates N1-2 and P3-4 forming a NAND structure to sense the low-to-high transition and turn on driver P6, while remaining insensitive to high-to-low transitions. Similarly, high-to-low transitions are detected by a NOR (P1-2, N3-4) that controls N6. To allow for this hysteresis, I7 and I8 form a latch to store the previous value on the wire. Lastly, N7 and P7 in the NAND/NOR detection circuits disable the sensing of transitions while P8 and N8 disable the output drivers.

Because of the internal delay chain, RSTR controls its own pulse width, namely the duration of the pull-up/pull-down time, hence careful delay selection is needed to ensure that the wire transitions substantially before the RSTR resets itself across a range of Vdd. Also the delay should not be so long that it interferes with the next signal transition. The delay chain consists of three SVT minimum-sized stacked inverters; simulation across design corners and process variation ensures all these requirements are met.

Fig. 2.3 shows the energy-delay curve for repeaters and RSTR at 0.5V and 1V, simulated with the industrial 45nm SOI CMOS models. The driven interconnect is a 7.5mm intermediate (2× thickness) wire with 140nm spacing (1× min.) and 280nm width (2× min.), chosen to represent a reasonably long within-block interconnect. At both voltages, the size and number of repeaters are swept to find the optimal energy/delay points, marked as the Pareto frontier curve in Fig. 2.3. On the 1V frontier, we chose "INV #23" to represent the 1V-optimized design containing  $N_{opt}=23$  inverter repeaters, each with size  $w_{opt} = 12\mu$ mPMOS and  $6\mu$ mNMOS. On the 0.5V frontier, design "INV #9" is selected with  $N_{opt}=9$  inverters ( $w_{opt} = 24\mu$ mPMOS,

Figure 2.3: Simulated energy versus delay curves for RSTR. Optimal inverter and RSTR designs are chosen from the frontier curves at each voltage.

$12\mu$ mNMOS). All repeaters are placed evenly along the interconnect.

The RSTR design space is similarly swept and we observed that some configurations on its 1V frontier also appeared on the 0.5V frontier. One such design "RSTR #6" uses  $N_{opt}=6$  RSTRs which are evenly distributed along the 7.5mm wire with device sizes given in Fig. 2.2. This RSTR design is labeled on both plots of Fig. 2.3 for comparison. Unlike traditional repeated interconnects, RSTR can achieve better performance and energy characteristics over a wide voltage range, such as 0.5V to 1V as demonstrated in this simulation.

Despite the simplicity of the proposed RSTR scheme (the regenerator topology adds only small overhead beyond the design in [35]) it provides the following important benefits over traditional repeated interconnects:

1) RSTR remains optimal (in energy/delay space) across the full VDD range.

2) RSTR reconfigurability provides a new knob for adaptive designs to compensate for variability at NT operation. This is achieved by selectively turning on/off RSTRs along a wire to trade performance for power (e.g., 24% performance loss for 40% lower energy).

3) RSTR is faster than an optimal repeater design at both full and NT supply

while maintaining energy efficiency.

4) RSTR does not partition the wire, allowing for bi-directionality.

# 2.3 Measurements and Results

Figure 2.4: Reported delays are measured based on the frequency of a ring oscillator structure. Each interconnect design is in a separate voltage domain to measure energy. Each interconnect under test has adjacent neighbors with 140nm spacing  $(1 \times \text{min.})$ .

A test chip was fabricated in 45nm SOI CMOS to evaluate the efficacy of RTSRs in silicon and validate simulation predictions. A total of four inverter repeater (INV) designs and two proposed RSTR designs were included on the test chip, which measured  $1 \times 1$ mm (Fig. 2.4). Fig. 2.5 shows the test harness; the interconnect matches the structure simulated above and is implemented as a bypassable delay chain within a ring oscillator. After level conversion and a clock divider, frequency is measured off chip both with and without interconnect to assess delay.

Fig. 2.6 shows measured results confirming the relatively poor voltage scalability of repeater-based designs. A 1V optimal design is 31% slower than the 0.5V optimal design when operating at 0.5V. Conversely, a 0.5V optimal design is 18% slower with 29% higher energy than a 1V optimal design when both operate at 1V. In contrast the RSTR design shows good voltage scalability. Specifically at 1V it is 28% faster than the 1V optimal INV design while consuming 5% less energy. At 0.5V, the "RSTR

Figure 2.5: Die photo of 45nm SOI test chip. The 7.5mm interconnect is folded ten times.

#6" energy and delay essentially match the 0.5V optimal INV design. In addition to being superior to INV-based designs, recall that "RSTR #6" appears along the Pareto optimal frontier at both supply voltages. This indicates that excellent performance can be obtained across voltage scaling, relative to other RSTR designs.

Green triangles in Fig. 2.6 represent RSTR energy-delay points with varying number of RSTR enabled, representing dynamic reconfiguration options depending on real-time energy-performance priorities. This allows the RSTR design to also operate at lower energy with faster delay than "INV #23" at 0.5V, if desired. Also, if interconnect was performance limiting for the design at full VDD (1V), turning on six additional RSTR along the wire (reconfiguring RSTR #6 into RSTR #12) offers 10% faster performance, potentially rebalancing the overall design. In NT mode (0.5V), regenerators can then be turned off to achieve a minimal energy of 0.6pJ in this example.

Figure 2.6: Measured energy versus delay curves showing RSTR and repeater performance. Green triangles represents different RSTR configurations (i.e., different number of RSTR enabled).

Fig. 2.7 shows measured delay scaling of repeater and RSTR designs across VDD, indicating the sub-optimality of using a single inverter-based repeater design in wide-range voltage scaling. RSTR is able to achieve better performance across the entire 0.5V to 1V range. Fig. 2.8 plots this measured data normalized to inverter FO4 delay across a range of voltages. Ideally an interconnect scales identical to circuit delay, which would be shown as a fixed line at 1.0 of FO4 in Fig. 2.8. Again, this supports the more graceful scaling of delay offered by an RSTR design over a conventional repeater-based approach.

## 2.4 Summary

Today's emerging mobile applications require high energy efficiency, which is often provided by scaling supply voltage across a wide range according to real-time workload variation. We present a reconfigurable, self-timed, regenerator-based interconnect scheme that remains optimal in terms of energy-delay efficiency at both full and nearthreshold voltages. RSTR interconnect delay tracks FO4 logic delay more closely than repeated wires. In addition, RSTR offers higher speed and better energy efficiency

Figure 2.7: Simulated energy versus delay curves for RSTR. Optimal inverter and RSTR designs are chosen from the frontier curves at each voltage.

Figure 2.8: RSTR speed scales more similarly to digital logic than inverter-based repeated wires.

overall compared to traditional repeater approaches.

## CHAPTER III

# A 28-nm Compute SRAM with Bit-Serial Arithmetic Operations for Programmable In-Memory Vector Acceleration

# 3.1 Introduction

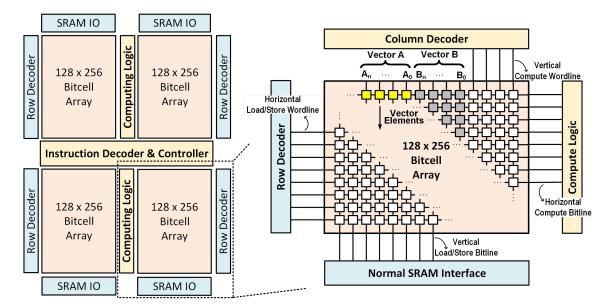

In the conventional von Neumann architecture, a clear gap lies between data storage and processing: memories store data, while processors compute on data. Thanks to Moore's Law, in the past few decades, the computing power of integrated circuits has rapidly scaled as logic gates became faster and faster and the number of processing cores increased steadily until we hit the "Memory Wall" [37]. But the on-chip global interconnects latency and energy cannot keep up with the scaling of logic gates. Thus, the computation throughput and energy have become dominated by the memory bandwidth and data movement energy. As shown in Figure 3.1a, the bandwidth at the I/Os of all SRAM banks inside a big memory macro such as a 20 MB L3 cache is over a hundred TB per second [38, 39], which is comparable to the theoretical maximum computation bandwidth of the state-of-the-art systolic processing array [40]. Hence, the bottleneck is the local data network inside the memory macro and the global data bus on chip. Furthermore, a large fraction of energy consumption today is spent on moving data back and forth between memory and compute units [14]. As shown in Figure 3.1b, it only takes sub-pico joules of energy to do a 32-bit addition while tens of pico joules are spent on retrieving data from far away memory banks.

Previously, people tried to overcome the "Memory Wall" by introducing more memory hierarchies, in an effort to bring the data closer to the computation. However, the memory problem is further exacerbated by the advent of data-intensive applications such as neural networks [41, 42], computer vision [43] and steam processing [44]. The need to shift from computation-centric to data-centric architecture has led to extensive research focused on the area of in-/near-memory computing, which moves computation to where the data is located. Recently, we have seen many studies that try to bring computation to different levels of memory hierarchies, including DRAM [45] and non-volatile memories like STT-MRAM [46], ReRAM [47], and Flash [48]. This paper focuses on designing computational SRAM banks. Most SRAM in today's chips is located in the caches of CPUs or GPUs. These large CPU and GPU SRAMs present an opportunity for extensive in-memory computing and have, to date, remained largely untapped.

There are two main types of emerging in-memory computing architectures for SRAM. The first is analog in-memory computing. In this case, one of the operands is pre-stored in the SRAM array. A multi-bit operand will have its bits spread into different word-lines, while the other operand is usually modulated into the analog voltage level in the word-lines [49] or pulse width of the word-line enable signal [50, 51]. The multiplication result of the two operands is then represented by the various discharge currents of the bit cell. Often multiple word-lines are activated simultaneously, and the multiplication results are accumulated on the bit-line as the total bit-line discharge current is the sum of the each individual bit-cell current. The final multiplyaccumulate result is naturally represented by the analog bit-line voltage, which can be sensed by an analog-to-digital converter. This approach can achieve very high energy

Figure 3.1: Bottlenecks in conventional von Neumann architecture: (a) low on-chip network bandwidth and (b) high data movement energy.

efficiency and performance, but it requires expensive analog-to-digital and digital-toanalog conversions at the array boundary. Also, the computation accuracy is highly susceptible to noise and PVT variations, and therefore its functionality is limited to low precision addition or multiplication. The second type is digital in-memory computing, which usually activates two word-lines with full-rail voltage in the same cycle and employs a sense amplifier on each bit-line to give a binary result [52, 53, 54, 55]. This type of approach offers better accuracy and robustness than analog approaches and can achieve a moderately high energy efficiency and performance. However, its functionality is limited to only bit-wise logic operation or low precision arithmetic in Binary Neural Networks.

Although traditional computing architectures such as CPU and GPU show limitations in energy efficiency and memory bandwidth, their appeal lies in their general functionality. They can perform a wide range of operations from bit-wise logic operation to Integer/Floating-Point Arithmetic. Not only are these computations accurate and robust since the designs are fully digital, but they are highly flexible and can implement many algorithms and neural network types and sizes. In this respect, both current in-memory approaches suffer from the same major limitation: they accelerate only one type of algorithm and are inherently restricted to a very specific application domain due to their limited bit-width precision and non-programmable architecture. On the other hand, software algorithms continue to evolve rapidly, especially in novel application domains such as neural networks, vision and graph processing, which makes rigid accelerators of limited use.

To address these limitations, we present a general purpose hybrid in-/near-memory Compute SRAM (CRAM) [56] that combines the efficiency of in-memory computation with the flexibility and programmability necessary for evolving software algorithms. It does part of the logic operations in SRAM bit-lines and most arithmetic operations in pitch-matched, near-memory peripherals at the end the each bit-line. It can accommodate a wide range of bit-widths, from single to 32 or 64 bits, and operation types, including integer and floating point addition, multiplication and division, with a small amount of hardware overhead. Its high-throughput computation is accurate and robust, and the design offers good energy efficiency. CRAM tries to repurpose the large existing on-chip memory storage by augmenting a conventional SRAM bank in a cache with vector-based, bit-serial in-memory/near-memory arithmetic. To maintain compatibility with current CPU/GPU architecture, CRAM writes/reads operands conventionally with horizontal word-lines and vertical bit-lines, which is made possible by the 8T transposable bit cell.

The remainder of this paper is organized as follows. Section II generally introduces the bit-serial operation and the architecture of the proposed Computational SRAM. Section III describes the 8T transposable bit cell and the computing peripheral in detail. Section IV presents the algorithm of multi-bit arithmetic operations. Section V discusses the measurement results of the proposed design, and finally, the conclusions are presented in Section VI.

## 3.2 Overview of Bit-serial Arithmetic and CRAM Architecture

### 3.2.1 Bit-serial Arithmetic

Several previous digital in-memory computing works [53, 54, 55] supported some simple bit-parallel operations such as bit-wise logic and copy. However, these are carry-less operations that do not require interaction between bit-lines. In order to make in-memory computing as general purpose as the ALU in a CPU, support is needed for more complex arithmetic operations such as addition, multiplication, and even floating point operation. The critical challenge in supporting these complex computing primitives is facilitating carry propagation between bit-lines. We propose bit-serial implementation with a transposable bit cell to address this challenge.

Since the 1980s, bit-serial computing architectures have been widely used for digital signal processing because it can usually provide the most area-efficient design in the presence of a massive bit-level parallelism [57, 58]. The key idea is to process one bit of multiple data elements every cycle. This model is particularly useful in scenarios where the same operation is applied to the same bit of all data elements in a vector, like in SIMD architectures. For example, in order to compute the elementwise sum of two arrays with 512 32-bit elements, a conventional processor would take at least 512 cycles to get the operands element-by-element from the SRAM and then perform the operation. A bit-serial processor, on the other hand, would complete the operation in 32 steps as it processes the arrays bit-slice by bit-slice instead of elementby-element. Note that a bit-slice is composed of bits from the same bit position but corresponding to different elements of the array. Since the number of elements in arrays is typically much greater than the bit-precision for each element stored in them, bit-serial computing architectures can provide much higher throughput than bit-parallel arithmetic. Note also that bit-serial operation allows for flexible operand bit-width, which can be especially advantageous in DNN hardware designs where the required bit width can vary from layer to layer [59, 60].

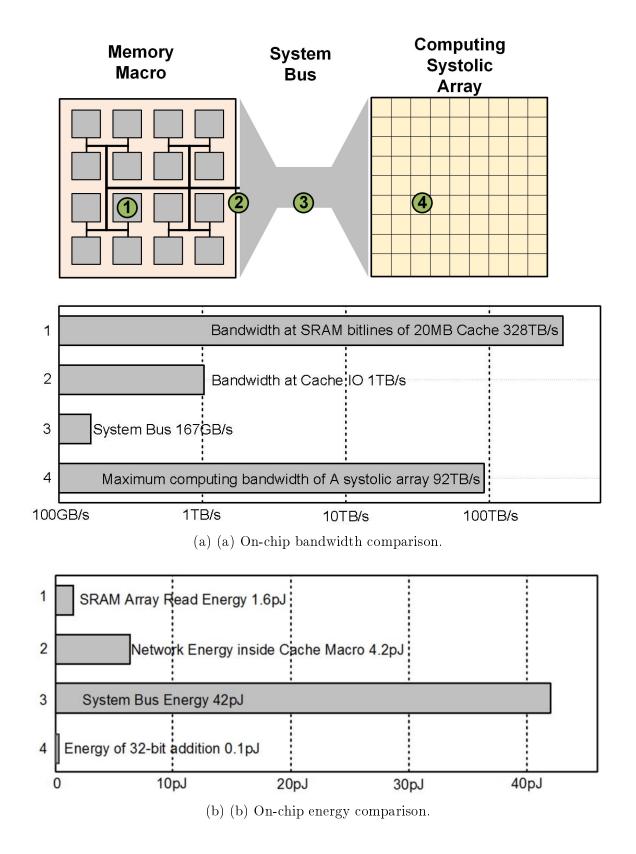

### 3.2.2 CRAM Architecture

Figure 3.2 shows the overall architecture of one 16-KB CRAM bank. Each CRAM bank consists of 4 128x256 arrays that load or store data conventionally using horizontal word-lines and vertical bit-lines. The normal SRAM peripherals, such as a row decoder, column mux, and sense amp, are shown in blue. In this diagram, the array has been preloaded with two vectors of data, vectors A and B. Data elements from the same vector are placed into different rows and aligned by the column, while the corresponding elements from the two vectors that are going to be operated must be

Figure 3.2: Proposed CRAM Architecture.

aligned on the same word-line. To perform bit-serial operation, we need to activate the same bit position from two vectors. Therefore, column decoder and pitch-matched compute logic are added so that in-memory computing can be performed using vertical compute word-lines and horizontal compute bit-lines. For example, in the first cycle, we simultaneously activate the vertical word-lines of the Least Significant Bits (LSB) from the two vectors. Then the computation is performed in both horizontal bit-lines and the compute logics at the end of the bit-lines. Near the end of the cycle, the result is then stored back in the array at some destination bit location selected by a third vertical word-line. In the next cycle, other bits of each operand are activated to continue the computation. Again, the result is stored back at the designated position at the end of the cycle. By repeating single bit operations cycle-by-cycle, we can perform any complex multi-bit arithmetic with carry-propagation. For example, a 32-bit adder will take 32 cycles to finish. Note that although bit-serial computation is expected to have high latency per operation, it gains significantly in terms of throughput. A 16-KB SRAM bank contains 256 vertical compute bit-lines in total, and a 35-MB Last Level Cache (LLC) in the Haswell server processor can accommodate 2240 such 16-KB banks [2], which means a total of 573,440 bit-lines can do computations in parallel. In this case, maximum throughput would be equivalent to 17,920 32-bit adders or 71,680 8-bit adders. The computing logic is shared between the arrays on the left and right and takes 4.5% of the CRAM bank area. The instruction decoder and controller in the middle of the bank, shared by all 4 arrays, take 32-bit instruction and generate control signals for the computing logic. They occupy 5.2% of the bank area. The details of the controller instructions will be presented in Section III.

## 3.3 CRAM Circuitry

#### 3.3.1 8T transposable bit cell

Many previous in-memory computing works [51, 55, 61] choose to store each word unconventionally by spreading bits into different rows of the same vertical bit-line. This approach makes the computation much easier and can directly use 6T bit cell for minimizing area. But the normal SRAM read/write operation gets much more complicated and becomes incompatible with current computer architecture since in one cycle, we can't read out a complete word but only the same bit position from multiple different words. Therefore, we propose to use an 8T transposable bit cell. Figure 3.3 shows the schematic and the layout of the bit cell [62]. Four of the transistors form the cross-coupled inverter pair to hold the data, and there are two pairs of access transistors for read/write. The structure is similar to the conventional 8T dual port SRAM bit cell except that it provides bidirectional access: the bit cell can be read or written from either vertical bit-line or horizontal bit-line. Therefore, CRAM can operate directly on the stored operands in memory by enabling the same bit position from two vector elements with vertical word-lines and perform the computation on horizontal bit-lines. Furthermore, it can also directly read a complete word by en-

Figure 3.3: Schematic and layout of 8T transposable bit cell.

abling the horizontal word-line and sense the result from vertical bit-lines. With the logic rule transistor in 28-nm CMOS, the bit cell size is 0.405 um by 1.93 um, which is  $638F^2$  when normalized to technology node feature size (F).

## 3.3.2 Computing Peripherals

Figure 3.4 gives a detailed view of one row in the bit cell array. Logic operations are performed on the bit-line (in-memory), while small additional in-row logic (nearmemory) enables carry-propagation between successive bit-serial calculations. An example of 1-bit addition will be used to illustrate the CRAM single cycle operation and computing peripherals. Here we add the second bit of vector A  $(A_1)$  and vector B  $(B_1)$  with carry-in  $(C_{in})$  from the previous cycle and store the sum back to the second bit of vector D  $(D_1)$  and latch the carry-out  $(C_{out})$  for the next cycle. First, the CRAM instruction decoder receives the ADD instruction with the 3 column addresses for bits  $A_1$ ,  $B_1$  and  $D_1$ . After pre-charging the compute bit-line (CBL) and compute bit-line bar (CBLB), we activate the vertical compute word-lines (CWL) of  $A_1$  and  $B_1$  simultaneously to generate 'A AND B' on CBL and 'A AND  $\overline{B}$ ' on CBLB. We use a separate voltage rail for the driver of  $CWL_{A/B}$ , so that we can lower the word-line voltage to prevent the read disturbance issue when necessary. This is the in-memory part of the computation. Next, after the dual sense amps are enabled, the in-memory logic operation results propagate into the near-memory region located at the end of each CBL. The NOR gate generates 'A XOR B,' which combined with  $\mathrm{C}_{\mathrm{in}}$  from the C latch produces Sum and  $C_{out}$ . Then  $CWLD_D$  is activated, and the sum is written back to destination bit  $D_1$ . Finally, near the end of the cycle, Cout updates the C latch, which provides C<sub>in</sub> for the next cycle.

When we activate the CWL, all 256 CBLs in the 16-KB CRAM banks are performing the same single bit instruction in a SIMD fashion. In order to support complex multibit arithmetic, CRAM has to be able to execute instructions only on certain

Figure 3.4: CRAM Array Architecture (Top-left), computation control signal timing diagram (Top-right), and in/near-memory computing peripherals (Bottom).

selected CBLs; and therefore, we add the Tag (T) latch to enable conditional operation. Tag latch is used as the enable signal of the write-back driver. Therefore, for the CBL whose Tag latch stores 0, the computation result will not be written-back to the memory, as if the instruction is not executed at all. The content of the Tag latch can be loaded from or written into the memory array. In addition to the logics introduced before, we also add a multiplexer to allow for the write-back of signals besides the Sum, such as A AND B, A OR B,  $C_{out}$ , or Tag.

With the computing peripherals shown in Figure 3.4, the CRAM controller can support up to 16 single-cycle instructions, shown in Table 3.1. Besides the logic and add operation, it includes copy, inversion, load/store of carry or tag, comparison, and set/reset carry. The CRAM controller takes 32-bit instruction. Four bits ([31:28]) are used for various enable signals for different features. Four bits ([27:24]) are used for the opcode for the 16 instructions. Eight bits are used for the address since every memory array contains 256 compute word-lines. Bits [23:16], [15:8], and [7:0] represent the address of operand A, the address of operand B and the destination location D, respectively. Using these single-cycle micro instructions, we can build complex multi-cycle macro instructions, including search, multiplication, division, and floating point arithmetic.

| bit <u>31 28 27 2</u> 4 |                   |        | 4 23 16 15   |              |                       | 8                                                                    | 7 0                    |  |  |

|-------------------------|-------------------|--------|--------------|--------------|-----------------------|----------------------------------------------------------------------|------------------------|--|--|

| Instruction             | enable            | opcode |              | RA           |                       | RB                                                                   | RD                     |  |  |

| Single-Cycle Primitives |                   |        |              |              |                       |                                                                      |                        |  |  |

| Туре                    | Opc               | ode    | RA           | RB           | RD                    | C                                                                    | omments                |  |  |

| Logic                   | AND/OI<br>NAND/NO |        | √            | ~            | ~                     | Perform logic operation on RA and RB and store the result back to RD |                        |  |  |

| Arithmetic              | AD                | D      | $\checkmark$ | $\checkmark$ | $\checkmark$          | Add RA and RB, write back to RD                                      |                        |  |  |

| cl.:c                   | Co                | ру     | $\checkmark$ |              | <ul> <li>✓</li> </ul> | Copy RA to RD                                                        |                        |  |  |

| Shift                   | IN                | V      | ~            |              | $\checkmark$          | INV RA and write back to RD                                          |                        |  |  |

| Comparison              | Equ               | ıal    | $\checkmark$ |              |                       | Write "RA == A                                                       | ddrRB[0]" to Tag latch |  |  |

|                         | LOA               | D T    | $\checkmark$ |              |                       | Load RA to Tag                                                       | latch                  |  |  |

|                         | STOR              | E C/T  |              |              | $\checkmark$          | Write Carry/Tag latch back to RD                                     |                        |  |  |

| Utility                 | Set               | C      |              |              |                       | Set Carry Latch to 1                                                 |                        |  |  |

|                         | Rese              | et C   |              |              |                       | Reset Carry Late                                                     | h to 0                 |  |  |

|                         | C to              | ъT     |              |              |                       | Write Carry Late                                                     | th to Tag Latch        |  |  |

Table 3.1: CRAM Instruction Set.

## 3.4 Multi-cycle Arithmetic

Users can program CRAM to achieve many complex computations. Table 3.2 shows a sample list of the supported multi-cycle operations and the number of singlecycle instructions each takes. Next, we will introduce some commonly used arithmetic operations and the way to program them in CRAM.

| Sample Multi-Cycle Operations |              |                 |  |  |  |

|-------------------------------|--------------|-----------------|--|--|--|

| Туре                          | Operation    | # Cycles        |  |  |  |

|                               | AND          | N               |  |  |  |

|                               | NOR          | Ν               |  |  |  |

| Logio                         | XOR          | Ν               |  |  |  |

| Logic                         | NAND         | Ν               |  |  |  |

|                               | OR           | Ν               |  |  |  |

|                               | XNOR         | Ν               |  |  |  |

|                               | Add          | N+1             |  |  |  |