## **Streaming Architectures for Medical Image Reconstruction**

by

Brendan Lee West

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in The University of Michigan 2021

#### **Doctoral Committee:**

Professor Thomas F. Wenisch, Chair Associate Professor Reetuparna Das Assistant Professor Ronald G. Dreslinski Professor Jeffrey A. Fessler

## Brendan Lee West

westbl@umich.edu

ORCID iD: 0000-0002-4245-4620

© Brendan Lee West 2020

| To my parents, He | rold West and Germaid West, whose dedication to my education tau | ght |

|-------------------|------------------------------------------------------------------|-----|

|                   | me the value of lifelong learning.                               |     |

|                   |                                                                  |     |

|                   |                                                                  |     |

|                   |                                                                  |     |

|                   |                                                                  |     |

|                   |                                                                  |     |

|                   |                                                                  |     |

ii

#### ACKNOWLEDGEMENTS

When first starting my graduate work, I believed that earning a Ph.D. demonstrated a great achievement by a single individual. However, over time I have learned that this could not be further from the truth—earning a Ph.D. is not the achievement of an individual; it takes a village. Without the support of my family, friends, labmates, and advisor, I never would have achieved this dream. In particular I want to acknowledge Robert and Samantha Nantau, who welcomed me into their family and gave me a "home away from home" during my college years—you may never truly comprehend how much that meant (and still means) to me.

On the academic side, I first want thank my advisor, Thomas F. Wenisch, for believing in my potential when even I questioned it and for his somewhat strange (but undeniably useful...for pranks) association with unicorns. I would also like to thank my fellow Sanctuary Lab members: Akshitha Sriraman, Amirhossein Mirhosseini, Harini Muthukrishnan, Hossein Golestani, Ofir Weisse, Steve Zekany, and Vaibhav Gogte. Although we have been mostly apart for the past year or more, I will always remember our conversations, adventures, and pranks with fondness. Thank you all for making our lab environment so enjoyable.

## TABLE OF CONTENTS

| DEDICATION               |                                |                                                    | i                                                 |

|--------------------------|--------------------------------|----------------------------------------------------|---------------------------------------------------|

| ACKNOWLED                | GEMENT                         | $\mathbf{S}$                                       | iii                                               |

| LIST OF FIGU             | RES                            |                                                    | vi                                                |

| LIST OF TABL             | ES                             |                                                    | X                                                 |

| ABSTRACT                 |                                |                                                    | xi                                                |

| CHAPTER                  |                                |                                                    |                                                   |

| I. Introd                | uction                         |                                                    | 1                                                 |

| •                        | Magnetic Compress              | Resonance Imaging                                  | 3                                                 |

| 2.1<br>2.2<br>2.3<br>2.4 | Delay Co<br>Evaluatio<br>2.4.1 | Transition from 2D to 3D                           | 77<br>9<br>10<br>10<br>11<br>12<br>13<br>18<br>18 |

| 2.5                      | Conclusio                      | on                                                 | 19                                                |

|                          |                                | ming Accelerator for Physics-Limited 3D Plane-Wave | 22                                                |

| 3.1    | Introduction                                               | 22       |

|--------|------------------------------------------------------------|----------|

|        | 3.1.1 3D Ultrasound in Custom Hardware                     | 23       |

|        | 3.1.2 Contributions                                        | 24       |

| 3.2    | Background                                                 | 26       |

|        | 3.2.1 Delay Compression                                    | 27       |

| 3.3    | TETRIS Microarchitecture                                   | 29       |

|        | 3.3.1 Pipeline Stages                                      | 31       |

|        | 3.3.2 TETRIS RS + Multiply-and-Accumulate                  | 35       |

|        | 3.3.3 System Integration                                   | 35       |

| 3.4    | Evaluation                                                 | 36       |

|        | 3.4.1 Why a[nother] Specialized Accelerator?               | 37       |

|        | 3.4.2 Hardware Analysis                                    | 38       |

|        | 3.4.3 Image Quality                                        | 40       |

|        | 3.4.4 Full-System Power                                    | 42       |

| 3.5    | Conclusion                                                 | 42       |

|        |                                                            |          |

|        | and-Dice: Rethinking Non-uniform FFT Interpolations in MRI |          |

| for Mo | odern Parallel Architectures                               | 44       |

| 4.1    | Introduction                                               | 44       |

| 4.1    | 4.1.1 Algorithmic Optimizations                            |          |

|        | 4.1.2 Contributions                                        |          |

| 4.2    | Background                                                 |          |

| 7.2    | 4.2.1 Non-uniform Discrete Fourier Transform               |          |

|        | 4.2.2 Non-uniform Fast Fourier Transform                   | _        |

|        | 4.2.3 Traditional Gridding                                 |          |

| 4.3    | Slice-and-Dice Design                                      |          |

| 4.3    | <u> </u>                                                   |          |

|        | $\mathcal{E}$                                              |          |

| 4.4    | 4.3.2 Simplifying Boundary Checks                          |          |

| 4.4    |                                                            |          |

| 4.5    | 4.4.1 Performance Comparison                               |          |

| 4.5    | Conclusion                                                 | 02       |

|        | W: Non-uniform Fast Fourier Transform Acceleration for MRI |          |

| Recon  | struction                                                  | 63       |

| 5.1    | Introduction                                               | 63       |

| 3.1    | 5.1.1 Reducing Computational Burden                        |          |

|        | 5.1.2 Parallelism Through Hardware                         |          |

|        | 5.1.3 Contributions                                        |          |

| 5.2    | Background                                                 |          |

| 3.2    | 5.2.1 Non-uniform Discrete Fourier Transform               |          |

|        | 5.2.2 Non-uniform Fast Fourier Transform                   |          |

|        | 5.2.3 Traditional Gridding                                 |          |

|        | 5.2.4 Slice-and-Dice Design                                | 71<br>74 |

|        | 2.4.T DIICC-anu-Dicc Design                                | /+       |

|             | 5.2.5      | A Streaming Approach                   | 7   |

|-------------|------------|----------------------------------------|-----|

| 5.3         | JIGSAW     | Microarchitecture                      | 77  |

|             | 5.3.1      | Fixed-Point                            | 79  |

|             | 5.3.2      | JIGSAW Pipeline Microarchitecture 8    | 3(  |

|             | 5.3.3      | Non-uniform Interpolations in JIGSAW 8 | 33  |

|             | 5.3.4      | FFT2/IFFT2 in JIGSAW                   | 34  |

|             | 5.3.5      | System Integration                     | 35  |

| 5.4         | Evaluation | on                                     | 36  |

|             | 5.4.1      | Performance Comparison                 | 37  |

|             | 5.4.2      | Varying Interpolation Window Width 9   | ) ] |

|             | 5.4.3      | Power & Area                           | )2  |

|             | 5.4.4      | Image Quality                          | )3  |

| 5.5         | Conclusi   | on                                     | )5  |

| VI. Conclu  | usion      |                                        | )6  |

| 6.1         | Future D   | irections                              | )7  |

| BIBLIOGRAPI | HY         | 9                                      | 99  |

## LIST OF FIGURES

## Figure

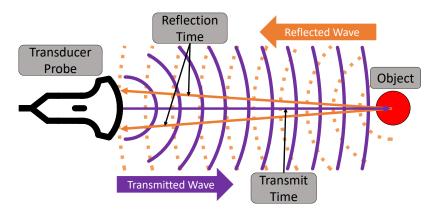

| 2.1 | Ultrasound basics: (1) a transducer probe transmits sound waves through a target medium. (2) these waves come into contact with a target object, they cause partial reflections of the sound waves which are then captured by the transducer probe. (3) the captured reflections are then beamformed to reconstruct the image.                                                                                                               | 8  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

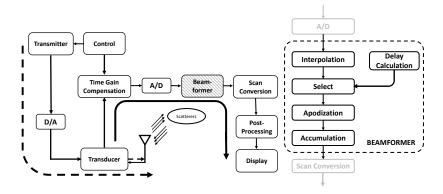

| 2.2 | In the transmit mode, the waveforms are converted to analog form by a D/A converter, amplified, and fed to the transducer elements. In the receive mode, the received signals undergo time gain compensation to reduce the dynamic range and are then digitized by analog-to-digital converters (ADC). The digitized signals are beamformed to form each scanline. After scan conversion and post-processing techniques, the B-mode image is |    |

|     | reconstructed                                                                                                                                                                                                                                                                                                                                                                                                                                | 9  |

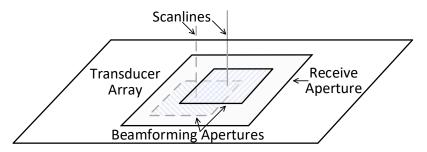

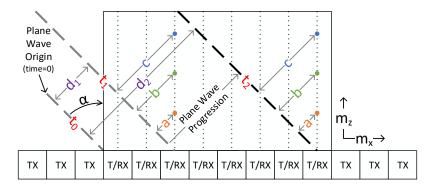

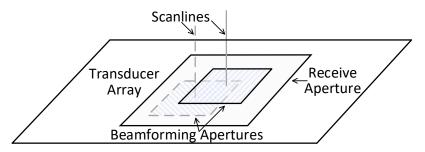

| 2.3 | 3D plane-wave transmit and receive setup; overlapping beamforming apertures "step" across the receive aperture, each creating a single scanline.                                                                                                                                                                                                                                                                                             | 12 |

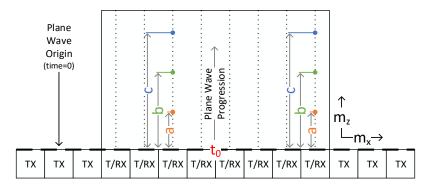

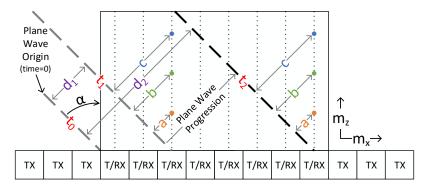

| 2.4 | X-Z slice of the image space showing a 2D component of Delay Compression. Unique transmit distances $a$ , $b$ , and $c$ represent the shared $d_{tx}$ distances from the plane to focal points $m_z$ along each scanline                                                                                                                                                                                                                     | 15 |

| 2.5 | X-Z slice of the image space showing a 2D component of Delay Compression. Unique $d_{tx1}$ distances are shown in $d_1$ and $d_2$ , while $a$ , $b$ , and $c$ represent the shared $d_{tx2}$ distances from the plane to focal points $m_z$ along                                                                                                                                                                                            | 13 |

|     | each scanline                                                                                                                                                                                                                                                                                                                                                                                                                                | 16 |

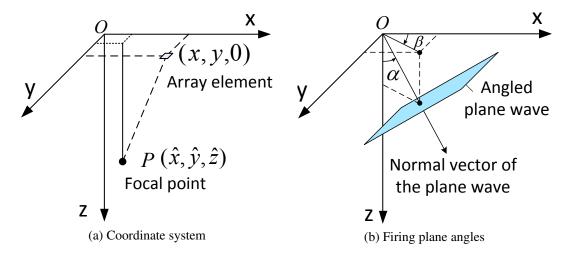

| 2.6 | Coordinate system and angle definition of 3D plane-wave system with coherent compounding                                                                                                                                                                                                                                                                                                                                                     | 17 |

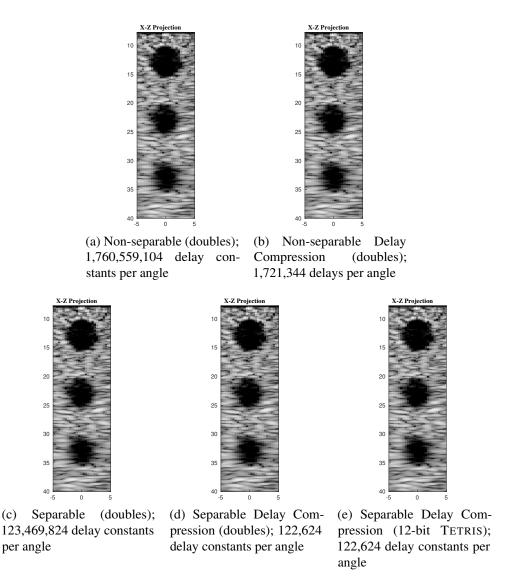

| 2.7 | 2D slices of simulated 3D cyst phantoms using non-separable and separa-                                                                                                                                                                                                                                                                                                                                                                      |    |

|     | ble plane-wave beamforming with 13-angle coherent compounding                                                                                                                                                                                                                                                                                                                                                                                | 20 |

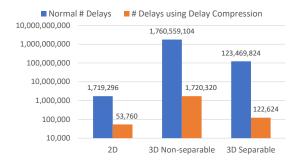

| 2.8 | Delay requirements across plane-wave algorithm variants. $M_z$ is 1,679 points for both 2D and 3D non-separable, while $M_z$ for 3D-Separable has                                                                                                                                                                                                                                                                                            |    |

|     | 2,089 points for the first stage and 1,679 points for the second stage                                                                                                                                                                                                                                                                                                                                                                       | 21 |

| 3.1 | 3D plane-wave transmit and receive setup; overlapping beamforming                                                                                                                                                                                                                                                                                                                                                                            |    |

|     | apertures "step" across the receive aperture, each creating a single scanline.                                                                                                                                                                                                                                                                                                                                                               | 26 |

| 3.2 | X-Z slice of the image space showing a 2D component of Delay Com-                             |    |

|-----|-----------------------------------------------------------------------------------------------|----|

|     | pression. Unique $d_{tx1}$ distances are shown in $d_1$ and $d_2$ , while $a$ , $b$ , and $c$ |    |

|     | represent the shared $d_{tx2}$ distances from the plane to focal points $m_z$ along           |    |

|     | each scanline.                                                                                | 28 |

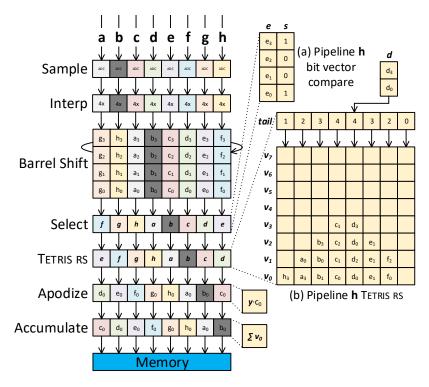

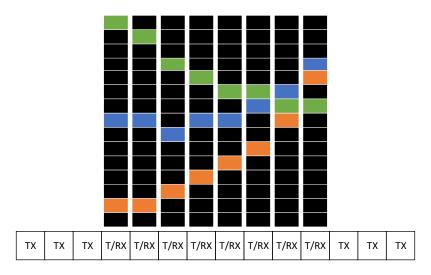

| 3.3 | Scaled-down depiction of TETRIS with one slice of eight pipelines (a-h).                      |    |

|     | New samples arrive at a fixed rate, while the core of the pipeline is clocked                 |    |

|     | 8× faster, allowing samples to rotate across all pipelines via the barrel shift               |    |

|     | stage. Samples matching each focal point are selected according to the                        |    |

|     | pre-computed bit-vector (a) in the select stage, and are then passed to the                   |    |

|     | TETRIS RS (b) for temporary storage. As the "bottom" row fills, samples                       |    |

|     | are sent to the apodization and accumulation modules to compute a single                      |    |

|     | voxel; once filled, the bottom row is "dropped" and erased                                    | 30 |

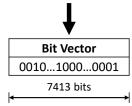

| 3.4 | Bit vector construction example: first the distances from the plane-wave's                    | 50 |

| 5.1 | origin to the focal points are calculated and converted into an index into                    |    |

|     | the sample stream. These indexes are then converted into the offset and                       |    |

|     | bit vector, with a 1 in the bit vector corresponding to each index value and                  |    |

|     | a 0 corresponding to all values between indexes. These points lie along a                     |    |

|     | single scanline; other scanlines may have different $d_{tx1}$ offsets depending               |    |

|     | on the firing angle                                                                           | 32 |

| 3.5 | Example channel data; each colored curve represents a reflection from a                       | J_ |

| 3.3 | unique focal point in the image space                                                         | 33 |

| 3.6 | 2D slices of simulated 3D cyst phantoms using non-separable and separa-                       |    |

| 2.0 | ble plane-wave beamforming with 13-angle coherent compounding                                 | 41 |

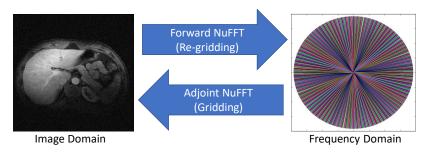

| 4.1 | Each NuFFT variant comprises three steps. Forward: (1) pre-apodization,                       |    |

|     | (2) FFT, (3) regridding. Adjoint: (1) gridding, (2) FFT, (3) de-apodization.                  |    |

|     | Image data from [40]                                                                          | 49 |

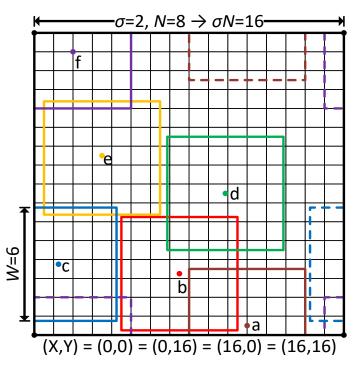

| 4.2 | Uniform grid (flattened torus) with $d = 2$ dimensions, $M = 6$ input samples,                | ., |

|     | base grid dimension $N = 8$ , oversampling factor $\sigma = 2$ , and interpolation            |    |

|     | kernel width $W = 6$                                                                          | 50 |

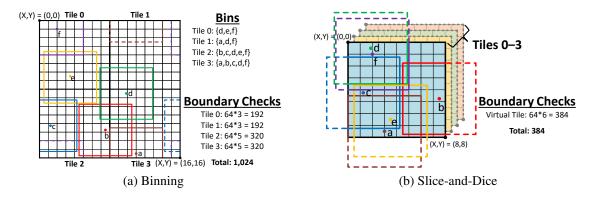

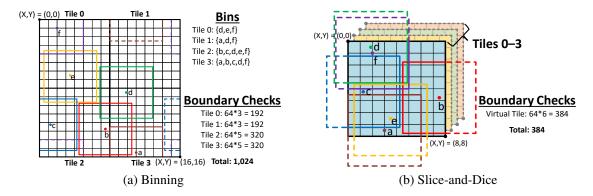

| 4.3 | Binning vs Slice-and-Dice. In this example, binning performs a boundary                       |    |

|     | check between each of the 64 uniform points in a tile and each non-uniform                    |    |

|     | sample in its associated bin. Due to some samples affecting multiple                          |    |

|     | tiles—and therefore being placed in multiple bins—binning processes 16                        |    |

|     | samples. In contrast, Slice-and-Dice obviates the need to presort the data                    |    |

|     | by performing a two step boundary check. Slice-and-Dice performs a                            |    |

|     | single comparison between the "top" view and each sample to determine                         |    |

|     | which relative coordinates (i.e., "columns") in the stack are affected; a                     |    |

|     | combination of the tile coordinates gives the location of the uniform point                   |    |

|     | affected (i.e., "depth" in the stack). Comparatively, binning requires 3×                     |    |

|     | more boundary checks                                                                          | 53 |

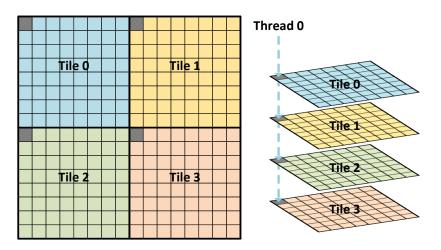

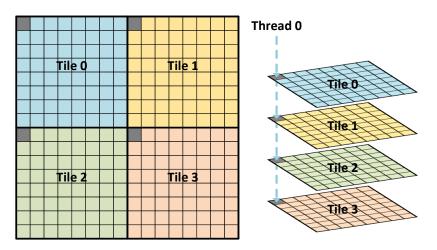

| 4.4 | Slice-and-Dice virtually stacks tiles on top of each other, with a single                     |    |

|     | thread processing all samples that affect a given position in any tile (i.e.,                 |    |

|     | a column in the stack). This drastically reduces the number of all-to-all                     |    |

|     | boundary checks, as each sample must only be checked against each column.                     | 56 |

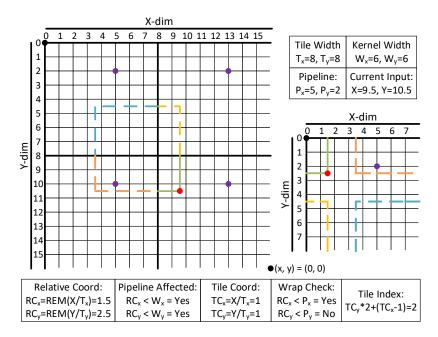

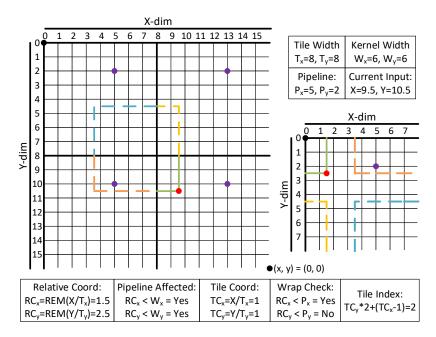

| 4.5 | Slice-and-Dice in action. The thread assigned to handle uniform points with relative positions $(x,y) = (5,2)$ is affected by an input sample with coordinates $(9.5, 10.5)$ if both relative coordinates are less than the interpolation kernel width. The thread is affected in tile $(0,1)$ but the sample's |    |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | coordinate is in tile $(1,1)$ , causing a wrap in the X dimension. If a wrap                                                                                                                                                                                                                                    |    |

|     | occurs, the corresponding tile coordinate is offset                                                                                                                                                                                                                                                             | 57 |

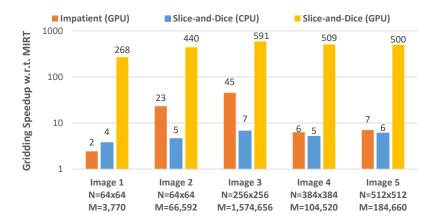

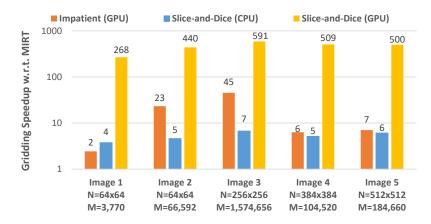

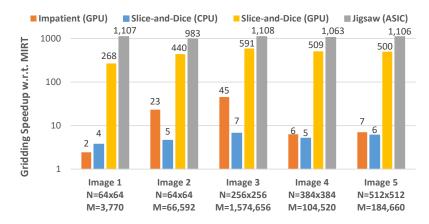

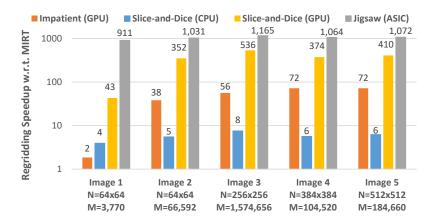

| 4.6 | Gridding speedups of Slice-and-Dice CPU, Slice-and-Dice GPU, and                                                                                                                                                                                                                                                | 51 |

| 4.0 | Impatient [12], normalized to the Michigan Image Reconstruction Toolbox (MIRT). The grid size N and number of non-uniform samples M for each                                                                                                                                                                    |    |

|     | image are labeled; $\sigma = 2$ and $W = 4$ for all images                                                                                                                                                                                                                                                      | 59 |

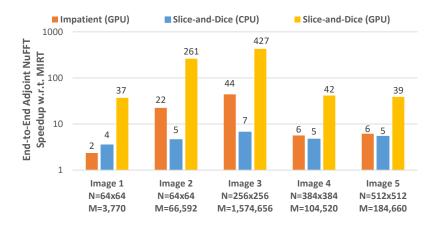

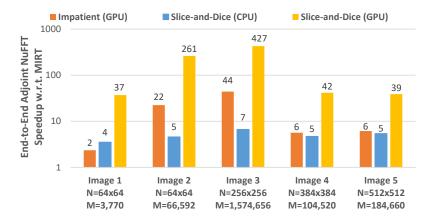

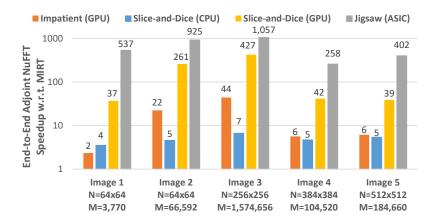

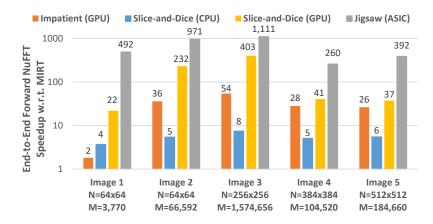

| 4.7 | End-to-end adjoint NuFFT speedups of Slice-and-Dice CPU, Slice-and-                                                                                                                                                                                                                                             | 0) |

| 1.7 | Dice GPU, and Impatient [12], normalized to the Michigan Image Reconstruction Toolbox (MIRT).                                                                                                                                                                                                                   | 60 |

| 4.8 | Regridding speedups of Slice-and-Dice CPU, Slice-and-Dice GPU, and Impatient [12], normalized to the Michigan Image Reconstruction Toolbox                                                                                                                                                                      |    |

|     | (MIRT). The grid size $N$ and number of non-uniform samples $M$ for each                                                                                                                                                                                                                                        |    |

|     | image are labeled; $\sigma = 2$ and $W = 4$ for all images                                                                                                                                                                                                                                                      | 61 |

| 4.9 | End-to-end forward NuFFT speedups of Slice-and-Dice CPU, Slice-and-                                                                                                                                                                                                                                             |    |

|     | Dice GPU, and Impatient [12], normalized to the Michigan Image Recon-                                                                                                                                                                                                                                           |    |

|     | struction Toolbox (MIRT)                                                                                                                                                                                                                                                                                        | 61 |

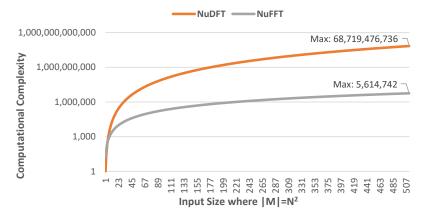

| 5.1 | Computational complexity of the unoptimized 2D NuDFT and NuFFT                                                                                                                                                                                                                                                  | 69 |

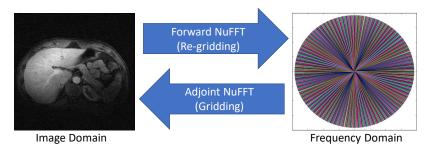

| 5.2 | Each NuFFT variant comprises three steps. Forward: (1) pre-apodization, (2) FFT, (3) regridding. Adjoint: (1) gridding, (2) FFT, (3) de-apodization.                                                                                                                                                            |    |

|     | Image data from [40]                                                                                                                                                                                                                                                                                            | 70 |

| 5.3 | Binning vs Slice-and-Dice. Binning presorts data into bins corresponding to which tiles the samples' interpolation windows intersect. In this example, binning performs a boundary check between each of the 64 uniform                                                                                         |    |

|     | points in a tile and each non-uniform sample in the associated bin. Due                                                                                                                                                                                                                                         |    |

|     | to some samples affecting multiple tiles—and therefore being placed in                                                                                                                                                                                                                                          |    |

|     | multiple bins—binning processes 16 samples. In contrast, Slice-and-Dice                                                                                                                                                                                                                                         |    |

|     | obviates the need to presort the data by performing a two step boundary                                                                                                                                                                                                                                         |    |

|     | check. Slice-and-Dice performs a single comparison between the "top"                                                                                                                                                                                                                                            |    |

|     | view of the stack (i.e., between columns) and each sample to determine                                                                                                                                                                                                                                          |    |

|     | which columns are affected. We then calculate the tile coordinates (i.e.,                                                                                                                                                                                                                                       |    |

|     | "depth" in the stack) to determine the location of the uniform point af-                                                                                                                                                                                                                                        |    |

|     | fected. Using our stacked tile approach, Slice-and-Dice requires only 384                                                                                                                                                                                                                                       |    |

|     | boundary checks versus 1,024 required by binning                                                                                                                                                                                                                                                                | 71 |

| 5.4 | Slice-and-Dice virtually stacks tiles on top of each other, with a single                                                                                                                                                                                                                                       |    |

|     | thread processing all samples that affect a given position in any tile (i.e.,                                                                                                                                                                                                                                   |    |

|     | a column in the stack). This drastically reduces the number of all-to-all                                                                                                                                                                                                                                       |    |

|     | boundary checks, as each sample must only be checked against each column.                                                                                                                                                                                                                                       | 74 |

| 5.5         | Slice-and-Dice in action. The thread assigned to handle uniform points with relative positions $(x,y) = (5,2)$ is affected by an input sample with coordinates $(9.5,10.5)$ if both relative coordinates are less than the interpolation kernel width. The thread is affected in tile $(0,1)$ but the sample's coordinate is in tile $(1,1)$ , causing a wrap in the X dimension. If a wrap occurs, the corresponding tile coordinate is offset | 76       |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

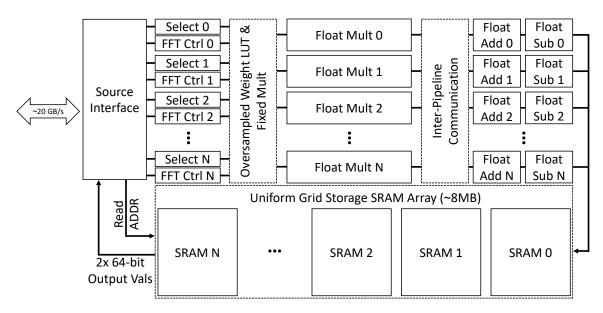

| 5.6         | JIGSAW microarchitecture. Operating at 1.0 GHz, non-uniform samples arrive on a 128-bit bus and are passed serially through the pipelines, which are connected in the Source Interface. Pipelines are logically arranged in a 2D grid, with FFT2 and IFFT2 communication occurring across rows and columns. Each pipeline has a local SRAM array to hold the uniform                                                                            |          |

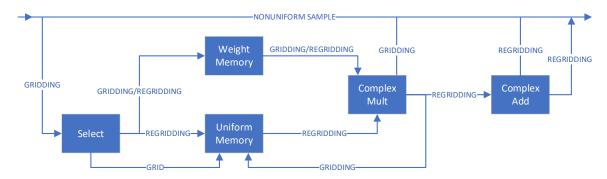

| 5.7         | points in its column                                                                                                                                                                                                                                                                                                                                                                                                                            | 78<br>83 |

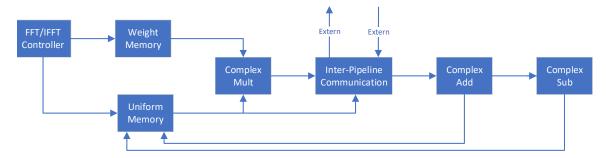

| 5.8         | JIGSAW FFT2/IFFT2 datapath                                                                                                                                                                                                                                                                                                                                                                                                                      | 84       |

| 5.9         | Gridding speedups of Slice-and-Dice CPU, Slice-and-Dice GPU, JIGSAW, and Impatient [12], normalized to the Michigan Image Reconstruction Toolbox (MIRT). The grid size <i>N</i> and number of non-uniform samples <i>M</i>                                                                                                                                                                                                                      |          |

| <b>7</b> 10 | for each image are labeled; $\sigma = 2$ and $W = 4$ for all images                                                                                                                                                                                                                                                                                                                                                                             | 87       |

| 5.10        | End-to-end adjoint NuFFT speedups of Slice-and-Dice CPU, Slice-and-Dice GPU, JIGSAW, and Impatient [12], normalized to the Michigan Image Reconstruction Toolbox (MIRT). The grid size $N$ and number of non-uniform samples $M$ for each image are labeled; $\sigma = 2$ and $W = 4$ for                                                                                                                                                       |          |

|             | all images                                                                                                                                                                                                                                                                                                                                                                                                                                      | 88       |

| 5.11        | Regridding speedups of Slice-and-Dice CPU, Slice-and-Dice GPU, JIG-SAW, and Impatient [12], normalized to the Michigan Image Reconstruction Toolbox (MIRT). The grid size $N$ and number of non-uniform samples $M$ for each image are labeled; $\sigma = 2$ and $W = 4$ for all images                                                                                                                                                         | 89       |

| 5.12        | End-to-end forward NuFFT speedups of Slice-and-Dice CPU, Slice-and-Dice GPU, JIGSAW, and Impatient [12], normalized to the Michigan Image Reconstruction Toolbox (MIRT). The grid size $N$ and number of non-uniform samples $M$ for each image are labeled; $\sigma = 2$ and $W = 4$ for all images                                                                                                                                            | 9(       |

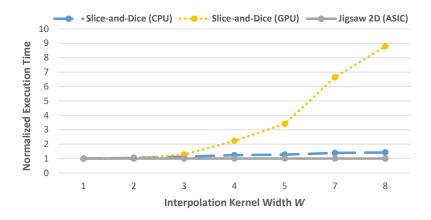

| 5.13        | Effects of interpolation kernel width on performance of CPU, GPU, and ASIC Slice-and-Dice gridding implementations. Each implementation is normalized to itself, showcasing the increase in execution time with increasing window width.                                                                                                                                                                                                        | 91       |

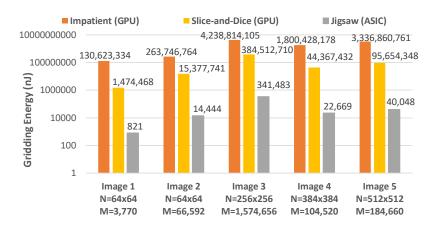

| 5.14        | Energy requirements of Slice-and-Dice GPU, JIGSAW, and Impatient [12]                                                                                                                                                                                                                                                                                                                                                                           |          |

| 5.15        | gridding implementations across images                                                                                                                                                                                                                                                                                                                                                                                                          | 93       |

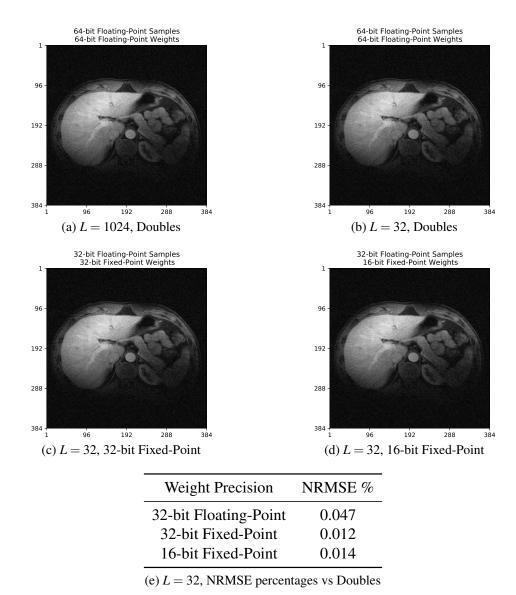

|             | each complex table value in Figures 5.15a and 5.15b. Image data from [40].                                                                                                                                                                                                                                                                                                                                                                      | 94       |

## LIST OF TABLES

| Table |                                                                        |

|-------|------------------------------------------------------------------------|

| 2.1   | 3D Plane-Wave System Parameters                                        |

| 2.2   | Delay Calculations Required — per angle                                |

| 2.3   | Anechoic Cyst CNR — 13-angle compounding                               |

| 3.1   | 3D Plane-Wave System Parameters                                        |

| 3.2   | System Performance — volumes per second                                |

| 3.3   | Beamforming Operations per Second/Watt                                 |

| 3.4   | Anechoic Cyst CNR — 13-angle compounding                               |

| 3.5   | Estimated Full-System Power — each column represents a different layer |

|       | in the 3D stack                                                        |

| 5.1   | JIGSAW System Parameters                                               |

| 5.2   | JIGSAW Synthesis Results in 16 nm Technology                           |

#### **ABSTRACT**

Non-invasive imaging modalities have recently seen increased use in clinical diagnostic procedures. Unfortunately, emerging computational imaging techniques, such as those found in 3D ultrasound and iterative magnetic resonance imaging (MRI), are severely limited by the high computational requirements and poor algorithmic efficiency in current parallel hardware—often leading to significant delays before a doctor or technician can review the image, which can negatively impact patients in need of fast, highly accurate diagnosis. To make matters worse, the high raw data bandwidth found in 3D ultrasound requires on-chip volume reconstruction with a tight power dissipation budget—dissipation of more than 5 W may burn the skin of the patient. The tight power constraints and high volume rates required by emerging applications require orders of magnitude improvement over state-of-the-art systems in terms of both reconstruction time and energy efficiency. The goal of the research outlined in this dissertation is to reduce the time and energy required to perform medical image reconstruction through software/hardware co-design. By analyzing algorithms with a hardware-centric focus, we develop novel algorithmic improvements which simultaneously reduce computational requirements and map more efficiently to traditional hardware architectures. We then design and implement hardware accelerators which push the new algorithms to their full potential.

In the first part of this dissertation, we characterize the performance bottlenecks of high-volume-rate 3D ultrasound imaging. By analyzing the 3D plane-wave ultrasound algorithm, we reduce computational and storage requirements in Delay Compression. Delay Compression recognizes additional symmetry in the planar transmission scheme found in 2D, 3D, and 3D-Separable plane-wave ultrasound implementations, enabling on-chip

storage of the reconstruction constants for the first time and eliminating the most power-intensive component of the reconstruction process. We then design and implement TETRIS, a streaming hardware accelerator for 3D-Separable plane-wave ultrasound. TETRIS is enabled by the TETRIS RESERVATION STATION (RS), a novel 2D register file that buffers incomplete voxels and eliminates the need for a traditional load-and-store memory interface. Utilizing a fully pipelined architecture, TETRIS reconstructs volumes at physics-limited rates (i.e., limited by the physical propagation speed of sound through tissue).

Next, we review a core component of several computational imaging modalities, the Non-uniform Fast Fourier Transform (NuFFT), focusing on its use in MRI reconstruction. We find that the non-uniform interpolation step therein requires over 99% of the reconstruction time due to poor spatial and temporal memory locality. While prior work has made great strides in improving the performance of the NuFFT, the most common algorithmic optimization severely limits the available parallelism, causing it to map poorly to the massively parallel processing available in modern GPUs and FPGAs. To this end, we create Slice-and-Dice, a processing model which enables efficient mapping of the NuFFT's most computationally-intensive component onto traditional parallel architectures. We then demonstrate the full acceleration potential of Slice-and-Dice with JIGSAW, a custom hardware accelerator which performs the non-uniform interpolations found in the NuFFT in time approximately linear in the number of non-uniform samples, irrespective of sampling pattern, uniform grid size, or interpolation kernel width.

The algorithms and architectures herein enable faster, more efficient medical image reconstruction, without sacrificing image quality. By decreasing the time and energy required for image reconstruction, our work opens the door for future exploration into higher-resolution imaging and emerging, computationally complex reconstruction algorithms which improve the speed and quality of patient diagnosis.

#### **CHAPTER I**

## Introduction

Non-invasive medical imaging modalities, such as X-ray CT, magnetic resonance imaging (MRI), and ultrasound have become cornerstones in modern medicine. Today, doctors are able to see high-resolution images of a patient's internals, both statically and in real-time, without the costly and often dangerous invasive diagnostic procedures required in the past.

In recent years, medical imaging has started to experience an evolution from 2D to 3D and real-time imaging capabilities. 3D and real-time imaging offer a more detailed view of the region of interest, without the need to rely on experienced technicians to estimate the "whole" from a set of 2D slices, in a manner which enables faster, more accurate diagnosis. Unfortunately, while great strides have been made in new 3D imaging algorithms, these algorithms often bring exponential increases in raw data volume, computational complexity, and execution time.

While computer performance has improved, in many cases existing architectures are still too slow or inefficient to support real-time data acquisition and image reconstruction. Commercial hardware has been able to reconstruct 3D images for some algorithms, but these often suffer from severe computational bottlenecks—resulting in long reconstruction times and/or poor resolution. As an example, state-of-the-art 3D ultrasound systems can only reconstruct tens of volumes per second [44, 18, 14, 19], which is far too low for emerging applications which require tracking high-frequency motion [37, 23, 55, 50]. These perfor-

mance problems are caused in part by the algorithms themselves: many algorithms in the medical domain are designed purely to enable a new imaging technique, without consideration of how the algorithm will actually be executed in hardware. To compound the problem, computer architects rarely design modern systems with the unique requirements of medical imaging reconstruction in mind. This has created a disconnect between imaging algorithm developers and hardware architects, with the result being that traditional architectures are far too inefficient to feasibly handle many real-time 3D imaging applications.

Many of the inefficiencies and computational bottlenecks found in reconstruction algorithms can be traced back to current architecture's load-and-store memory system. Medical imaging applications often have memory access patterns which do not mesh well with modern computer caches, leading to severe performance degradation and power consumption that in some cases make imaging entirely infeasible [1, 28, 44, 44, 14, 2]. To continue advancements in medical image reconstruction, algorithm developers and hardware architects must work together to enable new and improved imaging systems.

In this dissertation, we take an in-depth look at two of the most popular imaging modalities, ultrasound and MRI. Through careful benchmarking of each algorithmic component, we identify the primary bottlenecks encountered in traditional parallel systems, such as GPUs. We then partner with signal processing experts to rebuild the algorithms from the ground up. Using a hardware-centric focus, we develop novel algorithmic modifications and computational models which enable dramatic performance improvements when using traditional architectures.

While improved algorithms go a long way toward enabling emerging imaging modalities, not all applications can afford the space or power required by the racks of GPUs needed to reconstruct images in real-time. With this in mind, we demonstrate the full performance and power-saving potential of our algorithms by designing custom hardware accelerator architectures for 3D ultrasound and MRI reconstruction. We obviate the memory subsystem bottlenecks encountered in previous systems by doing away with the costly load-and-store

paradigm to which standard architectures have historically adhered to. Using stall-free, fully-pipelined hardware implementations, we achieve orders of magnitude improvements in both performance (latency and throughput) and power efficiency versus traditional systems and prior state-of-the-art research.

#### 1.1 3D Ultrasound

Ultrasound is an imaging modality widely used for non-invasive diagnostics because of its low transmit power, lack of ionizing radiation, and portability compared to X-ray and magnetic resonance imaging (MRI) [48, 42]. Relying on the principle of sonic transmission and reflection, ultrasound acts much like sonar and radar, transmitting sound waves into target volumes by exciting a transducer array with an electronic pulse. As the sound waves pass through the volume, partial reflections occur when the waves encounter tissue interfaces; these reflections are then sampled by the transducer array. The raw reflection signals collected by each transducer are used to reconstruct an image through a process called beamforming, wherein the signals are filtered to coherently sum reflections that originate from the numerous focal points within the image volume.

Beamforming is the most computationally expensive aspect of ultrasound imaging. Identifying the samples within each receive signal that correspond to each focal point is computationally expensive, as it requires numerous trigonometry calculations to calculate the delay constants (indexes into the received signal). In 2D systems, these delays can be trivially calculated ahead of time and stored in on-chip look-up tables to save power and improve performance. Unfortunately, an exponential increase in the number of delays for emerging 3D imaging applications precludes this possibility. Worse, the data rate found in 3D systems—often over 500 Gbps—is too high to offload to an external machine for reconstruction, instead requiring beamforming to occur within the ultrasound probe handle. This in turn adds another layer of complexity: the probe handle's power dissipation must be kept under 5 W, as higher dissipation may burn the skin of the patient [44].

Prior works have made great strides in lowering the computational complexity of ultrasound algorithms [64, 66, 63], delay approximation [44, 14], and custom accelerator architectures [44, 14, 19, 18]. Unfortunately, even the most performant of these are only able to reconstruct tens of volumes per second. Emerging 3D ultrasound applications in cardiac imaging [37], vector flow imaging [23, 55], and shear wave elastography [50] require extremely high volumetric image acquisition rates to track high frequency motion—orders of magnitude higher than possible using prior approaches.

In the first half of this dissertation, we discuss our work on 3D ultrasound algorithmic optimizations and hardware architectures. We first introduce Delay Compression, a novel decomposition of the 3D plane-wave beamforming algorithm's most computationally intensive component: calculation of the round-trip delay constants. Applicable to 2D, 3D, and 3D-Separable beamforming variants, Delay Compression reduces the number of delay constants requiring distinct calculation by a factor equal to the number of receive transducers in the ultrasound probe head—1024× using our 3D system parameters. Such a dramatic reduction in computational requirements results not only in the algorithm mapping more efficiently to traditional hardware accelerators, such as GPUs, but also enables first-of-its-kind custom hardware solutions for applications with extremely tight power constraints and performance requirements.

Next, we describe our work on TETRIS, a novel hardware accelerator for separable ultrasound beamforming that implements Delay Compression and enables volume acquisition rates up to the physical limits of acoustic propagation delay. TETRIS operates in a streaming fashion—without requiring on-chip storage of the entire receive signal—reconstructing volumes in real-time. For a representative imaging task, TETRIS generates physics-limited ~13,000 volumes per second in an estimated ~2 W system power budget. The TETRIS beamformer has an unprecedented power efficiency of 2.03 tera-beamforming operations per watt (tera-BOPS)—an increase in efficiency of nearly 3× compared to the prior work.

### 1.2 Magnetic Resonance Imaging

Magnetic resonance imaging (MRI) is a computational imaging modality popular in radiology due to its ability to enable high-resolution non-invasive imaging of anatomy. While it is desirable to visualize physiological processes in a non-invasive manner for diagnostic and post-operative care purposes, MRI historically suffers from long and often uncomfortable scan times—MRI scans can generate sound levels up to 110 decibels and take upwards of 90 minutes [13, 53].

To reduce scan time, MRI applications often rely on non-uniform, frequency-domain sampling trajectories such as radial, spherical, and spiral. Unfortunately, these irregular sampling patterns preclude use of the highly optimized Fast Fourier Transform (FFT) operations commonly found in reconstruction implementations. Instead, applications with irregular sampling patterns turn to the Non-uniform Fast Fourier Transform (NuFFT), an extension of the FFT which enables computation over irregular data. The NuFFT transforms data between the frequency and image domains using a three-step process: (1) interpolation of the non-uniform samples onto or from a uniform grid, (2) a standard [uniform] FFT, and (3) apodization, or weighting of the uniform data.

The time required to compute the NuFFT is dominated by the non-uniform interpolation component, which is responsible for over 99% of the reconstruction time. Because each non-uniform sample affects a window of non-contiguous memory locations, MRI reconstruction algorithms often require nearly random reads and writes. With little spatial and temporal locality available, NuFFT computation is severely limited by poor cache and memory bandwidth utilization [47, 30, 32, 28, 3, 2].

Prior work has offered algorithmic optimizations which focus on the NuFFT's performance by optimizing the memory bandwidth utilization during the non-uniform interpolation step. The most popular approach is a process called *binning* [24, 43]. Binning breaks the uniform grid into *tiles*, presorting the non-uniform samples into *bins* based on which tiles their interpolation windows intersect. Tile—bin pairs are then processed sequentially, with

the tile held in on-chip memory to reduce the number of cache misses.

While the algorithmic optimizations available through binning have led to significant speedups in both traditional processors and custom FPGA architectures [47, 38, 32, 31, 12, 3, 2], binning severely limits the amount of available parallelism. Paired with the overhead of presorting the non-uniform samples and maintaining the bins, current NuFFT implementations are insufficient to enable emerging MRI techniques requiring thousands or even millions of NuFFT calls [6, 10].

In the second half of this dissertation, we focus on optimizing the non-uniform interpolations found in MRI reconstructions. We develop a novel grid decomposition model, Slice-and-Dice, that obviates the presorting operations required by prior optimizations and exposes more parallelism to existing hardware architectures. Using a tiled memory layout, Slice-and-Dice results in a 1600× reduction in the number of boundary check operations when using our system parameters. When implemented on a GPU, Slice-and-Dice achieves significant improvements in terms of cache hit rate, latency, and occupancy compared to prior state-of-the-art GPU implementations.

To highlight Slice-and-Dice's full potential when paired with a custom memory subsystem and computational pipeline, we implement JIGSAW, a streaming hardware architecture for NuFFT acceleration. JIGSAW uses a mixture of fixed- and floating-point functional units to form 2D array of stall-free pipelines, performing interpolations with *M* non-uniform samples in approximately *M* cycles, irrespective of sampling pattern, interpolation kernel width, or uniform grid size. To enable end-to-end NuFFT acceleration, JIGSAW implements a 2D radix-2 FFT and IFFT operations on top of the Slice-and-Dice tiled memory layout. Processing up to eight FFTs in parallel, JIGSAW achieves unprecedented NuFFT performance while simultaneously reducing power requirements by orders of magnitude.

#### **CHAPTER II**

## Delay Compression: Reducing Delay Calculation Requirements for 3D Plane-Wave Ultrasound

#### 2.1 Introduction

Ultrasound is computational imaging modality often used in medical diagnosis. Its low cost, lack of ionizing radiation, and no known dangers or side effects provides a safe and economical imaging method compared to modalities such as X-ray and MRI [48, 42], with the added benefit of being amenable to parallel hardware.

Relying on the principle of sonic transmission and reflection, ultrasound acts much like sonar and radar. In its most simplistic form, visualized in Figure 2.1, an array of transducers located in the tip of an ultrasound probe handle transmits sound waves into the target volume by exciting the transducers with an electronic pulse. These sound waves pass through and partially reflect at tissue interfaces or scatter at inhomogeneities, with the scattered wave radiating outward in an expanding spherical geometry. Reflections and scattered waves are then captured by the transducer array by sampling the time-dependent intensity of the signal; different tissue inhomogeneities and interfaces result in varying intensities. The raw reflection signals collected by each transducer are then used to reconstruct a volumetric image through a process called beamforming. In beamforming, the received signals are

The work described in this section was published in DAC 2019 [60], IUS 2019 [58], and IEEE TC 2020 [59].

Figure 2.1: Ultrasound basics: (1) a transducer probe transmits sound waves through a target medium. (2) these waves come into contact with a target object, they cause partial reflections of the sound waves which are then captured by the transducer probe. (3) the captured reflections are then beamformed to reconstruct the image.

filtered to coherently sum reflections that originate from numerous focal points within the image volume.

Beamforming is the most computationally expensive aspect of ultrasonic imaging. In beamforming, the samples within each receive signal corresponding to each focal point are identified based on the round-trip time-of-flight and the speed of sound. This distance calculation requires using numerous trigonometry calculations for each focal point. Moreover, there is substantial data sharing and reuse, as each sample may contribute to numerous voxels in the final volumetric image. Hence, although calculating each voxel is in principle embarrassingly parallel, performing these computations efficiently while exploiting data sharing is difficult.

Time-delay beamforming, one of the primary beamforming methods, calculates a time delay for the propagation path from each transmit element to each focal point and then to each receive element. For a target image of size  $M_xM_z$  focal points and a receive array of  $N_x$  transducers, the number of required delays, and the associated computational complexity, is  $M_xM_zN_x$ . After sampling the reflected signals, the samples are commonly interpolated to improve axial resolution without the power overhead of faster analog-to-digital converters (ADCs) [4]. After interpolation, samples corresponding to each pixel are selected using the time delays. The selected values then undergo a process called apodization, in which

Figure 2.2: In the transmit mode, the waveforms are converted to analog form by a D/A converter, amplified, and fed to the transducer elements. In the receive mode, the received signals undergo time gain compensation to reduce the dynamic range and are then digitized by analog-to-digital converters (ADC). The digitized signals are beamformed to form each scanline. After scan conversion and post-processing techniques, the B-mode image is reconstructed.

the samples are multiplied by a weighting function. The weighting function accounts for any lateral distance between the receive transducer and the transducer aligned with the focal point in question, thereby improving focus and suppressing side lobes. Apodized samples are then summed to form the final pixel. A flowchart showing a generic time-delay beamforming algorithm is shown in Figure 2.2.

#### 2.1.1 Transition from 2D to 3D

In 2D imaging, delays can be trivially precalculated and stored in lookup tables [34], but the scale of 3D imaging has typically precluded such precomputation due to the vast number of delays required. Moreover, the transition from 2D images to 3D volumes comes with an exponential increase in computational complexity and raw data bandwidth. Given a 2D receive aperture of 32×32 transducers and a 40 MHz sampling rate using 12-bit resolution, the raw data bandwidth is nearly 500 Gbps per second. This bandwidth is too high for a power-constrained platform, such as an ultrasound transducer probe, to transmit to an ultrasound machine for processing in real-time—therefore requiring beamforming to be tightly coupled to the transducers. This tight coupling complicates matters by requiring that beamforming occur within the ultrasound probe handle, in close contact with the patient's

skin. If the probe handle dissipates more than ~5 W, including the beamformer, the resulting heat could burn the patient's skin [44].

#### 2.1.2 Difficulties of High-Volume-Rate Ultrasound

Emerging 3D ultrasound applications in cardiac imaging [37], vector flow imaging [23, 55], and shear wave elastography [50] require extremely high volumetric image acquisition rates to track high frequency motion. In 2D this has been achieved by precalculating the round-trip delay values used in the beamforming process and storing them in look-up tables (LUTs) instead of calculating them on the fly, or by offloading the data to external, power-hungry machines to handle beamforming. However, due to the increased complexity of 3D systems, these are no longer options—there are too many delays to store in on-chip look-up tables, and the raw data bandwidth is too high to offload to a larger, more powerful machine. To make matters worse, these applications also require large imaging apertures to capture sufficient resolution in a large region of interest. The combination of a large receive aperture (32×32 elements), large imaging volume (32×32×>1500 focal points), substantial precision requirement (10-12 bit ADCs), and enormous volume rate (>10,000 volumes / sec) pose a daunting computational requirement—straight-forward delay-and-sum beamforming is intractable in real-time even with a large array of GPUs.

#### 2.1.3 Reducing Computational Burden

To reduce the computational complexity of 3D ultrasound, researchers have proposed separable beamforming algorithms [64, 66, 63], which approximate traditional beamforming by splitting it into two stages. Separable algorithms perform beamforming consecutively along the two lateral image axes—first along the X-dimension, and then along the Y-dimension. The two-stage process reduces the 2D grid of contributing transducers (multiplicative complexity) for each voxel—a 3D pixel in the output volume—to two 1D arrays of contributing transducers (additive complexity), while sacrificing little image clarity. Despite such algo-

Table 2.1: 3D Plane-Wave System Parameters.

| Property                                        | Value           |

|-------------------------------------------------|-----------------|

| Speed of sound (tissue), m/s                    | 1540            |

| TX / RX Pitch, µm                               | 192.5 / 385     |

| Transmit aperture size, transducers             | $128 \times 96$ |

| Receive aperture size, transducers              | $32 \times 32$  |

| Beamforming aperture size, transducers          | $32 \times 32$  |

| Number of scanlines per stage                   | $32 \times 32$  |

| Stage 1 ADC input length, points                | 3,077           |

| Stage 1 scanline output length $(M_z)$ , points | 2,089           |

| Stage 2 scanline output length $(M_z)$ , points | 1,679           |

| Maximum imaging depth, cm                       | 6               |

| Center frequency, MHz                           | 4               |

| 6 dB transducer bandwidth, MHz                  | 2               |

| ADC sampling rate, MHz                          | 40              |

rithmic advances, however, naïve time-delay beamforming often remains impractical for 3D applications, as delay calculations involve complicated trigonometry.

#### 2.1.4 Contributions

In this chapter, we build upon the work in [64, 66], which proposed a separable variant of the 3D plane-wave algorithm to reduce the computational complexity of plane-wave imaging. To make the algorithm's computational complexity even more tractable, and therefore more amenable to hardware implementation, we present Delay Compression. Delay Compression is a novel refinement of the 2D plane-wave imaging algorithm that enables drastic reduction in the number of unique round-trip computations per volume. We then extend this reduction to 3D for both non-separable and separable variants, demonstrating that this approach is not limited to the 2D case. Our time-delay decomposition dramatically decreases hardware complexity, increases performance, and lowers power requirements. In our 3D non-separable system, Delay Compression achieves a 1024× reduction in the number of delays computed, while our 3D-Separable implementation results in an asymptotic reduction in the number of delays computed for the first and second stages—up to 1008× and 1006× reduction in the first and second stages when using the aperture dimensions in Table 2.1, respectively.

Figure 2.3: 3D plane-wave transmit and receive setup; overlapping beamforming apertures "step" across the receive aperture, each creating a single scanline.

With the number of unique delays reduced by over three orders of magnitude, precalculation and on-chip storage of delay constants for 3D systems becomes feasible for the first time, enabling new architectural approaches to high-volume-rate ultrasound imaging.

### 2.2 Background

Plane-wave imaging is an ultrasound variant that utilizes a planar transmission scheme. A large 2D array of transducers receive and sample the reflected signals, with each transducer outputting a *channel* of samples. The receive array is divided into smaller, overlapping 2D sub-arrays called beamforming apertures, as seen in Figure 2.3. The channels within each beamforming aperture contribute to voxels along a single *scanline*, or column of voxels in the final volume. In this paper, we assume a receive array of  $M_x M_y$  transducers, beamforming apertures of  $N_x N_y$  transducers, and a depth of  $M_z$ , resulting in a final volume size of  $M_x M_y M_z$  voxels.

Managing delay constants poses a significant challenge in many 3D ultrasound algorithms, and plane-wave is no different. For separable plane-wave imaging with angled compounding [64], which can produce high quality images with plane-wave transmits, each firing angle requires a combined  $M_xM_zN_xN_y + M_xM_yM_zN_y$  delay constants for the two beamforming stages. In Equations (2.1), (2.2),  $\alpha$  and  $\beta$  are the elevational and lateral angles of the plane, respectively.  $(m_x, m_y, m_z)$  are the coordinates of each focal point,  $(n_x, n_y)$  are the coordinates of each receive transducer within the beamforming aperture, and  $(x_0, y_0, z_0)$

is an arbitrary point on the plane at its origin; in this formulation, there is little symmetry between beamforming apertures due to the varying firing angle of the plane.

$$d_{tx} = (m_x - x_0)\sin\alpha\cos\beta + (m_y - y_0)\sin\alpha\sin\beta + (m_z - z_0)\cos\alpha \quad (2.1)$$

$$d_{rx} = \sqrt{(m_x - n_x)^2 + (m_y - n_y)^2 + m_z^2}$$

(2.2)

The high number of required delay constants is one of the principle difficulties of 3D ultrasound in general, as it prohibits large beamforming apertures, receive volumes, and depth combinations. Prior works [18, 19, 44, 46, 14, 15] have used specialized hardware to approximate delays or share small components of the computation between focal points to reduce the hardware requirements for beamforming, but all of these methods fall orders of magnitude short of the target 1,000+ volumes per second for plane-wave applications. Similarly, precomputing the delays and placing them in on-chip storage—or streaming them from off-chip storage—is also prohibitive due to the sheer quantity required (millions of delays per volume for large receive apertures); none of the prior approaches are sufficient for high-volume-rate beamforming.

## 2.3 Delay Compression

To combat the computational requirements of high-volume-rate beamforming, we propose *Delay Compression*. Delay Compression recognizes additional symmetry between the round-trip times for all focal points, thereby allowing us to drastically reduce the total number of computations required for each volume. At a high level, Delay Compression works by breaking the transmission component of the round-trip distance calculation into two pieces, which we call  $d_{tx1}$  and  $d_{tx2}$ .  $d_{tx1}$  is a set of unique distances from the planewave's origin to the first focal point along each scanline, where  $m_z = 0$ , hereafter referred to

as the *base* of each scanline, while  $d_{tx2}$  is a set of distances calculated from when the plane is touching the base of a single scanline to each focal point along that scanline. One  $d_{tx1}$  distance corresponds to each scanline, and the set of  $d_{tx2}$  distances is shared between all scanlines—the  $d_{tx1}$  distance acts as an offset for the  $d_{tx2}$  distances within each beamforming aperture. To thoroughly explain Delay Compression, we will work our way through its function in plane-wave's 2D, 3D non-separable, and finally 3D-Separable [64, 66] variants.

#### 2.3.0.1 Delay Compression in 2D

In its most simplistic form, plane-wave ultrasound fires a planar pulse directly into the target medium with an elevational angle of  $0^{\circ}$ ,  $M_x M_z N_x$  round-trip delays, and a final image size of  $M_x M_z$ . In this case the delay decomposition is straight-forward, as all of the transmission and reflection distances are equal—the distance from the plane's origin to the base of each scanline,  $d_{tx1}$ , is 0 for all scanlines. Equations (2.3), (2.4) demonstrate that the transmission distance does not vary across scanlines, so round-trip distance calculations can be shared—reducing the number of unique delays to  $M_z N_x$ .

$$d_{tx} = m_z - z_0 \tag{2.3}$$

$$d_{rx} = \sqrt{(m_x - n_x)^2 + m_z^2} (2.4)$$

Figure 2.4 illustrates the symmetry. In the figure, the transmission distance is identical for each focal point that lies at the same depth  $m_z$ . With this in mind, distances a, b, and c need to be computed only once for all scanlines, resulting in a single shared set of distance values. The same is true for the reflection distances: since each beamforming aperture is centered on the scanline it produces, the distances from each focal point on the scanline to each transducer within the beamforming aperture are identical across apertures.

However, whereas a planar pulse with an elevational angle of 0° leads to straight-forward

Figure 2.4: X-Z slice of the image space showing a 2D component of Delay Compression. Unique transmit distances a, b, and c represent the shared  $d_{tx}$  distances from the plane to focal points  $m_z$  along each scanline.

symmetry for delay reduction, there are cases, such as improving image quality through coherent compounding, which require transmits at varying elevational angles—resulting in  $M_x M_z N_x$  delay calculations. Equations (2.5), (2.6) show how the transmission and reflection distances are calculated for planar transmits with non-0° elevation angle  $\alpha$ .

$$d_{tx} = (m_x - x_0)\sin\alpha + (m_z - z_0)\cos\alpha \tag{2.5}$$

$$d_{rx} = \sqrt{(m_x - n_x)^2 + m_z^2}$$

(2.6)

For angled transmits, the transmit distance for each focal point at the same  $m_z$  depth depends on the scanline to which the focal point belongs. To recover the symmetry available in the  $0^{\circ}$  case, we use Delay Compression to decompose the transmission distance into two components, which we call  $d_{tx1}$  and  $d_{tx2}$ .  $d_{tx1}$  addresses the angle dependency by capturing the unique distance from the plane-wave's origin to the base of each scanline, from which the distances to each focal point are again equal across scanlines. By setting the value  $m_z$  in Equation (2.5) to 0, we find the distance from the plane-wave's origin to the first focal point in each scanline. We then set  $m_x$  equal to  $x_0$  and  $x_0$  equal to 0, essentially transforming the origin of the coordinate system to the base of the scanline. The 2D variant of the transmit distance decomposition can be seen in Equations (2.7), (2.8).

Figure 2.5: X-Z slice of the image space showing a 2D component of Delay Compression. Unique  $d_{tx1}$  distances are shown in  $d_1$  and  $d_2$ , while a, b, and c represent the shared  $d_{tx2}$  distances from the plane to focal points  $m_z$  along each scanline.

$$d_{tx1} = (m_x - x_0)\sin\alpha - z_0\cos\alpha \tag{2.7}$$

$$d_{tx2} = m_z \cos \alpha \tag{2.8}$$

Figure 2.5 again illustrates our delay decomposition, this time with an elevational angle of  $\alpha$ . In this example,  $d_{tx1}$  distances  $d_1$  and  $d_2$  vary, but the  $d_{tx2}$  distances a, b, and c are constant across scanlines. By computing one  $d_{tx1}$  value for each scanline and a single set of  $d_{tx2}$  values, all of the unique transmission distances can be recomputed by simply adding the  $d_{tx1}$  values to the set of  $d_{tx2}$  values—reducing the number of unique delays to  $M_x + M_z N_x$ .

#### 2.3.0.2 Delay Compression in 3D

3D plane-wave ultrasound requires drastically more round-trip calculations per volume than the 2D case. The coordinate system used for 3D plane-wave ultrasound includes both an elevational angle  $\alpha$  and lateral angle  $\beta$ , as shown in Figure 2.6. This additional angle results in the number of delay calculations increasing to  $M_x M_y M_z N_x N_y$ .

**3D Non-Separable.** We implement Delay Compression in the 3D non-separable planewave algorithm much like 2D, decomposing the distance calculation into a base component and a distance along the scanline, sharing the latter across all scanlines. First, we again set  $m_z$  to 0 in order to calculate the distance  $d_{tx1}$ . We then set  $m_x$  to  $x_0$ ,  $m_y$  to  $y_0$ , and  $m_z$  to

Figure 2.6: Coordinate system and angle definition of 3D plane-wave system with coherent compounding.

0—translating the coordinate system to the base of the scanline and facilitating calculation of  $d_{tx2}$ . This breakdown can be seen in Equations (2.9), (2.10).

$$d_{tx1} = (m_x - x_0)\sin\alpha\cos\beta + (m_y - y_0)\sin\alpha\sin\beta - z_0\cos\alpha$$

(2.9)

$$d_{tx2} = m_z \cos \alpha \tag{2.10}$$

With this decomposition, the unique delays are reduced to  $M_x M_y + M_z N_x N_y$ —nearly a 1024x reduction under our system parameters.

**3D-Separable.** Separable 3D plane-wave imaging [66, 64] is a technique designed to reduce calculations by splitting beamforming into two sequential steps—first performing beamforming along the X-axis, and then along the Y-axis. The original implementation of separable 3D plane-wave imaging entails a computational complexity of  $M_xM_zN_xN_y$  for the first stage and  $M_xM_yM_zN_y$  for the second stage. Although this reduction is already significant, Delay Compression can further reduce the number of required calculations to only  $M_xM_y+M_zN_x$  for the first stage and  $M_xM_y+M_zN_y$  for the second stage. By using 3D-Separable plane-wave imaging and Delay Compression in tandem, 3D ultrasound complexity is reduced to a point where on-chip integration is achievable without compromising image

Table 2.2: Delay Calculations Required — per angle.

| 2D Flat<br>2D Angled              | 53,728<br>1,719,296        |

|-----------------------------------|----------------------------|

| 2D Angled Compressed              | 53,760                     |

| 3D<br>3D Compressed               | 1,760,559,104<br>1,720,320 |

| 3D-Separable (stage 1)            | 68,452,352                 |

| 3D-Separable (stage 2)            | 55,017,472                 |

| 3D-Separable Compressed (stage 1) | 67,872                     |

| 3D-Separable Compressed (stage 2) | 54,752                     |

|                                   |                            |

quality or exceeding the power requirements of the ultrasound probe handle.

Delay Compression drastically reduces the number of delay calculations required in 2D, 3D, and 3D-Separable variants of the plane-wave algorithm. By reducing the number of calculations, far less work is needed in order to reconstruct images or volumes—directly affecting the hardware complexity and power requirements for the reconstruction process. The exact number of delay calculations required by each variant when using our system parameters is shown in Table 2.2.

#### 2.4 Evaluation

#### **2.4.1** Image Quality

We verify Delay Compression image quality using visual comparison of 2D volume slices and the calculated Contrast-to-Noise Ratio (CNR) of simulated cyst phantoms. CNR is a standard metric for comparing ultrasound image quality [41, 54, 5] where the contrast resolution of the echoic (tissue) and anechoic (cyst) regions are compared under the effects of clutter and receiver noise (outside interference that produces image artifacts); higher CNR values indicate better image quality. The purpose of this validation is to confirm that Delay Compression's decomposition does not degrade image quality relative to that of traditional double-precision floating-point calculations.