### Energy-Efficient Circuit Designs for Miniaturized Internet of Things and Wireless Neural Recording

by

Jongyup Lim

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical and Computer Engineering) in the University of Michigan 2021

**Doctoral Committee:**

Professor Dennis M. Sylvester, Chair Professor David T. Blaauw Associate Professor Cynthia A. Chestek Assistant Professor Hun-Seok Kim Jongyup Lim

jongyup@umich.edu

ORCID iD: 0000-0003-0306-3966

© Jongyup Lim 2021

# **DEDICATION**

To my wife Suzie, my parents, and family with love and gratitude

# **TABLE OF CONTENTS**

| DEDICATIONii                                                              |

|---------------------------------------------------------------------------|

| LIST OF FIGURES vi                                                        |

| LIST OF TABLES xi                                                         |

| ABSTRACT xii                                                              |

| CHAPTER 1 Introduction1                                                   |

| CHAPTER 2 A Gate-Leakage-based Frequency-Locked Timer for Ultra-Low Power |

| Sensor Nodes with Second-Order Temperature Dependency Cancellation        |

| 2.1 Introduction                                                          |

| 2.2 Gate-Leakage-based Frequency-Locked Timer                             |

| 2.3 First- and Second-order Temperature Dependance Cancellation           |

| 2.4 VCO with Switched Capacitor Voltage Doubler9                          |

| 2.5 Line Sensitivity Enhancement 10                                       |

| 2.6 Measurement Results 10                                                |

| 2.7 Conclusion 14                                                         |

| CHAPTER 3 An Energy-Efficient All-Analog ResNet Accelerator               |

| 3.1 Introduction                                                          |

| 3.2 N       | Main Concept of the AA-ResNet                                      |      |

|-------------|--------------------------------------------------------------------|------|

|             | 3.2.1 Convolution in Pulse-to-Charge Domain                        | 19   |

|             | 3.2.2 Sampling and Holding in Charge-to-Pulse Domain               |      |

|             | 3.2.3 NL function in Voltage-to-Pulse Domain                       |      |

|             | 3.2.4 Overall Structure                                            |      |

| 3.3 A       | AA-ResNet Circuit Implementation                                   |      |

|             | 3.3.1 In-memory Convolution SRAM Array Cells                       |      |

|             | 3.3.2 Analog Integrators                                           |      |

|             | 3.3.3 S/H buffers and Ramp Voltage Generators for BN and ReLU      |      |

| 3.4 F       | Performance Evaluation                                             |      |

|             | 3.4.1 Linearity of a Single Hidden Layer                           |      |

|             | 3.4.2 Multi-Layer Verification                                     |      |

|             | 3.4.3 Analysis on Noise and Dynamic Range                          |      |

|             | 3.4.4 Accuracy Evaluation                                          |      |

|             | 3.4.5 Energy BreakdownAccuracy Evaluation                          |      |

| 3.5 (       | Conclusion                                                         | 40   |

| CHAPTER     | 4 A Miniaturized Wireless Neural Recording IC for Motor Prediction | with |

| Near-Infrai | red-Based Power and Data Telemetry                                 | 41   |

| 4.1 I       | ntroduction                                                        | 41   |

| 4.2 \$      | System Overview and Top Circuit                                    |      |

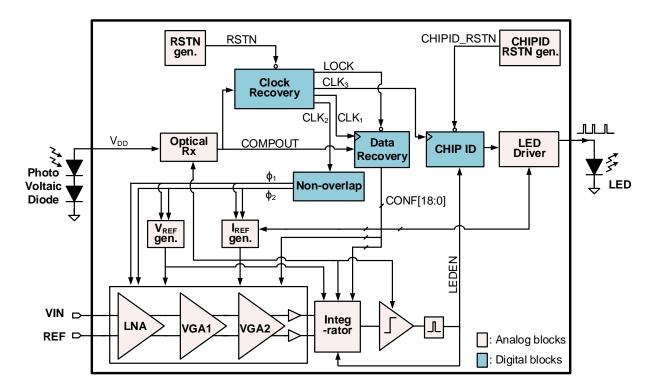

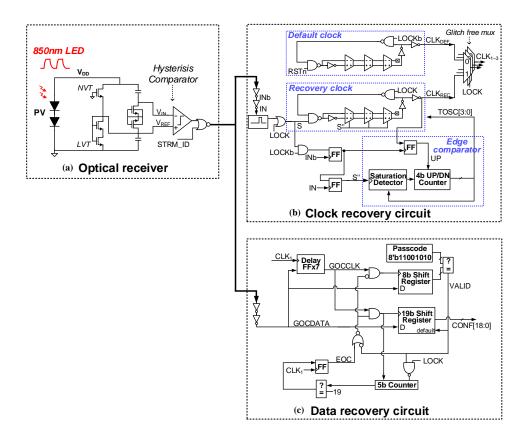

| 4.3 Optical Receiver and Clock and Data Recovery                              | 44 |

|-------------------------------------------------------------------------------|----|

| 4.4 Amplifier and Rectifier based Analog Integrator                           | 47 |

| 4.5 Measurement Results                                                       | 50 |

| 4.6 Conclusion                                                                | 55 |

| CHAPTER 5 A Light Tolerant Neural Recording IC for Near-Infrared-Powered Free |    |

| Floating Motes                                                                | 58 |

| 5.1 Introduction                                                              | 58 |

| 5.2 System Overview and Top Circuit                                           | 59 |

| 5.3 Light Tolerant Amplifer                                                   | 61 |

| 5.4 Flash ADC and Pulse-Counter-based SBP Computing Unit                      | 63 |

| 5.5 Optical Receiver and Remote Gain Control                                  | 65 |

| 5.6 Measurement Results                                                       | 66 |

| 5.7 Conclusion                                                                | 69 |

| CHAPTER 6 Conclusion                                                          | 70 |

| BIBLIOGRAPHY                                                                  | 74 |

# **LIST OF FIGURES**

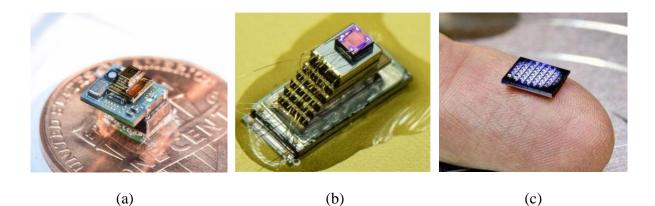

| Figure 1.1 Miniaturized sensor nodes and IoTs (a) Stacked audio sensor node [5], (b) Stacked    |

|-------------------------------------------------------------------------------------------------|

| pressure sensor node [6], (c) IBM 1mm <sup>3</sup> computing platform [7]                       |

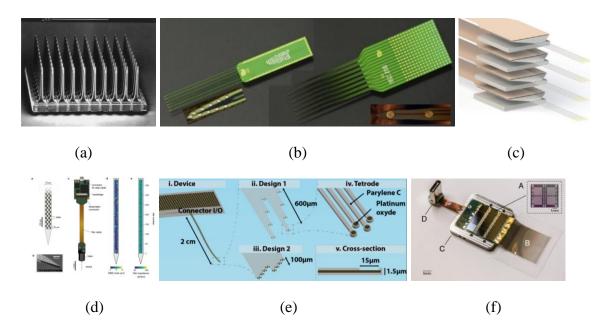

| Figure 1.2 Electrode arrays and neural recording system (a) Utah electrode array [16], (b)      |

| NeuroNexus Michigan Probes [17], (c) Caltech 3D electrodes[18], (d) imec                        |

| Neuropixels [19], (e) Standford NeuroRoots [20], and (f) Neuralink prototype [21]3              |

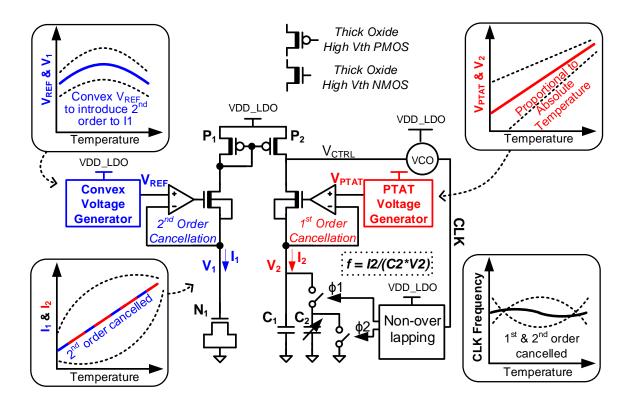

| Figure 2.1 Proposed gate leakage based frequency locked timer7                                  |

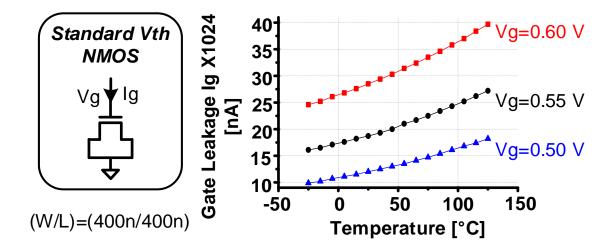

| Figure 2.2 Measured gate leakage current across temperature in 55nm CMOS                        |

| Figure 2.3 (a) Proposed convex voltage generator (b) PTAT voltage generator and (c) simulation  |

| result of first- and second-order cancellation9                                                 |

| Figure 2.4 Diagram of stacked inverter VCO with switched capacitor voltage doubler              |

| Figure 2.5 Measured frequency variation over temperature: (a) without calibration (b) with 2-pt |

| and (c) with 3-pt calibration11                                                                 |

| Figure 2.6 Measured line sensitivity of output clock frequency                                  |

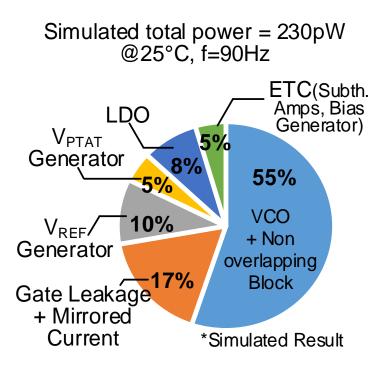

| Figure 2.7 Simulated power breakdown of timer                                                   |

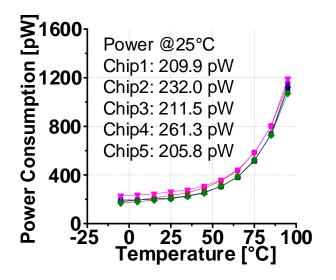

| Figure 2.8 Measured power consumption                                                           |

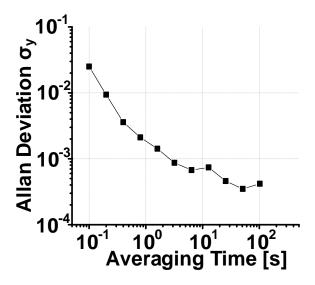

| Figure 2.9 Measured Allan deviation                                                             |

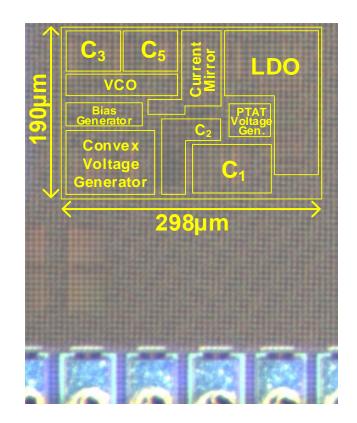

| Figure 2.10 Die Photo                                                                           |

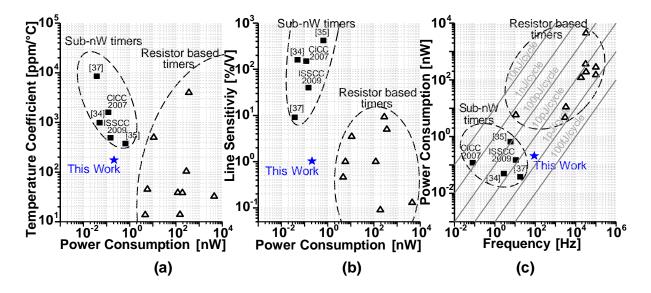

| Figure 2.11 Comparison scatter plots with previous work (best-reported dies): (a) temperature   |

| coefficient (b) line sensitivity and (c) energy per cycle                                       |

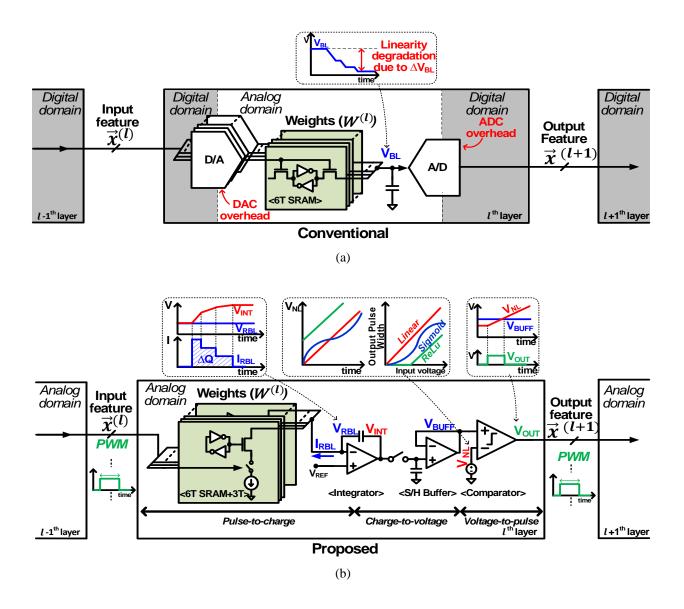

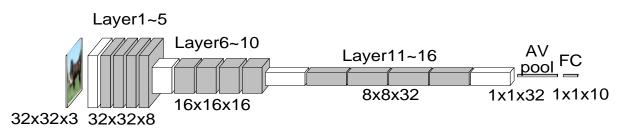

| Figure 3.1 Comparison of (a) conventional approaches with in-memory/mixed-signal computing         |

|----------------------------------------------------------------------------------------------------|

| and (b) proposed all-analog approaches                                                             |

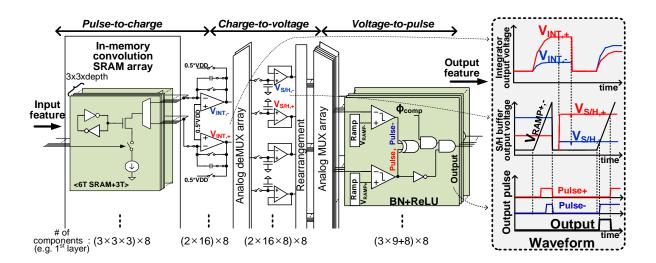

| Figure 3.2 A single layer(L1) structure of proposed AA-ResNet accelerator                          |

| Figure 3.3 Time domain mapping of non-linear voltage                                               |

| Figure 3.4 (a) A diagram of modified ResNet and (b) overall hardware architecture                  |

| Figure 3.5 (a) Circuit structure of in-memory convolution SRAM array cells and (b) diagram of      |

| the shortcut connection                                                                            |

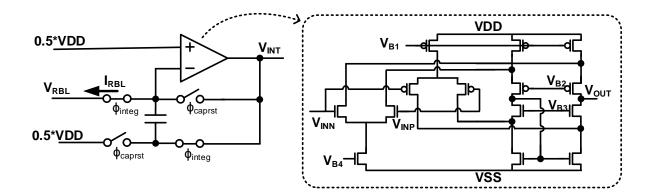

| Figure 3.6 Circuit structure of analog integrator                                                  |

| Figure 3.7 Circuit structure of (a) S/H buffer and (b) ramp voltage generator for BN and ReLU      |

| with tunable gain and offset                                                                       |

| Figure 3.8 (a) Proposed ReLU structure and (b) output waveform                                     |

| Figure 3.9 Linearity simulation result of (a) input pulse to voltage and (b) input pulse to output |

| pulse                                                                                              |

| Figure 3.10 Transient simulation waveform with input pulse width sweep from 0 to 5.12 ns with      |

| 160 ps time step                                                                                   |

| Figure 3.11 (a) A sample SVHN image and (b) Transistor-level SPICE simulation result of            |

| average pooling + FC layers and comparison with Matlab results                                     |

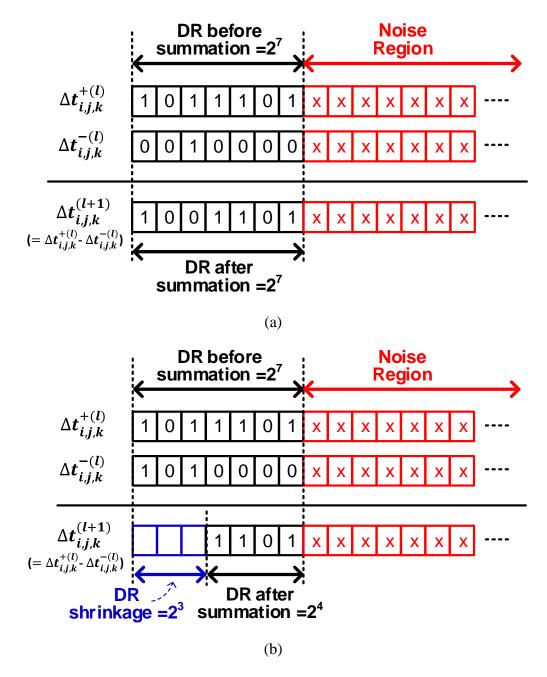

| Figure 3.12 Diagram of effective bit precision activations (a) without dynamic shrinkage (b) with  |

| dynamic shrinkage = $2^3$ after summation                                                          |

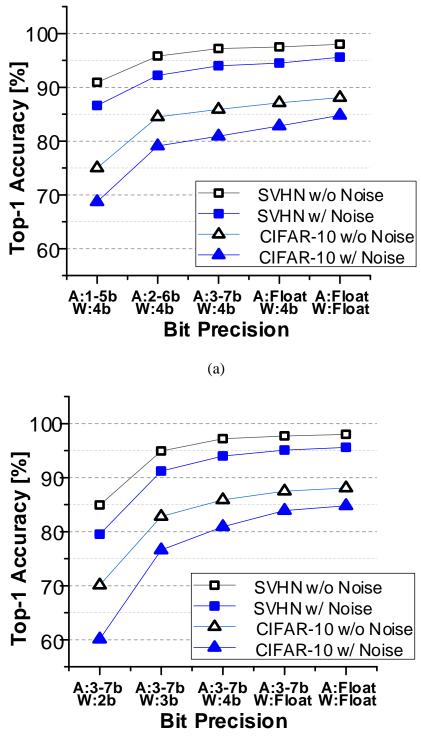

| Figure 3.13 Top-1 accuracy (a) over different bit precisions of activation with 4b-weight and (b)  |

| over different bit precisions of weight with 3~7b activation                                       |

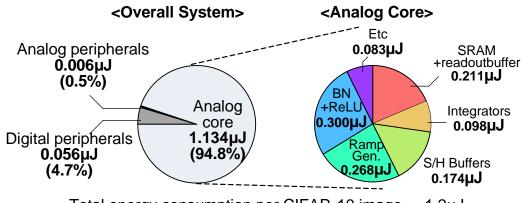

| Figure 3.14 (a) Energy breakdown of AA-ResNet accelerator and (b) energy distribution over         |

| different layers                                                                                   |

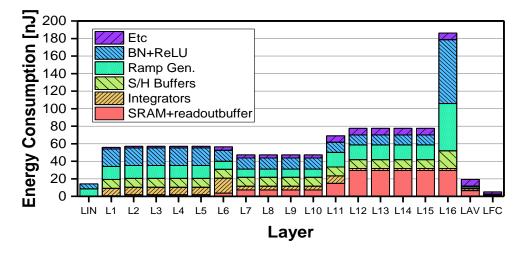

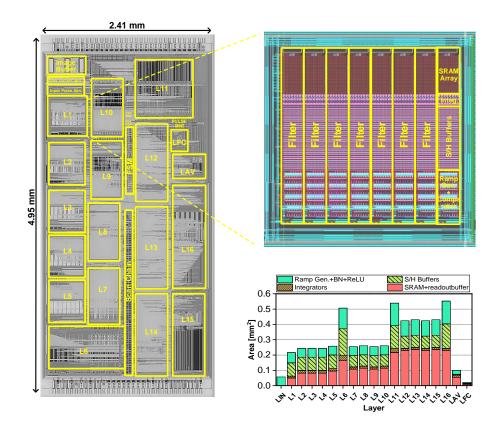

| Figure 3.15 (a) Layout view of the proposed AA-ResNet accelerator, (b) layout view of the 1 <sup>st</sup>  |

|------------------------------------------------------------------------------------------------------------|

| layer, and (c) area distribution over different layers                                                     |

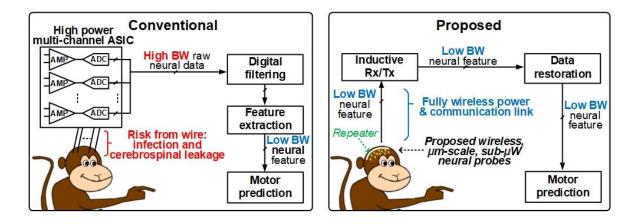

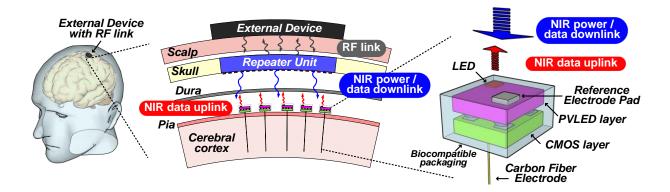

| Figure 4.1 Conventional and proposed neural recording system                                               |

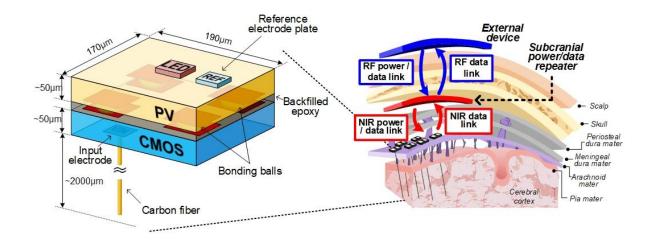

| Figure 4.2 Concept diagram of proposed neural probe and two-step approach for recording and                |

| transmitting neural signals                                                                                |

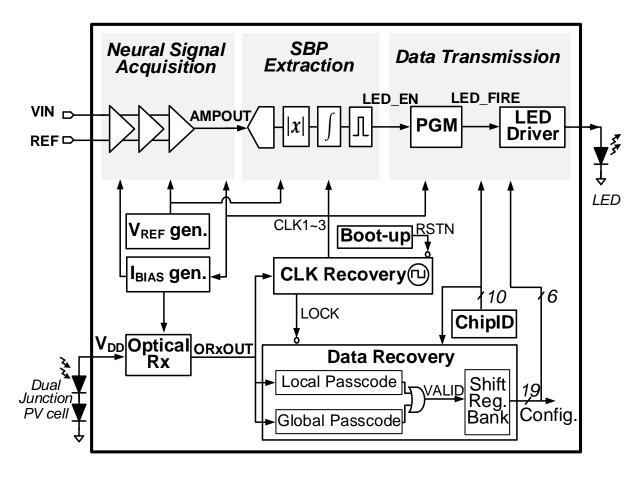

| Figure 4.3 Top-level circuit diagram of the neural recorder                                                |

| Figure 4.4 (a) Optical receiver, (b) clock recovery circuit, and (c) data recovery structure 45            |

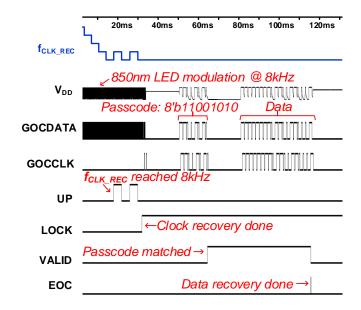

| Figure 4.5 Measured signal diagram during clock and data recovery                                          |

| Figure 4.6 Measured performance of the PV                                                                  |

| Figure 4.7 Amplifier structure                                                                             |

| Figure 4.8 Rectifier based analog integrator structure                                                     |

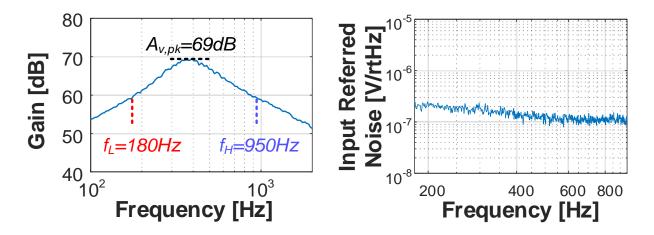

| Figure 4.9 Measured AC gain and input referred noise of amplifier                                          |

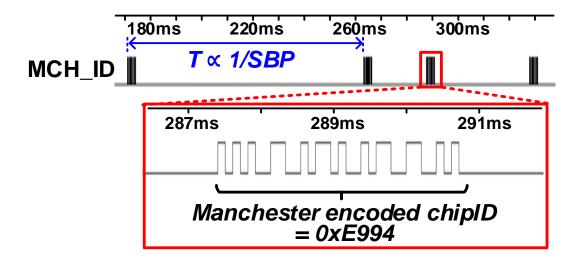

| Figure 4.10 Measured Manchester encoded chipID 50                                                          |

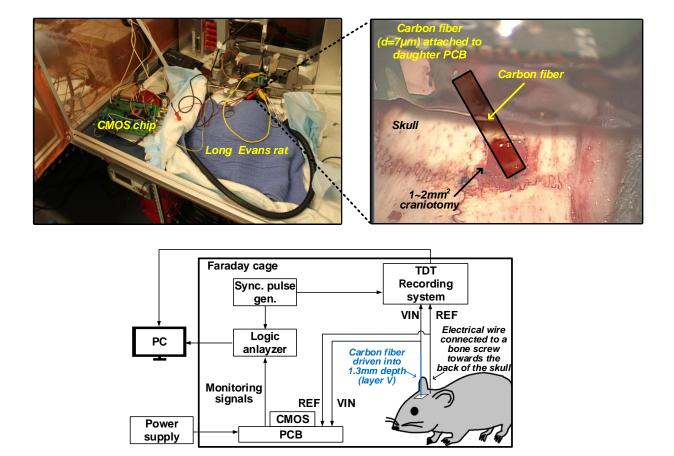

| Figure 4.11 Photo of <i>in vivo</i> testing setup (top left). Carbon fiber mounted to PCB is inserted (top |

| right) and a bone screw was placed at the most posterior portion of the skull.                             |

| Recordings were taken with the IC in parallel with RA16AC headstage, RA16PA pre-                           |

| amplifier, and RX7 Pentusa base station (Tucker-Davis Technologies, Alachua, FL,                           |

| 2.2-7500Hz bandpass filtered) (bottom)                                                                     |

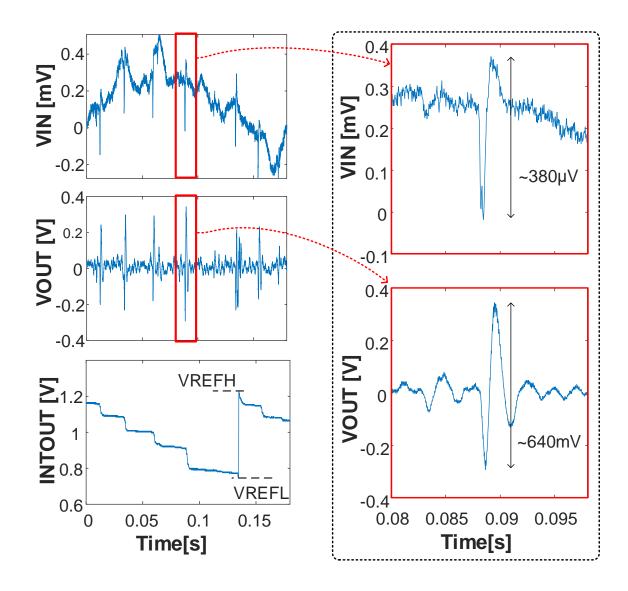

| Figure 4.12 In vivo transient measurement results with rat motor cortex neural signal                      |

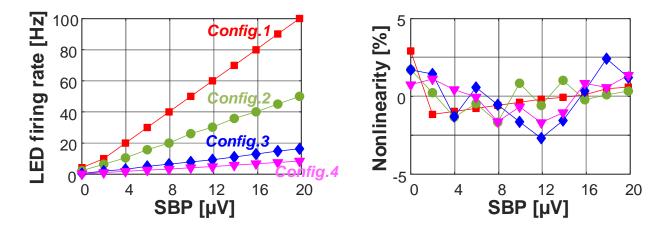

| Figure 4.13 Measured linearity of LED firing rate                                                          |

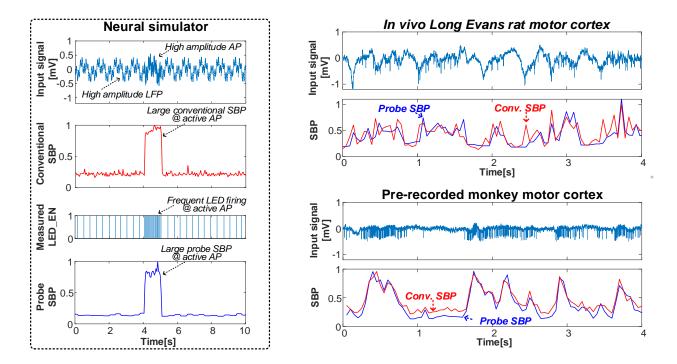

| Figure 4.14 Measured transient waveform from three types of input neural signals                           |

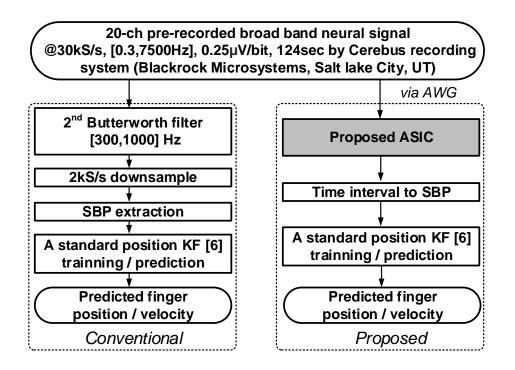

| Figure 4.15 Flow chart of finger position and velocity decoding                                            |

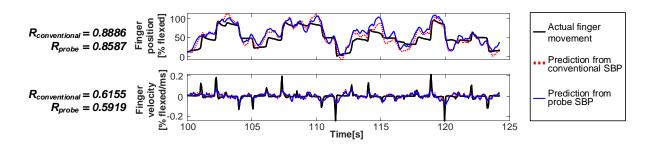

| Figure 4.16 Finger position / velocity decoding result using KF with the probe and conventional |

|-------------------------------------------------------------------------------------------------|

| SBP with pre-recorded 20-channel neural signals of a monkey                                     |

| Figure 4.17 Die photo of the IC in 180nm CMOS                                                   |

| Figure 4.18 Optical setup with the IC wire-bonded with a custom dual-junction GaAs PV 56        |

| Figure 4.19 Structure of switched capacitor based current reference                             |

| Figure 4.20 Structure of digitally controlled delay cell in clock recovery circuit              |

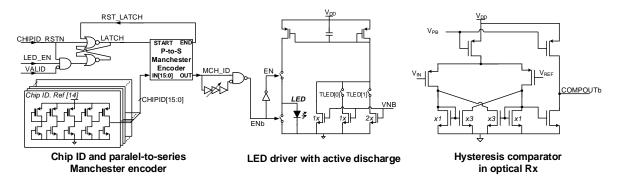

| Figure 4.21 Structure of chipID Manchester encoder, LED driver and hysteresis comparator in     |

| optical receiver                                                                                |

| Figure 5.1 Conceptual illustration of NIR based wireless neural recording motes                 |

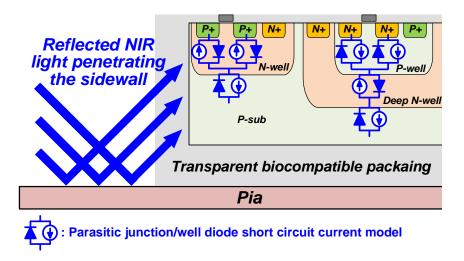

| Figure 5.2 Cross section of the CMOS layer with parasitic diode short circuit currents          |

| Figure 5.3 Top circuit diagram of the CMOS layer                                                |

| Figure 5.4 Simulated light robustness of three different feedback resistors (top) and proposed  |

| light tolerant amplifier (bottom) 61                                                            |

| Figure 5.5 Measured amplifier performance with 850nm light (IRS4, CMVision)                     |

| Figure 5.6 Flash ADC and pulse-counter-based SBP computing unit                                 |

| Figure 5.7 Quantization of absolute amplitude and width from the SBP computing unit             |

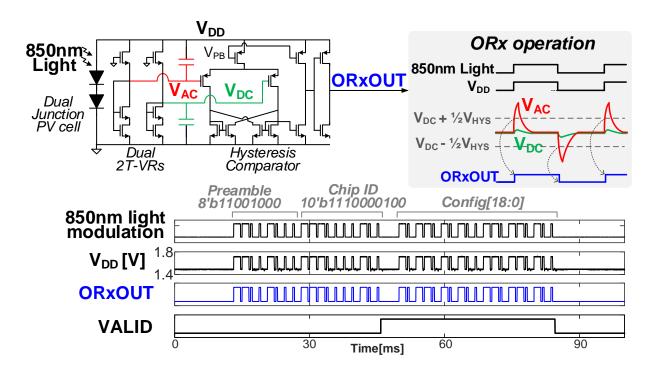

| Figure 5.8 ORx structure and operation (top), and measured selective programming waveforms      |

| from wireless optical setup (bottom) 65                                                         |

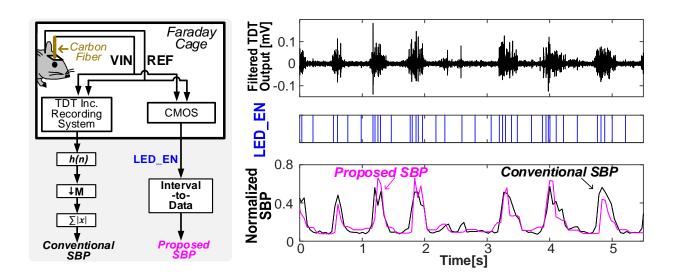

| Figure 5.9 In vivo measurement setup with RA16PA pre-amp and RX7 Pentusa base station from      |

| TDT Inc. (left) and measured waveforms (right)                                                  |

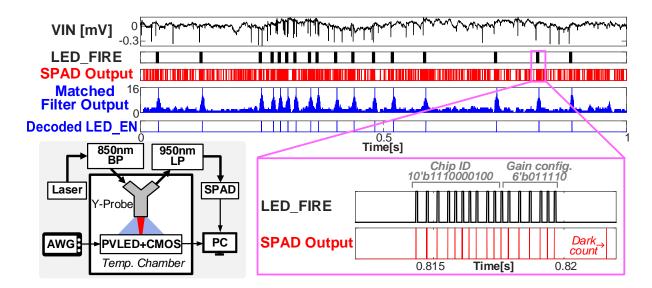

| Figure 5.10 Measured matched filter decoding result (top), and wireless optical setup with NIR  |

| laser (QFLD850200S, Qphotonics) and SPAD (SPDOEMNIR, Aurea) (bottom, left).                     |

|                                                                                                 |

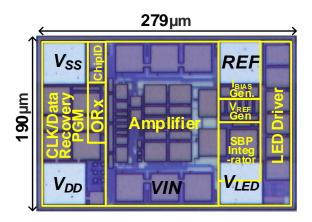

| Figure 5.11 Die photo 67                                                              |

|---------------------------------------------------------------------------------------|

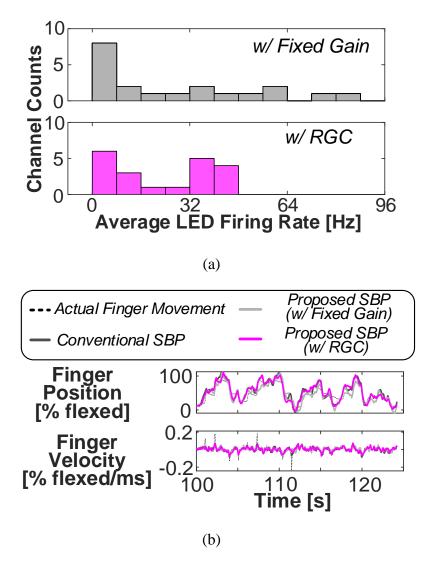

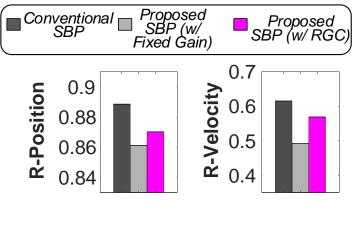

| Figure 5.12 Finger movement decoding result (a) average LED firing rate histogram (b) |

| predicted movement (c) correlation                                                    |

# LIST OF TABLES

| Table 2.1 Comparison table                          |      |  |

|-----------------------------------------------------|------|--|

| Table 3.1 RMS noise from transient noise simulation | . 34 |  |

| Table 3.2 Comparison with state-of-the-art.         | . 39 |  |

| Table 4.1 Comparison table.                         | . 56 |  |

| Table 5.1 Comparison table.                         | . 69 |  |

## ABSTRACT

Internet of Things (IoT) have become omnipresent over various territories including healthcare, smart building, agriculture, and environmental and industrial monitoring. Today, IoT are getting miniaturized, but at the same time, they are becoming more intelligent along with the explosive growth of machine learning. Not only do IoT sense and collect data and communicate, but they also edge-compute and extract useful information within the small form factor. A main challenge of such miniaturized and intelligent IoT is to operate continuously for long lifetime within its low battery capacity. Energy efficiency of circuits and systems is key to addressing this challenge. This dissertation presents two different energy-efficient circuit designs: a 224pW 260ppm/°C gate-leakage-based timer for wireless sensor nodes (WSNs) for the IoT and an energy-efficient all analog machine learning accelerator with 1.2 µJ/inference of energy consumption for the CIFAR-10 and SVHN datasets.

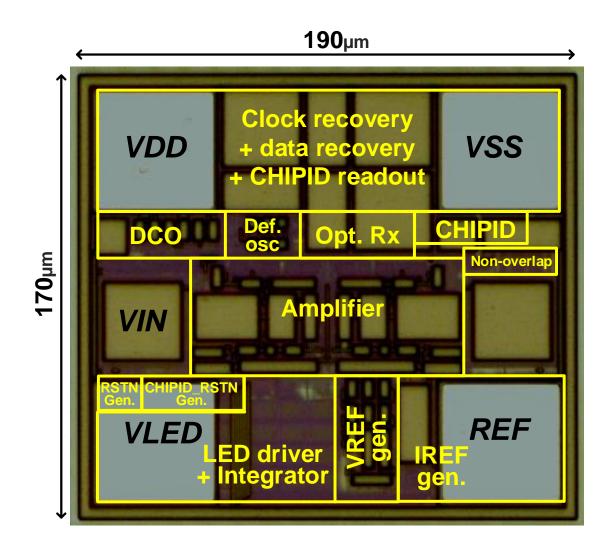

Wireless neural interface is another area that demands miniaturized and energy-efficient circuits and systems for safe long-term monitoring of brain activity. Historically, implantable systems have used wires for data communication and power, increasing risks of tissue damage. Therefore, it has been a long-standing goal to distribute sub-mm-scale true floating and wireless implants throughout the brain and to record single-neuron-level activities. This dissertation presents a  $0.19 \times 0.17$ mm<sup>2</sup>  $0.74\mu$ W wireless neural recording IC with near-infrared (NIR) power and data telemetry and a  $0.19 \times 0.28$ mm<sup>2</sup>  $0.57\mu$ W light tolerant wireless neural recording IC.

## **CHAPTER 1**

## Introduction

#### 1.1 Miniaturized and Intelligent Internet of Things

Beginning from early mainframe computers in the 1950s, the computing platform has evolved to personal computers (PC) in the 1980s, smartphones in the 2000s, and now various kinds of Internet of Things (IoT). Development of complementary metal-oxide-semiconductor (CMOS) technology along with expansion of new hardware/software and increasing user demands for inexpensive and convenient access have driven the computing platform to be less expensive and physically smaller in size. Today, the IoT with smaller physical dimension relative to its predecessors have become ubiquitous over various applications that require seamless monitoring or sensing; e.g., healthcare, smart building, agriculture, and so on. Furthermore, recent research on millimeter-scale wireless sensor nodes [1]-[10] have enabled further shrinkage of IoT size, opening up new applications including medical implants, environmental monitoring, surveillance, and blockchain technology to the supply chain as shown in Fig. 1.1.

Main challenge of the miniaturized sensor nodes and IoT, however, is their limited energy budget from small battery capacity. Since a large number of the miniaturized IoT should be deployed all over different application areas wirelessly, it is infeasible to externally supply power

Figure 1.1 Miniaturized sensor nodes and IoTs (a) Stacked audio sensor node [5], (b) Stacked pressure sensor node [6], (c) IBM 1mm<sup>3</sup> computing platform [7].

to individuals. Therefore, the IoT devices require battery as their power source. However, miniaturization of the system size has also forced the battery size to be shrunk limiting overall system energy budget. For instance, sub-mm<sup>3</sup> Li Thin-film battery has approximately  $10^6 \times$  lower energy capacity compared to the conventional alkaline AA battery with nearly 10 cm<sup>3</sup> of volume [11]. In other words, the miniaturized device using the sub-mm<sup>3</sup> Li Thin-film as a power source should consume only 10nW in average to achieve similar lifetime with the device using AA battery consuming 10mW in average. Therefore, energy-efficient and low power circuits and system design is key to addressing this challenge.

Another recent technological trend has been the explosive growth of deep learning [12] and its wide usage across numerous applications; e.g., self-driving cars, autonomous machines, medicine, entertainment, security, and so on. Along with the proliferation of IoT devices, demand of machine learning accelerators designed for edge computing has increased. Within small form factor and limited energy budget, the intelligent IoT need to not only sense and collect data and communicate, but also edge-compute to perform inference or even training. Therefore, the importance of energy-efficient circuit and system design has grown to meet the demand of increased computational capability of such IoT.

In chapter 2, an ultra-low power timer for wireless sensor nodes (WSNs) for the miniaturized IoT [13] is proposed. In chapter 3, an energy-efficient all analog machine learning accelerator for IoT edge computing [14] is presented.

#### **1.2 True Wireless Neural Recording**

Starting from 1970s, brain machine interfaces (BMI) [15] has been developed with an initial goal of restoring useful function of people who are paralyzed or disabled by neuromuscular disorders, such as spinal cord injury. Nowadays, active research on neural probe arrays have enabled high channel neural recording implants [16]-[21] (Fig. 1.2). However, implantable systems with these probe arrays use wires to connect the arrays to a bulky neural recording application-specific integrated circuit (ASIC). The use of wires and large form factor of system increase potential risks of tissue damage, infection, and cerebrospinal fluid leakage. Since the brain

Figure 1.2 Electrode arrays and neural recording system (a) Utah electrode array [16], (b) NeuroNexus Michigan Probes [17], (c) Caltech 3D electrodes[18], (d) imec Neuropixels [19], (e) Standford NeuroRoots [20], and (f) Neuralink prototype [21].

undergoes micro motion, even flexible wires can still create scraping and form scar tissue, making these systems unsuitable for long-term implantation.

Therefore, miniaturized, and true floating wireless neural recording motes that do minimal damage have been a long-standing goal. Recently, several miniaturized and wireless neural implants have been proposed including near-field RF, ultrasonic, and near-infrared (NIR) based powering and data telemetry [22]-[27]. However, RF-based motes [22]-[23] require 0.5W of transceiver power to operate exceeding the safety exposure limits by  $10\times$  [23], while ultrasonic-based motes remain relatively large in sizes (0.8mm<sup>3</sup>) due to a bulky ultrasound transducer [24]-[25]. On the other hand, NIR-based approach using a photovoltaic (PV) cell and a light-emitting diode (LED) has shown promising wireless implementation shrinking down the mote sizes to 100s of microns [26]-[27]. Several challenges, however, still exist with NIR-based approach. One of the main challenges is its limited energy and area budget. NIR optical power density must be maintained under 190  $\mu$ W/mm<sup>2</sup> due to safety limit of the brain [28], and the total energy that the PV cell can harvest is also limited by its small area (i.e.  $1.5\mu$ W of electrical power from 150  $\mu$ W/mm<sup>2</sup> NIR light with PV size of  $190 \times 204 \mu$ m<sup>2</sup> [28]). Therefore, the energy efficient and highly compact neural recording circuit and system design is key to addressing this challenge.

In chapter 4 and 5, two generations of sub- $\mu$ W and sub-mm wireless neural recording IC for motor prediction with NIR power and data telemetry are proposed [29]-[30].

Lastly, chapter 6 summarizes key contributions of the works presented from chapter 2 to chapter 5 and proposes future directions.

## **CHAPTER 2**

# A Gate-Leakage-based Frequency-Locked Timer for Ultra-Low Power Sensor Nodes with Second-Order Temperature Dependency Cancellation

#### 2.1 Introduction

Wake-up timers are a critical component of wireless sensor nodes (WSNs) for the Internet of Things. Since they are on even when the sensor node is in sleep mode, they must consume extremely low power. In addition, they should ensure high timing accuracy for synchronization between devices and general timekeeping while remaining compact, leading to a highly constrained design space. An RC oscillator [31] or frequency-locked oscillator [32] based on temperature-compensated resistors achieves frequency stability across temperature of <50ppm/°C. However, these approaches consume ~100 nW or more, which far exceeds the power budget of state-of-the-art ultra-low power sensors. Extending these approaches to sub-nW requires extremely large resistors, unacceptably increasing the area and cost. Recently, a switch-resistor based timer achieved a high effective resistance without increasing resistor size and obtained a temperature coefficient (TC) of 13.8 ppm/°C [33]. However, the approach requires large capacitors, and power consumption remains relatively high at 4.7 nW. An alternative to resistor-based timers is gateleakage-based timers; several such timers have been proposed [34]-[35], providing sub-nW power consumption in compact silicon area. However, gate leakage exhibits significant first- and second-order temperature dependence, complicating temperature compensation, and it is also sensitive to the gate voltage. As a result, previous gate leakage timers have TCs in excess of several hundred ppm/°C and line sensitivities (LS) >150%/V. The gate leakage timer in [35] achieves 31 ppm/°C but requires 10-point calibration, and its 660 pW power consumption does not include the power of a required auxiliary temperature sensor. Further, its LS is unacceptably high at 420%/V.

This chapter proposes a 224-pW gate-leakage-based frequency locked timer with first- and second-order temperature dependency cancellation, yielding a TC of 260 ppm/°C across -5 to 95°C. Supply insensitive reference voltage generators and an on-chip low dropout (LDO) regulator decrease LS to 0.93%/V for 1.1–3.3 V, which marks a 150× improvement compared to previous gate-leakage-based timers.

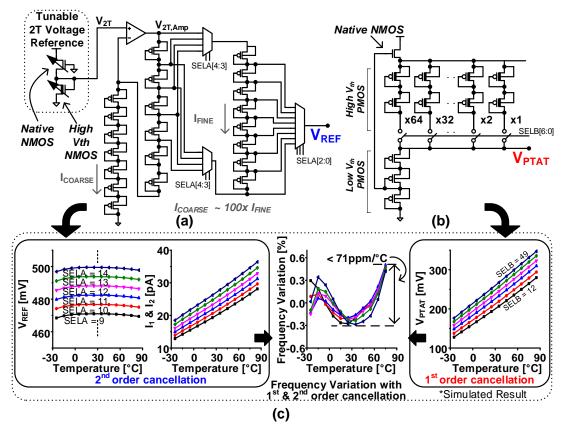

#### 2.2 Gate-Leakage-based Frequency-Locked Timer

The proposed design uses a frequency locked oscillator scheme [32]-[33] in which current  $I_1$ , set by the gate leakage of a standard-V<sub>th</sub> NMOS N<sub>1</sub>, is matched with current  $I_2$ , using modulation of the frequency of a switched capacitor C<sub>2</sub> (Fig. 2.1). The measured temperature dependence of N<sub>1</sub> gate leakage shows both first- and second-order components (Fig. 2.2). It is essential to cancel both components to achieve a good TC.

Figure 2.1 Proposed gate leakage based frequency locked timer.

Figure 2.2 Measured gate leakage current across temperature in 55nm CMOS.

#### **2.3 First- and Second-order Temperature Dependance Cancellation**

In the proposed design, we use two tuning mechanisms. We cancel the first-order dependence by varying  $V_2$  in a proportional to temperature (PTAT) fashion using a voltage reference with tunable temperature dependence (Fig. 2.1, right). This PTAT reference consists of two PMOS diode stacks, each with different threshold voltages and sizes to create a first-order dependence on temperature (Fig. 2.3b). Switches control the high-Vt PMOS size, which tunes the slope of  $V_{PTAT}$  from 0.5 to 0.68%/°C (simulation).

To cancel the second-order dependence, we use a 2T voltage reference, which has intrinsic convex temperature dependence [36] (Fig. 2.3a). However, the convexity of this reference is fixed and is not easily tuned to cancel the second-order dependence of gate leakage. Hence, we leverage the exponential dependence of gate leakage on voltage to provide this tuning mechanism, as follows: First, we remove first-order dependence by tuning the native NMOS and High-Vt PMOS sizes, resulting in  $V_{2T} = V_{2T,0} + \alpha (T-T_0)^2$ . We then amplify  $V_{2T}$ , and a mux structure selects the output voltage  $V_{REF} = V_1 = k_{mux}(V_{2T,0} + \alpha (T-T_0)^2)$  where  $k_{mux}$  varies with the mux selection. Note that this does not change the relative magnitude of the convexity of  $V_1$ . However, gate leakage I<sub>1</sub> is exponentially dependent on  $V_1$ , resulting in  $I_1 \propto \exp(\beta k_{mux}V_{2T,0}) \times \exp(\beta k_{mux}\alpha (T-T_0)^2)$ . Hence,

by changing  $k_{mux}$  (i.e., the mux setting) we can modulate the relative magnitude of the convexity of I<sub>1</sub>, which allows us to cancel the second-order temperature dependence of the gate leakage. Fig. 2.3c shows simulation results of this approach. After both first- and second-order temperature dependencies are canceled, only third- and higher-order terms remain. Finally, the center frequency (0th order) is adjusted by tuning C<sub>2</sub> in Fig. 2.1.

Figure 2.3 (a) Proposed convex voltage generator (b) PTAT voltage generator and (c) simulation result of first- and second-order cancellation.

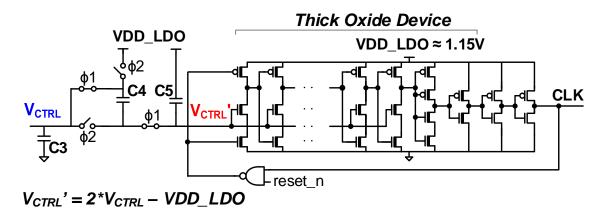

#### 2.4 VCO with Switched Capacitor Voltage Doubler

Two PMOS devices (P<sub>1</sub> and P<sub>2</sub>, Fig. 2.1) implement the current mirror. The devices are high threshold thick-oxide PMOS transistors operating in subthreshold with VDS >5 kT/q, which significantly reduces mismatch between I<sub>1</sub> and I<sub>2</sub>. The low power voltage controlled oscillator (VCO) in Fig. 2.1 provides the timer's output frequency and is composed of stacked high threshold inverters to minimize short circuit current (Fig. 2.4). The voltage range of V<sub>CTRL</sub> across temperature, 0.67-0.9 V, is too narrow and situated at too high a voltage to compensate the VCO frequency across temperature. We double the voltage range and shift it lower using switch capacitor C<sub>4</sub>, obtaining V<sub>CTRL</sub>' with range 0.2-0.65 V. Capacitors C<sub>3</sub>-C<sub>5</sub> also generate the dominant pole of the frequency lock scheme.

Figure 2.4 Diagram of stacked inverter VCO with switched capacitor voltage doubler.

#### 2.5 Line Sensitivity Enhancement

Gate leakage has high voltage sensitivity, leading to strong frequency dependence on supply voltage in previous gate-leakage-based timers. The proposed design addresses this by placing native NMOS transistors in the convex voltage generator and PTAT voltage generator, enabling low line sensitivity (1.3%/V and 2.2%/V, respectively, simulation). An on-chip LDO further reduces supply voltage dependence while consuming only 18 pW (simulation).

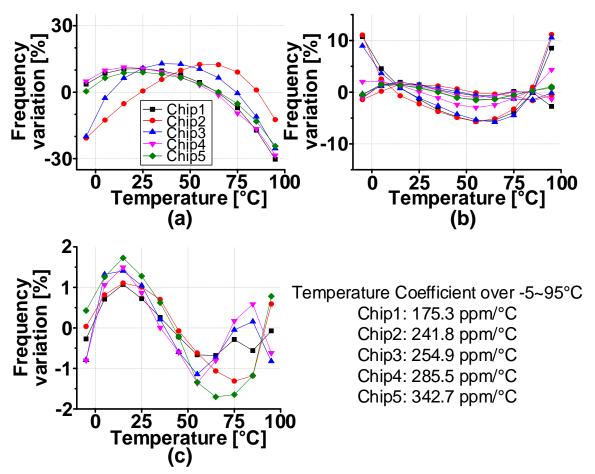

#### 2.6 Measurement Results

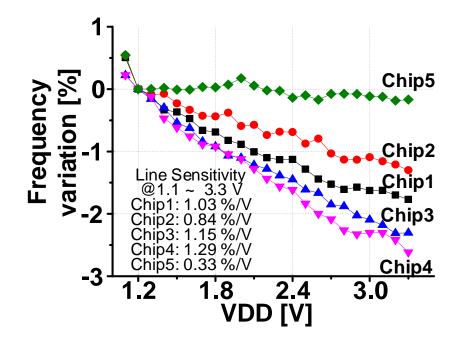

The proposed gate-leakage-based timer was implemented in 55nm CMOS (MIFS C55DDC) in 0.057 mm2. Fig. 2.5 show the measured frequency variation from -5 to 95°C for five typical corner dies. Fig. 2.5a gives results with no tuning, while Fig. 2.5b has 2-pt calibration to cancel first-order dependence. Fig. 2.5c uses the proposed second-order cancelation with 3-pt calibration, yielding measured TCs of 175–343 ppm/°C, which is 5× better than first-order cancelation only. The timer consumes 224 pW at 25°C with 90 Hz output frequency; power increases to 1.2 nW at

95°C (Fig. 2.8). Line sensitivity is 0.33–1.29%/V across 1.1–3.3 V supply voltage for the five dies (Fig. 2.6). Fig. 2.11 compares TC, LS, and energy per cycle to those of previous sub-nW timers and resistor-based timers.

Figure 2.5 Measured frequency variation over temperature: (a) without calibration (b) with 2-pt and (c) with 3-pt calibration.

Figure 2.6 Measured line sensitivity of output clock frequency.

Figure 2.7 Simulated power breakdown of timer.

Figure 2.8 Measured power consumption.

Figure 2.9 Measured Allan deviation.

Figure 2.10 Die Photo.

#### 2.7 Conclusion

The proposed timer is Pareto optimal in terms of TC and LS vs. power among the listed works, enabling a new ultra-low power timer design space. Energy per cycle of 2.49 pJ/cycle is comparable to the best reported among the listed works.

Figure 2.11 Comparison scatter plots with previous work (best-reported dies): (a) temperature coefficient (b) line sensitivity and (c) energy per cycle.

|                         | This<br>Work                       | JSSC<br>2016<br>[37] | JSSC<br>2016<br>[34]                              | JSSC<br>2013<br>[35]      | ISSCC<br>2009<br>(YS. Lin) | CICC<br>2007<br>(YS. Lin) |

|-------------------------|------------------------------------|----------------------|---------------------------------------------------|---------------------------|----------------------------|---------------------------|

| Process [nm]            | 55                                 | 180                  | 65                                                | 130                       | 130                        | 130                       |

| Supply Voltage [V]      | 1.2                                | 1.8/0.6              | 0.5                                               | 0.7 & 1.2                 | 0.6                        | 0.45                      |

| Power [pW]              | 206~261<br>(avg 224 <sup>a</sup> ) | 38 / 4.2             | 30 ~ 50 <sup>b</sup><br>(avg 44 <sup>a</sup> )    | 660 <sup>c</sup>          | 150                        | 120                       |

| Frequency [Hz]          | 90                                 | 18                   | 2.8                                               | 6                         | 11                         | 0.08                      |

| Temp. Coeff. [ppm/°C]   | 175~343<br>(avg 260 <sup>a</sup> ) | 8500<br>/ 21000      | 990~2200 <sup>b</sup><br>(avg 1260 <sup>a</sup> ) | 375<br>(31 <sup>d</sup> ) | 490                        | 1600                      |

| Temp. Range [°C]        | -5 ~ 95                            | -30 ~ 60             | -40 ~ 60                                          | -20 ~ 60                  | 0~90                       | 0 ~ 80                    |

| Line Sensitivity [%/V]  | 0.33~1.29<br>(avg 0.93ª)           | 9.1 / 240            | 160                                               | 420                       | 40                         | 150                       |

| Energy/cycle [pJ/cycle] | 2.49                               | 2.1 / 0.23           | 15.8                                              | 110                       | 13.6                       | 1500                      |

| Area [mm <sup>2</sup> ] | 0.057                              | 0.18                 | 0.026                                             | 0.015                     | 0.02                       | 0.0005                    |

| # of reported dies      | 5                                  | 1                    | 5                                                 | 1                         | 1                          | 1                         |

Table 2.1 Comparison table

a. Average over multiple samplesb. Calculated from Fig15.

c. Power consumption without a temperature sensor d. 10 point calibration with a temperature sensor

## **CHAPTER 3**

## An Energy-Efficient All-Analog ResNet Accelerator

#### **3.1 Introduction**

The development of machine learning hardware, along with deep learning algorithms, has allowed significant breakthroughs in a number of areas, including image classification, motion detection, and speech recognition. The proliferation of IoT devices has increased the demand of machine learning accelerators designed for edge computing and has reinforced the importance of energy efficiency of such accelerators. Most notably, the vast amount of energy consumed by frequent memory access [38]to load data (weights, features, and parameters) during inference must be reduced to meet the limited energy budget of edge computing. Recently, various in-memory and mixed-signal approaches [39]-[47] have attempted to address this issue and reduce energy consumption by replacing frequent memory read accesses and digital computations with inmemory and analog computations. In addition, recent studies have proposed modified training methods for mixed-signal-based accelerators with low bit precision [48] and in-situ methods for minimizing accuracy degradation due to process variation [49]. However, all of these approaches include digital-to-analog converters (DAC) and analog-to-digital converters (ADC) at the front and back of each hidden layer to store and broadcast features in digital representation [41]-[48] (Fig. 3.1a). Further, they implement the required nonlinear (NL) functions in the digital domain

[45]. The DACs/ADCs are energy bottlenecks, especially when high precision of weight or activation is required. The energy overhead gets even worse when implementing deep convolutional neural networks (CNNs) [50] that consist of many layers. Hence, prior in-memory or mixed-signal designs have been largely restricted to simple shallow networks. Other approaches implementing binarized CNN (BNN) [51] in a mixed-signal domain have been proposed using XNOR [52]-[53] for multiplication and charge-sharing techniques for addition [54]-[56]. BNN has the benefit of reducing computation complexity to a single bit, and as such, these mixed-signal accelerators reduce the DAC and ADC energy overhead since they only have a single bit precision for both weights and activations. However, the BNN works well only for moderately sized networks (e.g., AlexNet [57] and nine-layer networks with 328 KB [55]/ 295 KB [56] of weights) and has a critical limit on the scalability to support very large networks that are difficult to train with binary weights.

To address these challenges, this chapter introduces the first multi-layer (total, 18), all analog NN accelerator in 28-nm CMOS with 32.2 KB of weight storage, implementing not only convolution but also NL function, storage of value for subsequence use, and routing between layers all in the analog domain. Weights and activations are in 4-bit and 3-7-bit precision, respectively, thereby offering significantly better precision compared to BNNs. This work makes the following contributions:

• Energy-efficient all-analog structure without any DAC or ADC overhead between hidden layers (Fig. 3.1b): (1) activations are represented in the pulse-width domain with 3-7 bit precision; (2) convolution is performed using analog integration in the charge domain on the bit-lines to convert to voltage using a charge integrating amplifier to represent the activation output; (3) activation values are stored and broadcasted in the voltage domain by sampleand-hold (S/H) buffers; (4) NL functions (such as sigmoid and recta-linear) are performed while transforming the voltage domain back to the pulse-width domain using a simple comparator and a purposefully shaped voltage ramp; and (5) resulting output pulses are then routed to subsequent layers for their activation or to the final inference outputs.

• Fully pipelined structures (18 layers) for a fast throughput rate of 325K image/sec with CIFAR-10 and SVHN datasets [58]-[59], which is more than 830× faster than conventional mixed-signal approaches [55]-[56].

• Energy consumption per inference of 1.2  $\mu$ J over CIFAR10 and SVHN datasets, which is  $3 \times$  lower than prior mixed-signal approaches [55]-[56].

• The first implementations of a deep ResNet [60]-[61] fully in the analog domain including convolution, batch normalization (BN), rectified linear units (ReLU), average pooling and fully-connect (FC) layer.

• Linearity enhancement of analog convolution by maintaining a constant read bit line (RBL) voltage.

• Evaluation of linearity, noise, effective bit precision, accuracy, and energy efficiency of the proposed accelerator using transistor-level SPICE simulation and Matlab.

The rest of the chapter describes the proposed AA-ResNet accelerator and implementation details and provides an evaluation and conclusion.

Figure 3.1 Comparison of (a) conventional approaches with in-memory/mixed-signal computing and (b) proposed all-analog approaches.

#### 3.2 Main Concept of the AA-ResNet

In this section, we first describe the main concept of the AA-ResNet with analog operations of a single layer. Then we present the overall architecture of the AA-ResNet accelerator.

#### **3.2.1** Convolution in Pulse-to-Charge Domain

For every layer, the input activations are represented in the pulse-width domain as shown in Eq (1):

$$x_{i,j,d}^{(l)} = \Delta t_{i,j,d}^{(l)}$$

(1)

where  $x_{i,j,d}^{(l)}$  is the input activation value of the *i*-th row, *j*-th column, *d*-th depth of *l*-th layer, and  $\Delta t_{i,j,d}^{(l)}$  is the corresponding pulse width.

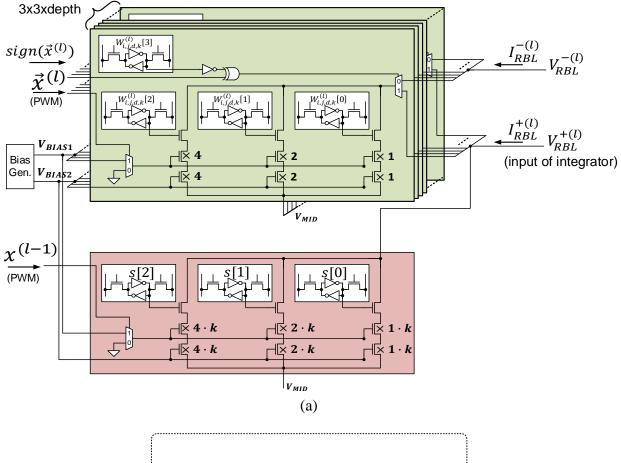

In the proposed analog convolution, the weights of kernels,  $w_{i,j,d,k}^{(l)}$ , represented by Eq (2), are the product of the 4-bit sign-and-magnitude digital values  $W_{i,j,d,k}^{(l)}$  stored in the 6T SRAM arrays and the weight control DC current  $I_{LSB}^{(l)}$  that charges capacitors in the analog integrators (see Fig. 3.2). In Eq (2), *k* represents the kernel index.

$$W_{i,j,d,k}^{(l)} = W_{i,j,d,k}^{(l)} \cdot I_{LSB}^{(l)}$$

(2)

Figure 3.2 A single layer(L1) structure of proposed AA-ResNet accelerator.

The input activation value (i.e., pulse width) determines the on-time of the DC current  $I_{LSB}^{(l)}$ in Eq (2). The accumulated charge is proportional to the DC current level  $I_{LSB}^{(l)}$ , the stored weight value, and the time period the current is turned on (i.e., the input pulse width). Therefore, the accumulated charge represents the multiplication of the input and weight. Multiple (e.g.,  $3\times3\times d$  as shown in Fig. 3.2) wires are shorted together at the input of an analog integrator, which merges all of the charge flowing through the tied wires. Thus, the total integrated charge is equivalent to the convolution output, as shown in Eq (3a) and (3b). Because the DC current has only a single polarity (pull down), a pair of the integrators integrate charge for the positive and negative convolution value separately; Eq (3a) and (3b).

$$Q_{i,j,k}^{+(l)} = \sum_{d} \sum_{j'=1,2,3} \sum_{i'=1,2,3} \left| W_{i',j',d,k}^{(l)} \right| \cdot I_{LSB}^{(l)} \cdot \Delta t_{i+i'-2,j+j'-2,d}^{(l)}$$

(3a)

$$sign(W_{i',j',d,k}^{(n)}) \ge 0$$

$$Q_{i,j,k}^{-(l)} = \sum_{d} \sum_{j'=1,2,3} \sum_{i'=1,2,3} \left| W_{i',j',d,k}^{(l)} \right| \cdot I_{LSB}^{(l)} \cdot \Delta t_{i+i'-2,j+j'-2,d}^{(l)}$$

(3b)

$$sign(W_{i',j',d,k}^{(n)}) < 0$$

$$y_{i,j,k}^{(l)} = Q_{i,j,k}^{+(l)} - Q_{i,j,k}^{-(l)}$$

(3c)

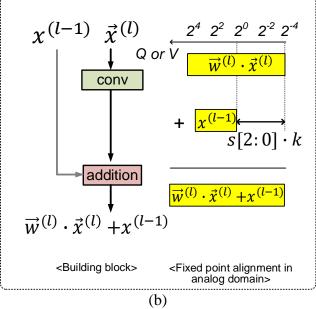

The final convolution result  $y_{i,j,k}^{(l)}$  is obtained by the difference of charge accumulated in the capacitors of a pair of integrators as in Eq (3c). The positive and negative convolution results  $Q_{i,j,k}^{+(l)}$  and  $Q_{i,j,k}^{-(l)}$  are separately stored in the form of electric charge or voltage, while subtraction for  $y_{i,j,k}^{(l)}$  is performed in the pulse domain after voltage-to-pulse conversion as explained in section 3.2.3. In the proposed design, we also implement the addition of convolution results with the bypassed input activations. This feedforward shortcut is the key idea of ResNet [60]-[61] that improves accuracy of very deep networks through residual learning. The shortcut connection of ResNet,  $y_{i,j,k}^{(l)} = \vec{w}^{(l)} \cdot \vec{x}^{(l)} + x_{i,j,k}^{(l-1)}$  is also calculated in the charge domain by tying the 6T SRAM arrays and current path for  $x_{i,j,k}^{(l-1)}$  to the input of the integrators. The detailed circuit implementation of residual learning is discussed in section 3.3.1.

#### 3.2.2 Sampling and Holding in Charge-to-Pulse Domain

The convolution results are stored in the analog (charge) domain and broadcasted at the proper timing to the NL function blocks and the next layers. The charge on the capacitors (Fig. 3.1) for the integrator pairs  $Q_{i,j,k}^{+(l)}$  and  $Q_{i,j,k}^{-(l)}$  can be directly converted into the voltage level  $V_{INT} {}^{+(l)}_{i,j,k}$  and  $V_{INT} {}^{-(l)}_{i,j,k}$ , respectively, as in Eq (4a) and (4b), since the analog integrators hold the bottom plate of the integrator capacitors to a constant voltage of  $\frac{1}{2} \cdot V_{DD}$ . The voltages  $V_{INT} {}^{+(l)}_{i,j,k}$  and  $V_{INT} {}^{-(l)}_{i,j,k}$  are sampled when the charge integration is complete. The buffers hold the sampled voltage to be fed into the NL block (Fig. 3.2).

$$V_{INT} {}^{+(l)}_{i,j,k} = \frac{1}{c} \cdot Q {}^{+(l)}_{i,j,k} + \frac{1}{2} \cdot V_{DD}$$

(4a)

$$V_{INT} \frac{-(l)}{i,j,k} = \frac{1}{C} \cdot Q \frac{-(l)}{i,j,k} + \frac{1}{2} \cdot V_{DD}$$

(4b)

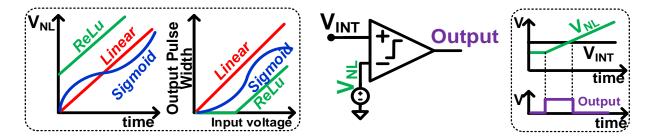

#### 3.2.3 NL function in Voltage-to-Pulse Domain

In the proposed approach, NL function is performed in the analog domain, converting the convolution output from voltage to the pulse-width domain (Fig. 3.1). In the NL block, a ramp voltage, which monotonously rises in time, is compared with  $V_{INT} {}^{+(l)}_{i,j,k}$  and  $V_{INT} {}^{-(l)}_{i,j,k}$  using a comparator. The binary output of the comparator encodes the NL function value in the pulse-width domain (Fig. 3.3).

Figure 3.3 Time domain mapping of non-linear voltage.

Various non-linear functions such as sigmoid and ReLU can be realized by properly shaping the ramp voltage that monotonously rises with a non-constant slope. In the proposed design, ReLU with batch normalization (BN) is implemented using the ramping voltages  $V_{RAMP,k}^+$  and  $V_{RAMP,k}^-$  generated by the ramp voltage generator structure discussed in section 3.3.3.

$$V_{RAMP,k}^{+}\left(\Delta t_{i,j,k}^{+(l)}\right) = V_{INT} \,_{i,j,k}^{+(l)} \tag{5a}$$

$$V_{RAMP,k}^{-}(\Delta t_{i,j,k}^{-(l)}) = V_{INT} \frac{-(l)}{i,j,k}$$

(5b)

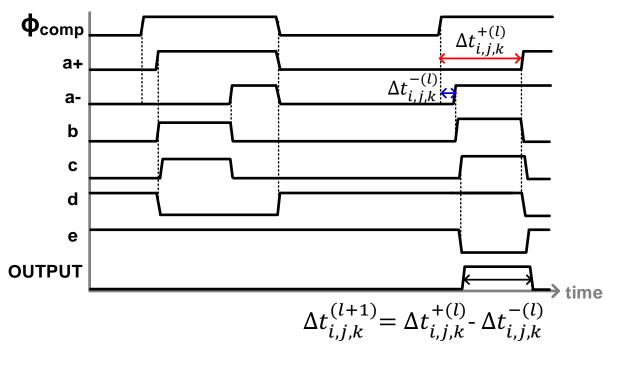

We define  $\Delta t_{i,j,k}^{+(l)}$  and  $\Delta t_{i,j,k}^{-(l)}$  as the time between the start of the comparison and the point where  $V_{RAMP,k}^+$  ( $V_{RAMP,k}^-$ ) exceeds  $V_{INT} _{i,j,k}^{+(l)}$  ( $V_{INT} _{i,j,k}^{-(l)}$ ).

$$\Delta t_{i,j,k}^{(l+1)} = \begin{cases} \Delta t_{i,j,k}^{+(l)} - \Delta t_{i,j,k}^{-(l)}, & \Delta t_{i,j,k}^{+(l)} \ge \Delta t_{i,j,k}^{-(l)} \\ 0, & \Delta t_{i,j,k}^{+(l)} < \Delta t_{i,j,k}^{-(l)} \end{cases}$$

(6)

Using the logic gates in Fig. 3.1, the final output pulse width  $\Delta t_{i,j,k}^{(l+1)}$  is obtained by the difference between  $\Delta t_{i,j,k}^{+(l)}$  and  $\Delta t_{i,j,k}^{-(l)}$  as in Eq (6), realizing ReLU. Note that until this point, the negative and positive convolution results are separately maintained. This final output pulse width  $\Delta t_{i,j,k}^{(l+1)}$  is streamed into the next layer representing the input activation  $x_{i,j,k}^{(l+1)}$  as in Eq (1).

#### 3.2.4 Overall Structure

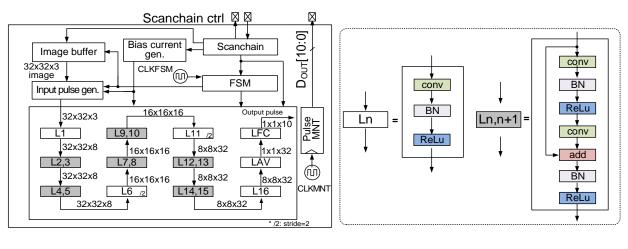

The proposed accelerator implements a modified ResNet [58]-[59] that consists of 16 convolution + BN + ReLU layers, an average pooling layer, and a fully connected (FC) layer as shown in Fig. 3.4a. The layers colored in grey in Fig. 3.4a have feedforward shortcut connections that are unique to ResNets.

The overall accelerator architecture is shown in Fig. 3.4b. The input image of  $32 \times 32 \times 3(RGB)$  pixels is loaded to image buffers implemented with 6912 bytes of compiled SRAM. The input image buffers hold two images for ping-pong buffering. An input image is divided into 64 sub-images of  $3 \times 18 \times 3$  pixels, and each of them is fetched into the input pulse generator in each 48-ns operation cycle. From the input pulse generator to the last FC layer, the entire ResNet datapath of 19 layers is fully pipelined to generate classification output at a very high throughput of one image per 64 cycles (64×48 ns) or 325,520 images/s, which is 830× faster

than reported in [55]-[56]. The final output pulses from ten channels of the FC layer are monitored by the TDC-based pulse monitor block to find the channel number with the longest pulse width. The channel index of the longest pulse width is the inferred image class number processed by the AA-ResNet. Trained weights and parameters are loaded to the accelerator via a scan-chain block (registers) before inference starts. The 48-ns operation cycle is composed of 24 clock cycles generated by an interal 500-MHz on-chip ring oscillator (included in the power estimation).

**(b)**

Figure 3.4 (a) A diagram of modified ResNet and (b) overall hardware architecture.

### **3.3 AA-ResNet Circuit Implementation**

This section presents the implementation details of various components, including the inmemory convolution SRAM array cells, integrators, S/H buffers, and NL function blocks.

#### **3.3.1 In-memory Convolution SRAM Array Cells**

Fig. 3.5 shows in-memory convolution SRAM array cells with 3T-readout buffers that generate current proportional to the magnitude of the weight. Stacked NMOS transistors offer tolerance to  $V_{DS}$  variation, generating linear currents. The MSB of the weight (sign) selects one of the current-conducting paths.

The average pooling and FC layers are also implemented with in-memory SRAM array cells and integrators. In the average pooling layer, constant weights are stored in arrays.

The convolution layers with residual learning (i.e., L2,3 and L4,5 in Fig. 3.4) require an addition block, as shown at the bottom of Fig. 3.5. In the addition block, instead of weight, a scaling factor, s[2:0], is stored in the SRAM cells. This is for aligning the fixed point of the convolution results and the input of the previous layer. Although activations are in the analog domain, we must consider their effective fixed-point representation (Fig. 3.5). The scaling factors vary over different training datasets and layers.

Figure 3.5 (a) Circuit structure of in-memory convolution SRAM array cells and (b) diagram of the shortcut connection.

### 3.3.2 Analog Integrators

The analog integrators are composed of a complementary folded cascode amplifier [62] with an auto-zeroing scheme [63] to cancel offset (Fig. 3.6). The amplifier holds the RBL voltage constant at 0.5 V =  $V_{DD}/2$ , and this further improves the linearity of the 3T-readout buffer (Figs. 3.2 & 3.5) by holding V<sub>DS</sub> of the NMOS devices constant. Linearity does degrade as the output voltage approaches the upper headroom of the amplifier, which is ~0.8 V. Therefore, in the proposed design, we only use an integrator output range of 0.5–0.75 V.

To fully utilize the output voltage range of the integrator,  $I_{LSB}^{(l)}$  in the in-memory convolution SRAM array block is determined based on the maximum value of the sum of the positive/negative parts of each convolution layer during off-line training. In addition, scaling of  $I_{LSB}^{(l)}$  includes compensation of the final pulse output  $\Delta t_{i,j,k}^{(l)}$  scaling from the previous layer for subtraction of two pulse widths,  $\Delta t_{i,j,k}^{+(l-1)}$  and  $\Delta t_{i,j,k}^{-(l-1)}$  (Eq 6). Note that the reduced pulse width can be recovered in the pulse-to-charge domain by scaling  $I_{LSB}^{(l)}$ ; however, the dynamic range issue still remains in this step. The impact of pulse-width reduction and limited dynamic range is discussed in section 3.4.3.

Figure 3.6 Circuit structure of analog integrator.

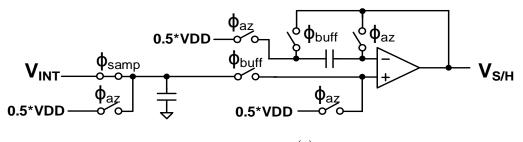

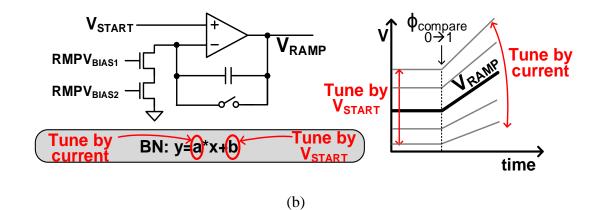

### 3.3.3 S/H buffers and Ramp Voltage Generators for BN and ReLU

The S/H buffer samples the integrator output voltage on a capacitor after the integrated voltage is settled. (Fig. 3.7a) The sampled voltage is buffered by an analog buffer for several operation cycles since the voltage (convolution result) can be reused for multiple convolution operations. An FSM controls both the analog deMUX arrays between the integrator pairs and S/H buffers and the analog MUX arrays between the S/H buffers and comparator pairs (Fig. 3.2).

(a)

Figure 3.7 Circuit structure of (a) S/H buffer and (b) ramp voltage generator for BN and ReLU with tunable gain and offset.

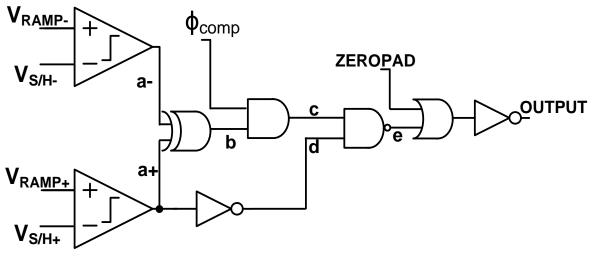

The ramp voltage generator in Fig. 3.7b, used for non-linear voltage (BN+ReLU) generation, has a similar structure as the analog integrator except is employs a 2T-NMOS-based always-on current rather than a 3T-NMOS-based readout buffer. The slope of the ramp signal is determined by the DC current level, which corresponds to the gain of the BN function. In addition, the bias of BN can be tuned with  $V_{START}$ , which is the starting voltage level of  $V_{RAMP}$ . A pair of ramp voltage generators share the DC current level (BN gain) but have separate bias voltages,  $V_{START}^+$  and  $V_{START}^- = 1V - V_{START}^+$ , allowing for identical BN to be applied separately to positive and negative convolution results.  $V_{TART}^+$  and  $V_{TART}^-$  are generated from a diode-stacked ladder. Continuous comparators evaluate  $V_{RAMP}^+ / V_{RAMP}^-$  against buffered voltage pairs, generating a rising edge when  $V_{RAMP}^+$  and  $V_{RAMP}^-$  cross the buffered voltage pairs. Finally, ReLU is performed by passing these pulses through the logic shown in Fig. 3.8a. In the waveform in Fig. 3.8b, the final output pulse is generated when  $\Delta t_{i,j,k}^{+(1)} \ge \Delta t_{i,j,k}^{-(1)}$  with the pulse width of  $\Delta t_{i,j,k}^{(l+1)} = \Delta t_{i,j,k}^{+(l)} - \Delta t_{i,j,k}^{-(l)}$ . If this inequality is not met, the output pulse width is zero (ReLU).

(a)

(b)

Figure 3.8 (a) Proposed ReLU structure and (b) output waveform.

### **3.4 Performance Evaluation**

### 3.4.1 Linearity of a Single Hidden Layer

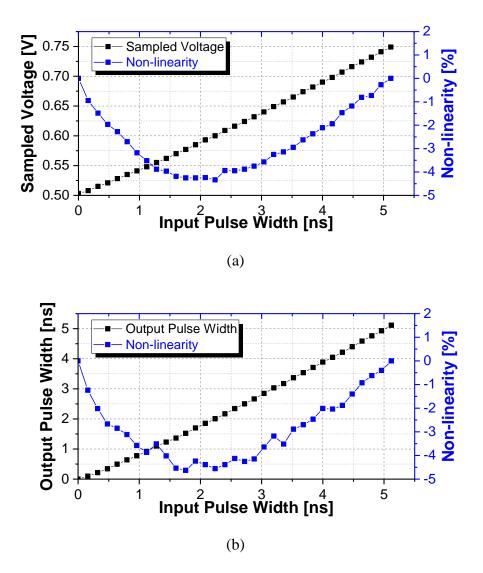

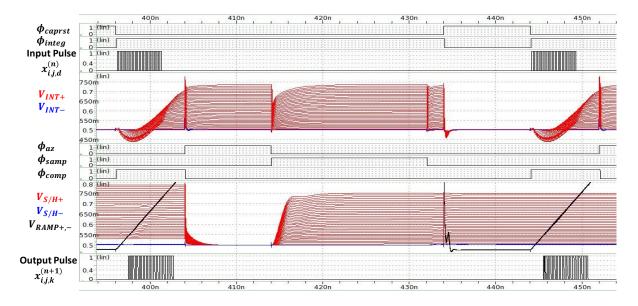

A single layer including in-memory convolution SRAM arrays, integrators, S/H buffers, ramp generators, and the BN+ReLU block is simulated in transistor-level SPICE simulation. Nonlinearity is measured by sweeping the input pulse width of the parallel channels of a single convolution kernel from 0 to 5.12 ns with a 160 ps time step (Figs 3.9 & 3.10).

Figure 3.9 Linearity simulation result of (a) input pulse to voltage and (b) input pulse to output pulse.

Figure 3.10 Transient simulation waveform with input pulse width sweep from 0 to 5.12 ns with 160 ps time step.

Thanks to the constant RBL voltage and stacked readout buffers, the nonlinearity incurred in the convolution SRAM arrays and analog integrators is limited to 4.5% in the worst case (Fig. 3.9a). This percentage is calculated by normalizing the difference between the output value and its ideal value to the full output range (250 mV). The nonlinearity in the voltage-to-output pulse domain is negligible compared to the nonlinearity from integrators, and hence the total nonlinearity in a single layer (input pulse to output pulse) is < 4.8%. This nonlinearity characteristic can be monitored outside of the chip and modeled in the offline training to further improve accuracy.

### **3.4.2** Multi-Layer Verification

Multi-level operation is verified by co-simulation using transistor-level SPICE simulation of the analog layers and VCS for the synthesized logics simultaneously. A sample image is loaded to the input image buffer, and the output pulse width of each layer is compared with output features from Matlab to ensure correct functionality. In Fig. 3.11, the transistor-level SPICE simulation results of the average pooling and FC layer match well with the output feature obtained from Matlab.

After validating the individual components in SPICE simulations, we employ Verilog-A models of analog components to reduce the simulation time and fully verify the wiring and timing of the full system with all of the layers.

| 1  | \   |

|----|-----|

| 1  | a ) |

| ١. | aı  |

| •  | /   |

| Class | SPICE sim.<br>waveform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Pulse width<br>[ps]<br>(SPICE) | Normalized<br>pulse width<br>(SPICE) | Normalized<br>output<br>feature<br>(Matlab) |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--------------------------------------|---------------------------------------------|

| 0     | 130H<br>Booe<br>600e<br>400e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 302.81                         | 0.5117                               | 0.4943                                      |

| 9     | 1 (M)<br>BODH<br>400m<br>400m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.00                           | 0.0000                               | 0.0000                                      |

| 8     | L (3H)<br>8006<br>1006<br>1006<br>1006                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 591.83                         | 1.0000                               | 1.0000                                      |

| 7     | L Cini I<br>Ilochi<br>400m<br>400m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0.00                           | 0.0000                               | 0.0000                                      |

| 6     | 1 (M)<br>100e<br>100e<br>100e<br>100e<br>100e<br>100e<br>100e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.00                           | 0.0000                               | 0.0000                                      |

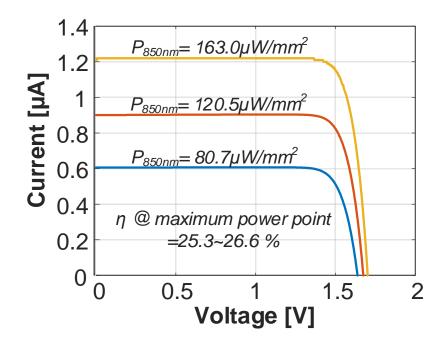

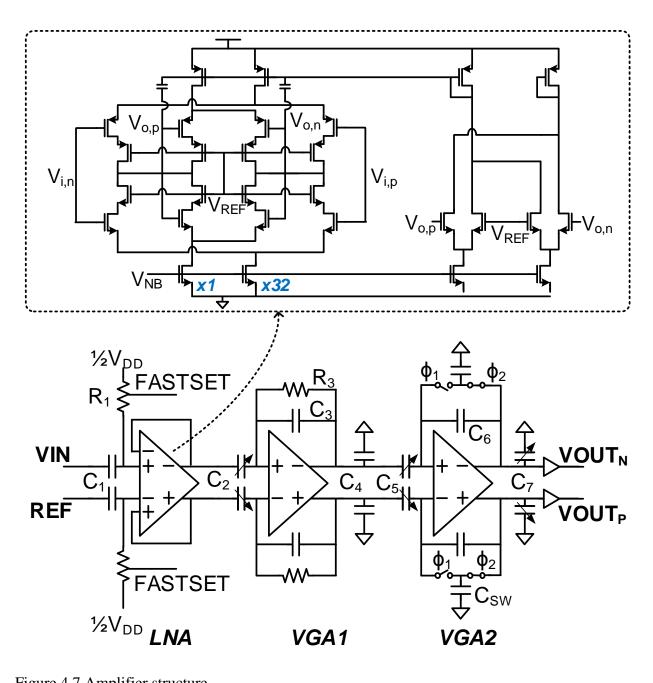

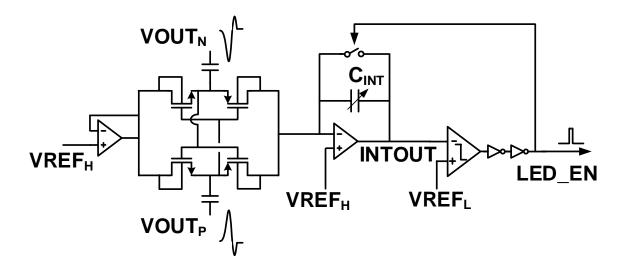

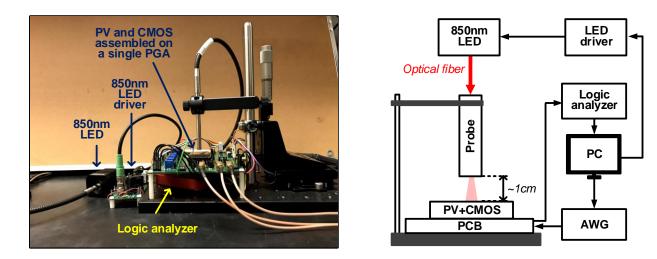

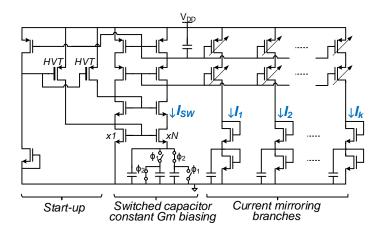

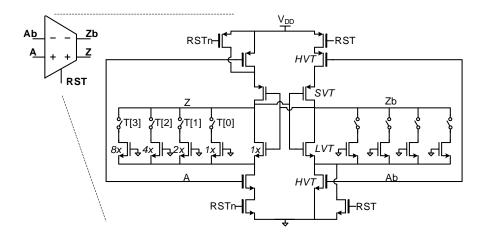

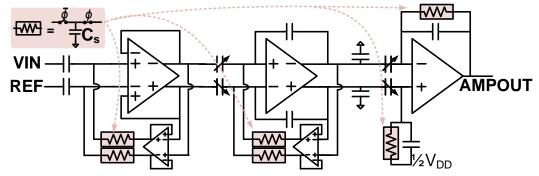

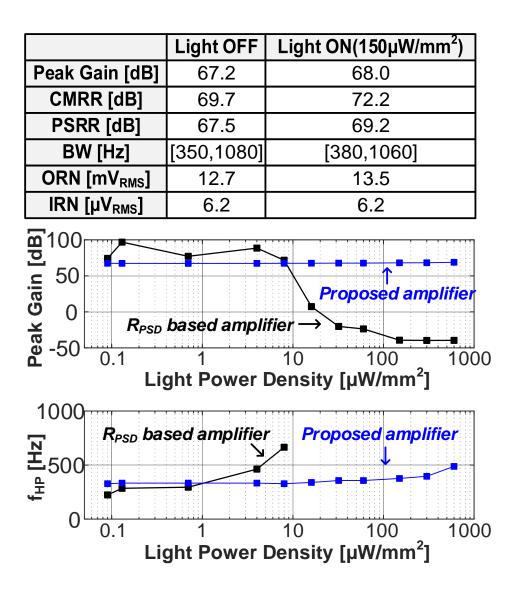

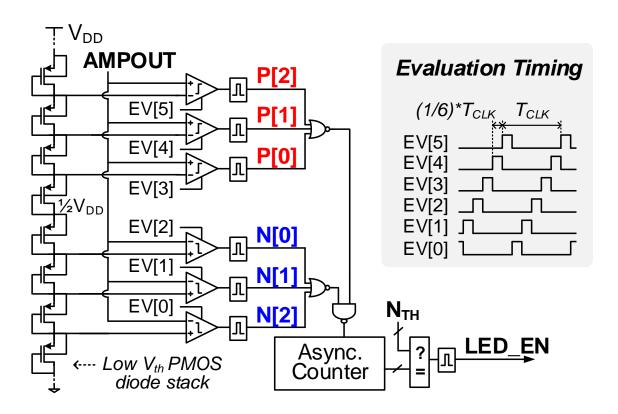

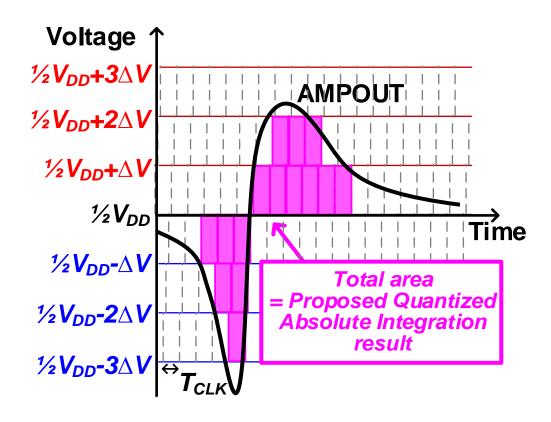

| 5     | 1 CMI<br>10069<br>10069<br>40069<br>40069<br>1006<br>100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 109.10                         | 0.1843                               | 0.1624                                      |