# **Architectural Enhancements for Data Transport in Datacenter Systems**

by

Hossein Golestani

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in The University of Michigan 2021

#### **Doctoral Committee:**

Professor Thomas F. Wenisch, Chair Associate Professor Robert Dick Assistant Professor Baris Kasikci Professor Scott Mahlke

# Hossein Golestani

hosseing@umich.edu

ORCID iD: 0000-0001-7293-6965

© Hossein Golestani 2021

To my family, the pieces of my heart...

#### **ACKNOWLEDGEMENTS**

Well, I have come to the end of a journey full of invaluable experiences and wonderful memories. Over the last five years in my PhD, I learned so many things not just in the matter of computer science but also about many aspects of life. True growth is always accompanied by discomfort and even pain. This was no exception for me during my PhD; I could only survive through the support and love of many amazing people around me, both physically and virtually. Words may not be enough to acknowledge them, but I will do my best.

First, I would like to thank my PhD adviser, Prof. Tom Wenisch. My first encounter with him was in my first semester at Michigan, where he was the instructor of the Computer Architecture course. I was absolutely amazed by how passionately he gave the lectures. Later, I realized he has the same passion and devotion in all aspects of his work, particularly in the research with his students. I started to work with Tom at one of those "in the right place, at the right time" moments. I joined his research group a few months before he took a sabbatical. Before leaving, he suggested a research direction to me, which eventually resulted in the material of this dissertation. Even after he left, he was there all the time to help me not only with my research but also with my career decisions. Tom has been an incredible source of research insight, technical knowledge, and professional advice for me.

I would also like to thank a number of other professional researchers who assisted me during my PhD. Profs. Robert Dick, Baris Kasikci, and Scott Mahlke kindly served in my doctoral committee and provided valuable feedback to my proposal and to the writing of this dissertation. Additionally, I had the chance to work directly with Prof. Scott Mahlke along with Prof. Satish Narayanasamy at the beginning of my PhD. They helped me, an

inexperienced researcher at the time, to learn how to define and approach a research problem and find solutions for it through critical thinking. I also appreciate Drs. Gagan Gupta and Rathijit Sen, who provided great mentorship for me during my two internships at Microsoft. The trust they placed in me helped me build confidence in conducting research, which has been beneficial to me ever since I worked with them.

I must also thank my colleagues in Tom's research group, unofficially called the "Sanctuary Lab". Vaibhav Gogte, Kevin Loughlin, Amirhossein Mirhosseini, Harini Muthukrishnan, Akshitha Sriraman, Ofir Weisse, Brendan West, and Steve Zekany are brilliant people, and I have fond memories of working with them in a dynamic, lively lab. In particular, I thank Amirhossein very much, who helped me hit the ground running when I joined the group. He was easy to reach and willing to cooperate, and in fact, I co-authored the research related to Chapters II and III jointly with him. I also particularly thank Steve for he helped me a lot with accessing the group servers and also ordering and building new ones. Additionally, I was lucky to be a labmate of another group of wonderful people: Jonathan Bailey, Armand Behroozi, John Kloosterman, Salar Latifi, Shikai Li, Brandon Nguyen, Sunghyun Park, Jiecao Yu, Babak Zamirai, Pedram Zamirai, and Ze Zhang. I truly enjoyed working and being friends with them. Ze and I also did two internships at Microsoft at exactly the same times and offices. I learned so much from and was inspired by such great colleagues and friends, in both my previous and current labs.

The BBB building—that is, U of M's Computer Science and Engineering (CSE) Department—was the reason to build many valuable connections. I was fortunate to interact with fabulous people other than my labmates, including Shaizeen Aga, Tanvir Ahmed Khan, Subarno Banerjee, Daichi Fujiki, Shruti Padmanabha, Mehrzad Samadi, Arun Subramaniyan, Shahab Tajik, and Hanyun Tao. Tanvir and I also interned in the same group at Microsoft, working at desks right next to each other in a memorable summer. Furthermore, I must thank the great CSE staff, who work hard to enable us to study and work smoothly. In particular, I appreciate Ashley Andreae, Jamie Goldsmith, Karen Liska, and Stephen Reger,

who were always prompt and perfect in many occasions I sought their help.

The PhD life would be too tedious without close friends. I have been fortunate enough to have Agreen Ahmadi, Ramin Ansari, Javad Bagherzadeh, Salar Latifi, Babak Zamirai, and Pedram Zamirai as my true friends. My friendship with Salar goes back to our undergrad school, Sharif University of Technology. We did almost all the projects we had in the last three years of our undergrad together. We did the same in our grad courses after we both got admitted to U of M. Beyond that, we have been roommates in Ann Arbor for five years; what a marvelous blessing. I also knew Babak back from Sharif, but our true friendship began thanks to U of M. He was always there to help me in Ann Arbor in every step of life and study. I was honored to officiate the wedding of two of my best friends, Agreen and Pedram, in Ann Arbor. This experience was full of ineffable joy and thrill for me. Ramin is a cool, outgoing friend, who hosted me in a one-month interval when I was switching apartments. Javad is also an amazingly energetic friend, and we have awesome memories of playing football (known as soccer in the U.S.) to death! In addition, I have been very lucky to have friends like Samin Aayanifard, Mehran Amini, Omid Bahrami, Navid Barani, Farima Fatahi, Ashkan Kazemi, Alireza Khadem, and Milad Moosavifar, happy moments with whom will always remain in my memory.

Last but definitely not least, I must express my immense gratitude towards my family for their everlasting, infinite love and support. Above all, my parents, Mahmoud and Fooziyeh, are the reason I got this far. Apart from the huge love and care they always have had for me, they provided for my education with all they had and taught me the highest levels of integrity, dedication, and commitment. My lovely sisters—Nasim, Sahar, and Tolou—mean the world to me, and the bond we have cannot be described by words. Moreover, I am so happy that I have such wonderful brothers-in-law—Mehrdad, Abolfazl, and Mohammadhossein. Specifically, I was only able to survive several mental meltdowns during my PhD through the counseling and psychological support that Abolfazl provided for me. The brutal travel restrictions imposed on Iranian students in the U.S. and their families outside the U.S.

not only deprived me from meeting my family during my PhD, but I have also never met Mehrdad and Mohammadhossein in person. I have yet to meet and hug my cute nephew, Karan, as well. Nevertheless, Sahar and Abolfazl have been kindly sending me videos of Karan, so that I don't miss the everyday growth of this adorable, little boy. All in all, my family is the pieces of my heart and all the strength I have; I literally feel them under my skin.

# TABLE OF CONTENTS

| DEDICATION   |                                               | ii   |

|--------------|-----------------------------------------------|------|

| ACKNOWLED    | GEMENTS                                       | iii  |

| LIST OF FIGU | RES                                           | X    |

| LIST OF TABL | ES                                            | xiii |

| ABSTRACT     |                                               | xiv  |

| CHAPTER      |                                               |      |

| I. Introd    | luction                                       | . 1  |

| 1.1          | Characterization of Software Data Planes      | . 2  |

| 1.2          | Acceleration of the Notification Mechanism    | . 3  |

| 1.3          | Acceleration of Data Transfer                 | . 4  |

| 1.4          | Road Map                                      | . 5  |

| II. Softwa   | are Data Planes: You Can't Always Spin to Win | . 7  |

| 2.1          | Introduction                                  | . 7  |

| 2.2          | Background                                    | . 10 |

|              | 2.2.1 Software Data Plane Mechanisms          | . 10 |

|              | 2.2.2 Software Data Plane Applications        | . 14 |

| 2.3          | Methodology                                   |      |

| 2.4          | Inefficiencies of Spin-Polling                | . 19 |

|              | 2.4.1 Polling Tax                             | . 19 |

|              | 2.4.2 Work Disproportionality                 |      |

| 2.5          | Lack of Queue Scalability                     | . 24 |

| 2.6          | Lack of Core Scalability                      | . 28 |

| 2.7          | Scale-up Queuing is Impractical               |      |

| 2.8          | Discussion: Solution Directions               | . 36 |

| 2.9          | Related Work                                  | . 38 |

| 2.1     | 0 Conclusion                                                                     | 39  |

|---------|----------------------------------------------------------------------------------|-----|

|         | rPlane: A Scalable Low-Latency Notification Accelerator for Soft-<br>Data Planes | 41  |

| ware    | Data Flancs                                                                      | 7.  |

| 3.1     | Introduction                                                                     | 41  |

| 3.2     | Background and Motivation                                                        | 45  |

|         | 3.2.1 Software Data Planes                                                       | 45  |

|         | 3.2.2 Software Data Plane Challenges and Goals                                   | 47  |

|         | 3.2.3 Case Study: DPDK Queue Scalability                                         | 48  |

| 3.3     | HyperPlane Design                                                                | 50  |

|         | 3.3.1 Programming Model                                                          | 51  |

|         | 3.3.2 Hardware Components                                                        | 55  |

| 3.4     | Detailed Microarchitecture                                                       | 59  |

|         | 3.4.1 Monitoring Set                                                             | 59  |

|         | 3.4.2 Ready Set                                                                  | 61  |

|         | 3.4.3 Hardware Costs                                                             | 64  |

| 3.5     | Evaluation                                                                       | 65  |

|         | 3.5.1 Methodology                                                                | 65  |

|         | 3.5.2 Queue Scalability                                                          | 66  |

|         | 3.5.3 Multicore Performance                                                      | 70  |

|         | 3.5.4 Work Proportionality                                                       | 72  |

|         | 3.5.5 Ready Set Implementation                                                   | 74  |

| 3.6     |                                                                                  | 75  |

| 3.7     |                                                                                  | 77  |

| IV Hypo | rData: A Data Transfer Accelerator for Software Data Planes                      |     |

|         | d on Targeted Prefetching                                                        | 78  |

| Dasec   | Ton Targeted Freierching                                                         | / ( |

| 4.1     | Introduction                                                                     | 78  |

| 4.1     |                                                                                  |     |

| 4.2     |                                                                                  | 83  |

| 4.3     | $\mathcal{E}$                                                                    | 84  |

|         | $\mathcal{E}$                                                                    | 85  |

|         | $\boldsymbol{c}$                                                                 | 88  |

|         | <u> </u>                                                                         |     |

| 1.1     |                                                                                  | 90  |

| 4.4     |                                                                                  | 92  |

|         | 4.4.1 Methodology                                                                | 92  |

|         | 4.4.2 Prefetching Performance                                                    | 93  |

|         | 4.4.3 Effectiveness with Scale-up Queuing                                        | 96  |

| 4 ~     | 4.4.4 Overhead Analysis                                                          | 97  |

| 4.5     |                                                                                  | 97  |

| 4.6     | Conclusion                                                                       | 99  |

| V Conc  | lusion                                                                           | 100 |

| 5.1         | Summary     | <i>'</i>                                          | . 100 |

|-------------|-------------|---------------------------------------------------|-------|

| 5.2         | Future Re   | esearch                                           | . 102 |

| APPENDIX    |             |                                                   | 104   |

| A. Chara    | cterization | n of Unnecessary Computations in Web Applications | . 105 |

| A.1         | Introduct   | ion                                               | . 105 |

| A.2         | Backgrou    | and Motivation                                    | . 108 |

|             | A.2.1       | Rendering Pipeline of Web Browsers                | . 108 |

|             | A.2.2       | Unnecessary Computations in Web Browsers          | . 109 |

|             | A.2.3       | Detection of Unnecessary Computations             | . 111 |

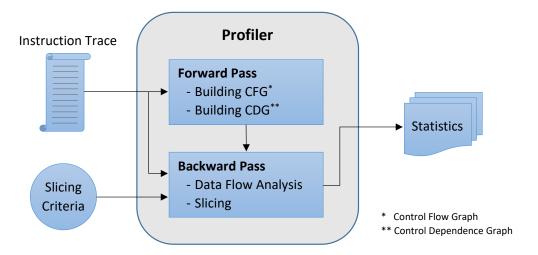

| A.3         | Profiler I  | Design                                            | . 112 |

|             | A.3.1       | Forward Pass                                      | . 113 |

|             | A.3.2       | Backward Pass                                     | . 114 |

| A.4         | Evaluation  | on Methodology                                    | . 115 |

|             | A.4.1       | Dynamic Binary Instrumentation                    | . 116 |

|             | A.4.2       | Benchmarks                                        | . 117 |

|             | A.4.3       | Choice of Slicing Criteria for Web Applications   | . 118 |

| A.5         | Results a   | nd Discussion                                     | . 120 |

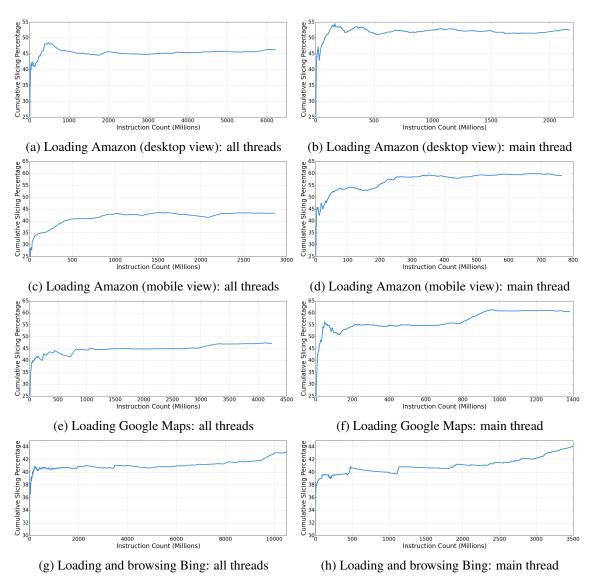

|             | A.5.1       | Calculated Slice                                  | . 120 |

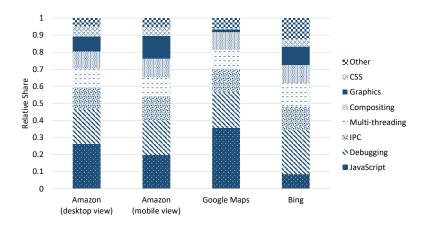

|             | A.5.2       | Categorization of Unnecessary Computations        | . 124 |

| A.6         | Related V   | Vork                                              | . 126 |

|             | A.6.1       | Workload Characterization of Web Applications     | . 126 |

|             | A.6.2       | Performance Optimization of Web Applications      | . 126 |

|             | A.6.3       | Energy-efficient Mobile Web Applications          | . 127 |

|             | A.6.4       | Architectural Support for Web Applications        | . 127 |

| A.7         | Conclusion  | on                                                | . 128 |

| BIBLIOGRAPH | ΗY          |                                                   | 129   |

# LIST OF FIGURES

| Figure     |                                                                                                                                                                                                                                                                                                                                                                                |     |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.1        | (a) Kernel-based I/O processing, (b) Spin-polling-based software data                                                                                                                                                                                                                                                                                                          |     |

|            | planes                                                                                                                                                                                                                                                                                                                                                                         | 11  |

| 2.2        | Data communication through RX/TX queues: (a) From a core to I/O                                                                                                                                                                                                                                                                                                                | 4.0 |

|            | devices or other cores, (b) From an I/O device to cores                                                                                                                                                                                                                                                                                                                        | 16  |

| 2.3<br>2.4 | The machine under test receives packets directly from the packet generator. Configurations of cores and queues in experiments: (a) Scaling up the number of queues in the machine under test; (b) Scaling up the number of core-queue pairs in the machine under test; (c) A shared queue accessed by multiple cores in the machine under test; (d) The generic setup of cores | 17  |

|            | and queues in the packet generator machine                                                                                                                                                                                                                                                                                                                                     | 18  |

| 2.5        | Useful cycles vs. cycles spent on polling in a core performing network                                                                                                                                                                                                                                                                                                         |     |

|            | routing                                                                                                                                                                                                                                                                                                                                                                        | 20  |

| 2.6        | Instructions Per Cycle (IPC) of a spin-polling core performing network                                                                                                                                                                                                                                                                                                         |     |

|            | routing                                                                                                                                                                                                                                                                                                                                                                        | 21  |

| 2.7        | The adverse effect of a spin-polling application and a regular matrix multiplication application on each other when collocated on two SMT hyperthreads: (a) The IPC of the co-running matrix multiplication decreases.                                                                                                                                                         |     |

| 2.8        | (b) Packet throughput of the spin-polling application drops Idle (zero-traffic) polling rate (left axis) and LLC loads per second (right                                                                                                                                                                                                                                       | 23  |

| 2.0        | axis) vs. number of queues                                                                                                                                                                                                                                                                                                                                                     | 25  |

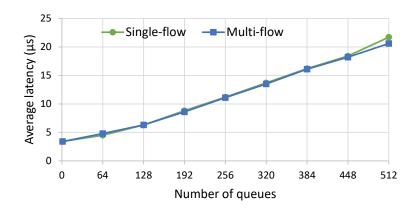

| 2.9        | Round-trip latency of packet forwarding under light traffic (< 1 Mpps),                                                                                                                                                                                                                                                                                                        | 26  |

| 2.10       | with varying number of queues                                                                                                                                                                                                                                                                                                                                                  | 26  |

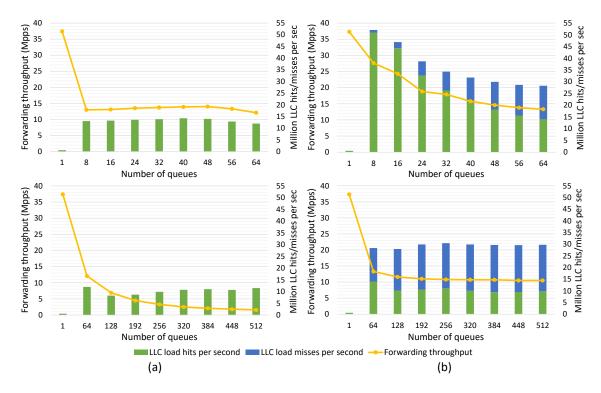

| 2.10       | Maximum forwarding throughput and LLC load hits/misses per second as                                                                                                                                                                                                                                                                                                           | 27  |

| 0.11       | the number of queues increases: (a) Single-flow, (b) Multi-flow                                                                                                                                                                                                                                                                                                                | 27  |

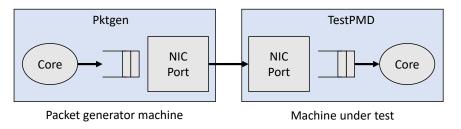

| 2.11       | Setup for measuring single-core throughput.                                                                                                                                                                                                                                                                                                                                    | 28  |

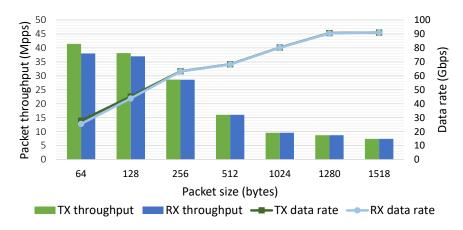

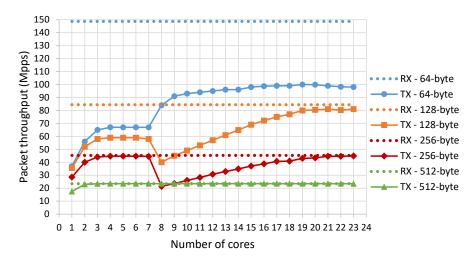

| 2.12       | Maximum throughput of a single core                                                                                                                                                                                                                                                                                                                                            | 29  |

| 2.13       | Packet throughput as the number of core-queue pairs increases. The RX                                                                                                                                                                                                                                                                                                          | 20  |

| 2.14       | line is saturated in all the cases                                                                                                                                                                                                                                                                                                                                             | 30  |

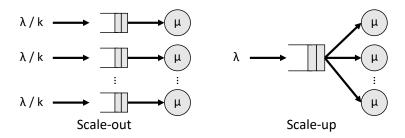

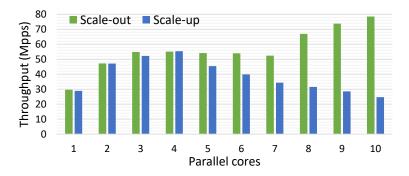

| 2.14       | Scale-out vs. scale-up queuing organizations with $k$ cores. ( $\lambda$ and $\mu$                                                                                                                                                                                                                                                                                             | 22  |

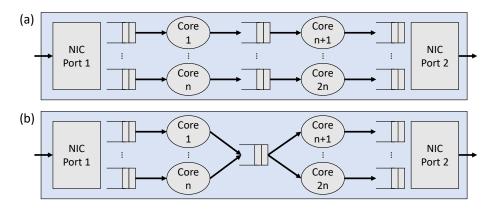

| 2.15       | represent arrival and service rates.)                                                                                                                                                                                                                                                                                                                                          | 32  |

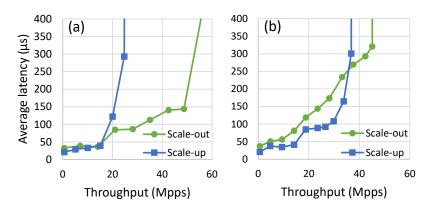

| 2.15       | Experimental setup of (a) scale-out, and (b) scale-up, configurations                                                                                                                                                                                                                                                                                                          | 33  |

| 2.16       | Maximum throughput achieved by scale-out and scale-up configurations                                                                                                                                                                                                                                                                                                           | 33  |

| 2.17 | Average round-trip latency of scale-out vs. scale-up configurations with     |    |

|------|------------------------------------------------------------------------------|----|

|      | 10 cores: (a) No hiccups, (b) 1 μs processing hiccup with 1% probability     | 34 |

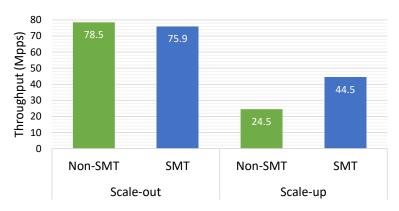

| 2.18 | Throughput of scale-out vs. scale-up configurations with 10 logical cores    |    |

|      | in case of using 2-threaded SMT cores or separate physical cores             | 36 |

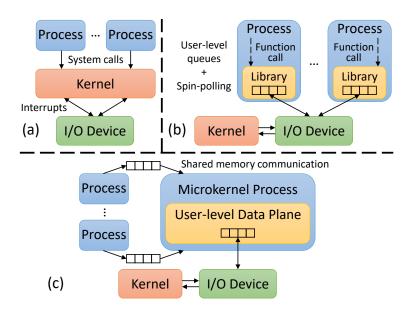

| 3.1  | I/O communication approaches: (a) conventional kernel-based, (b) user-       |    |

|      | level library OS, (c) microkernel-based "software data planes"               | 42 |

| 3.2  | Software Data Plane (SDP) operations                                         | 46 |

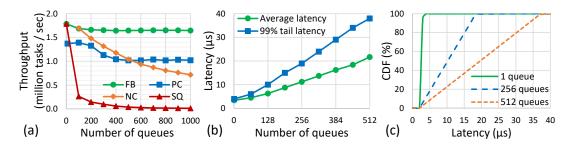

| 3.3  | DPDK: (a) Throughput of packet encapsulation in DPDK, (b) Round-             |    |

|      | trip latency of packet forwarding under light traffic (~0.01 Mpps), (c)      |    |

|      | Distribution of round-trip latency.                                          | 49 |

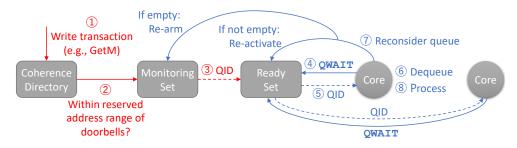

| 3.4  | High-level hardware block diagram of HyperPlane                              | 55 |

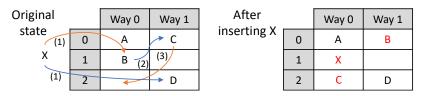

| 3.5  | An example 2-way Cuckoo hash table insertion                                 | 59 |

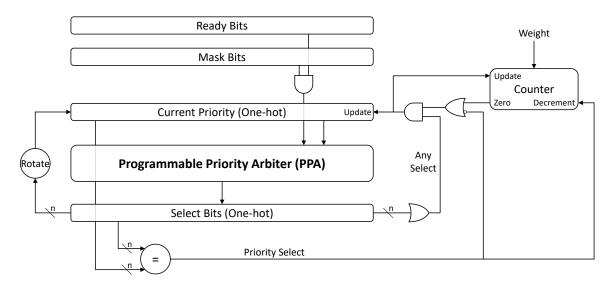

| 3.6  | High-level block diagram of the ready set hardware                           | 62 |

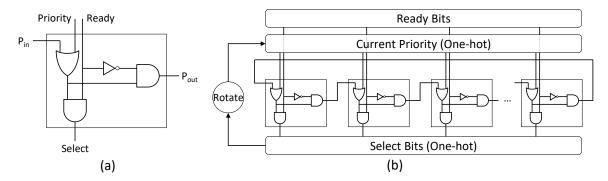

| 3.7  | (a) A bit-slice Programmable Priority Arbiter (PPA) cell, and (b) a multi-   |    |

|      | bit ripple-priority PPA design                                               | 63 |

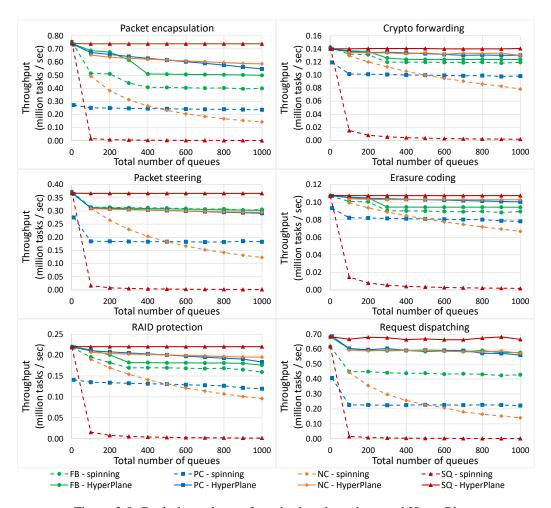

| 3.8  | Peak throughput of a spinning data plane and HyperPlane                      | 67 |

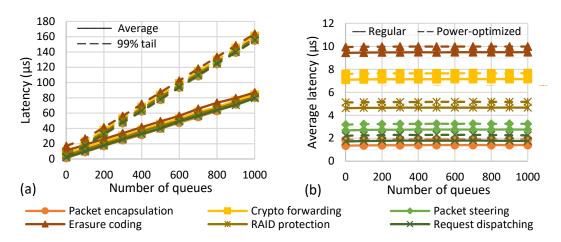

| 3.9  | Latency under light traffic (< 1% load): (a) Average and tail latency of     |    |

|      | a spinning data plane, (b) Average latency of HyperPlane in regular and      |    |

|      | power-optimized modes                                                        | 69 |

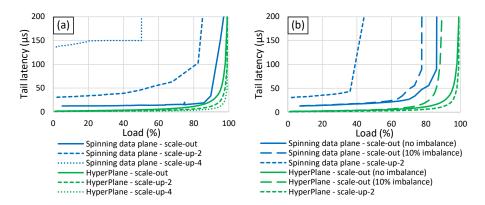

| 3.10 | Multicore 99% tail latency: (a) Fully balanced traffic, (b) Proportionally   |    |

|      | concentrated traffic                                                         | 71 |

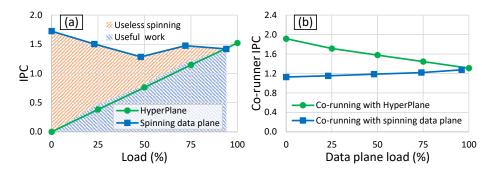

| 3.11 | (a) IPC breakdown of a software data plane, (b) IPC of an application        |    |

|      | co-running with the software data plane                                      | 72 |

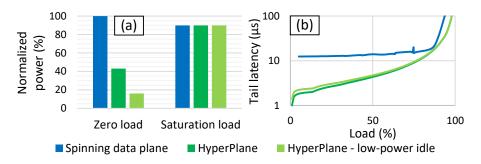

| 3.12 | (a) Power consumption of a spinning data plane and HyperPlane with-          |    |

|      | /without power optimization, (b) The effect of wake-up latency of power-     |    |

|      | optimized HyperPlane                                                         | 73 |

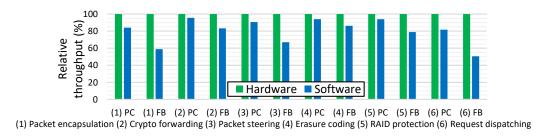

| 3.13 | Throughput of a software-based vs. hardware-based ready set with two         |    |

|      | different traffic shapes                                                     | 75 |

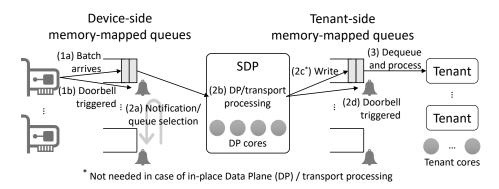

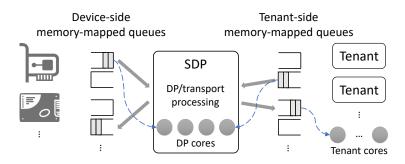

| 4.1  | Software Data Plane (SDP) architecture. We aim to prefetch data buffers      |    |

|      | related to the items in the device- or tenant-side queues to the target data |    |

|      | plane or tenant cores (shown by dashed arrows)                               | 79 |

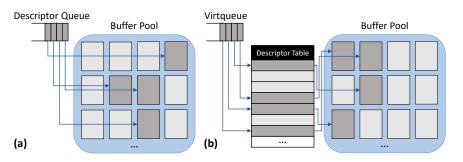

| 4.2  | Allocation of buffers from the pool to items in the queue: (a) A regular     |    |

|      | descriptor queue, (b) A Virtio queue (Virtqueue) with a corresponding        |    |

|      | descriptor table                                                             | 81 |

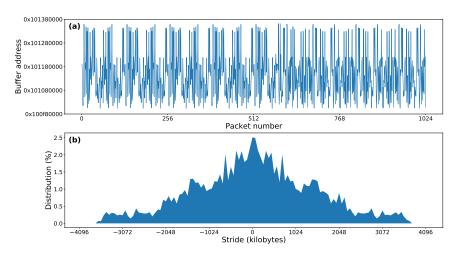

| 4.3  | (a) Buffer addresses of a sequence of packets, (b) Distribution of strides   |    |

|      | of buffer addresses                                                          | 83 |

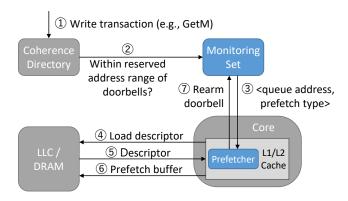

| 4.4  | Overview of HyperData design (monitoring set and prefetcher)                 | 85 |

| 4.5  | Initialization of the monitoring set                                         | 86 |

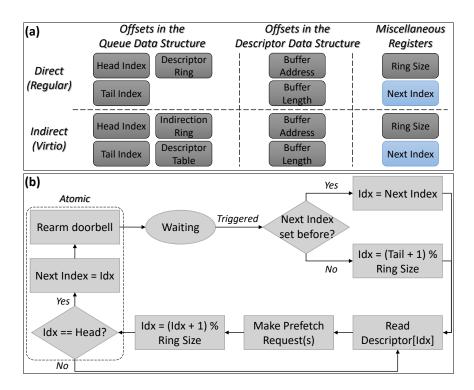

| 4.6  | HyperData's prefetcher design: (a) Registers that enable traversing the      |    |

|      | descriptor rings and reading the descriptors; programmable registers are     |    |

|      | shown by the dark color. (b) States and operations for making prefetch       |    |

|      | requests                                                                     | 89 |

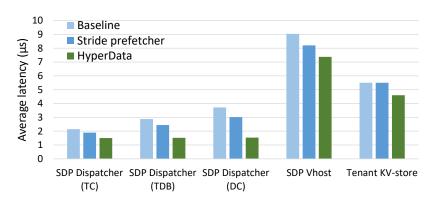

| 4.7  | Prefetching performance in terms of packet processing latency                | 94 |

| 4.8  | LLC hit/miss statistics of the dequeuer core                                 |    |

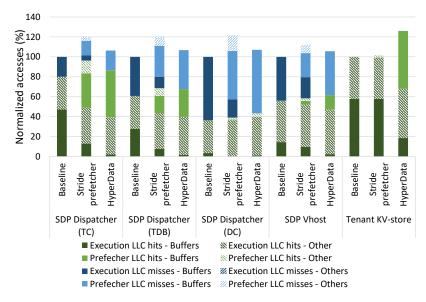

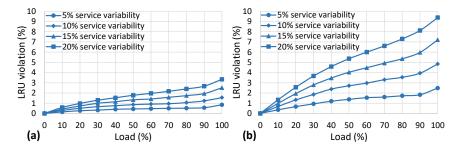

| 4.9 | The rate of prefetching to an incorrect core using the LRU mechanism        |

|-----|-----------------------------------------------------------------------------|

|     | with (a) 2 cores, and (b) 4 cores                                           |

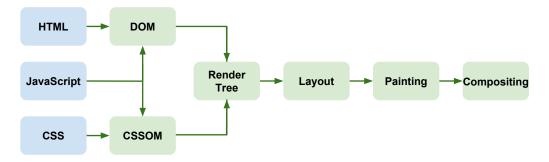

| A.1 | Rendering pipeline of a Web browser                                         |

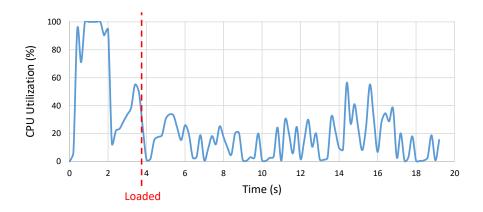

| A.2 | CPU utilization by the main thread of the tab process while browsing        |

|     | amazon.com                                                                  |

| A.3 | Profiler design overview                                                    |

| A.4 | Changes of slicing percentage over the backward pass. $x = 0$ indicates the |

|     | Web page is loaded or the browsing session is done, and the last point on   |

|     | the x-axis corresponds to entering the Web page URL                         |

| A.5 | Categorization of potentially unnecessary computations and their distribu-  |

|     | tion through analysis of instructions that do not belong to the pixel-based |

|     | slice                                                                       |

#### LIST OF TABLES

# Table2.1HW/SW specs of experimental machines.173.1Microarchitecture details.654.1Architectural details of the simulated SDP system.92A.1Unused JavaScript and CSS code bytes.110A.2Slicing statistics of pixel-based approach for all instructions and important threads.120

#### **ABSTRACT**

Datacenter systems run myriad applications, which frequently communicate with each other and/or Input/Output (I/O) devices—including network adapters, storage devices, and accelerators. Due to the growing speed of I/O devices and the emergence of microservice-based programming models, the I/O software stacks have become a critical factor in end-to-end communication performance. As such, I/O software stacks have been evolving rapidly in recent years. Datacenters rely on fast, efficient "Software Data Planes", which orchestrate data transfer between applications and I/O devices. The goal of this dissertation is to enhance the performance, efficiency, and scalability of software data planes by diagnosing their existing issues and addressing them through hardware-software solutions.

In the first step, I characterize challenges of modern software data planes, which bypass the operating system kernel to avoid associated overheads. Since traditional interrupts and system calls cannot be delivered to user code without kernel assistance, kernel-bypass data planes use spinning cores on I/O queues to identify work/data arrival. Spin-polling obviously wastes CPU cycles on checking empty queues; however, I show that it entails even more drawbacks: (1) Full-tilt spinning cores perform more (useless) polling work when there is less work pending in the queues. (2) Spin-polling scales poorly with the number of polled queues due to processor cache capacity constraints, especially when traffic is unbalanced. (3) Spin-polling also scales poorly with the number of cores due to the overhead of polling and operation rate limits. (4) Whereas shared queues can mitigate load imbalance and head-of-line blocking, synchronization overheads of spinning on them limit their potential benefits.

Next, I propose a notification accelerator, dubbed *HyperPlane*, which replaces spin-

polling in software data planes. Design principles of HyperPlane are: (1) not iterating on empty I/O queues to find work/data in ready ones, (2) blocking/halting when all queues are empty rather than spinning fruitlessly, and (3) allowing multiple cores to efficiently monitor a shared set of queues. These principles lead to queue scalability, work proportionality, and enjoying theoretical merits of shared queues. HyperPlane is realized with a programming model front-end and a hardware microarchitecture back-end. Evaluation of HyperPlane shows its significant advantage in terms of throughput, average/tail latency, and energy efficiency over a state-of-the-art spin-polling—based software data plane, with very small power and area overheads.

Finally, I focus on the data transfer aspect in software data planes. Cache misses incurred by accessing I/O data are a major bottleneck in software data planes. Despite considerable efforts put into delivering I/O data directly to the last-level cache, some access latency is still exposed. Cores cannot prefetch such data to nearer caches in today's systems because of the complex access pattern of data buffers and the lack of an appropriate notification mechanism that can trigger the prefetch operations. As such, I propose *HyperData*, a data transfer accelerator based on targeted prefetching. HyperData prefetches exact (rather than predicted) data buffers (or a required subset to avoid cache pollution) to the L1 cache of the consumer core at the right time. Prefetching can be done for both core—peripheral and core—core communications. HyperData's prefetcher is programmable and supports various queue formats—namely, direct (regular), indirect (Virtio), and multi-consumer queues. I show that with a minor overhead, HyperData effectively hides data access latency in software data planes, thereby improving both application- and system-level performance and efficiency.

#### **CHAPTER I**

## Introduction

Datacenters are composed of multi-tenant systems, each running a massive number of processes. Individual users rely on datacenter systems for services like cloud computing (through Virtual Machines (VMs), containers, etc.), cloud storage, Web search, emails, and cloud-assisted applications such as video/audio streaming, social media, and so on. Industrial and academic users leverage datacenter systems for high-performance computing [10, 12, 15], software-defined networking [4, 16], and network function virtualization [1, 3], to name but a few. Tenants of datacenter systems—i.e., host applications and client applications/VMs—frequently interact with each other as well as Input/Output (I/O) devices to connect to the outside world or other systems within the datacenter, or use peripherals such as storage devices or accelerators. Datacenters aim for high-throughput, low-latency data communication between CPUs and/or I/O devices, while being energy-efficient and keeping the systems highly utilized.

The Operating System (OS) performs I/O coordination and processing in conventional systems. Today's high-speed I/O devices—such as network cards, solid state drives, persistent memory, and PCIe-attached accelerators—have microsecond-scale access time, and due to their high throughput, they demand CPU attention every few microseconds. The OS and the underlying hardware are capable of effectively handling millisecond-scale and nanosecond-scale stalls, respectively. Nevertheless, they fall short of covering microsecond-

scale stalls, also known as the "Killer Microseconds" [61]. Furthermore, modern online data-intensive applications are shifting away from monolithic software architectures with millisecond-scale computation time, and leverage a distributed microservice-based software model that involves microsecond-scale computation time and much finer-grained inter-server communication [167, 169]. At such low latencies, high throughputs, and microsecond-scale service times, the overhead of I/O software stacks becomes absolutely critical.

Due to the shortcomings and overheads of existing operating systems in I/O processing, I/O software stacks are being re-architected [64, 87, 113, 115, 127, 151, 174, 176, 179]. State-of-the-art I/O software stacks, "Software Data Planes", bypass the OS kernel to avoid corresponding overheads such as context switches, system calls, interrupts, and cross-address-space copies. Kernel-bypass software brings the necessary OS functionalities to the user space, such as user-level thread/task scheduling, networking/storage transport processing, and device drivers [24, 43, 223]. In this dissertation, I show that software data planes have their own particular inefficiencies, especially when the I/O count and the number of tenants are scaled up. I propose hardware-software solutions to enhance the performance and efficiency of software data planes, as will be summarized in the following sections.

# 1.1 Characterization of Software Data Planes \*

Modern software data planes bypass the OS software stack to avoid the attendant overheads of kernel-based I/O processing, and rely on cores spinning on user-level shared I/O queues as a fast notification mechanism. In fact, spinning cores are notified of the arrival of new work/data in I/O queues through cache coherence invalidation signals corresponding to cache lines holding queue heads. Whereas spin-polling can improve latency and throughput, it entails significant shortcomings, especially when scaling to large numbers of cores/queues. In the first set of contributions of this dissertation, I pinpoint and quantify challenges of spin-polling–based software data planes using Intel's Data Plane Development Kit (DPDK),

<sup>\*</sup> Published in the 2019 ACM Symposium on Cloud Computing (SoCC'19) [104]

as a representative infrastructure, on a real system. I characterize four scalability issues of software data planes: (1) Spin-polling lacks work proportionality, meaning that even more (useless) work may be performed when there is less I/O traffic. (2) Throughput and latency are severely affected at high queue counts because a large fraction of time is wasted interrogating empty queues, especially when reading empty queue heads incurs cache misses, which is quite likely. (3) Operation rate limits (transactions per second) as well as a *Polling Tax* (the overhead of polling, which is considerable even when operating at saturation throughput) result in poor core scalability. (4) Multiple cores cannot efficiently spin on shared queues, which have theoretical merits in mitigating load imbalance and head-of-line blocking, because of coherence and synchronization costs. I identify root causes of these issues and discuss solution directions to improve hardware and software abstractions for better performance, efficiency, and scalability in software data planes. The design and implementation of a promising solution is the subject of the next part.

# 1.2 Acceleration of the Notification Mechanism $^{\dagger}$

In the spin-polling-based software data planes, cores often poll empty queues before finding work in non-empty ones. Interrogating empty queues hurts peak throughput, tail latency, and energy efficiency as it often entails fruitless cache misses. The second major contribution of this dissertation is *HyperPlane*, an efficient accelerator for the notification mechanism of software data planes. The key features of HyperPlane are (1) avoiding iteration over empty I/O queues, unlike software-only designs, resulting in queue scalability, (2) halting execution when I/O queues are idle, leading to work proportionality and energy efficiency, and (3) efficiently sharing queues across cores to enjoy strong theoretical properties of scale-up queuing. HyperPlane is realized through a hardware subsystem associated with a familiar programming model, centering on the QWAIT instruction. QWAIT either returns a ready queue to the calling core to be processed, or halts execution. HyperPlane's

<sup>†</sup> Published in the 2020 IEEE/ACM Symposium on Microarchitecture (MICRO'20) [161]

microarchitecture consists of a *monitoring set* and a *ready set*. The monitoring set, which is a lookup table structure with high or full associativity, watches cache coherence write transactions that indicate new data or work item arrivals in I/O queues. The ready set, which effectively functions as a task scheduler, tracks ready queues and distributes work to cores based on various service policies and priority levels. I model HyperPlane in a simulator, and show that it improves peak throughput by 4.1× and tail latency by 16.4× compared to a state-of-the-art software data plane. Furthermore, HyperPlane reduces the core power consumption down to only 16.2% at zero load or idle state. The monitoring and ready sets incur only less than 1% per-core power and area overheads.

#### 1.3 Acceleration of Data Transfer $^{\ddagger}$

In addition to the notification mechanism, data transfer itself is another key aspect of data communication. I aim to enhance data transfer among the software data plane, I/O devices, and applications/VMs by designing the *HyperData* accelerator, the third major contribution of this dissertation. Data items in software data plane systems, such as network packets or storage blocks, are transferred through shared memory queues. Consumer cores typically access the data from DRAM or, thanks to technologies like Intel DDIO [27], from the (shared) last-level cache. Today, consumers cannot effectively prefetch such data to nearer caches due to the lack of a proper arrival notification mechanism and the complex access pattern of data buffers. HyperData is designed to perform *targeted* prefetching, wherein the *exact* data items (or a required subset) are prefetched to the L1 cache of the consumer core. Furthermore, HyperData is applicable to both core—device and core—core data communication, and it supports complex queue formats like Virtio [185] and multiconsumer queues. HyperData is realized with a *per-core programmable prefetcher*, which issues the prefetch requests, and a *system-level monitoring set*, which monitors queues for data arrival and triggers prefetch operations. I show that HyperData improves processing

<sup>&</sup>lt;sup>‡</sup> Under review in the 2021 IEEE International Conference on Computer Design (*ICCD*'21)

latency by 1.20- $2.42 \times$  in a simulation of a state-of-the-art software data plane, with only a few hundred bytes of per-core overhead.

#### 1.4 Road Map

Throughout the remainder of this dissertation, I first elaborate on characterization of software data planes in Chapter II. I then discuss acceleration of the notification mechanism and data transfer in software data planes in Chapters III and IV, respectively. Finally, I summarize the dissertation in Chapter V and describe how the proposed solutions can be implemented in the near-future systems and how software data planes can be enhanced with further hardware support.

Additionally, I describe the earliest project that I completed during my PhD studies<sup>§</sup> in Appendix A. While the focus of this dissertation is on enhancement of datacenter systems, I initially concentrated on the performance and efficiency of Web applications at the client side, i.e., user phones and computers. I briefly describe the problem and findings here; the details are elaborated on in the appendix.

Web applications are widely used in many different daily activities—such as online shopping, navigation through maps, and social networking—in both desktop and mobile environments. Advances in technology, such as network connection, hardware platforms, and software design techniques, have empowered Web developers to design Web pages that are highly rich in content and engage users through an interactive experience. However, the performance of Web applications is not ideal today, and many users experience poor quality of service, including long page load times and irregular animations. One of the contributing factors to low performance is the very design of Web applications, particularly Web browsers. In the appendix, I argue that there are unnecessary computations in today's Web applications, which are completely or most likely wasted. I first describe the potential

<sup>§</sup> Published in the 2019 IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS'19) [103]

unnecessary computations at a high level, and then design a profiler based on dynamic backward program slicing that detects such computations. The profiler reveals that for four different websites, only 45% of dynamically executed instructions are useful in rendering the main page, on average. I then analyze and categorize the unnecessary computations. The analysis shows that processing JavaScript codes is the most notable category of unnecessary computations, specifically during page loading. Therefore, such computations are either completely wasted or could be deferred to a later time, i.e., when they are actually needed, thereby providing higher performance and better energy efficiency.

#### **CHAPTER II**

Software Data Planes: You Can't Always Spin to Win \*†

#### 2.1 Introduction

Software data planes, which use shared-memory queues and spinning cores to enable fast data transfer among application software, accelerators, and I/O subsystems, have become critical to the performance of datacenter systems. Originally conceived to enable fast network packet processing (e.g., firewalls, routing, denial-of-service protection, deep packet inspection), software data planes are now widely used to virtualize network and storage systems [87, 218], eliminate OS overheads to I/O latency and throughput [174, 179], administer shared I/O bandwidth [125, 211], construct virtual networks [122], enable Remote Direct Memory Access (RDMA) [48, 125, 171], implement network switches in software [35], facilitate high-performance computing applications [11] and microservices [200], and transfer data to hardware accelerators [184] for functionalities as diverse as erasure coding, encryption, and video transcoding [9, 44, 142].

Intel's Data Plane Development Kit (DPDK) [24] is a representative software infrastructure for building data planes to run on conventional Intel Xeon cores. Its central abstractions are (1) spinning cores—cores that execute a poll loop and never yield or invoke blocking OS functionality, and (2) user-level queue pairs—shared memory structures for the data

<sup>\*</sup> Published in the 2019 ACM Symposium on Cloud Computing (SoCC'19) [104]

<sup>&</sup>lt;sup>†</sup> Joint research with Amirhossein Mirhosseini

plane to communicate with client software and hardware devices. These abstractions are general enough, and they have been also used in many other software and hardware infrastructures, such as the Storage Performance Development Kit (SPDK) [43]. The key enabling mechanism for the spin-polling communication model of software data planes is that it relies on cores spinning on cacheable memory-mapped locations. The mechanism is similar to shared memory communication between two cores; it relies on cache coherence to propagate a write with low latency, and it generally does not produce much coherence traffic, as cores can spin locally in their cache, unless there is work, making it fast-reacting and low-overhead.

Software data planes improve latency and throughput of conventional systems through (1) bypassing the OS software stacks, and (2) enabling a fast signaling and notification mechanism by replacing hardware-managed interrupts and their associated overheads (e.g., switching address spaces, flushing hardware pipelines) with spin-polling. Data plane operating systems—such as IX [64], ZygOS [179], and Shenango [174]—leverage these mechanisms to implement low-latency and high-throughput OS-bypass I/O and networking stacks. Nevertheless, due to the rapid growth of the number of cores on a chip and the advent of Terabit Ethernet [8] and other high-bandwidth I/O devices [44], software data planes face considerable scalability challenges. In this chapter, we show that whereas software data planes provide an easy-to-use and efficient model for communication and signaling, they are far from ideal, especially when scaled to serve numerous clients/flows or require many cores to scale transport processing for high throughput.

Using Intel's DPDK as an example software infrastructure, we characterize four scalability challenges of software data planes, identify their root causes, and discuss solution directions and alternative approaches. We summarize our findings as follows:

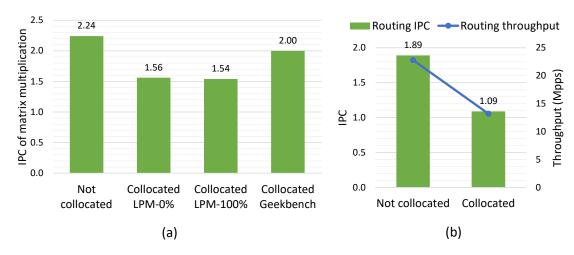

**Spin-polling performs more work when there is less.** Since spinning cores run full-tilt even when they have no work, polling performs more (useless) work when there is no I/O traffic or work items in the queue. Therefore, spin-polling lacks energy proportionality [62]

and speeds up core/chip aging [172], especially at low system loads. Furthermore, useless spinning can drastically slow co-running applications on Simultaneously Multi-Threaded (SMT) cores and result in severe quality-of-service violations.

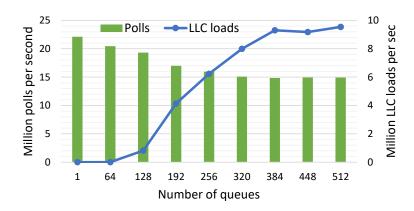

**Spin-polling is not scalable to many queues.** We show that increasing the number of queues on which a core spins increases processing latency and, depending on traffic balance, can harm peak throughput. This lack of scalability is caused by excessive pressure on processor caches. Moreover, we show that the performance overhead is greatest when most command queues are empty and traffic is concentrated in only a few queues; the overhead increases with the number of queues.

Spin-polling is not scalable to many cores. Spin-polling incurs a non-negligible instruction overhead for iterating over the body of the poll loop, which we call the *Polling Tax*. Even when operating at saturation throughput (100% load), we show that the polling tax is non-trivial. The polling tax increases the number of cores it takes to saturate network line rate, even for the simplest packet forwarding use case. Furthermore, various I/O devices and interconnects on the data-path (e.g., NIC, PCIe, DDIO) are constrained by operation rate limits (transactions per second), in addition to data rate limits. The Polling Tax and operation rate limits result in poor core scalability of software data planes.

Spin-polling is not well-suited for scale-up queuing. For many application classes, scale-up queuing organizations [160], wherein a single queue is shared among multiple cores, holds promise to improve latency and throughput through better queuing behavior by avoiding load imbalance and head-of-line blocking. However, most software data planes are currently implemented in a scale-out fashion, wherein there is a dedicated queue per core, to avoid the synchronization overheads of sharing a single queue across cores. We quantify this effect and show that software data planes can greatly leverage scale-up queuing organizations, specifically for high-disparity service distributions, but current spin-polling mechanisms are not well-suited for such queuing organizations.

This study aims to motivate better hardware and software abstractions to overcome

these challenges and enable greater data plane scalability to higher data rates and larger core counts. Future data planes should leverage advantages of spin-polling (e.g., OS kernel bypassing, low-latency I/O signaling) while avoiding the corresponding overhead and scalability issues. We envision a multi-address monitoring scheme, wherein multiple memory locations are monitored (through sufficient hardware support) for work arrival, as a promising solution direction. Moreover, data plane applications with unbalanced service distributions might benefit from work distribution schemes based on scale-up or hierarchical queuing. Such schemes could be enabled by wider SMT processors [159] with hardware task scheduling [158], or I/O-managed pull-based work distribution based on core availability [84].

We first provide a brief background on software data planes (Section 2.2) and describe our DPDK-based measurement methodology (Section 2.3). We then present each of our four main findings (Sections 2.4-2.7) and discuss potential solution directions to mitigate them (Section 2.8). Finally, we discuss related work (Section 2.9) and conclude (Section 2.10).

### 2.2 Background

We briefly describe the operation of software data planes and outline their applications in datacenter networking, storage systems, and I/O virtualization.

#### 2.2.1 Software Data Plane Mechanisms

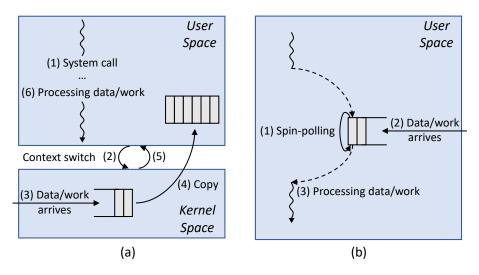

Conventional Systems. Figure 2.1 contrasts conventional kernel-based I/O stacks with modern software data planes. In kernel-based I/O stacks (Figure 2.1(a)), a user process signals the kernel that it wishes to perform I/O via a system call (e.g., through sockets or file system APIs). The protocol and transport processing needed to both read and write data is carried out by kernel threads, either by directly borrowing the CPU of the user process (e.g., during a system call), or by using interrupt mechanisms and kernel scheduling to place work on another core. Kernel I/O stacks are able to scale their CPU usage dynamically

Figure 2.1: (a) Kernel-based I/O processing, (b) Spin-polling-based software data planes.

with I/O load, stealing CPU from user processes as needed to perform transport work. However, system call and interrupt-based signalling mechanisms are slow and transport processing is disruptive (especially for incoming data) to the user processes it interrupts. Although the kernel goes to great lengths to spread transport work and optimize for affinity to user processes, the aggregate CPU cost for gigabit- and terabit-scale networking is significant [113].

Key Data Plane Mechanisms. As illustrated in Figure 2.1(b), software data planes rely on *spin-polling cores* and *user-level queue pairs* for low-latency and high-throughput communication, enabling both faster signalling than conventional system call/interrupt-based mechanisms and greater CPU efficiency for high throughput. In such systems, user processes communicate with transport processing code and I/O devices via in-memory queue pairs to schedule I/O operations and get notified of their completion. The key enabling mechanism of this approach is that the two queues, which may be called the submission/completion or send/receive queues, are typically in cacheable shared memory. Therefore, the two communicating end points can quickly signal one another if each spins on the head of its respective inbound queue. These locations are cached in a *shared* state within local L1/L2 caches, and the end points may locally spin awaiting a change without triggering any coherence transaction or on-chip network traffic [195]. In the shared state, all sharers

maintain a read-only copy of a memory location. Before any processor or I/O device may write to the location (i.e., to append a new request or completion to a queue), it must first invalidate these copies. These invalidation messages propagate rapidly (nanoseconds within a chip; hundreds of nanoseconds across I/O interconnects) and serve as a low-latency notification mechanism. The subsequent read of an invalidated line will obtain its new value. The key to this mechanism is that memory traffic between the communicating end points only occurs when the originator of a request or completion writes to a queue—a receiver spin-polling on an idle queue produces no traffic.

**Zero-Copy Data Transfer.** Software data planes can further improve CPU efficiency relative to kernel transport by using *zero-copy* data transfer mechanisms. With zero-copy data transfer, two communicating end points access common buffer pools in a shared memory space. Unlike traditional OS-based approaches, where data are copied multiple times within main memory to traverse address spaces (frequently incurring context switches along with each copy), zero-copy mechanisms source outgoing data directly from user-space buffers where the data were first prepared, and land incoming data directly in the address space of the user process that will receive them. The transport software in the data plane arranges for data to flow directly between buffer pools in user processes and I/O devices, without any intermediate copies into memory owned by the data plane or kernel. Zero-copy mechanisms typically require some hardware support, and rely on user applications to adhere to more stringent lifetime and flow control guarantees for data and buffers in shared pools than synchronous kernel I/O interfaces (i.e., they are harder for programmers to use correctly).

Off-Chip Devices. I/O devices on the same chip as the CPU core or connected via a Non-Uniform Memory Access (NUMA) fabric (e.g., integrated NICs or accelerators) can directly share memory with the user process running on the CPU through virtual memory. For PCIe attached I/O devices, data typically must be transferred to a local buffer on the I/O device before they can be transmitted/stored. This transfer is typically accomplished

in one of two ways. In a Memory-Mapped I/O (MMIO), individual CPU store instructions trigger a PCIe transaction to update buffers on the I/O device. To reduce the number of PCIe transactions, CPUs implement a "write combining" optimization, which combines stores to generate cache-line—sized PCIe transactions. In a doorbell-based approach, instead of generating PCIe transactions directly via stores, after preparing a larger chunk of data in memory, the CPU issues a single PCIe write to a "doorbell" location, which triggers the target device to perform a Direct Memory Access (DMA) transfer to the device's memory. The doorbell-based approach may use PCIe bandwidth more efficiently, but can result in higher latency and more CPU work for the doorbell operations [118].

**Bringing Data on Chip.** When PCIe-attached I/O devices receive data on behalf of a user process, the updates are propagated from device buffers to CPU-side shared memory buffers via PCIe transactions. A hardware steering mechanism that can determine to which user process incoming data are destined is required for zero-copy receive; high end network cards and Solid-State Drives (SSDs) provide such flow steering mechanisms. Conventionally, PCIe transactions write data to main memory. However, if data plane software or the receiving user process will immediately access the data, the CPU will incur a costly Last Level Cache (LLC) miss to retrieve the cache line. To avoid this cache miss, prior work has investigated direct cache placement of I/O data [66, 112]. Accordingly, Intel has introduced Data Direct I/O (DDIO) technology [27], where a bus-mastering PCIe device can write directly into and read from the processor's LLC. With this mechanism, if a processor accesses incoming I/O data shortly after they are received, they will still be present in the LLC and costly main memory reads can be avoided. Similarly, data targeted to the I/O device do not need to be written back to memory; the device can read outbound data directly from the LLC. To prevent the I/O device from displacing too much CPU data from the LLC, it is restricted to write only to a limited number of LLC ways.

**Steering to Multiple Queues.** When multiple processes/CPUs communicate with the same I/O device, multiple queue pairs are typically provisioned, to avoid synchronization

overheads on each queue. Most modern I/O devices (e.g., multi-queue NVMe SSDs [207]) readily support numerous queue pairs. When a CPU submits work to a specific submission queue, the I/O device knows that it has to acknowledge through the corresponding completion queue. However, directing completions to the correct queue is more challenging when communication is not solicited by the CPU. For example, when a NIC receives packets, it must choose to which CPU's receive queue to append the packet. This steering is challenging because the NIC seeks to load-balance transport work across CPUs, but also seeks to ensure that packets sent in the same flow (between the same communicating end-user processes) are delivered in order. The commonly used solution for this problem is Receive-Side Scaling (RSS) [40]. In RSS, the NIC performs a hash of various fields in packet headers to identify the flow to which a packet belongs. The result of the hash function is used as an index to an indirection table, which specifies a set of queues/cores to which the packet should be directed. For TCP/IP traffic, the hash function is typically a 4-tuple hash over source/destination IP addresses and port numbers.

#### 2.2.2 Software Data Plane Applications

We describe recent applications of software data planes.

Networking. With the advent of Software-Defined Networking (SDN), flexibility and programmability have been brought to network backends by having a logically centralized control plane and a data plane. In SDN, a decoupled control plane, as the network brain, programs the data plane on how to forward packets. This approach has transformed traditional switches to programmable ones (through languages like P4 [69]), and has also enabled implementation of network functions—such as routing, load balancing, address translation, and firewalls—on industry standard servers. As a result, many software data plane solutions in datacenter networks have been proposed and deployed [87, 122, 174, 179], which benefit from cores spinning on queues tightly coupled to Network Interface Controllers (NICs). Intel's DPDK [24] is a representative open-source infrastructure for building

spin-polling-based network data planes.

**Storage.** High-speed storage devices such as SSDs and new persistent memory technologies like Intel's Optane [29] have been explored for use in demanding applications in databases and big data analytics. Data planes for such storage systems demand fast mechanisms for data transfer between the CPU and the device, leading to the introduction of new protocols, such as NVM Express (NVMe) and NVMe over Fabrics (NVMe-oF). Consequently, the concept of spinning cores to process queues for such storage devices has been increasingly adopted. The Storage Performance Development Kit (SPDK) [43] is the canonical example of using CPU to spin-poll user-space queues for storage devices.

I/O Virtualization. Data centers are commonly virtualized, where multiple Virtual Machines (VMs) run on the same host. Through I/O virtualization, a single network or storage device can be used by multiple VMs. This sharing is enabled by virtual machine managers or hypervisors, which manage access of multiple VMs to the I/O device(s). Alternatively, VMs can directly access I/O devices through nascent Single Root I/O Virtualization (SR-IOV) technology, bypassing the hypervisor. These mechanisms make it feasible for the VM data plane to take advantage of the previously described spin-polling mechanisms of network and storage devices. A VM can therefore spin-poll an I/O device queue through the hypervisor (e.g., DPDK's Vhost library) or directly through SR-IOV.

# 2.3 Methodology

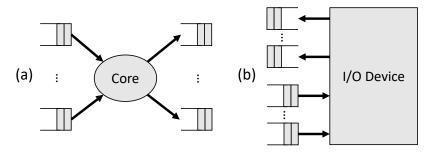

At the heart of the software data planes in software defined networking, whether in a virtualized environment or not, CPU cores read packets from receive (RX) queues, process them, and then send processed packets or newly generated ones to transmit (TX) queues. Each RX or TX queue pairs a CPU core with an I/O device or another core (e.g., a client process). In a generic scenario, a core must handle packets received from I/O devices or cores in a number of RX queues and eventually transmit a number of packets through TX queues back to them or to other I/O devices and cores (Figure 2.2(a)). As a result,

Figure 2.2: Data communication through RX/TX queues: (a) From a core to I/O devices or other cores, (b) From an I/O device to cores.

each I/O device (e.g., a NIC) communicates with CPU cores through these RX/TX queues (Figure 2.2(b)).

CPU cores and queues are points of scalability in software data planes. As in Figure 2.2(b), many queues (up to several hundred) may be introduced for a single NIC. Scaling up the number of queues communicating with a NIC is done either for application-specific purposes (e.g., differentiated QoS classes, each represented by a queue) or to scale transport processing to fully utilize the line rate offered by the NIC. In the latter case, CPU cores are also scaled up, each coupled with the NIC through one or more queues. We design experiments to investigate the performance and scalability of modern software data planes.

We use Intel's Data Plane Development Kit (DPDK) [24], an open-source project, as a representative infrastructure for building spin-polling-based software data planes. DPDK provides poll mode drivers for numerous modern NICs, which enable cores to spin on user-level queues to communicate with the NICs. DPDK is heavily optimized to offer high performance. For instance, DPDK pins its threads to specific cores to reduce context switches as much as possible. NUMA-aware memory allocation, use of 2MB and 1GB huge pages, and cache-alignment—aware data placement are among other optimizations done in DPDK.

Our experiments primarily use DPDK's Test Poll Mode Driver (TestPMD) and routing / Layer 3 Forwarding (L3Fwd) applications, and we modify them as needed to implement scalability experiments and to measure additional statistics, such as poll count and CPU

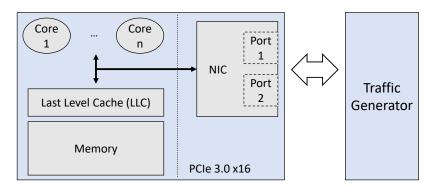

Figure 2.3: The machine under test receives packets directly from the packet generator.

Table 2.1: HW/SW specs of experimental machines.

| Item     | Machine under test                | Packet generator                           |

|----------|-----------------------------------|--------------------------------------------|

| CPU      | Single-socket, Xeon Platinum 8160 | Dual-socket, Xeon Gold 6138                |

|          | 24 physical cores @ 2.10-3.70 GHz | $2\times20$ physical cores @ 2.00-3.70 GHz |

|          | 32 KB L1 I/D-cache (per core)     | 32 KB L1 I/D-cache (per core)              |

|          | 1024 KB L2-cache (per core)       | 1024 KB L2-cache (per core)                |

|          | 33 MB LLC                         | 27.5 MB LLC (per socket)                   |

| Memory   | 96 GB (6×16 GB) DDR4 @ 2666 MHz   | 96 GB (12×8 GB) DDR4 @ 2666 MHz            |

| NIC      | Mellanox ConnectX-5 MCX556A-ECAT  | Mellanox ConnectX-5 MCX556A-ECAT           |

|          | 100 GbE dual-port                 | 100 GbE dual-port                          |

|          | PCIe 3.0 x16                      | PCIe 3.0 x16                               |

| OS       | Ubuntu 18.04.2 (LTS)              | Ubuntu 18.04.2 (LTS)                       |

| Software | DPDK 18.11.1 (LTS)                | DPDK 18.11.1 (LTS)                         |

|          |                                   | Pktgen 3.6.6                               |

cycles spent in different parts of the application. For CPU cycle classification, we read the x86 Time Stamp Counter (TSC) register at appropriate places in the code. In the L3Fwd application, the Longest Prefix Match (LPM) algorithm is used, and the routing table is filled with 16K entries. We have also developed a similar application to investigate the use of shared queues. Details of each application will be presented in the following sections as we introduce each experimental setup. Unless otherwise specified, we use 64-byte IPv4 UDP packets (96-byte for experiments requiring timestamps for latency measurement), but we vary packet sizes in several experiments.

Our system under test is a Skylake server equipped with a dual-port 100 GbE Mellanox ConnectX-5 NIC. Detailed specifications of this machine appear in Table 2.1. As shown in Figure 2.3, the NIC in the system under test receives traffic from a separate packet generator

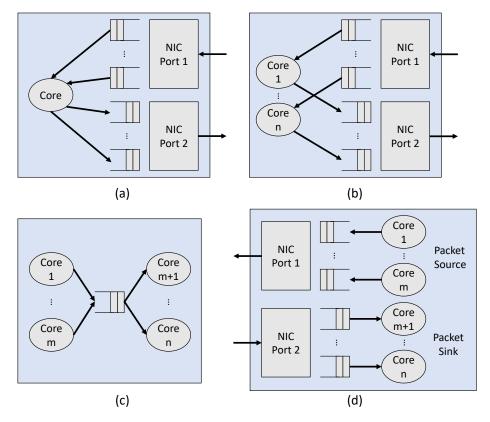

Figure 2.4: Configurations of cores and queues in experiments: (a) Scaling up the number of queues in the machine under test; (b) Scaling up the number of core-queue pairs in the machine under test; (c) A shared queue accessed by multiple cores in the machine under test; (d) The generic setup of cores and queues in the packet generator machine.

connected directly to the NIC ports. The setup for core/queue scalability experiments is shown in Figure 2.4(a) and (b). DPDK does not support sharing NIC queues among multiple cores; therefore, for queue sharing experiments, we instead investigate an application that distributes incoming packets among a set of cores (e.g., an intra-machine virtual network) as shown in Figure 2.4(c). Note that, unless otherwise specified, we use only a single hyperthread on each physical core (i.e., all threads run on different physical cores). We use the Linux Perf tool to gather microarchitectural statistics, particularly, cache hit and miss rates.

Our packet generator is another Skylake server, which also has a dual-port 100 GbE Mellanox ConnectX-5 NIC, as described in Table 2.1. Packets are generated using Pktgen [36], an open-source DPDK-powered application. Figure 2.4(d) illustrates the generic setup we

use to generate packets. Ports 1 and 2 of the NIC in the packet generator are connected directly to ports 1 and 2 of the NIC in the machine under test, respectively. For experiments where we wish to measure round-trip latency, the packet generator appends a timestamp to the packet when it is sent from port 1 and calculates the round-trip latency when an echoed/response packet is received at port 2 using a local high-precision time source. We also modify Pktgen to output a latency distribution.

#### 2.4 Inefficiencies of Spin-Polling

Spin-polling is the key mechanism for fast signalling between software data planes and their work sources (clients or devices). Although spin-polling typically enables lower latency than system-call or interrupt-based mechanisms, it suffers from two general inefficiencies: *polling tax* and *work disproportionality*.

# 2.4.1 Polling Tax

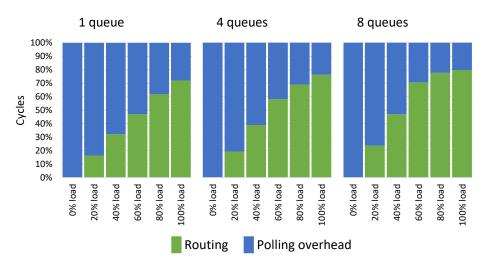

Spin-polling incurs a non-negligible overhead from the useless work of iterating over the body of the poll loop. We refer to the cycles wasted on these useless instructions as the *Polling Tax* as they are inherent/inevitable when polling is used. Figure 2.5 reports the breakdown of the cycles of a single CPU core spent on polling overhead (Tax) vs. useful work (i.e., routing packets) in an LPM-based routing application using the configuration shown in Figure 2.4(a), under different offered loads, and varying the number of RX queues on the first NIC port from one to eight (one TX queue for each port).

We have instrumented the application code to classify CPU cycles as "useful" and "polling overhead". The application body includes an infinite outer main loop, and an inner loop that traverses the queue heads. If an RX queue is non-empty, CPU cycles spent on reading packets from the RX queue, routing, and sending them to the TX queue are classified as useful. The rest of CPU cycles are classified as polling overhead (including loop branch overheads and polling of empty queues).

Figure 2.5: Useful cycles vs. cycles spent on polling in a core performing network routing.

As shown in Figure 2.5, even at 100% load (i.e., maximum routing throughput), a significant fraction of CPU cycles ( $\sim$ 20-28%) are spent on spin-polling, rather than the useful work of routing packets. Note that in each iteration of the main loop, n queue heads are checked. Therefore, overhead is amortized over n queues. This amortization results in overhead decreasing as the number of queues increases at a specific offered load. The high percentage of polling tax is due to the fact that the useful work per iteration is relatively simple (i.e., lookups in forwarding tables), highlighting the impact of poll loop overhead; with more complicated tasks in the loop body, we expect a smaller polling tax.

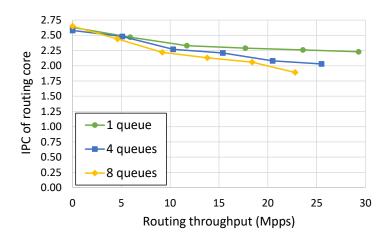

#### 2.4.2 Work Disproportionality

When polling, spinning cores run full-tilt even when they have no work. Modern cores can spin with remarkably high Instructions Per Cycle (IPC) while the core is not doing any useful work. To quantify this effect, we measure the IPC of a single core spin-polling 1, 4, and 8 queues for LPM routing at varying offered loads. Figure 2.6 reports the IPC of the poller core as throughput increases. As shown in the Figure, IPC decreases up to 29% as throughput increases. As throughput increases, more time is spent on useful work, which exhibits substantially lower IPC than spin-polling (e.g., due to cache misses). Our measurement confirms the observations of Alameldeen and Wood [56] that IPC is a harmful

Figure 2.6: Instructions Per Cycle (IPC) of a spin-polling core performing network routing.

metric for performance evaluation of workloads that use busy spinning for communication, as it does not necessarily represent useful work. Furthermore, our result shows that spin-polling harms core efficiency (the lower the load, the more instructions are executed). The high IPC of useless spin-polling has three implications:

Energy disproportionality and inefficiency. Spin-polling results in poor energy proportionality [62] as the core energy consumption when spinning is higher than when performing useful work. Moreover, spinning often costs turbo-boost head-room for other (application) cores. We have observed that 8 and 16 cores spinning full-tilt on empty queues reduce the frequency of a core running a regular application from ~3.45 GHz to ~3.25 GHz and ~2.95 GHz in our machine under test, respectively.

Modern datacenter applications usually exhibit low IPCs (often < 1; at most 1.5) on Xeon-class cores [57, 58, 95, 141, 198]. However, as shown in Figure 2.6, software data planes can yield average IPCs of 2-2.6, depending on the load and the number of queues. CPU IPC translates directly to circuit-level switching activity, which drives the switching power of VLSI systems. As a result, we expect cores running data plane software to consume at least 30% more switching power. These effects have also been observed in the case of spin-locks for synchronization-heavy applications [90].

**Faster aging.** Spin-polling also has an adverse effect on processor aging, due to the high

IPC and core power consumption despite doing no useful work. Prior work has reported a 7-10 year lifetime for server-class cores in 32nm technology [210]. We expect shorter nominal core lifetimes in more recent technology, as the aging rate of silicon increases substantially with smaller transistors [172]. Among various physical effects that cause transistor aging, *Negative Bias Temperature Instability (NBTI)* [215] and *Hot Carrier Injection (HCI)* [205] are dominant. HCI, in particular, arises from the cumulative effect of switching activity [172], which correlates with IPC at the microarchitecture level. In comparison to typical server applications, software data planes have higher IPC and never enter sleep states. Given 30% or more higher total activity, spinning core lifetimes may drop below the 5-year threshold, requiring larger supply voltage guard bands (implying higher power) or reduced peak frequency as chips age. Both energy proportionality and server lifetimes are particularly critical in datacenter environments, as they have significant impacts on the Total Cost of Ownership (TCO) [62, 129, 155, 156, 186].