# The Silicon Vertex Detector of the Collider Detector at Fermilab

- D. Amidei <sup>d</sup>, P. Azzi <sup>f</sup>, N. Bacchetta <sup>e</sup>, M.W. Bailey <sup>h</sup>, B. Barnett <sup>c</sup>, F. Bedeschi <sup>g</sup>, D. Bisello <sup>f</sup>,

- V. Bolognesi <sup>g</sup>, C. Boswell <sup>c</sup>, G. Busetto <sup>f</sup>, W.C. Carithers <sup>a</sup>, H. Carter <sup>b</sup>, A. Castro <sup>f</sup>,

- S. Dell'Agnello g, P.F. Derwent d, R. Ducar b, A. Dunn d, R. Ely a, B. Flaugher b, S. Galeotti g,

- A. Barbaro-Galtieri a, A.F. Garfinkel b, C. Haber a,\*, S. Holland a, M. Hrycyk b, D. Herrup b,

- R. Hughes <sup>1</sup>, S. Kleinfelder <sup>a</sup>, M. Loreti <sup>f</sup>, M. Mariotti <sup>f</sup>, J. Matthews <sup>e</sup>, A. Menzione <sup>g</sup>, T. Merrick <sup>a</sup>,

- C. Nelson b, L. Pescara f, N. Produit a, G. Punzi g, F. Raffaelli g, L. Ristori g, O. Schneider a

- S. Segler b, M.D. Shapiro a, N.M. Shaw h, T. Shaw b, J. Skarha c, F.D. Snider c, T.Y. Song d

- A. Spies c, P. Tipton, S. Tkaczyk, F. Tartarelli, J. Tseng, N. Turini, K. Turner, S. Vejcik, C,

- G. Watts i, T.R. Wesson b, W.C. Wester III a, H. Wenzel g, M. Wong a, W. Yao a, F. Zetti g

Received 8 March 1994

A silicon microstrip vertex detector has been constructed and installed in the Collider Detector at Fermilab. The device has been designed to operate at a hadron collider. It began collecting data in May of 1992 and has functioned within specification. Technical details are presented on all aspects of the system and its performance.

#### 1. Introduction

Among the issues of particular interest to high energy physics are the existence and mass of the top quark and the masses, decays, and production dynamics of b hadrons. These issues can be addressed, at least in part, by experiments performed at hadron colliders where the decay products of b hadrons are identified or reconstructed. In the first case, b hadrons should be produced in the decay of top. Their presence, in these typically complex final states, can be used to reject backgrounds. In the second case, b hadrons are produced copiously and directly at low p, in hadron colliders. For example at the Fermilab Tevatron Collider the cross section to produce a b particle with  $p_t > 10 \text{ GeV/}c$  is  $\approx 1.5 \mu \text{b}$ . Consequently hadron colliders can be good sources of b hadrons for study.

A significant distinguishing feature of b hadron decays is their relatively long lifetime ( $c\tau \approx 430 \mu m$ ). This implies the decay may be tagged and also the flight path

Corresponding author. Tel.: (510) 486 7050, fax: (510) 486 5101, e-mail: chaber@csa.lbl.gov.

measured with a sufficiently precise tracking detector. In an attempt to exploit the potential for interesting physics using b hadrons, a detector designed to resolve the event vertices in pp collisions at high energy has been constructed and installed in the Collider Detector at Fermilab (CDF) [4]. This device acquired data between May of 1992 and June of 1993 and functioned well. The capability of precise vertex tracking at CDF figures significantly into a number of physics analyses [1-3]. This detector utilizes silicon microstrip technology to achieve asymptotic impact parameter resolutions of order 10  $\mu$ m and is therefore referred to as the Silicon Vertex Detector (SVX). In this paper we present a comprehensive description of this device, its components, construction, subsystems, on-line and off-line performance, and radiation damage.

# 2. Overview and specification

The Collider Detector at Fermilab was first constructed and commissioned in the mid 1980s for use in the study of

<sup>&</sup>lt;sup>a</sup> The University of California at Berkeley and Lawrence Berkeley Laboratory, Berkeley, CA 94720, USA

<sup>&</sup>lt;sup>b</sup> Fermi National Accelerator Laboratory, Batavia, IL 60510, USA

<sup>&</sup>lt;sup>c</sup> The Johns Hopkins University, Baltimore, MD 21218, USA

<sup>&</sup>lt;sup>d</sup> The University of Michigan, Ann Arbor, MI 48109, USA

<sup>&</sup>lt;sup>e</sup> The University of New Mexico, Albuquerque, NM 87131, USA

<sup>&</sup>lt;sup>f</sup> University of Padova, I-35100 Padova, Italy

<sup>&</sup>lt;sup>8</sup> Istituto Nazionale di Fisica Nucleare, and University and Scuola Normale Superiore of Pisa, I-56100 Pisa, Italy

<sup>&</sup>lt;sup>h</sup> Purdue University, West Lafayette, IN 47907, USA

<sup>&</sup>lt;sup>1</sup> The University of Rochester, Rochester, NY 14627, USA

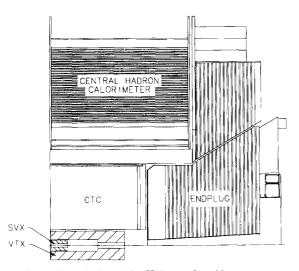

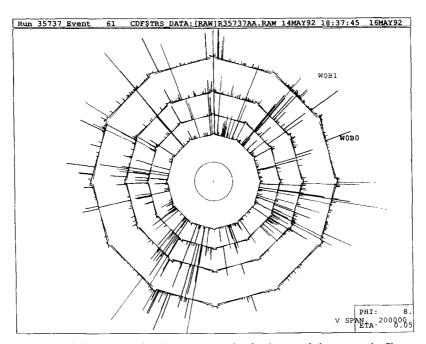

high transverse momentum phenomena. The detector, as originally configured, is described in detail in a series of articles published in Nucl. Instr. and Meth. [4]. The addition of the Silicon Vertex Detector described here is an upgrade to the original CDF tracking system. The feature of the original tracking system most relevant to the design and operation of the SVX is the magnetic spectrometer. This is comprised of a 1.41 T superconducting solenoid enclosing a cylindrical drift chamber, (the CTC [5]) of outer radius 1.32 m. This central tracking chamber contains both axial and stereo wire layers but tracks with higher resolution in the  $r\phi$  (transverse) plane. The performance of this chamber in conjunction with the SVX is described in Section 14. Fig. 1 shows the overall layout of the CDF central detectors including the SVX.

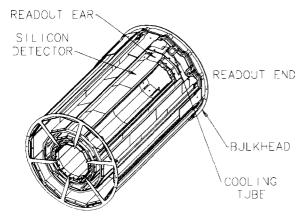

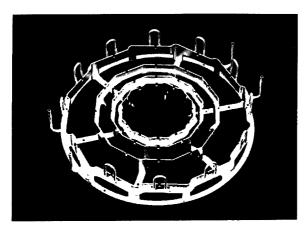

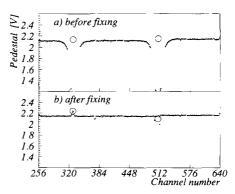

The Silicon Vertex Detector for CDF was designed to operate in the environment imposed by the Fermilab Tevatron Collider [6]. The consequences of this will be discussed in this section where we describe the design specifications of the device. Table 1 summarizes the operating parameters of the Tevatron Collider. Fig. 2 is a view of the SVX, and Table 2 summarizes its features. The organization of this section mirrors the body of the paper.

In developing this new detector for CDF, a number of general principles and specifications were followed. These led to various technical tradeoffs and design choices. These basic items were as follows:

- Detector performance should match the requirements of b decay reconstruction.

- The detector should be extended longitudinally to cover as much of the Tevatron luminous region as possible.

- The detector should have sufficient redundancy and granularity to handle complex events.

- The inner radius should be as small as possible to obtain the best impact parameter resolution.

Fig. 1. Overall view of the CDF central tracking system.

Table 1 1992–1993 Tevatron Collider operating parameters

| Beam:                 | proton-antiproton                                  |

|-----------------------|----------------------------------------------------|

| Beam Energy:          | 900 GeV/beam                                       |

| Luminosity:           | $10^{30} - 10^{31} \text{ cm}^{-2} \text{ s}^{-1}$ |

| Bunches/Beam:         | 6                                                  |

| Bunch Spacing:        | 3.5 µs                                             |

| Collision Region RMS: | 30 cm                                              |

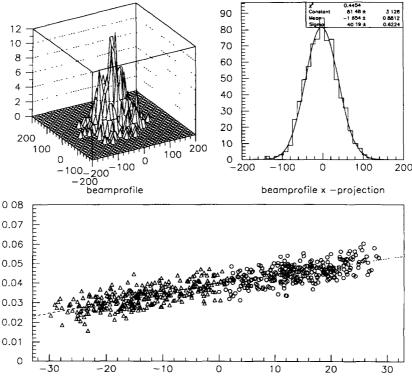

| Beam Spot:            | ≈ 40 µm                                            |

| Beam Pipe:            | 1.5 in. diameter                                   |

| •                     |                                                    |

- The mass of the detector should be minimized to reduce multiple scattering and photon conversions.

- The detector should function with the existing CDF tracking and data acquisition systems.

- Technological choices should be geared towards reliability and not an excessive use of new or untested concepts.

These principles led to a design which favoured redundant measurements of tracks in the  $r\phi$  (transverse) plane over full three dimensional tracking. Consequently we opted to install four concentric cylindrical layers of single sided silicon detectors rather than utilize the newer double sided detector technology. In addition we opted to concentrate effort on developing readout and data acquisition electronics which could efficiently filter out empty channels as early as possible. We wanted the event size and readout time to be determined by occupancy rather than channel count.

## 2.1. Mechanical configuration

At the Tevatron Collider, the  $\bar{p}p$  interaction vertex is Gaussian like distributed along the beamline with  $\sigma=30$  cm. Consequently a long vertex detector is required to have any reasonable acceptance. Long strips can impose a burden on the readout electronics due to increased input capacitance and leakage current. The SVX active region is 51 cm long and consists of two independent cylindrical modules of equal length. A gap of 2.15 cm exists at the center of the detector. The acceptance is  $\approx 60\%$  of the  $\bar{p}p$  collision vertices.

The SVX consists of four concentric cylindrical layers (numbered 0-3 in increasing radius). The inner and outer layers are at radii of 3.005 cm and 7.866 cm, respectively. The location of the inner layer is set by a combination of the readout electronics segmentation and pitch, and the minimum beampipe radius acceptable to the accelerator group at Fermilab.

The amount of material in the SVX has been minimized. This is because the creation of secondary particles and conversion pairs in SVX will be a source of background for all CDF detectors and triggers. In addition multiple scattering will be the limiting factor in measuring

Fig. 2. Isometric view of one barrel of the silicon vertex detector.

the impact parameter of low momentum tracks. And finally the presence of material in the path of electrons from the decay of W bosons will be a source of systematic uncertainty in the determination of the W mass which is an important experimental goal of CDF as well.

## 2.2. Silicon detectors

Number of layers:

In recent years AC coupled silicon microstrip detectors have become the favored technology for vertex detectors. However, at the time the technology choice was made for the SVX the AC coupled detectors were judged as still too developmental. Consequently an emphasis was put on having high quality single sided DC coupled detectors in a

four inch technology and readout electronics which would be relatively immune to strip to strip leakage variations.

#### 2.3. Front end electronics

The front end electronics process signals coming from the silicon strips and communicate with the data acquisition electronics located external to the collision region. The front end system must operate within the timing requirements set by the Tevatron Collider. It must keep all sources of noise within specified levels and handle loads due to detector capacitance and leakage current. Power dissipation in the front end should be minimized. The front end system consists of a readout chip bonded directly to the strips, mounting hybrids, interface circuits to drive and receive signals, regulate power, and provide calibration pulses and low mass interconnections between detector modules.

## 2.4. Cooling

Heat generated by the SVX readout electronics, and also due to surrounding detectors, may lead to relative motions of detector components, mechanical instability, damaging stresses, excessive leakage current, and failure of electrical components. For these reasons a cooling system is required which can remove  $\approx 100$  W while maintaining an operating temperature close to that present during construction,  $\approx 20^{\circ}$ C. A further requirement is that the cooling system not contribute excessive mass. With local sources of heat, liquid cooling is the natural choice.

Table 2

Basic Parameters of the CDF Silicon Vertex Detector

| Strip pitch: $60 \mu m \text{ layers } 0-2, 55 \mu m \text{ layer } 3$ Active length: $51 \text{ cm } (2 \times 25.5 \text{ cm with a } 2.15 \text{ cm gap})$ Resolution: asymptotic impact parameter $\approx 10 \mu m$ Technology: single sided DC coupled silicon microstrips  Front end readout: SVX Revision D IC with sparse scan  Signal-to-noise ratio: $9-10$ for normal incidence, most probable MIP  Number of channels: $46080$ |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Resolution: asymptotic impact parameter $\approx 10~\mu m$ Technology: single sided DC coupled silicon microstrips Front end readout: SVX Revision D IC with sparse scan Signal-to-noise ratio: 9–10 for normal incidence, most probable MIP Number of channels: 46080                                                                                                                                                                      |

| Technology: single sided DC coupled silicon microstrips Front end readout: SVX Revision D IC with sparse scan Signal-to-noise ratio: 9–10 for normal incidence, most probable MIP Number of channels: 46080                                                                                                                                                                                                                                 |

| Front end readout: SVX Revision D IC with sparse scan  Signal-to-noise ratio: 9–10 for normal incidence, most probable MIP  Number of channels: 46080                                                                                                                                                                                                                                                                                       |

| Signal-to-noise ratio: 9–10 for normal incidence, most probable MIP Number of channels: 46080                                                                                                                                                                                                                                                                                                                                               |

| Number of channels: 46 080                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Number of chine                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Number of chips: 360                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Power dissipation: ≈ 175 mW/chip                                                                                                                                                                                                                                                                                                                                                                                                            |

| Total power: ≈ 100 W (includes drivers, regulators)                                                                                                                                                                                                                                                                                                                                                                                         |

| Cooling: chilled water (14°C)                                                                                                                                                                                                                                                                                                                                                                                                               |

| Beam collision period: $3.5 \mu s$                                                                                                                                                                                                                                                                                                                                                                                                          |

| Support materials: rohacell, beryllium, alumina, aluminum nitride                                                                                                                                                                                                                                                                                                                                                                           |

| Segmentation: projective wedge (30° azimuth) = 1 readout unit.                                                                                                                                                                                                                                                                                                                                                                              |

| DAQ system: RABBIT + Fastbus                                                                                                                                                                                                                                                                                                                                                                                                                |

| Readout time: $1-2 \text{ ms}$                                                                                                                                                                                                                                                                                                                                                                                                              |

| Typical occupancy: 7%                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Radiation exposure: 15–20 krad over lifetime                                                                                                                                                                                                                                                                                                                                                                                                |

The SVX is cooled primarily by flowing chilled water under the readout chips in thin aluminum pipes.

# 2.5. Data acquisition system

The DAQ system is required to integrate into the existing hardware, software, and maintenance structure of CDF. It has to contain sufficient parallelism and bandwidth not to introduce any additional deadtime in the CDF readout. Finally it has to provide the required timing and control signals and diagnostic capabilities needed by the front end readout chips.

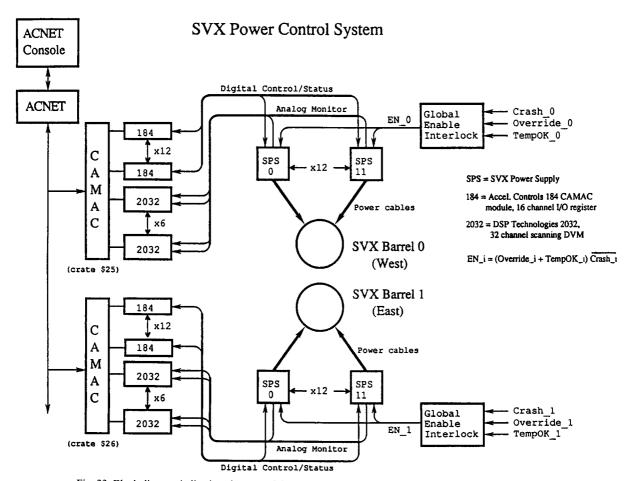

# 2.6. Power supplies and interlocks

The SVX detector requires power supplies to provide detector bias and operating voltages and currents for the front end chips and interfacing electronics. Due to the remote location of the detector, the power supplies have to protect the system from a range of possible failures and provide fast trip capability with latching of trip conditions. The supplies need to be remotely controlled and monitored. Finally, the power supplies, cooling system, and temperature monitors need to be integrated into an overall interlock system.

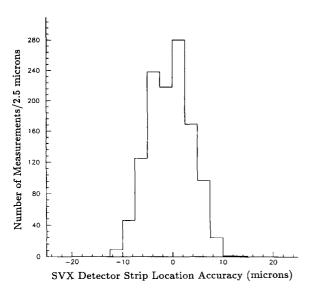

#### 2.7. Construction and testing

In the construction of the detector the scale of the mechanical tolerances must be comparable to the intrinsic position resolution of the strip detectors. In this case the position resolution should be  $\approx 10~\mu m$  using charge sharing information on neighboring strips. In order to achieve position information with similar resolution in the completed SVX detector, the construction errors must then be on order 10  $\mu m$  or less. This requires care in the choice of materials and assembly techniques and extensive survey during construction and installation.

Since the installed device will be difficult to access during the experiment the electrical systems internal to the barrel must be very reliable. Furthermore to ensure good data quality all components must be tested and characterized before assembly.

## 2.8. Radiation monitoring

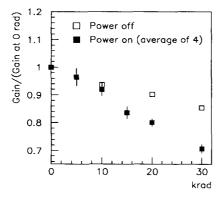

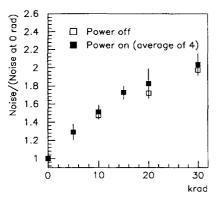

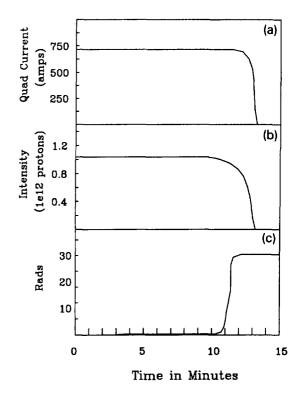

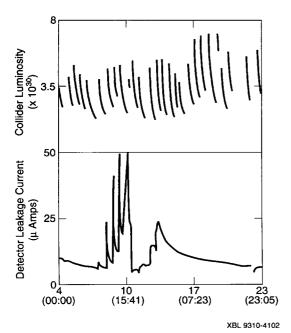

The SVX detector was conceived to operate during a period when the Collider delivered luminosity would approach 30 pb $^{-1}$ . Studies of radiation levels in the Tevatron Collider indicated that the expected dose would be  $\approx 400$  rad/pb $^{-1}$ . The electronics and detectors should tolerate this dose with acceptable degradation. Furthermore, it was recognized that the additional dose due to accidents in collider operation,  $\bar{p}p$  injection, and studies could be reduced through the use of a system of monitors placed around the collision region and a dose driven abort system

for the beams. Such a monitoring system is a valuable tuning aid for the accelerator operators.

#### 2.9. Calibration

On-line calibrations of the detector include measurements of pedestals, gains, noise, and other electrical parameters. Due to the large channel count such procedures can generate large amounts of data which can be difficult to filter and evaluate. Specific procedures and analysis tools are required to readily monitor detector performance and provide constants and correction factors for off-line analysis.

## 2.10. Off-line analysis

Reconstruction code for data generated by the SVX must integrate into the existing CDF framework. Specifically, SVX tracking has to link with the CTC reconstruction and provide a capability for refit with SVX hits added to tracks. In addition, new tools are required for vertexing and beamline determination. Finally an alignment procedure using tracks is required to compare with and improve optical alignment constants from construction and survey.

## 3. Mechanical Design

# 3.1. Configuration

The SVX overall layout is shown in Fig. 2. The SVX is located with its center on the nominal CDF interaction point and consists of two cylindrical modules placed end to end with their axes coincident with the beam axis. Cylindrical coordinates are used here with the z axis parallel to the beamline, the  $\phi$  coordinate giving the azimuth, and the radial coordinate, r, measured along a direction perpendicular to the beamline. The SVX provides track measurements in the  $r-\phi$  plane only.

The SVX is mounted inside the Vertex Time Projection Chamber (VTX) [7]. This is a another tracking system which instead measures the event in the r-z plane. It is used to locate the longitudinal position of the interaction vertex along the beamline and seed the CTC three dimensional reconstruction. While the SVX and VTX have little connection in the off-line analysis of track data, they are intimately coupled in an operational sense. Both detectors share the same argon/ethane gas volume and cabling flanges. Noise generated in the SVX can affect the VTX. The overall mechanical stability of the SVX relies on the VTX support.

The SVX consists of four radial layers of silicon strip detectors. These detectors are arranged as a twelve sided barrel at each radial position. The detectors are electrically bonded to each other along the beam direction in groups of three. These bonds are made with 25  $\mu$ m aluminum wire

which is ultrasonically fused to pads on the detector surface. At each radius and on each of twelve faces there are thus a total of six detectors, in two groups of three. These are read out electronically at the two outside ends. Each detector is 8.5 cm long so that an individual readout channel sees a 25.5 cm long strip. The total longitudinal coverage is thus 51 cm. A gap of 2.15 cm exists between the two barrels. The source capacitance of each strip is about 30 pF.

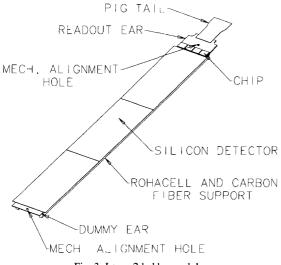

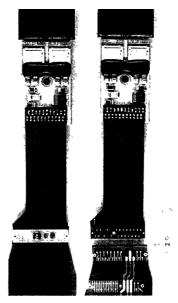

A group of three connected detectors is called a ladder, and is the basic subdivision of the device (Fig. 3). The ladder substrates are fabricated of Rohacell, a light weight foam, and reinforced with carbon fiber strips. Each ladder is individually assembled and mounted. There are four sizes of ladders corresponding to the four radial layers. The total number of ladders is 12 faces  $\times$  4 layers  $\times$  2 ends = 96, or 24 of each size. In its position on the face of the barrels, each ladder is rotated by 3° about its major axis to allow some overlap between adjacent faces. However, on the innermost layer no such overlap exists. At the outside end of each ladder sits a small circuit board. This circuit is the readout hybrid for the ladder. It contains the readout chips (Section 5.1) for that ladder as well as auxiliary components and buswork needed for the operation of the chips. A photograph is shown in Fig. 4. These boards are fabricated using a multilayer thick film process on 0.015 in. thick aluminum nitride (AIN) [8]. The readout hybrid also receives cables going to other layers carrying various bussed signals. These cables, fabricated as Kapton flexible circuits, are removable in the case of repair. The hybrid is thermally isolated from the silicon detector to prevent conduction of heat generated by the readout electronics into the detector. A second dummy board, sits at the opposite end of the ladder for mechanical connection to the support structure (described below). Both the read-

Fig. 3. Layer 2 ladder module.

Fig. 4. Photograph of an SVX readout hybrid for layer 3. This unit contains six SVXD readout chips serving 768 channels. High density wirebonds to the silicon strip detectors are seen at the top.

out hybrid and the dummy board are laser cut and contain a precision mounting hole to allow for the alignment of ladders with respect to a support structure. A group of four ladders at fixed azimuth projects back to the interaction point. This unit is called a *wedge*.

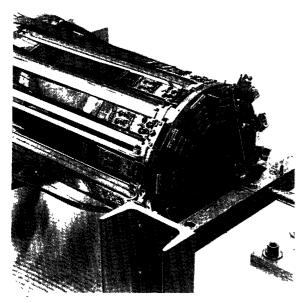

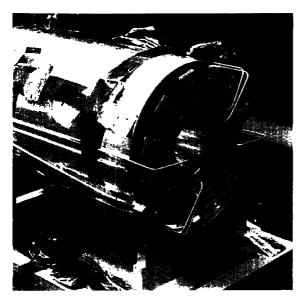

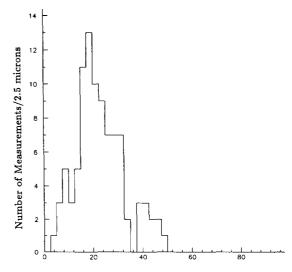

The SVX ladders are installed between two support pieces known as bulkheads using a small screw, O-ring and tapped pin combination which fits through the mounting holes of the ears and attaches to slots machined into the ledges of the bulkheads. The slots in the bulkhead allow the ladder to expand thermally along its length while maintaining good azimuthal location. These bulkheads were made from beryllium to reduce their contribution to the total radiation lengths for the completed SVX detector. Besides being low mass, the bulkheads have been machined very accurately [9] and typically the four circles on which the ladders are mounted have been made concentric to within 15  $\mu$ m. A photograph of one bulkhead, including cooling pipes, is shown in Fig. 5.

In the complete device, an external conductive cylindrical skin surrounds each barrel to isolate it from e.m. noise, external HV breakdown, and to add rigidity to the system. This shield also protects external detectors from noise which may be generated by switching within the SVX. The skin is fabricated as a sandwich of two layers of 50  $\mu$ m Aluminum separated by 1.5 mm of Rohacell foam. Details of the detector geometry are given in Table 3.

# 3.2. Material budget

A detailed material budget of the SVX was tabulated during design and construction. A breakdown is given in Table 4. Note that many of the items are further defined in later sections. After completion, the detector assembly was weighed and good agreement was found with calculations.

Fig. 5. Photograph shows one bulkhead prior to mounting on the barrel assembly fixture. Aluminum cooling pipe can be seen along the ledges. Loops are for cooling the port cards.

Table 3 SVX Geometry

| (a) Barrel geo |             |             |

|----------------|-------------|-------------|

|                | Radius [cm] | Length [cm] |

| Layer 0        | 3.005       | 25.6        |

| Layer 1        | 4.256       | 25.6        |

| Layer 2        | 5.687       | 25.6        |

| Layer 3        | 7.866       | 25.6        |

## (b) Silicon crystal geometrical dimensions

|         | Width<br>[ μm] | Length<br>[ μm] | Thickness [ μm] |

|---------|----------------|-----------------|-----------------|

| Layer 0 | $16040 \pm 50$ | $85000\pm 50$   | $300 \pm 15$    |

| Layer 1 | $23720 \pm 50$ | $85000 \pm 50$  | $300 \pm 15$    |

| Layer 2 | $31400 \pm 50$ | $85000 \pm 50$  | $300 \pm 15$    |

| Layer 3 | $42930\pm50$   | $85000\pm50$    | $300\pm15$      |

#### (c) Characteristics of the active area of the detectors

|         | Width [ µm] | Pitch<br>[μm] | Readout<br>strips | Number of chips | Length<br>[μm] |

|---------|-------------|---------------|-------------------|-----------------|----------------|

| Layer 0 | 15 360      | 60            | 256               | 2               | 84 500         |

| Layer 1 | 23 040      | 60            | 384               | 3               | 84 500         |

| Layer 2 | 30720       | 60            | 512               | 4               | 84500          |

| Layer 3 | 42 240      | 55            | 768               | 6               | 84500          |

## (d) Coverage in polar angle

|         | Theta      | Eta       |  |

|---------|------------|-----------|--|

| Layer 0 | ±6.3       | ± 2.9     |  |

| Layer 1 | $\pm 9.5$  | $\pm 2.5$ |  |

| Layer 2 | $\pm 12.6$ | $\pm 2.2$ |  |

| Layer 3 | ± 17.2     | ± 1.9     |  |

|         |            |           |  |

Table 4

Accounting for material in the SVX construction (in grams). Items listed as ? are not well known but are all very small (few gram range)

| Material          | L0   | L1   | L2   | L3   | SUM  | ×12   |        |

|-------------------|------|------|------|------|------|-------|--------|

| Silicon           | 2.9  | 4.2  | 5.6  | 7.7  | 20.4 | 244.7 |        |

| Support           | 2.2  | 2.9  | 3.2  | 3.3  | 11.6 | 139.7 |        |

| Hybrids,glue etc. | 2.0  | 2.6  | 3.4  | 4.9  | 12.9 | 155.3 |        |

| Subtotal          | 7.1  | 9.7  | 12.2 | 15.9 | 44.9 | 538.3 | 538.3  |

| External Screen   |      |      |      |      |      |       | 53.9   |

| Internal Screen   |      |      |      |      |      | ?     | ?      |

| Port Card         |      |      |      |      | 8.7  | 104.0 |        |

| Clamps and Bus    |      |      |      |      | 2.3  | 27.8  |        |

| External Cables   |      |      |      |      | 10.1 | 121.2 |        |

| External Tubes    |      |      |      |      |      | 29.0  |        |

| Heat Exchanger    |      |      |      |      |      | 30.5  |        |

| Gas Manifold      |      |      |      |      |      | ?     |        |

| Water             |      |      |      |      |      | 40.0  |        |

| Subtotal          |      |      |      |      |      | 352.5 | 352.5  |

| Bulkhead          | R/O  | Dum  |      |      |      |       |        |

| Beryllium         | 40.7 | 25.6 |      |      |      |       |        |

| Al Tubes          | 17.8 |      |      |      |      |       |        |

| Al Port           | 11.6 |      |      |      |      |       |        |

| Other             | 6.0  |      |      |      |      |       |        |

| Glue              | 8.5  |      |      |      |      |       |        |

| Subtotal          | 84.6 | 25.6 |      |      |      |       | 110.2  |

| Grand Total       |      |      |      |      |      |       | 1054.9 |

| Measured          |      |      |      |      |      |       | 1017.0 |

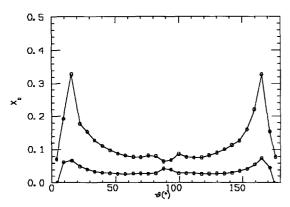

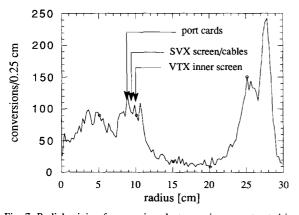

Furthermore, this accounting is used as input to software which returns the number of radiation lengths traversed by any track passing through the SVX given its trajectory. Such a code is useful for estimating conversion rates and radiative effects on electrons from W decay. The module is also used in Monte Carlo simulations of CDF. In Fig. 6 we present calculated material thicknesses for the total SVX system alone (including cabling) and for the total SVX + VTX + CTC inner support structure. Also shown is the effect of smearing the Tevatron beam spot with a  $\sigma$  of 30 cm. One method to check the effect of SVX material is to plot the radius of origin for conversion electrons. These conversions are identified by an algorithm which searches for tracks near an electron candidate reconstructing with the electron to a small invariant mass. In Fig. 7 we show this distribution. As indicated, the geometrical boundaries of the SVX are visible but the total rate is comparable to other sources.

#### 3.3. Expected performance

Given the strip geometry, positions of detector planes, material distributions in the SVX, and the parameters of

Fig. 6. Calculated material traversed by a particle passing through the SVX. In ((a) we show the radiations lengths due both to the SVX alone (including all cables and plumbing) and to everything inside the first tracking layer of the CTC. All tracks originate from the origin. In ((b) we show the effect of smearing the Tevatron luminous region with a  $\sigma$  of 30 cm.

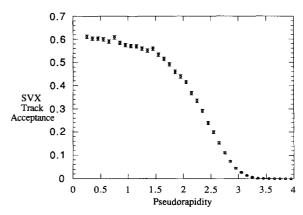

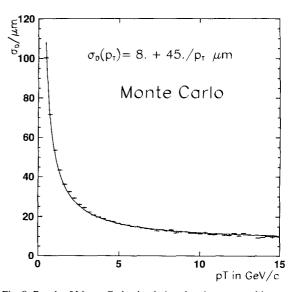

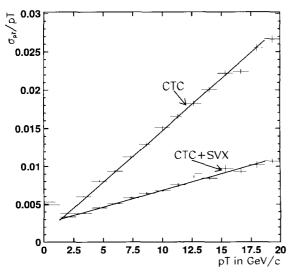

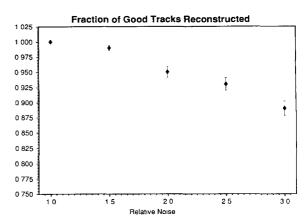

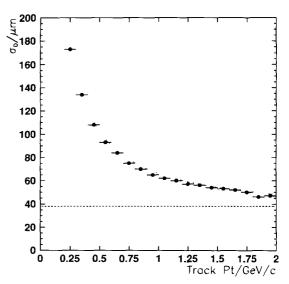

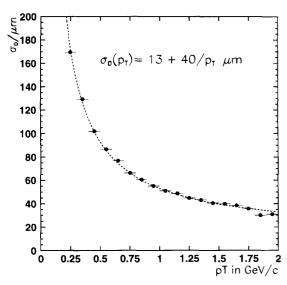

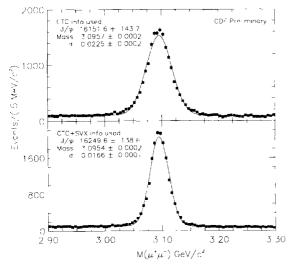

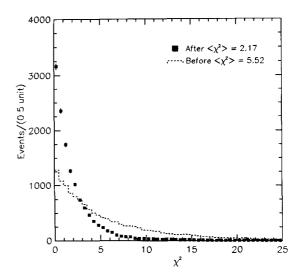

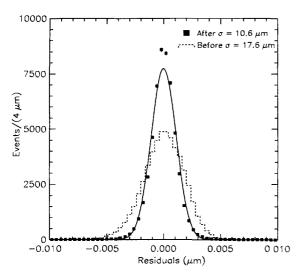

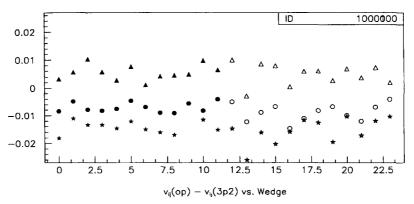

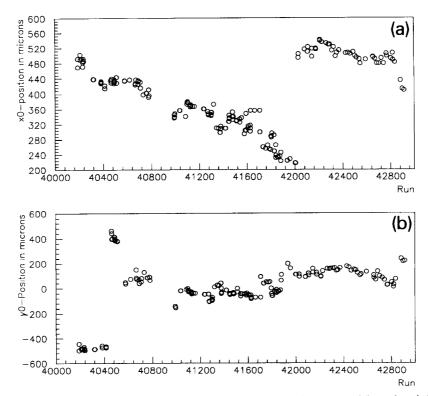

the CDF magnetic spectrometer an ideal expected performance may be inferred. In the actual device the performance will be degraded by misalignment, miscalibration, dead regions, and noise. Based upon Monte Carlo studies and calculations, a set of performance baselines have been determined for the SVX. In Fig. 8 we show the track acceptance as a function of track rapidity. The effect of the extended luminous region is clear. In Fig. 9 we show the track impact parameter resolution versus transverse momentum. The asymptotic impact parameter resolution is 8  $\mu$ m. Due to multiple scattering it drops to 53  $\mu$ m at 1 GeV/c. For tracks which originate at the primary interaction vertex, it is possible to perform a vertex constrained fit using the CTC alone. However for a track coming from a secondary vertex the SVX can be used to improve the momentum resolution. This is indicated in Fig. 10.

Fig. 7. Radial origin of conversion electron pairs reconstructed in CDF. Various geometrical boundaries within the SVX are indicated.

Fig. 8. Single track acceptance of the SVX versus track pseudorapidity including the effects of the long collision region.

#### 4. Silicon detectors

#### 4.1. Detector design

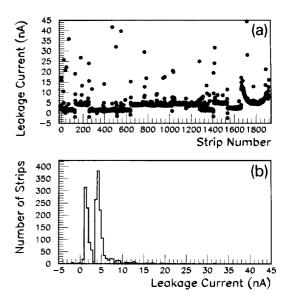

The silicon detectors used in the ladder construction are DC coupled and single sided. They were manufactured by Micron Semiconductor Ltd. [10]. For layers 0, 1 and 2 the strips are on a 60  $\mu$ m pitch. For layer 3 they are on a 55  $\mu$ m pitch. The processing steps used in fabrication were optimized for low surface leakage current. In particular, a final sintering step at 400°C in forming gas served to lower the average strip leakage to 300–500 pA for an 8.5 cm strip at 20°C. Consequently the full leakage for a ladder strip was less than 2 nA before irradiation. The detectors all have fully enclosing guard rings which were always

Fig. 9. Result of Monte Carlo simulation showing expected impact parameter resolution for ideal SVX geometry and point resolutions as specified in design.

grounded through the preamplifier ground on the readout chip. Typical guard ring currents are significantly higher than single strip currents, in the few hundred nA range. It is important that the total detector current (including the guard ring) not be too high because shot noise can cause large fluctuating voltage drops across a 10 k  $\Omega$  filtering resistor which is in the bias line. The drops will cause charge to be injected into the readout chip through the detector capacitance which will appear as common mode noise on all read out channels connected to that detector.

## 4.2. Quality control

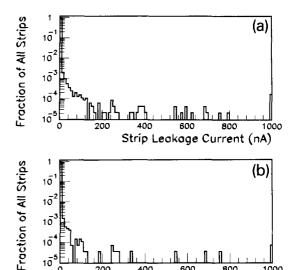

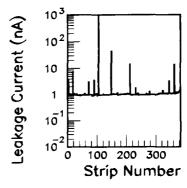

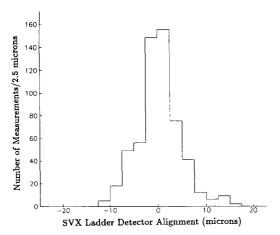

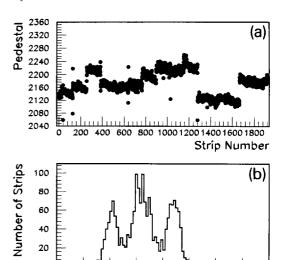

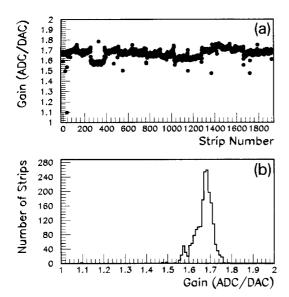

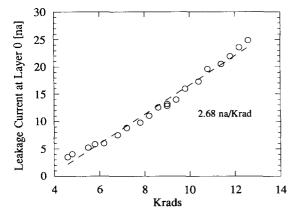

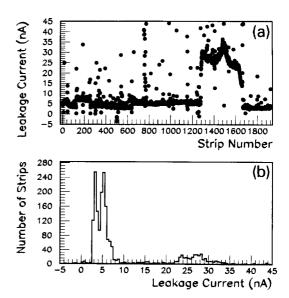

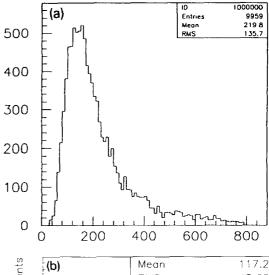

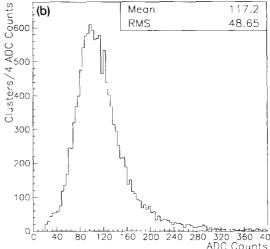

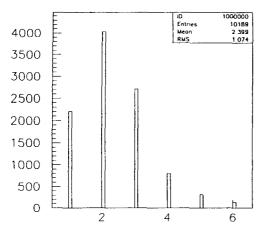

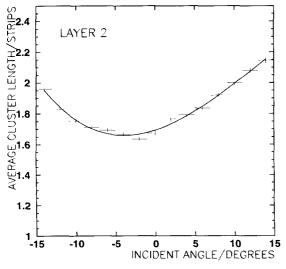

All strips on all silicon detectors used in the SVX were probed both at the manufacturer and at Fermilab during construction. Leakage currents and interstrip resistances were measured. An acceptance specification was applied to the silicon detectors based upon these measurements. A basic principle of this specification was to limit the number of strips with current above 70 nA. These are useless and had to be skipped during wirebonding. Fig. 11a shows the distribution of leakage currents for all the probed strips on Layer 2 detectors. Fig. 11b shows those which were used in the SVX only. The distributions for the other layers are similar. The strip to strip leakage on a typical good detector is shown in Fig. 12.

#### 5. Front end electronics

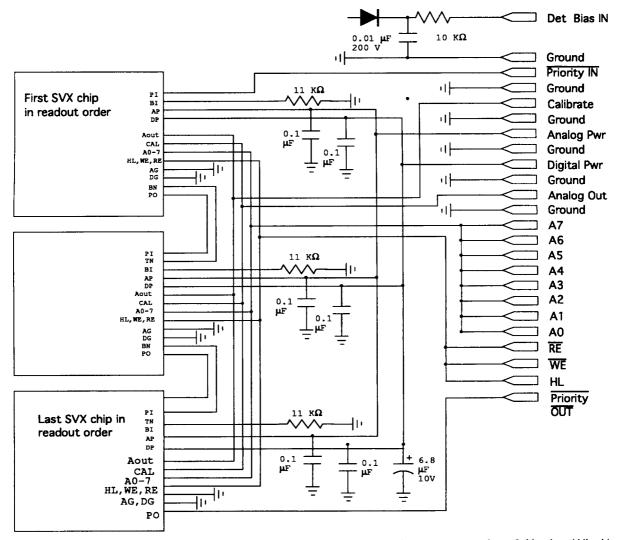

A group of four radial layers subtending 15° of azimuth form a wedge of the SVX detector and are an independent readout unit. The full detector consists of 24 wedges. Each wedge contains 1920 silicon microstrips. The overall elec-

Fig. 10. Improvement in momentum resolution of the CDF tracking system when SVX points are included in fit.

Fig. 11. Distribution of individual strip leakage currents for (a) all layer 1 detectors, (b) for layer 1 detectors which were used in the construction of the SVX. These distributions are typical of all layers.

Strip Leakage Current (nA)

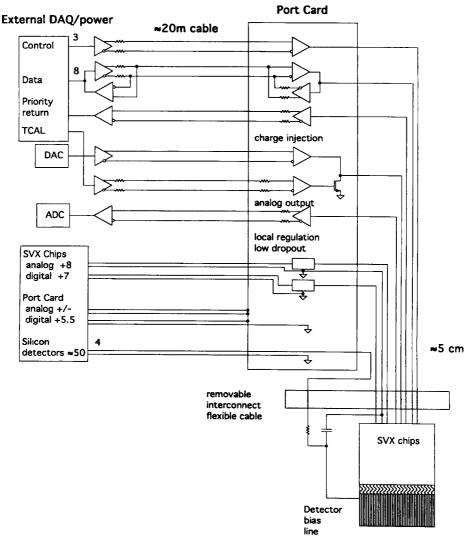

trical layout of a wedge is shown in Fig. 13. The front end readout circuit is the SVX chip Rev. D [11,12]. There are 2,3,4, and 6 of these per layer respectively. The chips are mounted on readout hybrids and the four layers are bussed up to an interface hybrid called the *Port Card*. Finally signals going into the port card are carried through the SVX barrel and out of the VTX on low mass etched copper on Kapton cables.

In this section we detail the elements of the front end system.

## 5.1. The SVX readout integrated circuit

The SVX chip is a mixed analog and digital signal processing circuit. Rev. D (SVXD), which is used in the

Fig. 12. Profile of individual strip leakage currents on a single typical crystal for the production sample.

final SVX system, was fabricated in 3  $\mu$ m CMOS technology. The CMOS process used was not radiation hard [13].

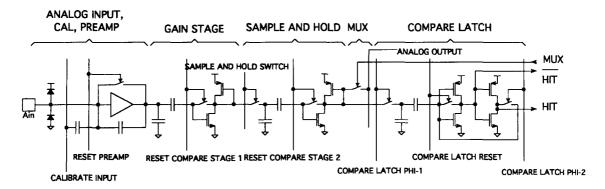

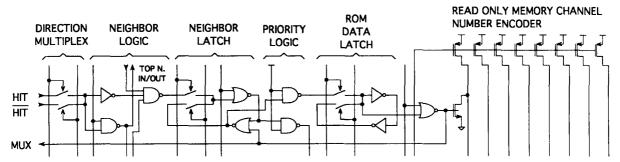

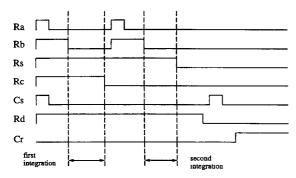

A block diagram of the SVXD chip and timing pattern is shown in Fig. 14 and Fig. 15. The chip contains 128 identical channels of charge integration, voltage amplification, sample and hold, and comparator/latch. These are followed by a priority encoding circuit which allows a multiplexed analog readout to select only those channels for which the latch is set (or not set). This selective readout mode is called *sparse*. Optionally, a global latch line may be asserted forcing a readout of all channels. This mode of readout is called *latch all*. When the chip is read out, the address of the channel currently being read appears on a 7 bit address bus along with the corresponding

analog level. The characteristics of the the SVXD readout chip are summarized in Table 5.

The SVXD chip was designed to read out DC coupled silicon detectors. In order to have an unbiased threshold comparison on a channel by channel basis it is necessary to subtract the baseline shift due to varying strip to strip leakage current which will be integrated during the sampling time. This process is accomplished in the SVXD chip through a quadruple sample and hold process. In this process, the charge is integrated twice (once *on beam* and once *off beam*). The results of these two integrations are subtracted. If any particles had passed through the detector *on beam* an excess would remain at the nearest strip.

In a charge integration and sample and hold circuit one

Fig. 13. Schematic diagram indicating the electrical layout of one SVX wedge and its connection to the external DAQ and power supply systems.

Fig. 14. Block diagram indicating the functional units of one channel of the SVXD readout chip.

integration from time  $t_1$  to time  $t_2$  would use two samples in order to cancel offsets due to pileup and internal charge injections. This is a double sample and hold measurement. The leakage current subtraction described here requires two integrations and is consequently a quadruple sample and hold measurement.

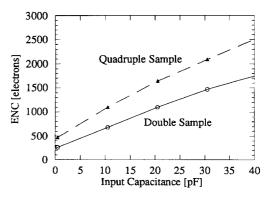

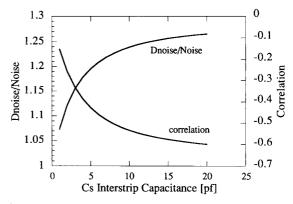

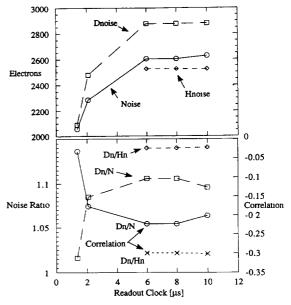

When the analog system noise is measured, a double sample-and-hold will increase the intrinsic preamplifier noise by a factor of  $\sqrt{2}$  for frequencies which are short compared to the inverse of the integration time. A quadruple sample and hole will contribute another factor of  $\sqrt{2}$  to double the intrinsic noise. In Fig. 16, we show the equiva-

Table 5

Basic operating parameters of the SVX readout chip, Rev. D

| Technology:                                 | 3 μm rad–soft CMOS                       |

|---------------------------------------------|------------------------------------------|

| Dimensions:                                 | ≈ 6.9 mm square                          |

| Number of channels/chip                     | 128                                      |

| Power dissipation                           | 175 mW/chip                              |

| Gain of analog channel                      | 15  mV/fC                                |

| Open loop gain                              | ≈ 2000                                   |

| Nominal feedback capacitor                  | 0.3 pF                                   |

| Nominal value of charge injection capacitor | 0.06 pF                                  |

| Range of front end (approx)                 | 10 MIP                                   |

| Leakage current (3 Si detectors (pre-rad))  | 3 nA/strip                               |

| Equivalent input noise (30 pF, quad sample) | $2200-2400 e^-$                          |

| Risetime at sample and hold capacitor       | 900 ns (10%–90%)                         |

| Reset time of charge integrator             | 700 ns                                   |

| Maximum digital readout speed               | 10 MHz                                   |

| Risetime of analog output                   | (exponential $\tau$ ) = 800 ns           |

| Analog supply voltage                       | 6 VDC                                    |

| Digital supply voltage                      | 5 VDC                                    |

| Digital data bits                           | 6 chip ID + 2 mode; 7 chan addr + 1 mode |

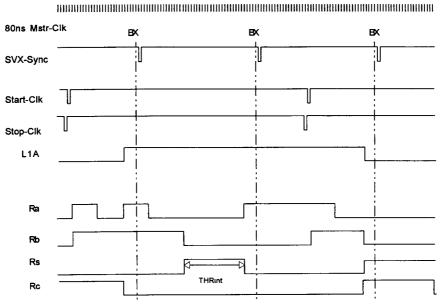

Fig. 15. Basic quadruple sample and hold timing diagram for the SVXD chip. The actual timing used in operation differs slightly from this and is discussed in the DAQ section of the text.

lent input noise (output noise voltage converted to input charge) of the SVXD chip as a function of detector capacitance for both a double and quadruple sample and hold measurement. The fully bonded SVX ladders correspond to about 30 pF of detector capacitance.

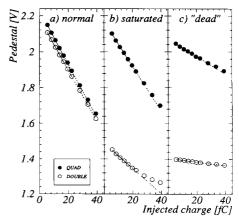

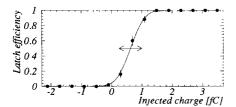

The behaviour of the comparator circuit in the SVX chip which controls the sparse readout will be affected by the electronic noise. Rather than having a perfectly sharp transition at threshold, the transition will be spread. The threshold value and its width can be measured by performing a quadruple sample and hold integration and observing the fraction of time a particular channel appears in the readout as the test input charge is varied for one of the two integration periods. A typical channel response is shown in Fig. 17. It is possible to unfold the width of the underlying Gaussian noise distribution from this curve by a method discussed in Section 10.2.3. For good channels this quantity is 0.4–0.5 fC which corresponds to the quadruple noise shown in Fig. 16.

The absolute value of the threshold itself is a quantity which will be affected by chip to chip variations in internal offsets, errors in the leakage current subtraction due to timing and preamplifier saturation, and parasitic charge injection related to the layout of the electrical system on the SVX. The requirement for efficient operation of the detector is to keep these variations at the same level as the threshold width. This is discussed further in Section 10.2.3.

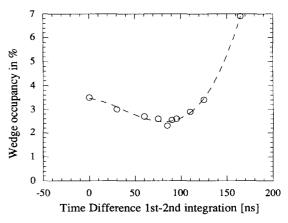

One subtlety of the threshold comparison using a quadruple sample and hold procedure concerns the relative duration of the two integration periods needed to measure the leakage current off and on beam. The sample and hold capacitors which store the integrated leakage current are labeled  $C_s$  and  $C_c$  in Fig. 14. During the first leakage current measurement both capacitors are a load on the output of the inverter labeled Comp1. During the second integration the switch  $R_c$  is open and the load is only due to  $C_s$ . Consequently the risetime of Comp1 is slightly different in the two cases. To get an optimal subtraction the two integration periods should differ by this risetime difference. We call this requirement the  $\Delta T$  effect. In the

Fig. 16. Equivalent input noise charge of the SVXD chip as measured on the test bench with discrete input capacitors.

SVX detector application, the integration period can only be set to the accuracy of the clock generation circuitry. As is discussed in Section 7.3.1, a design feature of the DAQ electronics, which drive the SVXD readout chips, is to allow for sufficient timing variation for an accurate leakage current subtraction. In Section 11.1 we discuss a procedure used during calibration of the full detector to set these timing differences optimally.

#### 5.2. Readout hybrids

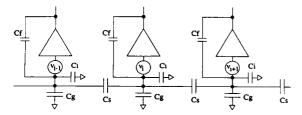

The basic function of the readout hybrids is to distribute power, ground, and signals to the SVXD chips. In addition, they contain bypassing capacitors for the power lines, resistors to set the current in the SVXD chip integrator, and and a filter for the detector bias line. An electrical schematic is shown in Fig. 18.

Corresponding to the ladders there are four versions of the these hybrids [14]. Layers 0, 1, and 2 are fabricated in 0.015 in. AIN (aluminum nitride), while layer 3 is fabri-

Fig. 17. Charge response of the SVXD chip for double and quadruple sample and hold. Effects of saturation and leakage subtraction are indicated. These curves are discussed in the text.

cated in 0.025 in. AlN. This unusual type of substrate was chosen for its good thermal conductivity (about 5 times higher than for the more commonly used Al<sub>2</sub>O<sub>3</sub>). Circuitry is patterned on both sides with through hole connections using a thick film technology. A larger number of layers were printed on the top side (SVXD chip side) and consequently a small bowing of approximately 0.001 in. was measured due to the higher coefficient of thermal expansion of the circuit dielectric layers over the AlN substrate. For layer 3, which has the largest aspect ratio, the thicker substrate material was chosen to limit this bowing.

The AlN technology choice improved the thermal performance of the detector but required a substantial developmental effort because the thick film system available for this material was not mature. The thermal performance of these circuits is further discussed in Section 6.2.

#### 5.3. Interface circuits

Each readout wedge of the SVX is serviced by an interface card which sits at a radius of 8.81 cm, just beyond the outermost tracking layer. This *Port Card* is fabricated on 0.025 in. thick Alumina in multilayer thick film process. The layout of this card is considerably more complex than the readout hybrids. It is constructed with seven conducting layers and a total of 35 separate photomasks. Due to this complexity and also uncertainties in the reliability of the AIN thick film process for this large number of layers the choice of the more conventional Alumina technology was made. The discrete components on this card are surface mounted and all integrated circuits are bare die.

A photograph of the port card is shown in Fig. 19. All

Fig. 18. Schematic diagram indicating layout of the SVX readout hybrid for a layer 1 ladder. For greater numbers of chips the middle chip connections are repeated.

Fig. 19. Photograph showing detail of port cards as mounted on SVX barrel.

lines coming out of the port card are distributed in parallel to the readout hybrids of the wedge and then to the SVXD chips themselves. The port card contains a number of different circuits.

To provide operating voltages for the SVXD readout chips, a set of low dropout regulators are used. Based upon test measurements, we determined that supplying regulated power nearby the SVXD chips was very effective in minimizing noise in the system and controlling systematic variations in the behavior of thresholds and offsets chip to chip. The SVXD chip requires two voltages to operate. One supplies the preamp only. The rest of the chip is supplied by the other. A serious failure mode occurs if the preamp voltage is less than the other. To prevent this a diode is placed between the regulators on the port card.

All the digital signals used to control the SVXD chips are received differentially by the port card and then converted to CMOS 5 VDC levels before leaving for the readout hybrids. The SVXD chips have digital I/O pads which are bi-directional. The digital data output by the chip (channel addresses etc.) are converted to differential signals on the port card for transmission to the external DAQ system. The driver/receiver chip set used conformed to IEEE standards RS-422 and RS-485. To minimize power dissipated on the card we chose to back terminate all the differential pairs serially. In this way standing current on the card was reduced significantly.

Analog data generated by the SVXD chips is converted to differential voltages on the port card before transmission to the external DAQ system. These lines are also series back terminated.

In order for the SVXD chip to sparsify the sampled

detector signals, a threshold signal is required. This is a voltage step which is input to the preamps through an on-chip calibration capacitor, one per channel, of 60 fF. There is one calibration input on an SVXD chip. It was not practical to provide calibration lines for each chip however. The choice was made to supply, on the port card, two identical calibration circuits. One provides the voltage step for the innermost layer while the other serves the outer three layers. Radiation effects will be largest on the inner layer. The ability to set a single threshold for multiple layers and still have good efficiency for hits from tracks is clearly a critical requirement for such a restricted system. In fact this worked well as is described in Section 11.1. The threshold voltages are generated by DACs in the DAQ crates and transmitted differentially to the port cards. The calibration circuits receive, filter, and chop these levels before passing them to the readout hybrids.

A total of 49 lines enter each port card on low mass etched copper on Kapton cables. These cables meet a set of larger gauge commercial cables at the outer radius of the VTX chamber and yet another even larger set after leaving the detector gas volume. For the digital lines the cable impedance is 95  $\Omega$ . The etched copper on Kapton cable which carries digital data was designed to match this impedance as well.

The total power dissipation of the port card is 1.8 W. Chips on the port card are placed in proximity to the cooling loop on the bulkheads in proportion to their power dissipation.

#### 5.4. Interconnects

The readout cable (known as a pigtail) attached to the end of the readout hybrid incorporates a gold-dot technology [15] to make electrical contact to a mating bus cable which serves each wedge and connects to the port card. In this technology, small gold plated bumps are deposited on traces at the end of the flexible Kapton pigtail cable. These bumps mate with the bus cable, which contains pads of a similar size, using a lightweight G-10 clamp fastened with a small bolt and nut to provide the necessary mechanical pressure to ensure electrical contact. The interconnect pitch used has traces on staggered 40 mil centers, giving an effective 0.020 in. pitch. This connection scheme has many advantages. Contact can be broken and re-established an arbitrary number of times. This allowed easy testing of ears and ladders before final assembly into the barrels. The mass of the interconnect is minimized. It also allows considerable flexibility of layout and spacing of traces. Conventional mechanical connectors are only available for traces on 0.050 in. pitch or larger and occupy excessive space. The gold dot scheme is illustrated in Fig. 20. The layout of the busing cables and the clamps can also be seen in Fig. 21.

No failure of a gold dot connection occurred in the SVX to date.

Fig. 20. Photograph showing gold dot interconnection scheme.

The connection is secured by squeezing flexible cables inside a G-10 clamp. Alignment is established by two precise pins in the clamp and corresponding holes in the Kapton.

## 6. Cooling system

#### 6.1. Specification and design

Approximately 50 W are dissipated by the SVXD chips and the port cards located inside each SVX barrel. This

Fig. 21. Photograph of the readout end of the SVX barrel showing busing cables which service each wedge and the G-10 clamps holding busing cable to readout hybrid pigtails.

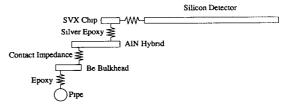

Fig. 22. Thermal model of the SVX chip to cooling pipe interface.

power can change by 5–7% depending upon the operating mode of the front end chips. In addition, the ambient environment of the SVX is heated to about 35°C by the surrounding CDF detector components. Without external cooling, the SVX barrels would rise to a temperature of about 90°C in approximately 20 min. To avoid relative thermal motions of detector components, mechanical instability, damaging stresses, excessive leakage current, and failure of electrical components, a cooling system is required which can remove the heat load while maintaining an operating temperature close to that of construction  $\approx 20$ °C. In addition, the elements of the cooling system on the SVX barrel should be as low in mass as possible. With the sources of heat being rather localized, liquid cooling is a natural choice.

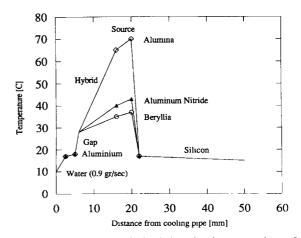

A thermal model of the readout hybrid and bulkhead system is shown in Fig. 22. The desire to keep material as far out from the interaction region as possible led to the design shown wherein heat is conducted partially along the length of the ceramic. Calculations and measurements on models indicate that the temperature drop between the SVXD chip and the cooling water is of order 20°C. The result of one such calculation which compares a number of substrate materials is shown in Fig. 23. Measurements also indicated little variation in the behavior of the SVXD chip up to 60°C.

Fig. 23. Result of thermal simulation showing comparison of temperature profiles expected for different readout hybrid substrate materials.

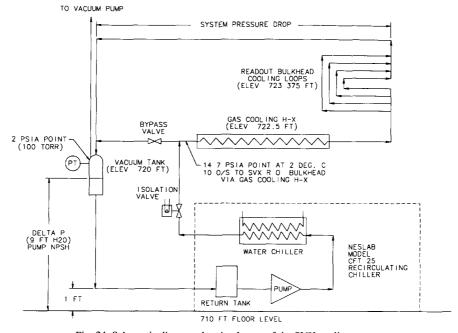

The SVX cooling system is shown in Fig. 24. Two Neslab CFT25 chillers deliver chilled de-ionized and filtered water, one for each SVX barrel. The chillers were originally to be placed far from the SVX barrel and therefore we have a bypass loop to return most of the water directly to the chiller. Approximately 10 g per second of water is sent to each barrel. The chiller runs at 13°C. The water just before reaching the SVX is about 19°C. The SVX bulkhead temperature during normal operation is ≈ 25°C. The chilled water circulates through thin 3003 series  $\frac{3}{32}$  in. outside diameter aluminum tubing, with 0.014 in. wall thickness, which is formed to the shape of the bulkhead and glued to the bulkheads just below the SVXD chips on all four layers. After testing many epoxys we chose to use Master Bond brand EP21ANHT thermal epoxy because it was sufficiently strong and had very good thermal properties. The two input and two output cooling tubes for each SVX barrel are glued to the outer SVX screen with the same epoxy. This provides additional cooling and acts to thermally isolate the SVX from its surroundings. The entire cooling circuit is kept under negative pressure. The pressure drop through the circuit is about 7 PSI. The lowest point on the circuit is kept about 3 PSI so that the pump in the chiller does not cavitate.

The number of readout chips varies from 2 to 6 per ladder for the 4 layers of silicon and the typical heat load is 175 mW/chip, giving a total heat load from the readout chips of 31.5 W per barrel. An additional cooling circuit is used to remove heat from the port card, which due to its power regulating and signal driving functions, generates 1800 mW each or 21.6 W per barrel. Thus, a total of 53.1

W of heat is typically generated by the electronics in each half of the SVX.

A system to flow chilled gas through the SVX barrel was also constructed in an attempt to even out the temperature distribution and provide slightly more cooling capabilities. A cast aluminum tube with a fin-shaped outer diameter acts as a heat exchanger. The input chilled water flows through it, and the gas to be cooled flows between the aluminum fins and a shrink-tube enclosure. The entire heat exchanger is 34 cm long. The temperature of the SVX is monitored by 12 AD592CN temperature probes per barrel, located throughout the device. The chilled gas system is observed to have a very small effect on the overall temperature distribution of the SVX.

## 6.2. Performance and operating experience

The cooling system operated almost continuously for about one year with few problems. The flow rate at a given pressure drop through the system was still approximately 90% of its original value at the end of the run, indicating that there was little or no flow restriction in the aluminum tubing.

According to the temperature sensors located throughout the detector all monitored locations were within 3°C. The largest temperature drop was between the bulkhead which averaged 22°C and the silicon closest to the port card which was typically 25°C.

A number of measurements were performed during commissioning which determined various thermal time constants of the system. The time to cool or warm up the

Fig. 24. Schematic diagram showing layout of the SVX cooling system.

the entire SVX was determined by the capacity of the chiller. We observed that for a given set of wedges under power and the chiller at fixed temperature, the addition of another wedge raised the bulkhead temperature by 1.2°C near the wedge with a time constant of about 110 s. If cooling water is abruptly stopped and then restarted the recovery time constant is about 60 s if the water is still cold. For single wedges under power strong correlations were observed for temperature probes near the wedge. To prevent possible mechanical distortions, we avoided situations where, for example, half the wedges were powered all on one side of a barrel.

## 7. Data acquisition system

## 7.1. System architecture

The architecture of the SVX data acquisition system was determined by the SVX detector design, the operation of the SVXD chips and their need for a variety of clocking

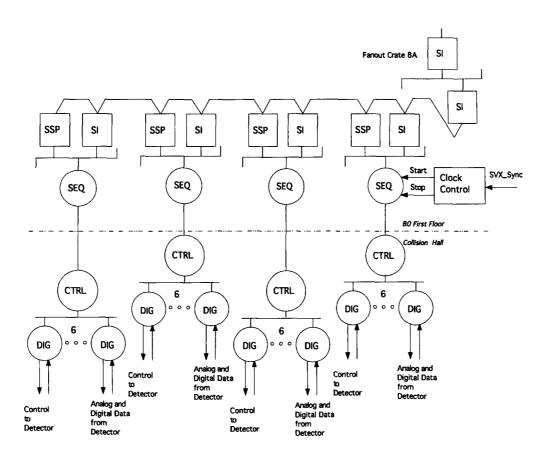

sequences, the required readout speed, and the existing CDF data acquisition network [16]. The system consists of a Fastbus Sequencer, a Crate Controller, and a set of Digitizer modules. Additional details can also be found in the literature [17–19]. The CDF SVX detector was instrumented with four Fastbus crates and four SVX RABBIT [20] crates each with 6 Digitizers to accommodate 24 SVX wedges as illustrated in Fig. 25. All SVX Fastbus crates are connected to a single cable segment in a Fanout crate.

The standard interface to the CDF data acquisition system is provided by a SLAC Scanner Processor (SSP) [21], a commercial product that is used extensively in the CDF network. It is a programmable Fastbus master that can reformat the event data and attach header information. It has adequate memory to buffer four events, a feature used in certain calibration modes.

The Sequencer, a Fastbus slave, is based partially on the SRS CAMAC module cited in Section 10.2 [22], but incorporates many additional capabilities. It is a programmable module which provides the clocking signals necessary to operate the SVXD chips, synchronization

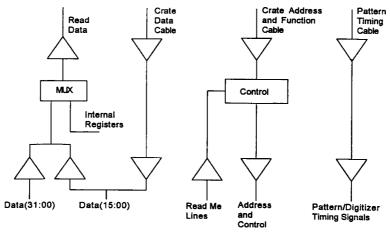

#### SVX DAQ System Diagram.

Fig. 25. Block diagram of SVX data acquisition system.

logic to link to the CDF data acquisition system, and contains storage for one event as a pipeline to the SSP.

The Controllers and Digitizers are housed in SVX Rabbit crates on the CDF Central Detector. The Controller provides the interface between the Digitizers and the Sequencer. The Digitizers process analog data and buffer digital data from the wedges. They are read out by the Controller.

## 7.2. Control and data flow

The Sequencer can read from and write to both the Digitizers and the Controller. It is also possible to direct the read information out a front panel port on the Digitizers to operate with a standalone on-line monitoring system. The primary mode for reading out wedge data is via automatic scans in which the Controller reads the wedge data register in each of its Digitizers reporting the presence of data.

Twelve signals control sample and hold operations within the amplifiers as well as the event readout. During beam crossings, the SVX timing signals pass from the Sequencer through the Controller and Digitizer to the wedge. Sample and hold operation is synchronized with the 3.5  $\mu$ s beam crossing interval. During readout, the timing signal drivers turn off, and the digitizer accepts the chip and channel addresses along with the analog data

from the wedge. The Sequencer also issues a convert signal telling the ADC on the Digitizers when to begin the hold and digitize cycle. Once the data for a channel have been prepared by the Digitizers, readout can commence. The Controller is commanded by the Sequencer to initiate a scan read. In this mode the controller will poll each digitizer and only send data to the Sequencer for those Digitizers which have responded that they have data. The SVX ICs will normally be programmed to provide sparsified data which will cause the Digitizers to stop responding as each wedge becomes empty. The Sequencer monitors the presence of data in the wedges and terminates the readout after all the wedges have been emptied. A 32 bit Read-Data path from the Digitizer to the Sequencer carries data during a read or presents data status from each Digitizer when a read is not in progress. Both the data and their status can be masked off. The data from any wedge can be masked in the Controller and data status is maskable in the Sequencer.

A compact data format was used to describe the digital and digitized analog output from the SVXD chip. Each hit is described by one 32-bit word. The control registers are read from the Digitizer or Controller modules using the same format as for the hit information. Data from all the Digitizer and Controller registers are read out with every event and appended to the raw data for diagnostics and calibration purposes.

Fig. 26. SVX Sequencer block diagram.

Table 6

Bit assignments for the SVX Sequencer

| Microprogram |        | Crate    |              | SVX Pattern         |         |  |

|--------------|--------|----------|--------------|---------------------|---------|--|

| Control      |        | Control  | Control Cont |                     | Control |  |

| Micro Instr  | (3:0)  | Sub Adr  | (3:0)        | Vernier Ctrl        | (3:0)   |  |

| Done         |        | Slot     | (3:0)        | NIM output          | (3:0)   |  |

| XQT Hold     |        | Function | (2:0)        | Vernier Adjustable: |         |  |

| Seq Function | (2:0)  | Test     | (3:0)        | NIM output          | (3:0)   |  |

| Branch Ctrl  | (6:0)  | Data     | (15:0)       | Digitizer           | (5:0)   |  |

| Branch Adr   | (15:0) | XQT      |              | Pattern             | (11:0)  |  |

The algorithms for the readout of the SVX Sequencer include data acquisition and data calibration modes. During data acquisition and data mode calibration (every event is read out to a disk), the SSPs read data from each Sequencer's buffers until an end of block code is returned. Then a check is made between the number of data words transferred and the actual number of words written to the

Sequencer's block. In case of a mismatch, an error condition is reported to the system. The raw data words are then sent through the DAQ chain and are written to disk. In scanner mode calibration the raw data words from the Sequencers are sent only to the SSPs. For each channel, the scanner accumulates the sums of relevant quantities as well as the number of events read. After collection of the

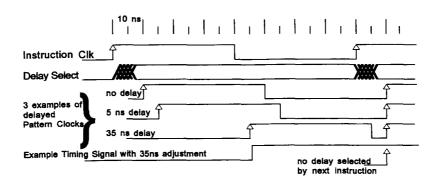

Delayed Clock Timing.

Pattern Timing Block Diagram.

Fig. 27. Sequencer timing vernier scheme.

predefined number of triggers, the data accumulated by the SSP are sent the rest of the way up the DAQ chain to be further analyzed by calibration consumer processes. This method of calibration runs much faster than in the data mode because it reduces the number of data transfers and uses the computing power of the SSP.

#### 7.3. System modules

## 7.3.1. The Sequencer

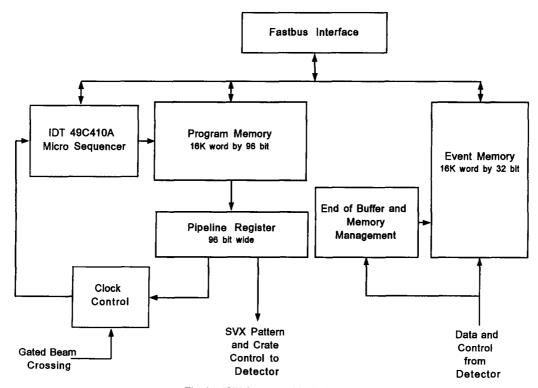

The block diagram of the Sequencer is shown in Fig. 26. One Sequencer can control and readout up to eight wedges of the detector. The Sequencer consists of a microsequencer chip, a program memory array and pipeline register and produces the clock patterns required to operate the SVX IC. The Event Memory and End of Buffer and Memory Management logic provide for temporary storage of the data for one event. The Event Memory is separated into eight 2K buffers each holding the data from a specific wedge. All registers and memories are accessible through Fastbus.

The IDT 49C410A [23] microsequencer contains a 16 bit program counter, 33 word deep stack and register that can be used for loop control. External logic provides for 32 branch conditions in their true and complement form as well as an unconditional branch. Instructions from the 16K word by 96 bit program memory are executed in the pipeline register. This 96 bit register can be thought of as a set of fields that describe functions to be performed during the present instruction execution as illustrated in Table 6. The Microprogram Control determines how the microsequencer generates the address of the next instruction. This

address is used to point to the program memory location of the next instruction to be executed. That instruction is loaded into the pipeline register to begin the cycle again. The Crate Control allows read/write access to any register in the SVX Rabbit Crates, and the SVX Pattern Control governs the timing transitions for the SVX IC. In this way transitions on control lines can occur as often as each instruction is executed.

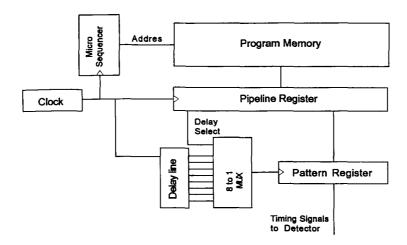

The Sequencer provides the timing signals necessary to operate the SVX IC and these signals must be synchronous with the beam crossing. Additionally, these signals must be tailored to the requirements for each phase of sampling and acquiring/rejecting an event as well as calibration and monitoring of the detector. The clock frequency for the microprogram engine is 12.5 MHz. The timing signals that operate the SVX IC are controlled directly by the program running. To eliminate timing jitter associated with the sequencer clock, the clock must be synchronized with every beam crossing.

To accomplish this, the Sequencer's clock is started by an external signal that is related to the beam crossing, and it is stopped before the next beam crossing signal. During the time when the sequencer's clock is operating, the internal program is generating the SVX IC timing pattern appropriate for sampling an event. The Sequencer program will execute 43 instructions during the 3.5  $\mu$ s interval between beam crossings, which includes the overhead of stopping and restarting the clock.

It is necessary to control the widths of some of the timing pattern lines to within 10 ns over a period of 1  $\mu$ s. This is due to the  $\Delta T$  effect discussed in Section 5.1. Since the edges of these lines are determined by the 80 ns

#### Communication with Sequencer

Communication with Digitizers thru SVX Rabbit Backplane

Controller Block Diagram

Fig. 28. SVX Controller block diagram.

clock period a method for delaying its arrival was developed and is illustrated in Fig. 27. The SVX Pattern Control field of the instruction controls a delay line circuit that produces clocks for the pattern portion of the pipeline register. A three bit field of the instruction selects one of 8 possible delay taps for use in clocking the SVX Pattern.

#### 7.3.2. The Controller

The Controller interfaces the Sequencer to an SVX Rabbit Crate. A block diagram of the Controller is shown in Fig. 28. It provides read and write access to all registers in the crate and passes the timing signals for the detector from the Sequencer to the Digitizers. The function code, slot, and subaddress information from the Sequencer are used to direct single word read and write operations as well as multi-word readout scans and broadcast operations. Digitizer data as well as status indicating the presence of data are issued to the Sequencer upon request. The front panel has five high density 36-pin connectors, three for receiving and another two for sending. Information from the SVX Timing Cable is passed directly to the Rabbit backplane.

The Controller translates function codes from the Sequencer. In a write operation to the Digitizers, control information along with the Write-Data from the Sequencer is driven onto the SVX Rabbit backplane. The appropriate addressing and control lines are set to cause the specified

register on the addressed Digitizer to accept the data. In a read operation, the Read-Data cable will be driven by the Controller along with a signal to tell the Sequencer that the data is valid. Data can come from either the Digitizers or from internal Controller Registers. It is also possible to direct the read information to a front panel port on the Digitizers. In addition to single word operations, the Controller can be commanded to scan the data from an entire crate eliminating the need to directly address a Digitizer for each word of data; a crate scan pushes data at a rate of 12.5 MHz.

## 7.3.3. The Digitizer

The Digitizer passes the clocking signals from the Sequencer to the detector and receives digital data and analog signals from the detector wedge. It contains registers for storage of digital data and a section for processing and conversion of the analog data. All of the digital information is formed into a 32 bit word that can be read out by the Controller.

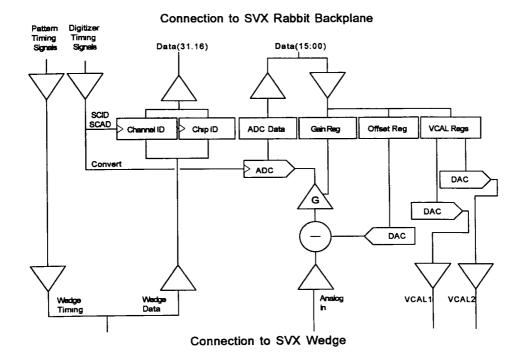

As shown in the block diagram in Fig. 29, the Digitizer contains a 12 bit ADC, three 12 bit DACs and registers for data, control and status. The ADC is a Datel 132S, with built in sample and hold, and an overall throughput of 2 MHz. A large offset voltage that accompanies the signals from the detector must be subtracted before any gain adjustment can be applied. One of the three DACs supplies

#### Digitizer Block Diagram.

Fig. 29. SVX Digitizer block diagram.

a voltage for this purpose. The programmable gain can be adjusted over a range of 15 equal steps. Each SVX wedge contains 2 calibration pulsers, each controlled by a separate calibration voltage. The pulsers are fired by one of the timing signals supplied by the Sequencer. Two of the three DACs supply these separate calibration voltages.

#### 7.4. Synchronization with the CDF DAQ

The operation of the SVXD chip is performed by an ensemble of timing signals generated by the Sequencer module in phase with the bunch crossing times regardless of the uneven spacing of alternate bunches. For this reason the Sequencer has to be synchronized with every beam crossing. The method also minimizes the impact of the jitter of the Sequencer's internal clock on the precise timing of the event and threshold integration times.

The 53 MHz CDF Master Clock generates timing signals correlated with the Tevatron bunch crossing times. Their edges are timed with 1 ns resolution relative to the bunch crossing. The Tevatron operates with 6 bunches alternately spaced by 185 and 186 clock cycles. One of these signals, SVX-Sync, is used by an LRS4222, a programmable delay module to generate a sequence of the

start and stop pulses for the control of the operation of the Sequencer's internal clock. SVX-Sync preceeds the next beam crossing by a fixed time.

The SVX sample and hold cycle contains 43 Sequencer timing cycles. To ensure accurate leakage current cancellation this timing must be stable. The duration of the 43 cycles was measured to be accurate to better than 1 ns.

The CDF data acquisition system is based upon a multi-level trigger which determines readout of the detector [24]. The first level trigger (L1) is determined before the next beam crossing. In the case of a L1 accept deadtime is incurred until a second level (L2) decision is reached. The time for L2 varies but is typically  $20-30~\mu s$ . In the case of a L2 accept full readout of the detector would commence. The data thus acquired is subject to a further filtering in a third level software trigger before being written to tape. The operation of the SVX Sequencer is linked to the various L1 and L2 decisions.

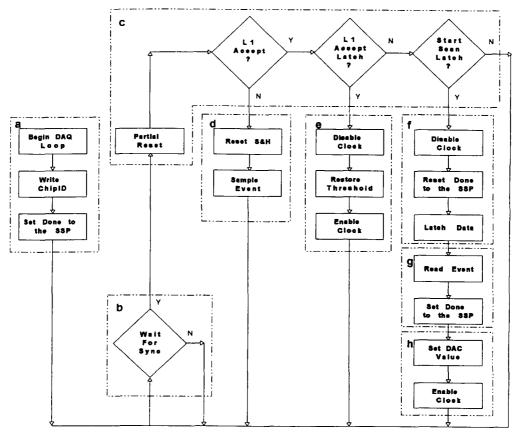

In Fig. 30 an example of the microsequencer program block diagram is presented, performing an event acquisition during the collider run. The program starts with the downloading of the chip numbers to the chips' memories and reading them back for the diagnostic purposes. This part of the program is executed only once. Then the

Fig. 30. Sample Sequencer code flow chart for data acquisition.

Sequencer's clock is shut off, waiting to be synchronized with the next beam crossing. After receiving the start clock signal, the Partial Reset procedure is executed in which only the chip integrator is reset and the events sampled in the previous crossing are kept on the Sample and Hold capacitor. Then a check is made of the level of the L1 trigger decision signal.

The absence of the L1 trigger signal is an indication to integrate a new sample. When the integration cycle is finished the Sequencer's internal clock is stopped by the next stop clock signal and the synchronization with the next beam crossing takes place. The following start clock signal enables the operation of the internal clock again and the Partial Reset is performed. There are 43 80-ns microsequencer's instructions executed between the Start-Clock and Stop-Clock sequence.

The presence of the L1 trigger signal indicates that the event stored during the previous crossing passed the L1 trigger conditions and the event may be prepared for readout. In this case a threshold sample is taken, which is used to cancel the leakage current component in the event sample. The event sampling and the threshold cycles must be executed with the full knowledge of the beam crossing. In the first case the beam crossing should appear inside the integration window and in the second one the integration must be performed between the beam crossings. The threshold restoring subprocess, shown in Fig. 31, requires two beam crossings to be performed with the constraints defined above. The microsequencer program inhibits generation of the Stop-Clock signal at the LRS4222 during the threshold cycle. When the threshold is restored, the synchronization mechanism is enabled again.

In the next step a test is done of the L2 trigger decision. Its presence initiates the readout cycle and its absence directs control to the synchronization subprocess. The Start Scan Latch signal is automatically reset when is it checked by the execution of a conditional branch microsequencer instruction. During the readout cycle the synchronization mechanism is disabled again until the cycle is finished. To indicate that readout is finished, the Sequencer sets a particular bit in one of its CSR space registers. The SSP continually polls this register after sending the Start Scan message and will recognize the signal and begin to read out the Sequencer within 2  $\mu$ s of the bit being set. For non-triggered events, a separate integration cycle is performed in the very next Start/Stop clock cycle.

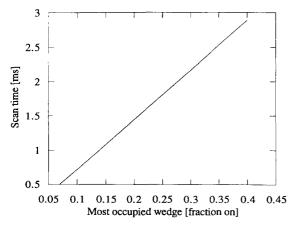

## 7.5. Scan times

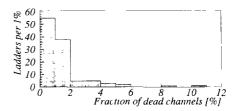

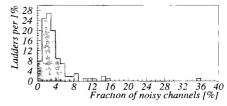

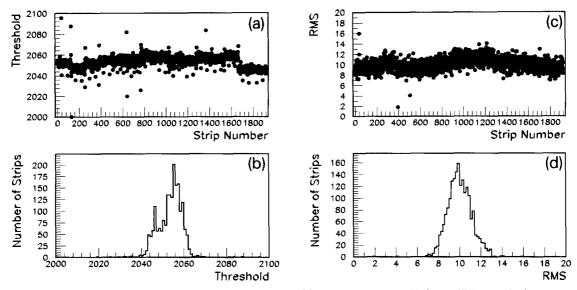

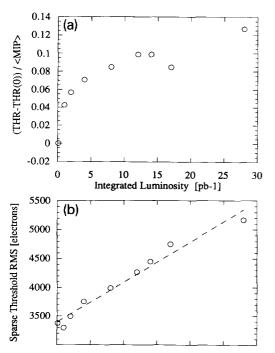

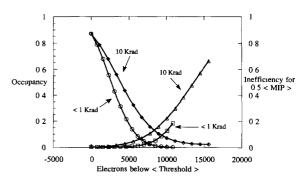

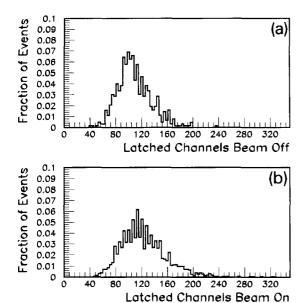

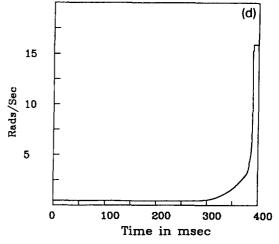

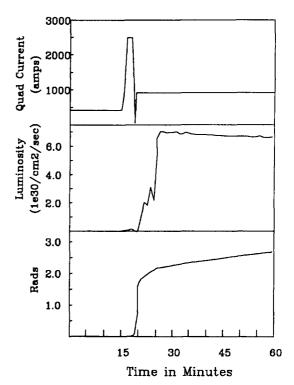

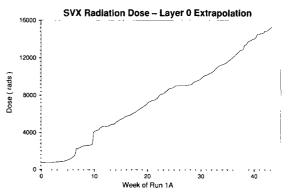

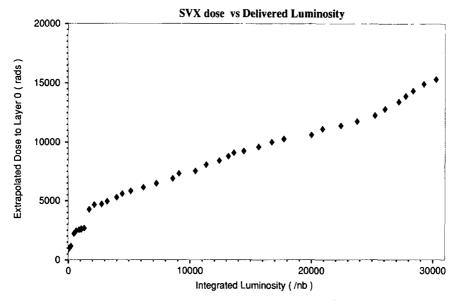

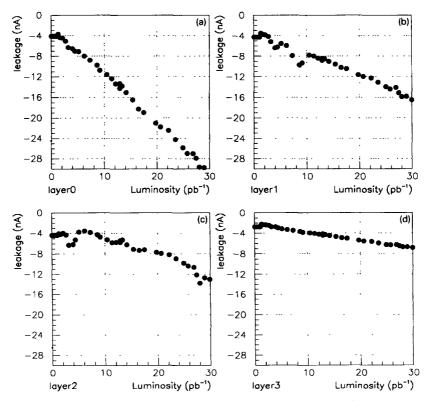

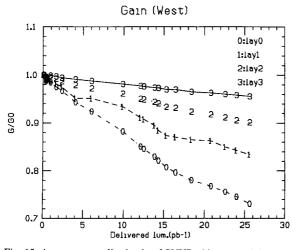

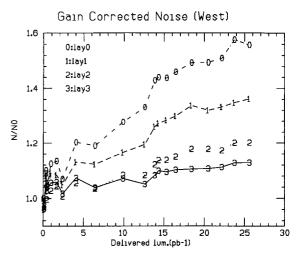

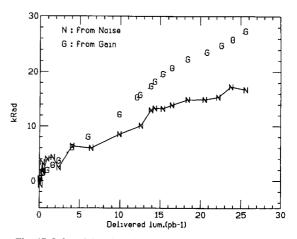

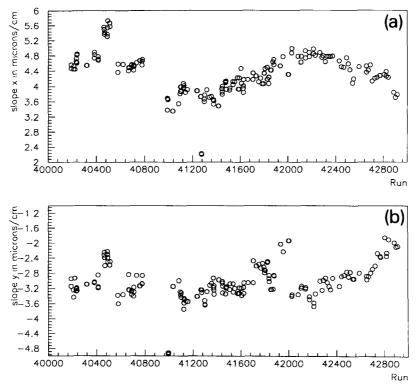

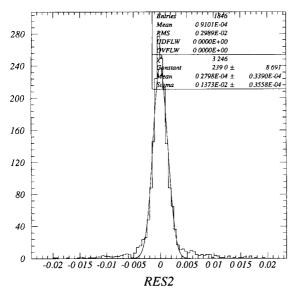

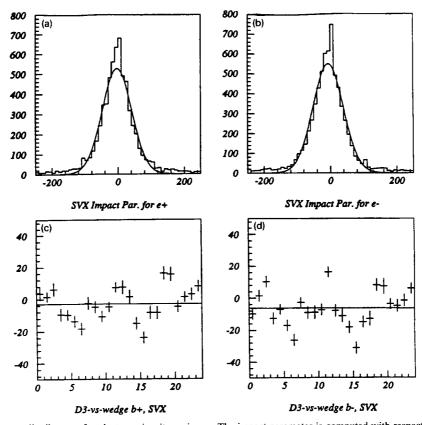

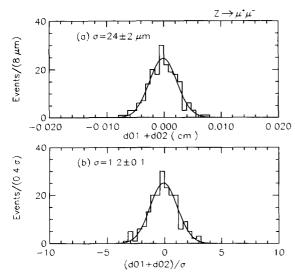

All detector elements in the CDF data acquisition system are required to read out within 2 ms. Due to the large number of channels it was necessary to partition the SVX into four independently read branches. The scan time is defined as a sum of two components: the time required to read SVXD chips in six wedges by the Sequencer and the time to move data from the Sequencer's Event Memory to the SSP's buffer.