## MANUFACTURABILITY AWARE DESIGN

by Jie Yang

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 2007

Doctoral Comittee:

Professor Dennis M. Sylvester, Chair

Professor David Blaauw

Professor Kensall D. Wise

Luigi Capodieci, Advanced Micro Devices

### ACKNOWLEDGEMENTS

My sincere gratitude to Professor Dennis Sylvester for providing me the opportunity to study at the University of Michigan. Without his vision, encouragement and continuous support, this dissertation was impossible. Professor Sylvester was always around to listen and to give advice. He not only taught me how to ask questions and express my ideas, also taught me to be a careful and meticulous researcher. He always provided timely responses for proof reading and commenting my papers and chapters, extremely patient even after I had made many revisions.

A special thank goes to Dr. Luigi Capodieci, who has always been very supportive and responsible for helping me complete the challenging research that lies behind this dissertation. He was always there listening to my ideas and giving me feedbacks and guidelines that help me go through my problems at many critical moments.

I'm also deeply indebted to the rest of my thesis committee: Professor David Blaauw, Professor Ken Wise, for their insightful comments, hard questions, constructive suggestions and numerous encouragement.

During the course of this work, I was part of the GSRC and SRC program. I would like to thank the sponsors for their continuous support of the projects.

A warm hug to my research fellows for their very valuable inputs and contributions for various projects: Professor Yu (Kevin) Cao, Professor Puneet Gupta, and Professor Andrew Kahng. Thanks also go to my colleagues and friends at VLSI Design / Automation lab and UM for sharing both research and life experiences: Kanak Agarwal, Himanshu Kaul, Harmander Deogun, Matthew Guthaus, Ashish Srivastava, Youngmin Kim, Aseem Agarwal, Donwoo Lee, Feng Gao, Feng Wang, Hui Zhang, Yunqing Chen, Yong Lei, Jun Cheng, Li Ding, Yan Lan and Cheng Peng. They have made my life at UM very pleasant and memorable:

Last, but not least, my utmost thanks to my family: my parents Yinxiang Yang and Xiumei Zhang, for giving me life in the first place, for educating me with aspects from both arts and sciences, for teaching me how to be a good person and for their unconditional support and encouragement to pursue my interests. Their patient love enabled me to complete this work.

# TABLE OF CONTENTS

| ACKNOWLE    | DGEMENTS                                                    | ii  |  |  |

|-------------|-------------------------------------------------------------|-----|--|--|

| LIST OF FIG | URES                                                        | vii |  |  |

| LIST OF TAI | BLES                                                        | xi  |  |  |

| CHAPTER     |                                                             |     |  |  |

| I. Intro    | duction                                                     | 1   |  |  |

| 1.1         | Litho Process and Challenges                                | 1   |  |  |

| 1.2         | Various RETs                                                | 5   |  |  |

| 1.3         | Modeling Process Variation in Design                        | 8   |  |  |

| 1.4         | Thesis Outline                                              | 11  |  |  |

| II. Desig   | n Sensitivities to Variability                              | 13  |  |  |

| 2.1         | Introduction                                                | 13  |  |  |

| 2.2         | Taxonomy of Variation                                       |     |  |  |

| 2.3         | Experimental Testbed and Methodology                        | 16  |  |  |

| 2.4         | Impact on Future Circuit Performance                        | 23  |  |  |

|             | 2.4.1 Studies for A Single Critical Path                    | 24  |  |  |

|             | 2.4.2 Studies of Multi-Critical Paths                       | 31  |  |  |

| 2.5         | Variation-Centric Physical Design                           | 37  |  |  |

| 2.6         | Conclusions                                                 | 40  |  |  |

| III. Perfo  | rmance-Driven OPC for Mask Cost Reduction                   | 42  |  |  |

| 3.1         | Introduction                                                | 42  |  |  |

|             | 3.1.1 OPC and Mask Cost                                     | 43  |  |  |

|             | 3.1.2 Design Function in the Design-Manufacturing Inter-    |     |  |  |

|             | face                                                        | 45  |  |  |

|             | 3.1.3 A Performance-Driven OPC Methodology                  | 45  |  |  |

| 3.2         | General Cost of Correction Flow (MinCorr) Based on Sizing . | 46  |  |  |

|             | 3.2.1 Slack Budgeting                                       | 50  |  |  |

|             | 3.2.2 Calculation of CD Tolerances                          | 52  |  |  |

|                   |                                                                                                                                                                                                                                                                                                     | 53                               |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|                   |                                                                                                                                                                                                                                                                                                     | 64                               |

| 3.3               | 1 1                                                                                                                                                                                                                                                                                                 | 55                               |

|                   |                                                                                                                                                                                                                                                                                                     | 55                               |

|                   | J.                                                                                                                                                                                                                                                                                                  | 55                               |

|                   |                                                                                                                                                                                                                                                                                                     | 66                               |

|                   |                                                                                                                                                                                                                                                                                                     | 57                               |

| 3.4               | Conclusions and Future Work                                                                                                                                                                                                                                                                         | 60                               |

|                   | nced Timing Analysis Based on Post-OPC Extraction                                                                                                                                                                                                                                                   |                                  |

| of Cri            | itical Dimensions                                                                                                                                                                                                                                                                                   | 52                               |

| 4.1               | Introduction                                                                                                                                                                                                                                                                                        | 52                               |

| 4.2               |                                                                                                                                                                                                                                                                                                     | 53                               |

| 4.3               | 00                                                                                                                                                                                                                                                                                                  | 66                               |

|                   |                                                                                                                                                                                                                                                                                                     | 57                               |

|                   | 0                                                                                                                                                                                                                                                                                                   | 71                               |

|                   |                                                                                                                                                                                                                                                                                                     | 71                               |

| 4.4               |                                                                                                                                                                                                                                                                                                     | 74                               |

| 5.1<br>5.2<br>5.3 | Introduction       7         RDR Evaluative Methodology       7         5.2.1       ASIC Design Flow Targeting RDR Evaluation       7         5.2.2       RDR Candidates       8         5.2.3       Evaluation Metrics for Manufacturability/Cost       8         Testbed and Experimental       8 | 76<br>76<br>77<br>77<br>31<br>32 |

|                   |                                                                                                                                                                                                                                                                                                     | 33<br>> 4                        |

|                   | 1                                                                                                                                                                                                                                                                                                   | 34<br>38                         |

|                   | 0                                                                                                                                                                                                                                                                                                   | 39                               |

|                   |                                                                                                                                                                                                                                                                                                     | )0                               |

|                   | Plus: Augmenting Standard DRC with Pattern Match-         a 2D Geometries       9                                                                                                                                                                                                                   | )2                               |

| 6.1               | Introduction                                                                                                                                                                                                                                                                                        | )2                               |

| 6.2               |                                                                                                                                                                                                                                                                                                     | )4                               |

| 6.3               |                                                                                                                                                                                                                                                                                                     | )4<br>)6                         |

| 0.0               |                                                                                                                                                                                                                                                                                                     | )6                               |

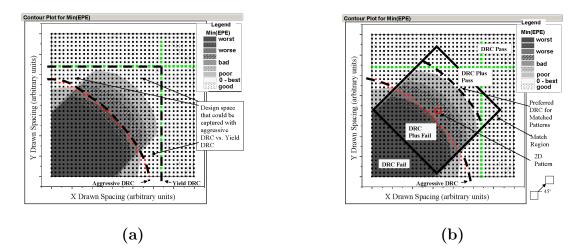

|                   | 6.3.2 DRC Plus vs. Preferred or Yield Design Rules 10                                                                                                                                                                                                                                               |                                  |

|                   | 0.0.2 Diversion in the property of the probability $0.000$                                                                                                                                                                                                                                          | · <b>エ</b>                       |

|            | 6.3.3 DRC Plus vs. Regular Design Grid or Restrictive                                                                  |     |

|------------|------------------------------------------------------------------------------------------------------------------------|-----|

|            | Design Rules (RDR) $\ldots \ldots \ldots$ | 01  |

|            | 6.3.4 DRC Plus vs. Simulation-based Layout Printability                                                                |     |

|            | and Scoring Methods                                                                                                    | 02  |

|            | 6.3.5 DRC Plus vs. Pattern Matching                                                                                    | 03  |

| 6.4        | Creating DRC Plus Rules                                                                                                | 03  |

| 6.5        | Runtime Performance of DRC Plus                                                                                        | 05  |

| 6.6        | Summary and Future Work                                                                                                | 06  |

| VII. Concl | usions and Directions for Future Work                                                                                  | 07  |

| 7.1        | Conclusions                                                                                                            | .07 |

| 7.2        | Suggestions for Future Work                                                                                            | 11  |

| BIBLIOGRA  | PHY                                                                                                                    | 13  |

# LIST OF FIGURES

# Figure

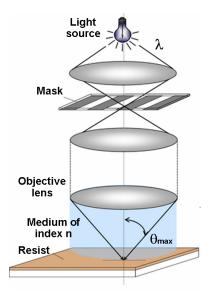

| 1.1  | $NA = n \times sin(\theta_{max})$ , where n is the refractive index of the imaging medium. When the imaging medium is air, n=1.0.                                                                 | 2  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

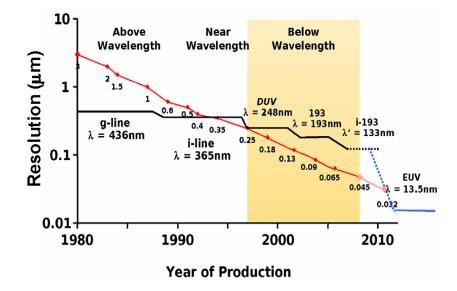

| 1.2  | Roadmap of wavelength vs. feature size.                                                                                                                                                           | 3  |

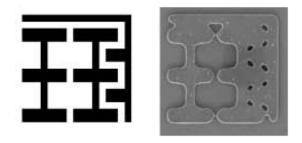

| 1.3  | Ideal layout (left) can be significantly distarted after wafer processing and etching (right) [1].                                                                                                | 4  |

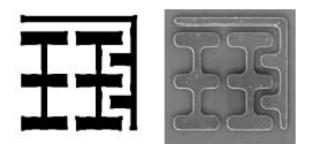

| 1.4  | Layout modified with OPC to "pre-compensate" for process distor-<br>tions [1]                                                                                                                     | 4  |

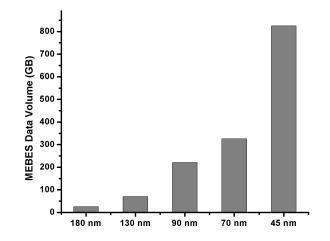

| 1.5  | Mask data volume as the technology scales [4]                                                                                                                                                     | 5  |

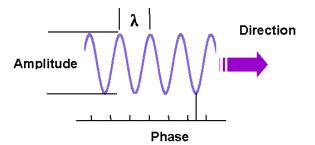

| 1.6  | Properties of a wave: wavelength, amplitude, phase, and direction                                                                                                                                 | 5  |

| 1.7  | Idealized pupil maps for various a) conventional and off-axis illumination schemes: b) annular; c) "fourfold" source; d) "separated" source; e) quadrupole; f) "CAUEST"; g) quasar; and h) dipole | 6  |

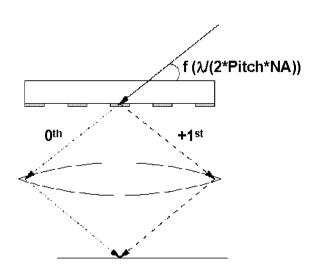

| 1.8  | Principle of OAI [7].                                                                                                                                                                             | 8  |

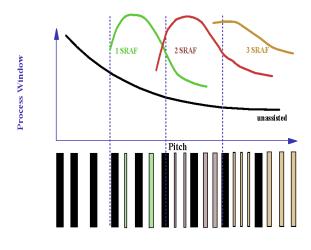

| 1.9  | SRAFs help maintain process windows for certain pitch ranges                                                                                                                                      | 10 |

| 1.10 | Model-based OPC on SRAF layout.                                                                                                                                                                   | 11 |

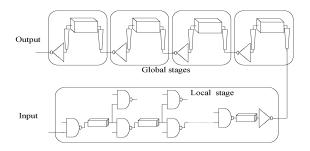

| 2.1  | A single critical path structure for performance study                                                                                                                                            | 17 |

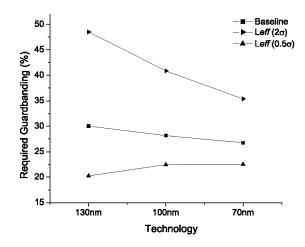

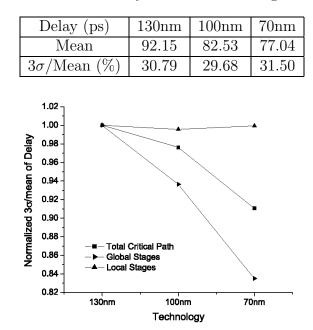

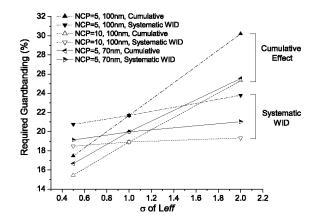

| 2.2  | Effect of process control on required guardbanding to achieve 99.7% parametric yield.                                                                                                             | 25 |

| 2.3  | Trends of normalized required guardbanding for global stages, local stages and total critical path.                                                                                               | 26 |

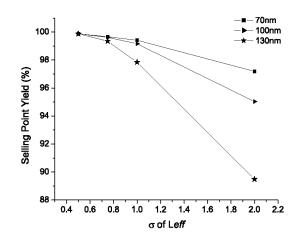

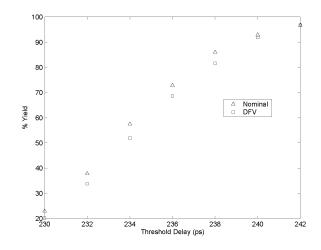

| 2.4  | Effect of $L_{eff}$ control on selling point parametric yield                                                                                                                                     | 28 |

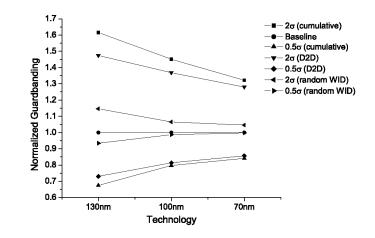

| 2.5  | Effect of control over variability $(L_{eff})$ sources (cumulative, random D2D, and random WID) on normalized guardbanding required to achieve 99.7% parametric yield.                                           | 29 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

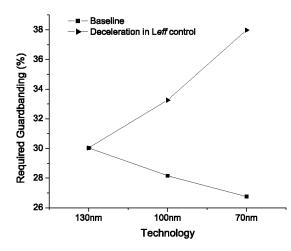

| 2.6  | Impact of technology roadmap deceleration in $L_{eff}$ control on re-<br>quired guardbanding.                                                                                                                    | 30 |

| 2.7  | Comparison of different $L_{eff}$ variation control on five critical paths<br>for 100nm technology node.                                                                                                         | 32 |

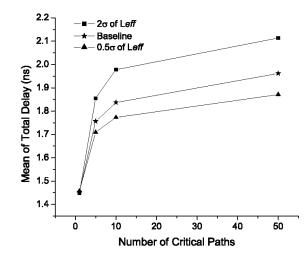

| 2.8  | Delay mean value as a function of number of critical paths. $\ldots$                                                                                                                                             | 33 |

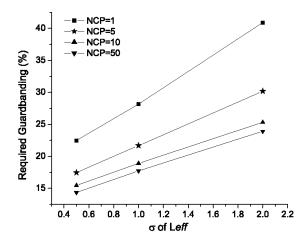

| 2.9  | Impact of $L_{eff}$ control on required guardbanding to achieve 99.7% parametric yield.                                                                                                                          | 34 |

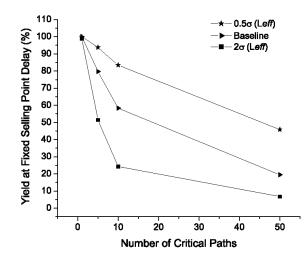

| 2.10 | Parametric yield as a function of the number of critical paths and process variation control.                                                                                                                    | 35 |

| 2.11 | Sensitivity of required design guardbanding for 99.7% yield to vari-<br>ation with respect to its sources (simulations results for the same<br>NCP and technology generation are shown in the same line styles). | 36 |

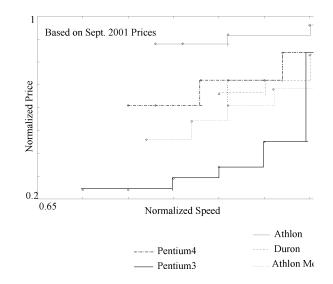

| 2.12 | Normalized market price of recent $\mu P$ products                                                                                                                                                               | 38 |

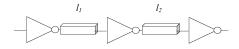

| 2.13 | Simulation structure for DVP vs. DFV study                                                                                                                                                                       | 38 |

| 2.14 | Difference in yield between DFP and DFV                                                                                                                                                                          | 39 |

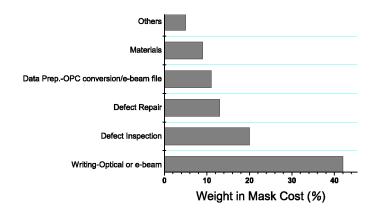

| 3.1  | Relative contributions of various components of mask cost [4]. $\ldots$                                                                                                                                          | 44 |

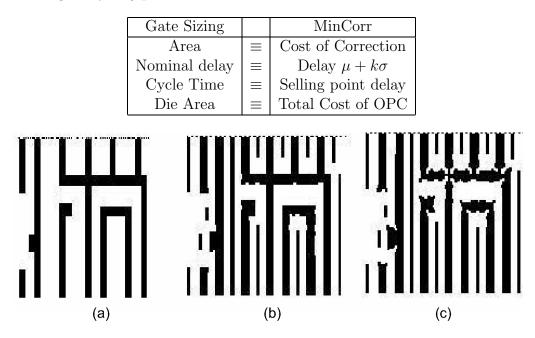

| 3.2  | An example of three levels of OPC [42]. (a) No OPC, (b) Medium OPC, (c) Aggressive OPC                                                                                                                           | 46 |

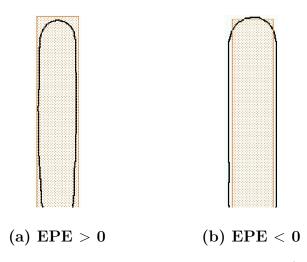

| 3.3  | The signed edge placement error (EPE).                                                                                                                                                                           | 48 |

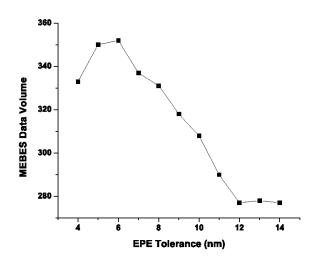

| 3.4  | Mask data volume (kB) vs EPE tolerance for a NAND3X4 cell in TSMC 130nm technology.                                                                                                                              | 49 |

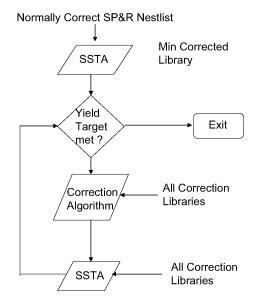

| 3.5  | The EPEMinCorr flow to find quantified edge placement error tol-<br>erances for layout features and drive OPC with them                                                                                          | 50 |

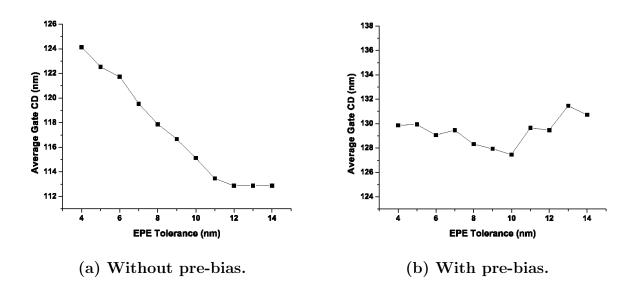

| 3.6  | Comparison of average printed gate CD with and without pre-bias for the cell macro NAND3X4                                                                                                                       | 54 |

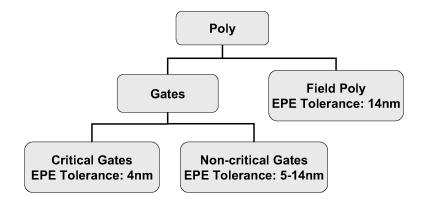

| 3.7  | Summary of EPE assignment for OPC level control                                                                                                                                                                                     | 57 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

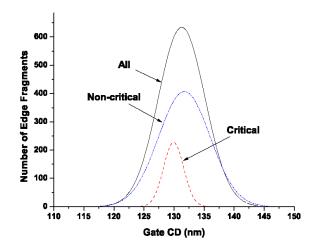

| 3.8  | Gate CD distribution for c432. Gates with budgeted 4nm EPE toler-<br>ance are labeled critical gates while others are labeled as non-critical.<br>The y-axis shows the number of fragments of gate edges with a given<br>printed CD | 58 |

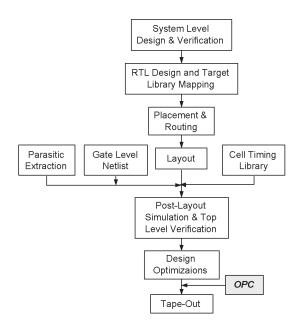

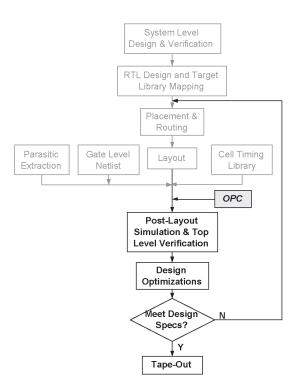

| 4.1  | Typical design flow in sub-micron VLSI design                                                                                                                                                                                       | 65 |

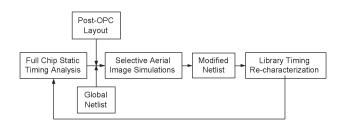

| 4.2  | Methodology overview.                                                                                                                                                                                                               | 66 |

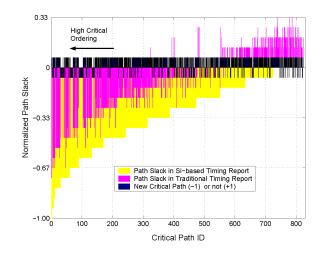

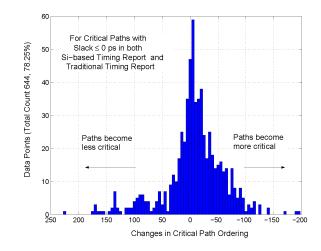

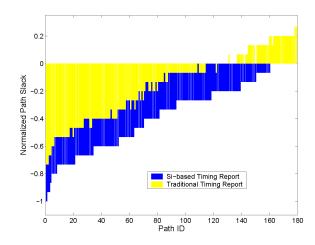

| 4.3  | Critical path reordering.                                                                                                                                                                                                           | 68 |

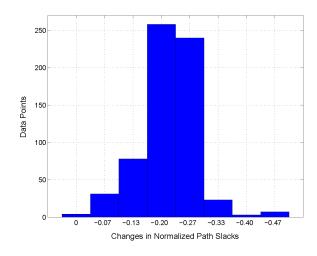

| 4.4  | Reordering of critical paths.                                                                                                                                                                                                       | 69 |

| 4.5  | Worsened slacks for <i>old</i> critical paths                                                                                                                                                                                       | 69 |

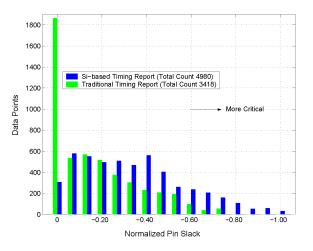

| 4.6  | Slacks for <i>new</i> critical paths                                                                                                                                                                                                | 70 |

| 4.7  | Pin slacks for critical cells                                                                                                                                                                                                       | 70 |

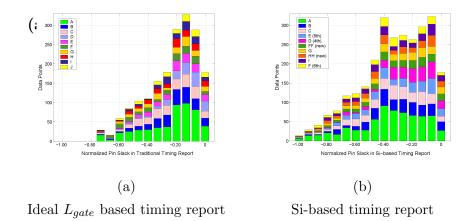

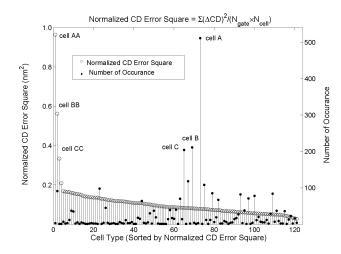

| 4.8  | Top ten most frequently used cells in ideal $L_{gate}$ based timing report<br>vs. in Si-based timing report.                                                                                                                        | 72 |

| 4.9  | Normalized $L_{gate}$ residual for cells on critical paths                                                                                                                                                                          | 73 |

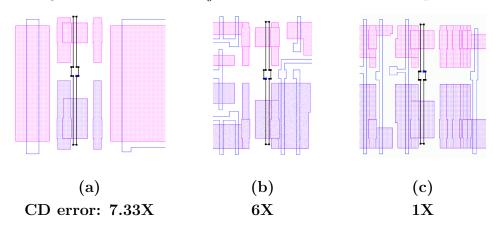

| 4.10 | Impact of environment on $L_{gate}$ residuals of the same gate. The error is extracted for the P-transistor only in the highlighted inverter and is normalized to (c)                                                               | 73 |

| 4.11 | Design flow with post-OPC verification                                                                                                                                                                                              | 74 |

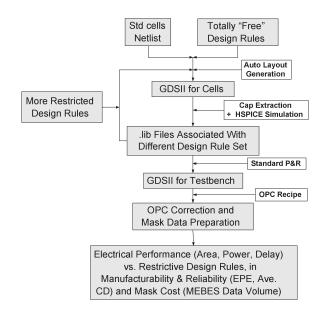

| 5.1  | ASIC design flow targeting RDR evaluation                                                                                                                                                                                           | 77 |

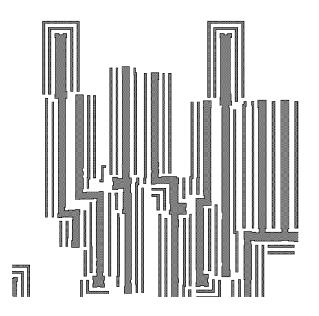

| 5.2  | Layout illustrations of RDR candidates                                                                                                                                                                                              | 80 |

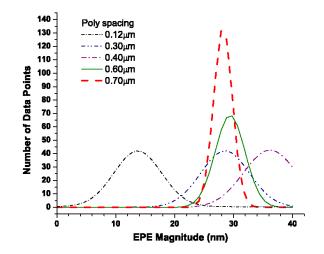

| 5.3  | Impact of pitch on the EPE histogram of a NAND2X2 without OPC.                                                                                                                                                                      | 82 |

| 5.4  | Mask data preparation (post OPC)                                                                                                                                                                                                    | 83 |

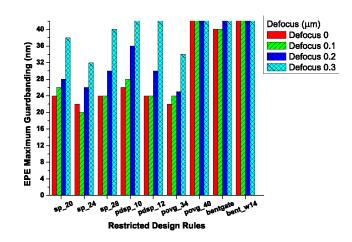

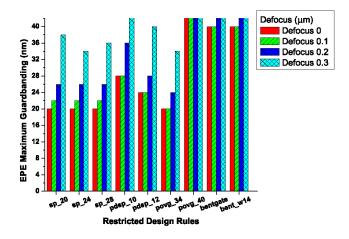

| 5.5  | Impact of defocus on c6288                                                                                                                                                                                                          | 86 |

| 5.6  | Impact of defocus on c7552                                                                                                                                                                                                          | 86 |

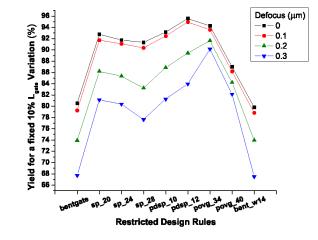

| 5.7 | Functional yield for a fixed 10% $L_{gate}$ variation for c7552                                                                                                                               | 87  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

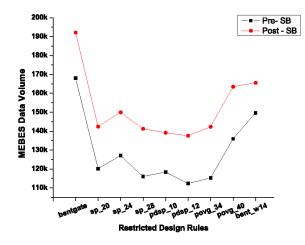

| 5.8 | Impact of scattering bars on data volume for various RDRs for the c7552 circuit.                                                                                                              | 88  |

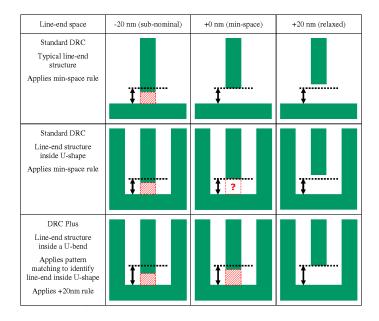

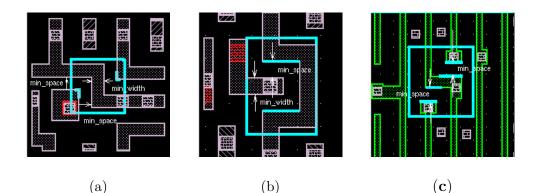

| 6.1 | DRC Plus compared to standard DRC                                                                                                                                                             | 95  |

| 6.2 | An example of a DRC Plus rule                                                                                                                                                                 | 99  |

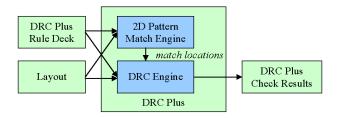

| 6.3 | DRC Plus software block diagram                                                                                                                                                               | 99  |

| 6.4 | Simulated edge placement error (EPE) in resist of various contact placements: (a) standard DRC options; (b) aggressive standard DRC and a DRC Plus rule.                                      | 100 |

| 6.5 | SEM image of redundant diagonal contact pair at minimum aggressive DRC rules.                                                                                                                 | 102 |

| 6.6 | Problematic configuration of poly tip to poly corners in regular, sin-<br>gle pitch, single orientation poly design                                                                           | 104 |

| 6.7 | Illustrations of DRC Plus rules:(a) close convex corners causing mid-<br>dle line pinching; (b) small U-shape opening causing middle line<br>pinching; (c) close landing pad causing bridging | 105 |

# LIST OF TABLES

## <u>Table</u>

| 1.1 | The ITRS requirement of gate dimension variation control is be-<br>coming more stringent as the technology scales [2]. MPU, micro-<br>processor unit                  | 5  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | Parameter values and $3\sigma$ variations $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                          | 17 |

| 2.2 | Comparison of RLC model with perfect correlations, spatial correlations and no correlations for 100 nm technology node                                                | 22 |

| 2.3 | Trends of performance variation                                                                                                                                       | 24 |

| 2.4 | Trends of delay variation for a single local stage $\ldots \ldots \ldots \ldots$                                                                                      | 26 |

| 2.5 | A comparison of changes in delay variation when the nominal $\sigma$ for<br>an individual parameter changes from 0.5X to 2X                                           | 27 |

| 2.6 | Tolerance of $\mathcal{L}_{eff}$ variation for a guardbanding budget of 30%                                                                                           | 31 |

| 3.1 | Correspondence between the traditional gate sizing problem and the minimum cost of correction (to achieve a prescribed selling point delay with given yield) problem. | 46 |

| 3.2 | Benchmark details.                                                                                                                                                    | 55 |

| 3.3 | Impact of EPEMinCorr optimization on cost and CD. All runtimes<br>are based on a 2.4GHz Xeon machine with 2GB memory running<br>Linux.                                | 59 |

| 5.1 | RDR default and modified values (note that the corresponding rule names appearing in all following figures are included in parentheses after values)                  | 80 |

| 5.2 | Impact of defocus on extracted CD mean and variation (unit: nm) .                                                                                                     | 87 |

| 5.3 | Comparison of the single pitch library (SP) and the reduced default library (RDL) | 89  |

|-----|-----------------------------------------------------------------------------------|-----|

| 5.4 | Summary of normalized performance and manufacturability results .                 | 90  |

| 6.1 | DRC Plus runtime and memory usage                                                 | 105 |

## CHAPTER I

## Introduction

### 1.1 Litho Process and Challenges

Since the invention of the integrated circuit (IC) in 1958, Moore's law has described the unprecedented march of innovation as chip features have become exponentially smaller and the number of transistors exponentially larger. The trend has continued for half a century and is not expected to stop for a decade at least and perhaps much longer. Today the most advanced circuits contain several hundred million components on an area no larger than a fingernail. While the invention and innovation of process steps has been the fundamental enabler of Moore's law's continuity, photolithography has been pushed the most in recent technology generations. It is worthwhile to mention the famous Rayleigh equation that governs optical lithography:

$$R = k_1 \times \lambda / NA \tag{1.1}$$

In Equation 1.1, R is the minimum feature width that we want to resolve.  $k_1$ is a process dependent adjustment factor.  $\lambda$  is the wavelength of light that is used to pattern an integrated circuit layout onto silicon. The opening angle of a lens that is used to project a mask or reticle is defined by the numerical aperture (NA)

Figure 1.1:  $NA = n \times sin(\theta_{max})$ , where n is the refractive index of the imaging medium. When the imaging medium is air, n=1.0.

(see Figure 1.1 for detailed definitions). For earlier process technologies, the ratio of target resolution to optical resolution, measured at  $\lambda/n$ , has remained above, or at least at, unity. The wavelength of light has been changed at least four times, ranging from Hg-arc lamps to excimer laser-based systems, and is now operating in DUV (Deep-UV) at 193 nm. As indicated in Figure 1.2, starting at the 350 nm generation, engineers face the challenges of dealing with features printed at less than  $\lambda$ , with  $k_1$  factors approaching 0.3 or even below - where  $k_1=0.25$  is the theoretical lower limit for single exposure optical lithography. In this type of *sub-wavelength lithography*, the projecting light passing through a diffraction limited system results in severe distortion of patterns printed on silicon compared to those created in the semiconductor physical design process. As illustrated in Figure 1.3, distortion effects impact pattern fidelity and edge placement on silicon, and in the worst case can even eliminate patterns entirely due to contrast zones. Figure 1.4 shows the improved pattern fidelity with a commonly used resolution enhancement technologies (RETs)

Figure 1.2: Roadmap of wavelength vs. feature size.

- OPC (optical proximity correction) [1].

Besides the difficulties of maintaining feature fidelity, future technology nodes are expected to see increased process variation and decreased predictability of nanometerscale circuit performance [2]. Despite the relaxation of some  $3\sigma$  tolerances, there are no known solutions for a number of near-term variability control requirements according to the ITRS (International Technology Roadmap for Semiconductors) [2]. Moreover, observation of key markets that drive the semiconductor industry reveals the potentially large impact of variability on the value of semiconductor products. Semiconductor enterprises must be cognizant of the different risks and ROI (Return on Investment) opportunities from, e.g., an extra increment of  $T_{ox}$  or  $L_{eff}$  CD (Critical Dimension) control (see Table 1.1), versus new design for value technologies, versus revised performance targets for products, etc. All of these have brought about the need for correction techniques to enhance resolution and avoid unacceptably high circuit and critical path performance variation [3]. Resolution enhancement techniques (RETs) that address three degrees of freedom in lithography, aperture,

# Figure 1.3: Ideal layout (left) can be significantly distarted after wafer processing and etching (right) [1].

*phase*, and/or *pattern uniformity*, are increasingly adopted in nanometer-scale design (i.e., 130 nm processes and beyond) with respect to not only the number of mask levels incorporating RETs but also the variety of techniques applied.

Due to the technological challenges of controllably printing very small features, the non-recurring engineering (NRE) and turn-around time (TAT) costs of correction (optical proximity correction (OPC), phase-shifting, dummy features) are very high in terms of design time and mask yield/verification. Many costs (yield, mask writing time, data volume, etc.) are directly proportional to the complexity of the shapes needed on the masks (e.g., Figure 1.5) shows the mask data volume for a 45 nm design is projected to be 33X larger than for a 180 nm design). Mask writing time has increased from just a few days to over a month due to RET complexity [5]. This brings up an important relationship between design and lithography costs, namely

Table 1.1: The ITRS requirement of gate dimension variation control is becoming more stringent as the technology scales [2]. MPU, micro-processor unit.

| Year                  | 2005    | 2007    | 2010                | 2013             |

|-----------------------|---------|---------|---------------------|------------------|

| Technology Node       | 90 nm   | 65  nm  | 45  nm              | 32  nm           |

| MPU gate length       | 32  nm  | 25  nm  | 18  nm              | $13 \mathrm{nm}$ |

| MPU Gate CD $3\sigma$ | 3.3  nm | 2.6  nm | $1.9 \ \mathrm{nm}$ | 1.3  nm          |

Figure 1.5: Mask data volume as the technology scales [4].

that the total cost to produce low-volume parts (such as most ASIC designs) is dominated by mask costs [6].

## 1.2 Various RETs

Figure 1.6 showed four basic properties: wavelength, amplitude, phase, and direction. RET (resolution enhancement technology) is wavefront engineering to enhance

Figure 1.6: Properties of a wave: wavelength, amplitude, phase, and direction.

$$O \bigoplus_{a)} \bigoplus_{b)} \bigoplus_{c)} \bigoplus_{d)} \bigoplus_{e)} \bigoplus_{f)} \bigoplus_{g)} \bigoplus_{h)}$$

Figure 1.7: Idealized pupil maps for various a) conventional and off-axis illumination schemes: b) annular; c) "fourfold" source; d) "separated" source; e) quadrupole; f) "CAUEST"; g) quasar; and h) dipole.

lithography by controlling these levers.

- Wavelength. In lithography, wavelength is set by the choice of light source, and it has been significantly shifted from 365 nm to 193 nm to achieve smaller resolutions since the 80's. However, if λ has to be further reduced to go beyond the limits of resolution, light is increasingly absorbed by practically any material so that it is impossible to build a refractive optics for small wavelength. It is expected that with immersion tools operating for instance at 193 nm, a resolution of 50 nm and below can be achieved.

- Direction. Different illumination types (see Figure 1.7) are used to change the direction of the wavefront to achieve the ultimate resolution of  $k_1$ =0.25. These techniques are referred to as OAI (off-axis illumination) and the principles are illustrated in Figure 1.8. As the resolution on the mask becomes small, the diffracted angle resulting from the first-order light becomes so large that it is beyond the acceptance of the exposure lens making the image contrast zero. OAI improves the contrast of the image by transmitting more of the diffracted orders through the lens. The angle of OAI is a function of feature pitch, which

leads to a well known phenomenon that the lithographic benefit afforded by OAI erodes as feature pitches vary from the one that the illumination angle has been optimized for. To prevent this loss of process window, dummy features (or sub-resolution assist features (SRAFs)) are added to the layout to lithographically emulate the primary pitch as mentioned in the next paragraph.

- Amplitude. Amplitude control comes from changing the shapes of the geometry openings. This technique is known as OPC (optical proximity correction), which include two types: rule-based OPC and model-based OPC. Rule-based OPC applies corrections to the mask based on a predetermined set of rules. Originally only rule-based OPC was needed, e.g., iso-dense biasing, line end extensions or serif additions, and SRAFs insertion (see Figure 1.9). It worked well for simple and moderate needs. From 130 nm technology onwards, rule-based OPC has given way to model-based OPC which uses process simulation to determine corrections to the masks. These corrections, generated in accordance with the results of these simulations, generally provide more accuracy and leads to higher yield at the expense of higher cost and longer run time. Most of the time, a hybrid flow of rule-based OPC followed by model-based OPC is adopted for best performance (illustrated in Figure 1.10).

- *Phase.* Phase shifting masks (PSMs) [8] are used to create interference fringes on the wafer that boost contrast, enabling extremely small features. It has been demonstrated for a variety of applications, and has been used to manufacture commercial devices. Many techniques for phase shifting and phase assignment algorithms have been demonstrated [9]. This technique, however, often results in conflicting phase assignment on layout regions, which can potentially be

Figure 1.8: Principle of OAI [7].

resolved by enforcing radically restricted design rules (RDRs).

### **1.3** Modeling Process Variation in Design

Although various RETs have been deployed to enhance feature resolution and improve chip yield, these modifications, significantly affected chip performance. There have been efforts to consider process variation of parameters such as gate CD, oxide thickness, metal width and thickness, temperature, voltage, etc., during circuit performance analysis at the design stage but this requires proper modeling of the variabilities [10; 11; 12]. The most common approach to modeling variability, typically aimed at speed/frequency prediction, is based on "worst case scenarios" (corner cases). This approach assumes all parameters are independent and hence yields overly pessimistic simulations, making the design unnecessarily difficult [13; 14]. Other approaches seek to provide more accurate variability modeling by considering its sources in more detail. Treated statistically, process variations are modeled using a probabilistic framework with effort to accurately model correlations [14; 15]. More than 50% of  $L_{gate}$  variation is due to systematic sources [16], which can be modeled

accurately once the physical layout is completed. In fact, assumptions about the  $L_{gate}$  distribution in Monte Carlo simulations and statistical timing analysis in general, could be made more rigorous by considering realistic systematic contributions (the majority of which arises due to proximity effects) to the overall process variation [51; 17; 18]. With measured data, [51] show a significant systematic intra-chip variability of  $L_{gate}$  leading to large circuit path delay variation. That work estimates the location-dependent  $L_{gate}$  variation by classifying the layout patterns within 5 categories; in actuality there are many more relevant scenarios, complicating the approach. References [17; 18] use aerial image process simulations to account for systematic  $L_{gate}$  variations; however, these simulations are limited to fixed layout patterns and cannot be expanded to full-chip timing analysis. In [19] the authors propose a systematic variation-aware static timing methodology using library-based OPC. However, at the full-chip level OPC features applied to a given library cell will not be identical across all instances and depend largely on neighboring geometries. This approach therefore loses the advantage of model-based OPC, particularly considering those cells with small sizes (in which OPC applied throughout the cell can easily be impacted by neighboring patterns) and high frequency of occurrence on critical paths (e.g., inverters, NANDs) sacrificing the accuracy claimed in their static timing analysis. It is necessary to investigate the impact of modifications on post-signoff designs (especially OPC) given that new steps emerging in advance technologies will notably change performance specs and therefore should be considered in the pre-signoff design flow.

Although RETs have historically been strictly a post-layout procedure, they now need to become part of a cohesive design flow in which libraries and layouts are optimized directly based on conflicts discovered by the RET tool [20]. This "trickle-

Figure 1.9: SRAFs help maintain process windows for certain pitch ranges.

down" effect of RETs towards the design process also yields more conservative design rules, particularly for the critical polysilicon layer. In particular, the ability to print very tight pitches as well as print a wide range of pitches in a given layer is very difficult for subwavelength lithographic systems. As a result, there is a trend towards limiting the range of allowed pitches in the polysilicon layer [21]. This type of restricted design rule (RDR) seeks to enforce a particular style of layout that is known to be highly manufacturable. As with any design rule, it is a tradeoff between manufacturability and performance, where performance can be measured as layout density, delay, power, etc. By nature, these RDRs seek to push the tradeoff more in favor of the manufacturing side, sacrificing performance in the process. Despite the move towards RDRs, there has been no comprehensive and systematic study of their expected impact on manufacturability and performance. On the other hand, RDRs may over constrain certain design layout and sacrifice the benefits achievable by technology scaling. The use of flexible design rules (FDRs - this approach starts with a RDR-compliant layout and relaxes the rules to recover area in the printability sweet spots, as well as tightens the rules in the hotspot regions) should be considered when RDRs alone are not sufficient to guarantee high yield or waste too much chip

Figure 1.10: Model-based OPC on SRAF layout.

area.

### 1.4 Thesis Outline

This thesis is organized as follows. In Chapter II, we first establish a framework for assessing the impact of process variation on circuit performance, product value and return on investment across various technologies. Elements of our framework include accurate device models and circuit simulation, along with Monte-Carlo analyses, to estimate parametric yields. We evaluate the merits of considering such previously unconsidered phenomena as correlations among process parameters. We also evaluate the impact of process variation with respect to such relevant metrics as *parametric yield at selling point*, amount of *required design guardbanding*, and *inferred process variation control*. Performance variation trends along with technology scaling in terms of the degree of control level in process variation and changes in number of critical paths is also presented.

Using the framework mentioned above, gate CD variation is identified as the most

important parameter on which performance shows most sensitivity. To address this effect and to meet the stringent ITRS requirement of gate CD  $3\sigma$  control while obtaining the lowest cost of ownership (CoO), Chapter III describes a novel minimum cost of correction (MinCorr) methodology. This approach determines the level of correction of each layout feature such that prescribed parametric yield is attained with minimum RET cost. This flow is implemented with model-based OPC explicitly driven by timing constraints. We apply a mathematical programming-based slack budgeting algorithm to determine OPC level for all polysilicon gate geometries. Designs using this methodology show up to 20% MEBES data volume reduction and 39% OPC runtime improvement.

Chapter IV uses state-of-art process control techniques to analyze the impact of systematic correction residual errors on a microprocessor's speedpath skew. A platform is created for diagnosing and improving OPC quality on gates with specific functionality such as critical gates or matching transistors. With the more accurate timing analysis we highlight the necessity of a *post-OPC verification* embedded design flow.

After this in Chapter V and Chapter VI, we show a framework to quantify the performance, manufacturability and mask cost impact of globally applying several common restrictive design rules (RDRs) to reduce pitch size induced process variations. At the end, a practical hybrid method for adapting restricted design rules and flexible design rules based on pattern matching are presented. In this way, we may greatly leverage learning from manufacture side to best use the design space for yield enhancement and performance improvement.

Finally, conclusions and directions for future work are given in Chapter VII.

### CHAPTER II

# Design Sensitivities to Variability

### 2.1 Introduction

Aggressive technology scaling has introduced new variation sources and made process variation control more difficult. As a result, semiconductor manufacturing equipment will be strained to maintain constant process variation levels in future technology nodes. Despite the relaxation of some  $3\sigma$  tolerances, there are no known solutions for a number of near-term variability control requirements (according to the ITRS [2]). Moreover, observation of key markets that drive the semiconductor industry reveals the potentially large impact of variability on the value of semiconductor products. Semiconductor enterprises must be cognizant of the different risks and ROI opportunities from, e.g., an extra increment of  $T_{ox}$  or  $L_{eff}$  CD control, versus new design for value design technologies, versus revised performance targets for products, etc. In this chapter, we describe key elements of a framework that will allow the semiconductor industry to assess the impact of process variation on circuit performance, manufacturing cost, and product value in nanometer technologies (130nm through 70nm). Our framework is built on accurate circuit design models, statistical models of process variation, a combination of circuit simulators and analytical performance models, and application of Monte Carlo analyses to estimate parametric yields. We evaluate the merits of taking into account previously unconsidered phenomena such as correlations among process parameters. We also evaluate the impact of process variation with respect to such metrics as *parametric yield at selling point*, amount of *required design guardbanding*, and *inferred process control* for desired design guardbanding. Key contributions of our work include:

- a more comprehensive modeling of process variation according to the causing sources, with different handling of die-to-die (D2D) and within-die (WID) variations;

- accurate models of *correlations* of variation;

- realistic and quantified projection to future process nodes of the impact of variability on critical-path delays; and

- analysis of the sensitivity of performance variation to improved control of individual device parameters and variation sources, measured by change in the number of "sellable" chips produced, extent of guardbanding required to meet a given parametric yield target, and inferred process variation control for the desired design guardbanding.

Our experimental results yield surprising insights into the scaling of process variation impacts through the next two ITRS technology nodes, as well as the prioritization of various areas for future technology investment. The latter type of contribution, even if not fully achieved by this initial work, is required for principled allocation of R&D resources among multiple semiconductor supplier industries to solve the variability problem (cf. "shared red bricks" [22]) <sup>1</sup>.

<sup>&</sup>lt;sup>1</sup>Sources at a major semiconductor vendor indicated that substantial effort and capital has been invested for  $V_{th}$  control because of its huge impact on design performance. This anecdotal evidence

## 2.2 Taxonomy of Variation

Circuit variability refers to deviations of either process or circuit parameters (e.g.,  $L_{eff}$ ,  $V_{dd}$ , conductor thickness, etc.) from nominal values. It is introduced either during chip fabrication or due to circuit operation. Based on the inherent spatial scales of such variability, it is often characterized as either within-die or die-to-die variation. In this study, we consider the impact of both types of variations. The taxonomy of variability used in our framework is as follows.

- D2D Variation. D2D variation affects each element on a chip equally and adds a random effect across the wafer. This variation determines the nominal value of each parameter on the die with these values differing among chips across the wafer and from wafer to wafer. D2D variation is estimated to comprise approximately 50% of the total CD variance for today's technology generations [30]. It is mostly design-independent and is related to equipment properties, wafer placement, processing temperatures, etc. [31]. For simplicity, we only model D2D variations due to random effects (i.e., we ignore systematic D2D effects that can be predicted, modeled, and designed around during the design process).

- *WID Variation.* WID variation can be divided into two contributors, *systematic* and *random*.

- Systematic WID variation. In contrast to D2D variation, systematic WID variation is layout-dependent and may cause chip malfunction. It is predictable in the sense that a given pattern yields the same characteristics on

supports our claim; that significant engineering effort and capital investment can be expended to reduce many sources of variability but we would like the investment to be directed to the key items.

all dies. Successful scaling of MOSFET technology to sub-100nm process geometries relies on compensation of systematic variation components at the design and reticle stages. Such corrections to systematic process variation can be applied to reduce the systematic WID variation but may not completely eliminate it. For example, the same optical proximity corrections applied to identical NAND gates may not result in identical physical dimensions due to the impact of different local feature densities.

- Random WID variation. Random WID variation is due to the inherent unpredictability of the semiconductor fabrication process. Fluctuations in channel doping, gate oxide thickness, and ILD permittivity are primarily due to random variation. This type of variation is likely to have spatial correlation, making nearby devices more similar than ones that are across the die from one another. As random phenomena cannot be compensated for and are difficult to minimize, this type of variability may eventually pose the most significant challenge to design of adequately yielding nanometer-scale MOSFET circuits.

### 2.3 Experimental Testbed and Methodology

In this section, we describe elements of our experimental testbed. The key components are

- a parameterized scalable single critical path circuit model, and a multi-critical path model composed of a user-selectable number of independent single critical paths;

- 2. consideration of correlations among the parameter variations;

Figure 2.1: A single critical path structure for performance study.

| <u> </u>                      | 100                               | 100                               | 100                               | -                                 |

|-------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|

| Technology                    | 180 nm                            | 130 nm                            | 100 nm                            | 70 nm                             |

| Device                        | NMOS PMOS                         | NMOS PMOS                         | NMOS PMOS                         | NMOS PMOS                         |

| $L_{eff}(nm)$                 | $100 \pm 16.7\%$ $100 \pm 16.7\%$ | $65 \pm 16.7\%$ $65 \pm 16.7\%$   | $45 \pm 16.7\%$ $45 \pm 16.7\%$   | $28 \pm 16.7\%$ $28 \pm 16.7\%$   |

| $T_{ox}(A)$                   | $22\pm4\%$ $22\pm4\%$             | $16 \pm 4\%  16 \pm 4\%$          | $13\pm\%4$ $13\pm\%4$             | $10\pm 4\%$ $10\pm 4\%$           |

| $R_{dsw}(\Omega - \mu m)$     | $250\pm10\%$ $450\pm10\%$         | $200 \pm 10\%  400 \pm 10\%$      | $180 \pm 10\%  300 \pm 10\%$      | $150 \pm 10\% = 280 \pm 10\%$     |

| $\mathbf{X}_t$ (nm)           | 30                                | 24                                | 20                                | 13                                |

| $V_{th}(V)$                   | $0.214 \pm 10\% - 0.327 \pm 10\%$ | $0.232 \pm 10\% - 0.273 \pm 10\%$ | $0.217 \pm 10\% - 0.254 \pm 10\%$ | $0.169 \pm 10\% - 0.218 \pm 11\%$ |

| Interconnect                  | Local Global                      | Local Global                      | Local Global                      | Local Global                      |

| ε                             | $3.5 \pm 3\%$                     | $3.2\pm5\%$                       | $2.8\pm5\%$                       | $2.2\pm5\%$                       |

| w(nm)                         | $250\pm20\%$ $525\pm20\%$         | $175 \pm 20\%$ $335 \pm 20\%$     | $123 \pm 20\%  237 \pm 20\%$      | $85 \pm 20\%$ 160 $\pm 20\%$      |

| s(nm)                         | $250\pm20\%$ $525\pm20\%$         | $175 \pm 20\%$ $335 \pm 20\%$     | $123 \pm 20\%  237 \pm 20\%$      | $85 \pm 20\%$ 160 $\pm 20\%$      |

| t(nm)                         | $500 \pm 10\%$ $1050 \pm 10\%$    | $280 \pm 10\% = 670 \pm 10\%$     | $197 \pm 10\%  498 \pm 10\%$      | $145 \pm 10\%  325 \pm 15\%$      |

| h(nm)                         | $500\pm15\%$ $1050\pm15\%$        | $280 \pm 15\% = 670 \pm 15\%$     | $197 \pm 15\%  498 \pm 15\%$      | $145 \pm 15\%$ $325 \pm 15\%$     |

| $\rho (\Omega - m)$           | $2.2e-8\pm30\%$                   | $2.2e-8\pm30\%$                   | $2.2e-8\pm30\%$                   | $2.2e-8\pm30\%$                   |

| $\operatorname{Rvia}(\Omega)$ | $23 \pm 20\%$                     | $25 \pm 20\% 2$                   | $27 \pm 20\%$                     | $29 \pm 30\%$                     |

| $Length(\mu m)$               | 62.5 5000                         | 55.56 3333                        | 50 2500                           | 45.45 2000                        |

| $Wn(\mu m)$                   | 1.26 15                           | 1.008 9.75                        | 0.756 - 6.75                      | 0.479 - 4.2                       |

| Dynamic                       |                                   |                                   |                                   |                                   |

| $V_{dd}(V)$                   | $1.8 \pm 10\%$                    | $1.2 \pm 10\%$                    | $1.0\pm10\%$                      | $0.9 \pm 10\%$                    |

| Tr(ps)                        | 160                               | 125                               | 110                               | 87                                |

| Temp $(^{o}C)$                | 25                                | 25                                | 25                                | 25                                |

Table 2.1: Parameter values and  $3\sigma$  variations

- 3. comprehensive and physically sensible handling of variation with respect to its underlying sources; and

- 4. use of detailed device modeling and circuit simulation within a Monte-Carlo methodology.

We start from the study of a single parameterized critical path, illustrated in Fig. 2.1. It is composed of l identical local stages and one long top-level buffered global interconnect. The parameter l is set to 10 at the 130nm technology node and is reduced by one in each subsequent generation to reflect aggressive pipelining techniques and other micro-architectural advancements. In each local stage, a 2-input NAND gate drives a short local line with length estimated by [2]. The NAND is sized to optimize the speed-power tradeoff (fanout=2), i.e., the knee of the delay vs.

sizing curve as in the Berkeley Advanced Chip Performance Calculator (BACPAC) [23].The global line length remains constant at 10mm in all technology nodes, consistent with the 2001 ITRS projections of fixed die size for future microprocessors [2]. Optimal inverting repeaters are inserted at even intervals into the global line to minimize delay. Parasitic via resistance is considered. Overall, we closely follow the 2001 ITRS (high-performance MPU) critical path model [2]. For each local stage and the global line, we add two quiet parallel neighboring lines to provide a more realistic capacitance environment. Each line is modeled as a sufficiently long chain of L segments to capture the distributed RLC characteristics. We then combine n such identical single critical paths to capture the impact on chips with multiple critical paths. Input transition times to initial stages are set at 20% of the clock period. Further details of the critical path models, including line lengths, gate sizes, and signal transition times, are listed in Table 2.1. The nominal dimensions of interconnect are taken from [24]. Note that the critical path structure is meant to include sources of delay such as local computation and global communication that are important in generic paths of the today's very large scale integrated circuits. Hence, the path delay is not meant for cycle time estimation so the absolute value is not relevant.

Previous work assumes that variation sources are either independent of each other [3] [25] or perfectly correlated [25]. By contrast, our work recognizes several strong correlations. Specifics include:

•  $V_{th}$  is a function of  $T_{ox}$ ,  $N_{ch}$ ,  $L_{eff}$  and  $X_t$ , calculated from a delta-doping approximation and BSIM3v3 models. Here,  $X_t$  is the retrograde channel depth and  $N_{ch}$  is the effective channel doping [26].

- Corresponding parameters of NMOS and PMOS have a correlation coefficient of one, i.e., NMOS and PMOS in the same gate exhibit the same deviations from respective means. This pertains to parameters that are shared among the two device types, such as drawn channel length and oxide thickness, but is not applicable to steps such as channel doping that are independent for NMOS and PMOS.

- Assuming a fixed wire pitch, wire spacing variation is the negative of wire width variation. Metal thickness (T) and underlying interlevel dielectric (ILD) thickness (H) are negatively correlated with a correlation coefficient of -1 (this value stems from the relationship of trench etch depth in damascene processes as well as chemical-mechanical polishing effects which act to reduce the correlation between T and H).

- Spatially proximate devices and interconnections (e.g., in local stages) have similar variations.

- We model the spatial correlation among repeaters inserted along the global line by incorporating a distance-dependent correlation parameter. This correlation decays linearly with distance to a value of zero (implying complete independence) over a length scale of 1cm [27]. This value of 1cm is parameterizable.

- Our interconnect spatial correlation modeling is more involved. We divide the global line into 100μm segments. Interconnect parameters within each segment are perfectly correlated. We assume that correlation between segments decays linearly with separation. At a certain distance, this correlation equals zero. For interconnect width and space, we take this separation distance to be 5mm for all the technology nodes [28] while it is 2mm for metal thickness and ILD

thickness [29]. In contrast to line width which is set by the dielectric etching process, ILD thickness and metal thickness is largely set by the CMP step in damascene processes. Numerous prior studies have investigated the concept of CMP planarization length; this relates to the distances over which features can be considered to be correlated due to pad deformation and other physical phenomena. This planarization length is typically found to be on the order of 2mm, motivating our choice of separation distance. This, in contrast to an interconnect model with perfect correlation, avoids the overestimation of interconnect variation.

• WID and D2D variation are assumed to be equal in magnitude [30]. Systematic WID variation equally affects all critical paths on the same die, while random WID variation adds random effects to the deterministic systematic WID variation.

We assume parameter variations to be normally distributed with mean and  $\sigma$  values derived from [2], [24], and industry sources. In [2], the allowed variability in physical gate length is fixed at 10%. The magnitude of the physical gate length is approximately half of the technology node, or the DRAM half-pitch. Translating this uncertainty to effective channel length, which is also a fraction of physical gate length due to source-drain extension (SDE) underdiffusion, we expect a  $3\sigma$  for  $L_{eff}$  of greater than 10%. In this work, we approximate  $L_{eff} = 0.6 \times L_{physical}$ , leading to a  $3\sigma$  process tolerance throughout the roadmap of 16.7%. Different approaches may be taken including an assumption that the SDE underdiffusion has a fundamental lower limit that pushes  $L_{eff}$  to be a smaller fraction of  $L_{physical}$ . This will result in either (1) larger uncertainty in  $L_{eff}$  or (2) less aggressive scaling of  $L_{physical}$  to compensate.

Either of these alternatives can be readily investigated in our framework.

We model variabilities caused by three types of sources: systematic WID, random WID and random D2D, in our Monte-Carlo analysis based framework. A prespecified number (n) of nominally identical independent critical paths are considered (note that these critical paths are only independent with respect to WID variation; their D2D components are identical). Systematic WID variation, which is assumed to be due to layout pattern dependence, is applied across different critical paths. We expect different dies to have the same distribution of systematic WID variation. Therefore, systematic WID variation is used to shift the nominal value of the parameters for different critical paths, i.e., systematic WID variation is modeled by generating n samples from a Gaussian  $N(0, \sigma_{SYS-WID})$  distribution before running the Monte-Carlo simulations.<sup>2</sup> Random WID variation is modeled as a Gaussian  $N(0, \sigma_{RAN-WID})$  random variable. It observes spatial correlation at the die-scale as previously described. Random D2D variation is modeled as a Gaussian  $N(0, \sigma_{RAN-D2D})$  random variable. All the variations observe the w-s and t-h correlations outlined previously. Hence, the value (X) for a given parameter for a device *i* in path *j* in the  $k^{th}$  Monte-Carlo run is given by Equation 2.1.

$$X = \mu + x_{SYS-WID}^{j} + x_{RAN-WID}^{i,j,k} + x_{RAN-D2D}^{k}$$

$$\forall 1 \ge j \ge n, \ 1 \ge k \ge m$$

$$(2.1)$$

where  $\mu$  is the nominal value of the parameter,  $x_{SYS-WID}^{j}$  is the systematic variation sample corresponding to path j and  $x_{RAN-WID}^{i,j,k}$  ( $x_{RAN-D2D}^{k}$ ) is the  $k^{th}$  sample for random WID (D2D) variation for device i in path j. Moreover, all variations are

<sup>&</sup>lt;sup>2</sup>Since the significance of systematic WID variation lies in introducing mismatch in *pathdelays* rather than individual device delays, we do not consider systematic WID variation within a path.

Table 2.2:

and no correlations for 100 nm technology node

| Delay (ps)          | Mean   | $3\sigma$ | Normalized $\frac{3\sigma}{mean}$ |

|---------------------|--------|-----------|-----------------------------------|

| 0 correlation       | 1453.9 | 133.9     | 0.9808                            |

| Spatial Correlation | 1452.5 | 136.4     | 1                                 |

| Perfect Correlation | 1454.3 | 139.5     | 1.0216                            |

assumed to be independent. Therefore, the total variance of the parameter is given by Equation 2.2.

$$\sigma_{total}^2 = \sigma_{SYS-WID}^2 + \sigma_{RAN-WID}^2 + \sigma_{RAN-D2D}^2$$

(2.2)

We perform circuit simulation for a single critical path in a projected 100nm technology with a distributed-lumped RLC interconnect model and all correlations included. Table 2.2 compares the delay distributions obtained using our Monte Carlo simulation methodology for RLC interconnect model with (1) perfect correlations (correlation=1), (2) no correlations (correlation=0) and (3) spatial correlations. As can be seen, simulations with perfect/no correlations in fact set the upper/lower bound for total delay variation and as such they either overestimate or underestimate. While the magnitude of the delay variation due to interconnect fluctuations is not large, this demonstrates the effect of more accurate and detailed modeling of process variability for the purpose of assessing its impact on circuit performance.

In contrast with the linear regression analysis used in [3], our studies use a Monte Carlo (MC) approach with 1000 trials where the variation sources all vary simultaneously. Each model of process variability, at each technology node, gives rise to 1000 sets of random parameter values within the single critical path model which we simulate using HSPICE. In the next section, we proceed to investigate the resulting delay distributions in the single critical path model, in an attempt to gauge (1) the true impact of variability on circuit performance, and (2) the true value of developing improved process control, e.g., 1nm tighter control on interconnect thickness. With knowledge of the above, simulations for multi-critical paths are then performed: the maximum delay is obtained for each die, and performance and yield analyses are performed on m such samples on the whole wafer.

#### 2.4 Impact on Future Circuit Performance

To assess the impact of process variation on critical path delay we adopt two different metrics.

- 1. Selling point parametric yield. We assume target parametric yield to be 99.7%. This corresponds to the mean+ $3\sigma$  point on the delay distribution and is taken to be the selling point of the chip. We take the delay distributions for values drawn from Table 2.1 as the "baseline" results for all technologies. The selling point is calculated from the baseline distribution. The change in parametric yield at the selling point is then taken as a measure of impact of process variation.

- 2. Guardbanding Analysis. Guardbanding is the typical approach followed in industry to account for variability. A larger amount of guardbanding implies a more conservative design and hence is not preferred. The expected ("designedfor") value of performance is given by the mean of the delay distribution. Thus, the difference between the selling point and the mean gives the amount of guardbanding required. That is,  $\frac{3\sigma}{mean}$  expressed as a percentage gives the required guardbanding.

| Delay (ps)                | 130nm | 100nm | 70nm  |

|---------------------------|-------|-------|-------|

| Mean                      | 1502  | 1453  | 1537  |

| $3\sigma/\text{Mean}$ (%) | 30.03 | 28.16 | 26.75 |

Table 2.3:

Trends of performance variation

We have conducted experiments that change the expected  $3\sigma$  variation of all parameters listed in Table 2.1, but due to space constraints we report results only for  $L_{eff}$ , which is the most significant contributor to process variation impact. Thus, the  $3\sigma$  variations listed in Table 2.1 for parameters other than  $L_{eff}$  are held fixed in the following experiments.

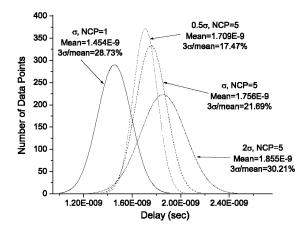

# 2.4.1 Studies for A Single Critical Path Cumulative Effect of All Parameter Variations

We simulate a single critical path and measure delay with all the parameters varying with  $3\sigma$  and mean values as specified in Table 2.1. This simulation result is taken as the "baseline" result for all the comparisons and analysis of a single critical path explained in the subsequent subsections. Table 2.3 and Fig. 2.2 shows the *baseline* delay variation trends with technology scaling. The  $\frac{3\sigma}{mean}$  value of delay drops by 6.6% from 130nm to 100nm, and by 5.3% from 100nm to 70nm. Overall, it remains fairly constant with technology scaling. The slightly decreasing trend of delay variation for our *baseline* setup with technology scaling can be explained as follows.

Assuming a critical path is formed by N identical stages, among which either perfect correlation (correlation=1) or no correlation (correlation=0) exists, the  $\frac{3\sigma}{mean}$  value of the total path delay is given by Equation 2.3.

Figure 2.2: Effect of process control on required guardbanding to achieve 99.7% parametric yield.

$$\left(\frac{3\sigma}{mean}\right)_{path} = \begin{cases} \left(\frac{3\sigma}{mean}\right)_{stage}, & correlation = 1\\ \\ \frac{1}{\sqrt{N}}\left(\frac{3\sigma}{mean}\right)_{stage}, & correlation = 0 \end{cases}$$

(2.3)

Parameter N increases for global stages due to more aggressive buffering but decreases for local stages. The zero correlation assumption leads to a  $(\frac{3\sigma}{mean})_{path}$  that is determined by both  $\sqrt{N}$  and  $(\frac{3\sigma}{mean})_{stage}$ , while under the assumption of perfect correlation, it is only a function of  $(\frac{3\sigma}{mean})_{stage}$ .

Our analysis follows three steps. First, in order to investigate the trend of  $(\frac{3\sigma}{mean})_{path}$ , it is essential to know what trend  $(\frac{3\sigma}{mean})_{stage}$  follows. Table 2.4 shows that the delay variation of a single local stage remains fairly constant though 130nm to 70nm technology node. Although a smaller average stage delay is expected for more advanced technologies, a constant trend for  $(\frac{3\sigma}{mean})_{stage}$  is possible due to the ITRS expectations of a constant level of process variation achieved through advanced lithography tools. Second, the delay variations obtained for local stages in our testbed show that spatial correlation and perfect correlation assumptions have very close re-

Table 2.4: Trends of delay variation for a single local stage

Figure 2.3: Trends of normalized required guardbanding for global stages, local stages and total critical path.

sults (difference within 4%). This implies that a decreasing N does not have an impact on path delay variation for local stages. Instead, the path delay shows a similar trend as obtained for a single stage - it remains fairly constant for the next two technology generations. Finally, the delay variation for global stages is shown to decrease at a reasonably fast rate due to the increased number of repeaters inserted (i.e., N is increased in Equation 2.3). This presents a dominating effect for future technologies and causes the trend of total delay variation to reduce, as shown in Fig. 2.3.

## Sensitivity to Process Tolerance

To determine the sensitivity of performance to individual parameter tolerances, we changed the  $\sigma$  values from those in Table 2.1 to 0.5 and 2 times their original values. This was done for each parameter individually while maintaining the normal

Table 2.5:

<sup>2.5:</sup> A comparison of changes in delay variation when the nominal  $\sigma$  for an individual parameter changes from 0.5X to 2X

| Parameter                        | $L_{eff}$ | $T_{ox}$ | W     |

|----------------------------------|-----------|----------|-------|

| Increase in Delay $3\sigma/mean$ | 82.08%    | 3.96%    | 1.89% |