# Vacuum and Hermetic Packaging of MEMS Using Solder

by

Warren Cornelius Welch III

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 2008

Doctoral Committee:

Professor Khalil Najafi, Chair Professor Yogesh B. Gianchandani Professor Katsuo Kurabayashi Professor Kensall D. Wise Assistant Professor Michel Martin Maharbiz © Warren C. Welch III All rights reserved 2008 To Kate: Your love, dedication, and support made this possible.

To Connor (and everyone else with a curious mind): The key is to never stop asking questions.

# TABLE OF CONTENTS

| Dedication                                    | ii   |

|-----------------------------------------------|------|

| List of Figures                               | vi   |

| List of Tables                                | xiii |

|                                               |      |

| Chapter 1 Introduction                        | 1    |

| 1.1 MEMS Packaging                            |      |

| 1.1.1 Packaging Process                       | 5    |

| 1.1.2 Package Design Considerations           |      |

| 1.2 Solder for Vacuum Packaging               |      |

| 1.3 Thesis Organization                       |      |

| Chapter 2 Wafer Bonding using Standard Solder | 25   |

| 2.1 Wafer Bonding Techniques                  |      |

| 2.1.1 Anodic Wafer Bonding                    |      |

| 2.1.2 Fusion Bonding                          |      |

| 2.1.3 Glass Frit Bonding                      |      |

| 2.1.4 Eutectic Bonding                        |      |

| 2.1.5 Solder Bonding                          |      |

| 2.2 Solder Bonding Theory                     |      |

| 2.2.1 Achieving Good Wetting without Fluxes   |      |

| 2.2.2 Under Bump Metallizations               |      |

| 2.2.3 Solder Temperature Reflow Profile       |      |

| 2.2.4 Bonding Environment                     |      |

| 2.3 Solder Bonding Experiments                |      |

| 2.3.1 Wafer Bonding Equipment                 |      |

| 2.3.2 Solder Experiments                      |      |

| 2.3.3 Localized Solder Bonding Methods                      | 57  |

|-------------------------------------------------------------|-----|

| 2.3.4 Standard Solder Bonding Conclusion                    | 60  |

| Chapter 3 Wafer Bonding using Transient Liquid Phase Solder | 61  |

| 3.1 Previous Work in TLP Solder Bonding                     | 63  |

| 3.2 TLP Solder Bond Process                                 |     |

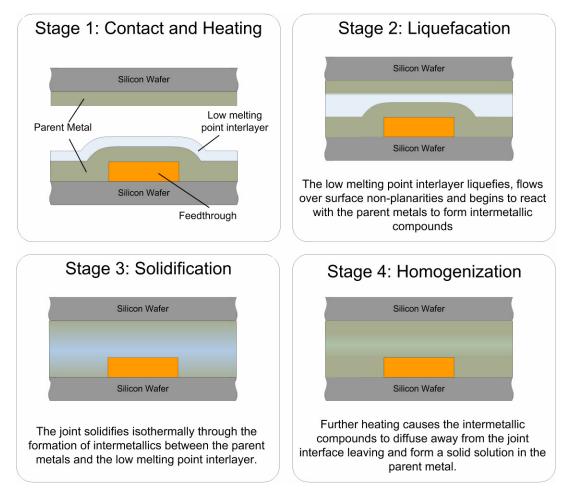

| 3.2.1 Stage 1: Contact and Heating                          | 66  |

| 3.2.2 Stage 2: Liquefaction                                 | 74  |

| 3.2.3 Stage 3: Solidification                               |     |

| 3.2.4 Stage 4: Homogenization                               | 77  |

| 3.3 TLP Bonding Experiments                                 |     |

| 3.3.1 Gold-Tin TLP Solder Bonding                           |     |

| 3.3.2 Nickel-Tin                                            | 83  |

| 3.3.3 Gold-Indium                                           | 89  |

| 3.4 Testing the Wafer Bonds                                 |     |

| 3.4.1 Hermeticity Testing                                   |     |

| 3.4.2 Strength Testing                                      |     |

| 3.4.3 Re-melting Temperature Test Results                   | 101 |

| 3.5 Design Rules for TLP Solder Wafer Bonding               |     |

| 3.5.1 Choosing a material family                            | 102 |

| 3.5.2 Process Design                                        | 104 |

| Chapter 4 Wafer-Level Vacuum Packaging with Solder Bonding  | 112 |

| 4.1 Motivation                                              | 113 |

| 4.1.1 Thermal Isolation                                     |     |

| 4.1.2 Reducing Viscous Fluid Losses                         |     |

| 4.1.3 Other Motivations for Vacuum Packaging                | 123 |

| 4.2 Creating Vacuum inside a MEMS Package                   |     |

| 4.2.1 Leaks                                                 |     |

| 4.2.2 Pumps                                                 |     |

| 4.3 Previous Wafer Bonding Vacuum Packaging Approaches      |     |

| 4.4 Vacuum Packaging with Solder Wafer Bonding                        | 141 |

|-----------------------------------------------------------------------|-----|

| 4.4.1 Vacuum Measurements                                             | 141 |

| 4.4.2 Packaging Experiments                                           | 149 |

| 4.4.3 Titanium Getter Activation                                      | 171 |

| Chapter 5 Transferred Thin-Film Packages with a Solder Transfer Layer | 175 |

| 5.1 Solder as a Transfer Material                                     | 175 |

| 5.2 Wafer-Level Packaging with Transferred Thin-Film Packages         | 176 |

| 5.2.1 Previous Transferred Thin-Film Packaging Approaches             | 177 |

| 5.2.2 Process Flow for Solder Transferred Thin-Film Packaging         | 178 |

| 5.2.3 Package Results                                                 | 180 |

| 5.2.4 Design Guidelines for Solder-Transferred Thin-Film Packages     | 185 |

| 5.2.5 Conclusion                                                      | 190 |

| Chapter 6 Conclusions and Future Work                                 | 191 |

| 6.1 Conclusion                                                        | 191 |

| 6.2 Future Work                                                       | 193 |

| 6.2.1 Lower Pressure Wafer-Bonded Packages                            | 193 |

| 6.2.2 Transferred Thin-Film Packages with Vacuum                      | 194 |

| Appendix A: Raw Data from Shear Strength Tests                        | 195 |

| Bibilography                                                          | 198 |

|                                                                       |     |

# List of Figures

| Figure 1.1: MEMS historical and projected sales by market segment [2] 1                                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

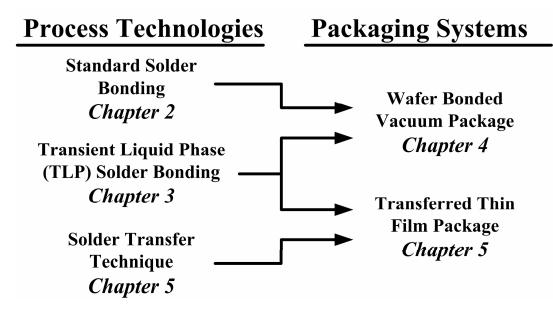

| Figure 1.2 Visual Overview of the research presented in this thesis                                                                                                                         |

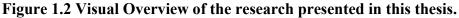

| Figure 1.3 Illustration of a generic MEMS device [3]                                                                                                                                        |

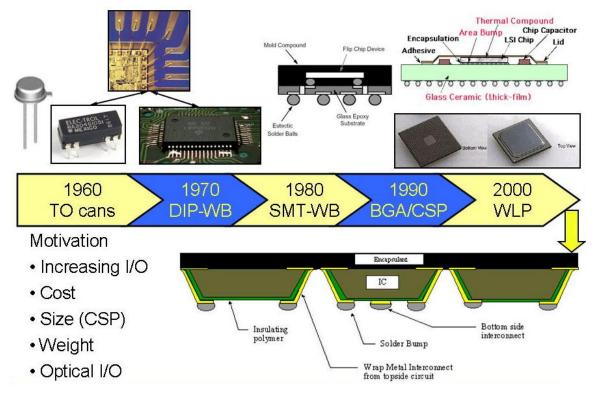

| Figure 1.4 History of the evolution of IC packaging techniques [3]                                                                                                                          |

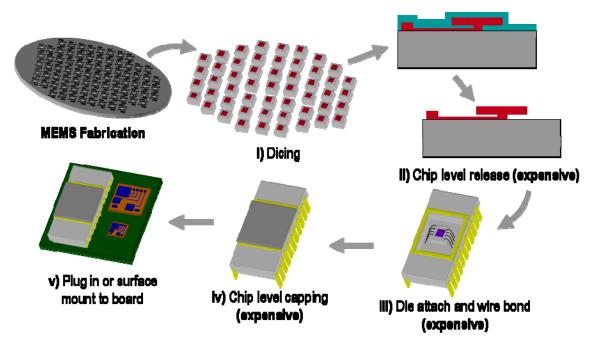

| Figure 1.5 A singulation first package process [5]                                                                                                                                          |

| Figure 1.6 A release-first packaging process [5]                                                                                                                                            |

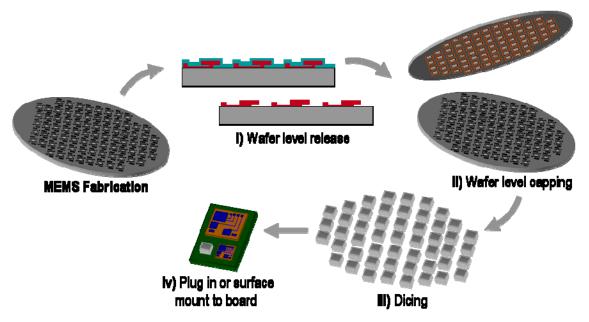

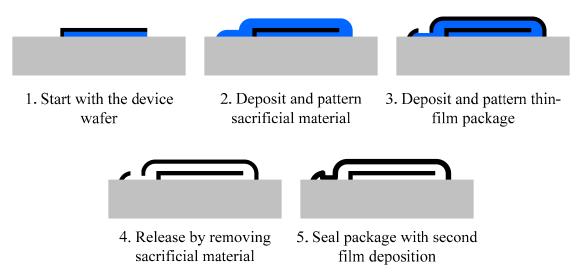

| Figure 1.7 Generic process for integrated thin-film packaging                                                                                                                               |

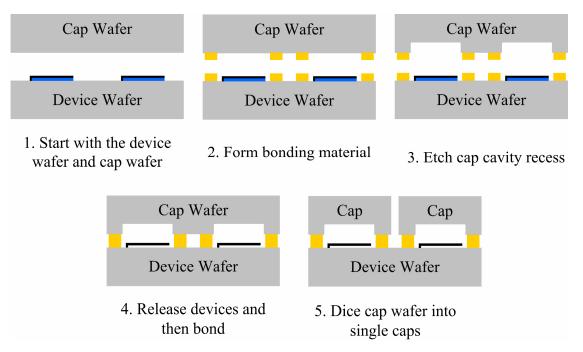

| Figure 1.8 Generic process for wafer bonding packaging                                                                                                                                      |

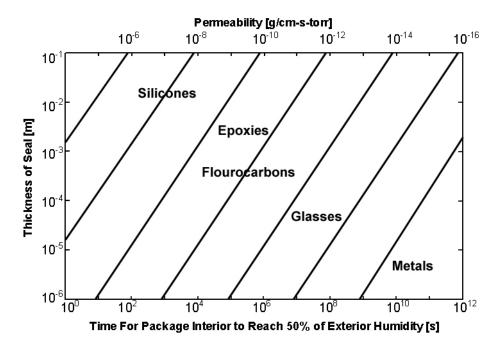

| Figure 1.9 Hermetic performance of different material classes [4]                                                                                                                           |

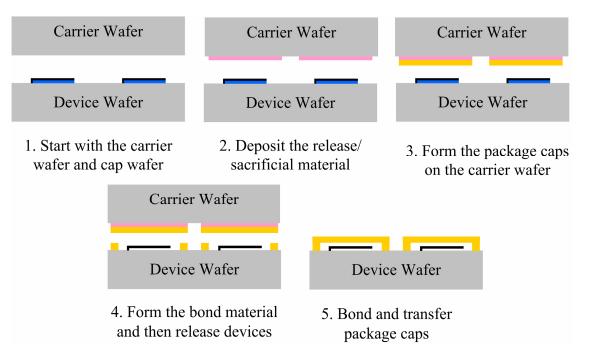

| Figure 1.10 Generic process for transferred thin-film packaging                                                                                                                             |

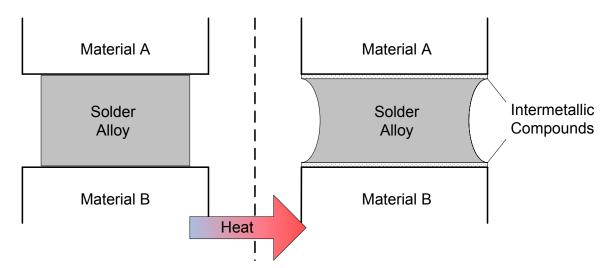

| Figure 2.1 Illustration of the solder bonding concept. Heat applied to the solder causes it to melt and spread over Materials A&B                                                           |

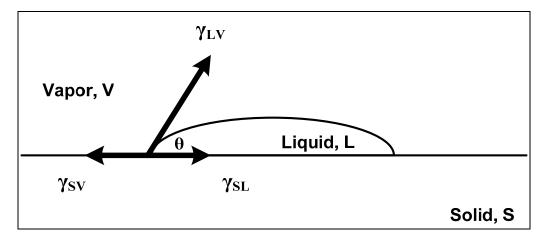

| Figure 2.2 The relative surface tensions of the solid, liquid, and solid-liquid interface will determine the contact angle of a drop of liquid on a solid surface                           |

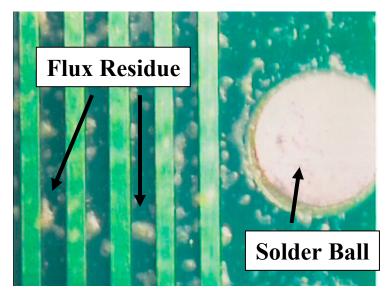

| Figure 2.3 Fluxes are normally used in solder processes, but the residues they leave behind preclude their use in a MEMS soldering process [20]                                             |

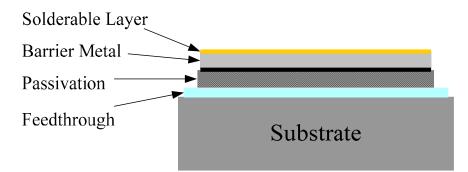

| Figure 2.4 Illustration of the various layers in a UBM that is necessary for a solder bond over a lateral electrical feedthrough                                                            |

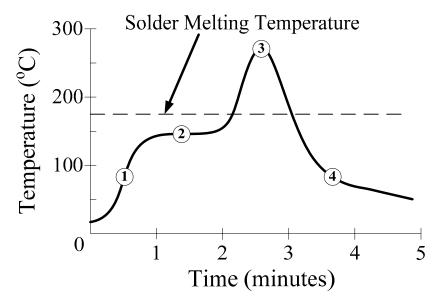

| Figure 2.5 Typical solder reflow profile for Pb-Sn Solder. The profile proceeds through 4 stages: 1) initial heating 2) dwell 3) reflow and 4) cooling [20]                                 |

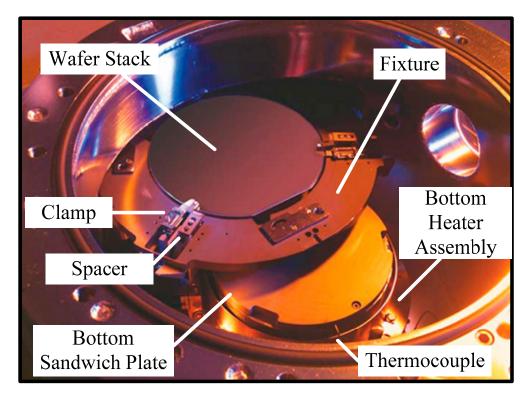

| Figure 2.6 Photograph of the inside of a SUSS SB-6e wafer bonder chamber as the fixture is loaded into the chamber. A great deal of equipment is needed to produce a well aligned bond [30] |

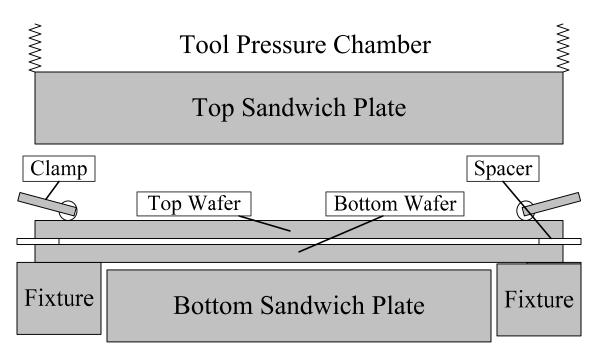

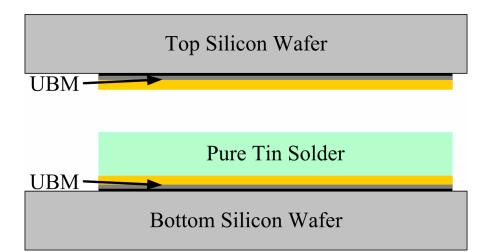

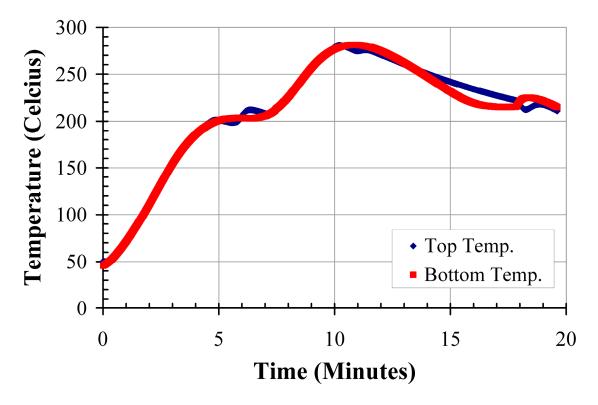

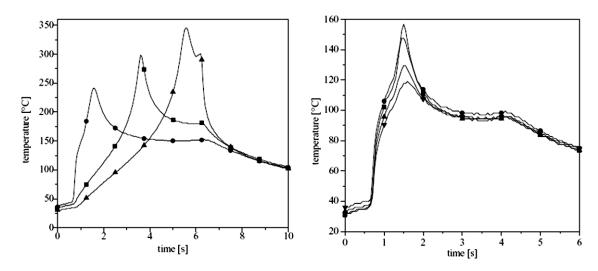

Figure 2.7 Illustration of the side view of the inside of the bond chamber detailing all the

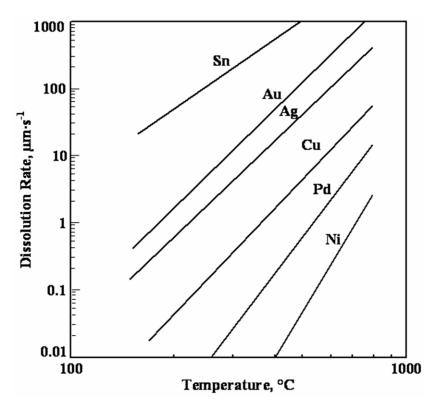

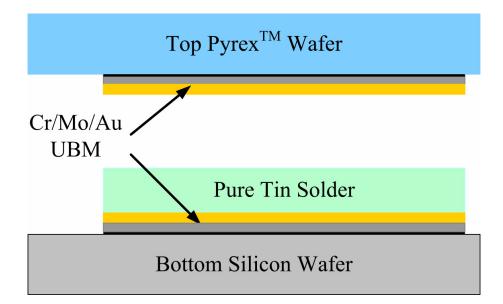

- Figure 2.14 Cross-section of the molybdenum barrier layer UBM experiment prior to bonding. Molybdenum does not form intermetallics with molten tin and therefore has a consumption rate of zero during a solder reflow process. 49

- Figure 2.17 Cross-section for the Au-Sn solder wafer bond directly before bonding. ..... 53

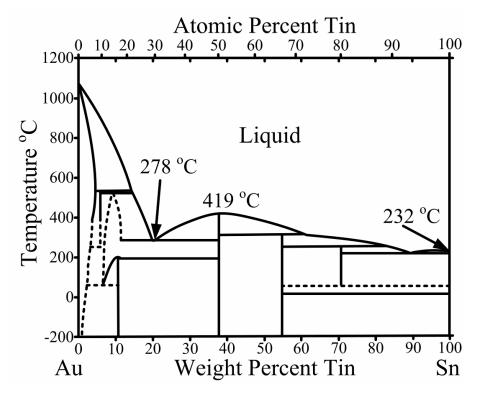

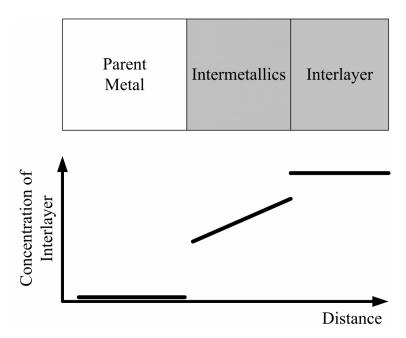

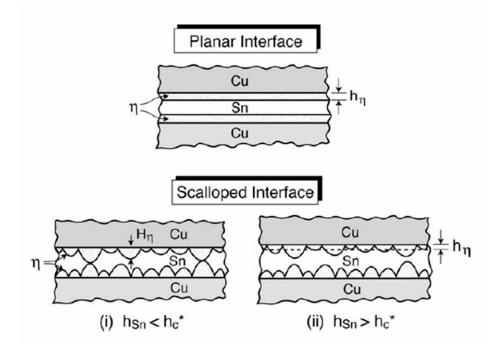

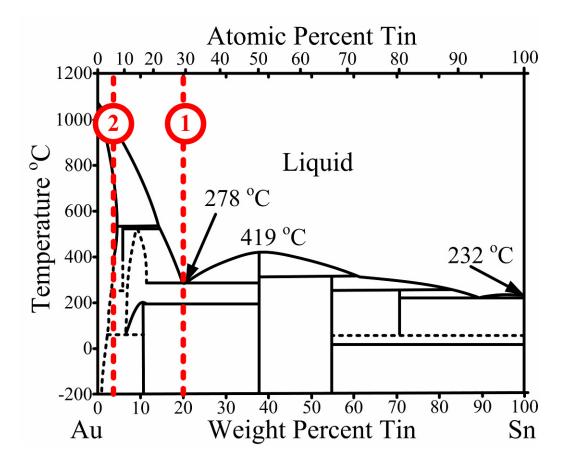

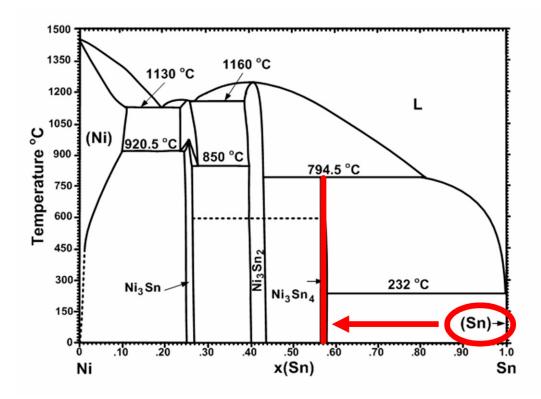

- Figure 3.4 Gold-Tin binary phase diagram. Dotted Line #1 represents the joint composition for a Au-Sn solder bond and Dotted Line #2 is the joint concentration for the Au-Sn TLP solder bond presented in this section... 79

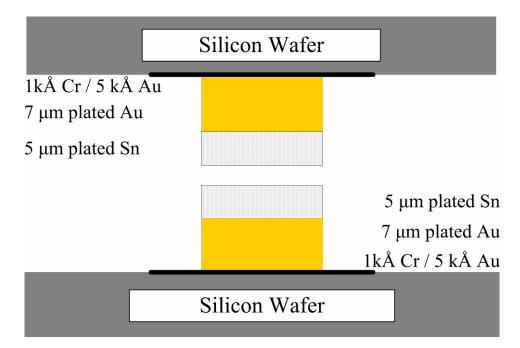

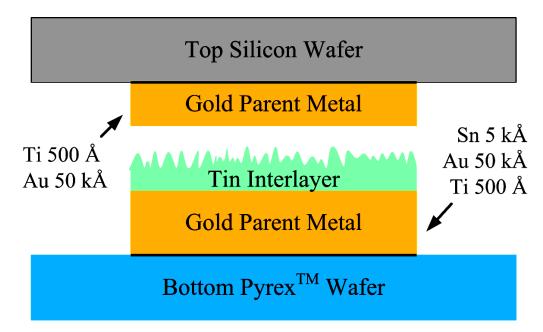

- Figure 3.5 Illustration of the cross-section of the Gold-Tin solder TLP experiment before bonding. The tin layer had an average roughness of 2.5 kÅ, which is typical for tin or indium evaporated onto un-cooled substrates [65]...... 80

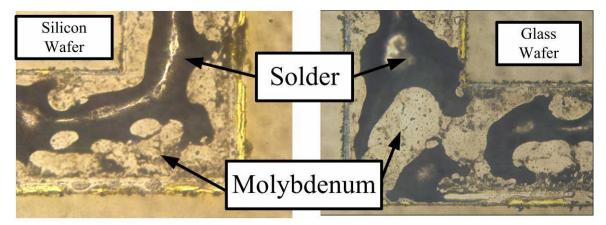

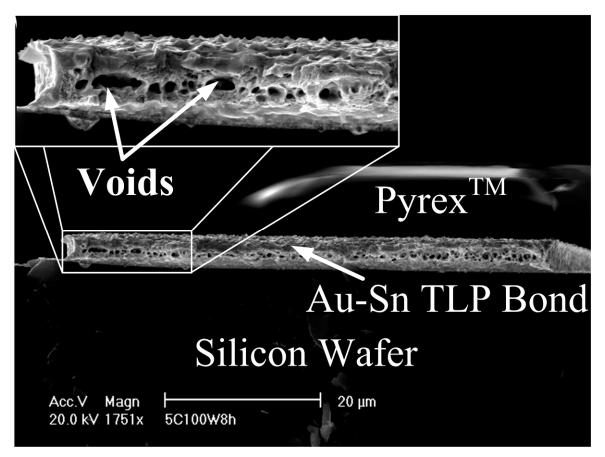

- Figure 3.7 A Gold-Tin TLP bond full of voids caused by a combined low heating rate, high gold-tin intermetallic formation rate, and small interlayer thickness.

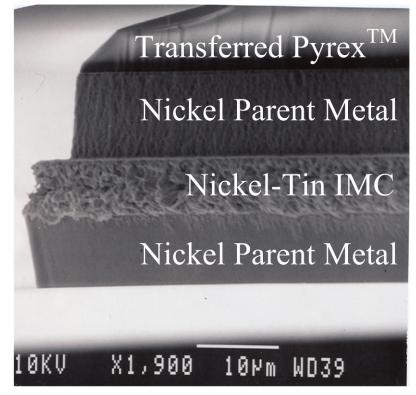

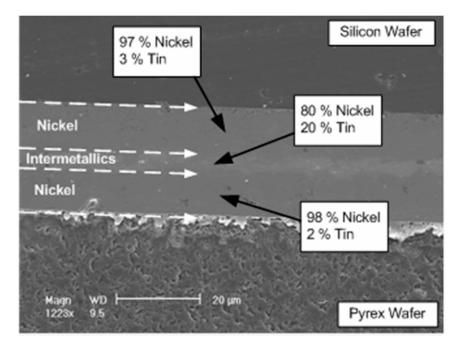

| C                | 50 μm wide nickel-tin TLP solder bond joint. The minimum thickness for TLP solder bond joint is more limited by the shear strength than th hermetic capabilites of the bond                                                     | e      |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

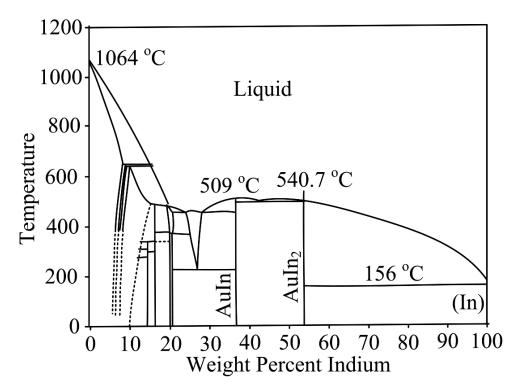

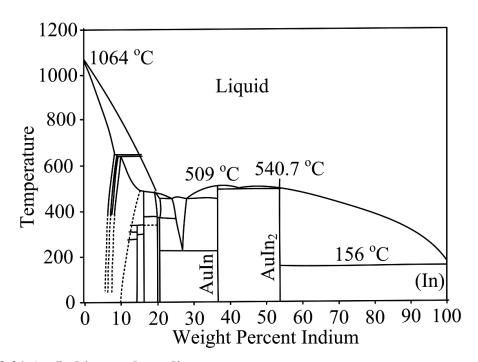

| -                | ne gold-indium binary phase diagram (Adapted from [70]). Au-In is th<br>lowest melting point phase left in the completed Au-In TLP solder bon<br>joints, giving this bond a theoretical re-melting temperature of over 50<br>°C | d<br>0 |

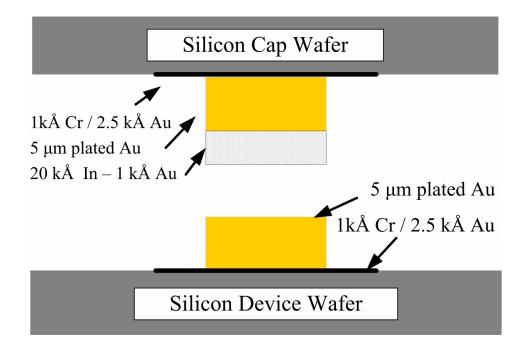

| C                | oss-section of the Au-In TLP solder bond directly before bonding. 1 kÅ o<br>gold is deposited in-situ on top of the indium interlayer so the process ca<br>be flux-free                                                         | n      |

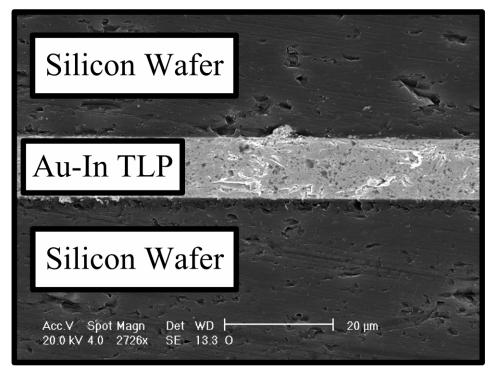

|                  | EM image of the cross-section of a Au-In TLP solder bond. The bond is formed with a maximum temperature of 200 °C.                                                                                                              |        |

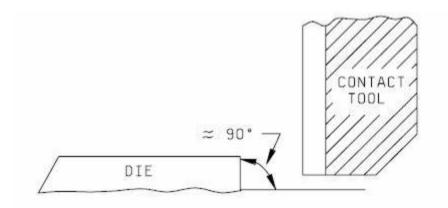

| -                | drawing of a partial shear test setup from MIL-SPEC-88F, Method 2019.7<br>[67]9                                                                                                                                                 |        |

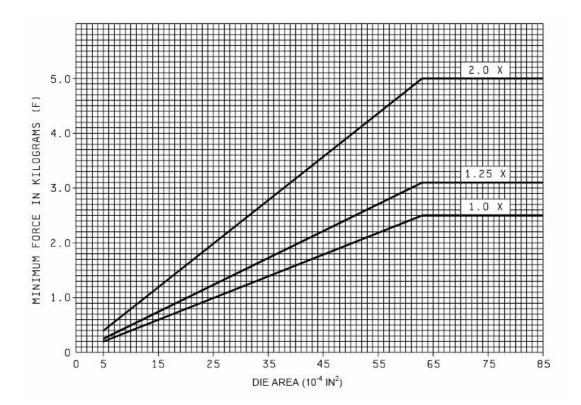

| -                | The shear strength failure criteria from MIL-STD 883 for three separat<br>cases. The most stringent (2.0 X) was used for qualifying the wafer bond<br>in this work [67]                                                         | ls     |

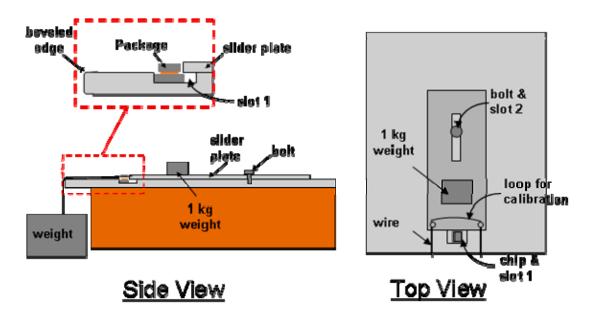

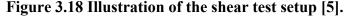

| Figure 3.18 Illu | ustration of the shear test setup [5]                                                                                                                                                                                           | 7      |

| -                | otograph of a package sitting in the shear test setup. The slot and slide plate apply the shear force perpendicular to the package cap edge                                                                                     |        |

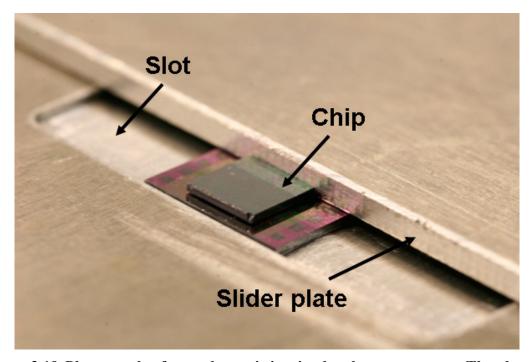

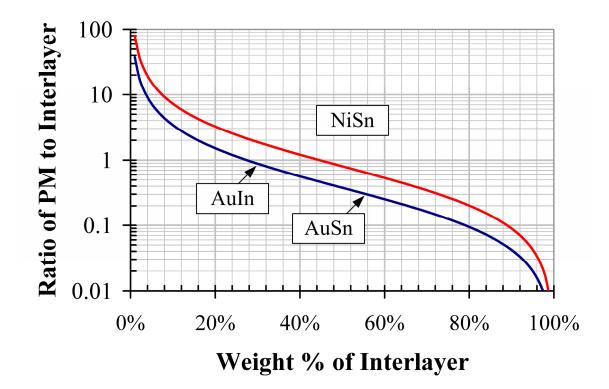

| C                | ot of the calculated critical interlayer thickness for the three TLP solde<br>material systems studied in this work. The heating rate used for thes<br>bonds was 60 °C/min                                                      | e      |

| Figure 3.21 Au   | -In binary phase diagram 10                                                                                                                                                                                                     | 8      |

| C                | ot of the ratio of parent metal thickness to interlayer thickness required t<br>produce a final microstructure that contains a certain weight percentage of<br>interlayer. 10                                                   | of     |

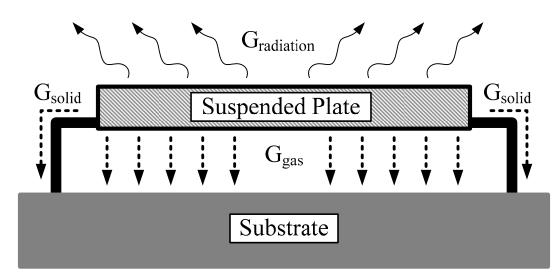

| -                | ustration of the thermal losses from a heated plate suspended over substrate                                                                                                                                                    |        |

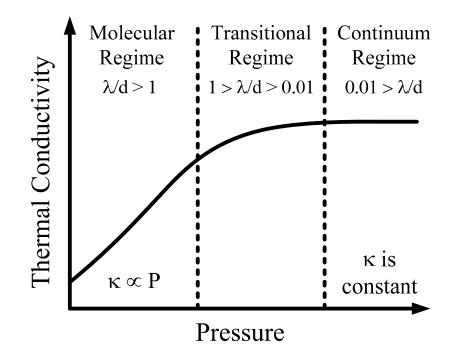

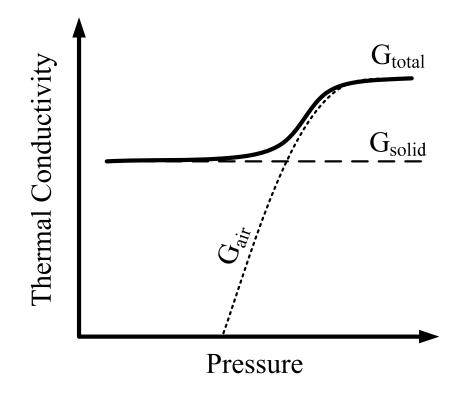

| Figure 4.2 Illus | stration of the pressure dependence of gaseous thermal conductivity11                                                                                                                                                           | 6      |

| Figure 4.3 Illus | stration of the total, gas, and air thermal conductivities versus pressure11                                                                                                                                                    | 7      |

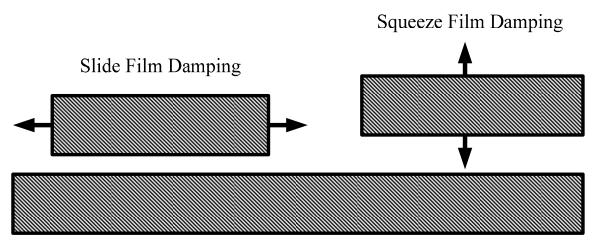

| Figure 4.4 Illus | stration of the two types of viscous fluid damping                                                                                                                                                                              | 0      |

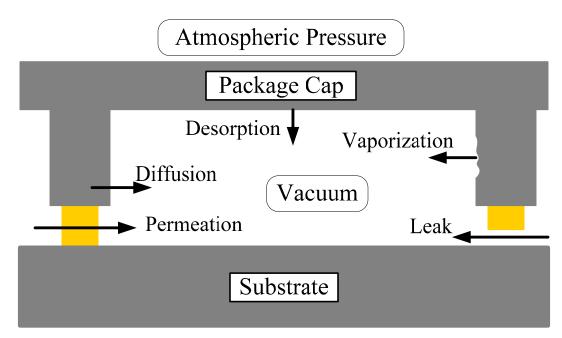

| Figure 4.5 Sou   | rces of gas inside a vacuum-sealed microcavity 12                                                                                                                                                                               | 5      |

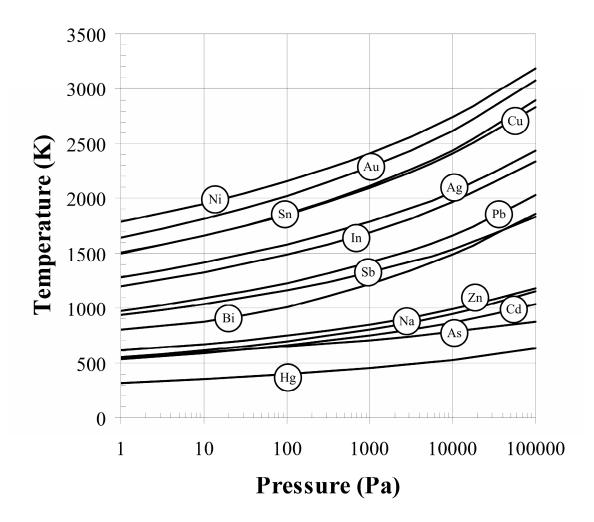

| Figure 4.6 Vapor pressures for several metals that might be used in MEMS packaging.<br>The most common metals must be heated very hot (> 1000 K) for their<br>vapor pressures to reach 1 Pa (7.5 mTorr) [81]                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

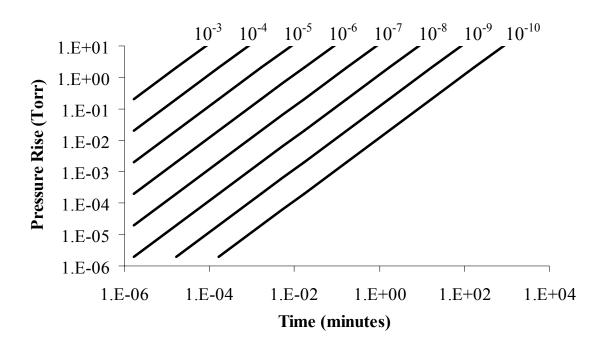

| Figure 4.7 Approximate pressure rise for a MEMS package with a volume of 2.5 µL for various leak rates labeled in torr liter/sec [95]                                                                                                                                                                |

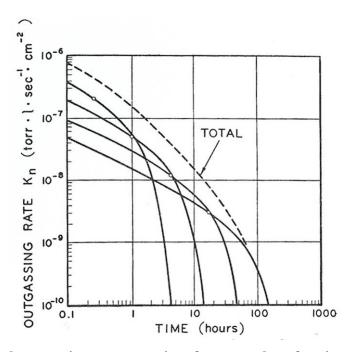

| Figure 4.8 Typical outgassing curve vs. time for a metal surface in a vacuum [96] 132                                                                                                                                                                                                                |

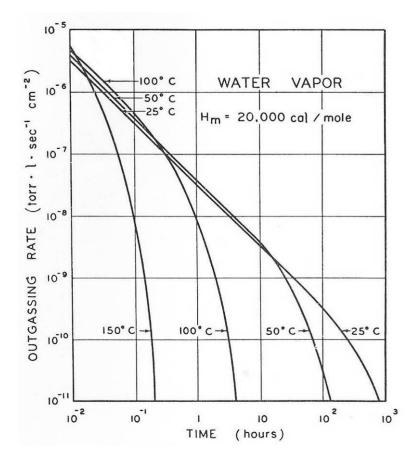

| Figure 4.9 Theoretical outgassing curves for water vapor at different temperatures [96].                                                                                                                                                                                                             |

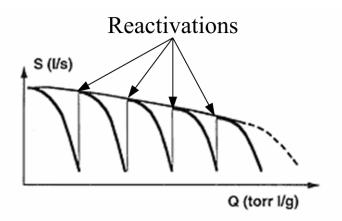

| Figure 4.10 Plot of pumping speed versus sorption capacity for a common thin-film NEG [81]                                                                                                                                                                                                           |

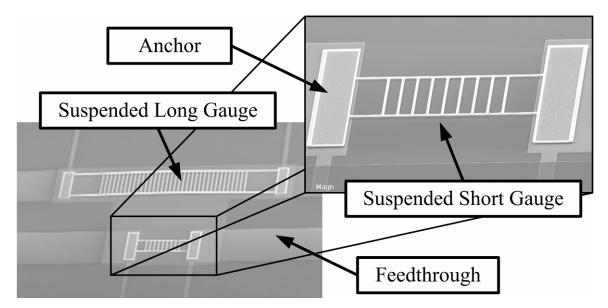

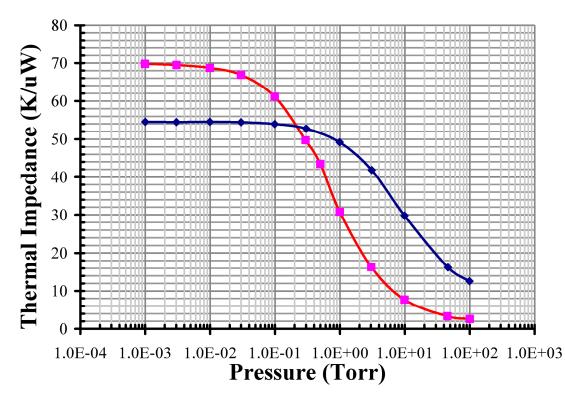

| Figure 4.11 SEM images of the short and long surface micromachined Pirani gauges [5].                                                                                                                                                                                                                |

| Figure 4.12 Characterization plot of the short and long Pirani gauge types. The short<br>gauge's maximum thermal impedance is 55 K/μW while the long gauge's<br>maximum is 70 K/μW.                                                                                                                  |

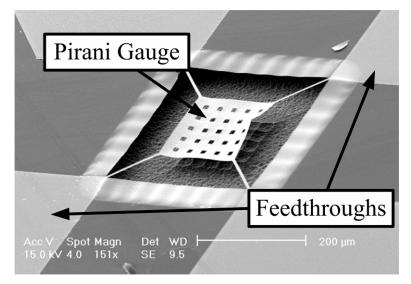

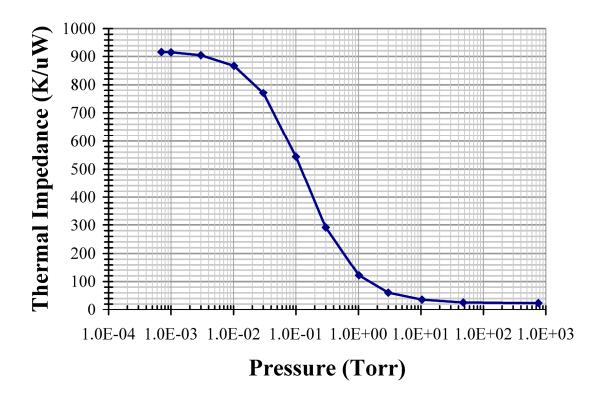

| Figure 4.13 SEM image of the platinum Pirani gauge                                                                                                                                                                                                                                                   |

| Figure 4.14 Platinum Pirani gauge characterization plot                                                                                                                                                                                                                                              |

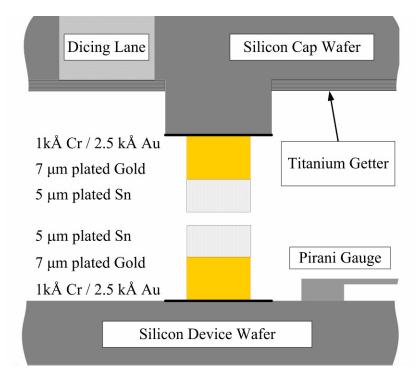

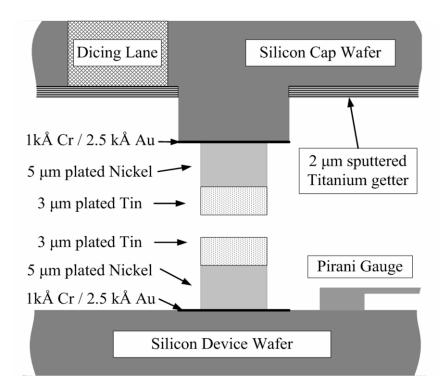

| Figure 4.15 Cross-section of the wafers directly before performing the Au-Sn standard solder bond                                                                                                                                                                                                    |

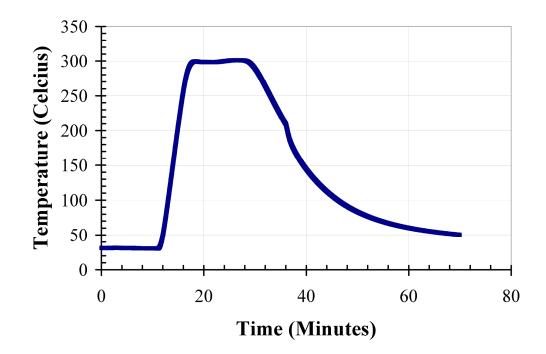

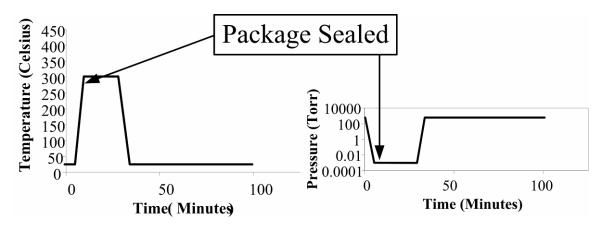

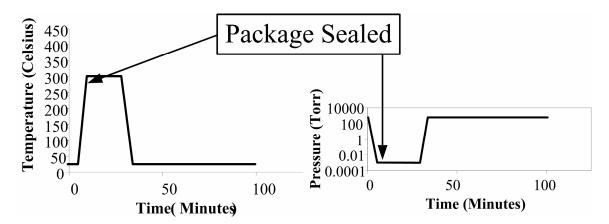

| Figure 4.16 Bond cycle temperature and pressure profiles for the Au-Sn standard solder bonded packages. The bond cycle requires approximately 30 minutes. 152                                                                                                                                        |

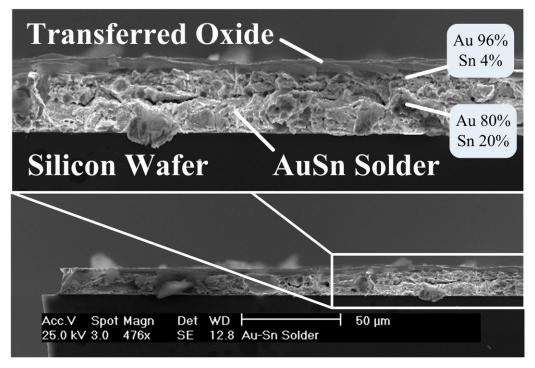

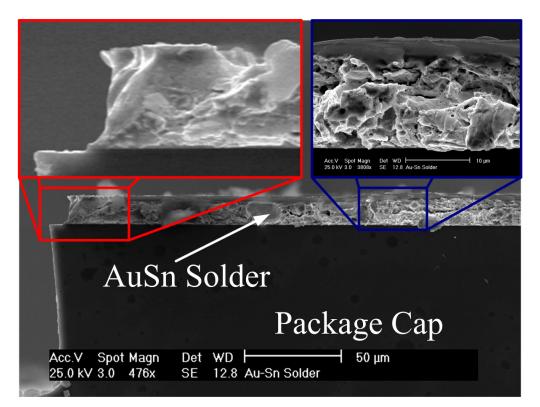

| Figure 4.17 SEM image of the Au-Sn bond from the package. The insets show magnified views of the Au-Sn solder layer                                                                                                                                                                                  |

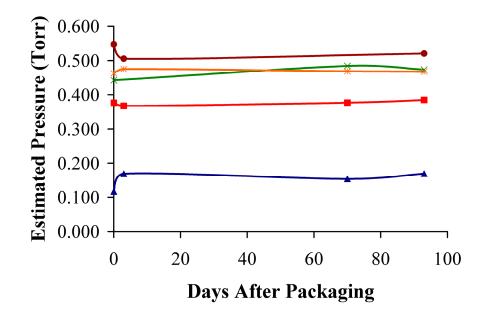

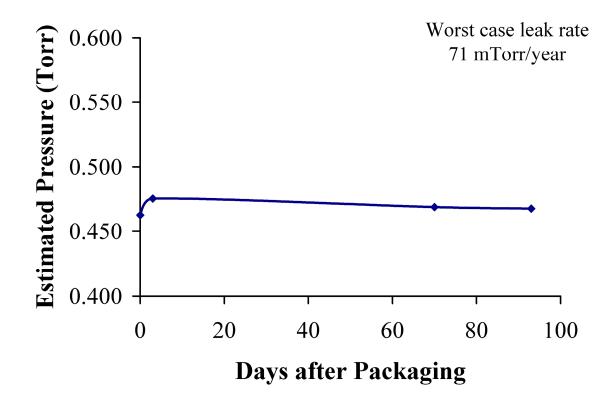

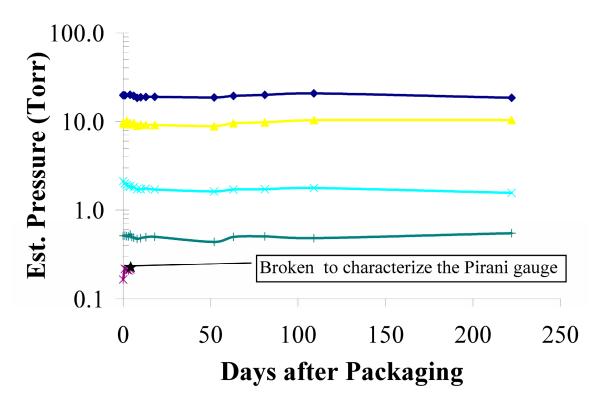

| Figure 4.18 Long-term vacuum data for the Au-Sn solder bond with fully activated getters. The pressures inside the packages varied from 600 mTorr to 200 mTorr and have remained stable over 90 days                                                                                                 |

| Figure 4.19 Magnified view of the pressure data for a package from the Au-Sn standard solder bonded wafer. The worst-case leak-rate that fits within the pressure measurement error for the Au-Sn Solder bonded packages is 71 mTorr/year (1.5 <sup>-10<sup>-15</sup></sup> atm cc s <sup>-1</sup> ) |

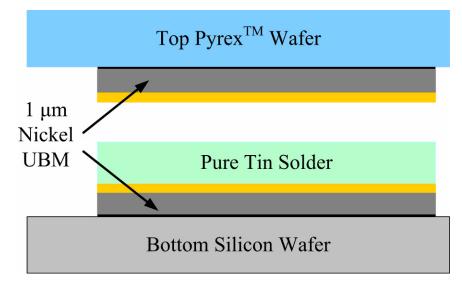

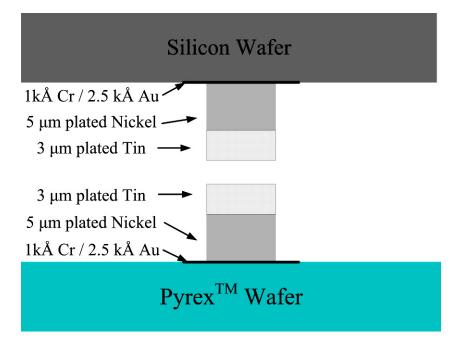

| Figure 4.20 Cross-section of the Ni-Sn TLP solder bonded wafers directly before the bond cycle                                                                                                                                                                                                       |

| Figure 4.21 Bond cycle for the Ni-Sn TLP solder bonded vacuum packages. The                                                                                                                                                                                                                          |

| packages are sealed at the beginning of the bond cycle                                                                                                                                                                                                                                                                       |

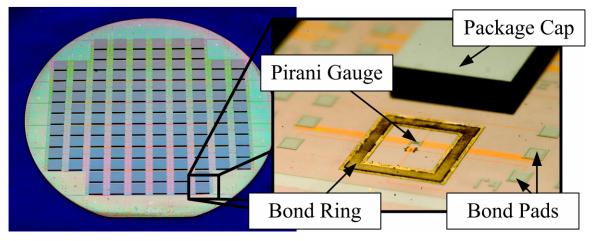

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

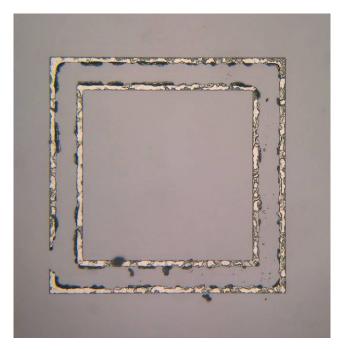

| Figure 4.22 Photo of Ni-Sn TLP solder bonded wafer. Inset shows a magnified view of a package cap, bond ring, and a polysilicon Pirani gauge                                                                                                                                                                                 |

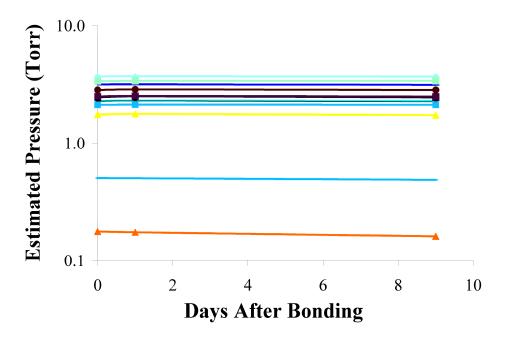

| Figure 4.23 Estimated long-term pressure data for the Ni-Sn TLP Solder bond. The pressures varied from 10s of Torr to 200 mTorr                                                                                                                                                                                              |

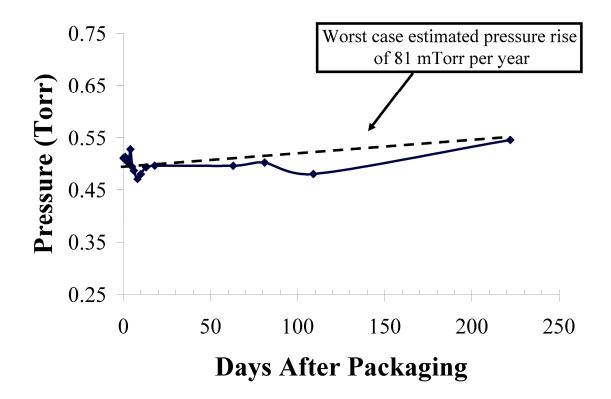

| Figure 4.24 Magnified view of the pressure of one die over time. The worst case leak rate for the Ni-Sn TLP solder bond was 81 mTorr/year (1.712 <sup>-10<sup>-15</sup></sup> cc atm s <sup>-1</sup> ).                                                                                                                      |

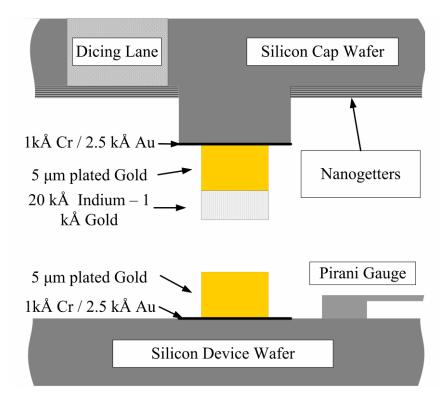

| Figure 4.25 Cross-section of the wafers directly before bonding                                                                                                                                                                                                                                                              |

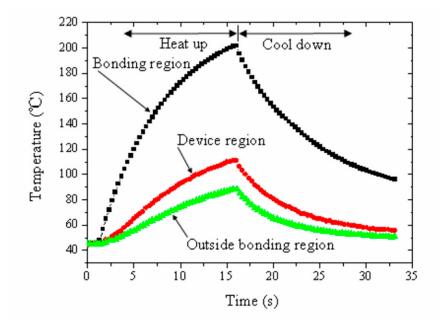

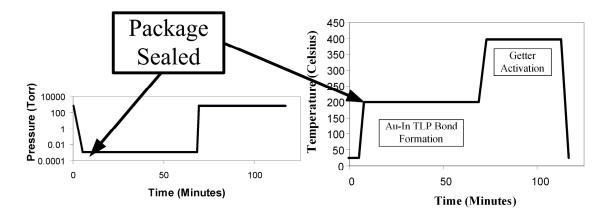

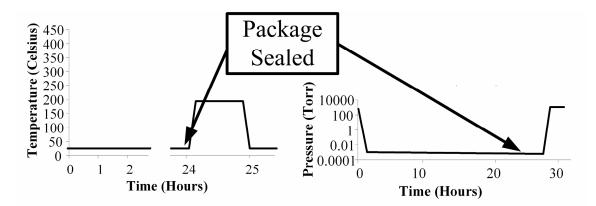

| Figure 4.26 Bond cycle for Au-In TLP solder. The package is sealed a few minutes into the vacuum cycle, therefore all the outgassing during the bond cycle is trapped inside the package                                                                                                                                     |

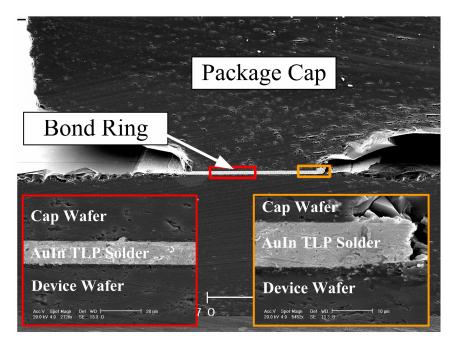

| Figure 4.27 SEM image of the Au-In TLP Solder bonded vacuum package 164                                                                                                                                                                                                                                                      |

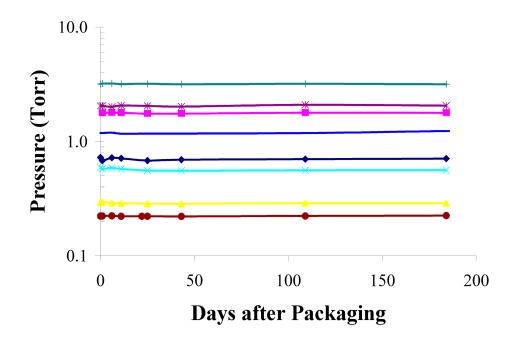

| Figure 4.28 Estimated long-term pressure data for the Au-In TLP solder bonded vacuum packages. The pressures ranged from several Torr to 200 mTorr after getter activation                                                                                                                                                   |

| Figure 4.29 Magnified view of a single die from the Au-In TLP solder bonded MEMS vacuum packages. The worst case leak rate that fits within the error of the pressure measurements is 16 mTorr/year (9.6 10 <sup>-17</sup> atm cc s <sup>-1</sup> )                                                                          |

| Figure 4.30 Modified Au-In TLP solder bond cycle. The package sits in a vacuum environment for 24 hours before the bond is performed. This results in a much lower pressure inside the packages due to the reduction in the outgassing rate                                                                                  |

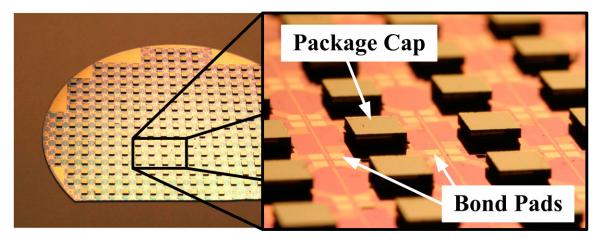

| Figure 4.31 Picture of the completed Au-In TLP solder bonded wafer with a magnified view inset                                                                                                                                                                                                                               |

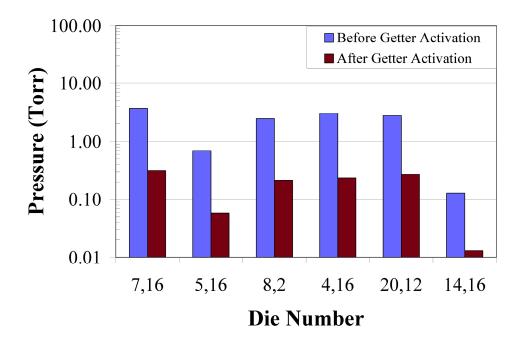

| Figure 4.32 Pressure data from the modified Au-In TLP solder bond sequence. The 24 hours at vacuum reduced the outgassing rate, such that the pressures before the titanium getters were activated are the same as the previous wafer after the getters had been activated                                                   |

| Figure 4.33 Pressures for various die from the modified Au-In TLP solder-bonded<br>packages before and after getter activation on a log scale plot. The<br>extended outgassing sequence at high vacuum for 24 hours before bonding<br>resulted in an internal pressure of less than 20 mTorr after getter activation.<br>170 |

| $\Gamma_{i} = 1.24  A stimution of the minimum setting setting and the Ni Co TLD solder hand. The methods are$                                                                                                                                                                                                               |

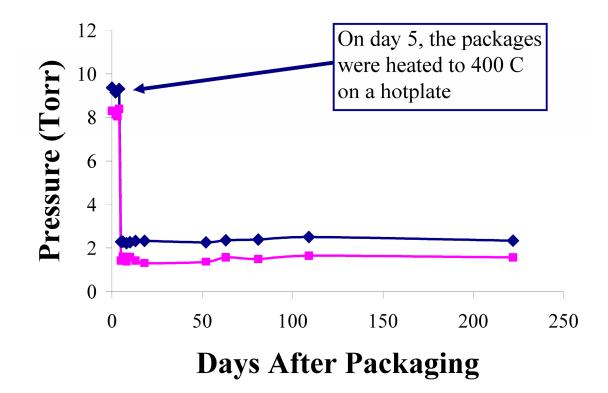

Figure 4.34 Activation of titanium getters with a Ni-Sn TLP solder bond. The packages

| were heated to 400 °C on day 5, which activated the getters and dropped the pressure by a factor of 5                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

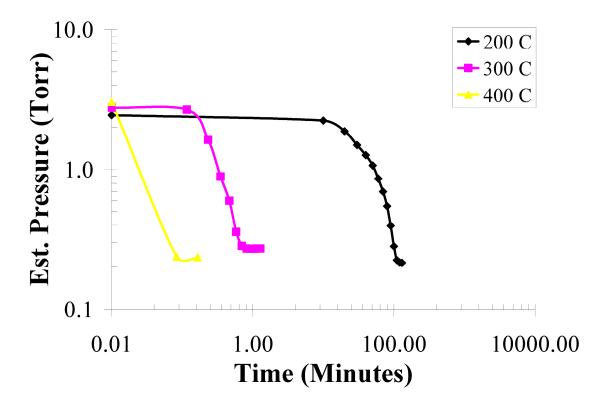

| Figure 4.35 Plot of pressure versus activation time for titanium getters. Titanium getters can be activated at temperatures as low as 200 °C, although the activation time increases substantially for lower temperature activation |

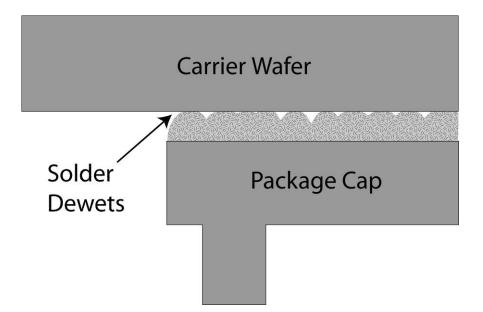

| Figure 5.1 Illustration of the solder transfer process. The solder consumes the seed laye it was electroplated on, and then dewets the carrier wafer                                                                                |

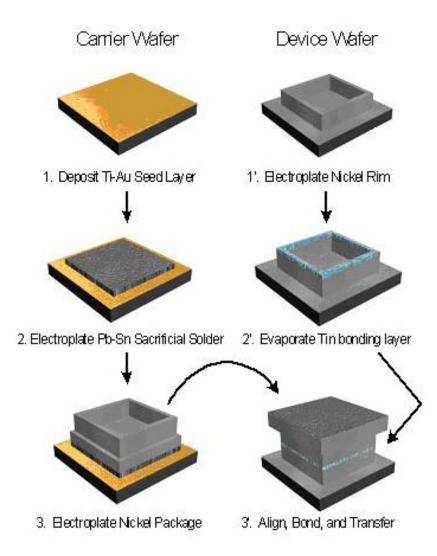

| Figure 5.2 Illustration of the process flow for transferred thin-film packaging with a nove solder transfer technique. 179                                                                                                          |

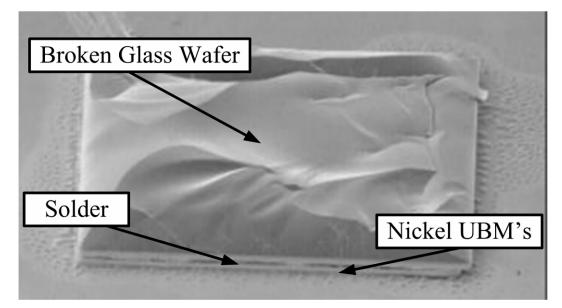

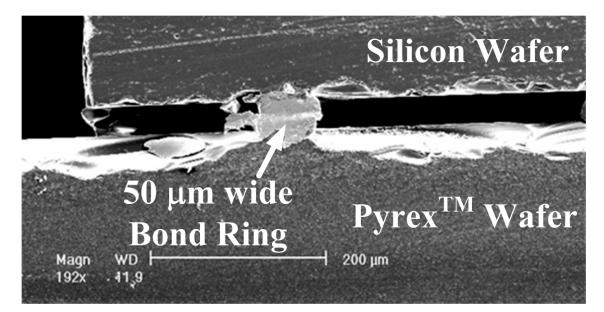

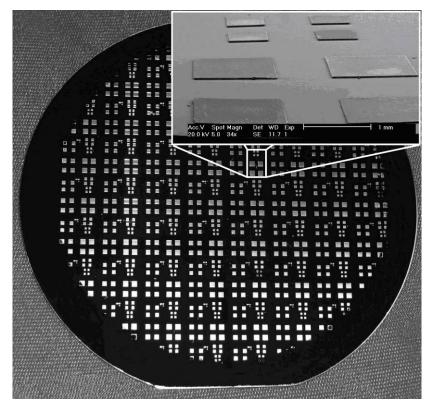

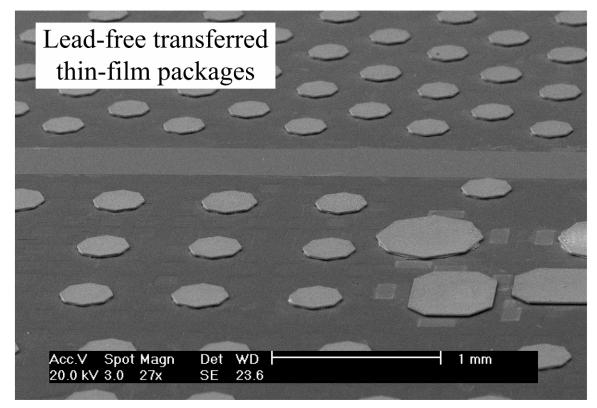

| Figure 5.3 Silicon substrate full of transferred thin-film packages                                                                                                                                                                 |

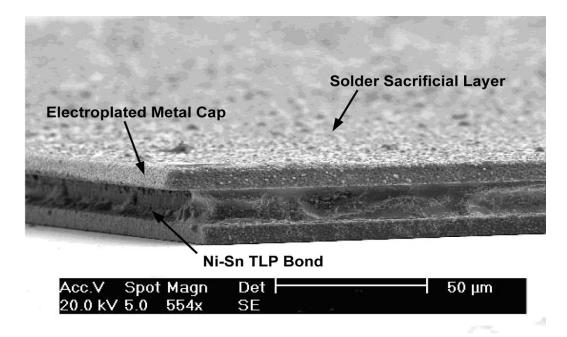

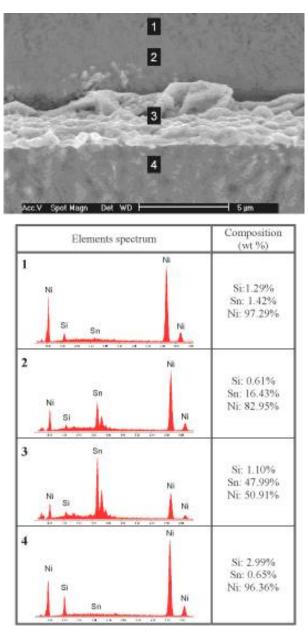

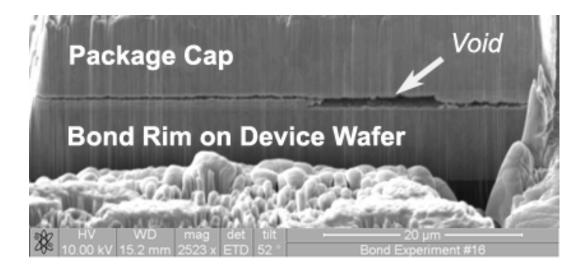

| Figure 5.4 SEM image of the profile of a transferred thin-film package                                                                                                                                                              |

| Figure 5.5 Magnified view of the Ni-Sn TLP bond and EDAX elemental analysis across the bond joint                                                                                                                                   |

| Figure 5.6 SEM image of lead-free transferred thin-film packages                                                                                                                                                                    |

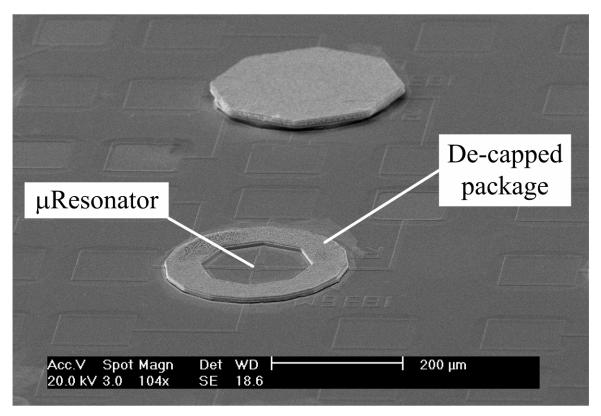

| Figure 5.7 Magnified view of a transferred thin-film package and a de-capped package showing a μ-disk resonator inside                                                                                                              |

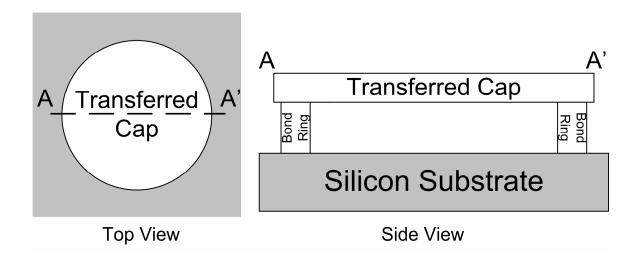

| Figure 5.8 Illustration of the top view and side view of a transferred cap                                                                                                                                                          |

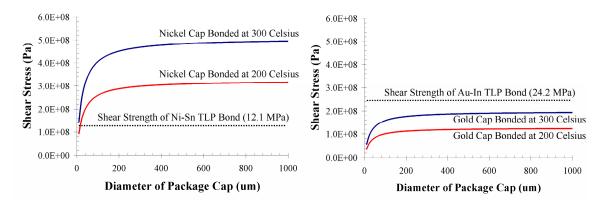

| Figure 5.9 Calculated shear stress from CTE mismatch for gold and nickel package caps that are 10 µm thick, with 50 µm bond rings. If the shear stress exceeds the bond strength, the package caps will fail                        |

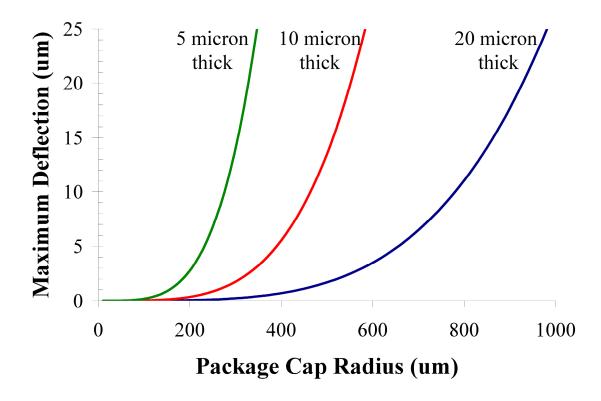

| Figure 5.10 The maximum deflection for 5, 10, and 20 µm thick gold transferred thin film caps                                                                                                                                       |

## List of Tables

| Table 1.1 IC and MEMS Packaging Hierarchy (adapted from [4]).    6                                                                                                                                                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 1.2 Comparison of three generic packaging approaches                                                                                                                                                                                                                                               |

| Table 1.3 Comparison of different wafer bonding techniques.    19                                                                                                                                                                                                                                        |

| Table 1.4 Several widely used low melting point solder alloys [20]                                                                                                                                                                                                                                       |

| Table 2.1 Summary of experimental results for standard solder bonds. Only the Au-Snsolder bond shows promise for MEMS wafer level vacuum packagingwith standard commercial wafer bonders.26                                                                                                              |

| Table 2.2 Comparison of various wafer bonding approaches across several metrics 27                                                                                                                                                                                                                       |

| Table 2.3 Data summary for the Gold-Tin solder bonding technique.    56                                                                                                                                                                                                                                  |

| Table 3.1 Overview of the material families investigated in this work and their results 62                                                                                                                                                                                                               |

| Table 3.2 The formation and melting temperatures of some TLP material systems (adapted from [20]).       64                                                                                                                                                                                              |

| Table 3.3 Intermetallic formation rates for selected materials systems when the interlayer is solid versus when it is liquid at similar temperatures.       76                                                                                                                                           |

| Table 3.4 Test results for Nickel-Tin TLP solder wafer bonding                                                                                                                                                                                                                                           |

| Table 3.5 Test results for Gold-Indium TLP solder wafer bonding.    93                                                                                                                                                                                                                                   |

| Table 3.6 Leak rates for the wafer bonding techniques presented in this chapter. Details of<br>the measurement technique are presented in Chapter 4                                                                                                                                                      |

| Table 3.7 Summary and comparison of the shear strength data from all tested wafer bonding techniques.    100                                                                                                                                                                                             |

| Table 3.8 Material constants used to calculate the critical interlayer thicknesses for the<br>TLP solder material systems. The order of the reference numbers in the<br>final column corresponds to the material family column (i.e. the first<br>reference is for Au-Sn, second is for Ni-Sn, etc.).106 |

Table 3.9 Effective growth rate constants calculated by numerical approximation of the

| integral in Equation (3.18) with MATLAB <sup>TM</sup>                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 4.1 Summary of the wafer bonding MEMS vacuum package data.       113                                                                                         |

| Table 4.2 Real leak rates for different sized leak paths (Adapted from [95]) 127                                                                                   |

| Table 4.3 Overview of selected wafer bonded MEMS vacuum packages. *The Al-Si to glass bonding was achieved with a localized heating bonding technique.         139 |

| Table 4.4 Summary of the MEMS vacuum packaging experiment results                                                                                                  |

| Table 4.5 Pressure measurements and statistical analysis based on Student's T-distribution for the long polysilicon Pirani gauge.       146                        |

| Table 4.6 Characterization data for the thin-film platinum gauge. Three measurements were taken at each pressure.       149                                        |

| Table 4.7 Summary of package testing data for the Au-Sn standard solder bond 155                                                                                   |

| Table 4.8 Summary of data from the tests on Ni-Sn TLP solder bonded packages 160                                                                                   |

| Table 4.9 Summary of data from the tests on Au-In TLP solder bonded packages 166                                                                                   |

| Table 6.1 Shear strength raw data for the Nickel-Tin TLP solder bonded wafer                                                                                       |

| Table 6.2 Shear strength raw data for the Gold-Indium TLP solder bonded wafer 196                                                                                  |

| Table 6.3 Shear strength raw data for the Gold-Tin solder bonded wafer.       197                                                                                  |

# Chapter 1 INTRODUCTION

Micro-Electro-Mechanical Systems (MEMS) research started in the 1960s with a resonant gate transistor [1]. Researchers used a suspended bridge to modulate the current flowing through a transistor gate. Being the first to combine a moving mechanical structure with electronic components on the microscale, they broke ground in what was to become a fertile field of research.

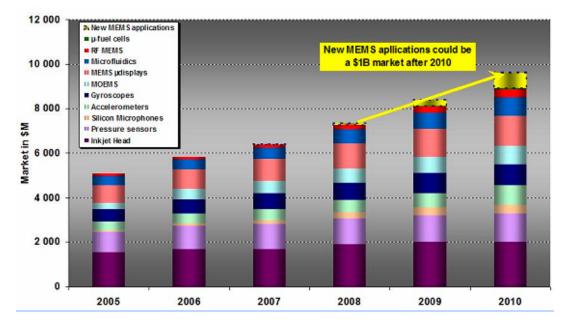

MEMS are a system of mechanical, electrical, and other components that interact with physical and chemical aspects of the outside world and interface with integrated circuits (IC). Almost 50 years after the resonant gate transistor, MEMS have found their way into a variety of products spanning markets from national defense to automotive to consumer electronics. Figure 1.1 shows that the MEMS market is currently worth more than \$6 Billion and projected to double in the next 5 years.

Figure 1.1: MEMS historical and projected sales by market segment [2].

Packaging is a critical component of the continued commercial success of MEMS devices. However, MEMS packaging is not a standardized process. Unlike ICs, which use very similar materials and contain no moving parts, MEMS devices rarely use the same materials and often have moving parts. This complexity results in specific custom packaging solutions that are only compatible with a certain process. With further research into MEMS packaging there is an opportunity to invent new packaging processes that are compatible with a wide range of devices and standardize MEMS packaging.

To that end, this research has explored the use of solder as a means of advancing the state of the art in MEMS wafer-level packaging (WLP). Figure 1.2 illustrates an overview of this work. Three processing technologies were developed: standard solder bonding, transient liquid phase (TLP) solder bonding, and a novel solder transfer technique. These process technologies were used to create two packaging systems: a wafer bonded vacuum package and transferred thin-film package.

Solder has several attributes, such as its planarization capabilities, low permeability, and low processing temperature, which make it an attractive material for MEMS vacuum WLP. In this work, solder was used to develop two processes. The first is a wafer bonding process that uses solder as an attachment and sealing method. The second uses

solder as a method for transferring structures from one wafer to another. These two processes were used to create wafer level approaches for MEMS vacuum packaging.

The major contributions of this thesis are:

- A Au-Sn standard solder wafer bonding process technology compatible with commercial wafer bonding systems.

- Advanced solder bonding process technologies, transient liquid phase (TLP) solder bonding, based on Ni-Sn, Au-Sn, and Au-In material systems.

- Detailed characterization and understanding of standard solder bonding and TLP solder bonding that are presented as a set of design rules.

- Wafer-level MEMS vacuum packages created with standard and TLP solder bonding that have internal pressures lower than 20 mTorr and 10 months of vacuum data.

- Characterization of titanium thin-film getters at low activation temperatures.

- A novel solder-transfer technique that enables a transferred thin-film package technique with potential as a low-profile modular MEMS wafer-level vacuum package.

These results achieve three firsts for MEMS packaging:

- The lowest maximum temperature (200 °C) MEMS wafer bonded vacuum packaging process with integrated getters reported.

- The first application of TLP solder bonding to MEMS vacuum packaging.

- The first use of solder de-wetting as a transfer technique for MEMS structures.

The rest of this chapter provides a brief introduction to MEMS packaging process, typical packaging requirements, and three general packaging approaches. Then, several reasons for using solder in a vacuum packaging process. To close the chapter, the organization of the thesis is outlined.

### **1.1 MEMS Packaging**

Micro-Electro-Mechanical Systems (MEMS) are the integration of mechanical structures and electronics on the  $\mu$ -scale through  $\mu$ -fabrication technology. With the addition of mechanical components to the electronics, the complexity of the system has increased exponentially because it has entered the multi-physical domain. The complexity of MEMS packaging has grown correspondingly to meet the new demands of the MEMS devices. A MEMS package serves four functions listed below:

- 1. Protect the device from the external environment

- 2. Provide the internal environment necessary for reliable operation

- 3. Allow it access to the information it needs to collect

- 4. Interface it with the other components

Figure 1.3 is an illustration of areas critical to MEMS packaging that highlights packaging of integrated circuitry, micromachined devices, and electrical and fluidic interconnects. The hermetic coatings and hermetic/vacuum-sealed cavity provide the necessary protection for the circuits and micromachined devices. The cavity also goes one step further: it not only protects the micromachined device from the outside environment, but also provides the necessary internal environment (in this case a vacuum) for reliable device operation. The integrated sensor outside the hermetic/vacuum-sealed cavity with the hermetic coating presents another common packaging challenge. It needs access to the outside environment as well as protection from it. A special hermetic coating over the sensor is needed to allow access to what it needs to measure while still protecting it from any contaminants in that environment. Finally, the electrical and microfluidic connects interface the system to the outside world.

Figure 1.3 Illustration of a generic MEMS device [3].

This level of complexity, integrated electronics and several micromachined devices with feedthroughs is typical for MEMS. The package process design must balance the differing package requirements from each sub-part of the overall system to arrive at the optimal design. It is imperative that this design be considered from the beginning in order to ensure all the packaging requirements are met while maintaining process compatibility. Inevitably, some tradeoffs are necessary to satisfy all of the requirements. However, some flexibility is afforded the packaging engineer because not all the packages are created in a single step; packaging is a process with several steps and a hierarchy.

### **1.1.1 Packaging Process**

The inherent complexity in MEMS packaging presented in the previous section can be simplified by breaking the packaging process down into distinct steps. Table 1.1 shows the packaging hierarchy for ICs with an added column describing a MEMS analogy. By splitting the packaging requirements into different hierarchical levels, the packaging engineer can limit the compromises that must be made to integrate the packaging and device process flows.

| Level   | III KIAMANE – NIKNIN ANGIAAV                    |                                                                                                     | Packaged /<br>Interconnected by                                                     |

|---------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| Level 0 | Single transistor<br>within an IC               | Single valve in a MEMS                                                                              | IC metallization, wafer-<br>level protection, thin-films                            |

| Level 1 | Complete IC                                     | microGas<br>Chromatography (μGC)<br>separation column with<br>integrated valves on the<br>same chip | Wafer bonded,<br>conventional lead frame<br>packages, multi-chip<br>module packages |

| Level 2 | Single- and<br>multi-chip<br>packages           | μGC column/valve chip<br>integrated with chemical<br>sensor chip                                    | Printed wiring boards,<br>microfluidic substrates,<br>WIMS Cube                     |

| Level 3 | Printed wiring<br>boards                        | Printed wiring boards (busses), mach                                                                | Connectors/backplanes<br>(busses), machined chassis<br>or box                       |

| Level 4 | Chassis or box                                  | Chassis or box                                                                                      | Connectors/ cable harnesses                                                         |

| Level 5 | System itself (a<br>computer or a<br>gas alarm) | Complete handheld µGC system                                                                        | Connectors/ cable<br>harnesses                                                      |

Table 1.1 IC and MEMS Packaging Hierarchy (adapted from [4]).

The first three packaging steps are where most of the differences lie. This is because after Level 2, ICs and MEMS are almost indistinguishable black boxes of packaged chips with interconnections. Current MEMS packaging research is focused on the first three levels of the packaging hierarchy because it is in these first critical levels that the four MEMS packaging functions are achieved.

As mentioned previously, the first MEMS packages were made from off-the-shelf IC packages to save cost and time. Over time, as IC packages improved, MEMS packages also improved as they adopted the latest and greatest IC packaging developments (See Figure 1.4).

Figure 1.4 History of the evolution of IC packaging techniques [3].

The IC package developments were driven by cost savings through greater parallel processing as well as improved performance through higher input/output counts and better thermal performance. Over the years, these improvements had an impact on IC cost and performance; however, little of that impact translated to similar improvements for MEMS due to the added complexity of MEMS packaging. The greatest improvement for MEMS packaging came with wafer-level packaging (WLP). The shift of the early packaging steps (Levels 0 and 1), from individual die to when the wafer is still whole, has enormous benefits by reducing cost and size and increasing the performance of MEMS devices. This is evident when a process where singulation is performed before these early packaging steps is compared to a process where they are performed at the wafer level.

Figure 1.5 A singulation first package process [5].

Figure 1.5 illustrates a process where the dicing step precedes the release step. Right after the MEMS fabrication steps are complete, the wafer is sawed into individual die. After dicing, the individual dies are released. The release step must be performed after dicing or the water from the dicing saw would ruin any released MEMS device. Since release steps typically require long etches in a vaporized acid or an acid bath, the individual die can be released at the same time with special multi-die handling equipment. All the subsequent steps, however, are serial because only one die can be handled at a time. Performing these steps individually for each die increases the cost of MEMS packaging. Parallel processing is one of the greatest strengths of IC processing. With so many MEMS parts fabricated simultaneously, each expensive process step is divided by a large number to calculate the cost for an individual die, which brings the die cost down to a sustainable level. This advantage and cost savings is lost once the wafer is sawed into individual die because all the subsequent processing steps must be individually performed on each die. Another disadvantage of this processing technique is the large package size. The individual dies are usually placed in a package such as a metal can or a dual in-line package (DIP) (See Figure 1.4), which precludes their use in next generation cell phones and other handheld devices. For a release-first packaging process, the dicing step is delayed until much later in the process after each of the first two packaging levels

has been completed. This delay produces a big cost savings and reduction in package size.

The release-first package process starts after the MEMS fabrication is completed, but instead of dicing the wafer next, all of the devices are released simultaneously while the wafer is still whole (See Figure 1.6).

Figure 1.6 A release-first packaging process [5].

The released devices are then protected using a WLP technique such as wafer bonding or thin-film encapsulation. Next, the wafer can be singulated without concern for the fragile released MEMS devices; the encapsulation provided by the WLP technique protects them from the harsh environment during dicing. After dicing, the chips are mounted on a board similar to the chip-level packages. By using a release first packaging process, more of the packaging steps occur in parallel to all of the dies at once, instead of one by one as in a singulation first package process.

The cost and size advantages of the release-first process are balanced by the technical challenges of integrating a WLP technique with MEMS processes. There is great amount of research into wafer-level packaging techniques that can be integrated with MEMS processes and serve the four functions of MEMS packages.

### **1.1.2 Package Design Considerations**

All of the different requirements, from process integration issues to final package specifications need to be addressed from the beginning of the packaging process. If the whole picture is not in view from the beginning, a problem could arise late that could require rethinking of the entire packaging approach. It is important that the packaging engineer be mindful of all of the issues that could arise during the process so they can be addressed with a packaging plan from the beginning.

#### **PACKAGE SPECIFICATION REQUIREMENTS**

#### Interconnections

One of the 4 main functions of MEMS packaging presented earlier was to interface the device with the outside world; interconnect or feedthrough are the generic terms applied these objects. Interconnects provide a path for charge or fluids to move from one place to another. With electrons, interconnects are usually made of metals or highly doped semiconductors that provide a conductive path into the package. The best materials for creating electrical interconnects are those with low resistivity. Metals such as aluminum or gold are widely used because they are excellent conductors.

Aside from electrons, fluids, such as gases in  $\mu$ GCs or liquids in DNA analysis chips, must also be transported from one region to another. Microfluidic interconnects provide the path for these fluids to move from one part of the system to another. These interconnects create a challenge not present in electrical interconnects because the fluids flowing down the interconnect are so varied. The materials for these interconnects should be chosen carefully to prevent any interaction between the interconnect walls and the fluid they are transporting. Another big issue with microfluidic interconnects is leakage, therefore, the quality of this seal is very important. There is plenty of research into different materials for microfluidic interconnects and creating leak-free seals. Be they electrical or fluidic, there are two major schemes for creating interconnects: the interconnects can be created laterally into the package by putting the interconnect on the surface of the wafer or, alternatively, they can be created through the bulk of the chip in a vertical manner. Vertical or lateral, electrical or fluidic, interconnects provide communication between the packaged devices and the outside world. The required performance and process integration issues need to be considered by the engineer during the package design process.

#### Internal Environment

Another of the four functions of MEMS packages is to provide the internal environment necessary for the device to operate reliably. This requirement varies from device to device. It can be as simple as keeping the internal environment the same as the external environment or as difficult as creating a high vacuum inside the package cavity.

The most common requirement of the internal environment is to keep it moisture-free. Water vapor causes many reliability problems for MEMS and electronics components. Many MEMS devices cannot tolerate any water vapor at all and those that can need a constant level of water vapor to limit drift. To achieve this, the internal environment of the package must be isolated from the external environment with a hermetic seal. An effective hermetic seal will prevent the varying water vapor concentrations in the outside environment from making it inside the package and causing problems with the devices inside. A hermetic seal is also required to create a vacuum environment inside the package and raising the pressure inside. Creating a vacuum package is much more difficult that just creating a moisture-free environment. The challenges mainly lie in removing all the outgassing that occurs off of packaging materials during package formation. Vacuum packaging, its motivation, and its challenges are covered in great detail in Chapter 4 since they are such a large part of this dissertation.

The internal environment is an important consideration in the package design process. Most devices need a dry, inert environment to operate with long-term reliability and some even need a more stringent vacuum environment, but both these devices need a hermetic seal to preserve their necessary environments.

#### Size

Market demands are driving consumer devices smaller and thinner while still offering the same features. The package size is critical if MEMS are going to be deployed in these applications.

There are two main aspects of the size issue that need to be addressed when developing a packaging process: area and profile. The area of the package is the extra area needed outside of the MEMS device it takes to provide the four functions of a MEMS package. This could be due to die space reserved for bond rings if the package is created using wafer bonding, or, it could be needed to accommodate the bond pads necessary on a thin-film packaging approach. A disadvantage of extra area is cost. In wafer-level packaging, if you need to reserve die space to place the bond rings for a wafer bonded package, that space costs money. If you can reduce the space necessary for the bond rings by reducing the size of the bond rings, the overall die size becomes smaller so you can fit more die on each wafer. There is much research into wafer-level packaging techniques that reduce the size reserved for bond rings or use a thin-film approach, which does not need a bond rings at all and further reduces the added area from the package.

Another major aspect of the package size is its height. At Level 0 or Level 1 in the packaging process, there are still many packaging steps left that need to be able to fit around any packaging steps performed at these first levels. If the package used for Level 0 or Level 1 is very thick or tall, then the subsequent packaging steps must accommodate this thickness by being even thicker. If the package used for Level 0 and Level 1 can be fabricated with a low-profile technique, it keeps more packaging options open for the later steps while still keeping the overall package size thin.

Size, in terms of added area and profile, is an important aspect of package design. It can affect the cost of the packaged devices by using up precious die area or complicate subsequent package steps by creating extra thickness. Pushing the limits to scale packages smaller and smaller such that they barely add any size to a MEMS device is a major goal of packaging research.

#### **External Environment**

The environment that the package must sit in will drive many of the choices in the packaging process plan. There are many different environments, each with special requirements that necessitate different packaging approaches.

MEMS have many interesting application opportunities inside the human body. There have already been devices that can measure a single neuron firing, devices that monitor blood pressure inside an artery stent, and devices that monitor ocular pressure are under development [6]. The human body is a unique environment that necessitates careful package design [3]. The materials used to fabricate this type of package must be able to withstand the chemicals present inside the body. Long soak tests have shown that saline in the body can dissolve common MEMS materials, such as polysilicon [7]. Not only must the packages survive the harsh environment inside the body without failing, they also must avoid causing any harm to the body. There has been a large research effort to determine what materials are bio-compatible, such that they can be implanted without any adverse effects to the host.

Other environments are not as sensitive to the packages themselves, they cannot be harmed by them; however, they are much more harsh than a hot saline bath to the packages. Oil and gas exploration as well as automotive applications are two such environments. The package materials must be able to survive this harsh environment, as well as protect the sensors and electronics. Other applications in automotive, such as pressure and temperature sensors deployed inside an engine cylinder, can create similar temperatures and pressures as well as harsh chemical byproducts. Research into silicon carbide and other harsh packaging approaches is trying to address these issues [8].

#### Access to the Measurand

For a MEMS device to operate properly, it must have access to what it is supposed to measure. Sometimes, as in the case of RF or other electrical signals, the signals can be brought in with a feedthrough which shifts the packaging challenges to creating the interconnect. In other cases, as in a MEMS microphone, the sensor must have access to

the pressure levels outside the package, which can greatly complicate the package design.

Microphones need to be able to measure high frequency pressure components from the atmosphere and convert them into electrical signals. To do this, the microphone needs to be exposed to the atmosphere to measure the pressure signals. The issue is that elements of the atmosphere where microphones are typically deployed can be harsh and change often. There are contaminants, such as particles, water vapor, and harsh chemicals, which can lead to reliability issues for these microphones. Also, the atmospheric pressure changes constantly: absolute barometric pressure changes with the weather as well as the humidity. Both of these changes can cause drift or reliability problems if the package is designed improperly. If they are included in the packaging plan from the beginning, however, there are several packaging techniques that can solve or alleviate these problems.

#### Cost

As mentioned previously, packaging costs make up a significant fraction of the overall MEMS device cost. This is because a new MEMS package needs to be developed for almost every new device. This fraction has come down in recent years as some packaging processes become standard; however, there are still aspects of the MEMS packaging process that should be considered to keep packaging costs low.

Wafer-level packaging is the key to keeping packaging costs low. By splitting the large costs of MEMS fabrication among many die, the individual die costs remain low. Serial processes, such as wire-bonding, metal can packages, and others that occur at the die level, will increase the packaging costs significantly.

Another aspect of the cost issue lies in the die yield from the wafer. The yield can be defined as the number of die that pass a performance metric, known as good die, divided by the total number of die on the wafer. Yield loss causes cost increases in two ways: 1) if it is a failed die, you cannot sell it 2) if the yield is not 100% you must test every die to find the failed ones or risk shipping poor quality parts that need to be returned. For high volume applications, it is more cost-effective to forego testing each device and cope with

the issues surrounding shipping bad parts. To keep the costs associated with this tactic to a minimum, yield losses must be reduced to the order of parts per million.

#### **Process Integration**

MEMS device and package processing is based on CMOS processes developed by the IC industry. However, MEMS uses many materials not found in IC fabrication. There is very little set order to the steps, and there are moving structures present in the finished chips. All these factors add up to create many challenges in combining a MEMS packaging process flow with a MEMS device process flow. Two major challenges, thermal budget and release compatibility, are covered below.

Since there are many non-CMOS materials used, such as metals, there is a large constraint put on the temperatures that can be used for fabrication. Metals such as gold and aluminum react with silicon to form a eutectic combination at relatively low temperatures below 400°C. Even before reaching the eutectic temperature, solid-state diffusion between common CMOS materials and metals can cause unwanted electrical effects, such as shorts and opens that would destroy a circuit. Aside from metal-semiconductor interaction, exotic materials such as low-k dielectrics and polymers are also reducing the maximum temperature CMOS circuits can survive. Depending on the polymer used, the maximum temperature for a CMOS die will be reduced to 320 °C or possibly even lower [9].

The mechanical structures used in MEMS need to be released before they can work properly. This step usually involves a long wet-acid etch or dry etch to dissolve away a sacrificial layer that frees the mechanical layers. Typically the processing steps after the release step are limited because the released mechanical structures cannot tolerate any wet process steps due to stiction effects. Combining this release step with the package materials can be a challenge since many of the materials that are used for packaging are not compatible with long wet-acid etches. Either the packaging materials need to be able to withstand the long release in acid or they have to be added after the release step.

#### **PACKAGING APPROACHES**

The wide range of different devices and their packaging needs makes it impossible to standardize the MEMS packaging process. However, a majority of packaging processes can be classified as one of three general approaches: integrated thin-film sealing, wafer bonding, and transferred thin-film. Table 1.2 compares the relative merits of the three generic approaches across several different metrics.

| Metric                       | Thin-Film<br>Sealing | Wafer Bonding | Transferred-<br>Thin Film |

|------------------------------|----------------------|---------------|---------------------------|

| Process Integration          | Difficult            | Flexible      | Flexible                  |

| Package Size                 | Small                | Large         | Small                     |

| Cost                         | Low                  | High          | Low                       |

| Die Area Used                | Low                  | Large         | Medium                    |

| Further Packaging Complexity | Minimized            | Low to High   | Minimized                 |

Table 1.2 Comparison of three generic packaging approaches.

#### Integrated Thin-Film Sealing

The integrated, thin-film sealing packaging approach uses a thin film of material that is deposited over the device to encapsulate it. However, it is challenging to achieve this for a MEMS device because there needs to be a cavity for the MEMS device to operate in. This is accomplished with thin-film packaging by depositing a sacrificial material before the thin-film package is deposited. Figure 1.7 illustrates a typical process flow. After depositing and patterning the thin-film package layer, the sacrificial material can be removed through a hole in the thin-film package. This hole is then plugged using another thin-film deposition step. There have been many demonstrations of thin film packaging techniques over the years that have found unique ways to create packages with several different thin-film materials deposited with different methods [10].

Figure 1.7 Generic process for integrated thin-film packaging.

Thin-film packaging has many features that make it an attractive choice for Level 0 packaging of MEMS. Recall from Table 1.1 that the Level 0 packaging is the step that packages individual devices. Individual MEMS devices can be very small, as small as tens of µms on a side. Thin-film packaging is appropriate for this size because it does not add much extra area for bond rings. A thin-film package requires only a ring approximately 10 µm wide surrounding the device to package it [10]; this is a substantial savings compared to a typical wafer bond ring size of several hundred. Thin-film packaging also maintains a low profile after completion. The thin film is typically 20-40 µm thick [11]; compare this to a wafer-bonded package, which has a 5-10 µm tall bond ring plus several hundred µms of wafer on top of it, making the package orders of magnitude taller. The low profile of thin-film packages enables much simpler integration of the packaged devices into total systems with subsequent packaging steps.

Thin-film packaging suffers from some disadvantages; most notably, it is a very process-specific packaging solution. The deposition of the thin film is typically a high temperature process that can only be integrated with certain process flows. The rest of the process needs to be adapted to the packaging step instead of adapting the packaging step to the process flow. This limits its use in many MEMS packaging solutions. For instance, CMOS circuits cannot be present on the wafers for the thin-film packaging achieved at higher temperatures because the elevated temperature causes the dopants to diffuse into

unwanted areas in the circuits. Even low-temperature, thin-film packaging processes suffer from process incompatibilities. Getters that are typically used in vacuum packaging are difficult to integrate into thin-film package processes because they need to be deposited on the package ceiling. If it can be integrated into process flow without compromising device performance, integrated thin-film sealing offers many size and cost advantages over other packaging techniques.

#### Wafer Bonding

The general approach for wafer bonding vacuum packaging is shown in Figure 1.8. The process starts with two wafers, one wafer with the devices on it and another blank wafer that will serve as the cap. Next, bonding material is formed on one or both wafers. Then a recess, or cavity, is etched into the top wafer that will form the final cavity housing the MEMS device. Finally, depending on the bonding technique used, the two wafers are bonded together by applying heat, pressure, and/or voltage.

Figure 1.8 Generic process for wafer bonding packaging.

There are many different types of wafer bonding approaches available that can provide the protection or integration necessary for MEMS packaging applications (see Table 1.3). For some wafer bonding techniques, it is as simple as electroplating a few thin films onto each wafer, integrating the getter, and then bonding the wafers together. The large number of bonding techniques at a range of temperatures give the package engineer some design flexibility when choosing a technique for the packaging process flow. The modular wafer bonding packaging approach offers much more flexibility compared to thin-film packaging which requires high-temperatures and a dedicated process flow.

| Bonding<br>Type   | Temperature | Planarization | Hermeticity | References |

|-------------------|-------------|---------------|-------------|------------|

| Anodic            | Medium-High | Poor          | Fair        | [12]       |

| Fusion            | High        | Poor          | Good        | [13]       |

| Eutectic          | Medium-High | Good          | Good        | [12],[14]  |

| Solder            | Low-Medium  | Good          | Good        | [12],[14]  |

| Glass Frit        | Medium-High | Good          | Fair        | [12],[15]  |

| Polymer           | Low         | Good          | Poor        | [16]       |

| Thermocompression | Low-Medium  | Fair          | Good        | [17],[18]  |

Table 1.3 Comparison of different wafer bonding techniques.

All these techniques have been used to bond wafers together; however, not all of them are suitable for vacuum packaging. All polymers and some glasses are too permeable to provide the hermetic seal necessary for vacuum packaging over typical MEMS scales (see Figure 1.9), so wafer bonding for vacuum packaging has usually been achieved with anodic, fusion, glass frit, and metal bonding. More details on the different wafer bonding approaches are covered in Section 2.1.

Figure 1.9 Hermetic performance of different material classes [4].

Wafer bonding vacuum packaging is a very flexible process that is easier to integrate into a process flow, but it suffers from some drawbacks: The bond rings take up a large amount of die area and the final product is a large multi-wafer stack. Also, the proven wafer bonding techniques, such as anodic, glass frit, and eutectic bonding, all require temperatures of 350 °C or higher. There is need for further research into lower temperature wafer bonding techniques for packaging thermally-sensitive devices.

#### **Transferred Thin-Film**

A newer packaging approach that combines some of the advantages of each of the two major packaging approaches has received some research attention lately [19]. A transferred thin-film package offers the low-profile of the thin-film packaging approach with the process flexibility of the wafer bonding approach. Unlike previous thin-film packaging approaches, a transferred thin-film package can accommodate getters in the process flow and can be realized with many low temperature bonding techniques.

Figure 1.10 shows a generic process flow for a TTF packaging approach. The process starts with the device wafer and a carrier substrate that will hold the package caps before they are transferred. A release layer is prepared on the carrier wafer. Then the package

caps are created on top of the release layer. Next, a bond ring is prepared on the device wafer and/or the carrier wafer full of packages. Finally, the packages are bonded and transferred to the device wafer using a wafer-bonding technique combined with a package transfer technique.

Figure 1.10 Generic process for transferred thin-film packaging.

Transferred thin-film packaging is an excellent candidate for 0-level MEMS packaging. It builds upon the inherent advantages of thin-film packaging, namely a low-profile and small size, by adding the modularity of wafer bonding. A transferred thin-film package can be adapted to many process flows to provide protection for MEMS devices, but much work needs to be done. Transferred thin-film packaging is an unproven technology. More research is needed to integrate getters, characterize different sealing bonds, and test the reliability of the packages. Solder has some interesting properties that make it an attractive material for accomplishing both the wafer bonding and transfer necessary for a transferred thin-film packaging process.

### **1.2 Solder for Vacuum Packaging**

Solder is a low melting point metal alloy (< 450 °C), typically containing tin or indium, which is used to join two metal surfaces together [20]. The solder acts as metal "glue"

that adheres to each metal surface and holds them together. Solder has several advantages that make it a good material for MEMS vacuum WLP.

First, there are many different solder alloys that melt at temperatures ranging from near room temperature to several hundred degrees Celsius (Table 1.4). The range of solder melting temperatures offers some thermal flexibility to the designer of a packaging process. As mentioned previously, all of the wafer bonding processes require temperatures of 350 °C or higher. There are many solders that melt at temperatures well below 350 °C that could be used as wafer bonding techniques.

| Composition, wt % |      |      |      |      |     |  | Eutectic |

|-------------------|------|------|------|------|-----|--|----------|

| Ag                | Bi   | In   | Pb   | Sn   | Au  |  | °C       |

|                   | 49.0 | 21.0 | 18.0 | 12.0 |     |  | 57       |

|                   | 57.0 |      |      | 43.0 |     |  | 139      |

| 3.0               |      | 97.0 |      |      |     |  | 144      |

|                   |      | 99.4 |      |      | 0.5 |  | 156      |

|                   |      |      | 38.0 | 62.0 |     |  | 183      |

| 3.5               |      |      |      | 96.5 |     |  | 221      |

|                   |      |      |      | 20   | 80  |  | 278      |

Table 1.4 Several widely used low melting point solder alloys [20].

Second, solders can planarize over wafer topography similar to the industry standard technique glass frit. A major source of topography in MEMS packaging is lateral feedthroughs that provide interconnection to the packaged MEMS. Direct bonds, like anodic and fusion, cannot seal over any topography greater than 100 Å. Bonds that are liquid or semi-fluid during the bonding process will flow over and conform to topography, which is a major advantage for a bonding technique if it will be used for packaging.

Third, solders are made of the best material for creating vacuum packages, metal. Figure 1.9 shows that as a material class, metals provide the greatest hermetic capability per unit thickness. This is advantageous for creating MEMS vacuum packages with scaleable bond rings. Metals will still provide the hermetic seal that is necessary to maintain good pressure levels for MEMS vacuum packages even as the bond ring widths get very small. No other material class is as effective at providing hermetic seals. For these reasons, different solder processes were developed and applied to create MEMS vacuum packages in this these. The next section gives an overview of the material presented as part of this research.

#### **1.3 Thesis Organization**

The goal of this thesis is to investigate uses of solder as a MEMS vacuum WLP material. The results from this effort are organized in the following manner:

Chapter 2 presents the background science of solder and the development of a solder wafer bonding process that is compatible with a commercial wafer bonder. The lessons learned from these wafer bonding efforts led to a successful implementation of a Au-Sn solder bond with good strength and hermeticity results.

Chapter 3 presents an advanced type of solder bonding, called transient liquid phase (TLP) solder bonding. This bonding technique is more compatible with the long thermal time constants of commercial wafer bonders and was therefore more successful than the standard solder bond in producing vacuum results. The Au-Sn, Ni-Sn, and Au-In TLP solder material systems were all investigated as wafer bonds for MEMS vacuum packages. Their strength, hermetic, and re-melting results are all presented as well as a section detailing the design rules for TLP solder bonding.

Chapter 4 covers the use of the standard and TLP solder bonds in creating vacuum packages. The motivation for vacuum packaging several classes of MEMS devices is covered. Some of the background science that explains the difficulties in creating MEMS vacuum packages, such as outgassing and getters, is reviewed. Two different Pirani gauges were used to make the pressure measurements in the vacuum packages. Finally, the vacuum data and some interesting low-temperature getter activation data are presented.

Chapter 5 explains a novel solder transfer process and its application in a transferred thin-film packaging process. The transfer process is combined with a TLP solder bond to transfer thin electroplated films from a carrier wafer to a device wafer. Several challenges in creating a vacuum package with this technique are covered, including process integration challenges and thermal coefficient of expansion stress issues.

Chapter 6 includes the conclusion and outlines proposed future work in MEMS vacuum packaging with solder.

# Chapter 2

# WAFER BONDING USING STANDARD SOLDER

Solder has been used since antiquity to bond two metal surfaces to one another at relatively low temperatures (150-300 °C). Modern electronics make use of solder as a bonding mechanism at many points during the assembly process: solder is used to form the interconnections and mechanical attachment between a chip and a PC board with a ball grid array, between dual-inline packages (DIP) and a PC board, and to attach wires in electronic systems. Despite solder's widespread use in electronics manufacturing, it has only recently been used for MEMS packaging [10]. As mentioned in the introduction, solder has several properties that make it an interesting candidate for MEMS wafer-level packaging research. Its low melting point, planarization capabilities, and low permeability give solder several advantages over other wafer bonding techniques for creating low-temperature scalable vacuum packages. The following sections discuss the fundamentals of a typical soldering process, some challenges that were faced in using it to create wafer bonds, and results from a wafer-level Au-Sn solder bonding process.

Section 2.1 briefly reviews wafer bonding technologies and compares them to solder bonding technologies. There are many different types of wafer bonding that can be used to create vacuum packages, but solder bonding offers several advantages that make it a unique approach among all others.

Section 2.2 reviews the basics of general solder bonding theory, such as wetting, intermetallic formation, and fluxless soldering. The process details of a standard solder bonding process are also covered, such as the reflow profile and bonding environment.

Section 2.3 covers the solder bonding experiments that were carried out as part of this work, including the shortcomings of the wafer bonding equipment used in the experiments. The results are summarized in Table 2.1. The long thermal-time constant of

standard commercial wafer bonding tools made applying standard solder bonding techniques to MEMS processes challenging. Several materials were explored to achieve reliable solder bonding on the wafer scale. In the end, only Au-Sn solder proved to be a reliable, robust wafer-level solder bonding technique that is suitable for MEMS vacuum packaging.