# Unreliable Silicon: Circuit through System-Level Techniques for Mitigating the Adverse Effects of Process Variation, Device Degradation and Environmental Conditions

by

#### **Eric Alexander Karl**

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 2008

#### **Doctoral Committee:**

Professor David Blaauw, Co-Chair Associate Professor Dennis M. Sylvester, Co-Chair Professor Trevor N. Mudge Associate Professor Michael Flynn © Eric A. Karl 2008 Dedicated to my mother and father, for their unwavering support and patience with me throughout my life.

# **Acknowledgements**

I would like to acknowledge the invaluable contributions of my advisors Dennis Sylvester and David Blaauw during my time at the University of Michigan. Many times you refocused my work when the light seemed "dim", inspired me and hardened my resolve to see my projects to a fitting conclusion. Thanks to Trevor Mudge and Michael Flynn for agreeing to serve on my thesis committee and for additional insight provided along the way. Special thanks to Todd Austin and the resilient group in GSRC; some of the quarterly meetings sparked new ideas in my work.

I've had the opportunity to work with some truly talented graduate students during the past six years, some of whom merit individual recognition. Prashant, thanks for your patience, hard work and your "resilience" on our many collaborative projects. Carlos, your attention to detail, willingness to help and overall demeanor make the research group a better place to work. Sanjay, Yushiang, Scott, Mike, Greg and those I haven't mentioned, I've enjoyed the opportunities that I've had to work on our various tapeouts over the last few years. I have many fond memories from difficult times largely due to the teamwork and cooperation in our lab. Thanks to Ashish, Sarvesh, Kanak and Himanshu for the solid foundation and reputation that you helped to build for our research group. I will truly feel proud to be an alumni of this group.

A large number of mentors in industrial positions have positively influenced my work and my development through interactions on my interships and coops. In no particular order, thanks to Spencer Gold, Steve Kosonocky, Dan Knebel, George Gristede, Keith Bowman, Vivek De and Robert Schwabel. Each of you positively impacted me at various points in my development as a young engineer.

# **Table of Contents**

| Dedic  | cation                                       | ii  |

|--------|----------------------------------------------|-----|

| Ackn   | owledgements                                 | iii |

| List o | of Figures                                   | vi  |

| List o | of Tables                                    | ix  |

| Chap   | oter                                         |     |

| 1.     | Introduction                                 | 1   |

| 2.     | Timing Error Correction for On-Chip Memories | 15  |

|        | 2.1 Timing Error Detection and Correction    | 18  |

|        | 2.2 Exploiting Address/Data Dependence       | 24  |

|        | 2.3 180nm Simulation Results                 | 26  |

|        | 2.4 130nm Physical Implementation            | 32  |

|        | 2.5 130nm Simulation Results                 | 40  |

| 3.     | Reliability Modeling and Management          | 46  |

|        | 3.1 Reliability Modeling                     | 49  |

|        | 3.2 System Level Modeling                    | 63  |

|        | 3.3 DRM System                               | 67  |

|        | 3.4 Results and Discussion                   | 73  |

|        | 3.5 Summary                                  | 82  |

| 4.     | Analysis of Real-time Reliability Monitoring | 84  |

|        | 4.1 Oxide Breakdown Simulation Methodology   | 87  |

|        | 4.2        | OBD Monte Carlo Framework                                  | 90  |

|--------|------------|------------------------------------------------------------|-----|

|        | 4.3        | Failure Distribution Analysis                              | 94  |

|        | 4.4        | Real-time Monitoring                                       | 98  |

|        | 4.5        | Summary                                                    | 102 |

| 5.     | A 130nm (  | Oxide Degradation Sensor                                   | 104 |

|        | 5.1        | Oxide Degradation Sensor Design                            | 105 |

|        | 5.2        | 130nm Testchip Implementation                              | 111 |

|        | 5.3        | Measured Results and Discussion                            | 114 |

|        | 5.4        | Summary and Discussion                                     | 117 |

| 6.     | A 45nm N   | BTI/Oxide Degradation Sensor                               | 119 |

|        | 6.1        | 2 <sup>nd</sup> Generation Oxide Degradation Sensor Design | 120 |

|        | 6.2        | 45nm Testchip Implementation                               | 127 |

|        | 6.3        | Simulated Results and Discussion                           | 130 |

|        | 6.4        | Summary                                                    | 133 |

| 7.     | Conclusion | າ                                                          | 135 |

|        | 7.1        | Future Work                                                | 138 |

| Biblio | graphy     |                                                            | 140 |

# **List of Figures**

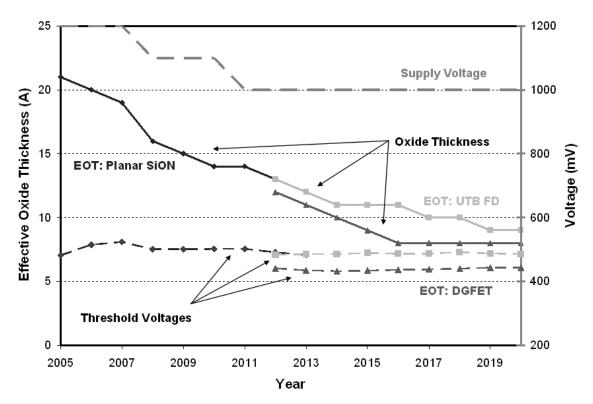

| 1.1  | 2005 ITRS low power roadmap scaling of oxide thickness, threshold voltage and supply voltage                                                       |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------|

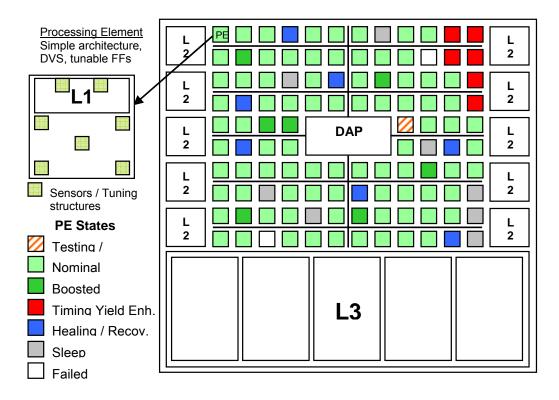

| 1.2  | Proposed ElastIC architecture, showing multi-processing elements in different operation modes                                                      |

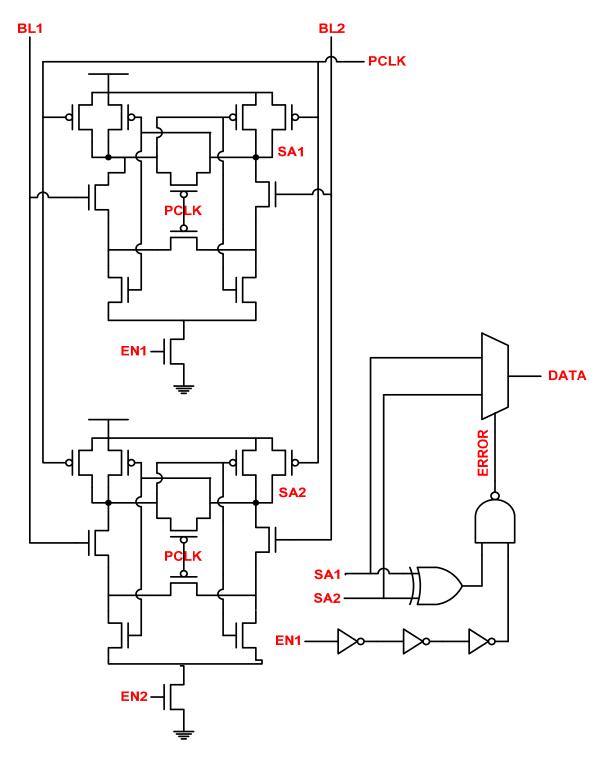

| 2.1  | Main and Shadow Sense Amplifiers latched and compared via XOR gate and multiplexed to an output bus                                                |

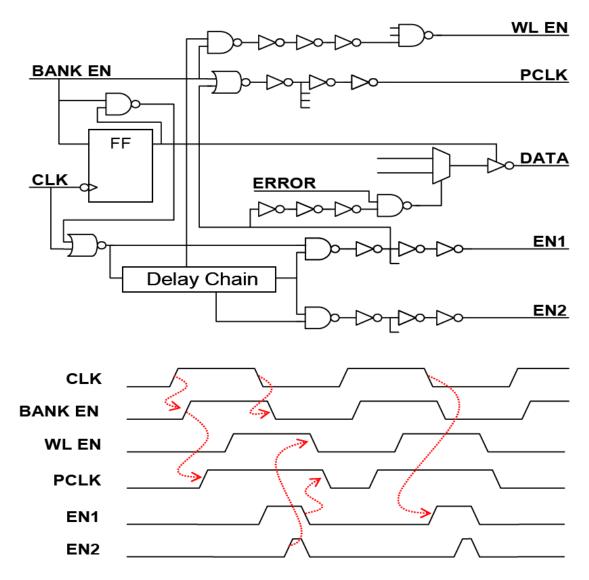

| 2.2  | Timing signal generation circuits and waveforms                                                                                                    |

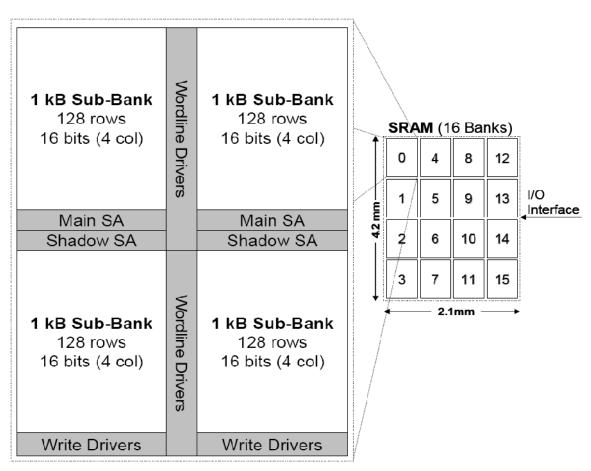

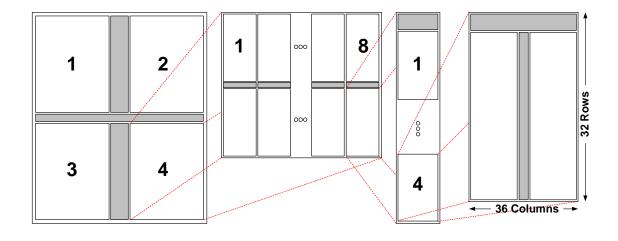

| 2.3  | Proposed SRAM floorplan                                                                                                                            |

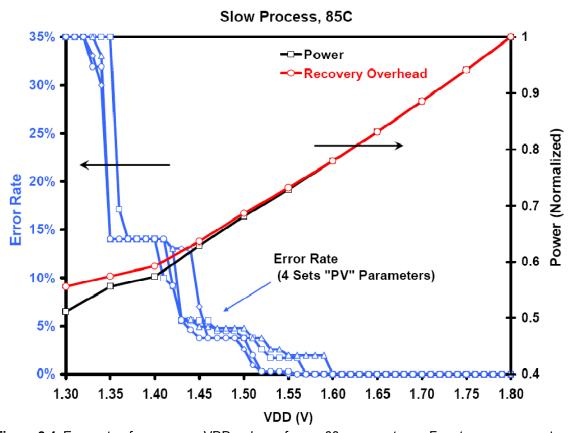

| 2.4  | Error rate of memory as VDD reduces for gap00 memory trace                                                                                         |

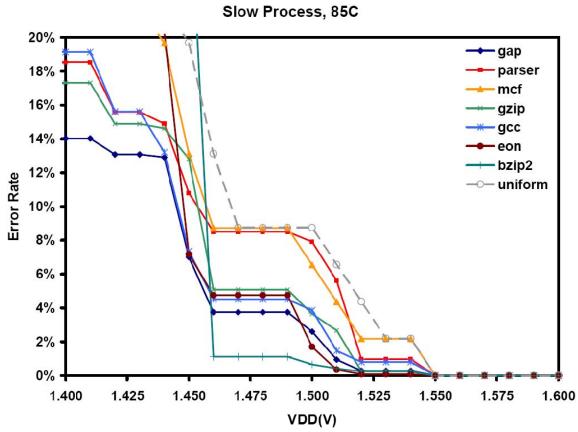

| 2.5  | Error rates for a set of benchmarks vs. supply voltage                                                                                             |

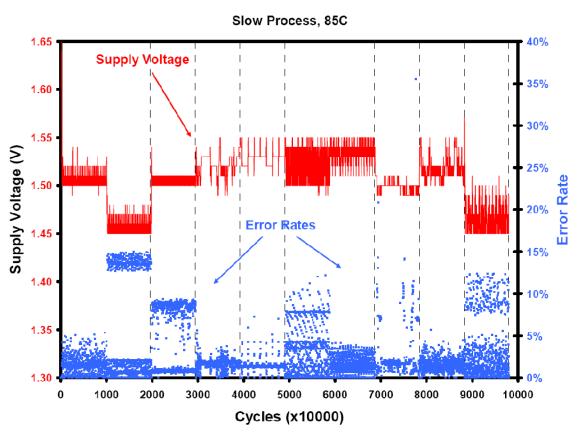

| 2.6  | Instantaneous supply voltage and error rate during 10M cycle DVS simulation with varying workload                                                  |

| 2.7  | Array Architecture and Output Path                                                                                                                 |

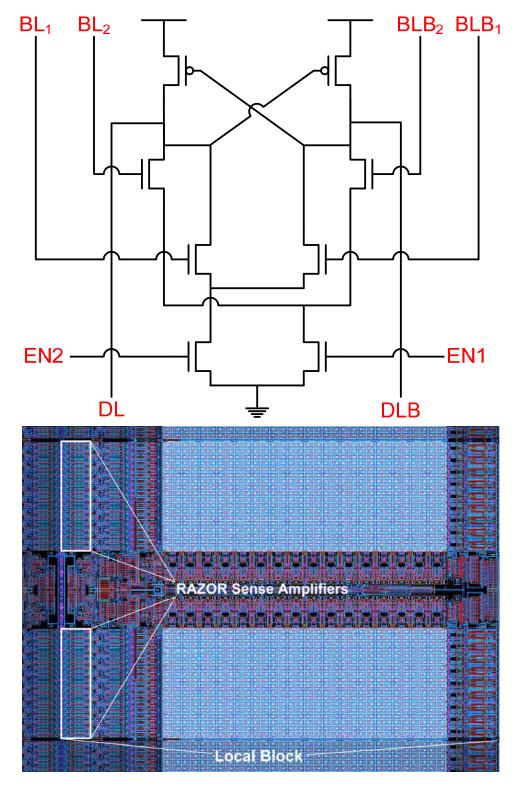

| 2.8  | Sense amplifier and integrated 2:1 column multiplexer and layout of new local block showing area overhead of "RAZOR" or shadow sense amplifiers 35 |

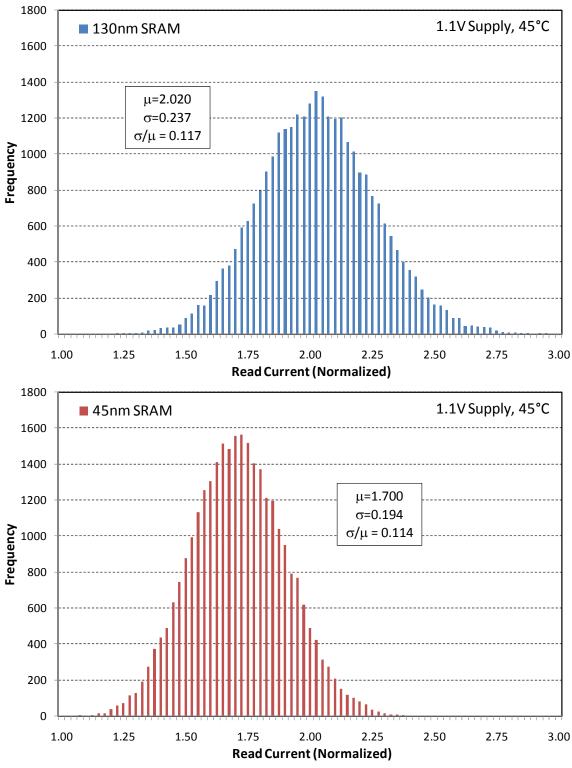

| 2.9  | Output latch with added <i>shadow latch</i> and error correction and detection circuitry                                                           |

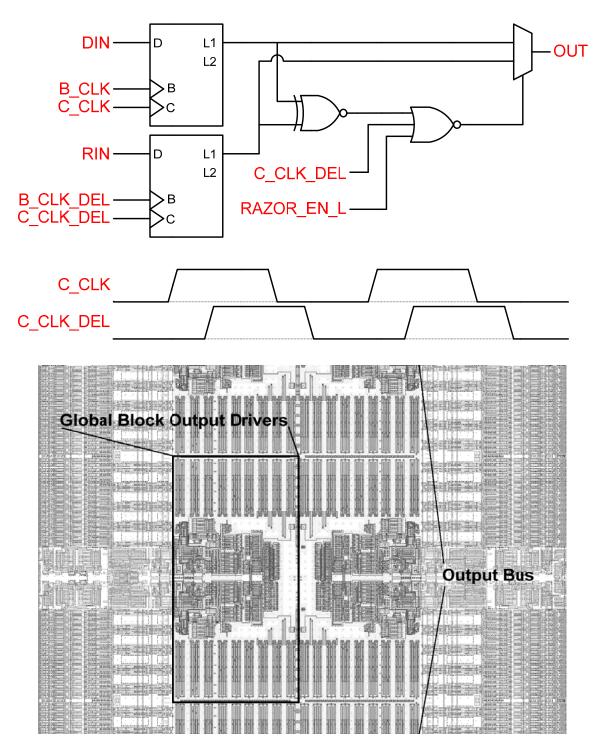

| 2.10 | Distribution of Read Current for 130nm and 45nm technologies 41                                                                                    |

| 2.11 | SRAM Read Path Timing and Read Current scaling with VDD for 130nm technology                                                                       |

| 2.12 | Minimum operating voltages for various combinations of threshold voltage variation for the implemented design of the time redundancy test chip 44  |

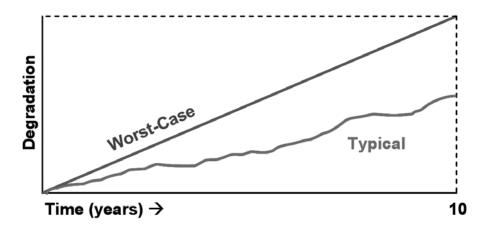

| 3.1 | Reliability Degradation over time                                                                                                            | 47  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.2 | Proposed piecewise NBTI calculation algorithm.                                                                                               | 62  |

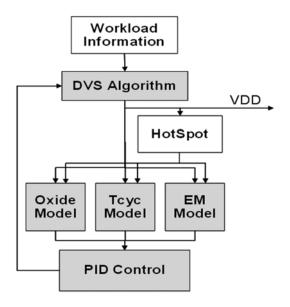

| 3.3 | DRM System block diagram.                                                                                                                    | 68  |

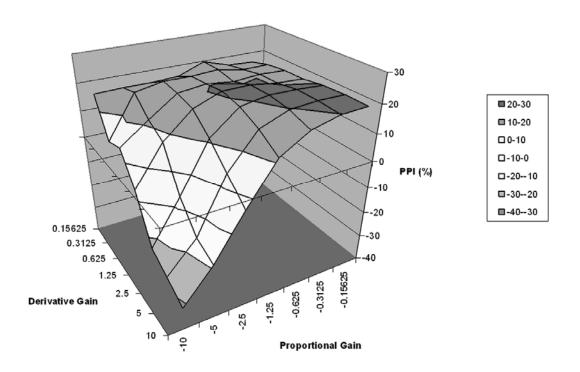

| 3.4 | PID Controller gain values vs. peak performance improvement for example DRM system                                                           |     |

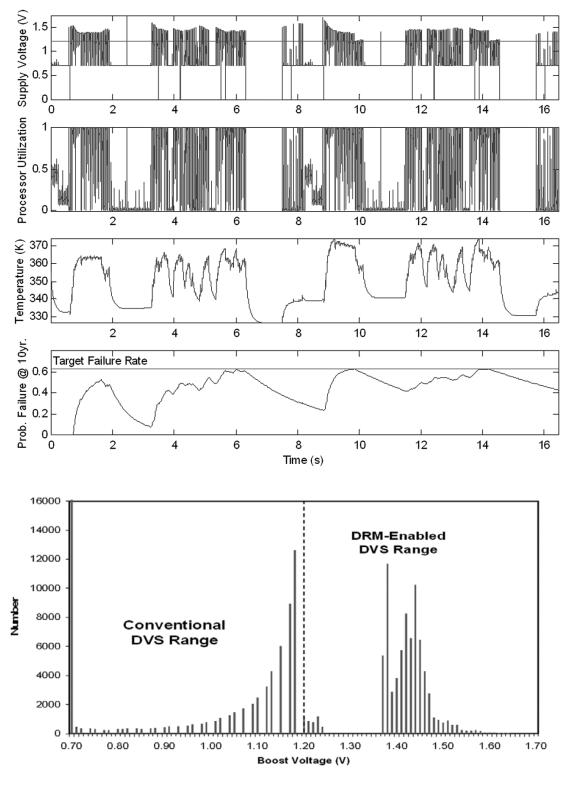

| 3.5 | DRM Operation for workload C630 (16 seconds) and supply voltage assignment histogram.                                                        | 76  |

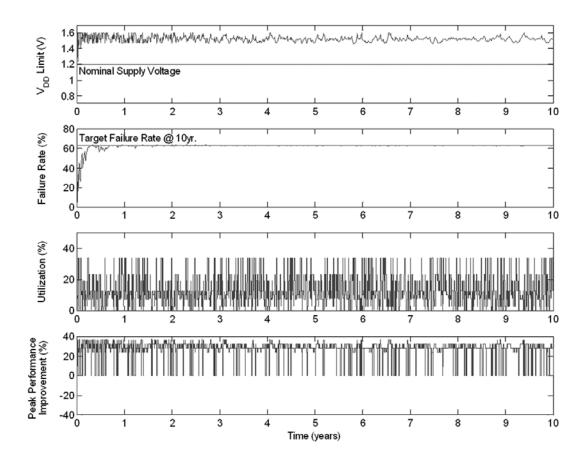

| 3.6 | DRM Operation over 10 year reliability simulation.                                                                                           | 77  |

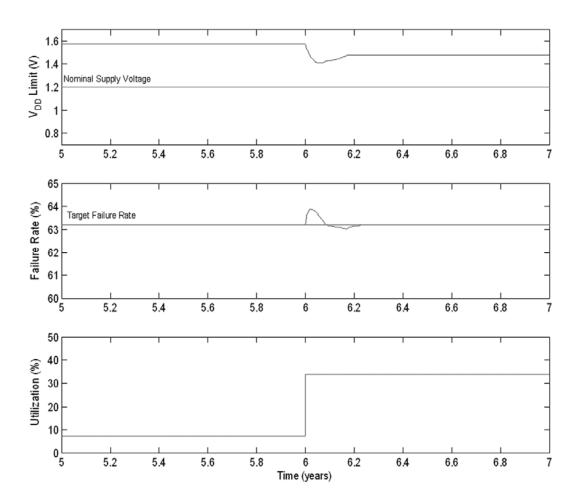

| 3.7 | DRM PID controller step input response, representing sharp change in usage profile mid-life.                                                 | _   |

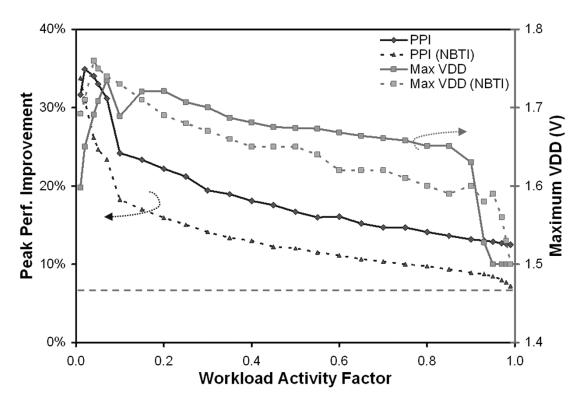

| 3.8 | Peak performance and max supply voltage vs. workload activity considering NBTI.                                                              | _   |

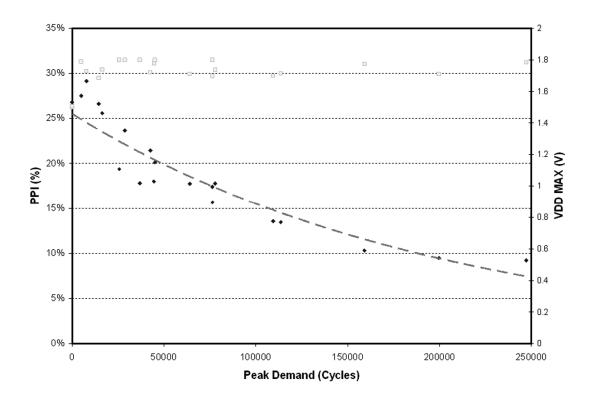

| 3.9 | Peak demand vs. peak performance improvement (with NBTI)                                                                                     | 82  |

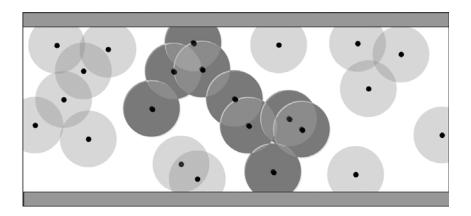

| 4.1 | Percolation model placement of point defects in 3-dimensional oxide space (2D diagram shown).                                                |     |

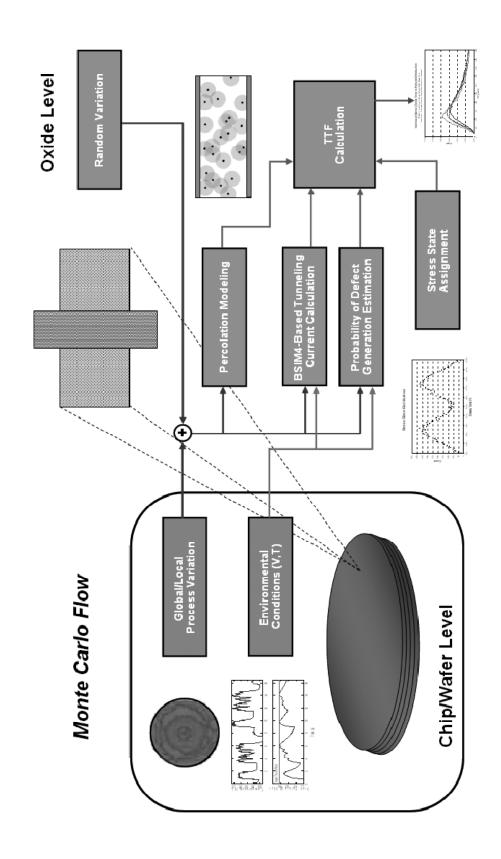

| 4.2 | Monte carlo simulation framework for generating oxide breakdown distribution                                                                 | 91  |

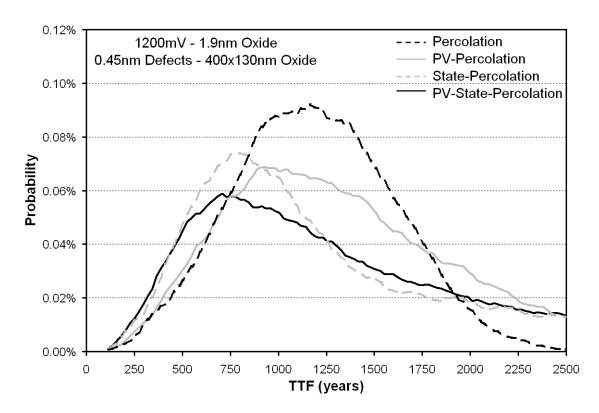

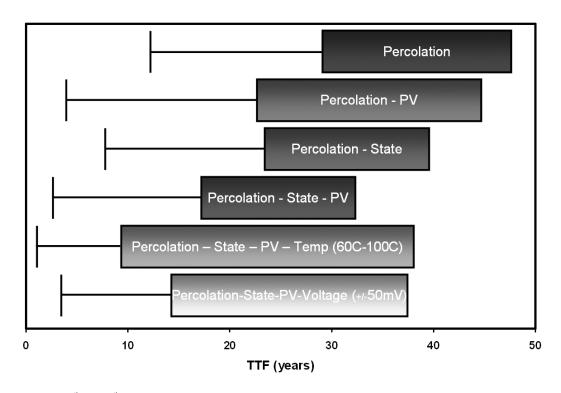

| 4.3 | Oxide failure distributions with different simulation components included                                                                    | 95  |

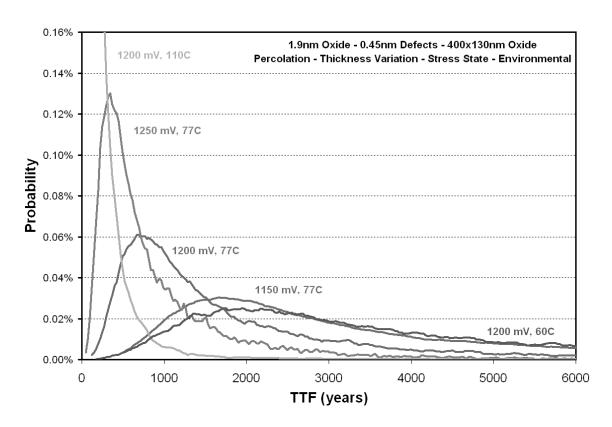

| 4.4 | Failure distribution for 1.9nm oxide with conditions varying from 1.15-1.25V and 60-110C.                                                    |     |

| 4.5 | 25 <sup>th</sup> to 75 <sup>th</sup> percentile ranges for 100 die simulation of 1.9nm oxide first failures                                  | 97  |

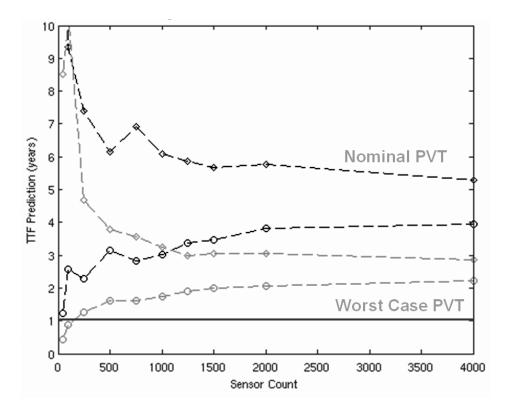

| 4.6 | 95% confidence interval in TTF prediction as sensor count increases for 2 different dies                                                     | 101 |

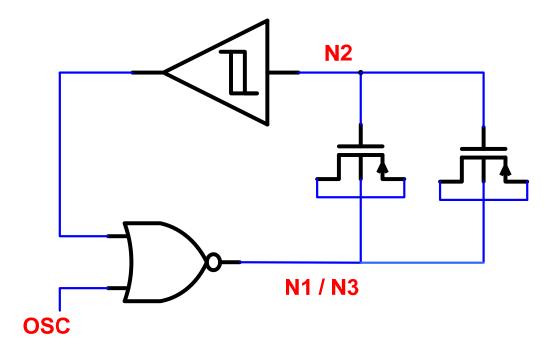

| 5.1 | Simple model of oxide degradation sensor measurement featuring series garantees oxide resistance and thick oxide Schmitt trigger oscillator. |     |

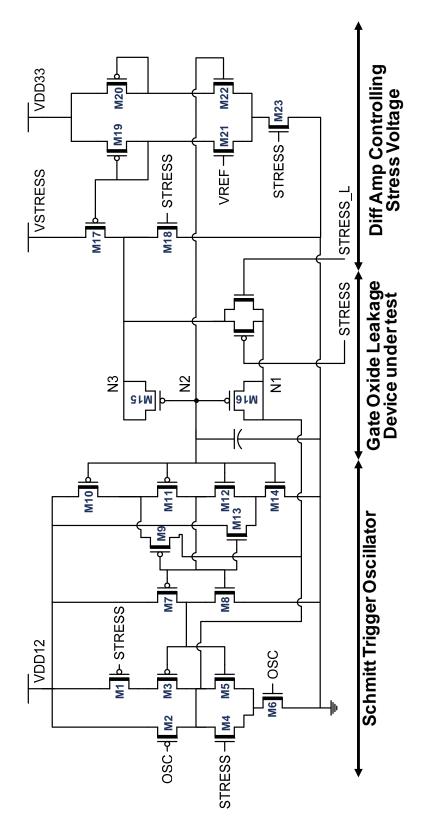

| 5.2 | Oxide degradation sensor schematic.                                                                                                          | 107 |

| 5.3 | Simulated waveforms demonstrating sensor operation                                                                                           | 110 |

|     | vii                                                                                                                                          |     |

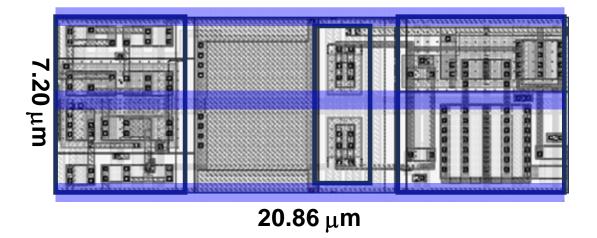

| 5.4 | Oxide degradation sensor standard cell compatible layout                                                                                             |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------|

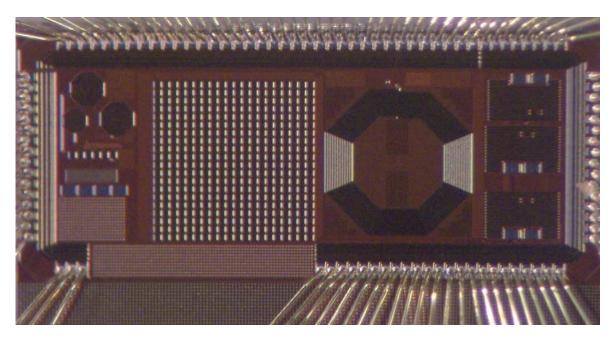

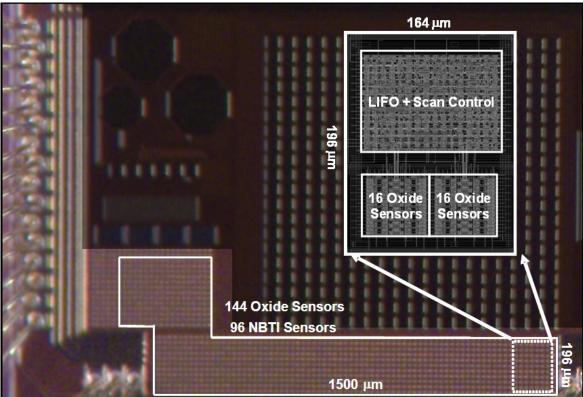

| 5.5 | (Above) Complete 130nm multi-project testchip. (Below) Detailed view of oxide and NBTI degradation sensor test chip with block layout view inset 113 |

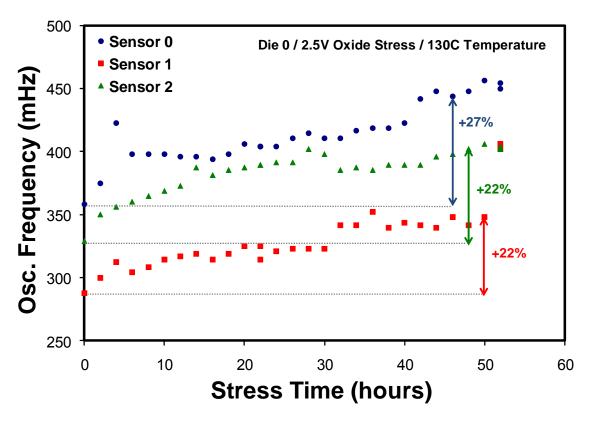

| 5.6 | Oscillator frequency increase as the gate oxide is stressed at 2.5V and 130C for 3 sensors from a single die                                         |

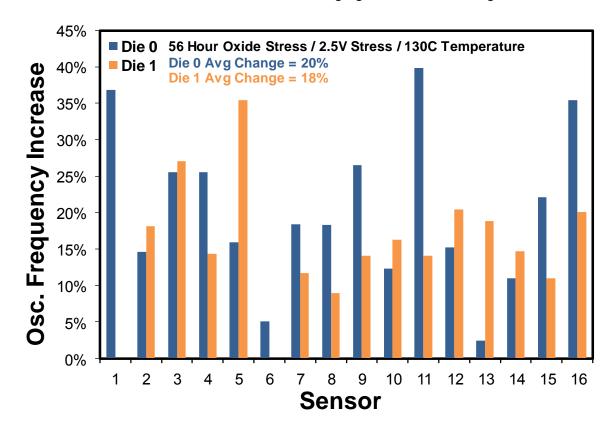

| 5.7 | Final oxide degradation sensor frequency increase following 56 hours stress period at 2.5V and 130C                                                  |

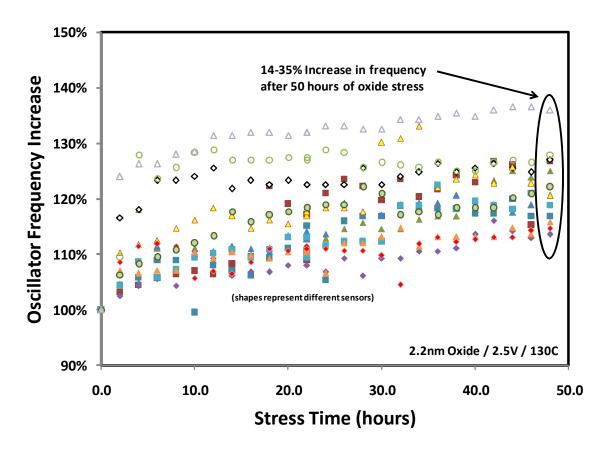

| 5.8 | Oxide degradation sensor frequency increase as a function of time 116                                                                                |

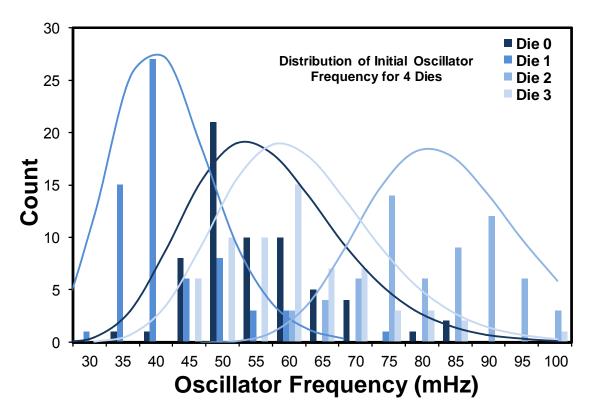

| 5.9 | Distribution of initial oxide degradation sensor oscillating frequencies 117                                                                         |

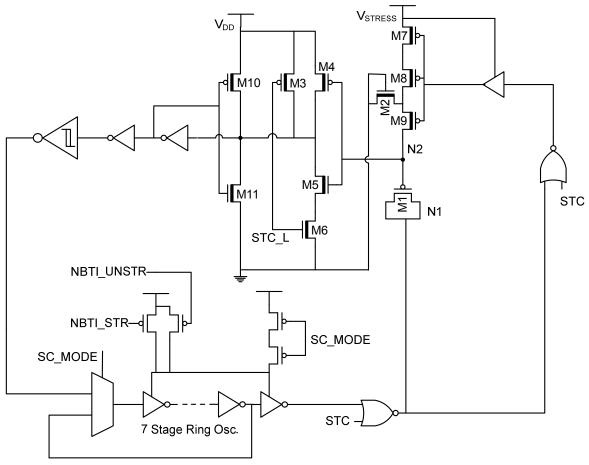

| 6.1 | 45nm oxide degradation sensor circuit diagram                                                                                                        |

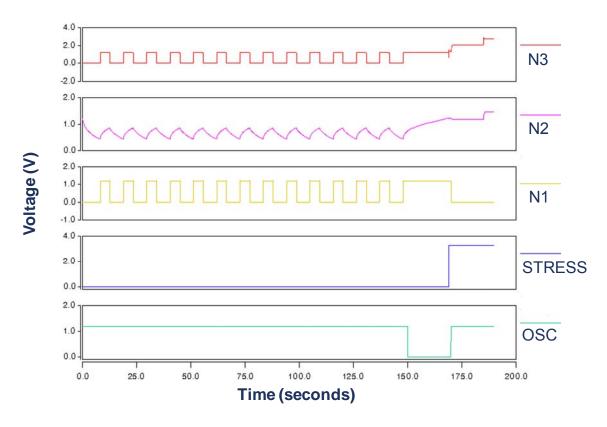

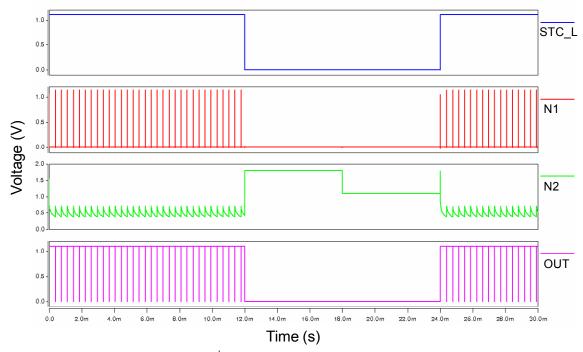

| 6.2 | Simulated operation of 2 <sup>nd</sup> generation 45nm oxide degradation sensor 126                                                                  |

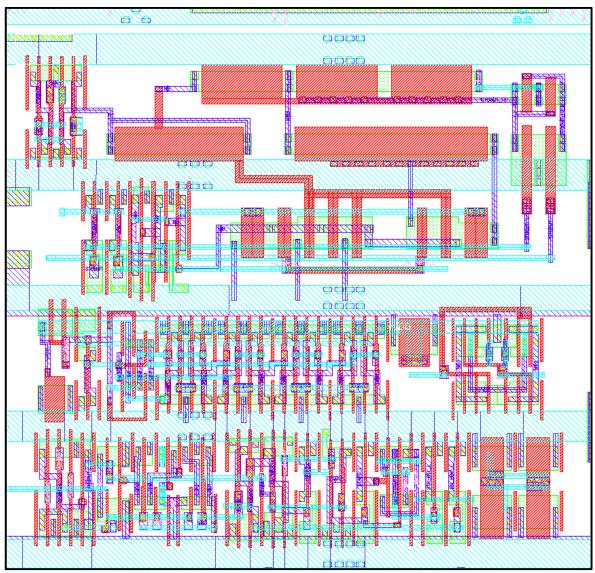

| 6.3 | 45nm oxide degradation sensor cell layout                                                                                                            |

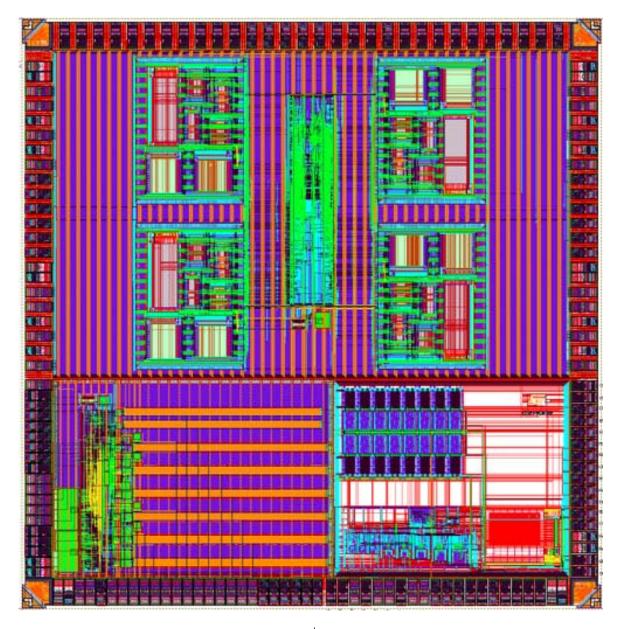

| 6.4 | 45nm multi-project testchip including 2 <sup>nd</sup> generation oxide and NBTI degradation sensors                                                  |

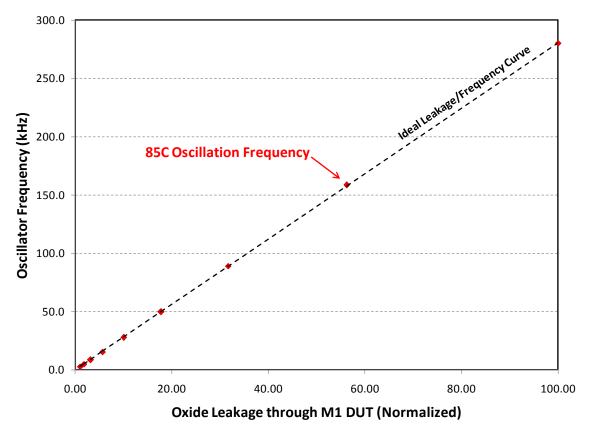

| 6.5 | Oscillation frequency vs. oxide leakage scaling for extracted parasitic simulation                                                                   |

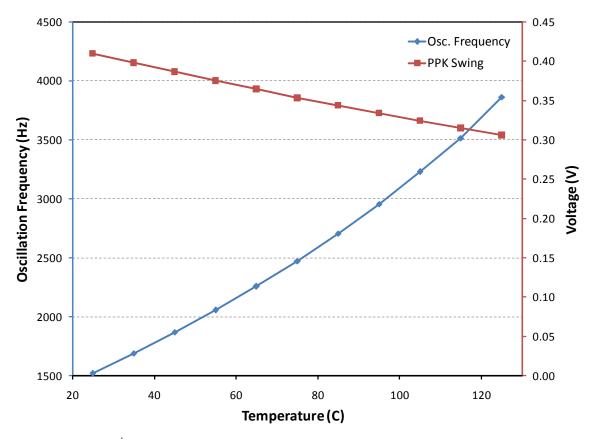

| 6.6 | 45nm 2 <sup>nd</sup> generation oxide degradation sensor temperature scaling 132                                                                     |

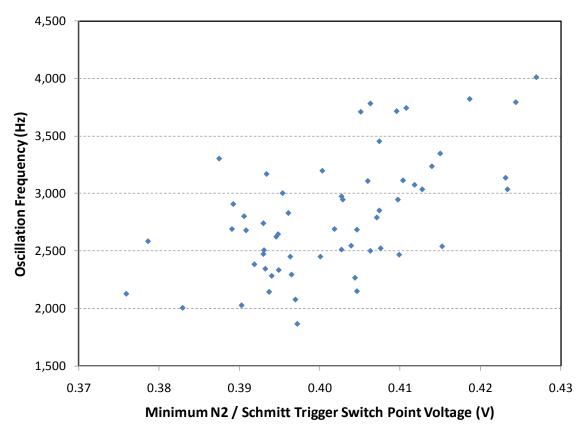

| 6.7 | Monte carlo simulation of 45nm oxide degradation sensor design 133                                                                                   |

# **List of Tables**

| T | a | bl | le |

|---|---|----|----|

| • | ~ | ~  | _  |

| 1.1 | Constant Field Scaling Factors                                                | 1     |

|-----|-------------------------------------------------------------------------------|-------|

| 2.1 | Power Consumption at Various Operating Points                                 | 30    |

| 3.1 | Simulation Technology Specification and Selected Model Parameters of Interest | 74    |

| 4.1 | Parameter Values for Simulation Framework                                     | 92    |

| 4.2 | Spatial Correlation between Blocks in the PV Model                            | 98    |

| 4.3 | Sensor Count and Prediction Error based on Ideal Sensors                      | . 100 |

| 5.1 | 130nm Oxide Degradation Sensor Sizing                                         | . 109 |

| 6.1 | Subthreshold vs. Gate Leakage in 2 Process Technologies (Normalized).         | . 121 |

| 6.2 | 45nm Oxide Degradation Sensor Sizing                                          | . 122 |

# **Chapter 1**

#### Introduction

The continued, aggressive downscaling of dimensions in forthcoming CMOS technology generations [1] stands to increase the risk of significant reliability issues in integrated circuits. Conventional or constant electric field scaling law, in Table 1.1, dictates that supply voltages must be reduced to maintain a constant electric field as the critical dimensions of CMOS transistors and wires shrink. However, in recent years, the voltage scaling trend of constant electric field scaling [2] has been ignored to maintain the saturation current and other performance metrics [1].

**TABLE 1.1**Constant Field Scaling Factors

| Parameter                      | Scaling Factor |

|--------------------------------|----------------|

| Length, Width, Oxide Thickness | 1/α            |

| Doping Concentration           | α              |

| Supply Voltage                 | 1/α            |

| Circuit Speed                  | α              |

| Circuit Power                  | $1/\alpha^2$   |

| Device Density                 | $1/\alpha^2$   |

| Power Density                  | 1              |

Over the past ten years, device designers have found that it impossible to scale supply voltage down to match the dimension scaling due to the opposing constraints

of standby power consumption and saturation current. The delay of digital circuits with short-channel MOSFETs is directly related to the velocity saturated drain current [3]. To continue scaling supply voltage and maintain a constant electric field, threshold voltage must be reduced to provide improvement in saturation current to offset the reduced supply voltage, according to the short channel velocity-saturation-limited current relationship [4] in Equation (1.1).

$$I_{dsat} = C_{ox}W\vartheta_{sat}(V_g - V_{th})$$

(1.1)

$$V_{dsat} = \sqrt{2\vartheta_{sat}L(V_g - V_{th})/m\mu_{eff}}$$

(1.2)

Notice that Equation (1.1) is independent of channel length and linear with respect to gate overdrive,  $V_g$ - $V_{th}$ . The saturation voltage required to achieve velocity saturation, in Equation (1.2), is a function of channel length (L), but the magnitude of short channel velocity saturated current is not a function of channel length, in the first order. Successive technology generations scale width and length with other dimensions in Table 1.1 to increase circuit density and minimize area, to save fabrication cost. In Equation (1.1), equal reduction in transistor width and oxide thickness are offset by the changes in  $C_{ox}$  (increases with decreasing  $T_{ox}$ ) and W. The reduction in oxide thickness traditionally must be accompanied by a reduction in supply voltage ( $V_g$ ) to maintain reliability integrity of oxides, and control dynamic power consumption, as detailed in Table 1.1. Since the saturation velocities of hole and electrons are constant, any reduction in supply voltage ( $V_g$ ) must be accompanied by a reduction in threshold voltage ( $V_{th}$ ) to maintain the saturation current of the scaled MOSFET.

The dramatic increase in off-state leakage of MOSFETs as technology scales [5] prevents designers from actually scaling the threshold voltage to maintain the saturation current. Figure 1.1, from the 2005 ITRS update data clearly displays these trends; oxide thickness is constantly scaled, while supply voltage and particularly threshold voltage remain nearly constant across this 15 year span. The result of this compromise is that with each technology generation, the supply voltage is not reduced at the rate dictated by constant-field scaling theory and the electric field across thin-film oxides and junctions is steadily increasing. The drawback is that reliability issues and device degradation become increasingly probable for most breakdown mechanisms due to the elevated electric fields.

**Figure 1.1** 2005 ITRS low power roadmap scaling of oxide thickness, threshold voltage and supply voltage.

Oxide breakdown (OBD) [6], electromigration (EM) [7] and the negative bias temperature instability effect (NBTI) [8] are three reliability failure mechanisms for integrated circuits that are strongly impacted by electric fields in the gate oxide region. OBD and NBTI mechanisms degrade device structure through collisions between particles in the oxide lattice or the oxide-silicon interface region. Two widely accepted models for oxide breakdown modeling, the  $E_{ox}$  model [9] in (1.3) and the  $1/E_{ox}$  model [10] in (1.4) clearly show exponential reduction in time to oxide breakdown with increasing oxide electric fields.

$$t_{BD} \propto e^{\frac{\Delta H_0}{k_B T} - \gamma E_{OX}} \tag{1.3}$$

$$t_{BD} \propto e^{G/E_{OX}} \tag{1.4}$$

The rate of threshold voltage shift in bias temperature instability also increases exponentially according to the NBTI stress model [11] in (1.5). The rate of interface trap generation and shift in threshold voltage ( $\Delta V_{th}$ ) is dependent upon gate voltage and oxide electric field, which are constant and increasing, respectively, under the current paradigm of transistor dimension scaling. Secondarily, increasing temperature also increases the rate of threshold shift in an exponential fashion (activation energy,  $E_a$  is typically negative).

$$\Delta V_{th} \propto A t_{ox} \sqrt{C_{ox} (V_{gs} - v_{th})} [1 - \alpha V_{ds} / (V_{gs} - V_{th})] e^{(E_{ox}/E_0)} e^{-\frac{E_a}{kT}}$$

(1.5)

Electromigration degradation occurs in metal wires with high current density when metal atoms shift along grain boundaries due to diffusion and collisions.

Black's law [7] is the classic relationship between current density, temperature and

mean time to failure for wires, as show in (1.6). In (1.6), *J* is the current density, which typically increases, with high electric fields across MOSFET drains and gates, leading to a super-linear decrease in mean time to failure. Similar to the NBTI effect, electromigration lifetime decreases with increasing temperature, *T*.

$$MTF = AJ^{-n} \exp\left(\frac{E_a}{kT}\right) \tag{1.6}$$

In all of these mechanisms, higher electric fields and temperatures lead to vastly increased rates of degradation and higher incidence of failure. The continued non-scaling of supply voltage in process technologies is clearly exchanging lifetime reliability and wearout margin for maintaining saturation current expectations and off-state leakage budgets. The importance of reliability qualification techniques is now enhanced due to the diminishing margins through increasing electric fields in CMOS circuits.

Traditional stress-based reliability qualification techniques, such as the JEDEC JESD-47 Standard [12], qualify designs by stressing sample systems under pessimistic environmental conditions with a zero failure pass/fail criteria. While the traditional approach is an accepted method of ensuring reliability, the limits it places on supply voltage and temperature leave a significant and increasing reliability margin between circuit performance at worst-case conditions and at typical conditions. Widely varying environmental conditions and significant process variation increase the margin required to meet worst-case design time conditions. This unnecessarily limits the specifications of the majority of integrated circuits to the performance of a highly improbable set of process variation and environmental conditions.

In [13], Borkar identifies two critical sources of increasing process variation, random, discrete placement of dopant atoms in shrinking transistor channel regions and patterning shapes with feature sizes below the wavelength of the lithographic light source. Chen recently declared that line edge roughness and dopant fluctuation pose fundamental barriers to controlling device parameters [14]. Reliability mechanisms like NBTI are directly related to random dopant fluctuations, since the process variation shifts the initial threshold voltage of a device from its nominal value, and the NBTI effect adds a dynamic, time-varying shift to the threshold voltage. Combined the static and dynamic shift from process variation and reliability degradation severely limits the worst-case performance of a transistor. As discussed above, continued scaling increases the possible range of transistor threshold voltages by increasing the impact of dopant fluctuation in a smaller channel region (seen in Equation (1.7) [4]) and also increasing the electric field across gate oxides to exacerbate NBTI degradation.

$$\sigma V_{th} \propto \frac{q}{C_{ox}} \sqrt{\frac{N_a W_{dm}^0}{3LW}} \tag{1.7}$$

Using sub-wavelength light to pattern features results in significant variation in edge resolution and sharpness. This is primarily seen as line edge roughness that impacts wire width and the channel length of polysilicon gates. Variations in wire width and thickness complicate the projection of wire lifetime when considering electromigration. Variations in gate oxide area, as well as thickness, significantly alter the breakdown statistics for oxide breakdown modeling.

In addition to the impact of process variation, semiconductor products are used in an increasingly wide range of applications, with widely varying environmental

conditions. Increased range of ambient operating temperature, leads to a greater variation in on-chip temperature. From (1.5) and (1.6), temperature is an exponential factor on many reliability degradation mechanisms, including NBTI, electromigration, and thermal cycling. Temperature is another factor increasing the margin utilized by traditional worst-case reliability qualification techniques.

Hence, there are opportunities for alternative approaches to ensuring lifetime reliability under dynamic operating conditions. One alternative to stress-based qualification, knowledge-based risk assessment, is a sophisticated methodology when compared to simplistic corner-case stress testing. The knowledge based approach (a framework for knowledge-based qualification is defined by JEDEC JESD-34 [15]) requires careful characterization and analysis of individual failure modes to assess a reasonable system reliability risk factor given the reliability targets for the system. Despite the advantages of the knowledge-based risk assessment methodology, it still suffers from limited information on actual stress conditions on-chip and must use some type of a priori profiling that will introduce voltage or timing margins.

An alternative to placing the burden of reliability qualification entirely upon a priori characterization techniques is the recent proposal to utilize adaptive systems, capable of monitoring and self-diagnosis. Adaptive systems can self-regulate voltage, temperature or other critical parameters to dynamically maintain their specified reliability lifetime. The goal of the dynamic, adaptive system architectures and enabling circuits is to vastly reduce the margins on timing and voltage for typical silicon, while maintaining proper functionality for devices or structures with worst-

case stress conditions or variation. The contribution of this thesis is in adaptive circuit and architecture techniques for coping with highly unpredictable and unreliable silicon.

Early work on dynamic voltage scaling systems (DVS) targeted power reduction for digital circuits by dynamically reducing the power supply voltage when the target application or circuit did not require a full nominal voltage. Coincidentally, DVS systems are an extremely powerful way to improve reliability lifetime of integrated circuits due to the exponential dependence on electric field of many reliability mechanisms. DVS systems [16-18] initially targeted voltage reduction only where the application had periods of reduced computational demand. Frequency is typically reduced as the voltage was scaled, preserving voltage margin in the design despite the reduced performance required.

RAZOR [19, 20] was proposed as a DVS system that reduced voltage at a fixed frequency, aiming to achieve power reduction by exploiting data-dependent circuit delays and reduce the timing and reliability related voltage margin that is added through worst-case design methodologies. RAZOR utilized a novel timing error detection circuit built into flip-flop circuits that allowed detection of late arriving signal transitions due to process variation, voltage droop or wearout effects. Another novelty in the RAZOR work is the concept of scaling the voltage below the point of the first detected failure, leveraging the fact that first failures occur very infrequently. Recent work [21, 22] on the RAZOR concept has resulted in latches with integrated timing error detection circuitry that refines the approach to obtain up to 17%

reduction in supply voltage. From a reliability standpoint, 17% reduction in oxide electric field increases typical process oxide lifetime by several orders of magnitude.

The drowsy cache [23] was proposed by Flautner to reduce the standby leakage for inactive memory banks by using DVS to reduce their voltage. In Chapter 2, a technique similar to RAZOR is implemented in SRAM sense amplifiers to enable dynamic and standby power reduction for all banks of memory while improving the reliability lifetime of all memory circuits [24]. The technique utilizes a secondary sense amplifier to evaluate the bitline differential development through an extended evaluation phase in order to capture read timing related errors from decode logic, SRAM cell read current or sense amplifier threshold voltage mismatch. Simulated results show that this technique is successful in eliminating 200-300 mV of design voltage margin in 180nm process technology.

Beyond the initial DVS based work targeted at power reduction, Sylvester [25] proposed ElastIC, a broad adaptive architecture targeted at delivering reliable system functionality in an era of unpredictable and unreliable silicon devices. ElastIC is a framework for massively multi-processor systems based upon self-test and diagnosis, adaptive operation and stress relaxation techniques. As shown in Figure 1.2, the ElastIC architecture leverages research concepts in the device, circuit, architecture and testing fields.

The foundation of ElastIC is an array of processing elements with built-in self-test (BIST) and power, performance and reliability monitoring circuits. Each processing element (PE) is tunable through voltage, frequency or timing boundaries in tunable flip-flops. The diagnostic and adaptivity processing (DAP) unit is centrally

located to manage the individual testing of each PE and schedule the variety of adaptive features for each PE. Some PEs will have an elevated voltage for high performance, some have adjusted flip-flop timing signals to improve functional yield. Other elements are in a low power sleep state, or placed into a beneficial bias state to "heal" reversible reliability related degradation (such as NBTI or positive bias temperature instability effect (PBTI)). Highly redundant memory and processors combine to deliver high reliability despite underlying uncertainty in the silicon devices.

**Figure 1.2** Proposed ElastIC architecture, showing multi-processing elements in different operation modes. Processing elements consist of a mini processor with dynamic voltage scaling and tunable flip-flop timing.

The precursor to ElastIC, was the initial proposal of dynamic reliability management systems (DRM) [26] by Srinivasan. DRM is a control architecture for integrated circuits and systems that attempts to dynamically ensure that the component meets its reliability lifetime specification by tuning voltage, restricting circuit activity and temperature in order to adjust the current rate of reliability degradation. The key concept introduced in DRM work was modeling reliability as a budget that can be consumed at different rates, based upon the stress and activity of the system. Srinivasan used a sum of failure rates modeling method while considering multiple reliability mechanisms and discussed the potential implementation of several control mechanisms.

Lu and co-authors [27] analyzed electromigration effects and suggested a dynamic thermal management (DTM) system. Lu's proposed DTM system monitors temperature of junctions on-chip and throttles execution when necessary to keep system temperature within specified bounds. This system is considerably simpler than Srinivasan's DRM system, yet also significantly reduces reliability uncertainty by restricting the range of operating temperatures dynamically.

McGowen and co-authors [28] describe an embedded feedback and control system implemented into a commercial microprocessor that simultaneously monitors and limits power consumption and junction temperature. Intel Foxton Technology (FT), as referred to in the original work, modulates voltage and frequency dynamically to maximize core clock frequency within specified power and temperature envelopes. The FT system is currently integrated on a shipping product, consuming 0.5% of the die area and 0.5% of the processor power budget.

In Chapter 3, a full multi-mechanism DRM system is described in detail using a PID controller to actuate voltage limits in a DVS system [29, 30]. System-level probabilistic modeling and a method for extrapolating simulation to full lifetime projection is detailed. With an implementation similar to Lu and McGowen, this work integrates a full DRM modeling system similar to the style of control needed by the DAP unit in the ElastIC architecture, relying upon on-chip measurement of voltage, temperature and reliability degradation to make accurate real-time reliability projection.

One drawback to the implementation of a full DRM system attempting to monitor reliability degradation in real-time, is the lack of suitable sensor circuits for directly observing the degradation on chip. In the work by McGowen, the power and temperature on chip are modeled directly, allowing the control system to accurately restrict power and temperature. Full DRM systems require similar on chip monitors for oxide degradation, NBTI and even electromigration to improve the feedback and control loop accuracy for improving system lifetime.

Kim proposes the Silicon Odometer [31] as an on-chip degradation monitor targeting generic delay degradation in digital circuits. The sensor consists of a pair of 105-stage ring oscillators, one of which is "stressed" and the other remains unstressed, that generate a beat frequency representing the difference in delay of the comparable oscillators. The results in this work attribute NBTI degradation for changes in oscillator frequency. The silicon odometer sensor consumes  $265 \times 132 \mu m^2$  in a 130nm process, roughly equivalent to 4900 NAND3 gates in that technology.

Keane introduced a specific sensor for monitoring NBTI degradation [32] utilizing a delay-locked-loop (DLL) to lock to a stressed delay element, outputting a voltage representing the amount of NBTI degradation. In this case, the DLL locking time is potentially too great ( $20\mu s$ ) to detect the maximal amount of threshold shift in the delay element, prior to significant recovery of the degradation. The design is implemented in 130nm technology and consumes 545  $\mu m$  x 255 $\mu m$ , roughly equivalent to 19,300 NAND3 gates.

In Chapter 4, an analysis of the impact of voltage, temperature, process variation and state dependence on oxide breakdown is used to define constraints on the implementation and use of on-chip sensors directly monitoring breakdown mechanisms[33]. Analysis on the quantity of such sensors needed to improve projection of an inherently random breakdown mechanism is addressed. Final results from this work are used to develop 3 novel and effective on-chip reliability monitoring sensors discussed in Chapters 5 and 6.

In Chapter 5, the design of a novel oxide degradation sensor is presented [34]. This sensor is based upon measuring the change in gate leakage current over time as an indicator of oxide degradation. As oxide devices under test are stressed using local supply voltage, the gate leakage current increases with progressive soft breakdown events, mirroring degradation in actual circuits under similar voltage and temperature stress. Based upon the results in Chapter 4, the design is optimized for area and the layout is standard cell compatible. The implementation of the oxide degradation sensor in 130nm technology uses  $7.20\mu m \times 20.86\mu m$ , roughly equivalent to 21 NAND3 gates.

In Chapter 6, a  $2^{nd}$  generation design of a combined oxide degradation and NBTI degradation sensor in 45nm technology is presented. The oxide sensor principle of operation is identical to the design in chapter 5, utilizing gate leakage current change to measure progressive soft breakdown events. The implementation and specifically power consumption is improved significantly over the design in 130nm technology. The NBTI sensor is integrated in the 45nm cell based upon a successful standalone sensor design in 130nm [34]. The NBTI monitor detects the change in oscillation frequency of a ring oscillator current starved by a stressed PMOS device biased in subthreshold. The area for the combined sensor implementation 45nm technology is  $8.5\mu m \times 9.1\mu m$ , roughly equivalent to 54.8 NAND3 gates.

The sensor designs from Chapters 5 and 6 represent enabling circuits for the system architecture proposed in Chapter 3 and the ElastIC architecture. Collectively, the work presented in chapters 2-6 represent a series of circuit and architectural innovations to enable adaptive, reliable system operation on an unreliable silicon platform. The material in chapters 2-5 has been published in top peer-reviewed conferences and journals and was met with positive feedback and commentary.

# Chapter 2

# **Timing Error Correction for On-Chip Memories**

Increasing demand for large, fast on-chip memories has placed growing importance on designing high-speed memories with minimal power consumption while delivering high parametric yields in an era of probabilistic device performance. Traditionally, the least intrusive and safest method for dealing with such uncertainties in circuit performance is to add some timing margin or voltage margin to the design, to ensure operation within this margined specification. Beyond the nominal circuit delay spec or operating voltage, designers must add margin for process variation, high temperatures, supply voltage droop and noise and device degradation and wearout. Recent work on adaptive designs [21, 22] suggests that designers are margining their supply voltage by 17% over the required minimum for typical circuit operation within specifications. From a power perspective, this translates to roughly 30-35% power overhead in margin. Leakage power in these large on-chip memories is significant and designers struggle to minimize leakage during both standby and active modes of operation.

An adaptive system that can reduce the supply voltage to eliminate these margins can provide significant power and reliability benefits. Leakage power decreases roughly cubically with reduction in supply voltage [35]; therefore dynamic supply voltage scaling systems provide a powerful mechanism to control dynamic

and leakage power with reasonable complexity and area overhead (i.e., no need for multiple voltage supplies within the memory array). Additionally, voltage is a dominant (typically exponential) stress factor in most reliability and wearout mechanisms. Any marginal reduction in long-term voltage stress will yield significant reductions in degradation due to mechanisms such as electromigration, oxide breakdown or bias temperature instability effects.

This work presents an approach to dynamic voltage scaling (DVS) for SRAM-based memories that allow aggressive scaling of supply voltage to reduce active power and gate and subthreshold leakage power with a simple, non-invasive sensing scheme, while simultaneously improving the operational lifetime of the circuits by operating at a reduced supply voltage. Conventional DVS techniques are limited to a conservative critical voltage that includes overly pessimistic margins for worst-case process variations and temperature fluctuations [19]. In addition to eliminating voltage margins and process and environmental fluctuations, the proposed circuits also provide a measure of protection from uncertainty due to SRAM access device bitline leakage currents. Exponential growth in leakage current variability is detailed in [35] and threatens to dramatically reduce the number of SRAM access devices per bitline in aggressively scaled process technology.

The proposed approach dynamically converges to a minimum operating voltage through an embedded timing error detection and correction circuit. The SRAM voltage is adjusted in real-time by monitoring the rate of timing errors detected, even allowing operation at sub-critical voltages (voltages below the first timing error incidences) for tradeoffs of error rate vs. supply voltage scaling. A differential voltage

is developed on the bitlines in the SRAM array and a standard latch-type sense amplifier is triggered speculatively by an enable signal generated from a clock edge. After a delay, a second sense amplifier re-samples the bitline to confirm the value, relying upon a larger voltage differential to provide greater confidence in the measurement. If a timing error (an error in the circuit due to insufficient time to evaluate) is detected, the correct data is available one cycle later from the conservatively-clocked sense amplifier. This technique is particularly advantageous considering technology scaling, since (i) intra-die and ambient variations lead to greater safety margins, (ii) interconnect leads to increased delay variability between SRAM banks, and (iii) data-dependent bitline leakage variability reduces certainty in effective read currents. These factors combine to result in overly-pessimistic worst-case design [36].

# 2.1 Timing Error Detection and Correction

A basic requirement to ensure proper operation in a sequential system is to guarantee the proper values are stored and propagated through the intermediate storage elements. Commonly used sequential storage elements rely upon sampling input values at clock edges (clock boundaries). In the proposed single-cycle SRAM, there are two clock boundaries that require delay-error detection and correction circuitry: 1) at the clocked storage element near the input/output (I/O) interface and 2) at the sense amplifier. Existing RAZOR flip-flop circuit structures from [19] can detect and correct timing errors in the signal at the I/O interface clock boundary. The RAZOR storage mechanism consists of an additional delayed-clock latch that resamples the final data to detect transient timing and voltage errors and returns the correct result with a one cycle penalty in the case of an error.

At the sense amplifier output on the read bitpath, two standard differential latch-type (DLT) sense amplifiers [37] are used to "double-sample" the bitline during a read operation in the SRAM. In Figure 2.1, the rising edge of the EN1 signal is generated from the falling edge of the clock to trigger the original sense amplifier. The output of this original sense amplifier is immediately stored in an unclocked S-R latch to guarantee stability of the static output bus during the precharge phase of the SRAM cycle. The rising edge of EN2 is delayed from EN1, while the bitlines in the bank continue to develop more significant differential voltage. As supply voltage is scaled down in the SRAM, the effective read current is decreased and the word-line pulse arrives later due to eroding performance in the decode logic. These effects

**Figure 2.1** Main and Shadow Sense Amplifiers latched and compared via XOR gate and multiplexed to an output bus.

combine to result in a reduced differential voltage present on the bitlines given a fixed amount of time from the beginning of the read cycle. Re-sampling the bitline voltage with a delay from the original sense enable signal allows additional time for the bitlines to discharge and overcome process-variation induced offset voltages, data-dependent leakage currents, and activity-dependent internal voltages in the sense amplifier.

Enable signal pulses are generated from the falling edge of the clock using an inverter delay chain connected to a NAND gate as shown in Figure 2.2. A point on the delay chain is tapped to generate the falling edge of the precharge clock (PCLK) using a NAND gate with the unlatched BANK\_EN signal. This ensures that the delayed pre-charge phase will begin as soon as the enable pulse (EN1) for the sense amp is de-asserted. EN1 is also used to clock the data bus mux enable to prevent XOR glitches from increasing latency. If the output of the error detection XOR is high when the enable signal is de-asserted, the NAND gate in Figure 2.1 will select the output of the second sense amp to be driven on the data bus. The rising edge of EN1 presets the multiplexor to select the output of the main sense amplifier to minimize delay impact.

When a speed path failure is detected at the sense amplifier, the correct value is muxed onto the static data bus. This result will not reach the I/O interface within the clock cycle, but the memory element at the I/O interface is capable of re-sampling the data bus and propagating the correct value via the latching mechanism proposed in [19]. If an error is detected at the latch column or at the sense amplifier block, the

SRAM can return a signal similar to a cache miss in a hierarchical memory system.

The corrected data is forwarded to the system at the end of the second cycle after

**Figure 2.2** Timing signal generation circuits and waveforms. Two-phased timing generation features the precharge path derived from the rising edge of the system clock, and the read path derived from the falling edge of the clock.

the request rather than in one cycle. Many existing systems support hierarchical memory models and would require few changes to include an SRAM with timing speculation.

Delaying the pre-charge phase of the SRAM to accommodate the shadow sense amp requires a 2X increase in pre-charge device and driver sizes in a 64kB 180nm SRAM design. Total area overhead is projected to be less than 8% for an SRAM with similar block sizes and organization. The area overhead is localized near the sense amplifiers; therefore, the overhead is highly dependent upon the cells/sense amplifier. A greater cell to sense amplifier ratio reduces the fractional area overhead due to the proposed dual-sensing scheme. The overall structure of the proposed 32-bit SRAM is detailed below in Figure 2.3. The 64 kB SRAM is divided into 16 rectangular banks subdivided into four 1kB blocks. The I/O buses for the SRAM were routed to minimize wirelength in the routing channels between banks.

In order to explore address-dependent delay, a precharged dual-rail address bus is used to prevent glitching and false evaluate paths without requiring an additional clock boundary in the decode logic. Traditional designs have relied upon clocked decode networks or arrival pulse propagation alongside the address bus to prevent glitching and initiate the read/write sequence. Using the dual rail bus allows simple arrival pulse generation at each bank as the data arrives. Generating the pulse and propagating it along the address bus is another option, but simulations revealed less variability between enable pulse and data arrival when using local pulse generators with the dual-rail bus.

**Figure 2.3** Proposed SRAM floorplan. Uneven buffering on input signals is used to allow banks closer to the I/O interface (9,10,13,14) to initiate read/write paths faster than further banks. Distant banks (0,1,2,3,4,7) have the most significant delay for read and write paths.

# 2.2 Exploiting Address/Data Dependence

Recent commercial SRAM designs consist of many banks spread over great distances on chip. Signal propagation and address decode delays typically dominate cycle times in large SRAM designs [38]. Typical design practice involves building a decode tree that equalizes the nominal delay from the boundary of the SRAM, to each bank. Although this hierarchy of decode provides roughly equivalent delays to each bank, banks in close proximity to the source of the access signals sacrifice performance in their decode network by being driven by the same signal nets with long wires and large drivers as banks that are millimeters away.

In an adaptive design that can detect and correct timing errors, limiting the performance of all portions of the address space to a pessimistic worst-case is neither necessary nor optimal. By using a combination of repeaters and long wire segments throughout the address bus, natural and substantial variation in the path delay between different banks in the SRAM can be exploited. This path delay variability causes portions of the address space in the SRAM to develop timing errors at widely varying supply voltages, allowing portions of the SRAM to continue functional operation at potentially lower voltages than other banks. Generating the arrival/enable pulses as the data arrives allows each bank to complete the read/write operation in the minimum cycle time rather than limiting quicker banks to a slower cycle. This benefits applications with high data access locality. When the SRAM is accessed, most accesses will target addresses from a few banks, allowing the SRAM to tune the supply voltage to the process and interconnect characteristics of the dominant banks in the active data set.

Beyond the benefits of exploiting address dependence in memory access, timing error correction allows a relaxation of the constraints placed by a pessimistic worst-case data state on a particular bitline. Bitline leakage depends upon the data stored in each cell connected to the bitlines. In addition to process-related variability, leakage currents dependent upon stored data influence the effective read currents of SRAM cells [39], particularly for long bitlines preferred for dense array designs. The bitline re-sampling technique allows designers to avoid margining for infrequent data storage patterns that lead to the worst-case read current. The shadow sense amplifier allows a speculative sensing phase with the detection/correction to maximize the cycle times of the SRAM in the presence of leakage-induced read current variability.

### 2.3 180nm Simulation Results

To evaluate the effectiveness and explore the trade-offs inherent to the shadow-sense amplifier, a 64 kB single-cycle SRAM was designed in 0.18um CMOS technology. Simulation results confirm that the SRAM operates at 250 MHz with worst-case device and interconnect models at 85°C with a 10% margin on the 1.8V supply. Under typical process conditions at 25°C the design approaches 400 MHz operation. The shadow sense amplifier is clocked with sufficient delay to reliably detect timing errors down to 1.3V in the worst-case corner at 250 MHz. Increasing the delay between sense amplifier enable signals decreases the minimum safe operating voltage, but increases the area penalty through a larger delay element and tighter constraints upon the pre-charge phase timing of the memory. Delay beyond 500ps between sense amplifier enable signals requires pre-charge logic differentiating read and write operations, allowing early precharge following a write.

Detailed variability simulations including parasitic models of the SRAM considering physical design were used to determine failure voltages for each SRAM bank. The variability model was adapted from industry-provided SPICE models and includes individual intra-die Gaussian distributions for W, L, and Vth and inter-die Gaussians for W, L,  $V_{th}$ ,  $R_{dsw}$ ,  $\mu_0$ , and  $T_{ox}$ . Each bank of the SRAM was simulated with a fixed set of inter-die variation (-1 $\sigma$  was used) and intra-die variation for devices (-2 $\sigma$  to +2 $\sigma$ ). Gaussian variations were generated for each relevant device, in each bank and combined to compose a "chip" for simulation purposes.

Figures 2.4 and 2.5 detail the timing error-rate vs. supply voltage with the SRAM used as a direct-mapped cache running memory traces obtained from 11 SPEC2000 benchmarks run on the SimpleScalar/Alpha v3.0 toolset [40]. The memory traces

**Figure 2.4** Error rate of memory as VDD reduces for gap00 memory trace. Four traces represent sets of intra-die variation with inter-die fixed at slow corner. Power both with and without recovery overhead is shown.

**Figure 2.5** Error rates for a set of benchmarks vs. supply voltage. Fixed "slow corner" inter and intradie variation. Error rate increases in discrete intervals since the variation in access time is dominated by the physical location of the bank accessed. In 180nm technology, very little within bank variation contributes to significant cycle time variation.

consisted of 10 million simulation cycles taken from an optimal point within the program execution to deliver typical memory access patterns using the Early SimPoint method [41]. Figure 2.4 displays the error rate on a trace of the gap00 benchmark for four different worst-case inter-die SRAMs defined by the Gaussian intra-die variability model described above. Figure 2.5 shows the impact of memory access patterns on error rate for a given chip. Applications with high data access locality (e.g., gzip) will exhibit dramatic fluctuations in error rate, while applications with lower data access locality (e.g., gap) will demonstrate frequent gradual increases in error rate as the voltage is lowered. Figure 2.6 is a trace of 100M cycles of SPEC benchmarks showing instantaneous voltage and error rates using a simple voltage control algorithm that updates every 10,000 cycles. The supply voltage ranges over 100mV during operation for a target error rate of 2%. Error rates surpass 2% in many instances due to the simple ± 10mV control algorithm.

In Table 2.1, the error detection/correction circuitry allows an SRAM design at the worst-case inter-die corner to operate at 1.55V at 85°C with a zero error rate and 1.5V with 5% error-rate, as compared to the 1.8V supply for an SRAM without error detection and with a safety margin, saving 12% and 17% power, respectively, after considering the overhead of the additional circuitry and reducing the voltage stress on the entire circuit by 200-250 mV. Without an additional voltage safety margin, the SRAM operates at 1.62V in the worst-case corner. At operating temperatures less than 85°C, the SRAM adjusted to 1.45V at 50C or 1.39V at 30°C, saving 23% and 29% power, respectively, over a margined design operating at a fixed 1.8V. A typical part (i.e., not at the worst-case inter-die corner) can be operated at 1.3V

VDD, achieving up to 35% power savings over a conservatively margined SRAM and also significantly lowering reliability degradation due to NBTI/PBTI and oxide breakdown mechanisms. Static power, while not appreciable for this technology, is sensitive to supply voltage with both gate and subthreshold leakage benefiting from lower operating voltages and corresponding reduced ambient temperatures [35].

**TABLE 2.1**Power Consumption at Various Operating Points

| Operating Point                         | VDD   | Total  | Static  |

|-----------------------------------------|-------|--------|---------|

| Single Sense Amp, WC, 85°C              | 1.80V | 76.5mW | 16.30μW |

| Single Sense Amp, WC, 85°C              | 1.62V | 64.3mW | 13.60μW |

| Dual Sense Amp, WC, 85°C (Zero Errors)  | 1.55V | 67.8mW | 12.60μW |

| Dual Sense Amp, WC, 85°C (5% Errors)    | 1.50V | 63.8mW | 11.90μW |

| Dual Sense Amp, WC, 50°C (Zero Errors)  | 1.45V | 58.9mW | 5.56μW  |

| Dual Sense Amp, WC, 30°C (Zero Errors)  | 1.39V | 54.0mW | 3.92μW  |

| Dual Sense Amp, TYP, 85°C (Zero Errors) | 1.30V | 49.4mW | 16.00μW |

All power results for dual sense amplifiers include overhead for the required signal generation, circuitry and increased pre-charge device sizes.

**Figure 2.6** Instantaneous supply voltage and error rate during 10M cycle DVS simulation with varying workload. Uses error counter with  $\pm$  10mV  $V_{DD}$  update every 10000 cycles over 10 benchmarks.

# 2.4 130nm Physical Implementation

A 130nm testchip from an industrial foundry has been designed and fabricated, including a 36kB SRAM containing a prototype implementation of the proposed time redundancy technique. The implementation of the test chip is based upon a fully functional, industry-designed 32kB SRAM verified to operate across voltages from 0.9V to 1.5V. The original SRAM, detailed in [42], was designed using 4 levels of metal and it consumed around 1.7 mm² of silicon area. The 36kB test chip containing an implementation of the time redundancy circuitry is around 2.25 mm², a 32% increase in array area; although the test array contains 12.5% more 6T SRAM cells in the increase from 32kB to 36kB. The specific components driving the additional increases in area are discussed below during description of the hierarchy of the SRAM and selected implementation-specific design issues.

The smallest segment of the initial design, the local block, contains 32 rows of SRAM cells 16 bits wide, including adjacent timing generation circuitry and pitch-matched write drivers and sense amplifiers devoid of any column multiplexing. The relatively short bit-line (32b) and word-line (16b) limits the skew between the word-line pulse and the sense amplifier enable signal and greatly reduces bit-line delay variability due to access transistor leakage currents. Reducing the sub-array size and eliminating column multiplexing transistors, discussed in [42], are alternative techniques for reducing the delay variability present in the SRAM design and presents a similar drawback to the proposed technique, leading to area overhead and reduced array efficiency. Despite the already small sub-array size and lack of

# GLOBAL COLUMNS 6T LSA LSSA GSA GSSA GSSA GSSA GSSA

**Figure 2.7** Array Architecture and Output Path. Each of 4 macros provides 18b of data. A macro is divided into 16 global columns and each global column into 4 sub-arrays. Sub-arrays contain 32 rows and 36 columns. Local Shadow SA connects to Global Shadow SA to separate output bus to shadow latch.

column multiplexing, the time redundancy circuits were added to the design in an effort to evaluate any potential improvements in delay variability related errors.

The original design includes 4 local blocks containing local sense amplifiers each connected to a global sense amplifier at the bottom of each global column. For the purposes of testing the output of both sense amplifiers before error detection via the scan chain, the output of the local shadow sense amplifier is connected to the input of a global shadow sense amplifier which drives a separate output bus connected to the shadow latch portion of the output latch bank. Figure 2.7 illustrates the configuration of the local and global sense amplifiers and the output latch bank. Since the design is limited to 4-levels of metal, this led to the first challenge associated with integrating the shadow sense amplifiers and routing their output through the congested metal tracks through the global column. No additional wiring tracks were available to support the shadow sense amplifiers, since M2 tracks contained local bit-lines and M4 contained global bit-lines and no column multiplexing was implemented.

A novel method of 2:1 column multiplexing is used to create an additional M4 wiring track for the outputs of the shadow sense amplifier, while avoiding adding pass transistors traditionally used in column multiplexing schemes. As Figure 2.8 illustrates, the cross-coupled PMOS devices in the sense amplifier are shared between separate matched pairs and footers connected to adjacent bit-line pairs. Each matched pair is activated by separate enable signals routed horizontally in M1, guaranteed that only one of the two enable signals can be activated in a given cycle. The shadow sense amplifiers are column muxed in the same manner and now can

**Figure 2.8** Sense amplifier and integrated 2:1 column multiplexer and layout of new local block showing area overhead of "RAZOR" or shadow sense amplifiers.

connect to a global bit-line in the M4 level adjacent to the output of the conventional sense amplifier pair. A similar design modification is necessary to allow the write drivers to multiplex two bit-line pairs. With this scheme, each local block would produce 9 bits of output rather than the 18 bits the SRAM required. Rather than adding to the width of the word-line to increase the output of each local block, the local block was copied, including word-line drivers and timing generation logic, and mirrored to produce a new larger local block seen in Figure 2.8. This technique allowed each new local block to generate 18 bits of output without requiring a redesign of the timing generation and word-line driver circuits that would invalidate the previous measured functionality of these circuits.

Combining two local blocks to form a new local block and incorporating the 2:1 column multiplexing requires some alterations to the address decode network in the SRAM. Formerly, 16 global columns created a half-quad in the SRAM and the four "G" address bits selected the global column to access. Reducing the 16 global columns to 8 global columns allows G<0:2> to be utilized to decode the global column enable signal, freeing G<3> to be used to control the column multiplexing scheme. Previously, 3-input NAND structures were used to generate static, partial global column enable signals from G<2:3> and B<0> address bits. The same structures are used with the new decode network by holding the input to the G<3> at "1" and generating the global column enable signal from only G<2> and B<0>. This simple alteration imposes minimal timing changes on this signal and the selection of signal G<3> to be removed from the global column select path ensures there is no

impact on the more critical pulsed G<0:1> path that controls both edges of the wordline and sense amplifier enable pulses.

Routing an additional output bus for the signals from the shadow sense amplifier path required increasing the width of the channel between half-quad blocks by around 10um. Gaps in the data input driver path can be seen where bit width was decreased from 18b to 9b per half global column as seen on the left and right edges of Figure 2.9, directly adjacent to the global block output drivers. The standard output bus is connected to the DIN input of the bank of output latches and the shadow output bus is connected to the RIN input of the output latches, corresponding to the shadow latches. Figure 2.9 illustrates the configuration of the output latch enabling input of two signals to produce one corrected output.

In Figure 2.9, the DIN signal is provided from the conventional sensing bit-path and RIN is the output signal provided at a later time from the shadow sense amplifier path. B\_CLK and C\_CLK are used to latch the signal from DIN, and the delayed version of each clock, B\_CLK\_DEL and C\_CLK\_DEL are used to latch the laterarriving RIN signal. When C\_CLK is high the latch is transparent and data flows through and the rising edge of C\_CLK\_DEL clock presets the output of the multiplexer to the output of the conventional bit-path data latch. If the DIN and RIN signals differ after C\_CLK\_DEL falls, the multiplexer is switched to transmit the data from the late arriving signal. This mechanism allows the later arriving signal to be forwarded to the next stage in the pipeline following the SRAM. In this implementation of the SRAM, the correction circuitry in Figure 2.9 is designed to allow use of the standard library latches and gates without manual design efforts.

**Figure 2.9** Output latch with added shadow latch and error correction and detection circuitry. Layout of the routing channel containing drivers for the additional output bus from the shadow sense path.

The multiplexer in the diagram, which is the only significant source of delay overhead, can be relocated to an internal feedback path in the conventional latch itself, to reduce the delay impact to only capacitive loading effects on internal latch nodes. In [19], a latch designed in this manner is presented and shown to cause a minimal impact on the D-Q delay path in the latch.

In this implementation of the proposed technique, altering the timing generation of the word-line and conventional sense amplifier enable signal is avoided to maintain the integrity of the reference SRAM design. The shadow sense amplifier enable signal is delayed from the initial sense amp enable signal with 5 inverters and a nand gate, which effectively creates a 90ps delay between enable signals at 1.5V supply and an 850ps delay between enable signals at 0.6V supply. This delay was set partially by area and time constraints in the layout and due to the realization that the goal of this test chip was to demonstrate the potential to capture delay errors using the technique rather than designing the entire system to exploit the traits of the time redundancy technique. Each successive enable signal in the output path of the shadow sense amplifier is delayed using an equal length and size delay chain to develop the delay required to accommodate the late-arriving shadow sense output signal.

Additional structures are added to count the number of errors detected at the output latch bank and to compress the output patterns from multiple cycles into a readily comparable signature (MISR).

# 2.5 130nm Simulation Results

This section presents some basic variability analysis of the SRAM cell in 130nm and 45nm process technologies, followed by a brief summary of findings from some simulations covering a fraction of the variability space in the local bank of the designed test SRAM.

Figure 2.10 shows the wide range of SRAM read currents possible at 1.1V supply, ranging from normalized values of 1.00 to 3.00, yielding variations of greater than 43% from the average read current value over a Monte Carlo sample of 30,000 cells. The complete 36kB SRAM contains nearly 300,000 SRAM cells making it likely to encounter read current variations greater than +/- 3 $\sigma$  from the mean. The Monte Carlo simulation was conducted using HSPICE BSIM4 and PSP models including variability modeling for 130nm and 45nm process technologies. SRAMspecific device models are used in the SPICE simulation to provide the best possible simulation-based prediction of actual read current variation. Designing the read bitpath to accommodate the outlying read currents from this distribution leads to a sacrifice in read delay that the proposed technique aims to improve by allowing more aggressive timing of the sense amplifier enable signal. When scaling supply voltage from 1.5V to 0.6V there is a slight upward trend in the ratio of standard deviation to mean read current, representing an increasing opportunity to achieve performance or reliability lifetime improvement via the time redundancy technique at lower supply voltages.

Figure 2.10 Distribution of Read Current for 130nm and 45nm technologies.

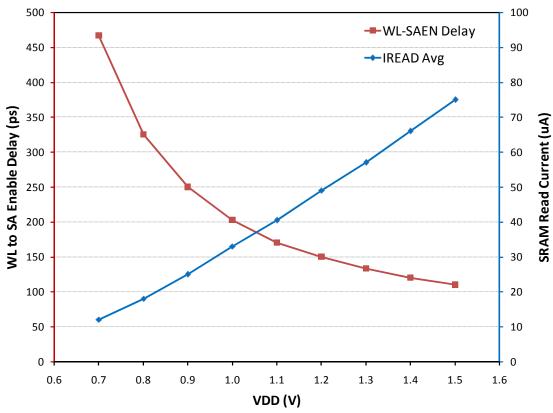

**Figure 2.11** SRAM Read Path Timing and Read Current scaling with VDD for 130nm technology. As supply voltage is decreased, the word-line to sense amp enable delay increases rapidly.

Figure 2.11 depicts the scaling of read current and the delay between word-line assertion and the sense amp enable pulse as power supply is decreased. The average read current decreases from 75.2  $\mu A$  at 1.5V to 11.9  $\mu A$  at 0.6V – a decrease of ~6.3X. The sense amp enable delay increases from 109 ps to 468 ps – an increase of nearly ~4.3X. This slight discrepancy in scaling reveals that in order to provide robust operation at low voltages near 0.7V, the design includes unnecessary timing margin at the higher range of the voltage scale. Unfortunately, this situation indicates that reducing supply voltage will be a less effective way of stimulating delay errors during testing of the SRAM including the time redundancy circuits. Scaling the cell supply voltage separately from the peripheral supply voltage was explored as a technique to degrade the read current of the SRAM

intentionally in an effort to ease the measurement and evaluation of the proposed technique. As the difference between cell supply voltage and peripheral supply voltage increases, the internal "0" storage node voltage during a read increases proportionally and results in read stability errors in simulation before effecting sufficient reductions in read current to allow more effective delay error detection with the proposed circuits.

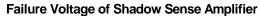

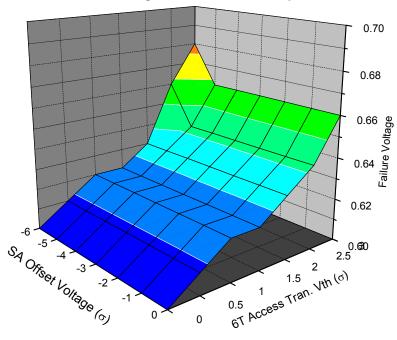

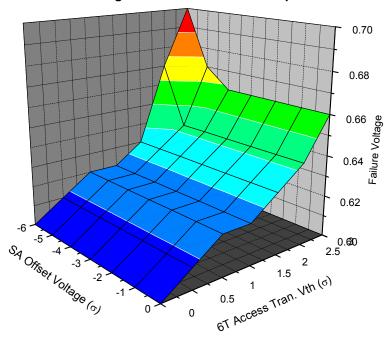

Transient simulations of the fabricated design of the test SRAM were conducted exploring the variability space including threshold voltage variation in access transistors, sense amplifier offset voltage variation and bit-line capacitance variation. Combinations of sense amplifier offset variation and access transistor threshold voltage variation showed the only positive results in which the shadow sense amplifier is noticeably more robust and scales to lower voltages than the conventional sense amplifier. Only with  $+2.5\sigma$  to  $+3\sigma$  increase in access transistor threshold mismatch and very unlikely values of  $-6\sigma$  sense amp offset variation did the shadow sense amplifier catch any delay errors. The failure voltages of each sense amplifier are plotted below in Figure 2.12, against sense amp offset voltage variation and access transistor variation.

Figure 2.12 summarizes the outlook for the proposed technique in the test SRAM. Comparing the minimum operating voltage of each memory, the failure voltages are very similar across the range of variation in access transistor and sense amplifier offset. Only in very extreme cases of variation in access transistor threshold mismatch and sense amplifier offset can the shadow sense amplifier provide any voltage margin prior to complete failure. Finding such a combination of

# Failure Voltage of Conventional Sense Amplifier

**Figure 2.12** Minimum operating voltages for various combinations of threshold voltage variation for the implemented design of the time redundancy test chip.

pessimistic variations in hardware, if possible, is extremely difficult with limited testing time. Many failures in Figure 2.12 are the result of the inability to write to the SRAM cell with the high levels of variation in 6T access transistor threshold voltage.

The design of the local sense amplifier in the original SRAM contributes to the inability of the proposed redundancy technique to provide additional reliability. The sense amplifier is weakly cross-coupled by only PMOS devices and the footer device is roughly 1/6<sup>th</sup> of the width of the devices in the matched NMOS pair. These factors cause the sensing time of the amplifier to be relatively slow and allow a great noise margin, allowing incremental discharge of the bit-line during the enable signal pulse to contribute to the final amplification. The weak cross-coupling in the sense amplifier prevents the amplifier from accelerating the sensing of the voltage differential when read current is greatly reduced, since the PMOS devices are nearly never out of subthreshold conduction in these situations. Previous work on this technique studied the behavior of a strongly cross-coupled sense amplifier with a larger footer device, which leads to a sensing operation that amplified the voltage differential on the bit-lines detected at the beginning of the enable pulse, rather than the slower sensing scheme used in this SRAM.

# Chapter 3

# **Reliability Modeling and Management**

Traditional stress-based reliability qualification techniques, such as the JEDEC JESD-47 Standard [12], qualify designs by stressing sample systems under pessimistic environmental conditions with a zero failure pass/fail criteria. While the traditional approach is an accepted method of ensuring reliability, the limits it places on supply voltage and temperature leave a significant and increasing reliability margin between circuit performance at worst-case conditions and at typical conditions. Widely varying environmental conditions linked to portable products combine with dynamic power reduction techniques to exacerbate the limitation of this conventional worst-case qualification methodology.

Hence, the need for alternative approaches to ensuring lifetime reliability under dynamic operating conditions is clear. Knowledge-based risk assessment is one alternative to simplistic corner-case stress testing that increases the complexity of qualification considerably. The knowledge based approach (a framework for knowledge-based qualification is defined by JEDEC JESD-34 [15]) requires careful characterization and analysis of individual failure modes to assess a reasonable system reliability risk factor given the reliability targets for the system. In this paper, we propose the use of so-called dynamic reliability management (DRM), where real-

time workloads and thermal information provides accurate inputs to real-time knowledge-based reliability models for projecting the degradation caused by various failure mechanisms. We then use the projected failure probability to control the maximum voltage assigned by a dynamic voltage scaling (DVS) algorithm.

**Figure 3.1** Reliability Degradation over time. Typical usage profile results in less degradation than a worst-case usage profile mandated by traditional qualification methods published by JEDEC.

The concept of DRM is conceptually motivated in Figure 3.1. The line labeled worst-case profile shows the accumulated damage due to a failure mechanism, such as oxide breakdown, over a 10 year time span under worst-case operating conditions (maximum operating frequency, voltage and ambient temperature). In traditional analysis, the maximum supply voltage is set such that at the accumulated damage at the 10 year mark results in a failure probability that meets the specified constraint (such as 63.2%, or 1-e<sup>-1</sup>). However, performance traces collected from an actual desktop processor show that the processor spends over 85% of its time in low power or sleep modes where the incurred damage rate is significantly lower. The accumulated damage from such typical usage is shown in Figure 3.1 with the line labeled typical profile and results in a much lower final damage at the 10 year mark.

Hence, the failure probability for this typical usage is well below that of the specification and the maximum allowed operating voltage was unnecessarily constrained resulting in a loss of potential performance.

Since the maximum supply voltage is currently set at design time or during post-fabrication testing, worst-case conditions must be assumed. It is becoming increasingly difficult to anticipate the actual usage of a part in order to construct reasonable worst-case corners for qualification. Under DRM, however, it is possible to dynamically monitor the operating voltage and temperature during part operation. With this operating condition history we propose the use of failure mechanism models to project the expected reliability and dynamically adjust the maximum supply voltage available to a DVS algorithm such that the required reliability constraint is met while the delivered processing performance during peak demand is maximized. DRM has the added potential benefit of theoretically allowing a user to select a desired lifetime or degradation envelope, post-fabrication. Furthermore, DRM provides designers and architects with the ability to control lifetime reliability independently for individual projects in a manner that is transparent to the manufacturing technology.

The concept of DRM was first introduced in [26] using a sum of failure rates method while considering multiple reliability mechanisms. Lu and co-authors [27] analyzed electromigration effects and suggested dynamic thermal management (DTM). However, both approaches focus on short time scales that are not indicative of realistic reliability requirements, and more critically do not propose an actual control system required to obtain performance gains.

In this chapter, we explore a DRM framework for digital logic using physics-based failure models for oxide breakdown, electromigration, thermal cycling and NBTI expressed as incremental damage mechanisms using a linear cumulative damage model referred to as Miner's rule [43]. The reversibility of NBTI damage is modeled and lifetime projection and the recovery effect on achievable system performance are explored. The performance impact of DRM in systems with DVS control techniques is analyzed with a focus on macro-level user collected processor usage profiles rather than traditional benchmark applications. The DRM system sets a maximum supply voltage based on the degradation characteristics modeled during operation, and exceeds the nominal supply voltage when possible while meeting the required reliability lifetime constraints. With the proposed implementation of a specific DRM control algorithm, this work demonstrates and quantifies the potential performance improvements of DRM utilizing dynamic voltage scaling.

This chapter is organized as follows: In 3.1, the adapted reliability models used to estimate failure rates under variable conditions are described. In section 3.2, the projection of failure rate at a desired lifetime using inputs from the reliability models is explored. In 3.3, The DRM control system that enables operation beyond nominal voltages is discussed and the simulation setup and results are presented. Finally, a summary of the simulation results and contributions of the work completes this chapter.

# 3.1 Reliability Modeling

In order to implement a real-time dynamic reliability management scheme, we require accurate models that can comprehend dynamic stress behavior with minimal

computational expense. High level compact models for oxide breakdown, electromigration and thermal cycling are addressed in the following sections. The models are adapted from state-of-the-art physics of failure work and applied to real-time DRM. In our proposed approach, we cast all reliability models such that they express wear-out in terms of an accumulated damage, or fraction of lifetime consumed. This approach allows simple projections of the failure rate at the desired lifetime and is key to the efficient computation of total failure probability which drives the proposed DRM control method. It also allows the use of degradation dependent models for each reliability mechanism, a capability that is lost when dealing directly with probabilities.

### Oxide Breakdown

Oxide breakdown, or dielectric breakdown, is a degradation mechanism that results in a low-impedance path through an insulating or dielectric barrier. During normal operation, each electron passing a dielectric barrier has a small probability to enter a high-energy state to tunnel through the insulating layer. Defect paths in the dielectric barrier reduce the energy level required for conduction through the layer, and therefore increase the probability that electrons will travel through the layer.

Each tunneling charge has a small probability of creating a defect when passing through the oxide. This probability of defect generation is the wear-out mechanism for thin dielectric films. When a critical defect density is reached, there is a high probability that a low-impedance defect path exists in the oxide and a runaway current path through the insulating film will develop. The exact microstructure and nature of the defects is not well understood and less than 1% of defect paths