# A CLOSED-LOOP DEEP BRAIN STIMULATION DEVICE WITH A LOGARITHMIC PIPELINE ADC

by

Jongwoo Lee

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 2008

Doctoral Committee:

Professor Daryl R. Kipke, Co-chair Associate Professor Michael P. Flynn, Co-chair Emeritus Professor David J. Anderson Assistant Professor David Wentzloff © Jongwoo Lee

2008

To Mom and Dad

## Acknowledgements

In the process of writing this dissertation, any single work was impossible without the inestimable support of many special people. I am deeply grateful to my research advisors Prof. Daryl Kipke and Prof. Michael Flynn for their encouragement and support. I want express my appreciation to all the other committee members, Prof. David Anderson, and Prof. David Wentzloff for their invaluable suggestions and time. I thank the Samsung Scholarship Foundation for the financial support for the entire Ph.D. period, and I also appreciate the support of WIMS ERC and the Catalyst Foundation.

I am deeply indebted to the people at the neural engineering laboratory for their supportive advice and the cordiality: Dr. Matt Johnson, Dr. Kevin Otto, Dr. David Pellinen, Dr. Jeyakumar Subbaroyan, Dr. Mark Lehmkuhle, K.C. Kong, Mohammad Reza Abidian, Nick Langhals, Rachel Miriani, Eugene Daneshvar, Greg Gage, Matt Gibson, Kip Ludwig, Tim Marzullo, Taegyun Moon, Hirak Parikh, Erin Purcell, John Seymour, Azaheh Yazdan, Takashi Yoshida, and Karen Coulter.

I thank all former and current members of Prof. Flynn's group for their assistance with their friendship: Dr. Jia-yi Chen, Dr. Sunghyun Park, Dr. Junhyung Park, Dr. Ivan Bogue, Dan Shi, Joshua Kang, Mark Ferriss, Shahrzad Naraghi, Andres Tamez, Chun Lee, Jorge Pernillo, David Lin, LiLi Lim, and Hyo-Gyuem Rhew.

I am grateful to my beloved family - father, mother, and my brother John for their love, encouragement, and prayer. I thank people at the Korean United Methodist Church, especially to Rev. Isaac Shin, Dr. Joseph Won, Rev. Kisang Jun, Jason Um, Allison Kim and Jungho Lee. Thanks must also go to the hundreds of friends and teachers, who shaped my life and helped me learn the truth of life. Above all I thank God for His grace and providence.

# **Table of Contents**

| Dedication                                                     | ii  |

|----------------------------------------------------------------|-----|

| Acknowledgements                                               | iii |

| List of Figures                                                | vii |

| List of Tables                                                 | xi  |

| List of Abbreviations                                          | xii |

| Abstract                                                       | xiv |

| Chapter                                                        |     |

| I. Introduction                                                | 1   |

| 1.1. Biological background                                     | 1   |

| 1.2. Deep brain stimulation (DBS) system                       | 6   |

| 1.3. Proposed closed-loop deep brain stimulation (CDBS) system | 10  |

| 1.4. Dissertation outline                                      | 15  |

| II. Micro-scale implantable neural interface                   | 16  |

| 2.1. Hybrid integration of neural probes                       | 16  |

| 2.2. Switched-capacitor amplifying filter                      | 21  |

| 2.3. Prototype implementation                                  |     |

| III. Logarithmic ADC                                           |     |

| 3.1. Logarithmic pipeline architecture                         | 41  |

| 3.2. Logarithmic ADC implementation      |     |

|------------------------------------------|-----|

| 3.3. Prototype measurements              | 62  |

| IV. Closed-loop Deep Brain Stimulator    | 68  |

| 4.1. Closed-loop DBS device architecture | 68  |

| 4.2. Circuit implementation              | 72  |

| 4.3. Prototype measurements              | 79  |

| V. In-vivo neural test                   | 89  |

| 5.1. Benchtop prototype                  | 89  |

| 5.2. Wearable device                     | 94  |

| VI. Conclusion and future work           | 103 |

| 6.1. Conclusion                          | 103 |

| 6.2. Future work                         | 106 |

| BIBLOGRAPHY                              |     |

# List of Figures

| Figure 1.1: A simplified schematic of the neural connections [3]                      |

|---------------------------------------------------------------------------------------|

| Figure 1.2: The basal ganglia loops [4]                                               |

| Figure 1.3: Placement of the DBS probe into STN [14]                                  |

| Figure 1.4: Soletra neurostimulator and DBS lead [18]                                 |

| Figure 1.5: Placement of the Medtronic DBS <sup>™</sup> system [19]7                  |

| Figure 1.6: Prototype model of the first CDBS system                                  |

| Figure 1.7: Block diagram of the proposed CDBS system                                 |

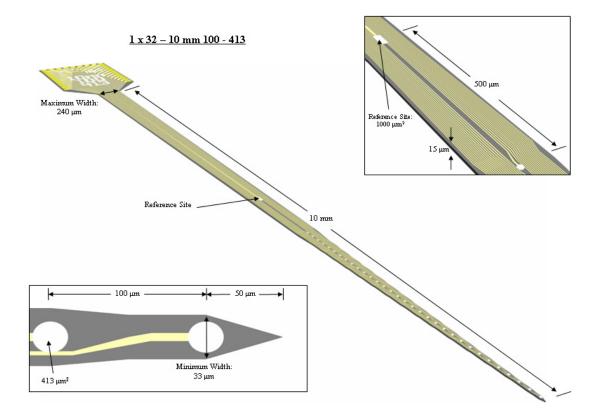

| Figure 2.1: Neural microprobe (NEL, U of Michigan) [46]17                             |

| Figure 2.2: 32-channel silicon-substrate probes for DBS [54] 20                       |

| Figure 2.3: Basic architecture of the proposed system                                 |

| Figure 2.4: The simplified equivalent electrical model of the neural probe included a |

| spreading resistance (Rsp), faradaic electrode resistance (Re), non-faradaic          |

| electrode capacitance (Ce), probe trace resistance (Ri), and shunt capacitance        |

| (Cp)                                                                                  |

| Figure 2.5: General band pass amplifier                                               |

| Figure 2.6: Resistor emulation with switched capacitor circuit                        |

| Figure 2.7: $1/f$ noise rejection by modulation with a switched capacitor circuit     |

| Figure 2.8: Low <i>Q</i> bi-quad with differential switched capacitor circuit         |

| Figure 2.9: Frequency response of the low <i>Q</i> bi-quad                                |

|-------------------------------------------------------------------------------------------|

| Figure 2.10: High $Q$ bi-quad implemented with a differential switched capacitor circuit  |

|                                                                                           |

| Figure 2.11: Frequency response of the high $Q$ bi-quad                                   |

| Figure 2.12: Die photograph of the fabricated device                                      |

| Figure 2.13: Original neural signal                                                       |

| Figure 2.14: <i>In-vitro</i> test output with low- <i>Q</i> bi-quad                       |

| Figure 2.15: <i>In-vitro</i> test output with high <i>Q</i> bi-quad                       |

| Figure 2.16: A single spike at the high- <i>Q</i> bi-quad output                          |

| Figure 3.1: Image quality comparison for standard image [70] with 3 bit linear and 3 bit  |

| logarithmic coding                                                                        |

| Figure 3.2: Companding characteristics of 5 bit logarithmic quantization                  |

| Figure 3.3: 6 bit logarithmic characteristics for three values of code efficiencies, C 42 |

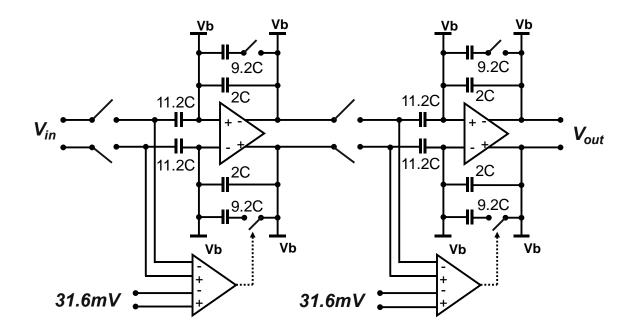

| Figure 3.4: Implementation of the logarithmic pipeline                                    |

| Figure 3.5: Logarithmic ADC residue plots                                                 |

| Figure 3.6: 1.5 bit residue plot and error due to finite gain                             |

| Figure 3.7: Input-referred systematic gain error due to finite OpAmp gain for a 1.5b      |

| logarithmic stage                                                                         |

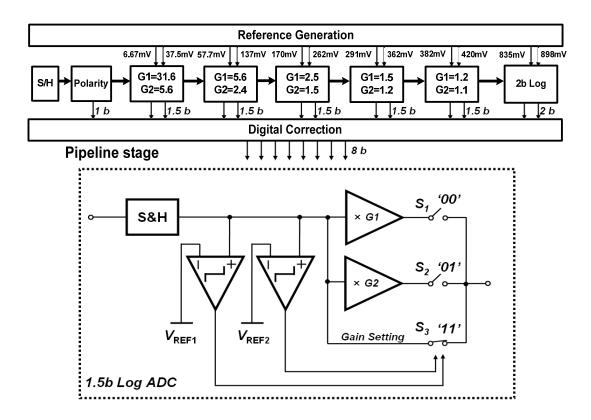

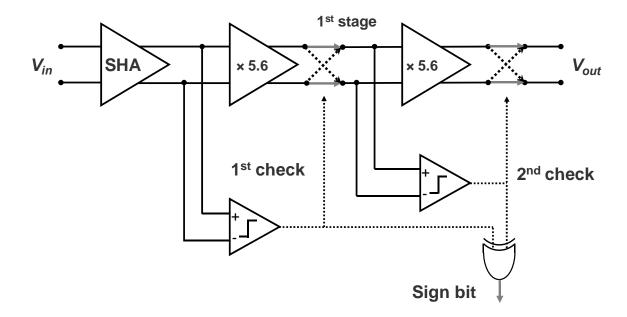

| Figure 3.8: Logarithmic ADC architecture                                                  |

| Figure 3.9: Logarithmic ADC stage                                                         |

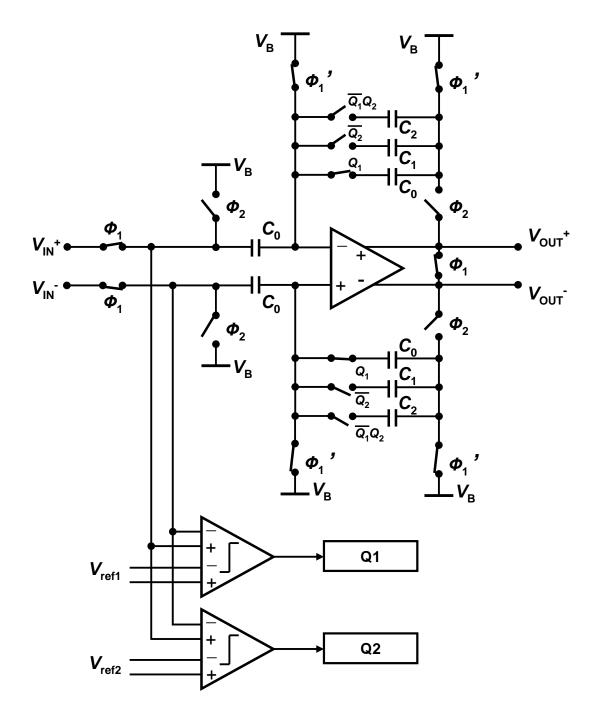

| Figure 3.10: The first pipeline stage is comprised of a cascade of two SC amplifiers 58   |

| Figure 3.11: Polarity decision                                                            |

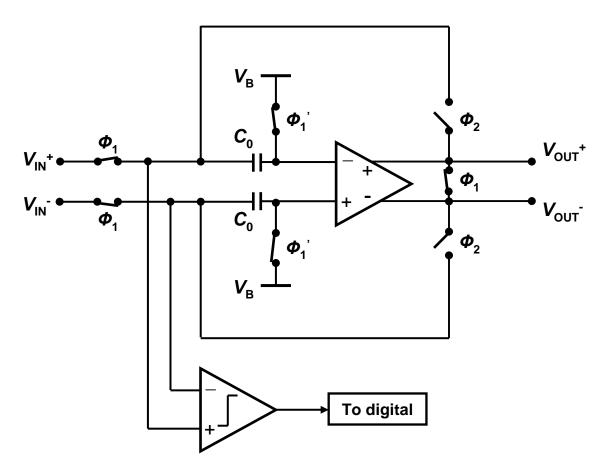

| Figure 3.12: Sample and hold circuit, and first polarity check comparator                 |

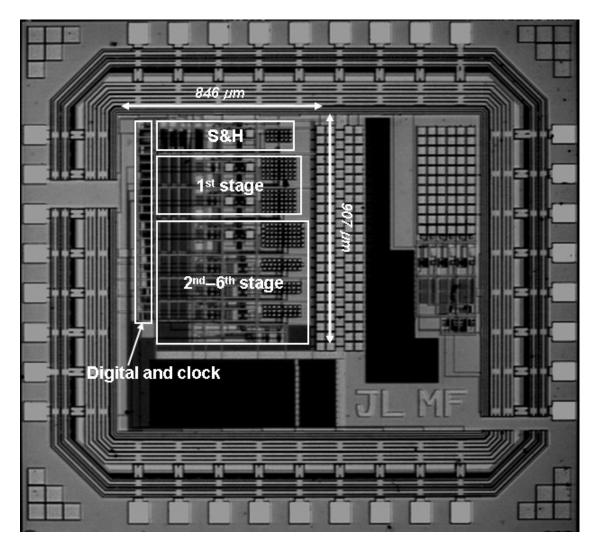

| Figure 3.13: Logarithmic ADC die micrograph.                                      | 62      |

|-----------------------------------------------------------------------------------|---------|

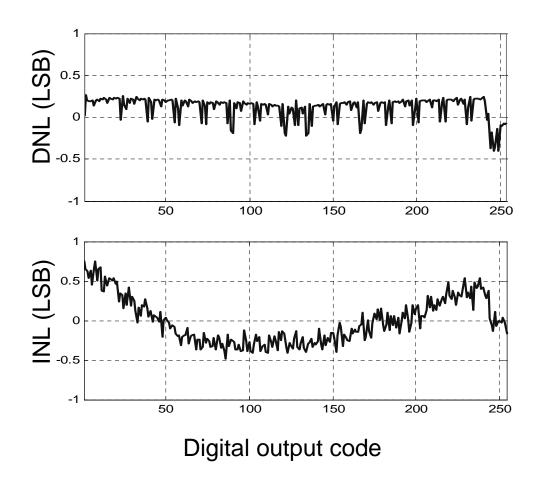

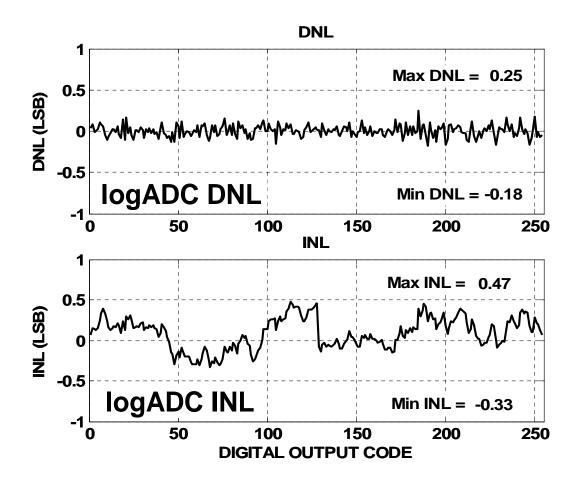

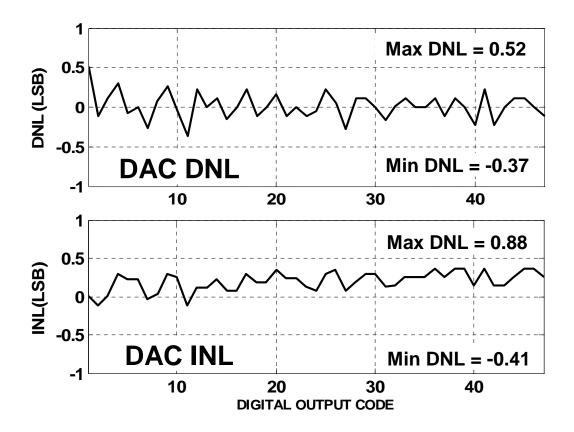

| Figure 3.14: Measured DNL and INL of logarithmic ADC.                             | 63      |

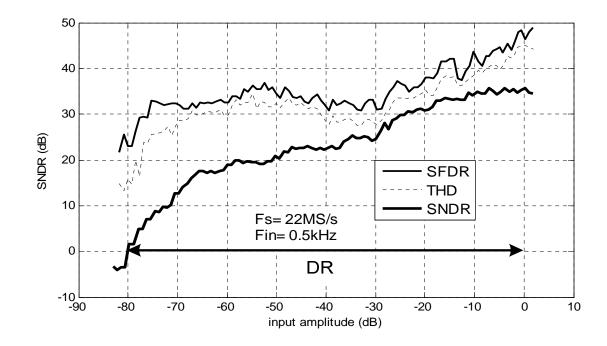

| Figure 3.15: Measured SNDR, SFDR, and THD versus input amplitude                  | 64      |

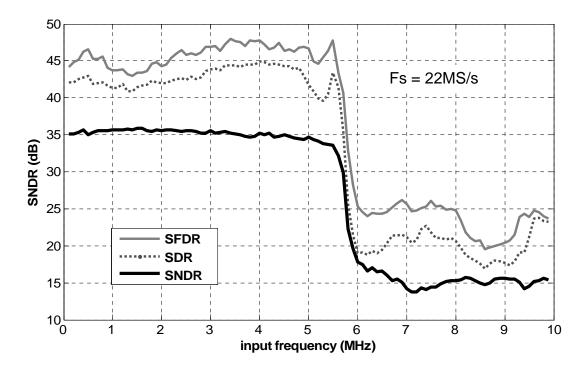

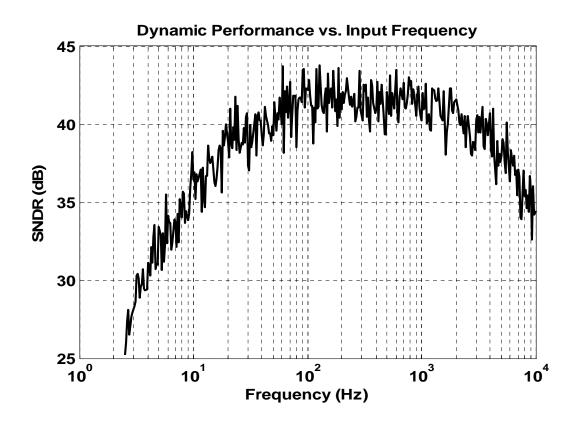

| Figure 3.16: Measured SNDR, SFDR, and THD versus input frequency.                 | 65      |

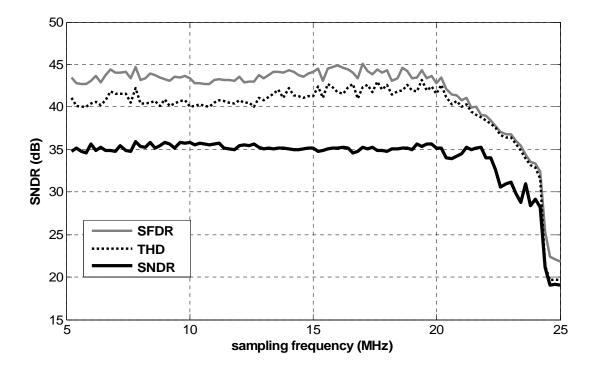

| Figure 3.17: Measured SNDR, SFDR, and THD versus sampling frequency               | 65      |

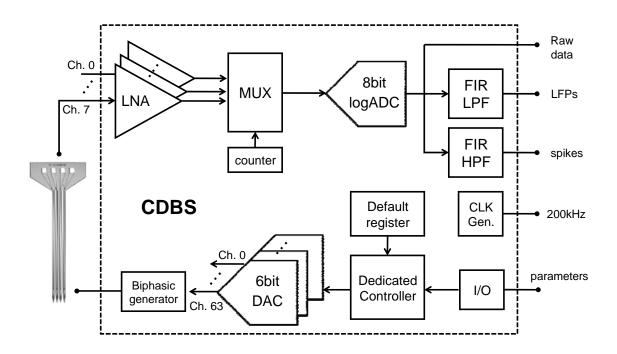

| Figure 4.1: The system architecture of CDBS.                                      | 69      |

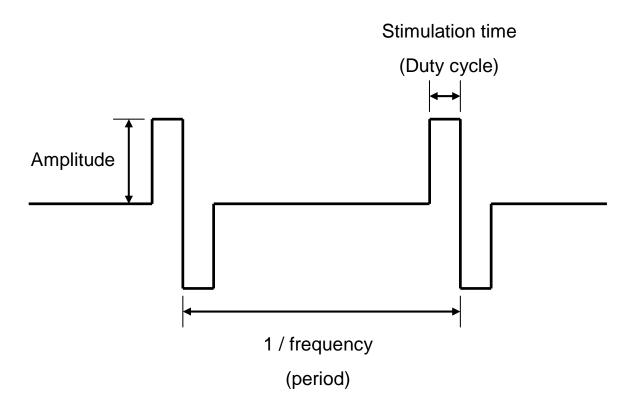

| Figure 4.2: Signal parameters of stimulation                                      | 70      |

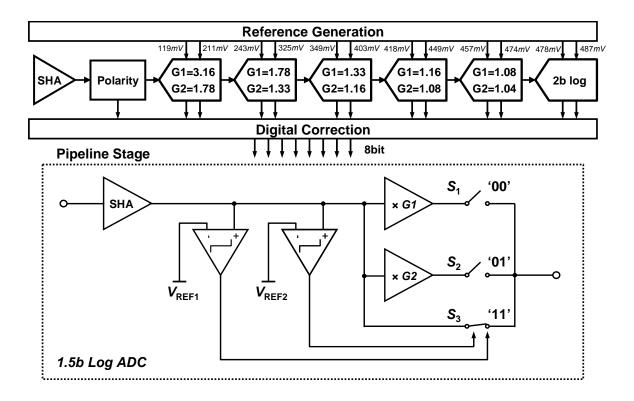

| Figure 4.3: Logarithmic ADC integrated in CDBS.                                   | 73      |

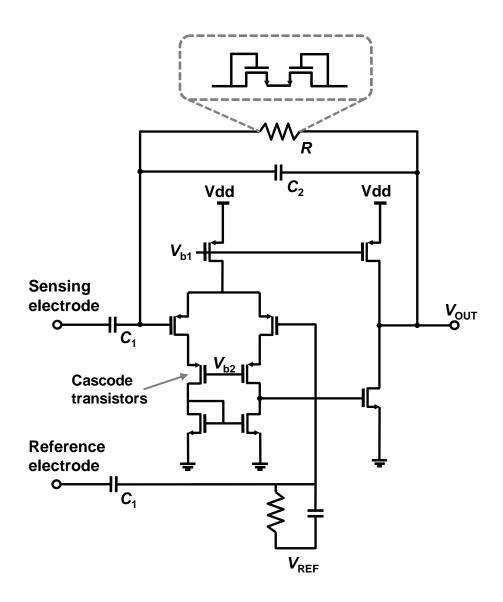

| Figure 4.4: Front-end low noise neural amplifier.                                 | 74      |

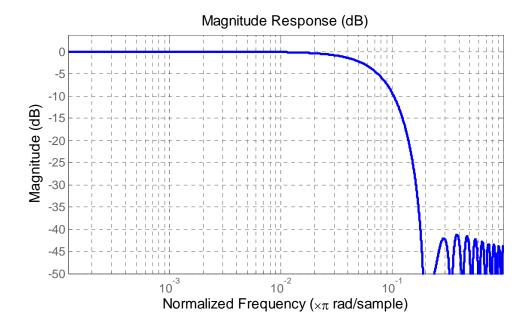

| Figure 4.5: High-pass digital filter for the spike detection                      | 76      |

| Figure 4.6: Low-pass digital filter for the spike detection                       | 76      |

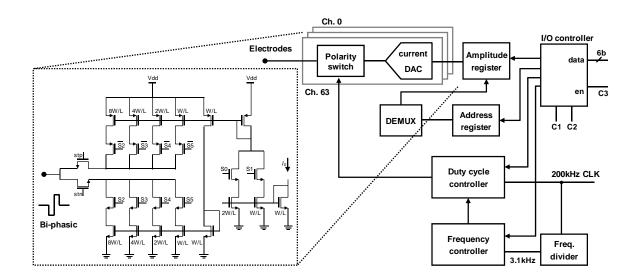

| Figure 4.7: 64 channel current DAC controller architecture.                       | 77      |

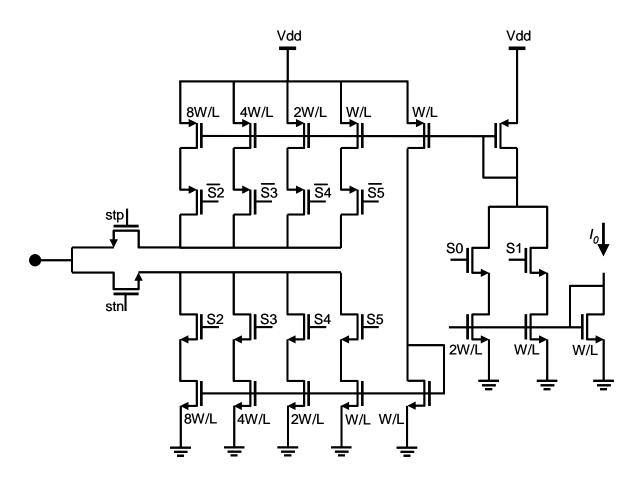

| Figure 4.8: MSB shared (2+4) bit bi-phasic current DAC.                           | 79      |

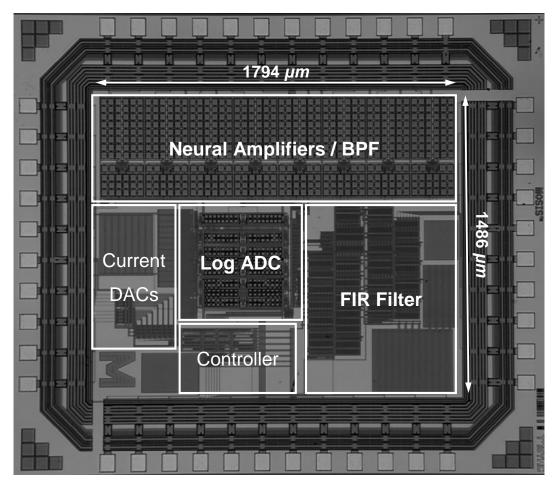

| Figure 4.9: Closed-loop DBS die micrograph.                                       | 80      |

| Figure 4.10: Measured SNDR of the combination of the neural amplifier and th      | e log   |

| ADC                                                                               | 81      |

| Figure 4.11: Measured DNL and INL of the logarithmic ADC.                         | 82      |

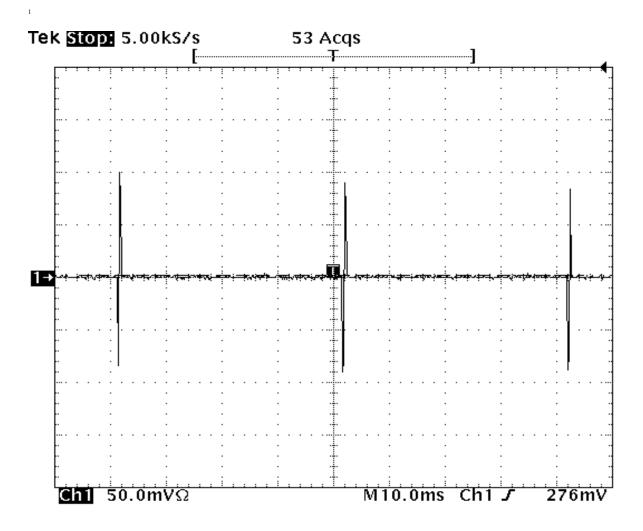

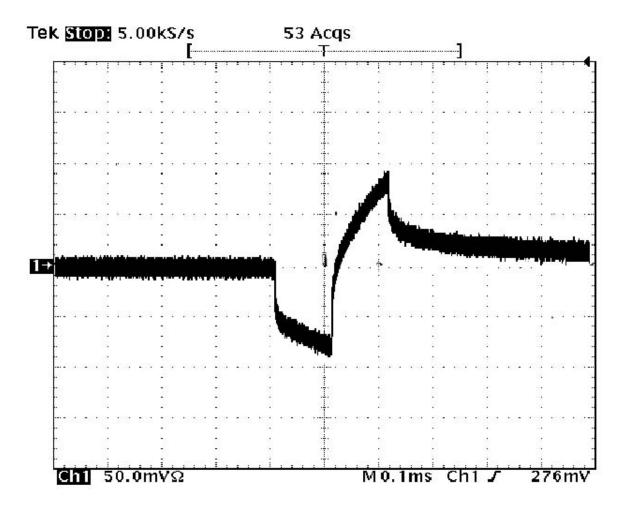

| Figure 4.12: Measured output of the stimulation DAC.                              | 83      |

| Figure 4.13: Measured output of the stimulation DAC.                              | 84      |

| Figure 4.14: Measured DNL and INL of the logarithmic ADC.                         | 85      |

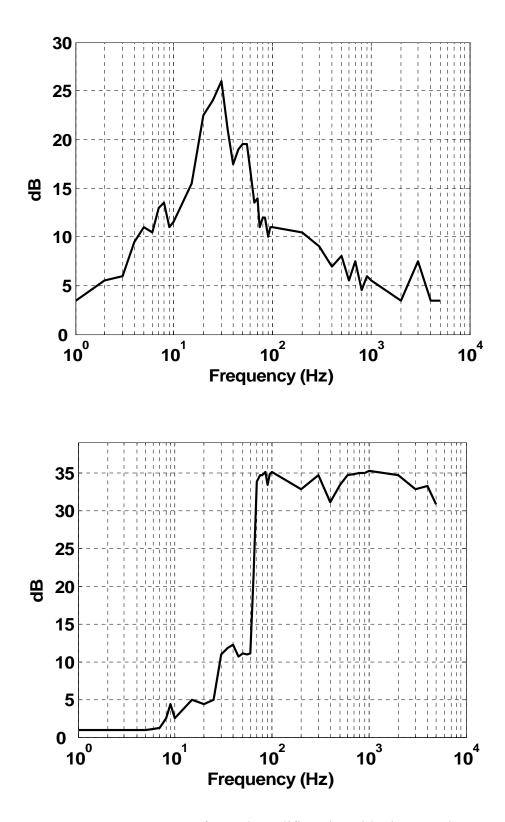

| Figure 4.15: Frequency response of neural amplifiers, logarithmic ADC, low pass d | ligital |

| filter (above) and high pass digital filter (below) output                        | 86      |

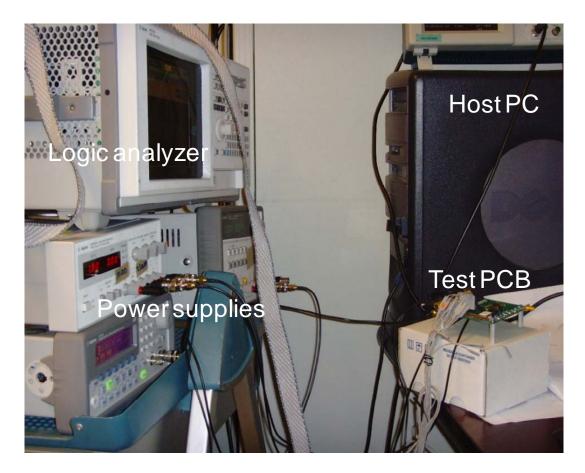

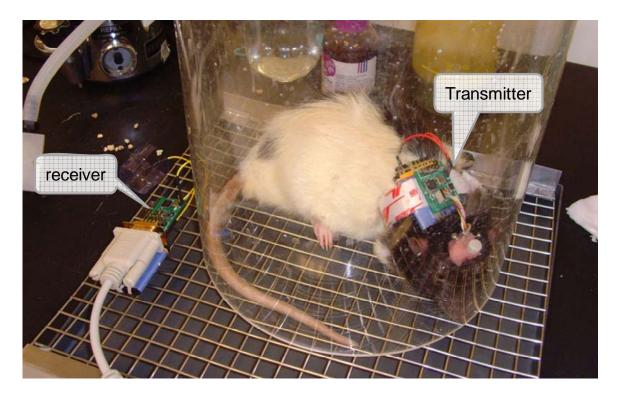

| Figure 5.1: Test bench                                                            | 90      |

| Figure 5.2: Animal test: unit NS-11 (Long Evans).                                  | 91     |

|------------------------------------------------------------------------------------|--------|

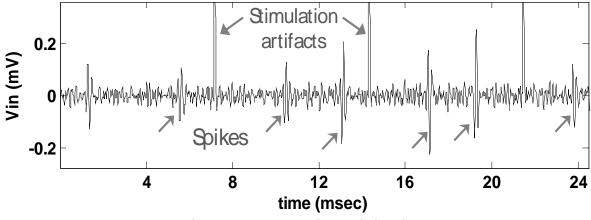

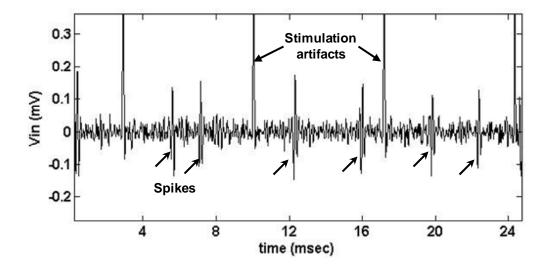

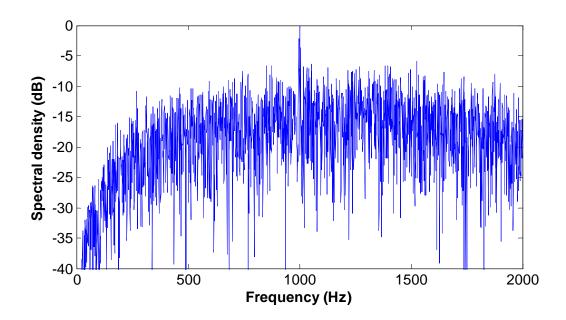

| Figure 5.3: Measured neural signals.                                               | 92     |

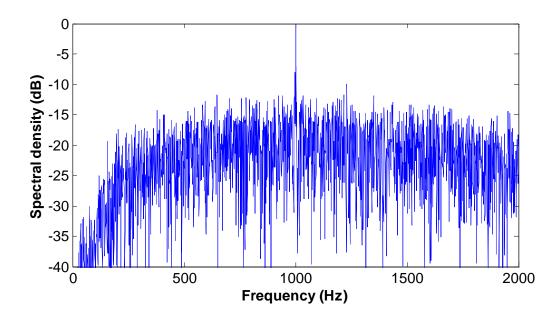

| Figure 5.4: Frequency response of the neural signal.                               | 93     |

| Figure 5.5: Implantable printed circuit boards                                     | 94     |

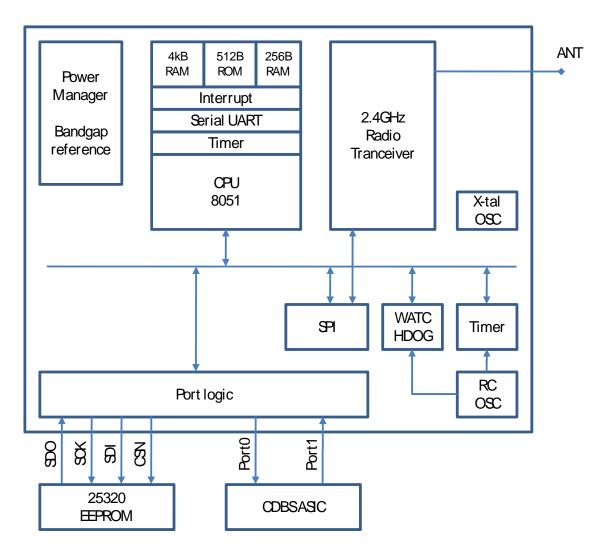

| Figure 5.6: The structure of nRF24E1 [102].                                        | 96     |

| Figure 5.7: The implantable prototype system (unit NS-17).                         | 97     |

| Figure 5.8: Measured neural signals                                                | 98     |

| Figure 5.9: Frequency response of the neural signals                               | 99     |

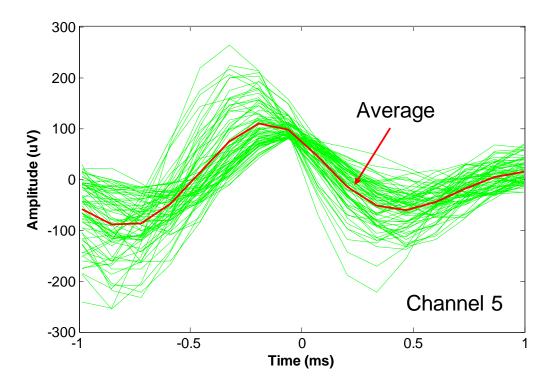

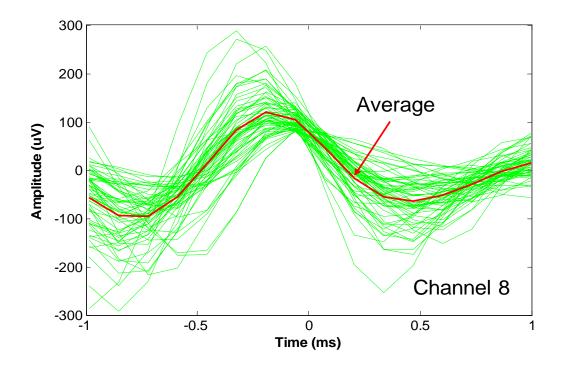

| Figure 5.10: Single-unit neural spike sorting (Channel 5)                          | 100    |

| Figure 5.11: Single-unit neural spikes sorting (Channel 8).                        | 100    |

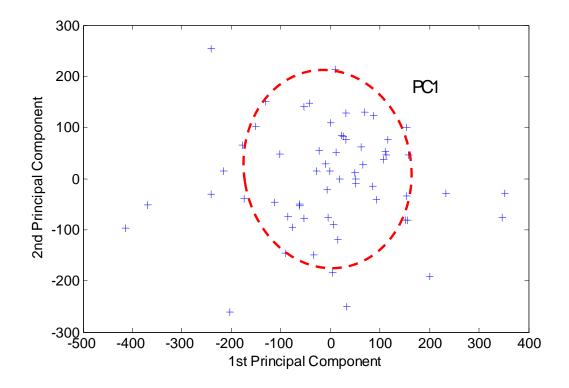

| Figure 5.12: The Principal Component Analysis of the neural signals from channel 5 | 5. 101 |

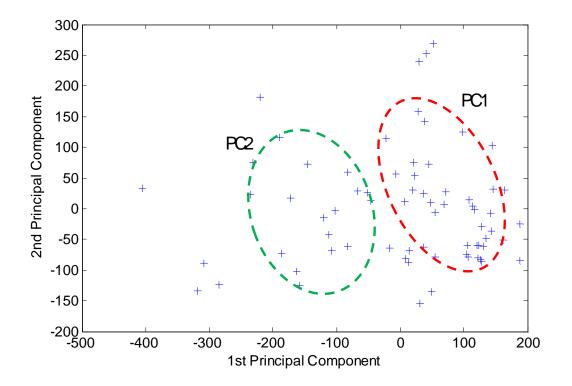

| Figure 5.13: The Principal Component Analysis of the neural signals from channel 5 | 5. 102 |

# List of Tables

| Table 2.1: Switched-capacitor filter performance.      |    |

|--------------------------------------------------------|----|

| Table 3.1: Performance comparison                      | 67 |

| Table 4.1: Stimulation control register operation mode |    |

| Table 4.2: Performance comparison                      |    |

# List of Abbreviations

| Acronym | Expansion                               |

|---------|-----------------------------------------|

| ADC     | Analog to Digital converter             |

| AGC     | Automatic Gain Control                  |

| ASIC    | Application Specific Integrated Circuit |

| CDBS    | Closed-loop Deep Brain Stimulation      |

| CMOS    | Complementary Metal-Oxide Semiconductor |

| DAC     | Digital to Analog converter             |

| DBS     | Deep Brain Stimulation                  |

| DNL     | Differential Non-linearity              |

| DR      | Dynamic Range                           |

| DSP     | Digital Signal Processing               |

| ESD     | Electro-Static Discharge                |

| FDA     | Food and Drug Administration            |

| FOM     | Figure of Merit                         |

| GPe     | Globus Palidus Externa                  |

| GPi     | Globus Palidus Interna                  |

| IC      | Integrated Circuit                      |

| Acronym | Expansion                               |

|---------|-----------------------------------------|

| INL     | Integral Non-linearity                  |

| INSD    | Input Noise Spectral Density            |

| LFP     | Local Field Potential                   |

| LNA     | Low-noise Neural Amplifier              |

| LSB     | Least Significant Bit                   |

| MDAC    | Multiplying Digital to Analog Converter |

| MiM     | Metal-insulator-metal                   |

| MSB     | Most Significant Bit                    |

| NEL     | Neural Engineering Laboratory           |

| NIH     | National Institute of Health            |

| Op Amp  | Operational Amplifier                   |

| PCA     | Principal Component Analysis            |

| РСВ     | Printed Circuit Board                   |

| PSD     | Power Spectral Density                  |

| SFDR    | Spurious Free Dynamic Range             |

| SN      | Substantia Nigra                        |

| SNDR    | Signal to Noise and Distortion Ratio    |

| SNR     | Signal to Noise Ratio                   |

| STN     | Subthalamic Nucleus                     |

| THD     | Total Harmonic Distortion               |

### Abstract

This dissertation is a summary of the research on integrated closed-loop deep brain stimulation for treatment of Parkinson's disease. Parkinson's disease is a progressive disorder of the central nervous system affecting more than three million people in the United States. Deep Brain Stimulation (DBS) is one of the most effective treatments of Parkinson's symptoms. DBS excites the Subthalamic Nucleus (STN) with a high frequency electrical signal. The proposed device is a single-chip closed-loop DBS (CDBS) system. Closed-loop feedback of sensed neural activity promises better control and optimization of stimulation parameters than with open-loop devices.

Thanks to a novel architecture, the prototype system incorporates more functionality yet consumes less power and area compared to other systems. Eight frontend low-noise neural amplifiers (LNAs) are multiplexed to a single high-dynamic-range logarithmic, pipeline analog-to-digital converter (ADC). To save area and power consumption, a high dynamic-range log ADC is used, making analog automatic gain control unnecessary. The redundant 1.5b architecture relaxes the requirements for the comparator accuracy and comparator reference voltage accuracy. Instead of an analog filter, an on-chip digital filter separates the low frequency neural field potential signal from the neural spike energy. An on-chip controller generates stimulation patterns to control the 64 on-chip current-steering DACs. The 64 DACs are formed as a cascade of a single shared 2-bit coarse current DAC and 64 individual bi-directional 4-bit fine DACs. The coarse/fine configuration saves die area since the MSB devices tend to be large.

A prototype device is fabricated in 0.18  $\mu m$  CMOS with a MiM capacitor option and occupies 2.67  $mm^2$ . The total power consumption of the entire system, including neural amplifiers, log ADC, current DAC, controller and digital filters, , reference generation, clock generation and biasing, is 112  $\mu W$  in normal operation mode and 351  $\mu W$  in configuration mode, which is significantly less than that of state-of-the-art stimulator circuits.

Real-time neural activity was recorded with the prototype device connected to microprobes that were chronically implanted in two Long Evans rats. The recorded *invivo* signal clearly shows neural spikes of 10.2 *dB* signal-to-noise ratio (SNR) as well as a periodic artifact from neural stimulation. The recorded neural information has been analyzed with single unit sorting and principal component analysis (PCA). The PCA scattering plots from multi-layers of cortex represent diverse information from either single or multiple neural sources. This exploits the benefits of a three-dimensional multi-layer neural probe such as the Michigan probe. The single-unit neural sorting analysis along with PCA verifies the feasibility of the implantable CDBS device for to *in-vivo* neural recording interface applications. To program an optimal closed-loop algorithm, further intensive studies will be necessary to examine the neural pattern changes related to the CDBS treatment. In addition, the CDBS device and implantable brain-machine interface (BMI) unit, has potential for the treatment of other neurological disorders such as stroke, epilepsy and seizure.

### **CHAPTER I**

#### Introduction

Parkinson's disease is a progressive disorder of the central nervous system affecting more than three million people in the United States [1]. Although the cause of Parkinson's disease is still not fully understood, there have been reports of symptoms related to Parkinson's disease including: tremor at rest, rigidity, bradykinetic movement and postural instability [2]. Deep brain stimulation (DBS) is one of the most effective neurosurgical procedures to alleviate these symptoms. In this chapter, we discuss the biological background and the DBS method. An explanation of the proposed system follows.

# 1.1. Biological background

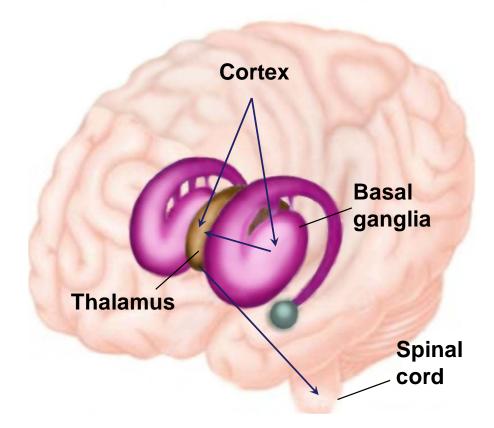

The basal ganglia consists of several groups of neuclei that function to process neural information sent from the cerebral motor cortex. The cerebral motor cortex can essentially be thought of as the conscious part of the brain, that is, the part of the brain that makes executive movement decisions. When a decision is made to move a muscle, the sensory-motor part of the cortex sends signals to the deep area of the brain. These signals are received by several regions including the thalamus, basal ganglia and cerebellum [3]. The thalamus is the region where the signals are then relayed down the spinal cord to the muscles, and further processing is done in the basal ganglia [4]. This processing is subsequently relayed to the thalamus again. A simplified schematic of the neural connections involved with executing a command to move a muscle is shown in Figure 1.1.

Figure 1.1: A simplified schematic of the neural connections [3].

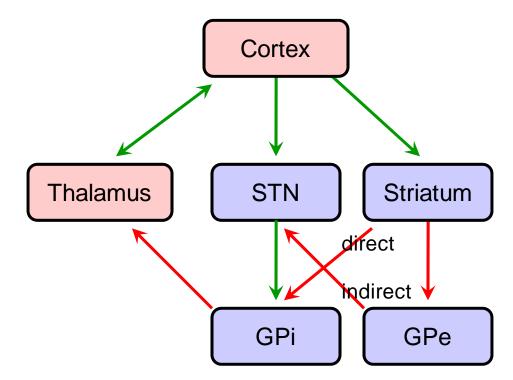

The processing in the basal ganglia has many functions, among which is judging whether or not a movement is appropriate. In order to accomplish this goal, the basal ganglia have two internal loops, a direct loop that leads to excitatory action on the thalamus, and an indirect loop that leads to inhibitory action on the thalamus [4]. These two loops work side-by-side in order for the brain to properly control desired movements. The basal ganglia network is shown in Figure 1.2 where STN represents the Subthalamic Nucleus, GPi represents the internal part of Globus pallidus, GPe represents the external part of Globus pallidus. Excitatory connections are shown in green and inhibitory connections in red [5-11].

Figure 1.2: The basal ganglia loops [4].

The network shown in Figure 1.2 results in the two loops described above [4]. The excitatory loop is also called the direct loop because it passes directly from the striatum to the GPi and then to the thalamus, this loop contains two inhibitory connections, so the result is excitation of the thalamus. The inhibitory loop, because it has two extra connections, is also called the indirect loop. In this loop, signals pass from the striatum to the GPe, then to the STN and then to the GPi before ending at the thalamus. Because of the three inhibitory connections contained in this loop, the result is inhibition of the thalamus [5].

Because each of these loops is needed for proper function, pathologies occur when either one of them overpowers the other. If the direct pathway overpowers the indirect, there is an excess of excitation, resulting in a hyperkinetic state, such as Huntington's disease [6]. On the other hand, if the indirect pathway overpowers the direct, there is excessive inhibition of the thalamus, leading to a hypokinetic state, such as Parkinson's disease [6-8]. The symptoms of Parkinson's disease are revealed as inability to execute the desired movements introduced above. Parkinson's disease is correlated to a decrease in the functioning of another basal ganglia nucleus, the Substantia Nigra (SN)[9]. When SN function is limited, the result is an increased signal being passed between the striatum and the GPe and a decreased signal being passed between the striatum and the GPi. This leads to the excessive inhibition of the thalamus described above [10-11].

There are several treatments currently used to alleviate Parkinson's symptoms including medications and neurological surgeries. One is the administration of levodopa, a drug that is the precursor to the dopamine which is the neurotransmitter secreted by the SN [12]. This treatment has the side effect of exposing the body to high amounts of dopamine that can lead to other neurological problems such as nausea [12]. Another treatment is the ablation of the GPe to stop the indirect loop by removing one of its components. Clearly, the ablation of a group of brain cells is a very invasive procedure and can lead to many problems if any additional cells are destroyed. A treatment that is currently not used, but has promise in the future is transplantation, implanting new cells, or to use stem cells to create a new SN for the patient [2]. This method would function to restore normal dopamine levels in the area of the basal ganglia, but not throughout the

entire body as in the levodopa treatment [10-11]. While this method could work well in the future, it is several years off at best.

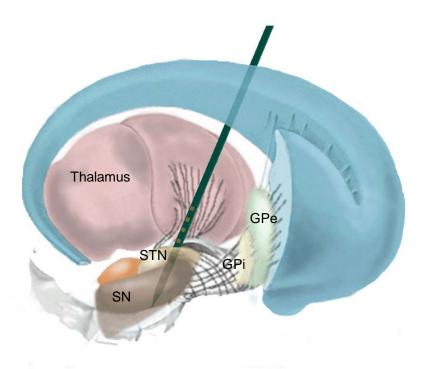

The other treatment for Parkinson's disease is DBS which delivers high-frequency electric stimulation to excite several parts of the basal ganglia including STN. DBS is a very effective neurosurgical procedure for the patients whose condition cannot be controlled with medications [12]. A thin, insulated wire or micro-machined electrode is surgically implanted into the deep brain target such as STN or GPi as shown in Figure 1.3. While the mechanism of the DBS works is still unknown, it seems that the high frequency nature of the signal acts to diminish the effectiveness of the inhibition on the thalamus.

Figure 1.3: Placement of the DBS probe into STN [14].

# 1.2. Deep brain stimulation (DBS) system

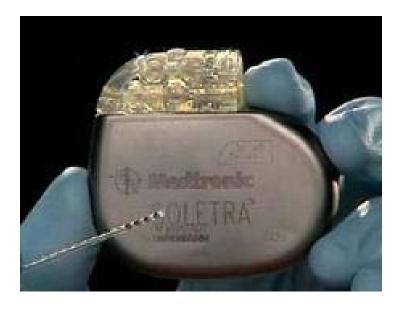

DBS has become a widely applied treatment of advanced Parkinson's disease since 1997 when the United States Food and Drug Administration (FDA) approved unilateral DBS systems to treat Parkinson's disease [15-16]. A medical technology company named Medtronic [17], that is seen these days, supplies bilateral DBS devices. Bilateral DBS devices, which were approved by FDA in 2002, consists of two neurostimulators. One for each side of brain [15-16]. Similar to a cardiac pacemaker, the DBS uses a neurostimulator to generate and deliver high-frequency electric pulses into STN or GPi through extension wires and electrodes. The Soletra neurostimulator, introduced as the most advanced battery-operated device from Medtronic, has the dimension of 55  $mm \times 60 \ mm \times 10 \ mm$  and the weight of 42 g as shown in Figure 1.4 [18].

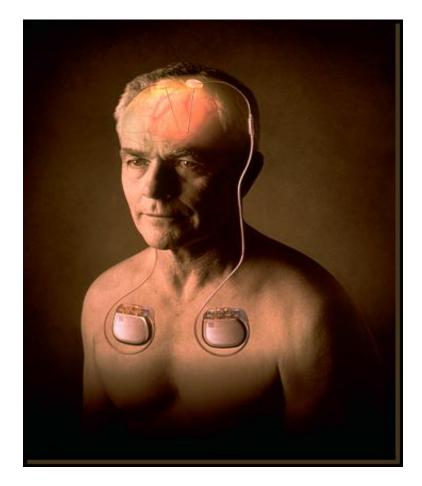

Figure 1.4: Soletra neurostimulator and DBS lead [18].

The neurostimulator is fairly large size and is subcutaneously implanted under the clavicle as shown in Figure 1.5 [19]. An insulated extension wire runs up under the skin of the shoulder, neck, and head to deliver the stimulation pulses. The stimulation pulses are generated from the neurostimulator to the electrodes implanted into the deep brain area through a burrhole in the skull. Unfortunately, several hardware complications have been reported that affects more than 26% of the patients [20]; this includes infections during the surgery, extension erosion, lead wire fracture and malfunction of the neurostimulator. These surgical complications incidents may be reduced by a smaller size and stand-alone device which doesn't require any extension wire.

Figure 1.5: Placement of the Medtronic DBS<sup>™</sup> system [19].

The Medtronic neurostimulator is programmed post-surgery by trained technicians to find the most effective signal parameters for alleviating Parkinson's symptoms. However, it can take up to one full year to find the best parameters for patients [21]. The effective signal parameters are amplitude, frequency, and pulse-width. This effective signal matching process is still not well understood. The only current feedback mechanism is the visual sign of tremor attenuation. Every patient has a unique set of signal amplitudes, frequencies, and pulse widths that are effective to treat their disease. Thus patients who are being implanted with DBS have to visit their doctors frequently to get fine tuned adjustments of their stimulation parameters. If any internal information from the brain in Parkinson's state is sensed, then the proper parameters can be found automatically by a dedicated microprocessor without the intricate travel to a medical center.

The strongest candidate for the internal feedback signal is an abnormal pattern change in neural spikes or field potentials from normal status when Parkinson's disease symptoms occur. Normally, it is shown that spike signals have bandwidths with 100 Hz to 10 kHz and amplitude levels up to  $\pm 500 \ \mu V$ , and local field potentials (LFPs) have bandwidths with 1 Hz to 50 Hz with amplitude levels up to  $\pm 10 \ mV$ . An excessive power of a 15 – 30 Hz low frequency field potential from the extracellular recording of rat's cortex has been delivered [22]. To measure the extracellular neural activities, multichannel microprobes are used. It has an ability to record a neural population activity in the form spike trains as well as slower LFPs. Also, the microelectrodes must deliver the localized electric stimulation for an extended period up to 5 years without damaging brain tissue [23]. For the clinical usage in humans, the electrode should be at least 10 cm

in length and small cross-sectional area. This helps to minimize tissue damage and fits to standard stereotaxic tools with stable and biocompatible characteristics [24]. Also, the electrode should be stiff enough to resist insertion forces during surgery and be able to position the probe channels precisely closed to the small STN [25].

The collected neural signals from the microelectrodes should be conditioned using front-end circuits such as pre-amplifiers and analog-to-digital converters (ADCs). Due to the low-level amplitude of the neural spikes, integrated pre-amplifiers have been used to amplify the small signals before the data conversion [26]. The front-end design should be low-noise to guarantee the signal integrity, and low-power. During the last decade, several types of the front-end neural recording circuits have been proposed [27]. In the earliest work, Ji et al. [28] at the University of Michigan presented an active integration of the multi-channel microprobes with complementary metal-oxide semiconductor (CMOS) circuits. However, the pass-band gain is unstable and the dynamic range is limited by a large direct current (DC) offset [29] which depends on the electrode-tissue interface. To stabilize this random DC potential, Mohseni et al. employed a shunt resistor connected to the electrode input [27]. This parallel resistor provides a short path for DC signal while the alternating current (AC) gain change rarely. It can be used only for an acute neural recording since the impedance of the microprobes varies along the time for a long-term experiment. A single-chip integration of pre-amplifiers, an ADC and telemetry has been proposed by Song et al. at the Arizona State University [30]. Recently, more advanced wireless integration with 100 neural recording channels has been developed by Harrison *et al.* at the University of Utah [31].

However, most of the work focused only on the neural spike recording, and there is no truly stand-alone, small-scale system for recording both spikes and LFPs simultaneously, because of the challenges imposed by their signal characteristics. To cover the entire range of both small-signal neural spikes and large-signal LFPs, a high dynamic range ADC is needed to digitize all the desired neural information.

Unfortunately, many researchers are still trying to discover the DBS locations in the deep brain area where DBS are most effective in alleviating Parkinson's symptoms [32]. Also, accurate positioning of the DBS electrode is an active research field [25]. Multichannel stimulation distributed throughout the target nuclei with microelectrodes can be a good solution for this issue if the system provides precise independent site control with a programmable spatial stimulation. In spite of growing interests in DBS research, engineering development is only limited into DBS electrode.

## 1.3. Proposed closed-loop deep brain stimulation (CDBS) system

This project is focused on developing a small-size and implantable CDBS device that searches for unique parameters of electric stimulation to treat the Parkinson's disease. The proposed device has neural recording front-ends, fully programmable stimulating channels, and a microprocessor that runs a programmable algorithm that takes recorded neural signals as feedback and calculates the parameters that attenuate the symptoms of the disease. A 16 channel, single-shank recording electrode is implanted on rat's Motor cortex while a stimulating electrode is implanted on STN to provide stimulation current for Parkinson's disease treatment. Thus, the project hypothesized that there is a specific neural pattern in the Parkinson's state and also there is the most effective stimulation parameters to alleviate the symptoms of abnormal patterns of neural information.

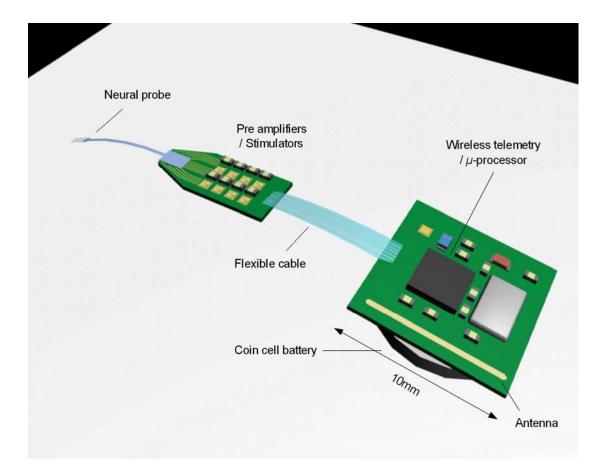

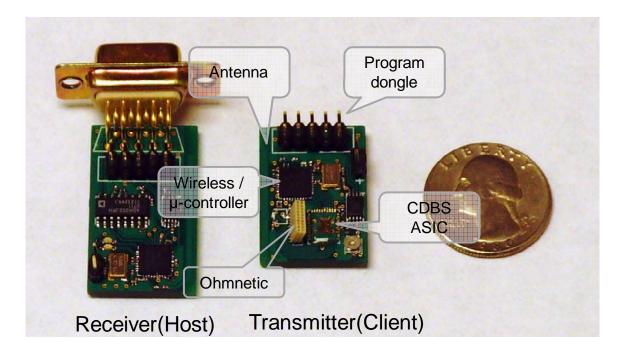

Figure 1.6: Prototype model of the first CDBS system.

The prototype system has been developed in two successive phases. The first system was built with commercially available parts, including instrumentation amplifiers, linear ADC, micro processor, wireless telemetry units for external monitoring and a coin cell battery as shown in Figure 1.6. The first generation device was used for the functional derivation of the closed-loop system. The second phase is an integrated singlechip application-specific integrated circuit (ASIC) containing 64 channel programmable stimulating circuitry, eight channel neural front-end, high dynamic-range logarithmic ADC, and a dedicated controller to set the stimulation parameters.

This small-scale ASIC device have many advantages: the minimized surgical complications because of the removal of extensions, the self-configurative parameter setting with an advanced neural interface capable of simultaneous neural recording of spikes and LFPs, and the fully-controllable multi-channel stimulation for the precise target positioning, as discussed in the previous section.

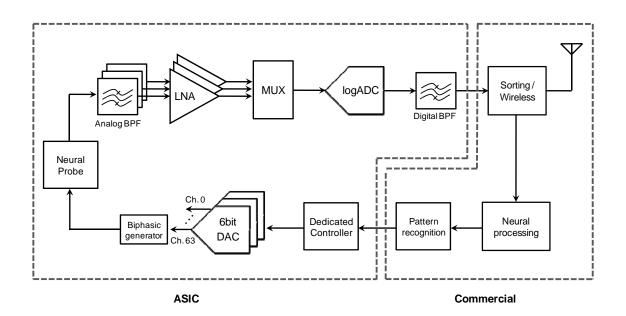

Figure 1.7 shows a block diagram of the integrated CDBS device including a wireless transmission for the post analysis of processed neural data by an external inspector.

Figure 1.7: Block diagram of the proposed CDBS system

Two multi-channel neural probes were implanted in the Motor cortex and STN, respectively. These are used to deliver the sensed neural signals and the stimulation pulses. The recorded neural waves are fed through individual low-noise neural amplifiers (LNAs) containing analog band-pass filtering and multiplexed into a single high dynamic-range pipeline logarithmic ADC. The proposed logarithmic ADC exploits the fact that the neural spike characteristic works on a companding scale. The most suitable way of encoding neural spikes is to use a variable resolution depending on the signal amplitude. The desired dynamic range is the span of spike magnitudes from neighbor neurons which generate action-potentials (APs). Since a higher dynamic range can be achieved for a given word length with a properly designed logarithmic conversion [33], it provides more efficient way to cover the entire dynamic range of both neural APs and LFPs than conventional linear encoding. Digitally converted neural data is filtered out by finite-impulse-response (FIR) digital filters to separate the neural APs and LFPs for the post processing. The employment of the digital filters has the benefit of reducing power consumption.

A microprocessor analyzes the neural patterns to classify the Parkinson's state, and to search for the most effective stimulation variables for the multi-channel current stimulation. The parameters decide the pulse shape of the stimulation. A bi-phasic pattern is used to minimize the remainding charge supplied to the tissue. A 64 channel current steering digital-to-analog converter (DAC) is used to form the desired pulse generation. The 64 DACs are based on a new (2+4) bit structure formed as a cascade of a single shared 2-bit coarse DAC and 64 individual 4-bit fine DACs. This format saves as much as an order of magnitude circuit area and delivers sufficient stimulation performance. Parkinson's disease needs to be better understood so a feedback algorithm can be designed. To facilitate research progress in this field, there is a need for the wireless monitoring link to an external host personal computer (PC) located outside the body. The wireless telemetry eliminates the large bundle of multi-channel wiring and the environmental noise from these cables. Also, it does not restrict movement of animals or humans [34]. The proposed system employs a 2.4 *GHz* radio-frequency (RF) transceiver capable of 1*Mbps* data rate communication for the physiological monitoring. The 2.4 *GHz* frequency band is allocated for industrial, scientific and medical (ISM) usage by US Federal Communications Commission (FCC) [35]. And, a 1*Mbps* data rate provides a sufficient bandwidth for the simultaneous multi-channel neural data streaming.

#### **1.4. Dissertation outline**

The biology of Parkinson's disease and the current DBS system is reviewed, and new architecture for the closed-loop techniques to improve performance has been introduced. This work is also relevant to other circuits and systems for the brain-machine interface systems that use neural interfaces.

Since the front-end circuitry of the proposed system is based on the micro-scale implantable neural interfaces, the research advances in multi-channel micro-electrode arrays and implantable neural recording devices in recent decades are reviewed in Chapter II. Also, a prototype of the multi-modal and cascaded switched-capacitor device provides simultaneous recording of both neural APs and LFPs with better noise performance, is discussed although it is not included in the CDBS ASIC, The logarithmic coding technique for high dynamic range is given in Chapter III. This high dynamic range provides the entire coverage of the neural APs and LFPs without need for the two-stage pre-amplifier introduced in Chapter II. The prototype circuit implementation of the CDBS ASIC device contains neural front-ends for both recording and stimulation as well as digital filters and controller, is presented in Chapter IV. The *in-vivo* test method and the measured neural data from an animal brain are described in Chapter V. Finally, the thesis is concluded in chapter VI with a summary and suggestions for future work.

### **CHAPTER II**

#### Micro-scale implantable neural interface

Multi-channel microprobes are used to investigate the structure and mechanism of neural networks. These microprobes are capable of recording neural population activity in the form of spike trains as well as slower local field potentials (LFPs). Both of these signal types provide unique information about biologically relevant time and spike pattern predictions. In some cases, implantable pre-amplifiers have been used to amplify the weak neural signals for the post processing, but most applications utilize external signal conditioning. In this chapter we will review the research in the micro-machined neural electrodes and the integrated front-end circuit for processing spikes and LFPs. This is important background information for the front-end recording channels of the proposed closed-loop deep brain stimulation (CDBS). In addition, a prototype of the twostage, multi-modal, and simultaneous neural recording device is presented.

## 2.1. Hybrid integration of neural probes

Implantable neural microprobe arrays enable sophisticated investigations of the structure and mechanisms of neural networks [36-37]. Recent studies in brain-machine interfaces have emphasized using LFPs as input signals, especially when chronically implanted devices lose their functionality for recording unit-spike activity [38-41].

Moreover, studies have also suggested that spikes and LFPs may encode different information [42, 43].

The development of micro electro-mechanical system (MEMS)-based implantable microelectrode arrays, which began with the seminal work of Wise, et al. [44], is an active research area in a number of laboratories [45]. Micro-fabricated probes provide a number of unique advantages including: precisely defined thickness and shape, customizable electrode size and configuration, and batch-fabrication. They also facilitate the use of many electrode sites, or in other words, many parallel recording channels.

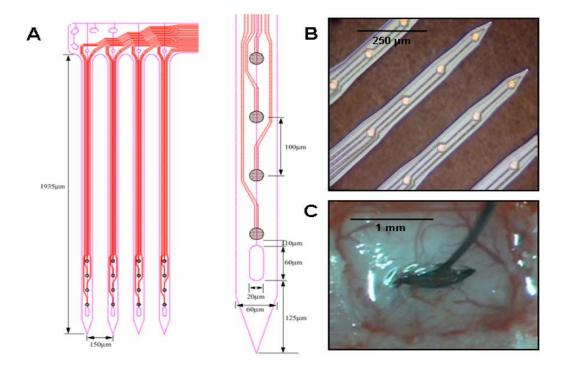

Figure 2.1: Neural microprobe (NEL, U of Michigan) [46].

Figure 2.1 shows the passive neural microprobes made by a MEMS process with thin film of sensing sites and conducting leads. The microprobes are fabricated with a silicon substrate whose shape and thickness are precisely decided using boron etch-stop micromachining. The substrate contains a conducting array of metal recording sites and Polysilicon leads that are insulated by thin-film dielectrics. On the upper side of the dielectrics, there are metal exposures for the contact with the tissue and the bonding pads for the signal delivery to the interface devices [46]. The extensibility of the microprobe enables custom designs for various applications including the multi-plane arrays for the precise three-dimensional placement of recording sites in the brain [47], and the connection with a polymer ribbon-cable to intensify mechanical flexibility [48]. In addition, probe designs can expand containing micro-fluidic channels along the shanks for drug delivery through the blood-brain barrier [49].

The small size of complementary metal-oxide semiconductor (CMOS) integrated circuits makes this technology useful for large-scale processing of neurophysiological signals. The scalability of the micro-fabrication technology enables active integration with electronic circuits for signal conditioning. Since active probes employ front-end circuits, noise and distortion from the environment are buffered before transmitting the signal through wired or wireless links to a data acquisition system. In addition, active probes provide the possibility of digital signal processing (DSP) such as data compression and spike sorting at the front-end to enhance signal integrity and reduce the number of tethering wires. Active probes have two types of integration – substrate integration and hybrid integration. The substrate type of active probes integrates electronics on a separate chip [51-53]. However, while commercial CMOS circuit technologies have been reached at already impressive acceleration down to the sub-micron scale, the MEMS

processes for the electrode fabrication stays at the multi-micron phase that is basically little changed over the last two decades. The imprecision of the MEMS process limits the large-scale integration (LSI) circuitry in the substrate active integration.

For large channel count integration, the hybrid type integration is preferable through a mixed device in which the probe substrate and electronics are fabricated on separate wafers. The hybrid probe has several advantageous attributes including high-density integration to include on-chip electronics for DSP and wireless transmission for no tethering force [51]. Separate electronics with state-of-the art circuit technology increases the density of integration and the number of channels. For example, for a given circuit design, the circuit fabricated in 90 *nm* technology can contain 1000 times more electronics than that in substrate integration with 3  $\mu m$  feature size. The front-end recording interface circuits are discussed in detail in the next section, as will a proposed simultaneous recording device.

Contrary to the neural recording probes, DBS electrodes deliver relatively large electric current pulses for stimulation. In order to apply DBS devices with the optimal functionality, diverse long-term stimulation research (in a proper animal model such as rats) is needed. Since a deep-set STN of a rat is tiny and is located in the deep brain area far away from the surface (about 10 *mm*), the DBS electrodes are designed to allow accurate positioning in the basal ganglia [23] and sufficient stiffness to resist insertion forces during surgery [24]. In addition, the electrodes must be bio-compatible to avoid chronic tissue response, have a sharp tip and a tapered shank for the minimally invasive design, and be stable enough not to migrate from the first implanted position [25].

Figure 2.2 shows an example of a multi-channel DBS neural probe that is able to

accurately stimulate the STN developed by NeuroNexus Technology [54]. The probe is based on silicon substrate in 15  $\mu m$  thickness for minimally invasive tissue injury. It also has a conducting pattern of recording sites and leads deposited with iridium. The electrode has 32 channels to provide a diverse spatially distributed stimulation and is separated by a distance of 100 $\mu m$  for each of the recording sites. The channel impedances vary depending on the tissue response within 200  $k\Omega$  to 3  $M\Omega$  [54].

Figure 2.2: 32-channel silicon-substrate probes for DBS [54].

#### 2.2. Switched-capacitor amplifying filter

As reviewed above, multi-channel microprobes are capable of recording neural population activity in the form of spike trains as well as slower LFPs. Both signal types provide unique information about biologically relevant time and spike pattern predictions [55].

However, there is no truly stand-alone, small-scale system for simultaneously recording both spikes and LFPs because of the challenges imposed by each of their signal characteristics. For the simultaneous recording of both neural signals, the amplifier system must exhibit a high dynamic range, which can be limited by the need for good noise performance and high ADC dynamic range (at least 16 bits). Together, these considerations inevitably limit the number of recording channels.

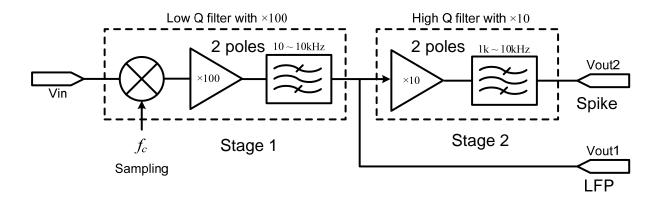

Here, a new architecture is introduced that uses a two-stage amplifier structure, which generates filtered LFP output at the first stage and processed spike output at the second stage as shown in Figure 2.2 [56]. The proposed device employs a switched-capacitor circuit to reduce flicker (1/f) noise and is less process dependent than a resistor based circuit. The first stage is designed as a low-Q bi-quad filter that passes a 10 Hz to 10 kHz frequency band with an amplification of 100 times for LFPs sensing. The second stage implements a high-Q bi-quad filter, which passes only 100 Hz to 10 kHz signals with an additional amplification of 10 times for spikes recording.

Figure 2.3: Basic architecture of the proposed system.

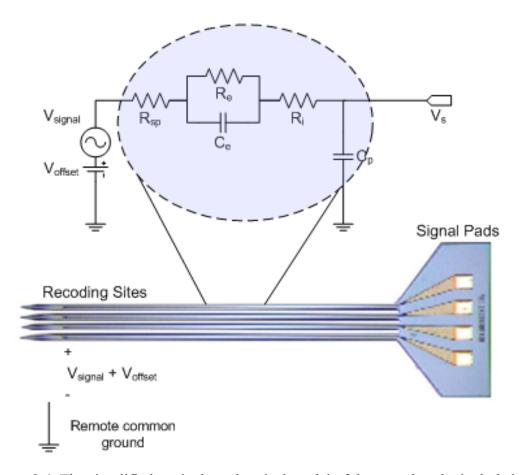

Figure 2.4 shows the equivalent electrical model of the neural microprobe, made by bulk micromachining and patterning of recording sites and lead wires. For the electrode-electrolyte interface, measurement of the Michigan probe shows that the spreading resistance,  $R_{sp}$  is 250  $k\Omega$ , the electrode resistance,  $R_e$  is 200  $G\Omega$ , the capacitance,  $C_e$  is 600 pF, and the interconnect resistance,  $R_i$  is 100  $k\Omega$ . Because of the high electrode resistance, most currents flow through the capacitor except for extremely low frequency signals [27].

Figure 2.4: The simplified equivalent electrical model of the neural probe included a spreading resistance (Rsp), faradaic electrode resistance (Re), non-faradaic electrode capacitance (Ce), probe trace resistance (Ri), and shunt capacitance (Cp).

Band-pass charge amplifiers are generally used to connect to this type of probe, as shown in Figure 2.5 because capacitive matching provides more accuracy than resistive dividers.

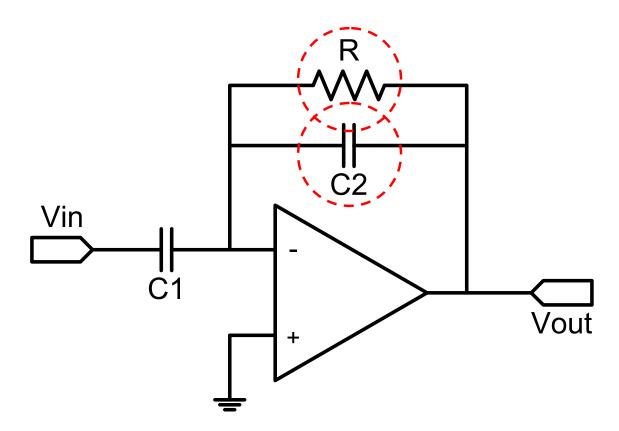

Figure 2.5: General band pass amplifier.

If the inputs to the charge amplifiers remain constant, the leakage currents that supply a constant current will saturate the output voltage to the supply limit. Hence, the voltage across the capacitor should be reset often enough so that leakage currents have no influence [57]. The switched-capacitor circuit refreshes the voltage across the capacitor frequently. Although this general charge amplifier works well, a very large feedback resistance, R, has been reported by R.H. Olsson *at el.* [58]. For example, for a 100 *Hz* high pass pole with 1 *pF* C2 capacitance , at least 1.6 *G* $\Omega$  resistance is indicated by Equation (2.1). Olsson *et al.* replaced the resistor with diode-connected transistors to form the large resistance. We describe another strategy to emulate a large resistance with a switched-capacitor technique.

$$R = \frac{1}{2\pi C_2 f_c} = \frac{1}{2\pi \times 1pF \times 100Hz} = 1.6G\Omega$$

(2.1)

As we scale down the transistor feature size, another issue arises since the 1/f noise of a MOSFET varies inversely with the transistor area (*WL*). The noise of a MOSFET consists of thermal noise and flicker (1/f) noise. Since 1/f noise is more important at lower frequencies, neural amplifier designs are focused on reducing this noise [59]. Empirically, PMOS transistors have about two to five times less 1/f noise than NMOS transistors and the first stage transistor is the dominant noise source. For example, input noise spectral density for a PMOS transistor is:

$$e_n^2 = \frac{B}{fWL} = \frac{2.02 \times 10^{-22} (V - m)^2}{f \times 1\mu m \times 0.18\mu m} = \frac{11.22 \times 10^{-10}}{f} V^2 / Hz$$

(2.2)

where the width (*W*) and length (*L*) of transistor is 1  $\mu m$  and 0.18  $\mu m$ , respectively and the 1/*f* noise constant of a PMOS transistor, *B*, is 2.02×10-22 (*V*-*m*)<sup>2</sup>. To estimate the root-mean-square (RMS) noise in the bandwidth from 1 *Hz* to 1 *kHz*, we perform the integration as:

$$V_n(rms) = \sqrt{\int_1^{1000} \frac{11.22 \times 10^{-10}}{f} df} = 88\mu V_{rms}$$

(2.3)

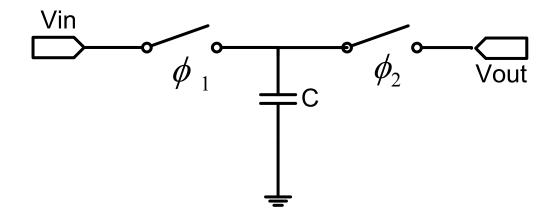

Since this device noise may be too large for the neural recording, we apply circuit techniques to suppress the 1/f noise below the thermal noise with switched-capacitor modulation. The parallel switched capacitor equivalent resistor circuit in Figure 2.6 [60] consists of two controlled switches with control clock phases,  $\varphi_1$  and  $\varphi_2$ , and a capacitor, C. The control clocks are non-overlapping complimentary signals. Hence, the input switch is shorted and the output switch is opened to charge the capacitor to the input voltage during phase,  $\varphi_1$ , and the input switch is opened and the output switch is shorted to deliver that stored charge to output during phase,  $\varphi_2$ .

Figure 2.6: Resistor emulation with switched capacitor circuit.

This charge transfer works as a resistor with a periodic control clock. For example, with a  $0.1 \, pF$  capacitor and a  $1 \, MHz$  clock, the emulated resistance is given by:

$$R = \frac{V_{in}}{I} = \frac{V_{in}}{\Delta Q / \Delta t} = \frac{V_{in}}{\Delta Q \cdot f_c} = \frac{V_{in}}{C V_{in} \cdot f_c} = \frac{1}{Cf_c} = \frac{1}{0.1 pF \times 1MS / s} = 10M\Omega$$

(2.4)

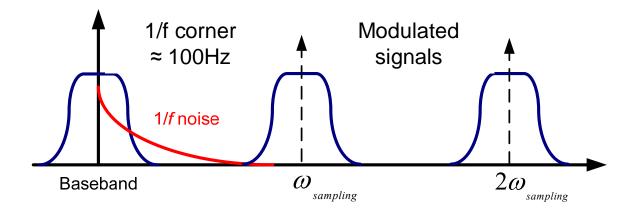

The switched capacitor circuit modulates the signal to multiples of the sampling frequency as shown in Figure 2.7. Since 1/f noise at the sampling frequency is much less than that at the baseband, the switched capacitor circuit can be used to eliminate 1/f noise like a chopping amplifier [61-66].

Figure 2.7: 1/f noise rejection by modulation with a switched capacitor circuit.

The 1/f noise with this sampling should be less than the wideband thermal noise. For this to occur, the sampling frequency has to be greater than the 1/f noise corner frequency and greater than twice the bandwidth of the input signal. The noise power spectral density (PSD) after sampling is given by [67],

$$S(f) = A_{o}^{2} \left(\frac{2}{\pi}\right)^{2} \sum_{\substack{n \ is \ odd}}^{+\infty} \frac{1}{n^{2}} S_{n}(f - nf_{c})$$

(2.5)

where  $A_o$  is the amplifier gain, and  $f_c$  is the sampling frequency. The spectral density of the thermal noise of a transistor with 10  $\mu$ S conductivity can be calculated by:

$$e_n^2 = 2 \cdot \frac{8kT}{3g_m} [1 + \sqrt{2}] = 2 \times 2.41 \times \frac{8 \times 1.38 \times 10^{-23} \times 300K}{3 \times 10\mu S} = 5.33 \times 10^{-15} V^2 / Hz$$

(2.6)

Combining Equations (2.5) and (2.6) together, we can find the noise corner where the thermal noise is equal to the 1/f noise. For a PMOS input device with 1  $\mu m$  width and 0.18  $\mu m$  length,

$$f = \frac{11.22 \times 10^{-10} V^2 / Hz}{5.33 \times 10^{-15} V^2 / Hz} = 210.5 kHz$$

(2.7)

Since the general value of the noise corner frequency is 210.5 *kHz*, a sampling frequency of more than 500 *kS/s* is required to achieve complete elimination of 1/f noise. However, a 100 *kS/s* sampling frequency used for the prototype device is sufficient to get the desired signal-to-noise ratio (SNR) in simulation.

Second-order bi-quad circuits have the advantage of potentially realizing complex poles and zeros. A band-pass second order response in the continuous time domain can be written in general as:

$$H(s) = \frac{V_{out}(s)}{V_{in}(s)} = \frac{-Ks}{s^2 + \frac{\omega_0}{Q}s + {\omega_0}^2}$$

(2.8)

Where  $\omega_0$  is the pole frequency, Q is the pole quality factor and K is coefficient for the amplification [68].

Charge injection and switching noise are non-idealities which need to be addressed when designing the switches. The amount of charge injected into the channel by the switching of the clock can be approximated as [69]:

$$\Delta q = \frac{WLC_{ox}}{2} (V_{ck} - V_{in} - v_{tn})$$

(2.9)

Where W, L,  $C_{ox}$ ,  $V_{tn}$ , are transistor parameters,  $V_{ck}$  and  $V_{in}$  are the clock and signal amplitudes respectively. If it is assumed that the charge splits equally between the source and drain, it follows that placing half-sized dummy transistors on either side controlled with an opposite clock absorbs most of this injected charge. In addition, the effect of switching noise can be eliminated by using a differential circuit implementation, because the noise equally affects both signal paths.

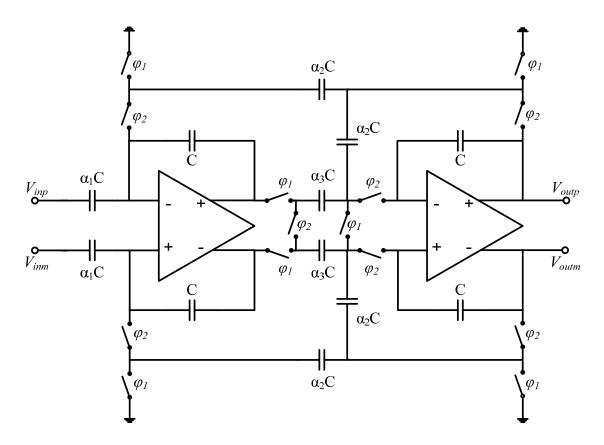

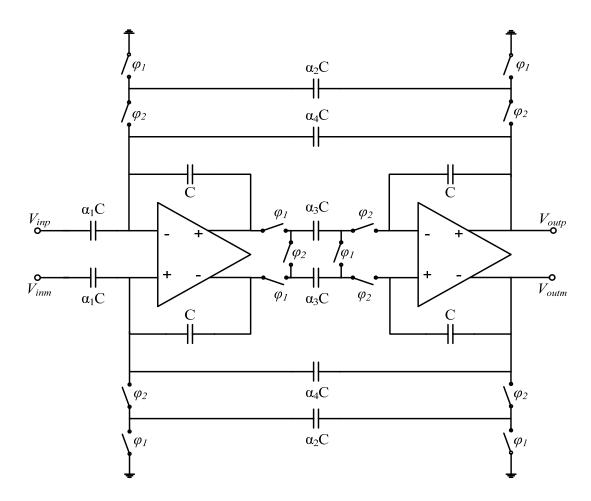

The differential circuit realization is shown in Figure 2.8 and the transfer function of the circuit is given by [63]:

$$H(s) = \frac{-Ks}{s^2 + \frac{\omega_0}{Q}s + {\omega_0}^2} = \frac{-\frac{\alpha_1}{T}s}{s^2 + \frac{\alpha_4}{T}s + \frac{\alpha_2\alpha_3}{T^2}}$$

(2.10)

Figure 2.8: Low Q bi-quad with differential switched capacitor circuit.

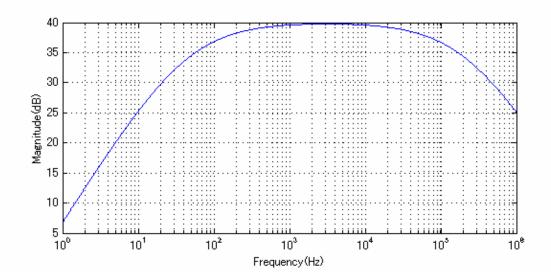

Figure 2.9: Frequency response of the low Q bi-quad.

To allow the circuit to pass all LFPs and spikes and limit direct current (DC) and high frequency noise, the coefficients are chosen as  $\alpha_1 = 0.7\pi$ ,  $\alpha_2 = \alpha_3 = 0.01\pi$ ,  $\alpha_4 = 0.7\pi$ , and K = 100 with a 100 kS/s sampling frequency. The simulated frequency transfer function is shown in Figure 2.9.

However, the pass band of the second stage, which passes spikes only, is narrow with a relatively high-Q value. If we use the circuit shown in Figure 2.8, we would need very large capacitors to meet this frequency range. Instead, we modify the circuit topology to high-Q circuit, to avoid large element spreads, as shown in Figure 2.10 and the transfer function is given by [63]:

$$H(s) = \frac{-Ks}{s^{2} + \frac{\omega_{0}}{Q}s + \omega_{0}^{2}} = \frac{-\frac{\alpha_{1}\alpha_{3}}{T}s}{s^{2} + \frac{\alpha_{3}\alpha_{4}}{T}s + \frac{\alpha_{2}\alpha_{3}}{T^{2}}}$$

(2.11)

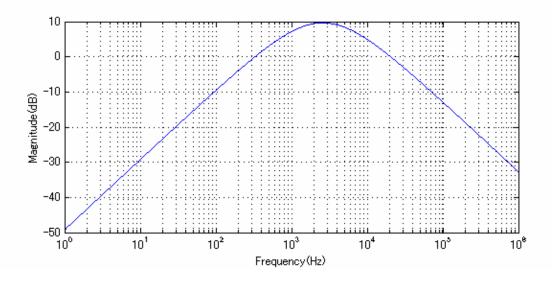

To pass spikes only and limit LFPs and high frequency noise, the coefficients are designed as  $\alpha_1 = 0.75$ ,  $\alpha_2 = 0.007\pi$ ,  $\alpha_3 = 0.01\pi$ ,  $\alpha_4 = 0.8$ , and K = 10 with a 100 kS/s sampling frequency, and the simulated frequency transfer function is shown in Figure 2.11.

Figure 2.10: High *Q* bi-quad implemented with a differential switched capacitor circuit.

Figure 2.11: Frequency response of the high *Q* bi-quad.

The overall amplification is performed in two stages as shown in Figure 2.3 as presented above. The first one is modulated signal amplification with low-Q band pass filtering matched to 40 dB gain. The second stage has relatively low gain (20 dB) and high-Q band pass filtering.

## 2.3. Prototype implementation

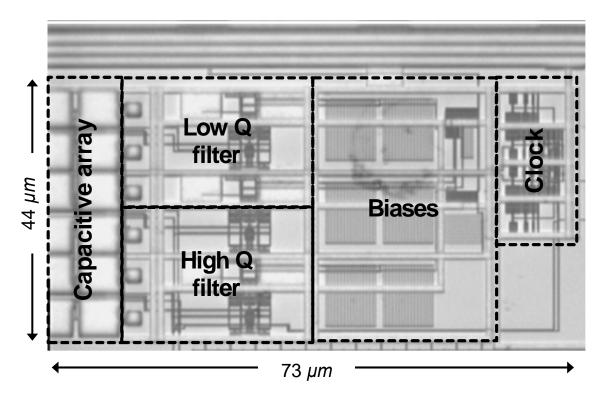

The layout was made to be as symmetric as possible to eliminate mismatches between the differential paths. A die photograph of the fabricated circuit is shown in Figure 2.12. The prototype device is fabricated in 0.18  $\mu m$  CMOS with a Metal-insulator-Metal (MiM) capacitor option and occupies 0.0032  $mm^2$  per each amplifying filter. The power consumption per each amplifier is 89  $\mu W$  per channel.

Figure 2.12: Die photograph of the fabricated device.

Testing was performed with pre-recorded neural data in the Neural Engineering laboratory (NEL) at the University of Michigan. Neural data were converted to an audio signal and supplied to the input of the prototype neural filter. The output of the circuit is delivered to an 8bit ADC and the ADC output is transmitted to a personal computer (PC) through a logic analyzer. The test board contains the fabricated neural amplifier, ADC, current sources and radio-frequency (RF) connectors for power and clock supplies. The acquired data is analyzed with a MATLAB tool.

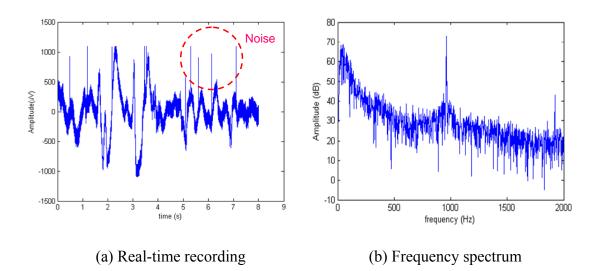

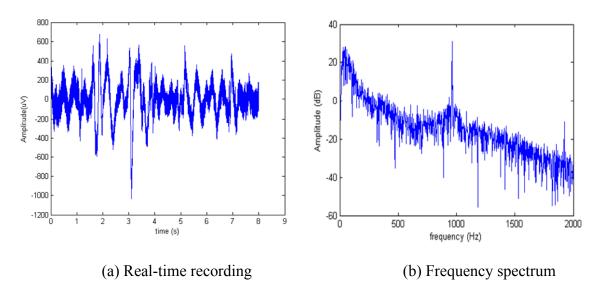

Figure 2.13 show the pre-recorded real-time fast-recording raw data (a) and the frequency responses (b) which contain spikes, LFPs and noise. The signal amplitudes are laid within the range of  $\pm 1 \ mV$  and the frequency spectrum by Fast Fourier Transform

(FFT) in the MATLAB software shows clean spikes around 1 kHz, LFPs at low frequency and high frequency noises.

Figure 2.13: Original neural signal.

The output from the first stage shows a high frequency noise reduction as shown in Figure 2.14. The gain of the filter is measured as 870.96 (58.8 *dB*). After the amplitude adjustment, the magnitude range of the real-time neural signal (a) is placed between -1 mV to 0.7 mV. We can see the high frequency noise is suppressed below the 0 *dB* level in the FFT plot (b).

Figure 2.14: *In-vitro* test output with low-*Q* bi-quad.

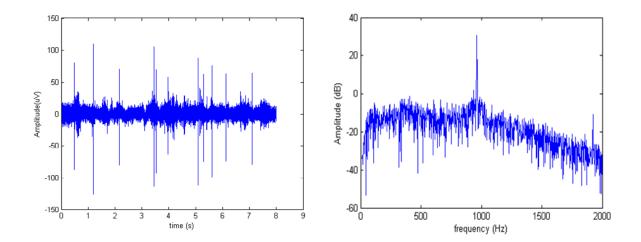

The output from the second stage shows spike trains with removing LFPs as shown in Figure 2.15. The measured gain is 90.16 (39.1 *dB*). After the amplitude adjustment, the real-time spike signal (a) range is between -125  $\mu V$  to 115  $\mu V$ . We can see the LFPs are decreased below the 0 *dB* level at the FFT plot (b).

(b) Frequency spectrum

Figure 2.15: *In-vitro* test output with high *Q* bi-quad.

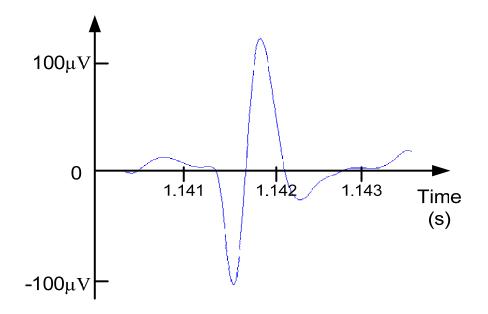

If we increase the time resolution of the real-time recording plotted in Figure 2.15 (a) in order to see spikes in details, we can see a very clean spike as shown in Figure 2.16. The duration of the spike is approximately 1 *ms* with an amplitude of 220  $\mu Vpp$ .

Figure 2.16: A single spike at the high-*Q* bi-quad output.

The noise performance is expressed in terms of an equivalent input noise, which gives the same output noise as the circuit under no other input. The device noise is measured at the output with the inputs shorted together. Then, the equivalent input noise spectral density (INSD) of the complete circuit is calculated by dividing the output noise by the gain. The measured output noise is 2.06mVrms and the equivalent input referred voltage as 2.36  $\mu Vrms$  and it represents INSD is 23.6  $nV/\sqrt{Hz}$ . This value is less than

source signal power and we can achieve an SNR as much as 30 dB. The 1/f noise components are rejected by the modulation and the INSD is flat across the signal band, since there remains only frequency independent noise sources such as thermal and shot noises. Table 2.1 shows the summary of the device.

| Spec.                       | Measured data                 |

|-----------------------------|-------------------------------|

| Power supply                | 1.8 V                         |

| Sampling frequency          | 100 <i>kS/s</i>               |

| Die size                    | $44 \ \mu m 	imes 73 \ \mu m$ |

| Power Consumption           | $89 \ \mu W/ch.$              |

| INSD                        | 23.6 $nV/\sqrt{Hz}$           |

| Pass band gain for low $Q$  | 39.1 <i>dB</i>                |

| Pass band gain for high $Q$ | 58.8 <i>dB</i>                |

| Technology                  | CMOS 0.18 μm                  |

Table 2.1: Switched-capacitor filter performance.

# CHAPTER III

## Logarithmic ADC

For a simultaneous neural recording of the spikes and local field potentials (LFPs), a two-stage filtering device, that separates the recorded neural data into a low-frequency, low-resolution signal set and a high-frequency, high-resolution spike set, is proposed in the previous chapter. Instead, a high dynamic range logarithmic analog-to-digital converter (ADC) and digital filtering can replace the analog filtering saving power consumption and area.

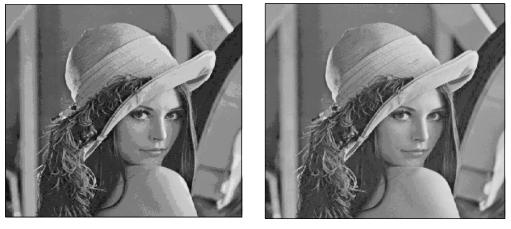

Most natural signals, including light intensity and audio amplitude, are measured on a logarithmic scale. A properly designed logarithmic coding scheme is more efficient than conventional linear encoding, in that, a higher dynamic range can be represented for a given word length. For example, Figure 3.1 shows that logarithmic coding achieves better image quality than linear coding for the same number of bits.

Expansion of dynamic range is traditionally achieved through automatic gain control (AGC) or nonlinear compression [71]. However, an AGC amplifier cannot respond to rapidly fluctuating signals. A logarithmic amplifier can be used to compress the dynamic range of an input signal [72], but this approach requires a look-up table to precisely describe the device-derived non-linear characteristics. Alternatively, a back-end digital compander [73] can be combined with a high-resolution ADC. However, this method is power-hungry and complex. Direct logarithmic analog-to-digital conversion has exactly the same beneficial characteristics as the combination of a logarithmic amplifier and linear ADC, but with potentially much lower power consumption.

(a) Linear 3bit coding

(b) Log 3bit coding

Figure 3.1: Image quality comparison for standard image [70] with 3 bit linear and 3 bit logarithmic coding.

In this chapter, we describe a logarithmic pipeline ADC technique and present a prototype logarithmic ADC which demonstrates a high dynamic range of 80 *dB* [33]. This approach is advantageous for many applications where high dynamic range is required such as audio, imaging and sensing. A novel switched capacitor (SC) logarithmic pipeline ADC architecture, that does not require squaring or any other complex analog function, is introduced in this chapter. Unlike a conventional pipeline ADC, the pipeline stages do not include an MDAC, so that the required accuracy of the reference voltage is greatly relaxed. Performance metrics such as signal-to-noise-ratio (SNR) and dynamic range are also discussed.

## **3.1.** Logarithmic pipeline architecture

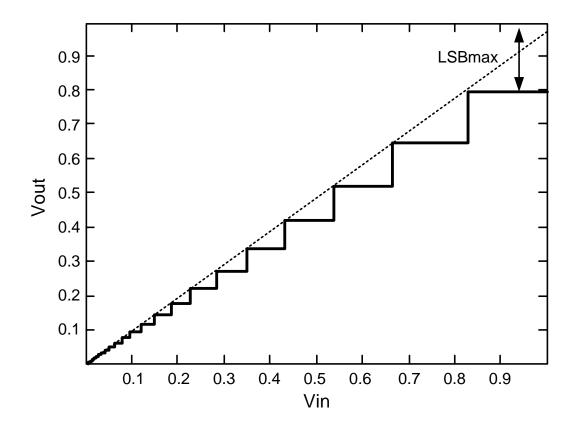

With logarithmic coding, the LSB size varies with the input signal level. Similar to a companding digitizer, small signals are quantized at fine resolution, whereas changes in large signals are quantized at coarse resolution. Figure 3.2 shows an example of a 5 bit logarithmic companding characteristic. Larger voltage input results in larger least significant bit (LSB) size.

Figure 3.2: Companding characteristics of 5 bit logarithmic quantization.

An L-bit logarithmic ADC converts an input analog voltage ( $V_{in}$ ) to a digital bit sequence ( $b_{L-1}$ ,  $b_{L-2}$ , ...,  $b_1$ ,  $b_0$ ), mapping to a logarithmic domain. This mapping equation is shown in Equation (3.1).

$$\log_{10}\left(\frac{V_{in}}{V_{range}} \times 10^{C}\right) = \frac{b_{L-1}2^{L-1} + \dots + b_{0}}{2^{L}}C$$

(3.1)

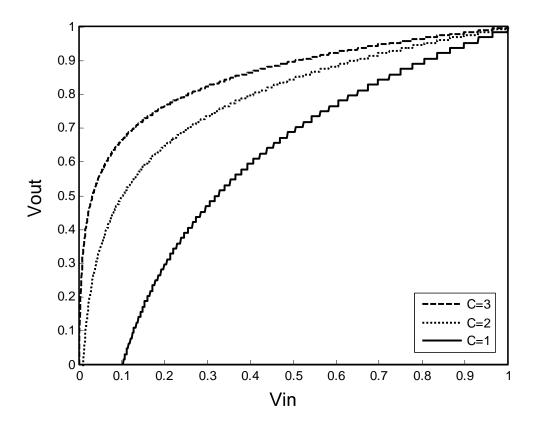

In Equation (3.1), the input voltage  $V_{in}$  is divided by the full-scale ADC input range ( $V_{range}$ ), mapping the input to a nominal range from 0 to 1. A *code efficiency* factor, *C* is introduced. Larger values of *C* result in a more logarithmic input-to-digital-output relationship, emphasizing smaller signals, and resulting in a higher dynamic range. Figure 3.3 illustrates how the code efficiency factor, *C*, affects the input-to-output relationship.

Figure 3.3: 6 bit logarithmic characteristics for three values of code efficiencies, C.

Although the LSB size of a conventional ADC,  $V_{range}/2^{L}$ , is constant over the entire input range, the logarithmic LSB size of a logarithmic ADC is  $C/2^{L}$ . As a result, the LSB size varies depending on the input amplitude. For the 8 bit logarithmic ADC, which is demonstrated in this work, *C* is set to 3, resulting in the minimum LSB size to  $1.109 \times 10^{-4} V_{range}$ . The theoretical dynamic range of considering only the positive polarity part of the logarithmic ADC range is 85 *dB*. A sign bit adds an extra 6 *dB*, resulting in a 91 *dB* theoretical dynamic range. The methodology for calculating theoretical dynamic range is presented later in this section.

Limited minimum detectable voltage due to noise, linearity, and device matching problems make practical circuit implementation with *C*>3 difficult. For example, with *C* = 2, and assuming  $V_{range}$  is 1 *V*, the minimum LSB size of 8bit ADC is 0.37 *mV*. On the other hand, with a code efficiency factor of 4 (*C* = 4), the minimum LSB size is only 7.5  $\mu V$ , which makes noise and matching difficult and impractical to overcome.

By rewriting Equation (3.1), the analog input corresponding to a digital code is given by Equation (3.2).

$$v_{in} = V_{range} \cdot 10^{C \cdot \frac{Digital \ code}{2^{L}} - C} = V_{range} \cdot 10^{C \cdot \frac{b_{L-1} 2^{L-1} + \dots + b_{0}}{2^{L}} - C}$$

(3.2)

The varying LSB size is calculated by subtracting  $v_{in}$  values from Equation (3.2) for two adjacent digital codes. Subtracting analog input values for codes 0 and 1, results in the minimum LSB size. If we subtract the analog input values corresponding to the

maximum digital codes  $2^{L}$  and  $2^{L}$ -1, we obtain the maximum LSB size. Equation (3.3) includes both the minimum and maximum LSB sizes.

$$LSB_{\text{min}} = V_{range} \times (10^{\frac{C}{2^{L}} - C} - 10^{-C}), \qquad (3.3)$$

$$LSB_{\text{max}} = V_{range} \times (1 - 10^{-\frac{C}{2^{L}}})$$

The dynamic range (DR) is defined as the ratio of the input range ( $V_{range}$ ) to the smallest resolvable signal, or the smallest difference between adjacent codes, as:

$$DR = \frac{V_{range}}{\min_{i} (V_{trip, j+1} - V_{trip, j})} = \frac{V_{range}}{LSB_{\min}}$$

(3.4)

Then, by substituting Equation (3.3), dynamic range is calculated as:

$$DR = 20 \log_{10} \frac{V_{range}}{LSB_{\min}} = -20 \log_{10} \left( 10^{\frac{C}{2^{L}} - C} - 10^{-C} \right)$$

(dB) (3.5)

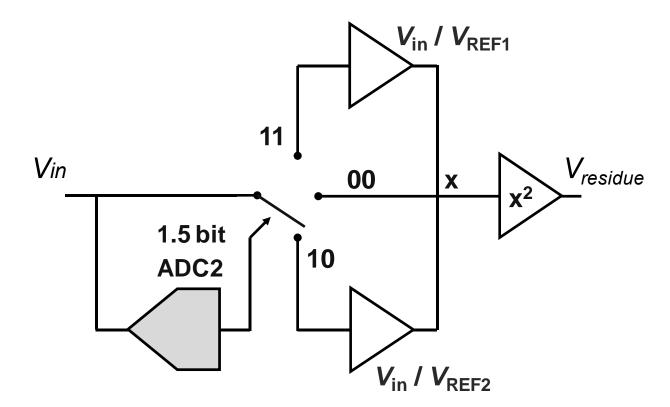

The proposed logarithmic-domain pipeline ADC architecture is based on simple scalar multiplication and does not require cumbersome analog math operations such as squaring or exponents. A direct log-adaptation of a conventional linear 1.5-bit-per-stage, pipeline ADC would replace subtraction with division, and multiplication by 2 with squaring [54]. Since  $log_{10}V_{in}$  -  $log_{10}V_{ref} = log_{10}(V_{in}/V_{ref})$  in a logarithmic pipeline ADC, a conditional attenuation (or gain) replaces subtraction, depending on the decision of the sub-ADC. This pipeline stage differs from a conventional 1.5 bit pipeline ADC's multiplying digital-to-analog converter (MDAC), which uses a linear stage that subtracts one of three MDAC settings; Instead, the logarithmic 1.5-bit-per-stage architecture presented here sets three different inter-stage gains. These three gains are achieved by switching in different values of feedback capacitance across an OpAmp. Figure 4 shows the three gain setting from the previous stage output ( $V_{in}$ ) to the current stage output ( $V_{residue}$ ). The 1.5 bit sub-ADC determines the stage gain and the residue plot.

Figure 3.4: Implementation of the logarithmic pipeline.

Although figure 3.4 also includes a squarer, we see next how squaring is eliminated in this log ADC architecture. In a log ADC, squaring is equivalent to a multiplication by 2 in a radix-2 pipeline ADC. Instead of attempting precise analog squaring, we achieve the same overall result by scaling the comparator reference voltages and gain settings for each pipeline stage (A similar scheme is proposed in [74]). In a logarithmic pipeline ADC, the residue of each stage is scaled to the full-scale input voltage range of the next stage. Considering that  $2xlog_{10}(Vresidue) = log_{10}(Vresidue^2)$ , this requires squaring of the residue, but accurate and reliable squaring is difficult in the analog domain.

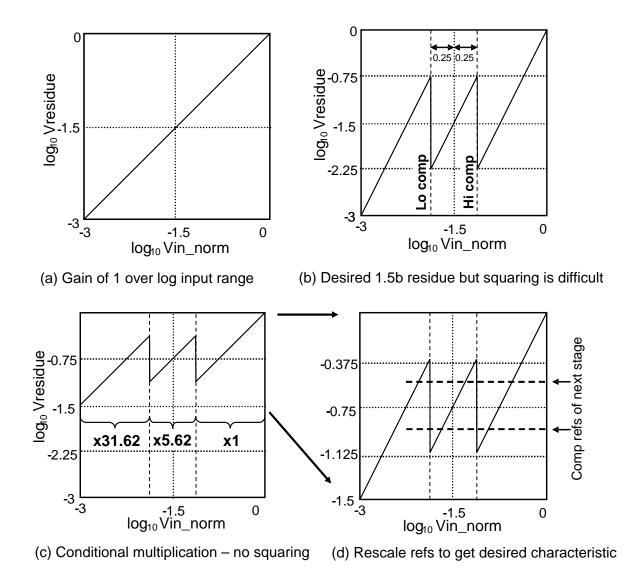

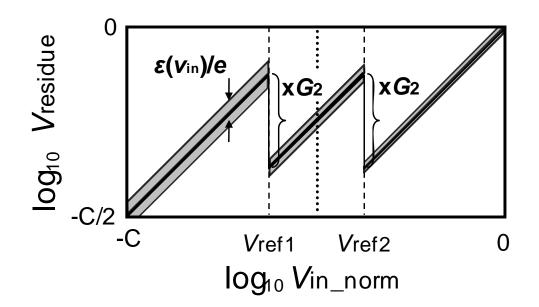

Figure 3.5: Logarithmic ADC residue plots.

Figure 3.5 (b) shows the residue characteristic of a 1.5 bit logarithmic ADC pipeline stage. For comparison, a direct linear relationship between input and output is plotted in Figure 3.5 (a). The residue plots are described on a logarithmic sale with a normalized  $\log_{10}$  range from -3 to 0 (i.e. C = 3). The residue of figure 3.5 (b) is divided into three regions as there are two comparators. A modified approach in figure 3.5 (c)

uses the same comparator thresholds, but the gain settings are chosen so that the residue now falls entirely into the top vertical half (i.e. logarithmic range: -1.5 to 0, or a corresponding linear range:  $10^{-1.5}$  to 1). Squaring of the residue of figure 3.5 (c) would double its logarithmic range to appear identical to the residue of figure 3.5 (b). However, instead of squaring, a different set of comparator reference voltages is chosen for the next stage. The reference voltages are set in the top half of figure 3.5 (c), effectively achieving a rescaled residue with the same shape (Figure 3.5 (d)). This approach is not only easier to implement but also advantageous since the reference and signal voltages become larger (i.e. closer to a normalized logarithmic value of 0) going down the pipeline. For example, the upper threshold of the second stage is 137 *mV* whereas, that of the first stage is 31.6 *mV*. Larger references are easier to generate and have more tolerance for comparator errors.<sup>1</sup>

The classic 1.5-bit-per-stage redundancy scheme used in linear pipeline ADCs [75] is adapted here to reduce the required accuracy of the comparators. Unlike the case with a linear pipeline, reference voltages are not used in MDAC stages, and therefore, redundancy significantly reduces the required accuracy of both the comparators and voltage references. In a 1.5 bit stage, the input range of each stage is divided into three regions, corresponding to the three possible outputs of the two comparators: "00", "01" and "11". Redundancy can correct for both comparator offset errors and reference voltage errors with a range given by Equation (3.6).

<sup>&</sup>lt;sup>1</sup> This log ADC architecture is fundamentally different to a classical linear pipeline architecture. A 1 bit per stage pipe subtracts binary weighted values of the reference from the input, attempting to reach a final residue of zero. On the other hand, this log pipeline gains up the input at each stage, ultimately attempting to achieve a residue of full scale.

$$\Delta V_{in,correct} = \log_{10} V_{ref} \pm (1/4) \log_{10} V_{ref}$$

(3.6)

The easiest way to calculate the reference voltages is to begin on a logarithmic scale and then to return to linear scale. For the residue plot of  $i^{th}$  stage, the center of the *x*-axis is at  $-C/2^i$  on a logarithmic scale. If Equation (3.6) for digital correction is applied, the reference voltages are defined as:

$$\log_{10} \frac{V_{ref}}{V_{range}} = -\frac{C}{2^{i}} (1 \pm \frac{1}{4})$$

$$V_{ref1} = V_{range} \times 10^{-\frac{1.25C}{2^{i}}}, V_{ref2} = V_{range} \times 10^{-\frac{0.75C}{2^{i}}}$$

(3.7)

where  $Vref_1$  is the lower threshold and  $Vref_2$  is the upper threshold. Similarly, the gains for stage *i* are:

$$\log_{10} G_{1} = \frac{C}{2^{i}} \log_{10} G_{2} = \frac{C}{2 \cdot 2^{i}} \log_{10} G_{3} = 0$$

$$G(v_{in}) = \begin{cases} G_{1} = 10^{\frac{C}{2^{i}}} & v_{in} \leq V_{ref 1} \\ G_{2} = 10^{\frac{C}{2^{i+1}}} & V_{ref 1} < v_{in} \leq V_{ref 2} \\ G_{3} = 1 & V_{ref 2} < v_{in} \leq V_{range} \end{cases}$$

(3.8)

In Equation (3.8),  $G_1$  is the highest gain setting for stage inputs less than  $Vref_1$ ;  $G_2$  is the gain for the stage inputs that lie between  $Vref_1$  and  $Vref_2$ ; and  $G_3$  is the bypass gain for the stage inputs larger than  $Vref_2$  for the i<sup>th</sup> stage. Note that  $G_1 = G_2^2$ .

In a conventional pipeline ADC, gain errors are caused by capacitor mismatch, finite opamp gain, and incomplete settling of the residue amplifiers. These gain errors reduce the linearity of the ADC. While both MDAC errors and gain errors are sources of nonlinearity in a conventional pipeline ADC, only gain errors contribute to nonlinearity in this logarithmic pipeline structure because it does not include an MDAC.

Ideally, a stage output is the product of the input signal and the gain;  $v_{out} = v_{in}$  $G(v_{in})$ , where  $G(v_{in})$  is the ideal (closed-loop) gain of the interstage amplifier defined in Equation (3.8). If we express the total gain error as  $\varepsilon(v_{in})$ , then the actual gain is  $G(v_{in})(1+$  $\varepsilon(v_{in}))$ . For example, without gain error, the mid-gain range of the first stage of the prototype ADC is 5.62, but varies from 5.57 and 5.68 with a ±1% capacitor mismatching error. If we express the relationship between the input and output of each pipeline stage in the logarithmic domain, the stage output or residue can be written as Equation (3.9):

$$\log_{10} v_{out} = \log_{10} v_{in} + \log_{10} G(v_{in}) + \log_{10} (1 + \varepsilon(v_{in}))$$

(3.9)

If  $\varepsilon$  is small ( $|\varepsilon(v_{in})| \ll 1$ ), we can approximate  $\log_{10}(1 + \varepsilon(v_{in})) \approx \varepsilon(v_{in})/e$ , where *e* is the natural logarithmic constant ( $e \approx 2.718$ ) giving:

$$\log_{10} v_{out} = \log_{10} v_{in} + \log_{10} G(v_{in}) + \mathcal{E}(v_{in})/e$$

(3.10)

A new residue plot considering gain error is drawn in Figure 3.6. The last term in this equation,  $\varepsilon(v_{in})/e$ , causes an undesired gain shift of  $\varepsilon(v_{in})/e$  in logarithmic domain. The  $\varepsilon(v_{in})/e$  term represents the input referred error in the logarithmic relationship between the stage input and output.

Figure 3.6: 1.5 bit residue plot and error due to finite gain

The gain error,  $\varepsilon(v_{in})$ , can be divided into a random component and a systematic component;  $\varepsilon(v_{in}) = \varepsilon_r + \varepsilon_f(v_{in})$ . The random part,  $\varepsilon_r$ , is due to device imperfections, in particular capacitor mismatch. On the other hand, the systematic component,  $\varepsilon_f(v_{in})$ , results from deficient amplifier gain and is inversely proportional to the feedback factor( $\beta$ ). In other words, the systematic component of gain error is predictable if we know the feedback factor and the operational amplifier (Op Amp) gain.

The systematic gain error can be derived from finite DC gain as:

$$\varepsilon_{f}(v_{in}) = \frac{1}{G(v_{in})} \cdot \frac{A_{0}}{1 + \beta A_{0}} - 1 = -\frac{G(v_{in})}{G(v_{in}) + A_{0}} \approx -\frac{G(v_{in})}{A_{0}} \quad (3.11)$$

Where  $A_0$  is the Op Amp gain, and we assume that  $\beta$ , the feedback factor is the inverse  $G(v_{in})$ , the ideal gain.

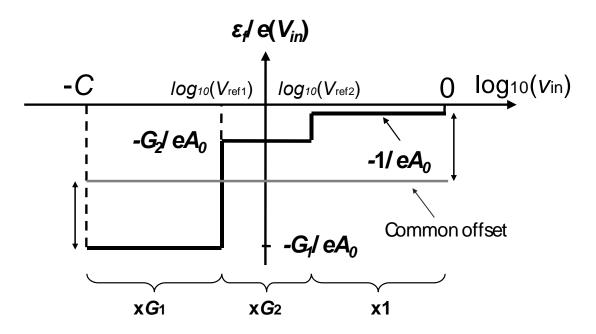

Using this approximation for gain error, Figure 3.7. plots the systematic component of the closed-loop stage gain error due to finite direct current (DC) gain. The gain error depends on the gain setting, and therefore there is a different gain error for each of the three input regions defined in Equation (3.8). The absolute value of gain error in the low-range is much larger than that in the mid-range since  $G_1$  is the square of  $G_2$ .

Figure 3.7: Input-referred systematic gain error due to finite OpAmp gain for a 1.5b

logarithmic stage.

The grey line in the figure represents the common offset  $(-(G_1+1)/2eA_0)$  which is the average of the maximum gain error in the low range and the minimum gain error in the high range. Then, the distances from common line to the low range gain error and the high gain range error are same, and it leads to the effective systematic error which is the maximum distance from the errors to common offset as  $(G_1-1)/2eA_0$ .

To guarantee the overall ADC linearity, this effective systematic error should be less than the LSB size. Note that in an 8bit logarithmic ADC an LSB =  $C/2^{L-1} = 0.023$ in logarithmic domain. Combining with Equation (3.10), the effective gain error due to finite DC gain in the logarithmic domain is then expressed as  $\varepsilon_f/e(=(G_1-1)/2eA_0)$ . To achieve an INL less than 0.5 LSB, the maximum gain error of the first stage can be up to 3.1%, compared to only 0.62% [76] in an 8bit linear ADC. Unlike a linear ADC the logarithmic ADC which does not include an MDAC, further reducing the requirements for linearity. The non-linearity error caused by MDAC is larger in practice than the nonlinearity caused by gain error in linear ADCs [76]. From the above criteria, we can estimate the gain requirement of the Op Amp limited by the finite DC gain from feedback as:

$$\frac{G_1 - 1}{2eA_0} > \frac{LSB}{K} \quad \Longrightarrow \quad A_0 > \frac{G_1 - 1}{2e} \cdot \frac{K}{LSB} = \frac{10^{\frac{C}{2^i}} - 1}{2e} \cdot \frac{K \cdot 2^{L-1}}{C} \tag{3.12}$$

Where K is the number of inter-stage Op Amps which cause gain errors, C is the code efficiency factor. Since the effect of gain error is cumulative over all stages, the gain error margin should be spread over the pipeline stages as a factor of K. K is 5 for the

prototype 8bit logarithmic ADC and *C* is 3. As shown in Equation (3.12), the gain requirement decreases exponentially down the pipeline. To achieve an integral non-linearity (INL) less than 1 LSB, the minimum Op Amp gain of the first stage should be greater than 1202 (= 61.6 dB), but only 182 (= 45.2 dB) in the second stage.

The thermal noise of the first stage is the dominant source of noise, since the first stage gain is large enough to minimize the input referred noise contribution of other stages. The input referred noise of  $i^{\text{th}}$  stage of an SC amplifier is given by [77],

$$v_{ni}^{2} = \frac{2kT}{C_{i}} + \frac{8kT}{g_{m1}}B_{n} = \frac{2kT}{C_{i}} + \frac{2kT}{(2+G_{i})C_{i}}$$

(3.13)

Where  $C_i$  is the sampling capacitor of  $i^{th}$  stage,  $g_{ml}$  is the transconductance of input transistors and  $B_n$  is the noise bandwidth that is  $g_{ml}/4(2+G_i)C_i$  [77] and  $G_i$  is the high gain of  $i^{th}$  stage. The first term is the sampling noise and the second is thermal noise in the hold phase. If we neglect the parasitic capacitances, the total input referred noise power can be calculate as:

$$v_n^2 = v_{n,SH}^2 + v_{n1}^2 + \frac{v_{n2}^2}{G_1^2} + \dots \approx \frac{14\,kT}{3C_i} + \frac{2kT}{G_1^2(2+G_i)C_i}$$

(3.14)

Where  $v_n^2$  is the total input-referred noise power,  $v_{n,SH}^2$  is the noise of the sample and hold amplifier,  $v_{nl}^2$  is the noise of the first stage and  $v_{n2}^2$  is the noise of the second stage. Since the gain of the first stage is relatively large, the noise contribution from second stage can be ignored. For C = 3, the high gain of the first stage is 31.6 and then, the total input referred noise is  $4.67kT/C_i$  ( $V^2$ ). To sense the minimum detectable signal,  $1.1 \times 10^{-4} V_{range}$ , for C = 3 at room temperature, the minimum input capacitor size is obtained as,

$$C_{i} = \frac{4.67 \ kT}{\left(1.1 \times 10^{-4}\right)^{2}} = 1.92 \ pF \tag{3.15}$$

#### **3.2.** Logarithmic ADC implementation