# FRACTIONAL-N SYNTHESIZER ARCHITECTURES WITH DIGITAL PHASE DETECTION

by

#### Mark A. Ferriss

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 2008

## **Doctoral Committee:**

Professor Michael Flynn, Chair Professor Dennis M. Sylvester Assistant Professor Jerome P. Lynch Assistant Professor David D. Wentzloff © Mark A. Ferriss 2008

## **ACKNOWLEDGENTS**

Thanks Everyone!

Firstly, I would like to thank my advisor, Professor Michael Flynn. It has been a long journey to get here, and Professor Flynn provided just the right combination of support, prodding and technical advice to get me through my Ph.D. I would also like to thank the rest of my committee members: Professor Dennis Sylvester, Professor Jerome Lynch, and Professor David Wentzloff. They were always approachable and had useful advice.

I couldn't have survived this process if it wasn't for the support of all our group members, past and present who helped with both technical support, and keeping each other sane when working the many late nights in the Michigan winters. In no particular order these include Ivan Bogue, Joshua Jaeyoung Kang, Jongwoo Lee, David Lin, Junyoung Park, Andres Tamez, Chun Chieh Lee, Li Li, Shahrzad Naraghi, Jorge Pernillo, Dan Shi, Jia-Yi Chen, Sunghyun Park, and Fatih Kocer.

I'd also like to thank Intel and the WIMS Engineering Research Center for funding this research project. This work would not have been possible without their generous support.

# **CONTENTS**

| Acknow    | ledgents                                                 | ii |

|-----------|----------------------------------------------------------|----|

| List of f | igures                                                   | vi |

| List of a | ppendices                                                | X  |

| Abstract  |                                                          | xi |

| СНАРТ     | TER 1 INTRODUCTION                                       | 1  |

| 1.1       | Background                                               | 1  |

| 1.2       | A brief overview of Radio Frequency transmission schemes | 4  |

| 1.3       | Introduction to the PLL                                  | 6  |

| 1.4       | A practical example of a modern PLL                      | 8  |

| 1.5       | A first attempt at non-integer based division            | 9  |

| 1.6       | A brief introduction to the $\Sigma\Delta$ modulator     | 11 |

| 1.7       | A conventional Fractional-N PLL(FPLL)                    | 14 |

| 1.8       | The programmable frequency divider                       | 15 |

| 1.9       | Chapter summary                                          | 16 |

| 1.10      | Thesis Contributions                                     | 17 |

| СНАРТ     | TER 2 DIGITAL PHASE DETECTION                            | 18 |

| 2.1       | Background                                               | 18 |

| 2.2       | A Time to Digital Converter (TDC)                        | 20 |

| 2.3       | A single bit phase quantizer as a phase detector         | 21 |

| 2.4       | Phase Minimization Loop (PML)                            | 23 |

| 2.5       | Viewed from a <i>Delta Modulator</i> perspective         | 26 |

| 2.6       | Comparison between the PML and a frequency discriminator | 28 |

| 2.7       | Desensitization to phase detector gain                   | 29 |

| СНАРТ | TER 3 PHASE NOISE AND SMALL SIGNAL MODELING                              | 32 |

|-------|--------------------------------------------------------------------------|----|

| 3.1   | Modeling assumptions                                                     | 32 |

| 3.2   | Phase detector modeling                                                  | 33 |

| 3.3   | Estimating the amount of the $\Sigma\Delta$ noise at the quantizer input | 37 |

| 3.4   | Transfer function of the other blocks                                    | 40 |

| 3.5   | The loop transfer functions                                              | 43 |

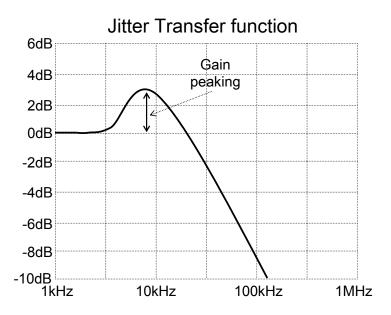

| 3.6   | Gain (and Jitter) peaking                                                | 46 |

| 3.7   | Additional comments on PLL Type                                          | 50 |

| 3.8   | Methodology for calculating output phase noise                           | 52 |

| 3.9   | Reference transfer function                                              | 55 |

| 3.10  | Divider $\Sigma\Delta$ quantization noise                                | 56 |

| 3.11  | Phase detector flip-flop quantization noise                              | 57 |

| 3.12  | VCO phase noise                                                          | 58 |

| 3.13  | DAC ΣΔ noise                                                             | 58 |

| 3.14  | Summing the noise sources to get the total output phase noise            | 58 |

| СНАРТ | TER 4 HIGH SPEED FREQUENCY MODULATION                                    | 61 |

| 4.1   | Introduction                                                             | 61 |

| 4.2   | Comparison with other techniques                                         | 62 |

| 4.3   | The proposed scheme                                                      | 65 |

| 4.4   | Implementation details                                                   | 70 |

| СНАРТ | TER 5 DESCRIPTION OF PROTOTYPE                                           | 73 |

| 5.1   | Overview                                                                 | 73 |

| 5.2   | A ΣΔ digital to analog Converter                                         | 74 |

| 5.3   | The Voltage Controlled Oscillator (VCO)                                  | 77 |

| 5.4   | The design of a low headroom Output Buffer                               | 79 |

| 5.5   | A Pseudo-Random Bit Sequence (PRBS) generator                            | 80 |

| 5.6   | A high speed asynchronous divider                                        | 81 |

| 5.7   | The Analog Multiplexer                                                   | 83 |

| 5.8   | Prototype layout                                                         | 84 |

| CHAPTER 6 MEASUREMENT RESULTS |                              | 86  |

|-------------------------------|------------------------------|-----|

| 6.2                           | Phase noise measurements     | 87  |

| 6.3                           | Frequency switching scheme   | 88  |

| 6.4                           | Comparisons with other works | 91  |

| CHAP'                         | TER 7 CONCLUSION             | 93  |

| 7.1                           | Dissertation Summary         | 94  |

| 7.2                           | Key Contributions            | 94  |

| 7.3                           | Ideas for future work        | 95  |

| APPEN                         | NDICES                       | 97  |

| BIBLI                         | OGRAPHY                      | 108 |

# LIST OF FIGURES

| Figure 1.1 : An overview of a transmission scheme. A quartz based clock is up-converted to high frequencies and modulated with transmission data before the Power Amplifier                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2 : Possible uses of synthesizers in an RF transmission scheme. a) In a direct conversion transmitter. b) Using just the FPLL as a modulator.                                           |

| Figure 1.3 : A simple PLL includes a Phase/Frequency detector, a Loop Filter, and a Voltage Controlled Oscillator.                                                                               |

| Figure 1.4 : A standard PLL. A charge pump is used to convert the output signals form the phase detector to a voltage.                                                                           |

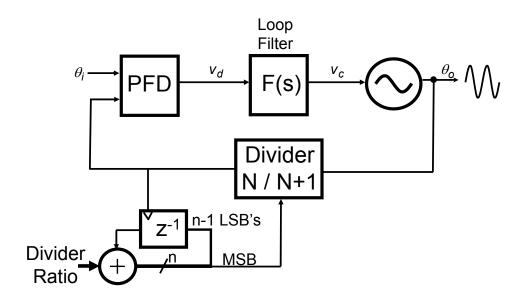

| Figure 1.5 : A first attempt at a Fractional-N Synthesizer [18]. The MSB from an accumulator controls the divider. The LSBs are recycled so there is no DC divider error.                        |

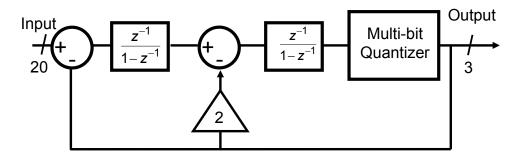

| Figure 1.6 : A second order digital $\Sigma\Delta$ modulator, which includes two integrators, and a quantizer                                                                                    |

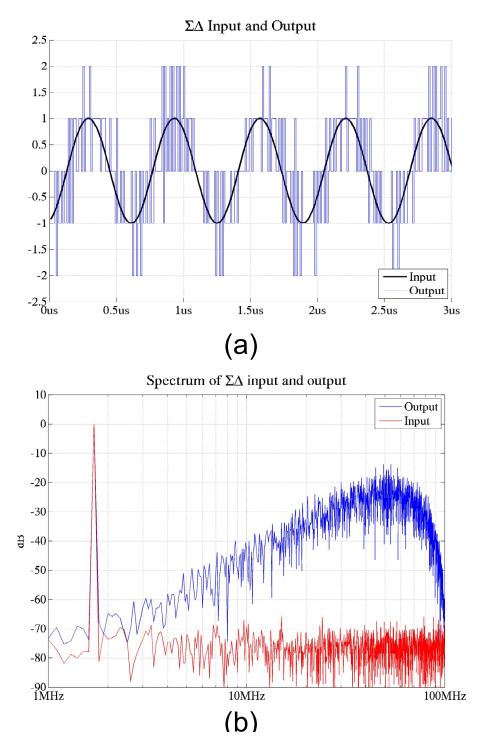

| Figure 1.7 Waveforms at input and output of the $\Sigma\Delta$ . (b) The spectrum of the input and output.                                                                                       |

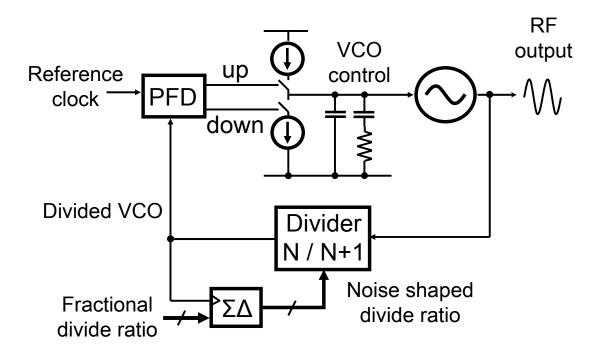

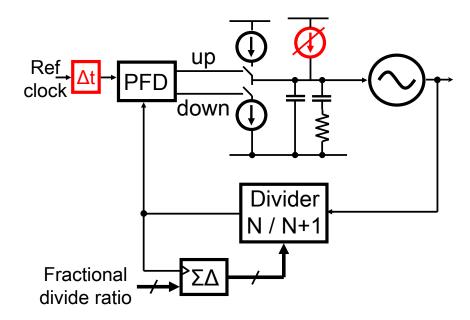

| Figure 1.8 : A conventional fractional-N synthesizer. In this example a $\Sigma\Delta$ modulator controls the programmable divider.                                                              |

| Figure 1.9 : A simple 2/3 Divider.                                                                                                                                                               |

| Figure 1.10 : A 8/9 bit asynchronous divider. The additional control logic tells the %2/3 to divide by 3 once per output period.                                                                 |

| Figure 2.1 : A conventional fractional-N synthesizer (Reproduced from Figure 1.8) 18                                                                                                             |

| Figure 2.2 : (a) A Flash analog-to-digital converter. (ADC) (b) A simplified time-to-digital converter (TDC), which can be considered a flash converter acting on phase 20                       |

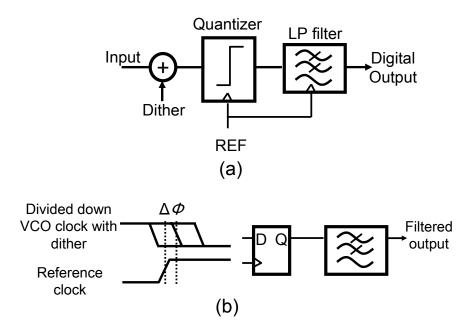

| Figure 2.3 : (a) Conceptual overview of a 1bit ADC. (b) Using a flip-flop as a phase quantizer. If dither is added to the input, the quantizer's output can be filtered, to reproduce the input. |

| 10p104400 010 11p40                                                                                                                                                                              |

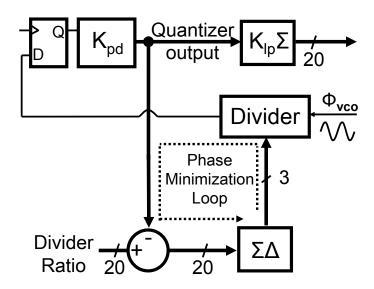

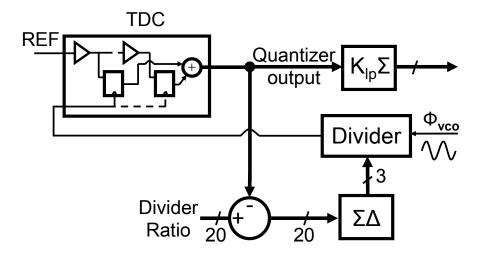

| Figure 2.4 : New Phase detector configuration with the Phase Minimization Loop (PML). The quantized phase information is fed back to the input of the $\Sigma\Delta$ .                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

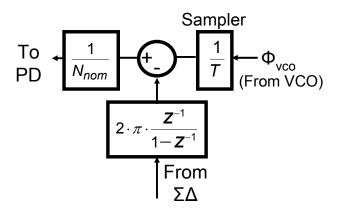

| Figure 2.5 : The small signal phase domain model of the programmable divider. It includes an integrator in the control path                                                                                                                          |

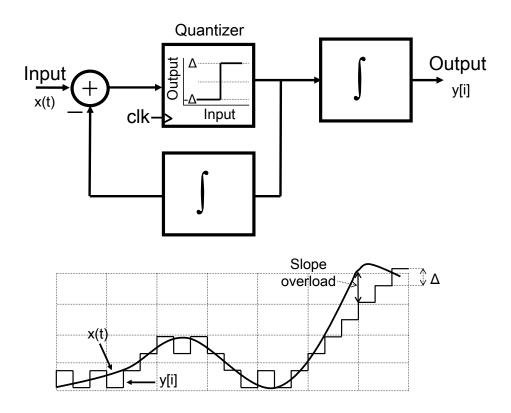

| Figure 2.6 : A delta modulator is a commonly used precursor to a $\Sigma\Delta$ modulator. There are two types of errors; slope overload and quantization error                                                                                      |

| Figure 2.7 : A simplified continuous time version of the PML feedback system. $K_1$ includes the phase quantizer gain.                                                                                                                               |

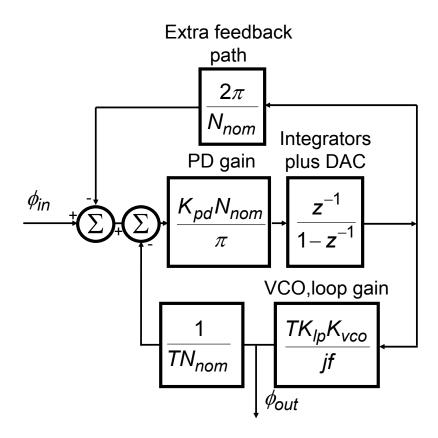

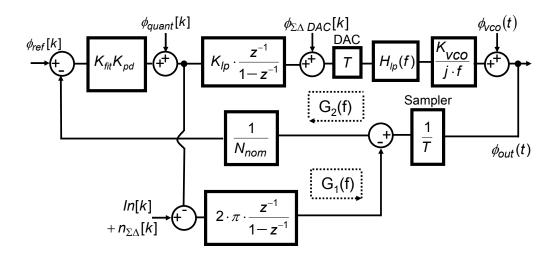

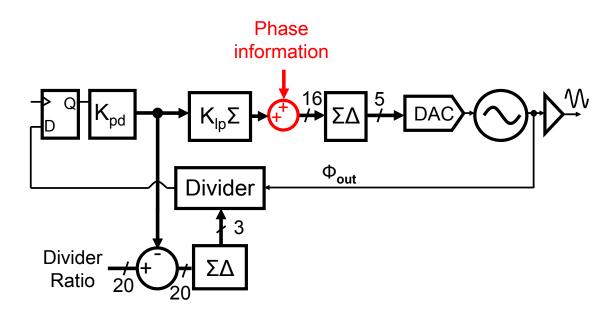

| Figure 2.8 : The overall architecture of the proposed FPLL, including the new phase detection scheme.                                                                                                                                                |

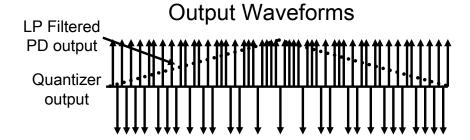

| Figure 3.1 : Waveforms approximating the signals at the phase detector output 33                                                                                                                                                                     |

| Figure 3.2 : In this example VCO's input, and hence the excess phase at the output, increases and then decreases. The output of the phase quantizer is either 1 or -1, but after being low pass filtered it resembles the required phase information |

| Figure 3.3 : (a) The path from the $\Sigma\Delta$ to the quantizer input (b) The phase domain model, which includes an integrator in the divider's control path                                                                                      |

| Figure 3.4 : Simulation experiment setup. The input is subtracted from the output of a $\Sigma\Delta$ modulator, leaving only the error. This is then integrated, and plotted on a histogram 38                                                      |

| Figure 3.5 Histogram of samples from the integrator output                                                                                                                                                                                           |

| Figure 3.6 : An overview of the small signal model for the FPLL                                                                                                                                                                                      |

| Figure 3.7 : Overview of small signal model for outer loop (Loop 2), with Loop 1 replaced by its equivalent transfer function.                                                                                                                       |

| Figure 3.8 : A typical response for a second order system including gain peaking 46                                                                                                                                                                  |

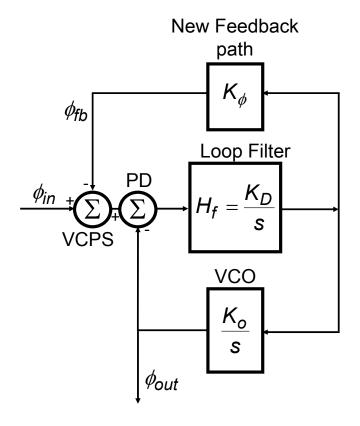

| Figure $3.9$ : Simplified architecture for a D/PLL. There are two feedback paths, one through the VCO, and the other through the Voltage Controlled Phase Shifter (VCPS). 48                                                                         |

| Figure 3.10 : Redrawn version of new architecture. The digital integrator represents both the integrator at the output of the flip-flop, and the integrator caused by the divider 50                                                                 |

| Figure 3.11 : Small signal model incorporating all of the noise sources which are considered.                                                                                                                                                        |

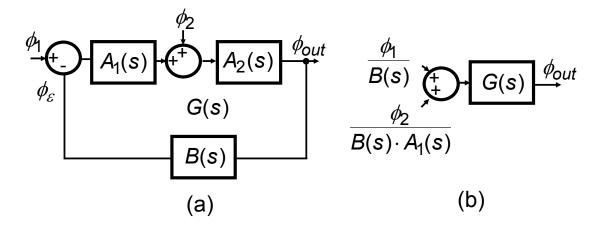

| Figure 3.12 : A brief review of feedback systems with multiple inputs. (a) System overview with two inputs. (b) Representing each of the transfer functions in terms of G(f).                                                                        |

|                                                                                                                                                                                                                                                      |

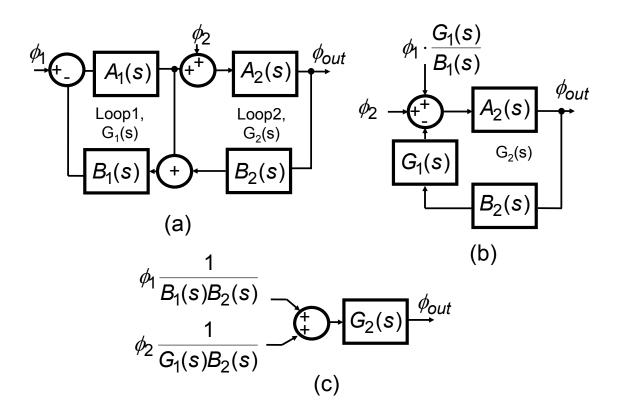

| Figure 3.13 : Calculating the output phase noise for a dual loop (a) System overview (b) Converted into a single loop (c) overall transfer function, simplified                                                     | _    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

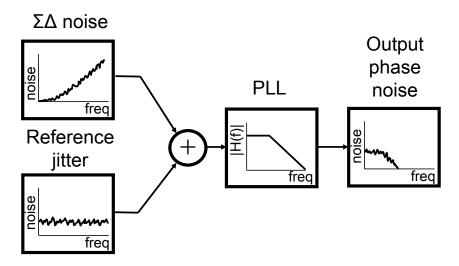

| Figure 4.1 : A PLL is often used to filter noise sources. In particular, high frequency noise sources such as $\Sigma\Delta$ noise can be effectively filtered by the PLL's low loop bandwidth.                     | . 62 |

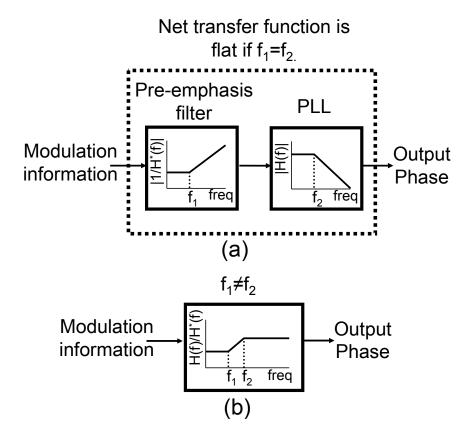

| Figure 4.2 : (a) Overview of pre-emphasis, where a digital filter is used to estimated the approximate inverse of the PLL characteristics. (b) Exact knowledge of the loop is needed, or the filters will mismatch. |      |

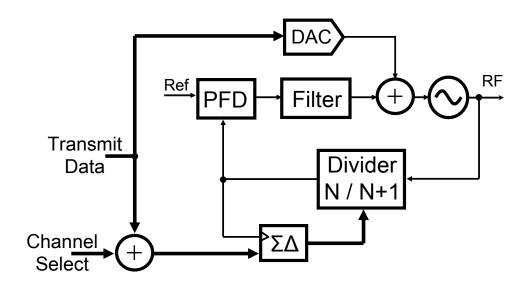

| Figure 4.3 : Overview of two point modulation. The transmit data is added both to the input to the $\Sigma\Delta$ and to the input to the VCO.                                                                      | . 64 |

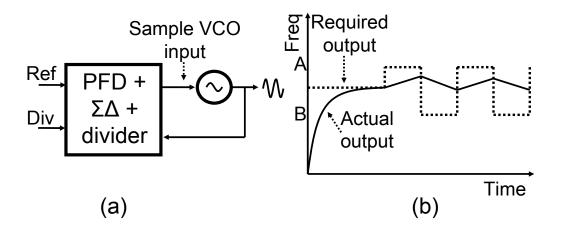

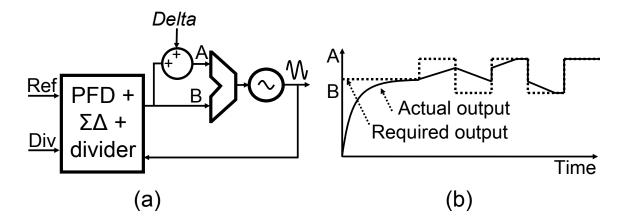

| Figure 4.4 (a): Simplified PLL. Input to VCO is analogous to the output frequency. (b) Plot of required output versus actual output.                                                                                |      |

| Figure 4.5 (a): PLL with Delta added. (b): Plot of output frequency.                                                                                                                                                | . 66 |

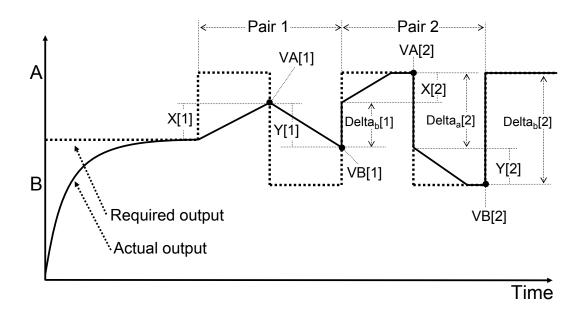

| Figure 4.6: Detailed timing diagram of the settling characteristics of the loop                                                                                                                                     | . 67 |

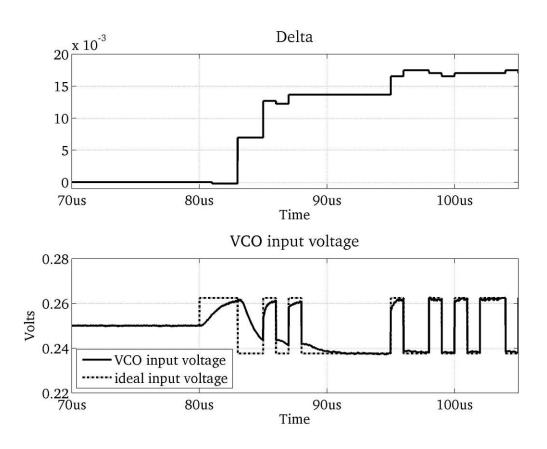

| Figure 4.7: Behavioral simulation results. The top plot shows delta, which starts at zer and quickly grows to the required size. The bottom plot shows the ideal and the actual VCO input waveforms.                |      |

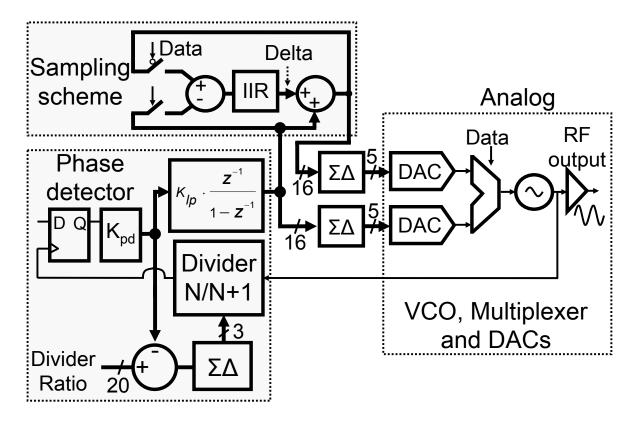

| Figure 4.8 : Details of the sampling scheme.                                                                                                                                                                        | . 70 |

| Figure 4.9 : The complete architecture including the digital phase detector and the proposed sampling scheme.                                                                                                       | . 72 |

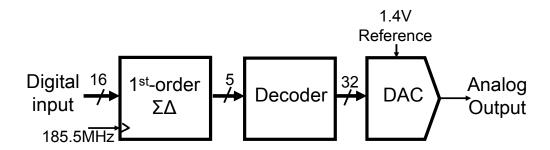

| Figure 5.1 : Overview of DAC scheme. Includes a $\Sigma\Delta$ modulator, a decoder and a resis string DAC.                                                                                                         |      |

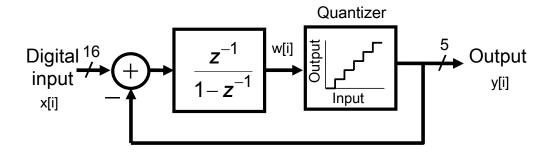

| Figure 5.2 : Overview of a first order $\Sigma\Delta$ .                                                                                                                                                             | . 75 |

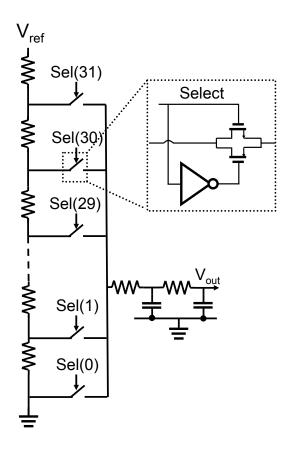

| Figure 5.3 : An overview of the resistor string DAC with a reconstruction filter at the output.                                                                                                                     | . 77 |

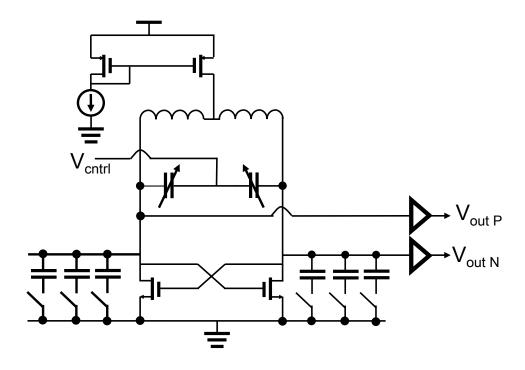

| Figure 5.4 : VCO overview                                                                                                                                                                                           | . 78 |

| Figure 5.5: Measure VCO Phase noise. (a) The VCO is configured in open loop. i.e. w the rest of the PLL turned off. (b) The measured noise of the VCO by its self                                                   |      |

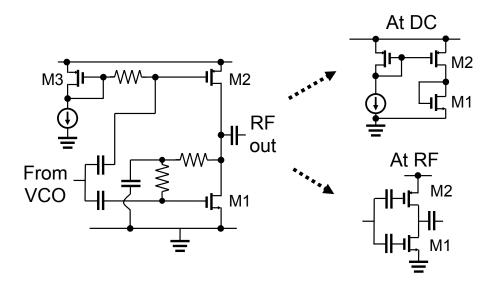

| Figure 5.6 : A push-pull Output buffer which automatically sets its output bias point without additional circuitry.                                                                                                 | . 80 |

| Figure 5.7 : Programmable Divider; Architecture and logic.                                                                                                                                                          | . 81 |

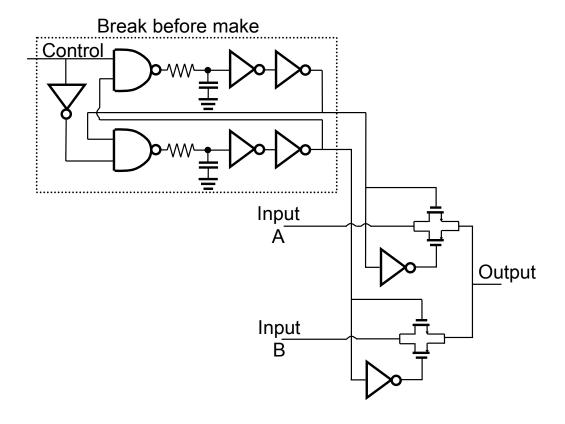

| Figure 5.8 : Overview of the analog multiplexer                                                                                                                                                                     | . 84 |

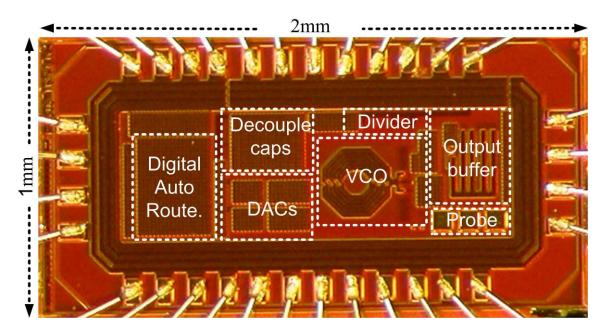

| Figure 5.9 : Micrograph of Prototype                                                                                                                                                     | 85    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

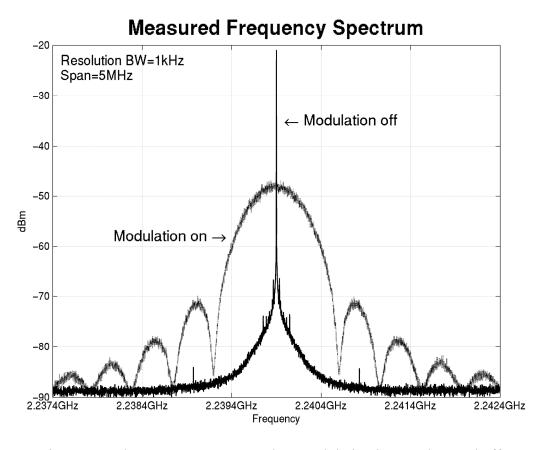

| Figure 6.1: The output spectrums, when modulation is turned on and off                                                                                                                   | 86    |

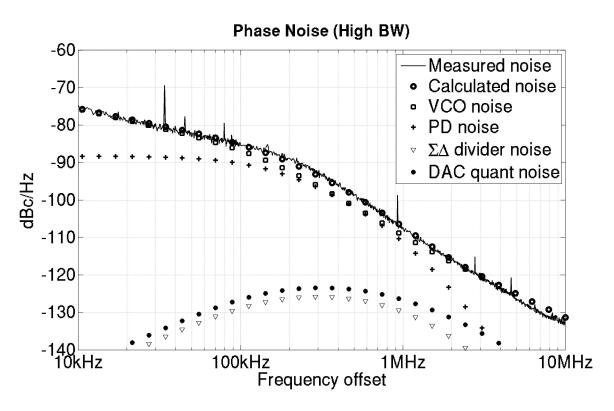

| Figure 6.2: Plot of measured and calculated noise sources. The noise is dominated at high frequencies by the VCO, at mid frequency ranges the phase quantizer noise is also significant. | so    |

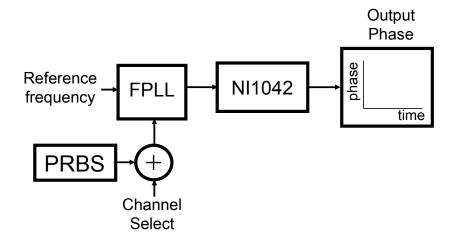

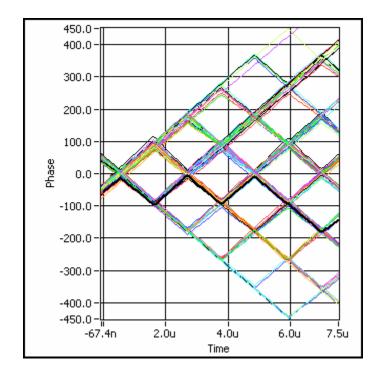

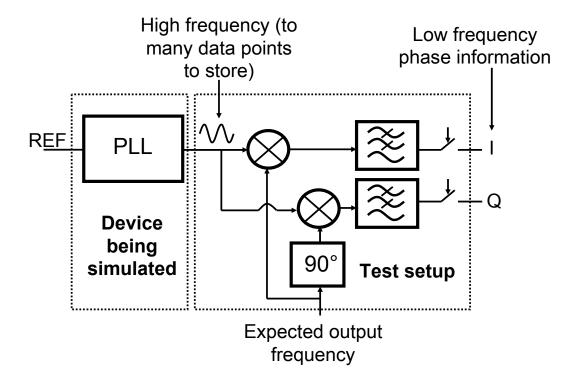

| Figure 6.3: Test setup for measuring the phase Trellis diagram at the output                                                                                                             | 89    |

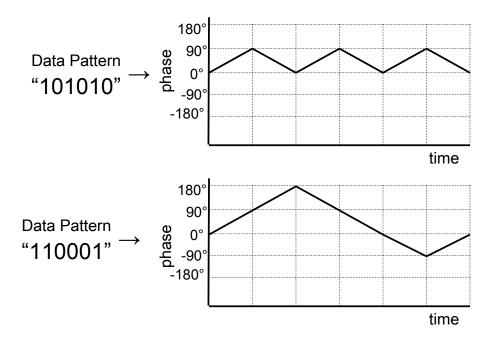

| Figure 6.4 : Expected phase changes for different data patterns.                                                                                                                         | 90    |

| Figure 6.5: Trellis diagram of the output phase, as measured from silicon                                                                                                                | 90    |

| Figure 7.1 : Using a TDC with the PML.                                                                                                                                                   | 95    |

| Figure A.1 : Alternative phase variation techniques                                                                                                                                      | 99    |

| Figure A.2 : Digital Phase control technique                                                                                                                                             | . 100 |

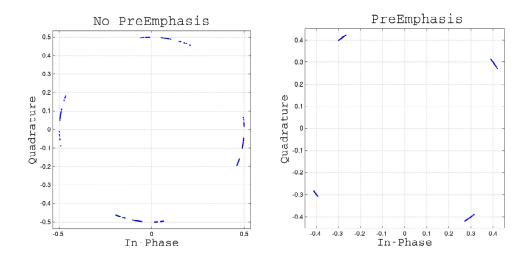

| Figure A.3 (a) Direct phase modulation, (b) with pre-emphasis                                                                                                                            | . 102 |

| Figure B.1 : Simulation technique used to avoid keeping too many data points                                                                                                             | . 105 |

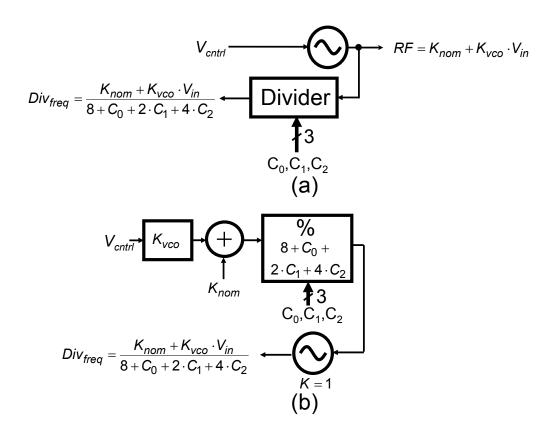

| Figure B.2 : The VCO and divider. (a) The actual configuration. (b) The behavioral model                                                                                                 | . 106 |

# LIST OF APPENDICES

| APPENDIX A DIRECT PHASE MODULATION |                                       | 98  |

|------------------------------------|---------------------------------------|-----|

| A.1                                | Phase control with a digital PLL      | 98  |

| A.2                                | Pre-emphasis                          | 101 |

| APPEN                              | NDIX B SIMULATION TECHNIQUES          | 103 |

| B.1                                | An overview of simulation limitations | 103 |

| B.2                                | Avoiding large simulation files       | 104 |

| B.3                                | Modeling the VCO and divider          | 106 |

**ABSTRACT**

FRACTIONAL-N SYNTHESIZER ARCHITECTURES

WITH DIGITAL PHASE DETECTION

by

Mark A. Ferriss

Chair: Michael Flynn

During the last decade there has been unprecedented growth in the use of portable

wireless communications devices for applications as diverse as medical implants,

industrial inventory control, and consumer electronics. If these communication devices

are to be low power, flexible, and reconfigurable, new radio architectures are needed

which take advantage of the major strength of state-of-the-art digital manufacturing

processes; that is the ability to build large, complex low power signal processing circuits,

with extremely fast clocking speeds. However, traditional radio architectures rely on

analog techniques which are ill suited for the use in modern highly integrated digital

systems.

A critical component of a radio system is the frequency synthesizer, a circuit

which can accurately synthesize and modulate high frequency signals. Traditional

χi

synthesizers still utilize a significant amount of analog circuitry. In this work, techniques are developed to replace this analog circuitry with digital equivalents. To do this, a digital phase detection scheme for a Fractional-N Phase Lock Loop (FPLL) is presented. The all-digital phase detector can be used as an alternative to a conventional analog-intensive phase detector, charge pump and loop filter blocks.

Another limitation of traditional synthesizers is the difficulty in modulating the frequency of the output signal at speeds larger the FPLL's bandwidth. A new technique is developed for modulating the output frequency of the FPLL at rates significantly faster than the loop bandwidth would typically allow. A digital sampling scheme that enables FSK modulation rates much larger than the loop bandwidth is demonstrated. The new scheme does not compromise on the frequency accuracy of the output signal. The key ideas presented have been proven in a proof of concept design. A prototype 2.2GHz fractional-N synthesizer, incorporating the digital phase detector and sampling scheme is presented as a proof of concept. Although the loop bandwidth is only 142kHz, an FSK modulation rate of 927.5kbs is achieved. The prototype is implemented in 0.13µm CMOS and consumes 14mW from a 1.4V supply.

### CHAPTER 1

# INTRODUCTION

### 1.1 Background

The wireless communication industry's exponential expansion is fuelling a search for the next generation of circuit tools and techniques which will enable faster, lower power and cheaper wireless devices. The starting point of this research is to identify the limiting features of today's technologies, and develop circuit concepts and architectures which address and overcome these short comings.

Most modern wireless communications systems are in essence frequency multiplexed systems, which consist of the simultaneous transmission of independent signals in separate frequency channels. For example in the GSM 900MHz band the channels are spaced just 200kHz apart. The ability to select a single channel from the myriad of other signals is a crucial part of the design of a modern radio system. (This is in contrast with the first three decades of radio (1885-1916) when spark-gap generators transmitted pulses of wide band energy). A crucial part of channel selection is the task of synthesizing signals with the correct frequency. As communications devices become ubiquitous, there is continuous downward pressure on the size and cost of the devices needed to modulated and demodulate radio signals. This has consequences when considering architectures of the future. Firstly, techniques are needed to ensure that the

radio circuitry of tomorrow can coexist on the same substrate as the large DSP microprocessor cores. This is essential if the level of integration is to be maximized, and the costs reduced. If follows that the ability to implement Radio Frequency (RF) functions in standard Complementary Metal-Oxide-Semiconductor (CMOS) processes, and avoid more exotic and expensive manufacturing processes, is critical. It makes sense to implement as much of these systems as possible in the digital domain in order to take advantage of the fast clock speeds of fine line CMOS. In addition tomorrow's circuits must be programmable and reconfigurable in order to support multiple standards.

This thesis focuses on the fractional-N Phase Locked Loop (FPLL). This circuit can fulfill many of the functions in the wireless devices of the future. Firstly, a critical function in all RF systems is the requirement to synthesis high frequency, low noise clocks. The FPLL can meet these needs and can be programmed to synthesize RF clocks with a wide range of frequencies, without gaps in the tuning range, as is the case for integer division PLLs. Much of the signal processing can be done in the digital domain, making it suitable for integration in a standard digital CMOS process. Another benefit of the FPLL is the ability to modulate the output signal using the same circuitry that is used to synthesis the LO signal in the first place.

While much of the signal processing in a classical FPLL is done in the digital domain, there is still a significant amount of analog circuitry. The design of analog circuits in the deep sub-micron (DSM) age is challenging, and can often lead to excessive power dissipation, increased sensitivity to substrate/power supply noise, and sensitivity to process variation which can compromise performance or yield. Many of these problems are evident in fractional-PLL (FPLL) design. Charge pumps require good matching

between currents of opposite polarity. Low loop-time-constants are typically required, so the loop filter must be implemented using large area capacitors or expensive off chip components. Furthermore, these blocks do not take advantage of the major strength of DSM processes, which is the ability to build fast, complex, low power digital signal processing circuits. This thesis addresses two limitations of this architecture; the reliance on analog circuitry in deep sub-micron technology, and the trade off between low loop bandwidth for good  $\Sigma\Delta$  noise rejection, and high loop bandwidth for fast modulation rates.

The fractional-N frequency synthesizer is a key building block of wireless systems as it can both generate a high frequency signal with a well defined frequency and modulate that signal [1], [2]. An introduction to the use of  $\Sigma\Delta$  modulator in frequency synthesis can be found in [4]. The popularity of this architecture is derived from its ability to do much of the signal processing required for control of the output frequency in the digital domain. Nevertheless, this architecture still relies on a significant amount of analog circuitry. In the remainder of this Chapter some of the uses of FPLLs are briefly reviewed, and some basic PLL concepts are introduced.

#### 1.2 A brief overview of Radio Frequency transmission schemes

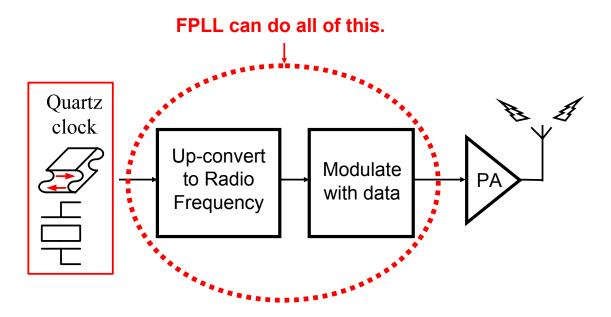

Figure 1.1: An overview of a transmission scheme. A quartz based clock is up-converted to high frequencies and modulated with transmission data before the Power Amplifier.

A conceptual overview of a typical radio transmitter is shown in Figure 1.1. There are two primary steps involved in generating the RF signal. Firstly a carrier signal, which is well defined, stable, and has low noise, must be synthesized. Typically, a low frequency clock source such as a quartz crystal is used as a reference, and a Phase Lock Loop (PLL) up-converts this source to the carrier frequency. The second task is to modulate the RF signal with the information to be transmitted. This task is typically accomplished with the use of a mixer. However, a Fractional-N synthesizer (or FPLL) can do both of these tasks. If an FPLL is described as a black box, then we could say that it has two inputs, and one output. The output is an RF signal of frequency equal to the product of its two inputs; the reference frequency and the digital input division ratio. As an FPLL can synthesize an RF signal of any frequency, it follows that it can also be used as modulator.

Figure 1.2: Possible uses of synthesizers in an RF transmission scheme. a) In a direct conversion transmitter. b) Using just the FPLL as a modulator.

In Figure 1.2(a) an overview of a direct conversion transmitter architecture is shown. A low frequency signal is up-converted to RF by mixing it with a Local Oscillator (LO) signal. In this case a Fraction-N PLL (FPLL) can be used to generate the LO signal. The frequency of the LO signal is given by  $\omega_{LO} = \omega_{ref} \cdot N$  where  $\omega_{LO}$  is the frequency of the LO signal,  $\omega_{ref}$  is the frequency of the reference and N is the Frequency control word that is fed into the synthesizer. If N is changed then the frequency of the LO changes, hence the synthesizer can be used to select the channel.

If N can be changed to select the output frequency, then if N is slowly modulated then the frequency of the LO signal is slowly modulated. In other words, the original synthesizer can be used to modulate the signal, and no other circuitry is required. Figure 1.2(b) shows a synthesizer being used in the transmission path. No other circuitry apart from the power amplifier is required. So what exactly does an FPLL consist of? To answer this question we first start with an introduction to some of basic PLL concepts.

#### 1.3 Introduction to the PLL

The earliest descriptions of the principles of PLLs date to the 1920's [5], and 1930's [6]. In the 1970's control theory was used to describe PLL's for the use in motor speed control systems [7], and many of the earliest IC implementations of PLLs were used for servo-mechanics [8]-[16]. An introduction to some of the underlying concepts can be found in [17].

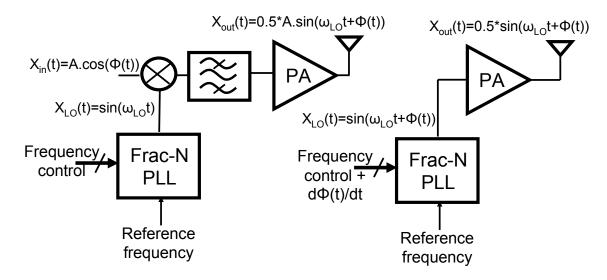

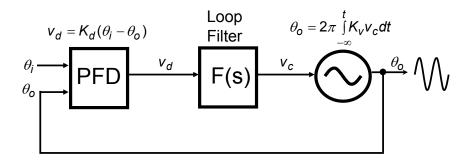

Broken down to its core function, a PLL is simply a feedback system acting on phase. The simplest configuration of a PLL is shown in Figure 1.3. The core components include a Voltage Controlled Oscillator (VCO) which produces a signal at its output which has a frequency proportional to the voltage at the VCO's input. In the phase domain this is the equivalent to producing a phase change at the output proportional to the integration of the input. Next a phase detector measures the phase difference between the output of the VCO and a suitable reference clock. Finally a loop filter completes the loop.

Figure 1.3: A simple PLL includes a Phase/Frequency detector, a Loop Filter, and a Voltage Controlled Oscillator.

6

<sup>&</sup>lt;sup>1</sup> In fact the description "Loop Filter" is somewhat misleading. The objective is not to filter the phase information, but to establish the dynamics of the feedback loop. However, in order to follow convention, the expression "Loop Filter" will be used in this work.

The VCO gain is  $K_v$ , and has units of Hz/Volt. (An occasionally used alternative notation is  $K_o$  which has units of Radians/Volt.) The phase detector gain is  $K_d$ , which has units of Volts/Radian. The loop filter typically includes an integrator and a proportional path, an example for a Type II<sup>2</sup> system is given by Equation (1.1).

$$F(s) = K_1 + \frac{K_2}{s} \tag{1.1}$$

The loop gain is typically defined as the gain around the proportional path of the loop, which is given by Equation (1.2).

$$K = 2\pi \cdot K_{V} \cdot K_{d} \cdot K_{1} = K_{o} \cdot K_{d} \cdot K_{1}$$

$$(1.2)$$

Finally, the system transfer function is given by Equation (1.3).

$$H(s) = \frac{\theta_0(s)}{\theta_i(s)} = \frac{2\pi \cdot K_v \cdot K_d \cdot F(s)}{s + 2\pi \cdot K_v \cdot K_d \cdot F(s)}$$

(1.3)

If a divider divides down the output frequency before the phase detector, then the PLL transfer function becomes:

$$H(s) = \frac{\theta_0(s)}{\theta_i(s)} = \frac{2\pi \cdot K_V \cdot K_d \cdot F(s)}{s + 2\pi \cdot K_V \cdot K_d \cdot F(s)/N}$$

(1.4)

Notice that at low frequencies (s $\rightarrow$ 0) Equation (1.4) simplifies to H(s) $\approx$  N. Hence when PLLs are used to up-converted a reference signal to a higher frequency, then low frequency phase changes at the input are multiplied by N before reaching the output.

7

<sup>&</sup>lt;sup>2</sup> In control theory the Type refers to the number of integrators in the loop. The VCO provides one integrator, so PLLs are always at least Type I, and typically Type II.

### 1.4 A practical example of a modern PLL

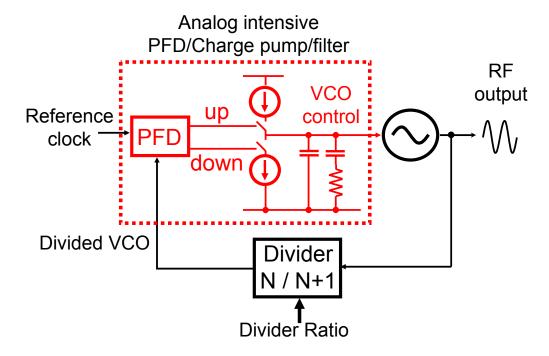

Figure 1.4: A standard PLL. A charge pump is used to convert the output signals form the phase detector to a voltage.

Shown in Figure 1.4 is a typical implementation of an integer-N PLL. On the right of the figure an oscillator generates a high frequency signal. The oscillator output signal is then divided down using a digitally programmable divider. The divider works by counting out phases of the high frequency signal. The counter is digital, and can be made programmable. However the count value, and hence the division ratio is restricted to integer numbers, as a digital counter can only count out whole phases of the output. The divided-down signal is then compared in phase with the reference clock, and the loop is completed with a charge pump and a loop filter. This is a negative feedback loop, the phase and hence the frequency of the divided-down signal is forced to be identical to that of the reference, therefore the frequency of the output signal is given by  $\omega_{out} = \omega_{ref} \cdot N$  where N is the division ratio of the divider.

At this point some observations are in order. The frequency of the output can be changed by changing the division ratio, N. However, N is restricted to integer numbers, therefore the frequency-step size at the output is restricted to the frequency of the reference. In other words, if a small frequency step at the output is required then a small reference frequency should be used. However, it is impractical to use references whose frequency is close to the bandwidth of the PLL. This is because a PLL is a sampled system, it can only represent phase information at frequencies less than Fs/2, where Fs is the reference frequency (This should not be mixed up with the frequency of the output signal, which can be order of magnitude higher). If aliasing is to be avoided, a reference frequency should be used which is significantly faster than the loop bandwidth. On the other hand, the PLL bandwidth needs to be sufficiently wide (a typical value is 100kHz) if the low-frequency VCO phase noise is to be suppressed. For these reasons, when using practical values of reference frequency, changing the value of N by an integer usually leads to a frequency step at the output that is too large to be used to select a channel in a conventional RF communication system. A second observation is that the input reference is typically a digital clock, useful phase comparisons can only be made on the edges of the reference clock<sup>3</sup>. Therefore this type of system can be considered to be a sampled system, even though the output is a continuous time signal.

### 1.5 A first attempt at non-integer based division

If the division ratio is set to a fractional number, then the frequency of the output signal is no longer restricted to integer multiples of the reference frequency. A potential

-

<sup>&</sup>lt;sup>3</sup> If the reference clock is a sine wave, and if the divider is not a digital divider (i.e. it also produces sine waves as a mixer would) then information can be extracted from the phase detector at time points other than the clock rising edge.

solution to this problem is to switch the divide ratio between different integer values so as to get an average divide ratio which is a fractional number. One approach is to use the carry out bit of an accumulator to control the divide ratio, so that the average output of the accumulator is equal to the input, similar to a first order  $\Sigma\Delta$  [18].

Figure 1.5: A first attempt at a Fractional-N Synthesizer [18]. The MSB from an accumulator controls the divider. The LSBs are recycled so there is no DC divider error.

Riley, et al., recognized that the accumulator in Figure 1.5 is actually a first order  $\Sigma\Delta$  modulator. If the modulator is replaced with a higher order modulator, then the

quantization noised can be shaped to high frequencies, and effectively filtered out without effecting the output signal [1],[20]. Miller, et al., independently cane to the same conclusion [22], [23]. Using these methods the frequency of the output signal can be changed indirectly, by change the division ratio within the loop, without adding low frequency noise to the output.

#### 1.6 A brief introduction to the $\Sigma\Delta$ modulator

In this section a brief overview of a  $\Sigma\Delta$  modulator is given.<sup>4</sup>

Figure 1.6: A second order digital  $\Sigma\Delta$  modulator, which includes two integrators, and a quantizer.

A  $\Sigma\Delta$  modulator can switch its output between different quantization levels, while keeping the low-frequency average of the output equal to the input. For example, in Figure 1.6 the architecture of a standard  $2^{nd}$  order  $\Sigma\Delta$  is shown. The forward path consists of two integrators and a quantizer. The feedback forces the average output signal to be equal to the average input signal, despite the fact that the output is a low resolution bus (3bits) and the input is a high resolution bus (20bit in this case). The second order nature of the feedback system means that the quantization noise is shaped to high frequencies

\_

<sup>&</sup>lt;sup>4</sup> For a more in-depth analysis, there are some excellent texts on this subject [46]

according to Equation (1.5), where n is the order of the feedback loop, E(f) is the quantization noise and N(f) is the quantizer noise as seen at the output [46].

$$N(f) = E(f) |1 - e^{-2\pi i fT}|^n$$

(1.5)

Using a higher order feedback system results in less noise at low frequencies at the expense of more noise at high frequencies (which can be filtered out by the PLL). As an example, Figure 1.7(a) shows the input and output, and Figure 1.7(b) shows the spectrum of these signals if the input of the  $\Sigma\Delta$  is a sine wave. Although at first glance the quantized output might not look much like the input, at low frequencies they are the same, as can be seen in the output spectrum. A key point is that the quantization noise is pushed to high frequencies, so if the output is low-pass-filtered then it faithfully represents the low frequency content of the input.

Figure 1.7 Waveforms at input and output of the  $\Sigma\Delta$ . (b) The spectrum of the input and output.

#### 1.7 A conventional Fractional-N PLL(FPLL)

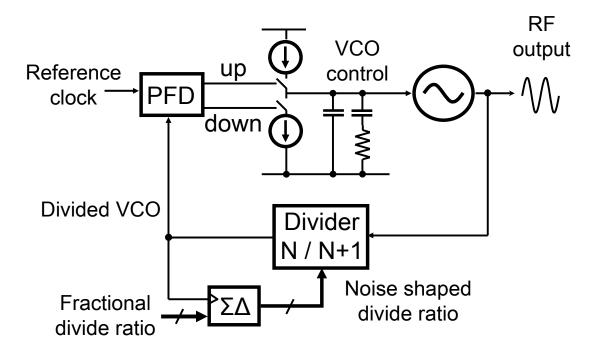

Figure 1.8: A conventional fractional-N synthesizer. In this example a  $\Sigma\Delta$  modulator controls the programmable divider.

The  $\Sigma\Delta$  can be used in the PLL to control the average divide ratio, as shown in Figure 1.8. The divider itself is restricted to integer numbers, but the  $\Sigma\Delta$  modulator allows us to set the average divide ratio to a non-integer or fractional number. The PLL has an overall transfer function which is low pass in nature, therefore the  $\Sigma\Delta$  noise, which is shaped to high frequencies, is filtered out.

This architecture derives much of its popularity from the fact that the frequency and phase of the output signal can be controlled and modulated using digital blocks; the programmable divider and the  $\Sigma\Delta$  modulator.

#### 1.8 The programmable frequency divider

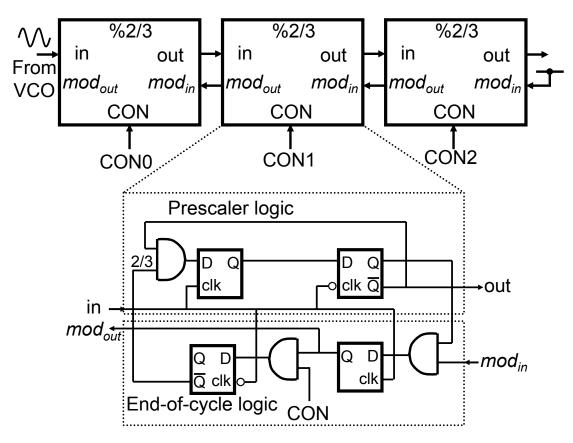

In this section a brief introduction to the programmable divider is given. The programmable divider, or pre-scalar, divides the RF signal by one of several possible integer divide ratios. Most implementations consists of asynchronous dividers in series where the first divider is programmable [24],[25],[26],[27], or where all of the dividers are programmable [28] which can used to achieve a wider division range. The basic idea is that one of the dividers can "swallow" a pulse, resulting in a higher count, and hence a larger divide ratio. Asynchronous designs are used so that only the first divider block is running at the full RF frequency. An example of a 2/3 divider is shown in Figure 1.9.

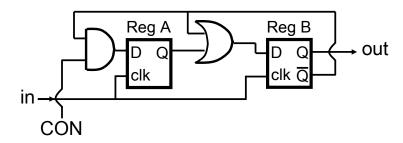

Figure 1.9: A simple 2/3 Divider.

If the CON signal is low then the output of *Reg A* is low, and hence *Reg B* simply acts as a divide-by-2 flip-flop. On the other hand, if CON briefly goes high, then the circuit "swallows" an extra pulse, resulting in a divide by 3. CON can be controlled by the divider so that it goes high only once per output cycle, as shown in Figure 1.10.

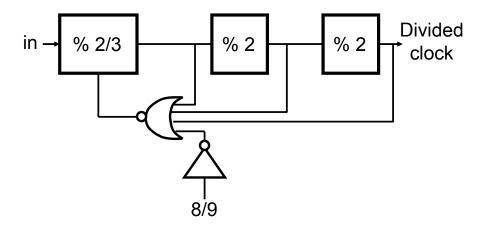

Figure 1.10: A 8/9 bit asynchronous divider. The additional control logic tells the %2/3 to divide by 3 once per output period.

By using 2/3 divider cells for each of the dividers, this idea can be easily extended to implement a divider which can be programmed to divide by values from 8 to 15. The divider used in this work is slightly more complicated, and will be described in Section 5.5.

#### 1.9 Chapter summary

This chapter began with a discussion on the applications and background of PLLs. Next, we introduced some of the key ideas needed to understand the basic FPLL. Although only a brief introduction to these concepts is provided, hopefully it gives enough background so that some of the more novel concepts in later chapters can be understood.

In this research work, techniques are proposed and demonstrated which address two limitations of the FPLL modulator architecture; the reliance on analog circuitry in deep sub-micron technology, and the trade off between low loop bandwidth for good  $\Sigma\Delta$  noise rejection, and high loop bandwidth for fast modulation rates. Chapter 2 introduces an all-digital phase detector, which relies on a single flip-flop for phase quantization.

Chapter 3 focuses on the small signal analysis of the new architecture. Chapter 4 introduces a digital dual-modulation scheme that alleviates the tradeoff between loop bandwidth and switching speed. Chapter 5 discusses the physical prototype, and Chapter 6 discusses measurements from silicon. Finally, Chapter 7 presents conclusions.

#### 1.10 Thesis Contributions

This thesis covers several aspects of digital Fractional-N Phase Lock Loops. The broad theme of this thesis is to implement an all digital phase detector, and to take advantage the digital nature of the system to increase the modulation rate. The key contributions are listed below:

- *Digital phase detection*: In a standard FPLL an analog intensive charge pump and loop filter is typically required. In this work a technique has been developed for implementing the phase detector in the digital domain.

- *High Speed Switching*: In an FPLL the speed at which the output frequency can be switched is limited by the bandwidth of the loop. In this work we propose and demonstrate a technique which breaks this trade off for 2-FSK switching schemes.

- *Small signal modeling*: A small signal model has been developed for the quantizer, which allows for the derivation of the loop dynamics and phase noise at the output.

- <u>Removal of jitter peaking</u>: Analysis of the design reveals that the proposed architecture avoids jitter peaking.

# **CHAPTER 2**

# **DIGITAL PHASE DETECTION**

This chapter introduces the new phase detection technique, and compares it with prior art. The focus will be on qualitative explanations, with some of the more quantitative derivations presented in Chapter 3.

### 2.1 Background

Figure 2.1: A conventional fractional-N synthesizer (Reproduced from Figure 1.8).

We start by taking a fresh look at the FPLL shown in Figure 2.1. An FPLL system can be considered to be a type of digital-to-analog or more specifically a digital-to-frequency converter, with the phase of the input clock acting as the reference, the frequency of the input clock corresponding to the sampling rate, the divider control corresponding to the digital input, and finally, the frequency of the RF signal corresponds to the output. It should come as no surprise that many of the challenges associated with building these systems in deep sub micron (DSM) processes are similar to the challenges associated with ADC/DAC design. In fact a typical FPLL contains a mixture of analog and digital sub-blocks within the loop, with implicit conversion from digital to analog. For example the combination of the  $\Delta\Sigma$  and the programmable divider are used to control the analog phase of the divider's output which implies the presence of a DAC. However, much of the loop remains analog.

In Figure 2.1 the information extracted by the phase detector is inherently analog in nature, since the phase information is not synchronized to either the reference clock or the divided down VCO clock, and is not quantized. Although conventional XOR and tristate phase detectors utilize digital building blocks, a charge pump and filter are still required to extract useful phase-difference information. If a phase-detector with a digital output were available then a digital loop filter could be used in place of the troublesome analog filter.

In this chapter a new method of digital phase detection is introduced. First, some examples of digital phase detection from the literature are discussed. Next, a method of using a single flip-flop as a phase quantizer is introduced. This phase quantizer scheme requires an extra loop, which we call a phase minimization loop.

## 2.2 A Time to Digital Converter (TDC)

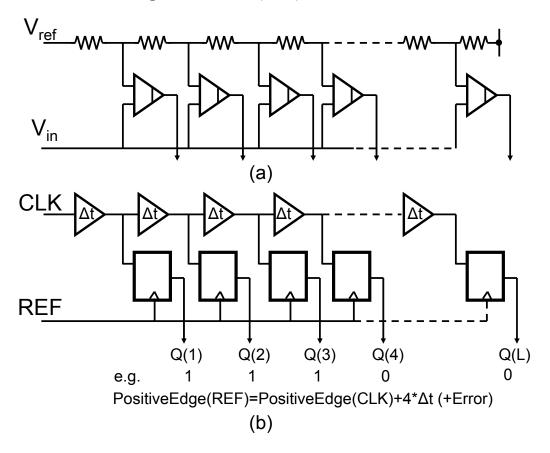

Figure 2.2: (a) A Flash analog-to-digital converter. (ADC) (b) A simplified time-to-digital converter (TDC), which can be considered a flash converter acting on phase.

An example of a digital phase detector is found in [33], where a time-to-digital converter (TDC) uses multiple flip-flops and unit delays (in practice inverters) to quantize the time difference between the edges of the reference clock and feedback clock, as shown in Figure 2.2(b). If each inverter has a unit delay of  $\Delta t$ , then the phase detector has a minimum phase step size of  $2\pi\Delta t/T$ . This architecture is analogous to a flash ADC, where a resistor ladder divides down a reference voltage, and a set of comparators compares the incoming signal with each of the references as shown in Figure 2.2(a). In a TDC the resistors are replaced with unit delay elements, and the comparators are replaced with flip-flops as shown in Figure 2.2(b). There are some interesting differences between

these ADC configurations. In a Flash ADC the two ends of the divider ladder are at well defined voltages,  $V_{ref}$  and ground, therefore the largest Integrated Non-Linearites (INL) will occur at the mid point at the ladder. In contrast we cannot say that the end of a TDC is at a well defined phase. The effects of random jitter and inverter mismatches accumulate as the signal progresses down the inverter chain, therefore it makes sense to use as short a chain as is possible.

While TDCs have been used successfully in all-digital PLLs [36], they have some limitations. Firstly, the resolution and linearity are dependant on the speed and matching of the unit delay elements, and hence are inherently process dependant. One of the key motivations for this work is to reduce process dependency, and to increase the accuracy of the phase detector. Secondly the gain of the TDC in [36] is a function of the inverter delays. While these delays could be controlled with a Delay Locked Loop (DLL), this would add significant additional analog processing. As will be shown, a new technique introduced in Section 2.4 addresses these limitations.

Recently other more complex TDC architectures have been proposed [34], which use techniques developed for Multiplying Delay Locked loops (MDLL) [35]. In these systems a Gated Ring Oscillator (GRO) is used in the TDC, which has been shown to shape the quantization noise to high frequencies, like a first order  $\Sigma\Delta$ .

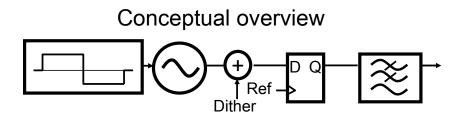

#### 2.3 A single bit phase quantizer as a phase detector

If a conventional TDC is analogous to a flash ADC, with the unit delays setting the quantization steps, then the proposed phase detector is analogous to an over-sampling 1bit ADC, with over-sampling and a phase integration loop used to improve the performance of a coarse single-bit phase quantizer. If only a single flip-flop is used as the

quantizer, then the problem of mismatch between unit delay elements is eliminated. There are some properties of a PLL which make this approach practical. First the bandwidth of the loop can be made to be a small fraction of the reference sampling rate. Secondly the  $\Sigma\Delta$  controlled divider adds dither, which is an important requirement of any over-sampled quantizer.

Figure 2.3: (a) Conceptual overview of a 1bit ADC. (b) Using a flip-flop as a phase quantizer. If dither is added to the input, the quantizer's output can be filtered, to reproduce the input.

The new phase detection technique uses a single flip-flop as a phase comparator, while an additional negative feedback loop around the programmable divider keeps the phases of the two clocks aligned to within a single quantization step. On the rising edge of the reference clock, the flip-flop samples the divided-down VCO signal, determining whether the divided clock is ahead or behind the reference clock. In this way, the flip-flop effectively acts as a one-bit phase quantizer. In Figure 2.3(b) a single flip-flop is used to quantize the phase difference,  $\Delta \Phi$ , between the reference clock and the divided

down VCO clock. The quantization noise of the  $\Sigma\Delta$  controlled divider is added to the divided down VCO clock and this acts as dither for the phase quantizer. If this dither were absent and for example if  $\Delta \Phi$  were positive, then the output of the flip-flop (quantizer) would always be one, irrespective of the magnitude of the phase difference between the divided down clock and reference clock. In the presence of the dither, the output of the flip-flop is sometimes one and sometimes zero. Similar to an over-sampled ADC, the low-pass-filtered output of the flip-flop can be proportional to  $\Delta \Phi$ , depending on the properties of the dither. An approximately linear relationship is achieved if the phase difference  $\Delta \Phi$  is small compared with the added dither. A more detailed discussion of the characteristics of the dither, and its effects on the quantizer gain takes place in Sections 3.2 and 3.3.

While using a single flip-flop as a phase detector is conceptually possible, there are some limitations which would make this scheme difficult to use without some additions to the loop. Firstly, the quantizer gain is a function of the probability density function of the  $\Sigma\Delta$  quantizer noise. If this *pdf* is non-uniform then the gain of the phase quantizer is non-linear, particularly for large phase deviations. For this reason a new technique is used to keep the phase difference at the input of the quantizer small. This is called a Phase-Minimization Loop (PML).

#### 2.4 Phase Minimization Loop (PML)

In conjunction to the use of a sampling flip-flop, an additional feedback loop is introduced, as shown in Figure 2.4. The new feedback loop has two purposes. Firstly, the new loop keeps the phase difference between the two clocks small, i.e. minimizing  $\Delta \Phi$ . For this reason the new loop is called the *phase minimization loop* (PML). Secondly, the

PML desensitizes the overall transfer function to the small signal phase detector gain. (Although the overall PLL keeps the average of  $\Delta \Phi$  at zero, the instantaneous value of  $\Delta \Phi$  is a function of the bandwidth of the PLL, which cannot be set arbitrarily large.) The bandwidth of the inner loop, however, can be set to be significantly larger than that of the overall PLL, hence can do a better job keeping the two clocks in close phase alignment. This is necessary in order for the phase detector to behave in an approximately linear fashion. If the phase deviation,  $\Delta \Phi$ , is too large then the quantizer output becomes stuck at 1 or -1, and the dither will not have the desired effect.

Figure 2.4: New Phase detector configuration with the Phase Minimization Loop (PML). The quantized phase information is fed back to the input of the  $\Sigma\Delta$ .

The one-bit output of the flip-flop is passed through a linear scaling block  $K_{pd}$ , so that the output of the quantizer is +/-  $K_{pd}$ . This quantized information is then fed back to the input of the  $\Sigma\Delta$  modulator that controls the programmable divider, forming the phase minimization loop.  $K_{pd}$  is used to set the bandwidth of the PML.

The only pseudo-analog component is the decision making flip-flop, everything else is synchronous digital circuitry. The flip-flop should be treated in a similar fashion to a comparator in an ADC, as its set-up and hold times are not necessarily respected, as would be the case in a truly digital synchronous system. Therefore attention must be paid to meta-stability, gain, and other characteristics as for a comparator in an ADC. Some techniques to build a suitable flip-flop are discussed in [33]. However, for our design a flip-flop from a standard digital cell library is adequate. This digital approach does not rely on component matching or on any process dependant parameters such as inverter delays.

From a phase perspective, the PML incorporates an integrator in its feedback path. This is because the quantized phase information is fed back to the *frequency* control of the divider. As phase is the integral of frequency, this implies the presence of an integrator in the phase domain. Referring again to Figure 2.4, the presence of this integrator changes nature of the transfer function from the VCO output ( $\Phi_{vco}$ ) to the output of the quantization flip-flop, and also changes the transfer function from the modulator input to the output of the flip-flop. A phase-domain model of the divider is shown in Figure 2.5, the derivation of which is discussed in [37].

Figure 2.5: The small signal phase domain model of the programmable divider. It includes an integrator in the control path.

The phase transfer function from the VCO output ( $\phi_{vco}$  in Figure 2.4 and Figure 2.5) to the output of the flip-flop is now high-pass instead of all-pass, because of the integrator in the feedback path.

Similarly, the transfer function between the input to the modulator ("Divider ratio" in Figure 2.4) and the quantizer output becomes flat instead of low-pass. Without the PML, the transfer function between the input to the modulator and the phase detector output would be low-pass, because the frequency control signal passes through an integration associated with the conversion to phase. However, the integrator is now within the forward path of a feedback loop. As shown in Figure 2.4 a digital integrator placed at the output of the quantizer compensates for the change in transfer function that the PML has caused.

### 2.5 Viewed from a *Delta Modulator* perspective

The PML is similar to a delta modulator, a popular ADC technique. (Several standard text books deal with delta modulators, such as [38], [39], [40], and [41].) It is worthwhile reviewing the delta modulator architecture, in order to get a better

understanding of the PML. In a delta modulator the forward path consists of a quantizer, and the feedback path includes an integrator. (In this work the integration occurs because phase information is fedback to the frequency control of the divider.) A standard delta modulator architecture is shown in Figure 2.6.

Figure 2.6: A delta modulator is a commonly used precursor to a  $\Sigma\Delta$  modulator. There are two types of errors; slope overload and quantization error.

The modulator consists of a feedback system with a 1bit quantizer in the forward path and an integrator in the feedback path. The input signal (x(t) in Figure 2.6) minus the feedback signal is quantized to  $\pm \Delta$ . The feedback keeps the input to the quantizer smaller than one quantization step. The key advantage to this is that a single bit quantizer with a step size much smaller than the signal swing can be used. If the feedback loop is not included then achieving the same input range would be challenging; either a multi-bit

quantizer with the same step size would be needed, or a single bit quantizer with a much bigger step size (resulting in a much greater amount of quantization noise.)

There are two types of noise. Firstly there is regular quantization noise, which can be reduced by using a smaller quantizer step size. Secondly there can be slope overload, which occurs when the input signal changes two quickly with the feedback being unable to catch up. To prevent slope overload a sufficiently large quantization step and clocking rate needs to be used.

The system shown in Figure 2.6 is similar in form to Figure 2.4, when the relationship between the VCO phase  $\Phi_{vco}$  and the phase detector output is considered. Both of these systems have an integrator in the feedback path. In the PML, the integrator consists of the conversion from the frequency domain to the phase domain i.e. Quantized phase information is fedback to the frequency control of the divider. In addition the feedback path in the PML includes a  $\Sigma\Delta$  modulator, which also injects noise into the loop. Therefore the PML is similar to a delta modulator but not identical.

### 2.6 Comparison between the PML and a frequency discriminator

A similar technique is presented as part of a frequency discriminator<sup>5</sup> in [42], which can be used as an RF demodulator or as part of a Fractional-N PLL [43], [44]<sup>6</sup>, in which the quantized phase signal is fed directly back to the divider control, and no  $\Sigma\Delta$  is used in the feedback path. The lack of the  $\Sigma\Delta$  in the feedback path means that the quantization step must be set by the divider step, which results in very large amounts of

<sup>5</sup> In this work *Phase Minimization Loop* is preferred to *Frequency Discriminator*, as the feedback is used to minimize the *phase* difference at the input of the quantizer.

<sup>6</sup> Also [42]- [44] include analog integrators with charge pumps in order to implement higher order noise shaping of the frequency error, a step that has been avoided in this work in order to maximize the digital nature of the system.

quantization noise. In this work, the use of the  $\Sigma\Delta$  to control the divider means that the combination of divider and  $\Sigma\Delta$  can be treated as one linear block, and hence the quantizer step size can be chosen independently of the divider. The  $\Sigma\Delta$  allows the average frequency change at the output of the divider to be smaller than just the divider itself would allow.

### 2.7 Desensitization to phase detector gain

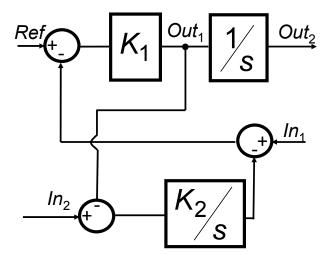

Consider the feedback system in Figure 2.7, which is intended as a simplified representation of the PML, for explanation purposes only. The digital integrators are replaced with analog integrators and all loop gain terms are lumped together into two constants  $K_1$  and  $K_2$ .

Figure 2.7: A simplified continuous time version of the PML feedback system. K<sub>1</sub> includes the phase quantizer gain.

The phase detector gain is included in the constant  $K_1$  and therefore it is desirable if the closed loop transfer function is not sensitive to this constant. Consider the relationship between the phase signal from the VCO  $(In_1)$  and the output of the system  $(Out_1)$ . If Ref and  $In_2$  are set to zero, it is trivial to show

$$Out_1 = K_1 \cdot \left( -\ln_1 - \frac{K_2}{s} \cdot Out_1 \right)$$

(2.1)

This can be rearranged to give Equation (2.2).

$$\frac{Out_1}{In_1} = \frac{-sK_1}{s + K_1K_2} \tag{2.2}$$

Out<sub>2</sub> is simply Out<sub>1</sub> integrated so the final output is given by Equation (2.3).

$$\frac{Out_2}{In_1} = \frac{-K_1}{s + K_1 K_2} \tag{2.3}$$

Notice that in Equation (2.3) at low frequencies ( $s << K_1K_2$ ) the gain simplifies to -  $1/K_2$ . Recall that it is  $K_1$  that contains the phase detector gain, while  $K_2$  is made of constants which are well defined and stable. Therefore the low frequency gain of the overall phase detector is desensitized to the absolute value of the phase detector gain. For this reason variations in the gain of the phase quantizer affect only the bandwidth of the inner loop, not the gain. This is a very useful and important property of the PML, which could well be used in many different digital phase detection schemes. For example, as the TDC's gain is process dependant, the PML loop could be used to desensitize the gain to process variation. This also explains why a phase detector with a poorly defined gain can reliably be used in the system.

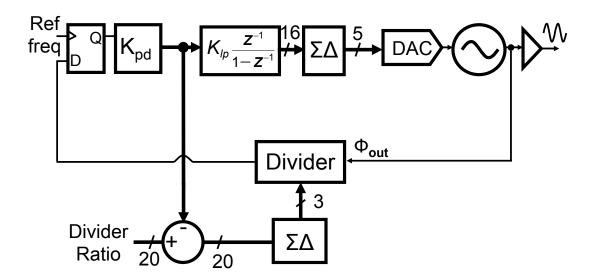

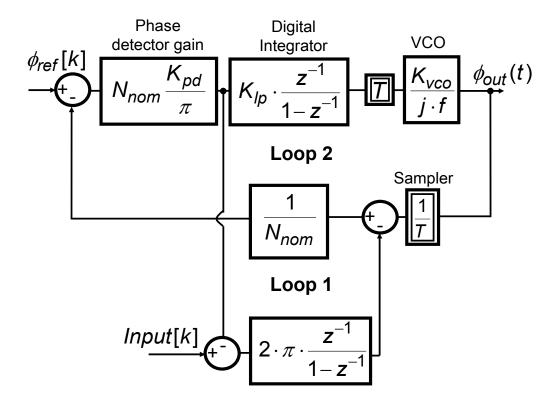

Figure 2.8 shows an overview of the new architecture with the new phase detector configuration. The output of the integrator goes to a DAC, which drives the analog control of the VCO, so as to complete the loop.  $K_{lp}$  is a digital gain that modifies the bandwidth of the overall loop, while gain block  $K_{pd}$  modifies the bandwidth of the inner

loop. Notice that almost everything in the loop is now digital apart from the DAC, VCO and output buffer.

Figure 2.8: The overall architecture of the proposed FPLL, including the new phase detection scheme.

### **CHAPTER 3**

## PHASE NOISE AND SMALL SIGNAL MODELING

### 3.1 Modeling assumptions

A key task in the development of new circuit techniques and architectures is deriving the small signal models for the main components, in order estimate the loop dynamics, and subsequently to estimate the phase noise at the output. Before beginning with the derivation of the small signal model, it is worth discussing some of the assumptions which are typically made in PLL the PLL modeling process, so that the limitations of the model are understood.

The eventual model is a linear model, and non-linear behavior is ignored. For locked or tracking behavior this approximation is reasonable [48], however for large signal behavior such as achieving lock, or for large disturbances, the model is not valid.

An FPLL contains a mixture of continuous time and discrete time blocks. The phase noise at the output is a continuous time signal, therefore a technique known as pseudo-continuous analysis is used, which involves approximating discrete time blocks as continuous time blocks, relying on the fact the PLL has low pass characteristics and only the low frequency alias of the signal need be considered [49].

The spectrum density is defined as the Fourier transform of the autocorrelation function, which exists only if the autocorrelation function is stationary. However the

autocorrelation of an oscillator with frequency drift is non-stationary. Therefore when discussing the spectrum density of an open loop oscillator, this should be taken as an engineering approximation of the spectrum, not a strict mathematical formulation.

One of the key modeling tasks is to derive the approximate small signal gain of the phase quantizer introduced in Chapter 2. First, we discuss the small signal gain of a conventional phase detector. Then the model of a tri-state phase detector will be related to that of our quantizer based detector, while making note of all appropriate approximations.

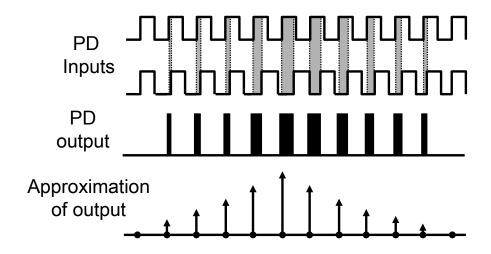

#### 3.2 Phase detector modeling

A standard tri-state phase detector produces a series of pulses which whose widths are proportional to the time difference between the reference clock and the divide down VCO clock. A common modeling approximation [37] is to substitute the time width modulation of the output of the phase detector with fixed width, amplitude modulated signals, as summarized in Figure 3.1.

Figure 3.1: Waveforms approximating the signals at the phase detector output.

This approximation allows us to model the phase detector's output as a sequence of impulses whose area is proportional to the phase difference. The approximation has little effect on the loop provided that the loop bandwidth is significantly smaller than the reference frequency as discussed in [29]. A general time domain model for a (tri-state) phase detector is given in Equation (3.1):

$$E(t) \approx \sum_{k=-\infty}^{k=\infty} \Delta t_k \partial(t - kT)$$

(3.1)

Where the pulses  $\Delta t_k$  are given by Equation (3.2). Note that the phases of the reference and divided-down VCO signals are treated as sampled signals, as the phase difference information is only extracted on the rising edge of the reference clock.

$$\Delta t_k = \frac{T}{2\pi} (\phi_{ref}[k] - \phi_{div}[k]) \tag{3.2}$$

From this it can be shown that the small signal gain of the tristate phase detector is given by Equation (3.3) which has units of seconds/radians (typically a charge pump and loop filter are used to convert the phase difference to voltage):

$$K_{pd\_tristate} = \frac{T}{2\pi}$$

(3.3)

Our objective is to develop a model for the phase quantizer which is similar in form to (3.3). The gain of the phase detector presented in Chapter 2 needs to be approximated with a linear gain. Even though the output of the phase quantizer is one of two values, if the output is low pass filtered then gain of the quantizer can be approximated, as shown in Figure 3.2.

Figure 3.2: In this example VCO's input, and hence the excess phase at the output, increases and then decreases. The output of the phase quantizer is either 1 or -1, but after being low pass filtered it resembles the required phase information.

Calculating the gain involves two steps; calculating the appropriate phase detector small signal gain, K, and calculating the approximate amount of quantization noise. The starting point for this derivation is to look to ADC analysis for estimating quantizer gain and noise. We start by noting that the quantizer rounds the input phase offset to  $+K_{pd}$  or  $-K_{pd}$  where  $K_{pd}$  is a digitally programmable quantization word. The phase-quantizer's low-frequency equivalent gain can be defined as the ratio of the average phase detector output to the input phase difference. Note that this is an over-sampled system, the gain term to be derived is based on an average of the output taken over many samples, and hence it is only valid at low frequencies. The average phase quantizer output can be approximated

with Equation (3.4) where p(1), p(-1) refers to the probability that the quantizer produces a 1 or -1 respectively<sup>7</sup>.

Out

$$\cong K_{pd} \cdot (p(1) - p(-1)) = K_{pd} \cdot (2p(1) - 1)$$

(3.4)

And the phase detector gain, K, is given by Equation (3.5), where Out is the average output from Equation (3.4), and  $\Phi$  is the phase from the VCO, after it has been divided but the divider:

$$K = \frac{\delta(\mathsf{Out})}{\delta(\phi)} \tag{3.5}$$

The next step is to discuss the chances of the quantizer producing a positive output, p(1). The quantizer produces a positive output if the combination of the nominal phase difference  $\Phi$ , and the  $\Sigma\Delta$  quantization noise is positive. In other words the probability of the phase detector producing a 1 is given in Equation (3.6) and Equation (3.7), where  $n_{\Sigma\Delta}$  is the noise added by the sigma delta modulator and  $pdf_{\Sigma\Delta}$  is its probability density function at the quantizer input:

$$p(1) = p(\phi + n_{\Sigma\Delta} > 0) \tag{3.6}$$

or

$$p(1) = 1 - p(\int_{-\infty}^{-\phi} p df_{\Sigma\Delta}(\phi) \partial \phi)$$

(3.7)

Thus the small signal gain is complicated by the fact that it is a function of the quantization noise added by the  $\Sigma\Delta$  modulator. The next step is to approximate the

$<sup>^{7}</sup>$  Of course the flip-flops output is not literally a 1 or -1, its 1 or 0. However, when the flip-flop produces a 0, this is treated as a -1, so the quantizer output is  $+/-K_{pd}$ .

probability density function of the noise generated by the  $\Sigma\Delta$ . The path from the sigma delta modulator to the quantizer is shown in Figure 3.3:

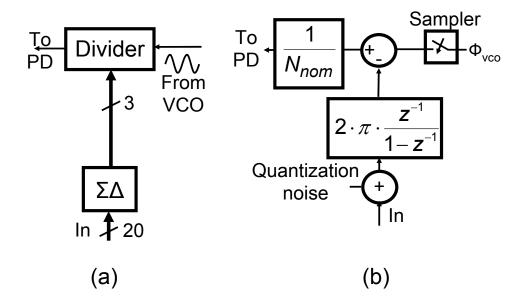

Figure 3.3: (a) The path from the  $\Sigma\Delta$  to the quantizer input (b) The phase domain model, which includes an integrator in the divider's control path.

## 3.3 Estimating the amount of the $\Sigma\Delta$ noise at the quantizer input

Unfortunately a closed form expression for the probability density function of the  $\Sigma\Delta$  noise is not available; instead some approximations are made based on simulation experiments. Firstly, a few observations are in order. According to Equation (3.7) the probability of the quantizer producing a one is a function of the *pdf* of the  $\Sigma\Delta$  noise. To produce linear behavior, the *pdf* should be continuous and preferably uniform. However the actual output of a  $\Sigma\Delta$  is quantized to a small number of fixed levels, therefore for a constant input to the  $\Sigma\Delta$  the error (or noise) at the output is restricted to quantized levels. For example if the input to the  $\Sigma\Delta$  is 0.73, the output is 1 or 0. In this case the quantization error will always be -0.73 or 0.13. However, what is needed is a noise source with a continuous pdf. Luckily a solution to this problem comes from the

realization that the  $\Sigma\Delta$  quantization noise passes through an integrator before reaching the phase quantizer, as shown in Figure 3.3(b). It is the pdf of the output of the integrator which is of interest. In order to approximate the pdf of the noise generated by the  $\Sigma\Delta$  modulator a simulation experiment, shown in Figure 3.4, is performed.

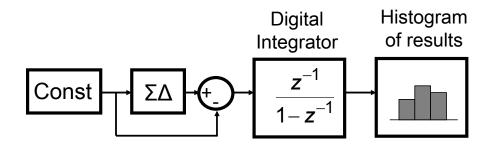

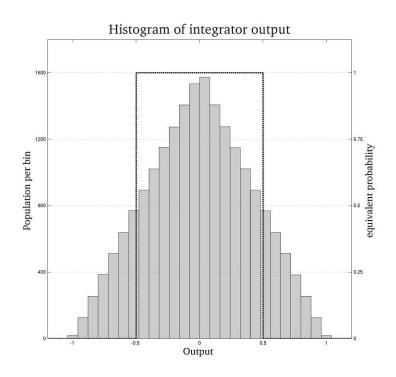

Figure 3.4: Simulation experiment setup. The input is subtracted from the output of a  $\Sigma\Delta$  modulator, leaving only the error. This is then integrated, and plotted on a histogram.

In this experiment, the input to a  $\Sigma\Delta$  modulator is set to a DC value. The DC value at the input is subtracted from the output, leaving just the error, or quantization noise. This noise is then passed through a digital integrator, which models the effects of the conversion from frequency control to phase control. The output of the integrator is sampled and the results are plotted in histogram form in Figure 3.5:

Figure 3.5 Histogram of samples from the integrator output.

On the left y-axis of Figure 3.5 is the population per bin. On the right y-axis is the population per bin expressed as its equivalent pdf. As can be seen the shape of the histogram is approximately triangular, not uniform as would be preferred. However the pdf can be approximated as a uniform value for small phase deviations, as part of a small signal analysis. (The approximation is shown in Figure 3.5 as the dotted line.) Note that it is the probability when then input is close to zero that is of most interest. Thus the pdf of the noise is approximated as having a constant value of 1, according to the right hand y-axis. As is the case in small signal analysis, this is a linear approximation of a non-linear transfer function, and is only valid for small phase deviations. According to Figure 3.3(b) in addition to the digital integration, the noise passes through a gain of  $2\pi$  and is divided by  $N_{nom}$  before reaching the phase quantizer, and hence the pdf at the input to the quantizer has an approximate value of  $N_{nom}/2\pi$ , with a range of  $+/-\pi/N_{nom}$  (for any pdf the

total area must be 1, so for a uniform pdf with a magnitude of X, then the range must be from  $\pm -0.5/X$ . This can be combined with Equation (3.7) to get Equation (3.8).

$$p(1) = 1 - p(\int_{-\infty}^{-\phi} p df_{\Sigma\Delta}(\phi) \partial \phi) \approx 1 - p(\int_{-\pi/N_{nom}}^{-\phi} \frac{N_{nom}}{2\pi} \partial \phi)$$

(3.8)

This can be simplified to give Equation (3.9).

$$p(1) \approx 0.5 + \phi \cdot \frac{N_{nom}}{2\pi} \tag{3.9}$$

Combining this with Equations (3.4) and (3.5) results in the approximate small signal gain.

$$K = K_{pd} \frac{N_{nom}}{\pi}$$

(3.10)

At this point a few comments are appropriate. The expression for small signal gain is calculated using a combination of derivations and simulation results. Because of the approximation in calculating the *pdf* of the noise, this expression is only valid for small phase deviations. However, as discussed in 2.7, the quantizer is nested in a feedback loop which includes an integrator; therefore the overall phase detector gain is desensitized to the quantizer gain. This is advantageous, as the derived gain can only be used as an approximation.

#### 3.4 Transfer function of the other blocks

Now that a model for the gain of the phase detector has been developed, we turn our attention to some of the other blocks. The phase at the output of the VCO can be summarized with Equation (3.11).

$$\phi_{\text{VCO}}(t) = 2\pi \cdot f_{\text{nom}}t + \phi_{\text{out}}(t)$$

(3.11)

Where  $f_{nom}$  is the nominal VCO frequency and  $\Phi_{out}$  is the excess phase, given in Equation (3.12).

$$\phi_{out}(t) = \int_{0}^{t} 2\pi K_{vco} V_{in}(t) \partial t$$

(3.12)

The small signal model for the divider is shown in Figure 3.3. This can be summarized by observing that the phase at the output of the divider is given by Equation (3.13), which is derived in [37]. Here n[i] is the  $i^{th}$  sample of the  $\Sigma\Delta$ ,  $\Phi_{div}[k]$  is the phase of the  $k^{th}$  output of the divider, and  $\Phi_{out}[k]$  is the excess phase of the VCO output.

$$\phi_{div}[k] = \frac{1}{N_{nom}} (-2\pi \sum_{m=1}^{k} n[m-1] + \phi_{out}[k])$$

(3.13)

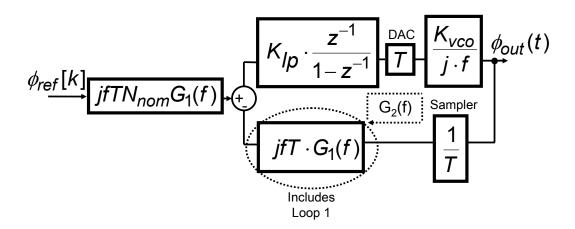

The small signal models for the divider, the phase detector, the VCO and the divider are put together to give a complete small signal model, as shown in Figure 3.6. The two loops are labeled Loop 1 (which is the PML) and Loop 2. Loop 1 consists of the phase detector, divider and  $\Sigma\Delta$ , while Loop 2 consists of the digital integrator, the VCO, and Loop 2 also includes Loop 1.

Figure 3.6: An overview of the small signal model for the FPLL.

As can be seen the model contains a mixture of continuous time and discrete time components. For simplicity, the poles at the output of the DAC are not included. These higher order poles are placed well outside the loop bandwidth, and hence have little effect on the loop settling characteristics (The effects of the poles are included in the numerical calculations in Chapter 6). To analyze Figure 3.6 pseudo-continuous analysis can be used, which involves modeling discrete time components as continuous time blocks. The relationship between the Fourier transform of a continuous time signal, Y(f), and its sampled equivalent,  $\hat{Y}(f)$ , is given by Equation (3.14).

$$\hat{Y}(f) = \frac{1}{T} \sum_{k=-\infty}^{\infty} Y(f - \frac{k}{T})$$

(3.14)

The discrete time transform consists of the continuous time transform replicated in frequency, and scaled by the sampling frequency. However the bandwidth of the loop must be a small fraction of the sampling rate, hence all replicas of the transform are suppressed, except for the fundamental. Therefore the transform from continuous domain to the sampled domain can be approximated by scaling the signals by 1/T. An analog model needs to be developed for the digital integrators. It has been shown in [37] that a digital integrator can be approximated using Equation (3.15).

$$\frac{z^{-1}}{1-z^{-1}} \approx \frac{1}{j2\pi fT} \quad \text{for} \quad f \ll \frac{1}{T}$$

(3.15)

Using this model the loop dynamics can be analyzed.

### 3.5 The loop transfer functions