# Design, Analysis and Test of Logic Circuits under Uncertainty

by Smita Krishnaswamy

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in The University of Michigan 2008

## **Doctoral Committee:**

Professor John P. Hayes, Co-Chair Associate Professor Igor L. Markov, Co-Chair Associate Professor Todd Austin Associate Professor Dennis M. Sylvester Assistant Professor Martin J. Strauss  $\bigcirc \qquad \frac{\text{Smita Krishnaswamy}}{\text{All Rights Reserved}} \quad 2008$

To my family and friends

## ACKNOWLEDGEMENTS

I have been blessed with numerous wise and caring people who have supported me through my Ph.D. and earlier education. I would like to thank my advisors John Hayes and Igor Markov for their advice in all aspects of research including conceptualization, sanity checking, technical writing, and presentation. Their feedback and unending patience were essential in helping me develop as a researcher. Financial support from the Air Force Research Laboratory and the National Science Foundation is also gratefully acknowledged.

I wish to thank all the professors I have worked with, either as a GSI or a student, including Marios Papaefthymiou, Bill Rounds, Kevin Compton, Alfred Hero, Alyce Brady, Tom Askew, and Eric Barth. I would also like to thank my secondary and primary school teachers, especially my math teachers Peggy Becker, Rosemary Brown, and Marcia Weinhold who encouraged me to keep thinking differently.

I wish to thank George Viamontes and Stephen Plaza with whom I collaborated extensively. Their insights and tireless efforts enriched our work. I also would like to thank all of the intelligent students I befriended at Michigan including Shaili Jain, David Papa, Jarrod Roy, Kai-Hui Chang, Ramashis Das, Jin Hu, Hector Garcia, Chien-Chih Yu, Sungsoon Cho, Dae Young Lee, and Ganesh Dasika. I gained a lot of "megaknowledge", technical insights, and practical skills from each of them.

I wish to thank my entire family who taught me to believe that I have the ability to achieve anything as long as I put my mind to it. I thank my grandmother Nagalakshmi

for all her love and support. I wish she were still here with us. I thank my parents Jyothi and Tipa who did everything possible to support me including paying for parking tickets, listening to complaints, and cooking for me weekly. I would not be able to do anything without them. Most people have two parents, I have about sixteen. I wish to thank these extra parents; my uncles Satyamama, Ramu, Papu, Raghu, Somu, Shekhar and Visweswar, and my aunts for always being there for me and telling me the right things to do. Way back in kindergarten, when I hated going to school, my uncle Shekhar would personally drop me off and say, "when you get your Ph.D. you'd better thank me for this." Twenty four years later, here it is. I thank my sister Esha who lived with me and brought joy and humor to my life. Finally, I thank my husband Ben for being supportive, rational, and distracting me at just the right moments with earth-shattering football news.

## **PREFACE**

Integrated circuits (ICs) are becoming increasingly susceptible to uncertainty caused by soft errors, inherently probabilistic devices, and manufacturing variability. These effects can be detrimental to the reliability of logic circuits as device technologies scale. In order to address these issues, we develop methods for analyzing, designing, and testing circuits subject to probabilistic effects. The main contributions of this work are: 1) a fast, soft-error rate (SER) analyzer that uses functional-simulation signatures to capture error effects, 2) novel design techniques that improve reliability using little area and performance overhead, 3) a matrix-based reliability-analysis framework that can capture many types of probabilistic faults, and 4) test-generation and test-compaction methods aimed at probabilistic faults in logic circuits.

SER analysis must account for the three main error-masking mechanisms in ICs: logic, timing, and electrical masking. We observe that logic masking is closely related to node testability of the circuit. We use functional-simulation signatures, i.e., partial truth tables, to efficiently compute the testability measures (signal probability and observability). To account for timing masking, we compute error-latching windows from timing analysis information. Electrical masking is incorporated into our estimates through derating factors for gate error probabilities. The SER of a circuit is computed by combining the effects of all three masking mechanisms within our SER analyzer called AnSER.

Based on AnSER, we develop several low-overhead techniques that increase reliability, including: 1) a design method called SiDeR to enhance circuit reliability using partial

redundancy already present within the circuit, 2) a guided local rewriting technique to resynthesize small windows of logic to improve area and reliability simultaneously, and 3) a post-placement gate-relocation technique that increases timing masking by decreasing the error-latching window of each gate.

In order to analyze probabilistic effects beyond soft errors, we develop a reliability analysis method that can evaluate circuits under a variety of fault assumptions. This method represents faulty gate behavior by means of stochastic matrices called probabilistic transfer matrices (PTMs). To improve computational efficiency, PTMs are, in turn, compressed into algebraic decision diagrams (ADDs). Several ADD algorithms are developed for the corresponding matrix operations.

We propose new algorithms for circuit testing under probabilistic faults. This context requires a reformulation of existing techniques for circuit testing. For instance, any given fault may remain undetected by a given test vector, unless the test vector is repeated sufficiently many times. Also since different vectors detect the same fault with different probabilities, the number of repetitions required is a key issue in probabilistic testing. We develop test generation methods that account for these differences, and integer linear programming (ILP) formulations to optimize our test sets for various objectives.

# TABLE OF CONTENTS

| DEDICAT   | ON                                                                                                             | i  |

|-----------|----------------------------------------------------------------------------------------------------------------|----|

| ACKNOW    | LEDGEMENTS                                                                                                     | ii |

| PREFACE   |                                                                                                                | V  |

| LIST OF F | IGURES                                                                                                         | X  |

| LIST OF T | ABLES                                                                                                          | XV |

| PART      |                                                                                                                |    |

| Chapte    | · I. Introduction                                                                                              | 1  |

| 1.1       | Background and Motivation                                                                                      | 3  |

|           | 1.1.1 Soft Errors                                                                                              | 3  |

| 1.2       | 1.1.2 Technology Trends                                                                                        | 6  |

| 1.2       | Related Work                                                                                                   | 10 |

|           | , and the second se | 14 |

|           | 8                                                                                                              | 18 |

|           | 8                                                                                                              | 20 |

| 1.3       |                                                                                                                |    |

| 1.3       | Thesis Outline                                                                                                 | 21 |

| Chapte    | II. Signature-based Soft-error Analysis                                                                        | 27 |

| 2.1       | SER in Combinational Logic                                                                                     | 28 |

|           | 2.1.1 Fault Models for Soft Errors                                                                             | 29 |

|           | 2.1.2 Signatures and Observability Don't-Cares                                                                 | 32 |

|           |                                                                                                                | 36 |

|           | 2.1.4 Multiple-Fault Analysis                                                                                  | 39 |

| 2.2       | SER Analysis in Sequential Logic                                                                               | 42 |

|           |                                                                                                                | 43 |

|           |                                                                                                                | 45 |

| 2.3       | 1                                                                                                              | 48 |

|           | 2 3 1 Static Analysis of Timing Masking                                                                        | 49 |

| 2.4    | 2.3.2 Statistical-Interval Weighting      | 52  |

|--------|-------------------------------------------|-----|

| 2.4    | Empirical Validation                      | 54  |

| 2.5    | Summary                                   | 62  |

| Chapte | r III. Design for Robustness              | 63  |

| 3.1    | Signature-Based Design                    | 64  |

| 3.2    | Impact Analysis and Gate Selection        | 67  |

| 3.3    | Local Rewriting                           | 69  |

| 3.4    | Gate Relocation                           | 70  |

| 3.5    | Empirical Validation                      | 71  |

| 3.6    | Summary                                   | 76  |

| Chapte | r IV. Probabilistic Transfer Matrices     | 78  |

| 4.1    |                                           | 0.0 |

| 4.1    | PTM Algebra                               | 80  |

|        | 4.1.1 Basic Operations                    | 82  |

|        | 4.1.2 Additional Operations               | 85  |

|        | 4.1.3 Handling Correlations               | 90  |

| 4.2    | Applications                              | 92  |

|        | 4.2.1 Fault Modeling                      | 92  |

|        | 4.2.2 Modeling Glitch Attenuation         | 95  |

|        | 4.2.3 Error Transfer Function             | 99  |

| 4.3    | Summary                                   | 102 |

| Chapte | r V. Computing with PTMs                  | 103 |

| 5.1    | Compressing with Decision Diagrams        | 104 |

|        |                                           | 108 |

| 5.2    |                                           | 114 |

|        |                                           | 115 |

|        | 5.2.2 Hierarchical Reliability Estimation | 117 |

|        | •                                         | 123 |

| 5.3    | 7 1 6                                     | 124 |

| Chapte | r VI. Testing for Probabilistic Faults    | 126 |

| •      |                                           |     |

| 6.1    | <b>,</b>                                  | 127 |

| 6.2    |                                           | 133 |

| 6.3    | Summary                                   | 140 |

| Chapte | r VII. Conclusions                        | 141 |

| 7.1    | Summary of Contributions                  | 142 |

| 7.2      | Direction | ons for Future Work                         | 144 |

|----------|-----------|---------------------------------------------|-----|

|          | 7.2.1     | Scalability of PTM-Based Analysis           | 145 |

|          | 7.2.2     | SER-aware Design of Sequential Circuits     | 146 |

|          | 7.2.3     | Impact of Process Variations on Soft Errors | 147 |

|          | 7.2.4     | Probabilistic Analysis of New Technologies  | 149 |

| BIBLIOGR | APHY      |                                             | 151 |

# LIST OF FIGURES

| <b>Figure</b> |                                                                                                                           |    |

|---------------|---------------------------------------------------------------------------------------------------------------------------|----|

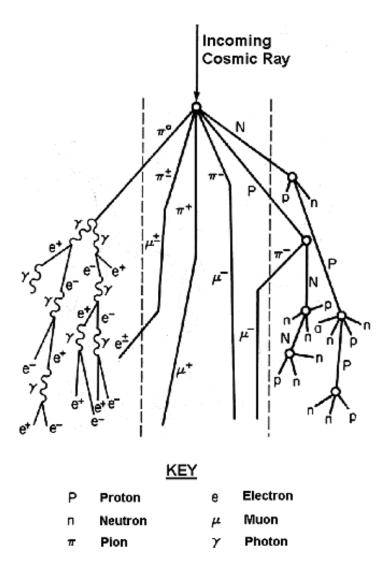

| 1.1           | Shower of error-inducing particles caused by a primary particle in the atmosphere [129]                                   | 4  |

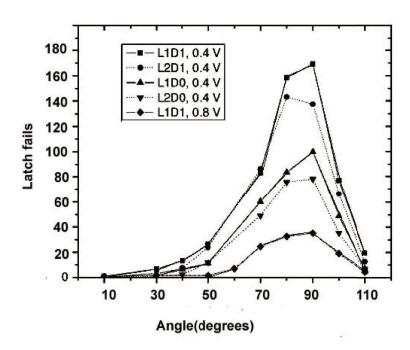

| 1.2           | Latch failure for 1.25MeV proton strikes, as a function of the angle of incidence [106]                                   | 5  |

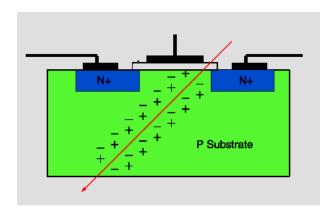

| 1.3           | Ionized track in a transistor, caused by cosmic radiation [34]                                                            | 6  |

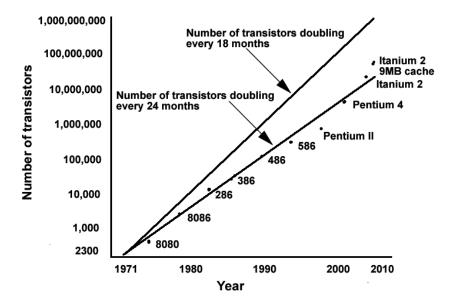

| 1.4           | Moore's law, showing IC density increase per year                                                                         | 7  |

| 1.5           | Memory and logic sensitivity to soft errors in the RISC processor [44]                                                    | 8  |

| 1.6           | Feature-size trends in ICs by year [34]                                                                                   | 9  |

| 1.7           | Illustration of transient-fault propagation in combinational logic                                                        | 10 |

| 1.8           | Illustration of logically sensitized paths (in heavy lines) for error propagation with respect to a specific input vector | 12 |

| 1.9           | Basic SER computation algorithm                                                                                           | 12 |

| 1.10          | Algorithms for SER computation used by (a) SERA, (b) FASER, and (c) SET                                                   | 24 |

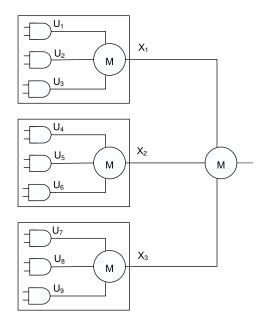

| 1.11          | The cascaded TMR scheme; <i>M</i> denotes a Majority gate [125]                                                           | 25 |

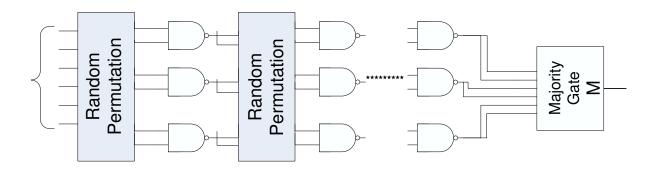

| 1.12          | The NAND-multiplexing scheme [125]                                                                                        | 25 |

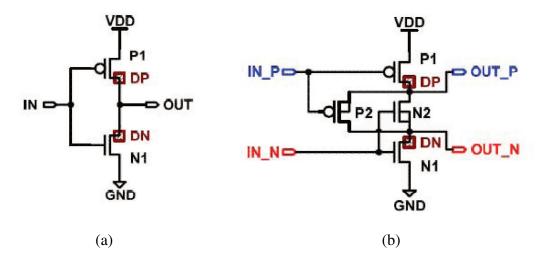

| 1.13          | (a) Normal and (b) dual-port CMOS inverter with two additional transistors in an isolated well [9]                        | 26 |

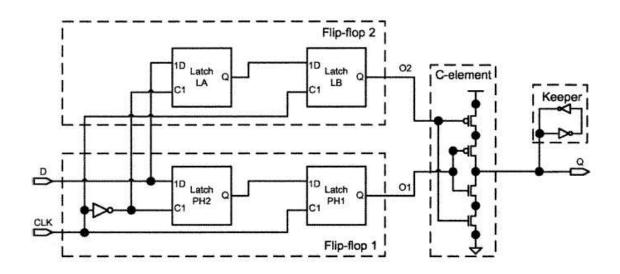

| 1.14          | The error-correcting BISER flip-flop design with a <i>C</i> -element and a keeper circuit [131]                           | 26 |

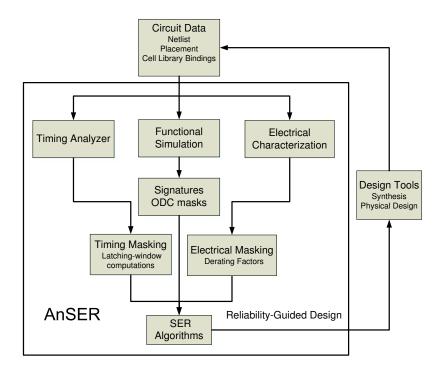

| 2.1  | Computational flow of AnSER                                                                                   | 29 |

|------|---------------------------------------------------------------------------------------------------------------|----|

| 2.2  | Basic algorithm for signature computation                                                                     | 33 |

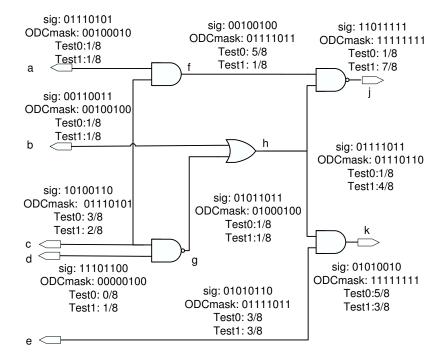

| 2.3  | Signatures, ODC masks, and testability information associated with circuit nodes                              | 34 |

| 2.4  | (a) Exact and (b) approximate ODC mask computation algorithms                                                 | 35 |

| 2.5  | Algorithm to compute SER under the TSA fault model                                                            | 37 |

| 2.6  | Algorithm to compute SER under the TMCSA fault model                                                          | 41 |

| 2.7  | Algorithm to compute SER under the TMSA fault model                                                           | 41 |

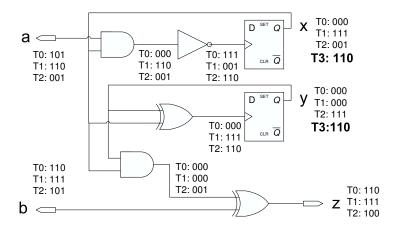

| 2.8  | Algorithm for multi-cycle sequential-circuit simulation                                                       | 45 |

| 2.9  | Illustration of bit-parallel sequential simulation                                                            | 45 |

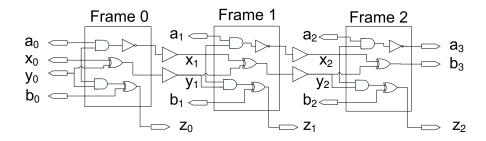

| 2.10 | Illustration of time-frame expansion into three frames: $C_0, C_1, C_2$                                       | 46 |

| 2.11 | Algorithm to compute SER in sequential circuits under TSA faults                                              | 48 |

| 2.12 | Error-latching windows illustrated                                                                            | 50 |

| 2.13 | Computing error-latching windows (ELWs)                                                                       | 51 |

| 2.14 | Computing the union of two ELWs                                                                               | 52 |

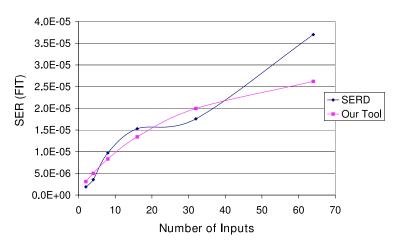

| 2.15 | Comparison of SER trends on inverter chains produced by SERD [100] and AnSER                                  | 57 |

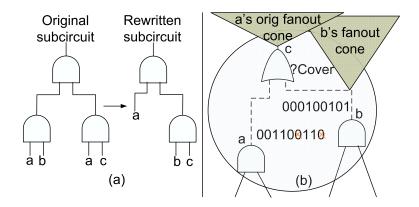

| 3.1  | (a) Rewriting a subcircuit to improve area. (b) Finding a candidate cover for node <i>a</i>                   | 65 |

| 3.2  | Algorithm to approximate <i>impact</i>                                                                        | 69 |

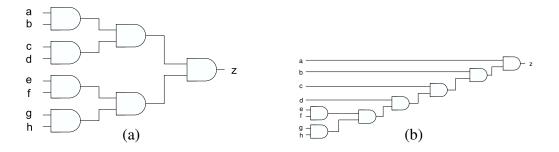

| 3.3  | Two different realizations of an 8-input AND                                                                  | 70 |

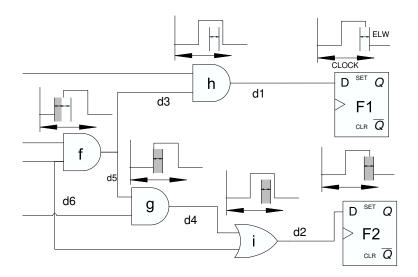

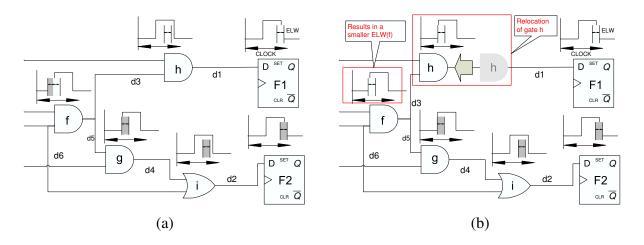

| 3.4  | (a) Original circuit with ELWs; (b) Modified circuit with gate $h$ relocated to decrease the size of $ELW(f)$ | 72 |

| 4.1  | Sample logic circuit and its symbolic PTM formula                                                             | 81 |

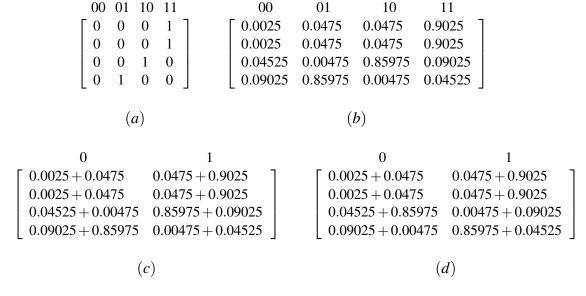

| 4.2  | (a) ITM for the circuit in Figure 4.1; (b) circuit PTM, where each gate experiences error with probability $p = 0.01 \dots \dots \dots$                                                                                                                                           | 81 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

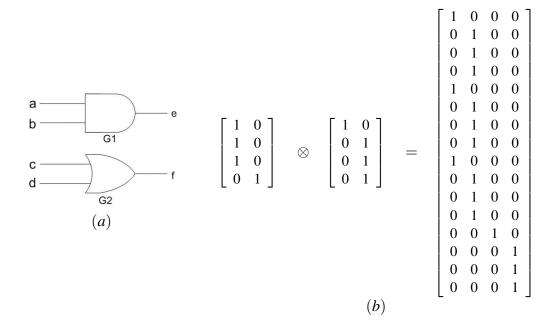

| 4.3  | Illustration of the tensor product operation: (a) circuit with parallel AND and OR gates; (b) circuit ITM formed by the tensor product of the AND and OR ITMs                                                                                                                     | 83 |

| 4.4  | Wiring PTMs: (a) identity gate $(I)$ ; (b) 2-output fan-out gate $(F_2)$ ; (c) adjacent swap gate $(swap)$                                                                                                                                                                        | 84 |

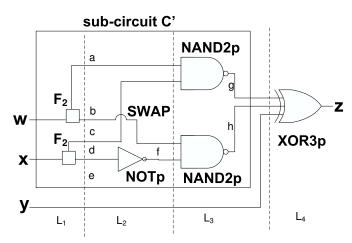

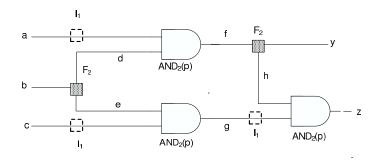

| 4.5  | Circuit to illustrate PTM calculation; vertical lines separate levels of the circuit; the parenthetical subexpressions correspond to logic levels                                                                                                                                 | 84 |

| 4.6  | Matrices used to compute <i>fidelity</i> for the circuit in Figure 4.1: (a) input vector; (b) result of element-wise multiplication of its ITM and PTM; (c) result of left-multiplication by the input vector                                                                     | 86 |

| 4.7  | Example of the <i>eliminate_variables</i> operation: (a) ITM of subcircuit $C'$ from Figure 4.5; (b) PTM of $C'$ ; (c) Output variable $h$ eliminated; (d) Output variable $g$ eliminated                                                                                         | 88 |

| 4.8  | Signal forwarding using <i>eliminate_redundant_variables</i> : (a) circuit with signal $b$ fanning out to two different levels; (b) $NAND \otimes I$ , adding $b$ as an input and output; (c) final ITM for circuit computed by removing rows in boldface                         | 90 |

| 4.9  | Example of output inseparability: (a) PTM for a probabilistic wire-swap; (b) PTM for each individual output after applying <i>eliminate_variables</i> ; (c) incorrect result from tensoring two copies of the PTM from part (b) and applying <i>eliminate_redundant_variables</i> | 91 |

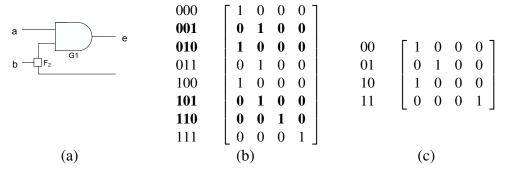

| 4.10 | PTMs for various types of gate errors: (a) a fault-free ideal 2-1 MUX gate; (b) first input signal stuck-at 1; (c) first two input signals swapped; (d) probabilistic output bit-flip with $p=0.05$ ; (e) wrong gate: MUX replaced by 3-input XOR gate                            | 92 |

| 4.11 | Circuit to illustrate crosstalk faults                                                                                                                                                                                                                                            | 94 |

| 4 12 | Representing a crosstalk error using PTMs                                                                                                                                                                                                                                         | 94 |

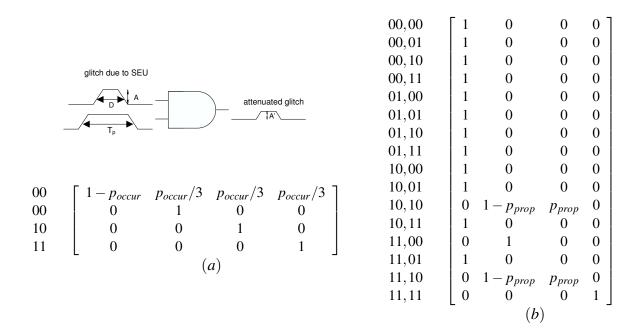

| 98   | (a) $I_{2,2}(p_{occur})$ describes a probability distribution on the energy of an SEU strike at a gate output, (b) $AND_{2,2}(p_{prop})$ describes SEU-induced glitch propagation for a 2-input AND gate. The type-2 glitches become attenuated to type 3 with a probability $1 - p_{prop}$ | 4.13 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

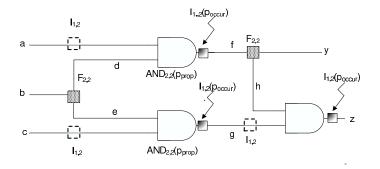

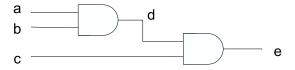

| 99   | 4 Circuit with ITM and PTMs describing an SEU strike and the resultant propagation with multi-bit signal representations                                                                                                                                                                    | 4.14 |

| 99   | Circuit used in Example 8 to illustrate the incorporation of electrical masking into PTMs                                                                                                                                                                                                   | 4.15 |

| 100  | PTM for the circuit used in Example 8 which incorporates electrical properties of the gates.                                                                                                                                                                                                | 4.16 |

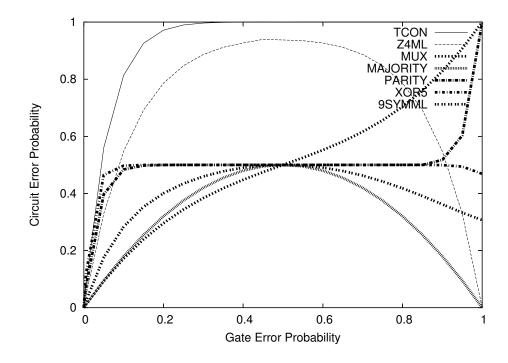

| 101  | 7 Circuit error probability under various gate error probabilities                                                                                                                                                                                                                          | 4.17 |

| 106  | PTMs with identical ADDs without zero-padding: (a) matrix with only one column variable; (b) matrix without dependency on the second column variable                                                                                                                                        | 5.1  |

| 107  | Algorithm to pad matrices with zeros                                                                                                                                                                                                                                                        | 5.2  |

| 108  | (a) NOT gate ITM; (b) zero-padded NAND gate ITM; (c) their tensor product with incorrect placement of all-zero columns                                                                                                                                                                      | 5.3  |

| 110  | Algorithm to compute the ADD representation of a circuit PTM. The <i>gate</i> structure stores a gate's functional information, including its PTM, input names, output names, and ADD                                                                                                       | 5.4  |

| 112  | Algorithm to eliminate redundant variables                                                                                                                                                                                                                                                  | 5.5  |

| 113  | Algorithm to compute <i>fidelity</i>                                                                                                                                                                                                                                                        | 5.6  |

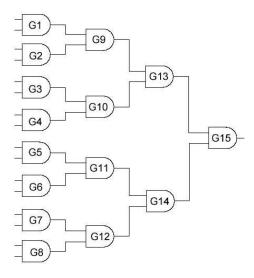

| 115  | Tree of AND gates used in Example 9 to illustrate the effect of evaluation ordering on computational efficiency                                                                                                                                                                             | 5.7  |

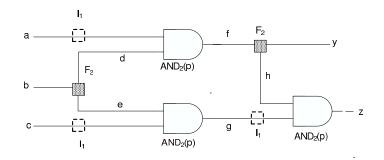

| .118 | Circuit used in Example 10 to illustrate hierarchical reliability estimation                                                                                                                                                                                                                | 5.8  |

| 120  | The <i>Bit_fidelity</i> estimation algorithm                                                                                                                                                                                                                                                | 5.9  |

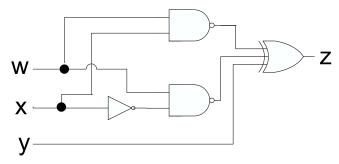

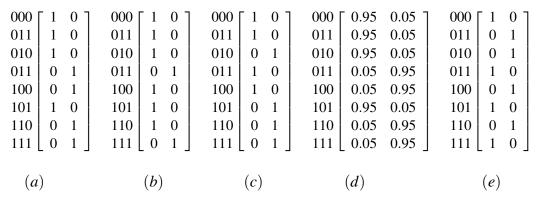

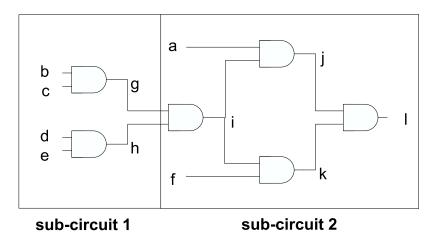

| 128  | Circuit to illustrate test-vector sensitivity computation                                                                                                                                                                                                                                   | 6.1  |

| 130  | Sensitivity computation on the circuit of Figure 6.1                                                                                                                                                                                                                                        | 6.2  |

| 6.3 | Algorithm for output-vector computation                                                                                                                                                     | 133 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.4 | Greedy algorithm for minimizing the number of test vectors (with repetition) required for fault detection.                                                                                  | 136 |

| 6.5 | ILP formulations for test-set generation for a fixed number of expected detections: (a) to minimize the number of test vectors required (b) to maximize fault resolution (minimize overlap) | 137 |

# LIST OF TABLES

| <u>Table</u> |                                                                                                     |    |

|--------------|-----------------------------------------------------------------------------------------------------|----|

| 1.1          | Summary of differences between three SER evaluation tools                                           | 14 |

| 1.2          | Summary of error-masking mechanisms and fault-tolerance techniques at various levels of abstraction | 18 |

| 2.1          | Comparison of SER (FIT) data for AnSER and ATALANTA                                                 | 55 |

| 2.2          | Runtime comparisons of four SER analyzers                                                           | 57 |

| 2.3          | SER (in FITs) and runtime for AnSER on the IWLS 2005 benchmarks                                     | 58 |

| 2.4          | SER evaluation of various benchmarks with exact and approximate ODCs.                               | 59 |

| 2.5          | Comparison of multi-cycle simulation runtimes                                                       | 59 |

| 2.6          | Change in SER for sequential circuits with increasing number of time frames                         | 60 |

| 2.7          | SER under single-event multiple-bit upsets                                                          | 61 |

| 2.8          | SER evaluation with logic and timing masking                                                        | 61 |

| 3.1          | Improvements in SER obtained by SiDeR                                                               | 73 |

| 3.2          | Improvements in SER and area with local rewriting                                                   | 74 |

| 3.3          | Improvements in SER, by a combination of rewriting and SiDeR                                        | 74 |

| 3.4          | SER improvements through gate hardening                                                             | 75 |

| 3.5          | Improvements in SER, through gate relocation                                                        | 76 |

| 4.1 | Polynomial approximations of circuit error transfer curves and residual errors. The fitted polynomials are of the form $e(x) \approx a_0 + a_1x + a_2x^2 + a_3x^3 \dots \dots$ | 102 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.1 | Statistics on various small benchmarks                                                                                                                                                                                                                                               | 111 |

| 5.2 | Comparison of runtimes and memory usage for levelized ordering and ordering computed by dynamic programming                                                                                                                                                                          | 117 |

| 6.1 | Key differences between deterministic and probabilistic testing                                                                                                                                                                                                                      | 127 |

| 6.2 | Runtime and memory usage for sensitivity computation for benchmark circuits. Faulty gates all have error probability 0.05 for all inputs                                                                                                                                             | 133 |

| 6.3 | Number of repetitions required using random vectors versus maximally sensitive test vectors                                                                                                                                                                                          | 138 |

| 6.4 | Number of test vectors required to detect input signal faults with various threshold probabilities $p_{th}$ . $R$ and is the average number of test vectors selected during random test generation                                                                                   | 139 |

## **CHAPTER I**

# Introduction

Digital computers have always been vulnerable to a variety of manufacturing and wearout defects. Integrated circuit (IC) chips, which lie at the heart of modern computers,

are subject to silicon-surface imperfections, contaminants, wire shorts, etc. Due to the

prevalence of such defects, various forms of fault tolerance have been built into digital

systems since the 1960s. For example, the first computers NASA sent to space were

equipped with triple-modular redundancy (TMR) [113] to protect their internal logic from

defects.

Over time, IC technology scaling has brought forth heightened device sensitivity to a different kind of error, known as a soft, or transient, error. Soft errors are caused by external noise or radiation that temporarily affects circuit behavior without permanently damaging the hardware. These errors first became problematic in the 1970s, when scientists at Intel noticed that DRAM cells experienced spontaneous bit-flips that could not be replicated. May and Woods [70] discovered that these errors were a result of  $\alpha$ -particles emitted by trace amounts of radioactive material in ceramic chip packaging. Although the  $\alpha$ -particle problem was eliminated for a period of time by using plastic packaging mate-

rial, other sources of soft error soon became apparent. Later that year, Ziegler et al. [130] at IBM, showed that cosmic rays, consisting primarily of neutrons produced by cosmic rays from outer space, could also cause errors. The neutrons could strike p-n junctions of transistors and create enough electron-hole pairs for current to flow through the junctions.

With the advent of nanoscale computing, soft errors are beginning to affect not only memory but also combinational logic. Unlike errors in memory, errors in combinational logic cannot be easily corrected and can lead to system failures, with potentially disastrous results in error-critical systems such as pacemakers, spacecraft, and servers. Additionally, new device technologies such as carbon nanotubes (CNTs), resonant tunneling diodes (RTDs), and quantum computers exhibit inherently probabilistic behavior due to nanoscale and quantum-mechanical effects. Resilience under these sources of uncertainty is vital for technology and performance improvements.

Due to the cost and high power consumption of modern ICs, the widespread addition of redundancy is not a practical option for curtailing error rates. Instead, careful circuit analysis and low-cost methods of improving reliability are necessary. Further, circuits must be tested post-manufacture for their vulnerability to transient faults as well as to manufacturing defects.

In the remainder of this chapter, we describe soft errors and technology trends that lead to increased uncertainty in circuit behavior. We also survey previous work on soft-error rate (SER) analysis, fault-tolerant design, SER testing, and probabilistic-circuit analysis. Finally, we state the goals of our research and outline the remaining chapters.

# 1.1 Background and Motivation

Soft errors are one of the main causes of uncertainty and failure in logic circuits [114]. Current trends in circuit technology are exacerbating the frequency and impact of soft errors. In this section, we describe soft errors and how they affect circuit behavior. We also survey technology trends, from current CMOS ICs to quantum and molecular computing.

#### 1.1.1 Soft Errors

A soft error is a signal that has an incorrect logic value but does not imply a permanent defect. Soft errors can be caused by cosmic rays,  $\alpha$ -particles, and even thermal noise. Cosmic rays are particles that originate in space, usually from supernovas or solar flares, and enter the Earth's atmosphere. They are estimated to consist of 92% protons, 6%  $\alpha$ -particles, and 2% heavy nuclei [129]. When primary cosmic particles enter the atmosphere, they can create a shower of secondary and tertiary particles, as shown in Figure 1.1. Some of these particles can eventually reach the ground and disturb circuit behavior.

While cosmic rays are more problematic at higher altitudes,  $\alpha$ -particles can affect circuits at any altitude. An  $\alpha$ -particle (or equivalently, a helium nucleus) consists of two protons and two neutrons that are bound together. They are emitted by radioactive elements, such as the uranium or lead isotopes in chip-packaging materials. When packaging materials were improved in the 1980s, the problem was eliminated to a large extent; however, as device technologies scale down towards 32nm, the particle energy required to upset the state of registers and memory circuits becomes smaller [41]. Figure 1.2 shows that even at 1.25 MeV, incident particles can alter the state of latches, depending on the angle of incidence. As the energy threshold for causing an error decreases, the number

Figure 1.1: Shower of error-inducing particles caused by a primary particle in the atmosphere [129].

of particles with sufficient energy to cause errors increases rapidly [106]. For instance, even the lead in solder balls or trace amounts of radioactive contaminants in tin can affect CMOS circuits at lower energies [40].

When a particle actually strikes a circuit and lands in the sensitive area of a logic gate, it can cause an ionized track in silicon, known as a single-event upset (SEU), as illustrated

in Figure 1.3. An SEU is a transient, or soft, fault as opposed to a permanent fault. The effects of an SEU do not propagate if the charge deposited is below the critical charge  $Q_{crit}$  required to switch the corresponding transistor on or off [114]. If an SEU deposits enough charge to cause a spurious signal pulse or glitch in the circuit, it produces a soft error. Error propagation from the site of fault occurrence to a flip-flop or primary output is stopped if there is no logically sensitized path for the error to pass through. If a soft error is propagated to and captured or "latched" by a flip-flop, then it can persist in a system for several clock cycles.

A single latched error can also fan out to multiple flip-flops. Unlike errors in memory, errors in combinational logic cannot be rectified using error-correcting codes (ECCs) without incurring significant area overhead. Hence, it becomes vital to find ways to accurately

Figure 1.2: Latch failure for 1.25MeV proton strikes, as a function of the angle of incidence [106].

Figure 1.3: Ionized track in a transistor, caused by cosmic radiation [34].

analyze and decrease the soft-error rate (SER) of a circuit through careful design. This is especially true of circuits in mission-critical applications, such as servers and aircraft and medical devices.

# 1.1.2 Technology Trends

As described by Moore's Law in 1965, the number of transistors in an IC tends to double every two years—a trend that has continued to the present; see Figure 1.4. In order to facilitate this growth, chip features have become smaller, alongside the amount of charge stored and transferred between gates during computation. Consequently, the various sources of uncertainty described in the previous section can disrupt circuit functionality with greater ease. Other technology trends affecting the SER include decreasing power supply voltage and increasing operating frequency.

The power supply voltage has steadily decreased to improve the power performance of ICs. Additionally, dynamic voltage scaling is now being employed for further reductions in power consumption. Keyes and Landauer [47] lower-bound the energy required to switch a logic gate by  $KT \ln 2$ , where K is the Boltzmann constant and T is the temperature.

A more accurate estimate is given by  $CV^2$ , where V is the supply voltage and C is the capacitance of the gate given by  $C = WC_{out} + \sum_{fanout} C_{in}W_j + C_L$ . Here,  $C_{in}$ ,  $C_{out}$ , and  $C_L$  are the input, output, and load capacitance of the gate, respectively, while W is the width of the transistor. Therefore, as W and V decrease, the switching energy approaches  $KT \ln 2$ , causing logic gates to become more susceptible to noise.

Figure 1.4: Moore's law, showing IC density increase per year.

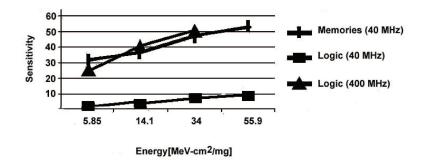

Increased operating frequency—another technology trend—can lead to designs with smaller logic depth, i.e., fewer levels of logic gates. This means that fewer errors are masked by the intermediate gates between the site of fault occurrence and a flip-flop. Engineers at IROC Technologies have observed that the SER in logic circuits increases proportionally with operating frequency [44]. Processors with 40MHz operating frequency were tested, and 400MHz processors were simulated. The results, shown in Figure 1.5, indicate that at higher frequencies, the SER of logic is only 10 times smaller than the SER of memories—despite the additional sources of masking present in logic circuits.

Figure 1.5: Memory and logic sensitivity to soft errors in the RISC processor [44].

IC technologies beyond CMOS are expected to exhibit even more probabilistic behavior. Examples of new device technologies under active investigation include carbon nanotube transistors (CNTs), resonant-tunneling diodes (RTDs), quantum cellular automata (QCA), and various quantum computing technologies, like ion traps that handle quantum bits (qubits). CNTs and RTDs experience high error probabilities because they operate near the thermal limit of  $KT \ln 2$  [69, 14]. QCAs have two main sources of error: 1) decay—when electrons that store information are lost to the environment, and 2) switching error—when the electrons do not properly switch from one state to another due to background noise or voltage fluctuations [62, 104]. Quantum computing devices are inherently probabilistic (even during fault-free operation) because qubits exist in superposition states and collapse to either 0 or 1, with different probabilities upon measurement.

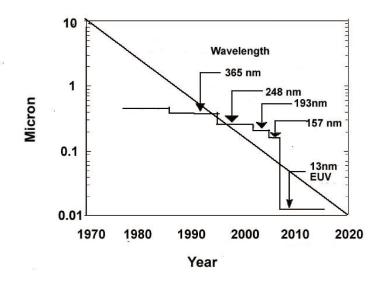

Finally, technology scaling also makes devices harder to manufacture. Process variations cause stochastic behavior, in the sense that device parameters are not accurately known after manufacture. While most process parameters do not change after manufacture, they can often be modeled probabilistically. Figure 1.6 illustrates the lithography wavelengths associated with smaller IC feature sizes by year. As the gap between the

wavelength and feature sizes continues to widen, it becomes difficult for manufacturers to control gate and wire widths. Neighboring wires can suffer from crosstalk, the capacitive and inductive coupling that occurs when two adjacent wires run parallel to each other. Crosstalk can delay or speed up signal transitions and sometimes causes glitches that resembles SEUs to appear [96]. Also, as the number of dopant atoms in transistors decreases, a difference of just a few atoms can lead to large variations in threshold voltage [15]. These variations can cause inherent uncertainty in circuit behavior.

Figure 1.6: Feature-size trends in ICs by year [34].

# 1.2 Related Work

In this section, we discuss related work in soft-error rate (SER) analysis, fault-tolerance techniques, soft-error testing, and probabilistic circuit analysis.

## 1.2.1 Soft-Error Rate Analysis

We first introduce the problem of SER estimation and discuss solutions that appear in the literature, often alongside our work. The aim here is to reveal the intuition behind SER analysis methods and to motivate techniques introduced in later chapters.

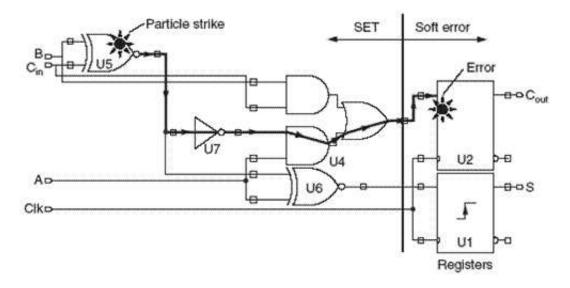

Figure 1.7: Illustration of transient-fault propagation in combinational logic.

There are several factors to consider in determining the SER of a logic circuit. Figure 1.7 illustrates the three main conditions that are required for an SEU to be latched, and these conditions are explained below.

- The SEU must have sufficient energy to change a signal and propagate the erroneous signal value through subsequent gates. If not, the fault is electrically masked.

- The change in a signal's value must be propagated through the logic to affect a primary output. If not, the fault is logically masked.

- The fault must reach a flip-flop during the sensitive portion of a clock cycle, nor-

mally known as the latching window. If not, the fault is temporally masked.

The probability of electrically masking a fault depends on the electrical characteristics of the gates it encounters on its way to the primary output, i.e., it is path-dependent. Similarly, the propagation delay of the SEU, before reaching a latch or a primary output, depends on the gate and interconnect delays along the path it takes. Any path the SEU takes has to have non-controlling values on side inputs. Therefore, different input vectors can sensitize different sets of paths.

Assuming a single strike per clock cycle, the SER can be computed using the brute-force algorithm given in Figure 1.9. In this algorithm,  $P_{err}$  is the probability of an error on a gate. It is computed using the following variables.

- P(i), the probability of vector i being applied to the input,

- $P_{strike}(n)$ , the probability of a fault at location n,

- $P_{attenuate}(path(p))$ , the probability of attenuation along path p, and

- $P_{latch}(p, o)$ , the probability of an error arriving on path p at output o during a latching phase of a clock cycle.

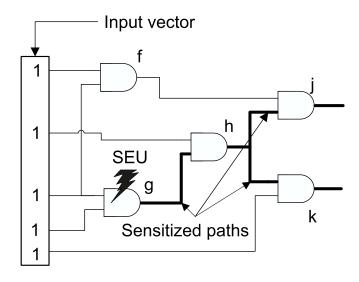

Since the four values are probabilities, neglecting to model any of these factors leads to overestimation of the SER. Figure 1.8 shows an example of an SEU in the ISCAS-85 circuit C17, along with logically sensitized paths for different input vectors.

The algorithm of Figure 1.9 is only practical for the smallest of circuits. The number of input vectors to a circuit is exponential in the number of inputs, and the number of sensitized paths can grow exponentially in the size of the circuit [99]. Therefore, even

Figure 1.8: Illustration of logically sensitized paths (in heavy lines) for error propagation with respect to a specific input vector.

```

\label{eq:compute_SER} \begin{array}{l} \text{compute\_SER}(\text{circuit } C) \\ \{ & \textbf{for}(\text{input vector } i) \\ & \textbf{for}(\text{node } n \in C) \\ & \textbf{for}(\text{output } o \in C) \\ & \textbf{for}(\text{sensitized path } p \in path(i,n)) \\ & P_{prop}(n) = (1 - P_{attenuate}(p)) \\ & Perr(C) + = P(i)P_{strike}(n)P_{prop}(n)P_{latch}(p,o) \\ & \textbf{return } Perr(C) \\ \} \end{array}

```

Figure 1.9: Basic SER computation algorithm.

determining the probability of logical masking is as difficult as counting the number of solutions to a SAT instance—a problem in the #P-hard complexity class.

Several software tools have been recently shown to approximate the SER for combinational circuits. Below, we describe three of these tools and their SER computation techniques [134, 135, 100]. Of the three algorithms, SERA is closest to that of Figure 1.9. SERA relies on user-specified input patterns and analyzes each input vector individually. For each gate, SERA finds all the paths from the gate to an output. Then, SEU-induced

glitches are simulated on inverter chains of the same lengths as the paths in order to determine the probability of electrical masking. In general, there can be many paths of the same length, but only one representative inverter chain of each length is simulated. Since the number of paths is in the size of the circuit, this algorithm runs in exponential time in the worst case. However, the average runtime is much smaller since SERA only simulates paths of unique length.

Unlike SERA, FASER [135] uses binary decision diagrams (BDDs) to enumerate all possible input vectors. A BDD is created for each gate in a circuit—a static BDD for gates outside the fan-out cone of the glitch location, and duration and amplitude BDDs for gates in the fan-out cone of the glitch location. Then, these BDDs are merged in topological order. During the process of merging, the width and amplitude of glitches at inputs are decreased according to FASER's estimation of electrical masking. Due to complete input-vector enumeration, FASER's BDD representations can require a lot of memory for many practical circuits, especially multipliers. FASER attempts to lessen the amount of memory used by partitioning the circuit into smaller subcircuits and then treating the inputs to these subcircuits as pseudo-primary inputs.

SET's algorithm [100] proceeds in topological order and considers each gate only once. For each gate, SET encodes the probability and shape of a glitch as a Weibull probability-density function. This distribution over the Weibull parameters is known as an SER descriptor (SERD). The SERD for each gate is combined with those of its inputs, to produce the output SERD. The Weibull parameters are slightly changed at each gate to account for electrical attenuation, and the new output SERDs are passed on to their successor gates.

The SET algorithm is similar to static timing analysis (STA) and does not consider false paths. The authors of SET do provide another vector-driven mode that computes SER vector-by-vector to account for input-pattern dependence.

Table 1.1 summarizes the main characteristics of the tools described above, as well as their methods for incorporating masking mechanisms. These tools have vastly different methods of computing SER, and their different assumptions can yield very different SER values for the same circuit.

| Attribute          | SERA                      | FASER                 | SET                   |

|--------------------|---------------------------|-----------------------|-----------------------|

| Logic masking      | Vector simulation         | BDD-based analysis    | Vector simulation     |

| Timing masking     | SER derating              | No details given      | SER derating          |

| Electrical masking | Inverter-chain simulation | Gate characterization | Gate characterization |

| Fault assumptions  | Single                    | Single                | Multiple              |

Table 1.1: Summary of differences between three SER evaluation tools.

Our work aims to build SER analysis tools that are scalable and can be used early in the logic design phase [58, 59, 55]. Due to our emphasis on reliability-driven logic design, we focus on modeling logical masking both accurately and efficiently. We then use our tools to guide several design techniques to improve circuit resilience against soft errors.

#### 1.2.2 Fault-Tolerant Design

Techniques for transient-fault tolerance have been developed for use at nearly all stages of the design flow. Generally, these techniques rely on enhancing masking mechanisms to mitigate error propagation. Below, we discuss several techniques and highlight their masking mechanisms.

Faults can be detected at the architectural level via some form of redundancy and can be corrected by rolling back to a checkpoint to replay instructions from that checkpoint. Redundant multi-threading (RMT) [82, 107] is another common method of error detection at the architectural level. RMT refers to running multiple threads of the same program and comparing results. The first thread, known as the leading thread, often executes ahead of other threads to allow time for transient glitches to dissipate.

The DIVA method [7, 126] advocates the use of a functional checker to augment detectand-replay by recomputing results before they are committed. Since the data fetch is

assumed to be error-free (and memory is assumed to be protected by ECC), the functional

checkers simply rerun computations on pre-fetched data. Other methods attempt to detect

errors using symptoms that are unusual behaviors for specific programs. An example

is given by an instruction that accesses data spatially far from previous executions of the

same instruction. Another example is a branch predictor that misspeculates with unusually

high frequency [97, 6]. The main masking mechanism in these techniques is functional

masking. Components are selected for the addition of fault tolerance using a metric called

the architectural vulnerability factor (AVF) of the component in question, as computed by

statistical fault injection or other forms of performance analysis [80].

At the logic level, designers have complete information about the function of the circuit and its decomposition into gates or other low-level functional modules. At this level, one can assess logic masking in more detail. Traditionally, logic masking has been increased by adding gate-level redundancy to the circuit. John von Neumann [125], in his classic paper on reliability, showed that it is possible to build reliable circuits with unreliable components, using schemes like cascaded triple modular redundancy (CTMR) and NAND multiplexing. CTMR contains TMR units that are, in turn, replicated thrice, and this

process is repeated until the required reliability is reached.

In NAND multiplexing, each unreliable signal is replicated *N* times. Then, a set of NAND gates, each of which takes two of the *N* redundant signals as inputs, is used as a simple majority function. Some of these NAND gates may produce incorrect outputs due to an unfortunate combination of inputs; however, such instances are rare since a random permutation changes the gate-pairs between stages of multiplexers. von Neumann concluded that as long as component error probabilities are below a certain threshold, redundancy can increase the reliability of a system to any required degree.

Techniques that involve replicating an entire circuit increase chip area significantly and, therefore, decrease chip yield. Mohanram and Touba [76] propose to partially triplicate logic by selecting regions of the circuit that are especially susceptible to soft errors. Such regions are selected by simulating faults with random test vectors. Dominant-value reduction [76] is also used to duplicate, rather than triplicate, selected logic. Dominant-value reduction mitigates the soft errors that cause only one of the erroneous transitions 0-1 or 1-0, depending on which is more common. More recently, Almukhaizim et al. [3] used a design modification technique, called rewiring, to increase reliability. In the spirit of [3], our work focuses on lightweight modifications to the circuit that increase reliability without requiring significant amounts of redundancy. These types of modifications will be discussed further in Chapter III.

At the transistor level, gates can be electrically characterized, and electrical masking can be used as an error-mitigation mechanism. Gate sizing is a common technique for increasing electrical masking: increasing the area of a gate increases its internal ca-

pacitance and, therefore, the critical charge  $Q_{crit}$  necessary for a particle strike to alter a signal. However, this technique increases circuit area and can also increase critical path delay. Therefore, gates are usually selected for hardening according to their susceptibility to error, which requires error-susceptibility analysis at the logic level.

Another transistor-level technique for soft-error mitigation is the dual-port design style proposed by Baze et al. [9] and, later, by Zhang et al. [132]. Dual-port gates, illustrated in Figure 1.13, decrease charge-collection efficiency, using two extra transistors placed in a separate well from the original transistors.

In the 1990s, Nicolaidis proposed another method of increasing electrical masking [87]. In this method, three latches sample a signal with small delays between, and a voter is used to decide the correct value of the signal. Since stray glitches tend to have short durations, the erroneous value induced by a glitch is likely to be sampled by only one of the three latches. Razor [33] uses this idea for dynamic voltage scaling, sampling signals twice and, when an error is found, restoring program correctness via a detect-and-playback scheme. The recently-proposed BISER [131] architecture duplicates flip-flops and feeds the outputs to a *C*-element and a keeper circuit. At each clock cycle, if the new flip-flop values are the same, the *C*-element forwards the new value to the primary outputs; otherwise, the *C*-element retains the value from the previous cycle. See Figure 1.14 for the BISER flip-flop design.

Finally, after the placement and routing of a circuit are completed, gate and interconnect delays can be determined. In earlier IC technology, timing was usually analyzed at the gate level, since wire delay contributed only a small (often negligible) fraction of the

| Level            | Masking mechanism  | Fault-tolerance techniques                     |

|------------------|--------------------|------------------------------------------------|

| Architecture/RTL | Functional masking | Multithreading, functional checkers, replay    |

| Logic            | Logic masking      | TMR, NAND-mux, partial replication, rewiring   |

| Transistor       | Electrical masking | Gate hardening, dual-port gates, dual sampling |

| Physical         | Timing masking     | No known techniques                            |

Table 1.2: Summary of error-masking mechanisms and fault-tolerance techniques at various levels of abstraction.

critical path delay. However, in current technology, wire delay dominates gate delay and needs to be incorporated into any accurate timing analyzer. Once we can analyze the timing, we can also obtain information about timing masking [114, 74]. To date, very few techniques that decrease timing masking have been proposed.

In summary, faults can be mitigated at several levels of abstraction including the architecture, logic, transistor, and physical levels. Solutions at the logic and transistor levels tend to be more general and do not depend on the function of the circuit. Our work indicates that fine-grained, accurate SER analysis at low levels is computationally feasible and decreases overhead [58, 59, 55]. Table 1.2 summarizes the fault-tolerance techniques and masking mechanisms discussed in this section.

#### 1.2.3 Soft-Error Testing

Chip manufacturers including IBM, Intel, and Toshiba, as well as medical equipment manufacturers like Medtronics, routinely test their chips for SER [129, 70, 50, 127]. SER testing is normally done in one of two ways: field testing or accelerated testing. In field testing, a large number of devices are connected to testers and evaluated for several months under normal operating conditions. In accelerated testing [130], devices are irradiated with neutron or  $\alpha$ -particle beams, thus shortening the test-time to a few hours. Accelerated tests

can be further sped up by reducing the power-supply voltage, which changes the  $Q_{crit}$  of transistors.

There has been some difficulty, however, in translating the SER obtained by accelerated testing to that of field testing [50]. For instance, the SER may vary over time due to solar activity, which can be difficult to replicate in a laboratory setting. Also, intense radiation beams can cause multiple simultaneous errors, triggering system failures more often than normal. Therefore, it is necessary to field-test some devices to calibrate the accelerated tests.

Since field testing requires a vast number of devices and dedicated testers for each device, Polian et al.[39] have proposed a non-concurrent built-in self-test (BIST) architecture for online testing. They define the impact of various soft faults on the circuit in terms of frequency, observability, and severity. For instance, more frequent and observable faults are considered more impactful than rare faults. With this fault characterization, integer linear programming (ILP) is used to generate tests for various objectives, such as ensuring a minimum fault-detection probability.

Recently, researchers have sought to accelerate testing by selecting test patterns that sensitize faults. Conceptually, the main difference between testing for hard errors versus soft errors is that soft errors are only present for a fraction of the test time. Therefore, test vectors must be repeated to detect faults, and they must be selected to sensitize the most frequent faults. Sanyal et al. [108] accelerate testing by selecting a set of error-critical nodes and deriving test sets that, using ILP, sensitize the maximum number of these faults. In our work, which preceded [108], we developed a way of identifying error-sensitive test

vectors for multiple faults, which could include other masking mechanisms like electrical masking, and we devised algorithms for generating test sets to accelerate SER testing [54, 53].

#### 1.2.4 Probabilistic Analysis of Circuits

Soft errors and new device technologies are projected to make circuit behavior generally more uncertain. Therefore, circuit design and testing require new types of probabilistic analysis that goes beyond soft error analysis only. In this section, we provide background on the probabilistic analysis of logic circuits, using Bayesian networks and Markov random fields.

In our work, we develop a novel probabilistic matrix-based model for gates, and we use matrix operations and symbolic methods to evaluate overall circuit error probabilities [60, 61]. More recently, Rejimon et al. [104] proposed capturing errors in nano-domain logic circuits by Bayesian networks. A Bayesian network is a directed graph with nodes representing variables and edges representing dependence relations among the variables. If there is an edge from node a to another node b, then we say that a is a parent of b. If there are n variables,  $x_1 \dots x_n$ , then the joint-probability distribution for  $x_1$  through  $x_n$  is represented as the product of the conditional probability distributions

$$\prod_{i=1}^{n} P[x_i | parents(x_i)]$$

If  $x_i$  has no parents, its probability distribution is said to be unconditional. In order to carry out numerical calculations on a Bayesian network, each node  $x_i$  is labeled with a probability distribution, conditioned on its parents. The probability distribution of  $x_i$  can be given in tabular form or by specifying a known distribution. Certain nodes (such as

those corresponding to primary inputs) are given pre-defined probabilities. The probabilities of other nodes are then computed using a method called belief propagation. Joint probabilities are computed in large Bayesian networks using sampling methods such as importance sampling. Many tools [35, 89] exist for Bayesian network analysis.

Bahar et al.[14] propose to model and design CNT-based neural networks using Markov random fields (MRFs). MRFs are similar to Bayesian networks in that they specify joint-probability distributions in terms of local conditional probabilities, but they can also describe cyclic dependences. In [14], the neural network is described by an MRF with node values computed by a weighted sum of conditional probabilities of a neighboring clique of nodes. This formulation of an MRF is known as the Gibbs formulation and lends itself to optimizing for clique energy, which is translated into low probabilities of node error in [14]. Related to this, Nepal et al. [86] present a method for implementing MRF-based circuits in CMOS, and Bhadhuri et al. [12] describe a software tool, known as Nanolab, which uses the algorithm from [14] to automate the design of fault-tolerant architectures, like CTMR, in nanotechnologies.

### 1.3 Thesis Outline

In this dissertation, we focus on gate-level SER analysis, probabilistic circuit analysis, and fault-tolerant design. We carefully study the input-vector dependence in logic, as well as timing masking, in order to design circuits with better reliability. We further develop methods to model inherently probabilistic methods in logic circuits and to test circuits for determining their reliability after they are manufactured. Our main goals are:

• To develop scalable and accurate methods of SER and susceptibility analysis, usable

during the CAD flow at the gate level,

- To devise methods that guide logic design towards greater resilience against soft errors,

- To develop general and accurate methods for modeling and reasoning about probabilistic behavior in logic circuits, and

- To develop test methods for accurately and efficiently measuring soft-error susceptibility in circuits after they are manufactured.

The remainder of this dissertation is organized as follows. Chapter II presents an efficient technique to analyze SER at the logic level. Here, we formulate probabilistic fault models, based on the stuck-at model used in the testing literature. We propose ways to account for the three basic masking mechanisms, using probabilistic reasoning and functional simulation. We also present techniques in the spirit of static-timing analysis to estimate timing masking and use derating factors to account for electrical masking. Our analysis methods are also extended to sequential circuits.

In Chapter III, we apply the analysis techniques from the previous chapter to the design of reliable circuits. Our techniques include logic rewriting, gate hardening, and a novel technique we call SiDeR. This technique uses functional relationships between signals to partially replicate areas of logic with low redundancy. We also present a gate relocation technique that targets timing masking, a factor which has often been overlooked in fault-tolerant design. This technique entails no area overhead and negligible performance overhead. For sequential circuits, we derive integer linear programs for retiming, which

move latches to positions where they are less likely to propagate errors to primary outputs.

Chapter IV presents a general matrix-based reliability analysis technique, the probabilistic transfer matrix (PTM) framework, to model faulty gate behavior. PTMs form an algebra for reasoning about uncertain behavior in logic circuits. The algebra includes several specific types of matrices to describe gates and wires, along with matrix operations that can be used symbolically or numerically to combine the matrices. Several new matrix operations that are useful in modifying and combining PTMs are introduced to derive information about circuit reliability and output error probabilities, under various types of faults.

Chapter V develops decision diagram-based methods for compressing and computing with PTMs. Several heuristics are presented for improving the scalability of PTM-based computations, including dynamic evaluation ordering, partitioning, hierarchical computation, and sampling.

Chapter VI introduces a new method to test for probabilistic faults. We discuss the differences among traditional testing methods geared towards identifying structural defects and assessing circuit susceptibility to probabilistic faults. We also present algorithms for compacting the test-vector set.

Finally, Chapter VII summarizes our work and discusses possible directions for future research.

```

compute_SER_SERA(circuit C, vectors V)

for (v \in V)

for(nodes n \in C)

for(output o \in C)

for(sensitized path p \in path(n, v))

l = length(p)

Perr(n) = simulate_inverter_chain(l)

K = Area(n)/Area(C)

Perr(C) + = Perr(n) * K

return Perr(C)

}

(a)

compute_SER_FASER(circuit C)

for (n \in C)

create_strike_BDD(n)

for(output o \in C)

for(gate g \in C

create_static_BDD(g)

if (g \in fanout(n))

modify_terminals(g)

sort_topological(C)

for (g \in C)

attenuate(inputs(g))

merge_BDD(inputs(g))

Perr(C) + = (Area(n)/Total) *Flux *P_{err}(BDD(o))

return Perr(C)

}

compute_SER_SET(circuit C)

sort_topological(C)

for (gate g \in G)

SERD(g) = calculate\_strike\_SERD(g)

SERD(g) = merge\_input\_SERD(SERD(g), inputs(g))

for (output o \in C)

P_{err}(C) += P_{err}(SERD(o))

return P_{err}(C)

(c)

```

Figure 1.10: Algorithms for SER computation used by (a) SERA, (b) FASER, and (c) SET.

Figure 1.11: The cascaded TMR scheme; M denotes a Majority gate [125].

Figure 1.12: The NAND-multiplexing scheme [125].

Figure 1.13: (a) Normal and (b) dual-port CMOS inverter with two additional transistors in an isolated well [9].

Figure 1.14: The error-correcting BISER flip-flop design with a *C*-element and a keeper circuit [131].

#### **CHAPTER II**

# Signature-based Soft-error Analysis

As soft errors become increasingly prevalent in logic circuits, soft-error rate (SER) prediction becomes important in all phases of design. As discussed in Section 1.2, the SER depends not only on noise effects, but also on the logical, electrical, and timing-masking characteristics of the circuit. Each of these types of masking can be predicted with a fair amount of accuracy after certain phases of the design process—logic masking after logic design, electrical masking after technology mapping, and timing masking after physical design—and generally stays in effect through the rest of the design flow. Therefore, it is important to efficiently and accurately analyze the SER during the actual design process.

This chapter presents the SER analyzer called AnSER. AnSER employs functional-simulation signatures extensively in order to estimate logic masking and to account for the input-vector dependence in timing and electrical masking. Signatures provide an efficient way of computing testability measures like signal probability and observability, which are, in turn, closely connected to the probability of error propagation. More specifically, the probability of logic-fault propagation is the same as the testability of the fault. The testability of a fault is the likelihood of a test vector for the fault being applied at the

primary inputs. Enumerating test vectors for a particular fault is known to be a problem with #P-hard complexity. In other words, it has the same complexity as counting the number of solutions to a SAT instance. Since exact analysis is impractical for all but the smallest of circuits, we estimate testability using a new and efficient signature-based algorithm.

Figure 2.1 illustrates the flow of computation in AnSER. Functional-simulation signatures are computed from logical information, error-derating factors from gate-characterization information, and error-latching windows from static-timing analysis. These smaller computations are combined to form an estimate of circuit SER. Since AnSER is intended to be used alongside logical and physical design tools, we pay particular attention to runtime, memory requirements and the incremental-use model. Figure 2.1 also shows how AnSER can be incorporated into a typical RTL-to-GDSII flow through incremental calls after each change to the netlist or placement.

The remainder of this chapter is organized as follows. Section 2.1 develops our method for computing the SER of logic circuits by accounting for logic masking. Section 2.2 extends this methodology to sequential circuits. Finally, Section 2.3 incorporates timing and electrical masking into our SER estimates. Most of the techniques and results presented in this chapter also appear in [58, 55, 59, 57].

## 2.1 SER in Combinational Logic

In this section, we present an SER analysis method for combinational logic which, by definition, contains no memory. We first develop fault models for soft errors. Then, we provide background on functional-simulation signatures, which we use extensively in

Figure 2.1: Computational flow of AnSER.

AnSER. Next, we derive SER algorithms for single- and multiple-fault assumptions using signal probability and observability measures that are computed using signatures. Finally, we show how to account for electrical and timing masking.

#### 2.1.1 Fault Models for Soft Errors

For the purposes of logic-level reasoning, we formulate a model for single transient faults with extensions to account for multiple faults. In general, fault models are abstract, logic-level representations of defects and are usually employed in automatic test-pattern generation (ATPG) algorithms. Fault models for soft errors, as we show in Chapter VI, can be useful for testing. However, in this section their primary use is in SER analysis; the close connections between testability and SER facilitate this use.

We conceptualize external noise (such as an SEU) as a probabilistic fault. The main

difference between a permanent fault and a transient fault is its persistence, which we model as a probability of error per clock cycle. Each circuit node g can potentially experience a temporary single stuck-at-1 (TSA-1) fault with probability a  $Perr_1(g)$ , and a temporary single stuck-at-0 (TSA-0) fault with probability  $Perr_0(g)$ .

**Definition 1** A transient stuck-at (TSA) fault is a triple, (g, v, Perr(g)) where g is a node in the circuit,  $v \in \{0,1\}$  indicates a stuck-at value, and Perr(g) is the probability of a stuck-at fault when the node has correct value v.

The advantage of basing a fault model on the stuck-at model is that test vectors for TSA faults can be derived in the same way as for SA faults. Therefore, the same ATPG tools can be used for TSA faults as well. The TSA fault model, in particular, assumes that at most one fault will occur in any clock cycle. This assumption is common in much of SER research because for most technologies, the intrinsic error rate (due to neutron flux, for instance) is fairly low. Using the single-error assumption, SER can be computed as the sum of gate/component contributions. The contribution of each gate to the SER depends on the SEU rate of the particular gate, as captured by Perr(g), and on the observability of the error.

In the case of multiple faults, we have to consider the possible sets of gates that experience faults in the same cycle and the possibility that these faults interfere with each other. The TSA model can be extended to two types of multiple faults called transient multiple correlated stuck-at faults, and transient multiple stuck-at faults.

Faults are correlated if the occurrence of one fault changes the probability of another fault. An example is a multiple-bit upset where a single particle strike causes multiple

upsets in nearby gates. Such upsets are spatially correlated.

**Definition 2** A transient multiple-correlated stuck-at fault (TMCSA) is the triple (G, V, Perr) where G is a set of node  $\{g_1, g_2, g_3, \ldots\}$ , V is a set of binary values  $\{v_1, v_2, v_3, \ldots, v_n\}$  that correspond to the stuck-at values of nodes in G, and Perr is the joint-fault probability of nodes in G.

Transient multiple stuck-at faults apply to circuits with independent probabilities of gate or node failure.

**Definition 3** A transient multiple stuck-at fault (TMSA) fault is represented by (G, V, P) where G is a set of nodes  $\{g_1, g_2, \ldots g_n\}$ , V is the set of corresponding binary stuck-at values  $\{v_1, v_2, \ldots v_n\}$  and P is the corresponding vector of independent error probabilities  $\{p_1, p_2, \ldots p_n\}$ .

Unlike TSA and TMSA faults, a circuit may contain only one TMSA fault of interest—the fault with *G* containing all the nodes in the circuit. TMSA faults may be used to model independent device failure probabilities rather than SEU effects.

In the next two sections, we mainly utilize the TSA fault model to compute the SER of logic circuits. It is sometimes convenient to measure the SER in terms of the probability of error per cycle. The results can easily be converted into units of FIT, or failures per  $10^9$  seconds. If the soft-error probability per cycle is p, then the expected number of failures per  $10^9$  seconds is simply  $p \times freq \times 10^9$ , where freq is the clock frequency. Assuming only one error occurs in each cycle,  $Perr_0(g)$  is the probability that only gate g experiences an error. Therefore, gate SER in units of FITs can also be used in a similar fashion. In general, we denote probabilities of error Perr and gate SER as gerr.

### 2.1.2 Signatures and Observability Don't-Cares

We systematically use node signatures for three purposes: 1) to compute the SER, 2) to identify error-sensitive areas of a circuit, and 3) to identify redundant nodes for resynthesis. A circuit node g can be labeled by a signature as defined below.

**Definition 4** A signature, denoted,  $sig(g) = F_g(X_1)F_g(X_2)...F_g(X_K)$  is the sequence of logic values observed at circuit node g in response to applying a sequence of K input vectors  $X_1, X_2, ..., X_K$  to the circuit.

Here,  $F_g(X_i) \in \{0,1\}$  indicates the value appearing at g in response to  $X_i$ . The signature sig(g) thus partially specifies the Boolean function  $F_g$  realized by g. Applying all possible input vectors (exhaustive simulation) generates a signature that corresponds to a full truth table. In general, sig(g) can be seen as a kind of "supersignal" appearing on g. It is composed of individual binary signals that are defined by some current set of vectors. Like the individual signals, sig(g) can be processed by EDA tools such as simulators and synthesizers as a single entity. It can be propagated through a sequence of logic gates and combined with other signatures via Boolean operations. This processing can take advantage of bitwise operations available in CPUs to speed up the overall computation compared to processing the signals that compose sig(g) one at a time.

Signatures with thousands of bits can be useful in pruning non-equivalent nodes during equivalence checking [137, 92]. A related speedup technique is also the basis for "parallel" fault simulation [19]. The basic algorithm for computing signatures is shown for reference in Figure 2.2. Here, Op < g > refers to the operation gate g. This operation is applied to the signatures of the input nodes of gate g, denoted input sigs(g).

```

\begin{tabular}{ll} $\operatorname{compute\_sigs}(\operatorname{Circuit}\ C,\ \operatorname{size}\ K)$ \\ $\{$ & \begin{tabular}{ll} $\operatorname{for}(\operatorname{all\ inputs}\ i\in C)$ \\ $sig(i) = \operatorname{gen\_random\_sig}(K)$ \\ $\operatorname{sort\_topological}(C)$ \\ $\operatorname{for}(\operatorname{all\ nodes}\ g\in C)$ \\ $sig(g) = Op < g > (inputsigs(g))$ \\ $\}$ \\ \end{tabular}

```

Figure 2.2: Basic algorithm for signature computation.