# AUTOMATIC DESIGN OF EFFICIENT APPLICATION-CENTRIC ARCHITECTURES

by

Kevin C. Fan

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in The University of Michigan 2008

Doctoral Committee: Associate Professor Scott Mahlke, Chair Professor Stéphane Lafortune Professor Trevor N. Mudge Associate Professor Todd M. Austin © <u>Kevin C. Fan</u> 2008 All Rights Reserved

#### ACKNOWLEDGEMENTS

This dissertation would not have been possible without the guidance and support of many people. First and foremost, I would like to thank my advisor, Scott Mahlke. His insight, expertise, enthusiasm, and encouragement played a large part in my success in graduate school. Without his guidance, this dissertation would not exist. In addition, Scott was one of the first to encourage me to undertake graduate studies in the first place after I worked with him as an undergraduate.

I would also like to thank my thesis committee, Professors Trevor Mudge, Todd Austin, and Stéphane Lafortune. They donated their time, giving valuable comments and suggestions to help improve the research and refine the thesis. In addition, I would like to thank Bill Mangione-Smith, who first exposed me to compilers and to graduate school when I worked with him at UCLA.

The research presented in this dissertation was not the work of one person; I was fortunate to have the assistance of a number of other students in the Compilers Creating Custom Processors research group. Manjunath Kudlur provided significant help with the ILP and SMT scheduling formulations presented in this dissertation. Hyunchul Park assisted with creating the Verilog back-end of the synthesis system. Ganesh Dasika implemented the Verilog simulation framework and also answered my numerous questions about the area and power analysis tools. In addition, my work is based on the Trimaran compiler infrastructure; Mike Chu, Nate Clark, Rajiv Ravindran, and Hongtao Zhong, among others, have done significant work in maintaining and improving this infrastructure.

Outside of the technical reasons, I appreciate the opportunity to have worked with a great group of people who provided moral support and made my graduate school experience enjoyable, namely: Amin Ansari, Jay Blome, Mike Chu, Nate Clark, Ganesh Dasika, Shuguang Feng, Shantanu Gupta, Jeff Hao, Amir Hormati, Po-Chun Hsu, Manjunath Kudlur, Steve Lieberman, Yuan Lin, Mojtaba Mehrara, Rob Mullenix, Pracheeti Nagarkar, Hyunchul Park, Yongjun Park, Rajiv Ravindran, Misha Smelyanskiy, and Hongtao Zhong. I have shared offices, and in many cases, homes with these friends and my time in Ann Arbor would not have been the same without them.

I would like to thank my family for their support, encouragement, and advice. Finally, and most importantly, I thank Jennifer Mato for her unconditional love and support over the years, even through separation over long distances and long periods of time. Her companionship added invaluable depth to my years in graduate school and has made its completion all the more sweet.

# TABLE OF CONTENTS

| ACKNOWLE                            | ii                                                                                                                                                                   |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LIST OF FIG                         | vi                                                                                                                                                                                                       |

| LIST OF TAI                         | <b>BLES</b>                                                                                                                                                                                              |

| ABSTRACT                            | ix                                                                                                                                                                                                       |

| CHAPTERS                            |                                                                                                                                                                                                          |

| 1 Introd<br>1.1<br>1.2              | uction       1         Contributions       4         Organization       4                                                                                                                                |

| 2 Backg<br>2.1<br>2.2<br>2.3<br>2.4 | round and Motivation6The Costs of Computation6Automated Synthesis8Hardware Reusability10Related Work11                                                                                                   |

| 3 Hardw<br>3.1<br>3.2<br>3.3        | vare Organization and Design Flow13System View13Accelerator Template14Accelerator Design Flow163.3.1FU Allocation163.3.2Modulo Scheduling173.3.3Datapath Construction183.3.4Architecture Instantiation19 |

| 4 Cost S<br>4.1<br>4.2<br>4.3       | Sensitive Modulo Scheduling20Introduction20Related Work23Scheduling Techniques254.3.1Greedy Scheduling27                                                                                                 |

|       |        | 4.3.2 Branch-and-Bound Solution                                                                                                                                    |

|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |        | 4.3.3 Integer Linear Programming Formulation                                                                                                                       |

|       | 4.4    | Decomposition Methods                                                                                                                                              |

|       |        | 4.4.1 Operation Partitioning                                                                                                                                       |

|       |        | 4.4.2 Time and Space Decomposition                                                                                                                                 |

|       |        | 4.4.3 Space and Time Decomposition                                                                                                                                 |

|       | 4.5    | Experimental Results                                                                                                                                               |

|       | 4.6    | Summary                                                                                                                                                            |

| 5     | Multif | unction Accelerator Design                                                                                                                                         |

|       | 5.1    | Introduction                                                                                                                                                       |

|       | 5.2    | Synthesizing Multifunction Accelerators 61                                                                                                                         |

|       |        | 5.2.1 Joint Scheduling $\ldots \ldots \ldots$      |

|       |        | 5.2.2 Union of Accelerators $\ldots \ldots \ldots$ |

|       | 5.3    | Experimental Results                                                                                                                                               |

|       | 5.4    | Summary                                                                                                                                                            |

| 6     | Progra | ammable Loop Accelerator Design                                                                                                                                    |

|       | 6.1    | Introduction                                                                                                                                                       |

|       | 6.2    | Motivation                                                                                                                                                         |

|       |        | 6.2.1 Architecture Style vs. Efficiency                                                                                                                            |

|       |        | 6.2.2 Programmability Case Study                                                                                                                                   |

|       | 6.3    | From Single-function LA to Programmable LA                                                                                                                         |

|       |        | 6.3.1 Single-function Accelerator                                                                                                                                  |

|       |        | 6.3.2 Programmable Loop Accelerator                                                                                                                                |

|       | 6.4    | Constraint-driven Scheduling                                                                                                                                       |

|       |        | 6.4.1 Scheduling Overview                                                                                                                                          |

|       |        | 6.4.2 SMT-based Scheduling                                                                                                                                         |

|       | 6.5    | Graph Perturbation                                                                                                                                                 |

|       | 6.6    | Experimental Results                                                                                                                                               |

|       |        | 6.6.1 Overview                                                                                                                                                     |

|       |        | 6.6.2 Area and Power Comparison                                                                                                                                    |

|       |        | 6.6.3 Datapath Generalizations                                                                                                                                     |

|       |        | 6.6.4 Programmability                                                                                                                                              |

|       | 6.7    | Accelerator Efficiency Analysis                                                                                                                                    |

|       | 6.8    | Related Work 117                                                                                                                                                   |

|       | 6.9    | Summary                                                                                                                                                            |

| 7     | Conclu | sion $\ldots \ldots 121$                                  |

|       | 7.1    | Summary                                                                                                                                                            |

|       | 7.2    | Future Directions                                                                                                                                                  |

| BIBLI | OGRAI  | <b>PHY</b>                                                                                                                                                         |

# LIST OF FIGURES

# Figure

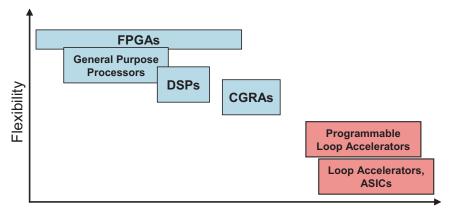

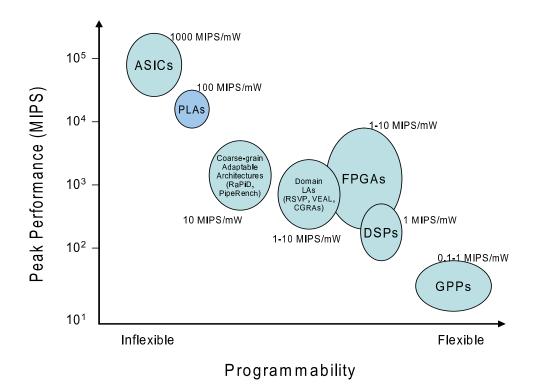

| 2.1 | Architecture design space.                                                                                                                                                                                              | 7        |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

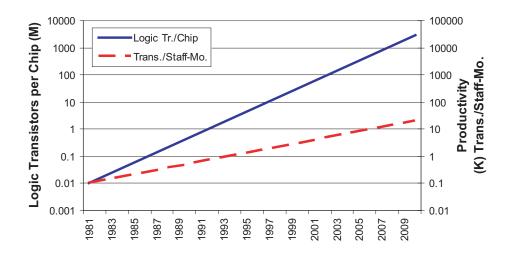

| 2.2 | Design productivity gap [61]                                                                                                                                                                                            | 9        |

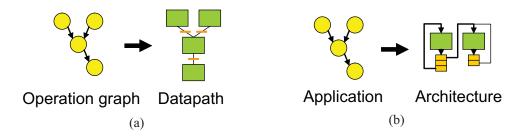

| 2.3 | (a) Traditional behavioral synthesis. (b) Application-centric architec-                                                                                                                                                 |          |

|     | ture synthesis.                                                                                                                                                                                                         | 10       |

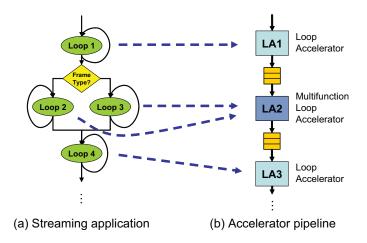

| 3.1 | Streaming application mapped to pipeline of loop accelerators                                                                                                                                                           | 14       |

| 3.2 | Loop accelerator template.                                                                                                                                                                                              | 14       |

| 3.3 | Loop accelerator design flow                                                                                                                                                                                            | 16       |

| 3.4 | An example loop accelerator design. (a) sobel source code, (b) result<br>of FU allocation with $II = 4$ , (c) a portion of the sobel modulo sched-<br>uled loop, (d) datapath derived from the modulo schedule shown in |          |

|     | (c), (e) lowered datapath. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                                      | 18       |

| 4.1 | Effect of schedule on wire cost.                                                                                                                                                                                        | 26       |

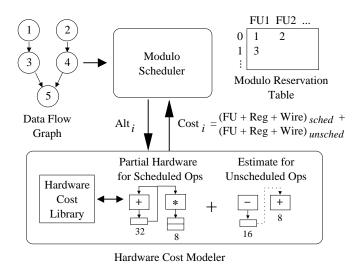

| 4.2 | Cost sensitive scheduling framework used for greedy and branch-and-                                                                                                                                                     | 20       |

| 4.3 | bound schedulers                                                                                                                                                                                                        | 28<br>29 |

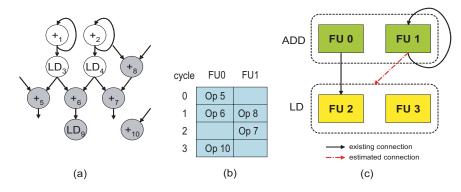

| 4.4 | Wire estimation example: (a) DFG, (b) partial schedule, (c) connection diagram                                                                                                                                          | 31       |

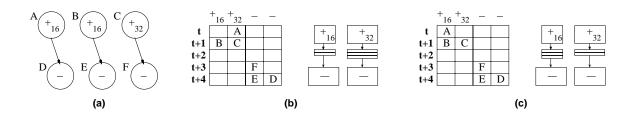

| 4.5 | Effect of space-time decomposition. (a) Dataflow graph, (b) schedule resulting in optimal FU cost but suboptimal overall cost, (c) schedule                                                                             | 01       |

|     | with same FU cost and improved overall cost                                                                                                                                                                             | 48       |

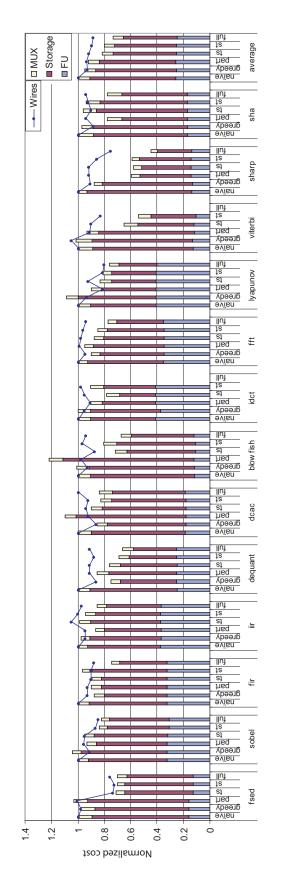

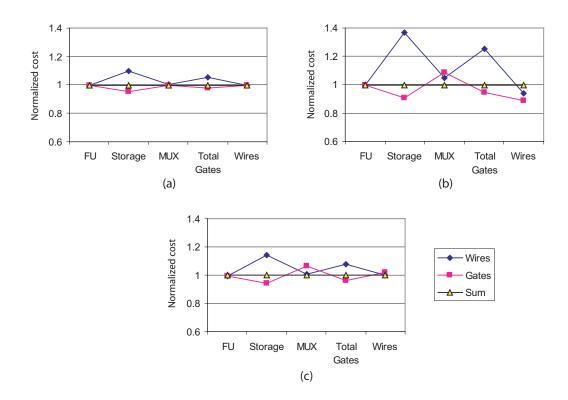

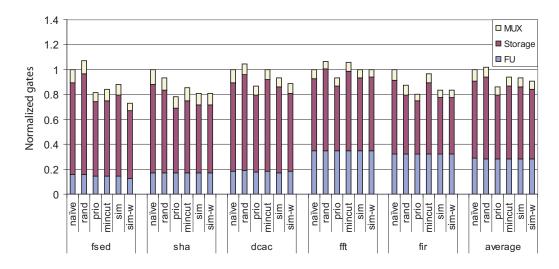

| 4.6 | Hardware cost breakdown of loop accelerators synthesized using vari-<br>ous scheduling techniques, relative to naïve scheduler.                                                                                         | 51       |

| 4.7 | Effect of different cost objectives on (a) iir, (b) sha, and (c) average                                                                                                                                                |          |

| 1.0 | across all benchmarks.                                                                                                                                                                                                  | 54       |

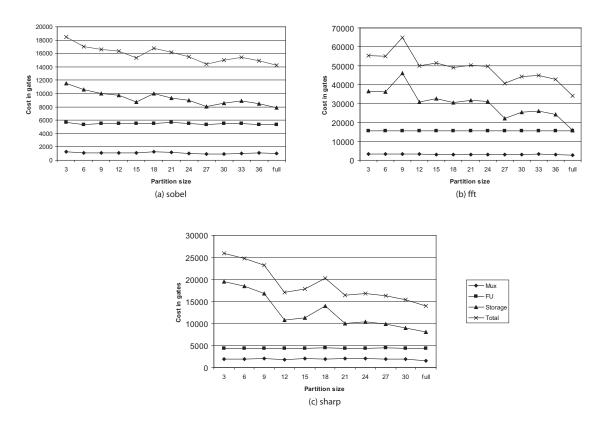

| 4.8 | Effect of partition size on hardware cost.                                                                                                                                                                              | 55       |

| 4.9 | Cost breakdown for various partitioning methods                                                                                                                                                                         | 57       |

| 5.1 | ILP formulation for joint scheduling                                                                                                                                                                                    | 62       |

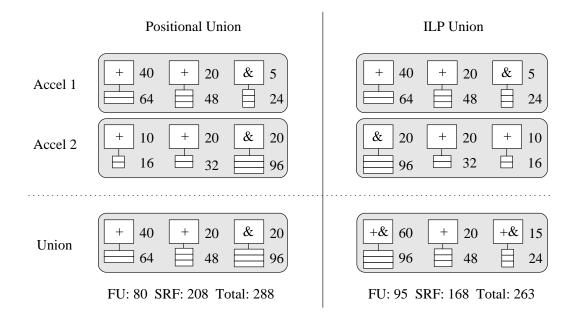

| 5.2  | Example of union techniques. Two single-function accelerators, each with three FUs, are combined using positional (left) and ILP (right) methods. The cost of each FU and SRF is shown on its right.                          | 67   |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

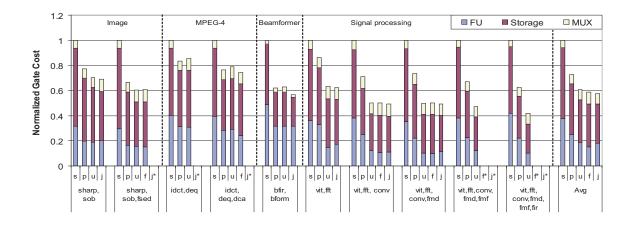

| 5.3  | Gate cost of multifunction accelerators designed using sum (s), posi-<br>tional union (p), pairwise union (u), full union (f) (not shown for 2-loop<br>combinations), and joint scheduling (j). * indicates the synthesis did |      |

|      | not complete due to problem complexity                                                                                                                                                                                        | 71   |

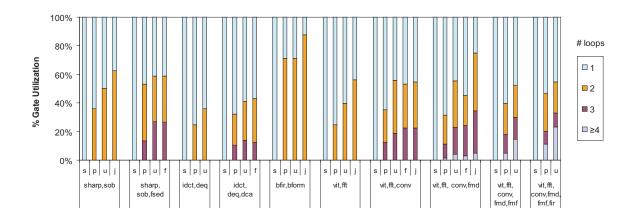

| 5.4  | Degree of sharing of multifunction accelerator gates across loops                                                                                                                                                             | 73   |

| 6.1  | Peak performance and power efficiency of different architecture styles.                                                                                                                                                       | 80   |

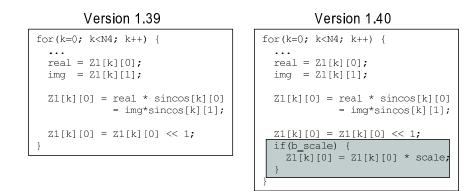

| 6.2  | Feature Addition to mdct.c in faad2                                                                                                                                                                                           | 83   |

| 6.3  | Bug-fix to mdct.c in faad2.                                                                                                                                                                                                   | 84   |

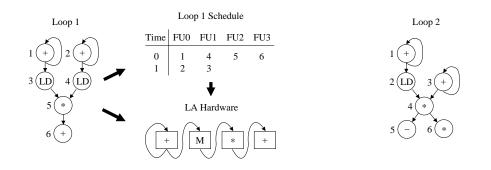

| 6.4  | LA scheduling and synthesis example                                                                                                                                                                                           | 85   |

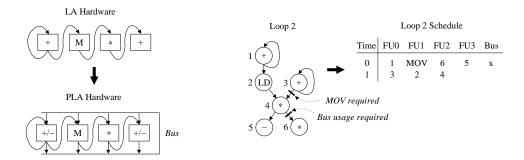

| 6.5  | PLA generalization and scheduling example                                                                                                                                                                                     | 88   |

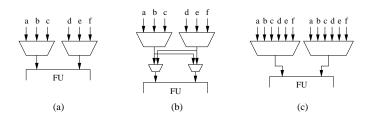

| 6.6  | Generalizing port-specific connections: (a) baseline, (b) allowing swaps,                                                                                                                                                     |      |

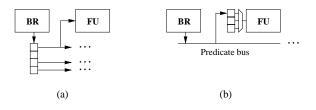

|      | (c) generalized. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                                                      | 90   |

| 6.7  | Generalizing staging predicate: (a) direct hardwired connections, (b) generalized.                                                                                                                                            | 91   |

| 6.8  | Template for programmable loop accelerator                                                                                                                                                                                    | 92   |

| 6.9  | Design and compilation flow for programmable loop accelerator                                                                                                                                                                 | 93   |

| 6.10 | Graph perturbation example from the heat benchmark: (a) original                                                                                                                                                              |      |

|      | loop, (b) after 5 perturbations, (c) after 10 perturbations.                                                                                                                                                                  | 102  |

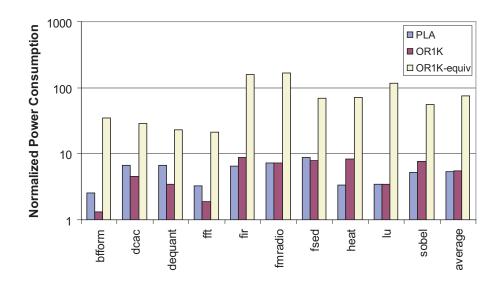

| 6.11 | Power consumption of PLA and OR-1200 relative to single-function LA                                                                                                                                                           | .105 |

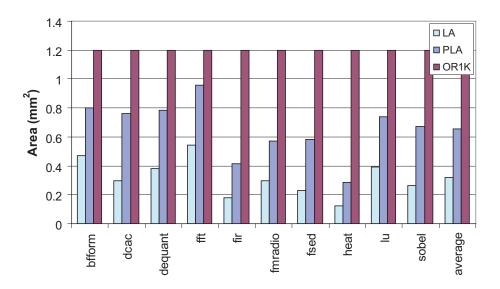

| 6.12 | Area of loop accelerators and OR-1200                                                                                                                                                                                         | 105  |

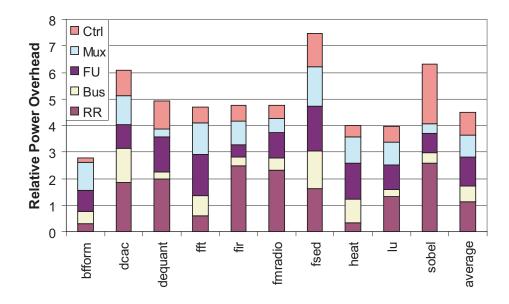

| 6.13 | Power consumption breakdown of PLA generalizations.                                                                                                                                                                           | 107  |

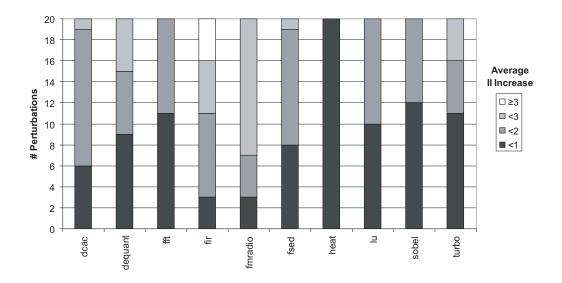

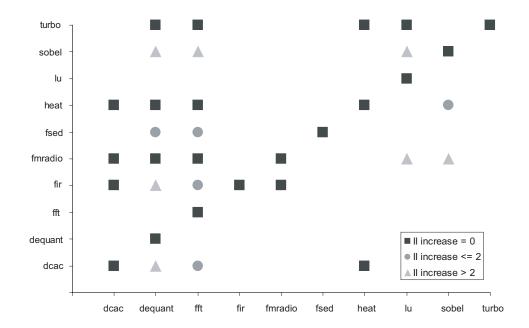

| 6.14 | II increase necessary to schedule loops with perturbations                                                                                                                                                                    | 110  |

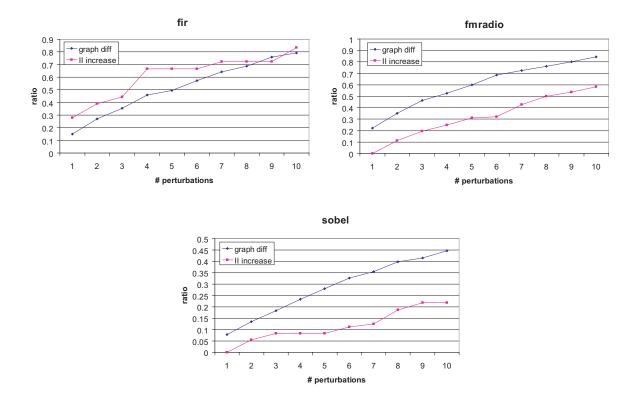

|      | Relative II increase and graph difference vs. perturbations for fir,                                                                                                                                                          |      |

|      | fmradio, and sobel.                                                                                                                                                                                                           | 111  |

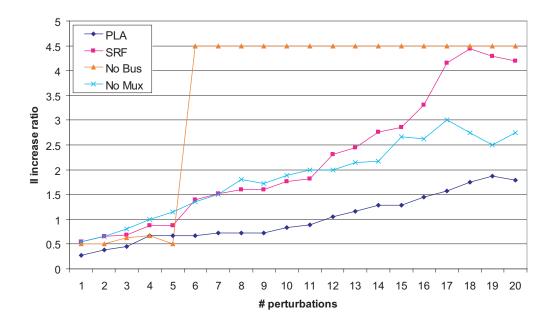

| 6.16 | Perturbation studies with more restrictive PLAs.                                                                                                                                                                              | 112  |

| 6.17 | Cross compilation results. PLAs are designed for loops along the x-                                                                                                                                                           |      |

|      | axis at II values listed in Table 6.1. Loops along the y-axis are then                                                                                                                                                        |      |

|      | mapped onto them.                                                                                                                                                                                                             | 113  |

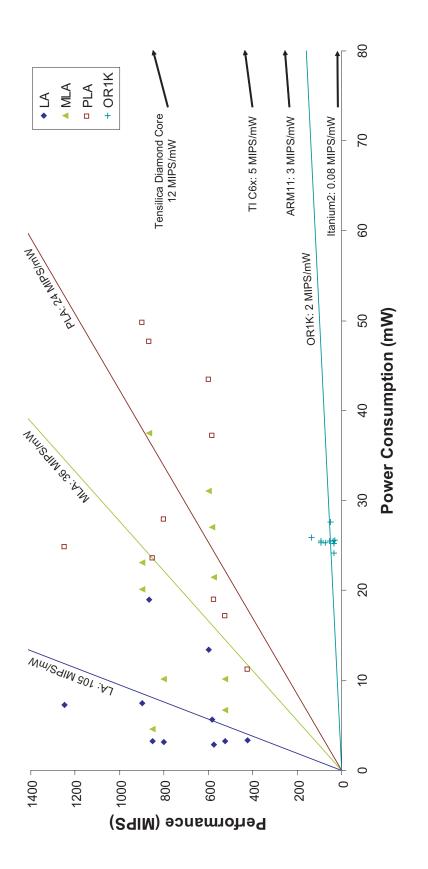

| 6.18 | Performance/power of loop accelerators, OR-1200, and commercial ar-                                                                                                                                                           |      |

|      | chitectures.                                                                                                                                                                                                                  | 116  |

# LIST OF TABLES

#### Table

| 6.1 | Loop kernels from DSP and media applications                       | 109 |

|-----|--------------------------------------------------------------------|-----|

| 6.2 | Similarity of loop kernels; a lower number means the two loops are |     |

|     | more similar to each other                                         | 114 |

#### ABSTRACT

# AUTOMATIC DESIGN OF EFFICIENT APPLICATION-CENTRIC ARCHITECTURES

by

Kevin C. Fan

Chair: Scott Mahlke

As the market for embedded devices continues to grow, the demand for high performance, low cost, and low power computation grows as well. Many embedded applications perform computationally intensive tasks such as processing streaming video or audio, wireless communication, or speech recognition. Often, performance requirements are on the order of 10-100 billion operations per second and must be implemented within tight power budgets on the order of 100 mW. Typically, general purpose processors are not able to meet these performance and power requirements. Custom hardware in the form of loop accelerators are often used to execute the compute-intensive portions of these applications because they can achieve significantly higher levels of performance and power efficiency. Automated hardware synthesis from high level specifications is a key technology used in designing these accelerators, because the resulting hardware is correct by construction, easing verification and greatly decreasing time-to-market in the quickly evolving embedded domain. In this dissertation, a compiler-directed approach is used to design a loop accelerator from a C specification and a throughput requirement. The compiler analyzes the loop and generates a virtual architecture containing sufficient resources to sustain the required throughput. Next, a software pipelining scheduler maps the operations in the loop to the virtual architecture. Finally, the accelerator datapath is derived from the resulting schedule.

In this dissertation, synthesis of different types of loop accelerators is investigated. First, the system for synthesizing single loop accelerators is detailed. In particular, a scheduler is presented that is aware of the effects of its decisions on the resulting hardware, and attempts to minimize hardware cost. Second, synthesis of multifunction loop accelerators, or accelerators capable of executing multiple loops, is presented. Such accelerators exploit coarse-grained hardware sharing across loops in order to reduce overall cost. Finally, synthesis of post-programmable accelerators is presented, allowing changes to be made to the software after an accelerator has been created.

The tradeoffs between the flexibility, cost, and energy efficiency of these different types of accelerators are investigated. Automatically synthesized loop accelerators are capable of achieving order-of-magnitude gains in performance, area efficiency, and power efficiency over processors, and programmable accelerators allow software changes while maintaining highly efficient levels of computation.

### CHAPTER 1

## Introduction

Embedded devices such as cellular phones, personal digital assistants, digital cameras, gaming platforms, and music players continue to proliferate. The embedded computing systems that go into these devices must meet the demands of higher performance and greater energy efficiency to support new functionality and higher bandwidth communication. For example, the projected data rates for 4G wireless data communication are expected to increase 50 times over current 3G standards [71]. Conventional programmable processors are unable to meet the demands of these applications, so custom hardware is used to provide the desired levels of performance and energy efficiency. This custom hardware commonly takes the form of loop accelerators, which execute the compute-intensive portions of applications. Low cost, high performance, systematic verification, and short time-to-market are all critical objectives for designing these accelerators. Automatic synthesis technology to build loop accelerators from high-level specifications is critical to achieving these objectives.

A key challenge with automatic synthesis is creating quality designs. Quality

can be defined along many axes, including performance, cost, and energy. Tradeoffs among these axes can be made depending on the particular goals of the application. In this work, various loop accelerator designs are proposed, and the performance, cost, and energy tradeoffs are investigated. The objective is to automatically create customized hardware for a given application or set of applications, so that order-ofmagnitude wins can be achieved in performance, cost, and energy consumption over general purpose processors.

Efficient accelerators are synthesized by optimizing the design in a number of ways. First, hardware structures are sized just large enough to meet the worst-case requirements of the application, both in terms of datapath width and number of entries in the storage structures. Second, connectivity between hardware structures is tailored to the application, decreasing interconnect costs, or conversely allowing the number of structures to be scaled up to exploit parallelism. Third, hardware can be shared by time multiplexing hardware components when either the hardware is required under disjoint conditions or the performance of dedicated hardware is not necessary.

This work examines the design of a loop accelerator synthesis system. The proposed system utilizes a compiler-directed approach for designing accelerators that was inspired by the PICO-NPA (Program-In Chip-Out Non-Programmable Accelerator) system [60]. The inputs to the system are a target loop expressed in C and the desired throughput. Synthesis is divided into three steps. First, a simple, single-cluster VLIW (Very Long Instruction Word) processor is designed to meet the throughput requirements of the application. The simple processor consists of a set of function units, connected to a centralized register file with unlimited entries and an unbounded memory. It provides an abstract target to which the compiler can efficiently map algorithms. Next, modulo scheduling [58] is performed to map the application onto the simple processor. Finally, a stylized loop accelerator is synthesized from the resulting schedule. Since the cost of the resulting accelerator is highly dependent on the schedule, an intelligent *cost sensitive modulo scheduler* is proposed that minimizes accelerator cost during the scheduling phase.

In order to achieve greater hardware efficiency, multiple loops may be implemented on the same loop accelerator if the loops are to be executed disjointly. The accelerator synthesis system is augmented to create accelerators that can execute multiple target loops given their respective throughput requirements. By reusing a common datapath for multiple loops, coarse-grained hardware sharing is achieved, reducing the overall hardware cost from the baseline case of creating individual accelerators for each loop.

Finally, programmability is added to the accelerator hardware in order to combat a downside of ASIC design, namely the inability to change the software. Applications in the embedded domain evolve rapidly, and it is important to be able to reuse accelerator hardware when the loop is changed. By introducing a degree of programmability to the accelerator, its flexibility and usable lifetime is increased, while maintaining the efficiency advantages of customization.

# **1.1** Contributions

This dissertation makes the following contributions:

- An automated synthesis system, taking as input a loop expressed in C code and a throughput requirement, and generating Verilog code representing a custom loop accelerator.

- A cost sensitive modulo scheduler that schedules operations to minimize the hardware cost of the resulting accelerator.

- A system to synthesize a multifunction loop accelerator given a set of input loops and throughput requirements.

- Extensions to the loop accelerator architecture and toolchain to enable postprogrammability, and evaluation of the tradeoffs between accelerator flexibility and efficiency.

# 1.2 Organization

The remainder of this dissertation is organized as follows. Chapter 2 provides an overview of the motivations and tradeoffs of designing customized hardware, and the benefits of automated design and hardware reuse. Chapter 3 describes the hardware organization of a loop accelerator and how it may be integrated into a system of accelerators. It then describes the synthesis flow for a single-function accelerator. Chapter 4 presents the cost sensitive modulo scheduler used in the synthesis. It also presents experimental data about the effectiveness of the scheduler and the methods of decomposing the scheduling problem to make it tractable for larger applications. Chapter 5 discusses multifunction loop accelerators and evaluates different methods of synthesizing them. Chapter 6 discusses the synthesis of programmable loop accelerators and the mapping of loops to such accelerators. The programmable accelerators are evaluated in terms of their area and power efficiency as well as their programmability. Finally, Chapter 7 concludes the dissertation and provides future research directions.

## CHAPTER 2

### **Background and Motivation**

## 2.1 The Costs of Computation

An algorithm or task has an inherent energy cost of computation, independent of what type of computing system is used to implement it. That is, given a task consisting of a set of operations to execute, there is a minimum amount of energy that must be expended in order to complete the task. If each operation corresponds to a computation by a function unit (FU), this overall minimum cost can be calculated by multiplying the energy cost of the FU executing each operation by the number of times that the operation needs to be executed, and summing up across all operations.

In reality, when the task is implemented on a computing system, there are additional costs that vary depending on the implementation, whether it is a traditional programmable processor, a coarse-grained reconfigurable architecture, an ASIC, or some other implementation. For example, intermediate values need to be stored in registers or memory, which have associated costs. Values need to be routed from pro-

Efficiency, Performance

Figure 2.1: Architecture design space.

ducing operations to consuming operations, and the associated wires and multiplexers have costs associated with them. Also, if the task is implemented in a programmable machine, there are costs associated with fetching and decoding instructions and controlling the datapath.

For example, an ASIC has relatively low cost overhead over the inherent computation costs, because the storage and routing elements are tailored for the needs of the specific application, and there are no costs associated with control. Conversely, a general purpose processor has significant costs because it consists of a pipeline that fetches and decodes instructions, reads values from a central, wide register file, bypasses values between FUs, etc. The tradeoff is that the processor is usable for a wide variety of applications, while the ASIC, though much more efficient, is only usable for one. Figure 2.1 shows several implementation types in this space. The tradeoffs between flexibility and efficiency of different implementations will be further discussed in Section 6.2.1 in the context of designing programmable accelerators. Thus, a typical embedded computing system is a heterogeneous mix of different types of computing implementations, each tailored towards different parts of the target applications. A critical loop nest, for instance, could be implemented on an ASIC, while more control-intensive out-of-loop code could be implemented on a general purpose core. In this way, different parts of the applications are matched with the most appropriate hardware implementations to achieve a design that is efficient overall.

In this dissertation, the focus is on applications in the embedded domain, including image, video, and audio processing, wireless communications, and encryption. Such applications typically consist of tight loops processing streaming data, and as such, the loops are critical to the overall performance. By creating efficient hardware accelerators targeted towards loops, significant wins are possible in performance and overall efficiency. These accelerators could be integrated into a heterogeneous system consisting of, for example, a general purpose core and a pipeline of several loop accelerators.

#### 2.2 Automated Synthesis

When creating ASICs, much of the cost comes from the design and verification process, which must be repeated for each new ASIC; these costs are not as easily amortized as when designing general purpose processors. In addition, the design and verification process takes a significant amount of time, which is challenging in the rapidly evolving embedded domain where market requirements and standards evolve quickly. Thus, automated synthesis from high-level specifications, such as C, becomes

Figure 2.2: Design productivity gap [61].

key.

Automated synthesis provides a design system that is correct by construction, thereby reducing verification times significantly. In addition, design times are reduced from months or years to weeks, greatly speeding time-to-market of new devices. This translates into increased performance relative to other devices on the market. For example, if performance improves by 50% every year, and it takes a year longer to do a hand design than an automatic design, then the hand design must be 50% faster just to break even.

Furthermore, as hardware continues to grow more complex each year, non-automated design methods fail to keep up. Figure 2.2 shows that the number of transistors per chip is growing at an exponentially faster rate than the growth in designer productivity. Thus, automated synthesis systems are needed to create new devices within a competitive time frame and keep up with the embedded market.

Traditionally, hardware synthesis from high-level specifications consists of directly

**Figure 2.3:** (a) Traditional behavioral synthesis. (b) Application-centric architecture synthesis.

translating C operators into hardware gates; see Figure 2.3. The synthesis system presented in this dissertation, however, takes a different approach, designing *applicationcentric architectures* for given applications. A performance requirement is specified in terms of the required loop throughput, and the system designs an application-specific loop accelerator to achieve the required throughput while maximizing hardware sharing, reducing overall cost and improving efficiency.

The synthesis system takes a compiler-directed approach, using compiler analyses to discover relationships between operations in a loop and expose instruction-level and loop-level parallelism. Compiler techniques are used to schedule the operations to maximize hardware sharing while meeting specified throughput requirements.

## 2.3 Hardware Reusability

As shown in Figure 2.1, the downside to creating an efficient application-specific accelerator is its lack of flexibility: the hardware cannot be reused to perform other tasks. Two methods are investigated to increase the reusability of the hardware.

The first method is to create an accelerator that can execute more than one loop.

In many cases, an embedded system will use hardware to accelerate multiple loops, and not all loops are executing simultaneously. When two or more loops are disjoint, one loop accelerator may be designed that is capable of executing some or all of the disjoint loops. This is referred to as a multifunction accelerator [20]. Coarse-grained hardware sharing is achieved, because a single multifunction accelerator is created rather than multiple single-loop accelerators.

Though multifunction accelerators increase hardware reuse and thus reduce cost, they still have the downside that all loops that will execute on the hardware must be known a priori. Therefore, the second method of increasing accelerator flexibility is to introduce post-programmability [21]. This allows a loop to be changed after the hardware has been created, and still be runnable on the hardware. Tradeoffs must be considered between the degree of customization of hardware to a given loop versus allowing more programmability, because as the datapath is generalized, additional cost overheads are introduced that reduce efficiency. An additional challenge is the question of how to quantify programmability of a hardware datapath.

#### 2.4 Related Work

Datapath synthesis from behavioral specifications is a field that has been studied for many years. The basic techniques, including resource allocation and scheduling, have been well established [22]. Cathedral III represents a complete synthesis system developed at IMEC and illustrates one comprehensive approach to high-level synthesis [49]. It uses an applicative language for program specification and designs customized datapaths for signal processing applications from this specification. Forcedirected scheduling is used to synthesize datapaths for ASIC design in [57]. The Sehwa system automatically designs processing pipelines from behavioral specifications [56]. The PICO system synthesizes C loop nests into a synchronous array of customized processor datapaths [60].

The above systems produce standard cell based designs. Automatic mapping of applications to FPGA-based and other reconfigurable systems has also been investigated. One of the first efforts to automatically map applications onto an FPGA was Splash [23], subsequently productized as the NAPA system [24]. Other automatic compiler systems for FPGA-based platforms include GARP [6], PRISM [70], and DEFACTO [5]. Modulo scheduling has been used to map critical loops onto reconfigurable coprocessors [27, 62]. Compilation for architectures consisting of predefined FUs and storage with reconfigurable interconnect have been investigated, including RaPiD [13] and PipeRench [25]. The MOVE processor [10] is an application specific instruction-set processor (ASIP) based upon transport triggered architectures, where instructions direct the flow of operands rather than the computation.

In addition to the works discussed here, there are related works relevant to specific chapters of this dissertation. Those chapters will contain their own discussion of related work.

## CHAPTER 3

# Hardware Organization and Design Flow

### 3.1 System View

Embedded devices commonly execute streaming applications, in which multiple compute-intensive loops (such as filters) operate in turn on large amounts of streaming data. The natural realization of these tasks is a hardware pipeline of accelerators, each implementing one or more of the tasks that process the data. Figure 3.1(a) shows an example of a streaming application that consists of multiple loops; in some cases, different loops are executed depending on the type of input data. Figure 3.1(b) shows a pipeline of loop accelerators designed to execute the loops in the application. Each accelerator executes one or more of the loops, and SRAM buffers in between the accelerator allow the output of one accelerator to feed into the input of the next. The accelerator labeled LA2 is a multifunction accelerator, and can execute either Loop 2 or Loop 3.

The hardware pipeline is designed in an intelligent way, matching the throughput

Figure 3.1: Streaming application mapped to pipeline of loop accelerators.

Figure 3.2: Loop accelerator template.

of each accelerator and sizing the buffers so that an overall performance goal is met while the overall system cost is minimized [34]. The specifics of the system-level design of the accelerator pipeline is outside the scope of this dissertation; this work focuses on synthesizing efficient individual accelerators.

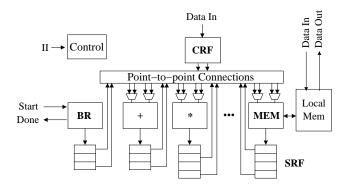

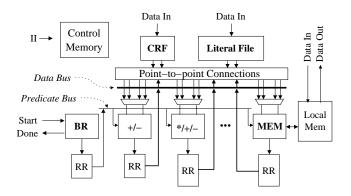

### **3.2** Accelerator Template

Figure 3.2 shows the hardware schema used in this system. It is designed to exploit the high degree of parallelism available in modulo scheduled loops with a large number of function units (FUs). Each FU writes to the top entry of a dedicated shift register file (SRF); entries move down at every cycle. Wires from the registers back to the FU inputs allow data transfer from producer to consumer. Multiple registers may be connected to each FU input; a multiplexer (MUX) is used to select the appropriate one. Since the operations executing in a modulo scheduled loop are periodic, the selector for this MUX is simply a modulo counter. Other than this counter, no control signals are needed to address the registers.

Literals and static live-in register values cannot be stored in the SRFs. Therefore, live-in values are supplied by a central register file (CRF), and literals are hardwired to the inputs of FUs that require them. FUs that access memory are connected to a local memory structure such as a scratchpad, cache, or stream buffer. The loop accelerator begins execution when a *start* signal is asserted by the host processor. When the loop execution is complete, the branch FU asserts a *done* signal to the host processor.

Support for predication in the loop accelerator hardware is useful, because it allows loops with internal control flow to be modulo scheduled and accelerated. In addition, modulo scheduling itself uses predication to implement the prolog, kernel, and epilog phases of the schedule. Predication is supported in the loop accelerator via a valid bit associated with each register. In each cycle, each FU produces a value that is written to the top entry of the corresponding SRF. If the guarding predicate of the FU is true during this cycle, the corresponding valid bit is set to true, otherwise it is set to false. Later, when the value is used by an FU, a data-merge MUX at the FU

Figure 3.3: Loop accelerator design flow.

input selects the register whose corresponding valid bit is set. If multiple registers are valid, the MUX should select the most recently computed valid value. Recency is known statically, as the register closest to the top of its SRF will have been computed most recently.

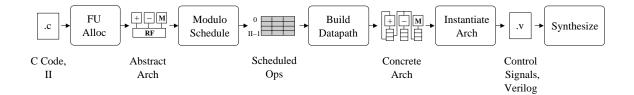

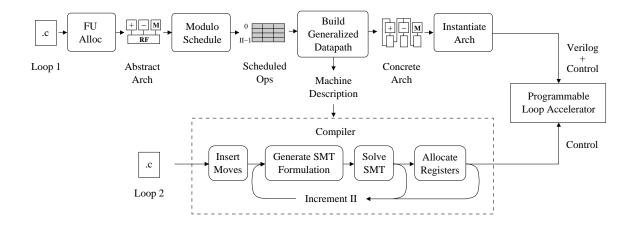

### 3.3 Accelerator Design Flow

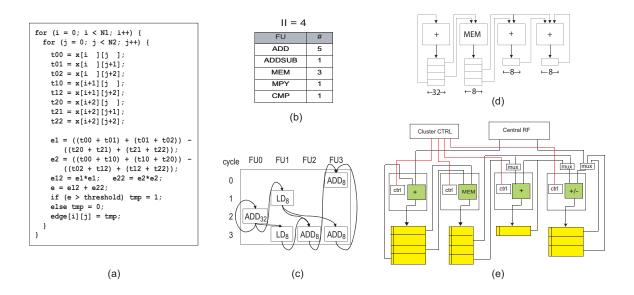

The overall flow of the synthesis system is presented in Figure 3.3. Each step of the flow is described in this section with an example from **sobel**, an edge detection algorithm.

#### 3.3.1 FU Allocation

This step takes the inputs of the system and creates an abstract VLIW architecture that represents a high-level view of the accelerator's functionality. The abstract architecture is parameterized only by the number of FUs and their capabilities; a single unified register file with infinite ports/elements that is connected to all FUs is assumed. Given the operations in the loop, the desired throughput (expressed as the initiation interval of the loop or II [58]), and a library of hardware cell capabilities and costs, the problem of FU allocation is to come up with a mix of FUs that minimizes cost while providing enough resources to meet the throughput constraint. In this phase, all FUs are assumed to be full width for cost purposes. (Bitwidth specialization is performed after the cost sensitive scheduling, when operations have been assigned to specific FUs.) In the simplest case where each operation can be executed by only one type of FU, [*compatible\_ops/II*] instances of each FU type should be created. However, operations can generally be executed by multiple types of FUs, such as when both adder and adder/subtractor units are available. In this case, the FU allocation problem becomes more complex and can be formulated as an integer linear program, minimizing the sum of the FU costs while supporting all of the operations. Figure 3.4(b) shows the result of FU allocation for **sobel** with II=4. There are 22 ADD and 2 SUB operations in the loop, which are covered by the 5 ADD and 1 ADDSUB units.

#### 3.3.2 Modulo Scheduling

The loop is modulo scheduled to the abstract architecture created in the previous step. A cost-sensitive modulo scheduler, to be described in Chapter 4, assigns operations to the resources and timeslots in the abstract architecture. At the completion of this phase, all of the loop operations are bound to resources and time, and the producer-consumer relationships between FUs have been determined. Figure 3.4(c) shows some operations from the modulo schedule for **sobel**, with edges indicating communication between operations. The number associated with each operation in-

Figure 3.4: An example loop accelerator design. (a) sobel source code, (b) result of FU allocation with II = 4, (c) a portion of the sobel modulo scheduled loop, (d) datapath derived from the modulo schedule shown in (c), (e) lowered datapath.

dicates its width; the width of each FU is set to the width of the largest operation assigned to it.

#### 3.3.3 Datapath Construction

The virtual FUs of the abstract architecture, concretized by operation assignments, directly become the FUs of the loop accelerator. The rest of the accelerator datapath is derived from the producer-consumer relationships in the modulo schedule. Wires connect a shift register entry at the output of a producing FU to the input of a consuming FU. The register entry that should be connected is determined from the difference in execution time between the producer and consumer, since register entries move down at every cycle. More specifically, the register number r that should be connected to transfer a value from producing operation p to consuming operation

$$r = time(c) - time(p) + iteration\_distance(p, c) * II - latency(p)$$

assuming that the topmost register in each SRF is numbered 0.

The bitwidths of FUs and register files are determined by the maximum bitwidth of operations that are mapped to the FU or contained in the register. The depth of a register file is set to the longest lifetime of the values produced by the corresponding FU. Figure 3.4(d) shows the SRFs and connections resulting from the scheduled operations in Figure 3.4(c).

#### 3.3.4 Architecture Instantiation

Lastly, the architecture created in the previous step is lowered into a Verilog realization of the accelerator. Each module in the datapath is translated into a set of primitive modules that have pre-defined behavioral Verilog descriptions. To reduce global wiring of control signals, we employ a distributed hierarchical control scheme that consists of three levels of control logic: FU control activates the appropriate primitive FU with the proper functionality and sets any internal MUX selects; cluster control converts the II value to generate high-level FU opcodes and sets the input MUXes select signals; and, processor control generates the II counter value. A subset of the final lowered datapath for **sobel** is presented in Figure 3.4(e). Input MUXes are added when multiple wires share the same FU input port, and the control path is generated to direct the MUXes and FUs.

c is:

# CHAPTER 4

### Cost Sensitive Modulo Scheduling

## 4.1 Introduction

This chapter focuses on the scheduling component of single-function accelerator synthesis. The scheduler is a key component of the synthesis system because the accelerator datapath is determined from the modulo schedule of operations, as described in Section 3.3.

Modulo scheduling is a method of overlapping iterations of a loop to achieve high throughput. The performance of the schedule is determined by the *initiation interval* (II), or the number of cycles between successive iterations of the loop. The modulo schedule contains a *kernel* which repeats every II cycles and may include operations from multiple loop iterations. As the modulo schedule implements a software pipeline, the execution of kernel operations must be orchestrated so that the pipeline fills and drains properly. The pipeline fill and drain phases are known as the *prolog* and *epilog*, respectively, and they are controlled during execution by a *staging predicate*. Scheduling algorithms used in compilers traditionally focus on goals such as reducing schedule length and register pressure or producing compact code. In the context of a hardware synthesis system where the schedule is used to determine various components of the hardware, including datapath, storage, and interconnect, the goals of a scheduler change drastically. In addition to achieving the traditional goals, the scheduler must proactively make decisions to ensure efficient hardware is produced.

The objective of cost sensitive modulo scheduling is to create a schedule that not only achieves a specified throughput, but also yields the lowest cost accelerator design. To accomplish this objective, the accelerator design is modeled during scheduling, so the impact of binding decisions on cost can be assessed. Our first approach to this problem utilized a greedy strategy, wherein at each scheduling step, the alternative that produced the least cost increase to the current design was made. The greedy approach was generally better than the baseline cost insensitive scheduler, but not by a large amount. The scheduler got trapped in too many local minima and the overall quality did not improve much.

The central problem is that each portion of the accelerator architecture is not the result of an individual scheduling decision, but rather is determined by many interrelated scheduling decisions. Each decision for a single operation has cost implications on earlier and later decisions. Thus, a greedy approach inherently does not make sense as the cost saved by making one decision is often unrelated to the cost of the entire design. As a result, we decided to focus on two scheduling methods that provide exact solutions: branch-and-bound and integer linear programming. Our approach is to develop cost sensitive formulations of both methods.

As with most exact formulations, these methods break down for moderate to large problem sizes as the run-time and memory usage of these methods explode. Thus, the scheduling problem is decomposed into a set of more manageable subproblems, where each subproblem is solved in a phase-ordered manner. We utilize three techniques to break down the problem: graph partitioning, space-time decomposition, and timespace decomposition. Graph partitioning divides loop bodies into smaller subgraphs, optimally scheduling the subgraphs, while space-time and time-space decomposition split the scheduling process into two separate phases, time slot and resource assignment. These methods sacrifice optimality of the schedule and thus of the cost of the accelerator, but enable realistic problems to be solved in a reasonable amount of time, while achieving substantial cost savings.

The contributions of this chapter are two-fold:

- Two exact methods for cost sensitive modulo scheduling are presented: branchand-bound and integer linear programming. Each method can be applied to optimize for area, interconnect, or a simple combination of both. The effectiveness of these methods is compared to traditional cost insensitive and greedy cost sensitive modulo schedulers.

- To address the issue of problem size explosion common to exact scheduling methods, three methods for decomposing scheduling algorithms into phased solutions of simpler subproblems are utilized. They consist of graph partitioning, time-space decomposition, and space-time decomposition. The implementation

details of each are presented along with analysis of the performance tradeoffs.

#### 4.2 Related Work

Cost sensitive scheduling in the context of data path synthesis has been studied for many years. Force-directed scheduling integrates resource allocation and scheduling into a common synthesis algorithm to minimize overall cost of synthesized datapaths [57]. Tradeoffs in allocating either low latency and expensive or high latency and inexpensive resources have been considered within an integrated scheduling and resource allocation algorithm [4]. [54] proposes a polynomial time scheduling algorithm based on heuristics that produces near optimal results. [36] presents an integer programming formulation for the scheduling problem in data path synthesis. Generation of more efficient designs by sharing hardware across basic blocks was recently proposed [46]. All of the above work handle only acyclic code regions. The optimization criteria usually is achieving shortest schedule length, or given a schedule length, achieving the least cost of data path. The focus of our work is cyclic scheduling. Though the components of the cost are the same, the optimization strategy is different because of the way in which function units are utilized in a cyclic schedule.

Heuristics that work as a preprocessing step to scheduling and try to minimize cost of the resulting hardware have also been studied. Clique-based partitioning algorithms were developed in the FACET project to jointly minimize function unit and inter-function unit communication costs [68]. Within the PICO system, width clustering is used to bind operations of narrow bitwidth to common resources to reduce datapath cost [42]. Assignment of scheduled operations to resources with the goal of increasing interconnect sharing has been proposed [55]. The advantage of preprocessing heuristics is that they are fast and usually achieve good results when used in conjunction with a traditional scheduling algorithm. Our work intertwines the cost minimization into the scheduling algorithm to achieve greater cost savings.

In the compiler domain, software pipelining is a technique to exploit instructionlevel parallelism by overlapping the execution of successive loop iterations. Modulo scheduling is a class of software pipelining algorithms that achieve high quality solutions and have been implemented in production compilers [58]. A number of extensions to modulo scheduling have been proposed to increase the quality of the solution, including reducing register requirements [14, 28, 40] and code size [41]. Reducing register requirements is most closely related to accelerator cost reduction. Swing modulo scheduling changes the core modulo scheduler to reduce register requirements by considering operations in different orders and changing how time slots are chosen [40]. Conversely, stage scheduling is a post-processing to shift the pipeline stage of instructions to reduce register requirements [14]. While the application of these techniques can reduce the cost of loop accelerators, the affect is limited as traditional compiler-based measures, such as register lifetimes, do not reflect the structure of a loop accelerator. For instance, a long lifetime may be free in an accelerator if it is scheduled to share a register with a similar lifetime. Hardware sharing and all aspects of cost must be considered to create efficient loop accelerators.

Many techniques for optimal modulo scheduling have been proposed in the lit-

erature. [15] proposes and efficient integer programming formulation for optimal modulo scheduling. [2] proposes an enumeration based approach for optimal modulo scheduling. Both of these techniques focus primarily on achieving a valid schedule. Minimizing register requirements has been the main optimization criteria for many of the works published on optimal modulo scheduling. [26], [16], and [17] formulate the modulo scheduling with minimum register requirements as an integer linear programming problem. Our work uses the basic ILP formulation from [15] and builds upon it significantly by adding variables and constraints to represent the cost of hardware and uses the hardware cost as the objective function.

### 4.3 Scheduling Techniques

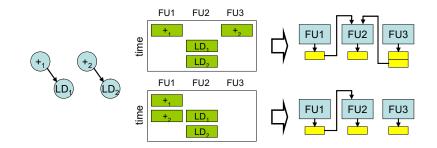

Cost sensitive modulo scheduling focuses on reducing the cost of three components of the hardware: FUs, register storage, and interconnect wires. These components were found to dominate the hardware cost of loop accelerators; other components such as multiplexers and control signals are less significant and are not specifically targeted for cost reduction in this work. By reducing the sizes of FUs and shift registers required to support execution of a given loop, the resulting hardware implementation will achieve the same throughput with fewer logic gates and less power. In addition, with high numbers of FUs and registers to support loop level parallelism, the interconnection network feeding values from registers to FU inputs can grow very large. Decreasing the number of wires required to support these data transfers reduces chip area from the wires themselves as well as from simplifying the placement and routing

Figure 4.1: Effect of schedule on wire cost.

of other structures in the hardware layout.

FU and storage cost can be reduced by scheduling operations cognizant of their resource and communication requirements, such as bitwidth and register lifetimes; by maximizing hardware reuse, the total amount of hardware is reduced. Wire cost can be reduced by maximizing reuse of the same wires by different producer and consumer operations. Wires are reused if producers and consumers are scheduled on the same respective FUs, and the consumers read data from the same shift register entry (i.e., the time differences between producers and consumers are identical). In Figure 4.1, assume the two pairs of operations to be scheduled are 32 bits wide. An interconnect-unaware modulo scheduler might produce the upper schedule, which requires 64 wires, while the lower schedule would have required only 32.

The remainder of this section describes approaches for achieving these goals, assigning operations to FUs and time slots such that the cost of the hardware needed to support their execution is minimized.

## 4.3.1 Greedy Scheduling

The baseline (naïve) scheduler used in this work is the iterative modulo scheduler described in [58], with a stage scheduling postpass [14]. This scheduler arbitrarily selects an available scheduling alternative for each operation in order to meet a given II, and does not consider hardware cost. The stage scheduling postpass reduces register lifetimes, which may reduce hardware cost, but this is done without cognizance of the hardware.

A straightforward way to make the scheduler cost-aware is to augment the naïve modulo scheduler with a hardware cost model and a greedy heuristic to minimize cost. The cost aware scheduling framework is shown in Figure 4.2. The main component of this framework is the hardware cost modeler, explained in more detail in Section 4.3.2.1. The hardware cost model is able to represent the cost of a partial machine, that is, the cost of hardware resources required to support execution of just the scheduled operations. In addition, the cost modeler can estimate the cost of hardware that would be required to support the remaining, unscheduled operations. (This estimate is explained in more detail in Section 4.3.2.2.)

To choose the best local alternative, the greedy modulo scheduler makes queries about the machine cost to the hardware cost modeler. The cost modeler returns a cost estimate that includes both the partial machine cost as well as the estimated cost of unscheduled operations. Based on this cost, the scheduler chooses the best alternative and schedules the operation on that particular FU and time slot. This is done for all operations in priority order, backtracking as needed. After the completion

Figure 4.2: Cost sensitive scheduling framework used for greedy and branch-andbound schedulers.

of greedy scheduling, the stage scheduling postpass is performed to decrease register lifetimes.

## 4.3.2 Branch-and-Bound Solution

A second method of obtaining a modulo schedule that minimizes hardware cost is to utilize an optimal branch-and-bound (BNB) solution. The goal is to search all possible schedules in order to find one that has the lowest hardware cost. The search is performed by scheduling each operation at all of its valid alternatives (FUs  $\times$  time slots). In a modulo schedule, each operation can be scheduled in at most II different time slots. Operations are considered in order of least to most available alternatives; the order does not affect the algorithm's optimality, only its runtime. The search space can be represented by a tree as shown in Figure 4.3. Each node represents a partial schedule, or a state in which some operations have been assigned FUs and

Figure 4.3: Branch-and-bound search. The highlighted state corresponds to the partial schedule shown.

time slots. The children of a node are formed by scheduling the next operation at all of its valid alternatives, subject to resource and dependence constraints. Leaf nodes in the tree therefore represent full schedules, and the goal is to locate a leaf node whose schedule requires the minimum amount of hardware.

#### 4.3.2.1 Hardware Modeling

The BNB scheduler uses a hardware model to estimate the cost of a machine supporting a given partial schedule. Three aspects of hardware cost are modeled: FUs, register storage, and interconnect wires. Function unit cost is determined by its capabilities and width. In the loop accelerator synthesis system, FU capabilities are determined during the FU allocation phase described in Section 3.3, prior to scheduling. Therefore, the scheduler has influence only on the width of the FU – if only narrow bitwidth operations are scheduled on an FU, then its cost can be reduced. The FU cost for a given partial schedule can therefore be determined as a function of the maximum bitwidth operation scheduled on each FU.

The register storage cost is determined similarly. Each shift register must be wide enough to accommodate the maximum bitwidth operation scheduled on the corresponding FU, and deep enough to hold the value with the longest lifetime. Also, interconnect wires must connect specific registers with FU input ports. Given a partial schedule, the known producer-consumer relationships between operations is used to obtain the widths and depths of the shift registers, as well as the number of interconnect wires required.

The BNB algorithm requires a single metric to determine whether a given schedule is better or worse than previously explored schedules. Therefore, when the objective is to decrease overall hardware cost, the combined metric used is the sum of wires, storage bits, and FU cost. The units of FU cost are scaled such that they are equivalent to storage bits in terms of the number of logic gates required for implementation. The wire, storage, and FU metrics may also be used alone, for example, to obtain a schedule with the objective of minimizing only storage cost.

### 4.3.2.2 Hardware Cost Estimation

An effective bound function is a crucial element in any BNB algorithm in order to prune, as early as possible, search paths that will not yield optimal results. The search is bounded using an estimate of the hardware needed to support operations that have not yet been scheduled. Thus, for any partial schedule, when the cost of hardware required by scheduled operations plus hardware estimated for unscheduled operations exceeds the best solution found so far, that search path is pruned. As long as the estimate is conservative (i.e., never overestimates the actual hardware cost), optimality is preserved as no search paths will be erroneously pruned. Additionally, the more accurate the estimate, the more likely a wrong path will be pruned earlier,

**Figure 4.4:** Wire estimation example: (a) DFG, (b) partial schedule, (c) connection diagram

thus decreasing the run time of the search.

Wire estimation. For the wire estimation, FUs are placed into groups based on their functionality. An FU group is the basic unit for estimation, and estimated connections are made between FU groups. For a given pair of FU groups, we collect all compatible edges<sup>1</sup> whose producer or consumer ops are unscheduled. Then, we determine the minimum number of additional connections required to support those unscheduled edges based on the number of available slots on the FUs (each FU has II slots). We optimistically assume that empty slots in the FUs can be occupied by any compatible unscheduled producer, ignoring scheduling constraints. This assumption guarantees that the estimation is a lower bound for the wire cost. It is assumed that existing wires in an FU group with *n* free slots can be reused by *n* unscheduled operations with compatible edges. When there are more than *n* such operations, new estimated connections are made to support the remaining operations.

Figure 4.4 shows how the estimation is performed for the ADD FU group. The processor consists of four FUs, two in the ADD FU group (FU0, FU1) and two in

<sup>&</sup>lt;sup>1</sup>Multiple dataflow edges whose producer and consumer operations can execute on corresponding FU groups.

the LD FU group (FU2, FU3). Assume the shaded operations are already scheduled and wires are being estimated for the unshaded operations. There are two types of edges originating from ADD operations: ADD $\rightarrow$ ADD and ADD $\rightarrow$ LD. As there is already a connection from FU 0 to FU 2 and FU 0 has one available slot, one of the two ADD $\rightarrow$ LD edges can potentially be scheduled without generating additional connections. This will make FU 0 fully occupied and the producer of the second edge must be placed on FU 1. Therefore, a new estimated connection between FU 1 and the LD FU group is created. Another estimation is performed independently for the ADD $\rightarrow$ ADD edges. Here, both can potentially be scheduled by placing the producers on FU 1, as it has two available slots. Thus, the ADD $\rightarrow$ ADD edges will not require any additional connections. As a result, the wire estimation for the ADD FU group is one. Wire estimation for the LD FU group proceeds in a similar manner.

**Storage estimation.** Estimating the incremental storage requirements for unscheduled operations is performed using an analogous method. First, the overall storage requirements for the unscheduled operations is determined; then, based on the number of available execution slots in the FUs and the existing register storage, the number of bits of new storage needed to support the unscheduled operations is estimated.

For each unscheduled operation, an estimate of the number of register bits needed to hold its result is obtained. This value depends on the width and depth of the output register; the width is simply the bitwidth of the operation, while the depth can be estimated from the estart/lstart<sup>2</sup> times of the operation and its consumers.

$<sup>^{2}</sup>estart_{op}$ : earliest start time of op ignoring resource constraints.  $lstart_{op}$ : latest start time of op

More specifically, for operation *op* with consumers *cons*:

$$depth = \left(\max_{c \in cons} estart_c\right) - lstart_{op} - latency_{op} \tag{4.1}$$

Once register requirements are approximated for the unscheduled operations, it is optimistically assumed that existing shift registers at the outputs of compatible FUs with available execution slots can be reused to satisfy these requirements. Any required register bits that cannot be satisfied by existing registers become part of the incremental storage estimation. Similarly to the wire estimation, this storage estimation does not take dependence constraints into consideration and is therefore conservative.

**Function unit estimation.** FU cost estimation is somewhat simpler than wire or storage estimation, since FU capabilities are fixed prior to scheduling and only the FU width varies depending on the schedule. First, unscheduled operations are grouped by type and their maximum bitwidth is determined. Next, existing FUs with free slots are used to satisfy these FU requirements. Finally, the additional cost of FUs needed to support the remaining operations (either by widening existing FUs or creating new FUs) is calculated.

For a given partial schedule, once the wire, storage, and FU costs have been estimated for the unscheduled operations, the search may be pruned. Once again, a single metric is needed for the hardware cost estimate, and this is obtained by the weighted sum of the wire, storage, and FU cost metrics. Note that these hardware without delaying exit operations. estimations are performed at every step of the BNB search. Therefore, they are implemented in a computationally efficient way, using incremental updates to internal data structures in order to minimize their impact on the execution time of the search. Note also that it is worthwhile to spend some computation time obtaining an accurate estimate if it allows the search paths to be pruned earlier, since the number of states eliminated by pruning a node is exponential in the height of the node.

### 4.3.3 Integer Linear Programming Formulation

The third approach to the problem is an integer linear programming (ILP) formulation for achieving modulo schedules optimal with respect to the cost of hardware generated from the schedule. The basic structure of the formulation is identical to the one proposed in [15, 26]. The basic formulation described in these works do not perform FU assignment, but only ensure that a valid assignment is possible. FU assignment is crucial in determining cost of hardware derived from the schedule. In the formulation described in this section, additional variables and constraints to represent FU assignment for operations is added to the basic formulation. An objective function to represent hardware cost is derived from these variables and constraints.

### 4.3.3.1 Basic Formulation

The body of the loop under consideration is represented by a graph  $G = \{V, E\}$ , where V represents the set of operations in the loop body and E represents data dependence edges between operations. Each dependence edge has an associated latency  $l_{i,j}$  which specifies the latency of the producer *i*, and a distance  $d_{i,j}$ , which specifies the difference in iterations between when the value is produced by *i* and when the value is consumed by *j*.

Consider a loop with |V| = N operations. Let II be the initiation interval. The schedule for this loop is represented by  $II \times N$  binary variables  $X_{i,s}$ . Operation  $i \in \{0, N-1\}$  is scheduled in slot  $s, 0 \leq s \leq II - 1$ , if  $X_{i,s} = 1$ . The following constraint enforces a unique slot for every operation i.

$$\sum_{s=0}^{II-1} X_{i,s} = 1 \qquad \forall i \in \{0, N-1\}$$

(4.2)

N integer variables  $k_i, i \in \{0, N-1\}$  are introduced to represent the stage in which each operation is placed.  $X_{i,s}$  and  $k_i$  uniquely identify the cycle in which an operation *i* is scheduled. In fact, the schedule time of an operation *i* is given by

$$t_i = \sum_{s=1}^{II-1} s \times X_{i,s} + II \times k_i \tag{4.3}$$

Note that  $t_i$  is used as a shorthand to represent the schedule time of an operation *i*. In a real implementation, there is no need to introduce a new variable to represent the schedule time. Given the  $t_i$ 's for all operations, the data dependences between operations can be enforced with the following set of constraints.

$$t_j + d_{i,j} \times II - t_i \ge l_{i,j} \qquad \forall (i,j) \in E$$

$$(4.4)$$

The schedule times should satisfy the resource constraints, i.e., the number of operations scheduled in each slot should not exceed the available number of FUs for each FU type. Suppose  $I_f$  are the set of operations that require a FU of type f and  $M_f$  are the total number of FUs of type f available. Then, the following constraint enforces the resource constraints.

$$\sum_{i \in I_f} X_{i,s} \le M_f \qquad s \in \{0, II-1\}$$

$$(4.5)$$

Note that the above constraint only ensures a valid FU assignment and does not actually perform the assignment.

#### 4.3.3.2 Function Unit Assignment

The FU assignment for operations is represented by a set of binary variables  $R_{i,j}$ ,  $i \in \{0, N-1\}, j \in \{0, M_f - 1\}$ , i.e., there are  $M_f$  binary variables for every op i, where  $M_f$  is the number of compatible FUs to which i can be assigned. The following constraint enforces a unique assignment.

$$\sum_{j=0}^{M_f - 1} R_{i,j} = 1 \qquad \forall i \in \{0, N - 1\}$$

(4.6)

The number of operations assigned to a particular FU cannot exceed *II*. The following constraint enforces this.

$$\sum_{i \in I_j} R_{i,j} \le II \qquad i \in I_j \text{ can execute on } j \qquad (4.7)$$

Even with the above constraint, an FU can be assigned to two operations in the same cycle. To prevent this from happening, the following constraint has to be enforced for every FU.

$$\sum_{i \in I_j} R_{i,j} \times X_{i,s} \le 1 \qquad \forall s \in \{0, II-1\} and i \in I_j \text{ can execute on FU } j \qquad (4.8)$$

The above equation is a sum of products of two binary variables, and is non-linear; it can be linearized as follows. For every  $R_{i,j}$  and  $X_{i,s}$  appearing in the above set of equations, an auxiliary binary variable  $Z_{i,j,s}$  is introduced and following set constraints are enforced on  $Z_{i,j,s}$ .

$$\begin{array}{rcl}

-R_{i,j} + Z_{i,j,s} &\leq 0 \\

-X_{i,s} + Z_{i,j,s} &\leq 0 \\

R_{i,j} + X_{i,s} - Z_{i,j,s} &\leq 1

\end{array}$$

(4.9)

Now the product terms in Equation 4.8 can be replaced with the corresponding  $Z_{i,j,s}$ 's. Solving equations 4.2 through 4.9 would yield a valid schedule and FU assignment for operations in a loop.

#### 4.3.3.3 Cost Minimization