# An Effective Verification Solution for Modern Microprocessors

by Ilya Wagner

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in The University of Michigan 2008

Doctoral Committee:

Assistant Professor Valeria M. Bertacco, Chair Professor Nilton O. Renno Associate Professor Todd M. Austin Associate Professor Scott Mahlke

To my Mom and Dad

### ACKNOWLEDGEMENTS

I would like to thank my advisor Professor Valeria Bertacco, who guided me on the path towards my degree. For every project, paper and presentation that we worked on together she provided priceless advice, ensuring that the work was performed on time and with the best possible quality. I am also infinitely grateful to her for all the patience and tenacity with which she helped me improve my writing and presentation skills. I feel very fortunate to have her as my academic advisor, teacher and mentor.

I would also like to thank my committee members: Professor Todd Austin, Professor Scott Mahlke and Professor Nilton Renno. Throughout the years of graduate school I've enjoyed working with Professor Austin personally on several projects and always appreciated his brilliant ideas and advise. Likewise, I'd like to thank Professor Nilton Renno who supervised the Mars Rover Design Team - an extracurricular project that have been a major part of my life for four years. Although I have not worked personally with Professor Mahlke, I have always respected his opinion and advise, and would like to thank him for providing valuable comments that made the completion of this dissertation possible. Additionally, I thank Mark Brehob, one of the best teachers and lecturers I met in my life; it was his classes that sparked my interest to microprocessor design in the last year of undergraduate school.

I am deeply grateful to the all the people who collaborated with me on several of the projects: Andrew DeOrio, Kai-hui Chang, Joseph Greathouse and David Ramos. I also would like to thank all of the fellow Computer Science and Engineering students, who did not formally work with me, yet have become my good friends: Steven Plaza, Smitha Shyam, Kypros Constantinides, Andreas Moustakas, Andrea Pellegrini, Jin Hu, Jeff Hao, David Papa, Jarrod Roy, David Roberts, Adam Bauserman, Debapriya Chatterjee, David Meisner, Shobana Sudhakar, Bashar Al-Rawi, James Anderson, Hector Garsia and Geoff Blake. To those of you who have graduated already and those who remain in the lab – I bid you farewell and the best of luck. Likewise, I thank my friends in Russia, who, despite of being far away, still remain in my heart.

Finally, I'd like to thank my entire family, especially my brother Dmitriy and my sisters Vera and Anna, who always stood by me. I'd like to specially thank my sister-in-law Vita, whose help, hospitality and culinary skills I enjoyed on so many occasions, while living in Ann Arbor. I wish her the best of luck with her Ph.D. research and dissertation. Last, but not least, completion of this work would not be possible without the support of my mother and father who always encouraged me to follow the path of learning and discovery, supported me in the times of failure and celebrated my successes.

### PREFACE

Over the past four decades microprocessors have come to be a vital and inseparable part of the modern world, becoming the digital brain of numerous electronic devices and gadgets that make today's lifestyle possible. Processors are capable of performing computation at astonishingly high speeds and are extremely integrated, occupying only a few square centimeters of silicon die. However, this computational power comes at a price: the task of verifying a modern microprocessor and guaranteeing correctness of its operation is increasingly challenging, even for most established processor vendors. Always attempting to deliver higher performance to end-users, processor manufacturers are forced to design progressively more complex circuits and employ immense verification teams to eliminate critical design bugs in a timely manner. Unfortunately, too often size doesn't seem to matter in verification, as schedules continue to slip and microprocessors find their way to the marketplace with design errors.

This work describes a novel verification framework targeting specifically today's complex microprocessors. The scope of the work spans many levels of verification and different phases of the processor life-cycle, from validation of individual sub-modules to complete multi-core system, and from pre-silicon design verification to in-the-field hardware patching. In particular, our StressTest and MCjammer approaches enable efficient generation of high-quality tests at the pre-silicon level for individual cores and multi-core systems, respectively, using machine learning techniques and making the process as automatic as possible. On the other hand, Reversi and Dacota enable low cost validation in post-silicon, while delivering even higher coverage than pre-silicon techniques. Finally, the Field-repairable control logic (FRCL) and Caspar techniques allow designers to patch different classes of escaped errors in processors that are deployed in the field.

The integrated set of solutions that we introduce with this thesis empowers processor vendors to drastically shorten their development timeline and, at the same time, to deliver more reliable and correct systems to their customers at a lower cost. Altogether, this work has the potential to solve the long-standing challenge of guaranteeing the complete functional correctness of modern microprocessors.

# **TABLE OF CONTENTS**

| DEDICAT   | ΙΟΝ                                                         | ii  |  |  |  |

|-----------|-------------------------------------------------------------|-----|--|--|--|

| ACKNOW    | LEDGEMENTS                                                  | iii |  |  |  |

| PREFACE   |                                                             |     |  |  |  |

| LIST OF F | IGURES                                                      | X   |  |  |  |

| LIST OF 1 | ABLES                                                       | ٢V  |  |  |  |

| Chapte    | r I. Introduction                                           | 1   |  |  |  |

| 1.1       |                                                             | 4   |  |  |  |

| 1.2       |                                                             | 6   |  |  |  |

| 1.3       | Guiding Principles in Developing the Verification Solutions | 8   |  |  |  |

|           |                                                             | 8   |  |  |  |

|           |                                                             | 9   |  |  |  |

|           | 1.3.3 Minimization of Area and Performance Overhead         | 9   |  |  |  |

| Chapte    | <b>r II. Pre-silicon Verification of a Single Core</b>      | 1   |  |  |  |

| 2.1       |                                                             | 12  |  |  |  |

| 2.2       |                                                             | 3   |  |  |  |

|           |                                                             | 4   |  |  |  |

|           |                                                             | 6   |  |  |  |

|           | 1 2                                                         | 8   |  |  |  |

|           |                                                             | 20  |  |  |  |

| 2.3       | 5                                                           | 22  |  |  |  |

|           |                                                             | 22  |  |  |  |

|           |                                                             | 25  |  |  |  |

| 2.4       | 5                                                           | 26  |  |  |  |

| 2.5       | r · · · · · · · · · · · · · · · · · · ·                     | 28  |  |  |  |

|           |                                                             | 28  |  |  |  |

|           | 1 2                                                         | 30  |  |  |  |

|           | 2.5.3 Stability of the Activity Monitors                    | 31  |  |  |  |

|             | 2.5.4<br>2.5.5<br>2.5.6 | StressTest Coverage Density and PerformanceDepth-driven Activity MonitorsEvaluation of Hierarchical Markov Models | · · |   | 33<br>37<br>37 |

|-------------|-------------------------|-------------------------------------------------------------------------------------------------------------------|-----|---|----------------|

| 2.6<br>2.7  |                         | ed Work                                                                                                           |     |   | 39<br>41       |

| Chapte      | r III. I                | Post-silicon Verification of a Single Core                                                                        |     |   | 42             |

| 3.1         | Revers                  | si Test Generation System                                                                                         |     |   | 43             |

|             | 3.1.1                   | Reversible and Non-reversible Instructions                                                                        |     |   | 45             |

|             | 3.1.2                   | Limitations                                                                                                       |     |   | 50             |

|             | 3.1.3                   | Reversi Generator                                                                                                 |     |   | 50             |

| 3.2         | Exam                    | ple                                                                                                               |     |   | 52             |

|             | 3.2.1                   | Experimental Framework                                                                                            |     |   | 54             |

| 3.3         | Exper                   | imental Evaluation                                                                                                |     |   | 54             |

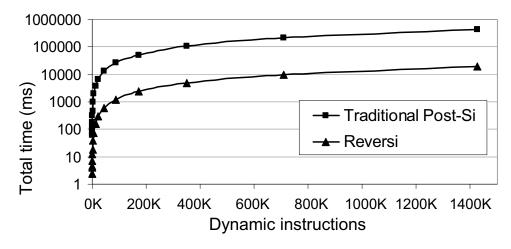

|             | 3.3.1                   | Performance Evaluation                                                                                            |     |   | 54             |

|             | 3.3.2                   | Design Error Coverage                                                                                             |     |   | 56             |

| 3.4         | Summ                    | nary                                                                                                              |     | • | 57             |

| Chapte      | r IV. H                 | Iardware Patching of a Single Core                                                                                |     |   | 59             |

| 4.1         | Backo                   | ground                                                                                                            |     |   | 60             |

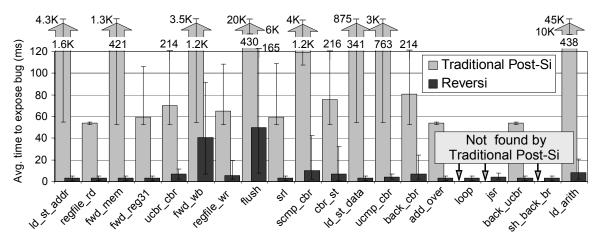

| 1,1         | 4.1.1                   | Analysis of Escaped Errors in Commercial Processors                                                               |     |   | 60             |

|             | 4.1.2                   | Hardware patching approaches                                                                                      |     |   | 62             |

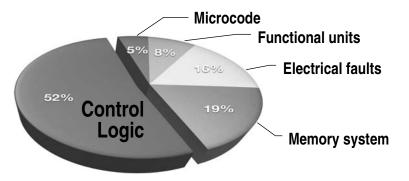

| 4.2         |                         | repairable Control Logic (FRCL) flow of Operation                                                                 |     |   | 64             |

| 1.2         | 4.2.1                   | Pattern Generation                                                                                                |     |   | 64             |

|             | 4.2.2                   | Matching Flawed Configurations                                                                                    |     |   | 65             |

|             | 4.2.3                   | Pattern Compression Algorithm                                                                                     |     |   | 67             |

|             | 4.2.4                   | Processor Recovery                                                                                                |     |   | 70             |

|             | 4.2.5                   | Example                                                                                                           |     |   | 72             |

| 4.3         |                         | n Flow                                                                                                            |     |   | 73             |

| <b>+</b> .J | 4.3.1                   | Overview of the Design Framework                                                                                  |     | • | 73             |

|             | 4.3.2                   | Verification Methodology                                                                                          |     |   | 74             |

|             | 4.3.3                   | Control Signal Selection                                                                                          |     |   | 75             |

|             | 4.3.4                   | Automatic Signal Selection                                                                                        |     |   | 76             |

|             | 4.3.5                   | Performance-critical Execution                                                                                    |     |   | 77             |

| 4.4         |                         | ed Hardware Design with Semantic Guardians                                                                        |     |   | 78             |

| 4.4         | 4.4.1                   | Combining Semantic Guardians and Hardware Patching.                                                               |     |   | 80             |

| 4.5         |                         | imental Evaluation                                                                                                |     |   | 81             |

| 4.3         | 4.5.1                   | Experimental Framework                                                                                            |     |   | 82             |

|             | 4.5.1                   |                                                                                                                   |     |   | 85             |

|             | 4.5.2<br>4.5.3          | Design Defects                                                                                                    |     |   | 85<br>86       |

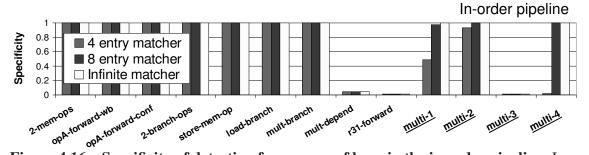

|             |                         | Specificity of the Matcher                                                                                        |     |   |                |

|             | 4.5.4                   | State Matcher Area and Timing Overheads                                                                           |     |   | 88             |

|             | 4.5.5                   | Performance Impact of Degraded Mode                                                                               | • • | • | 89             |

|          | 4.5.6 Semantic Guardian Framework Analysis 90  |

|----------|------------------------------------------------|

| 4.6      | Summary 94                                     |

|          |                                                |

| Chapte   | r V. Pre-silicon Verification of Multi-Cores   |

| 5.1      | Background                                     |

| 5.2      | MCjammer Tool                                  |

| 5.2      | 5.2.1 Overall Structure                        |

|          | 5.2.2 Dichotomic Finite-State Machine          |

|          | 5.2.3 Agents' Goals                            |

| 5.3      | Feedback and Correctness                       |

| 5.5      | 5.3.1 Coverage and Pressure                    |

|          | 5.3.2 Error Check                              |

| 5.4      | Experimental Results                           |

| 5.5      | Summary                                        |

| 5.5      | Summary                                        |

| Chapte   | r VI. Post-Silicon Verification of Multi-Cores |

| <b>I</b> |                                                |

| 6.1      | Dacota Overview                                |

| 6.2      | Activity Logging                               |

|          | 6.2.1 Access vector                            |

|          | 6.2.2 Core activity log                        |

|          | 6.2.3 Activity Logging Example                 |

| 6.3      | Policy Validation                              |

|          | 6.3.1 Access log aggregation                   |

|          | 6.3.2 Graph construction                       |

|          | 6.3.3 Graph analysis                           |

|          | 6.3.4 Examples of error detection              |

|          | 6.3.5 Requirements for checking algorithm      |

| 6.4      | Strengths and Limitations                      |

|          | 6.4.1 Debugging with Dacota                    |

|          | 6.4.2 Design Considerations                    |

| 6.5      | Experimental Evaluation                        |

|          | 6.5.1 Experimental Framework                   |

|          | 6.5.2 Design Error Coverage                    |

|          | 6.5.3 Performance Evaluation                   |

|          | 6.5.4 Area Evaluation                          |

| 6.6      | Summary                                        |

|          |                                                |

| Chapte   | r VII. Hardware Patching of Multi-Cores        |

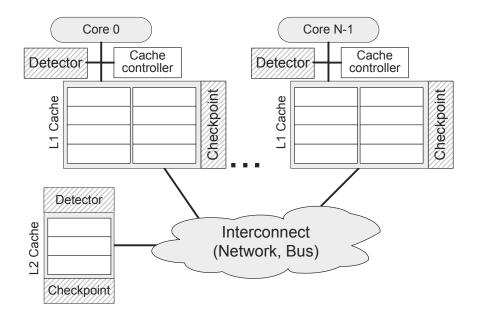

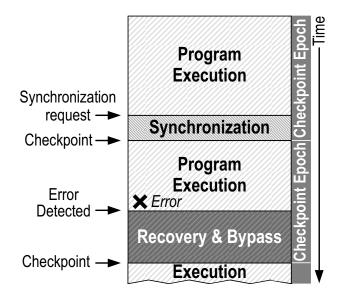

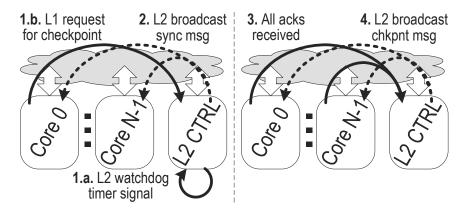

| 7.1      | Caspar Overview                                |

| /.1      | 1                                              |

|          | I C                                            |

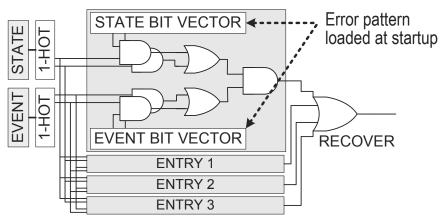

|          | 7.1.2 Detection                                |

|          | 7.1.3   | Recovery and Bypass                |

|----------|---------|------------------------------------|

|          | 7.1.4   | Post-silicon debugging with Caspar |

| 7.2      | Exper   | imental Evaluation                 |

|          | 7.2.1   | Experimental Platform              |

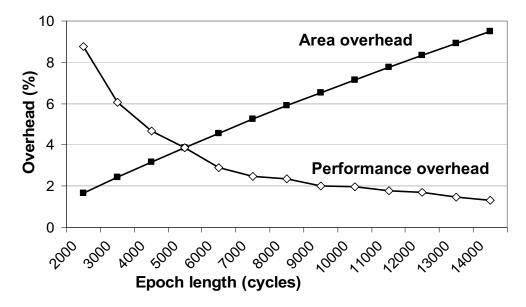

|          | 7.2.2   | Checkpointing Overheads            |

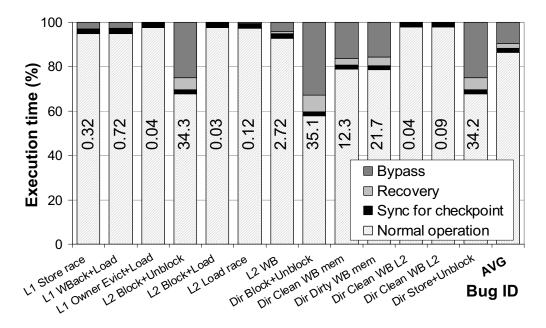

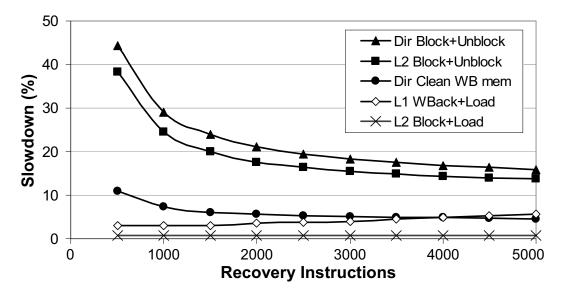

|          | 7.2.3   | Error Resiliency Analysis          |

|          | 7.2.4   | Caspar Recovery Performance        |

|          | 7.2.5   | Event Detector Area Overhead       |

| 7.3      | Summ    | nary                               |

| Chapter  | r VIII. | <b>Conclusions and Future Work</b> |

| BIBLIOGH | RAPHY   |                                    |

# **LIST OF FIGURES**

# Figure

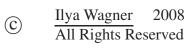

| 1.1  | Modern microprocessor design and verification flow.                                                 | 5  |

|------|-----------------------------------------------------------------------------------------------------|----|

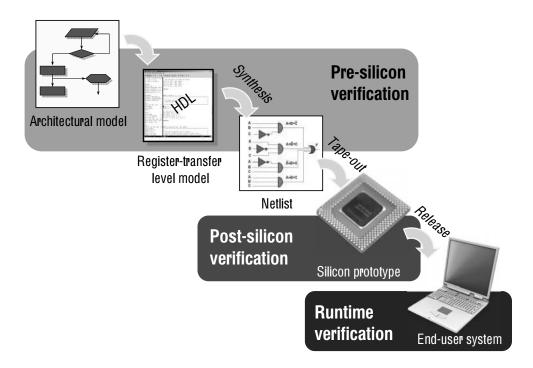

| 1.2  | Verification throughout a processor's life-cycle                                                    | 7  |

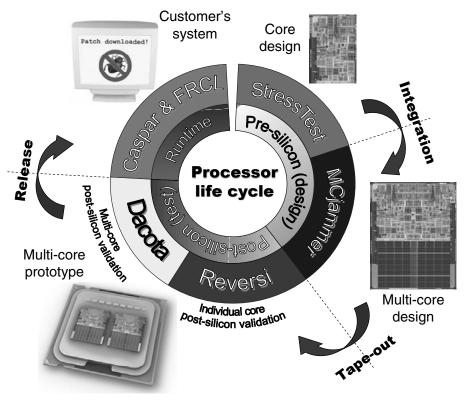

| 2.1  | StressTest structure                                                                                | 13 |

| 2.2  | Example of Markov model                                                                             | 15 |

| 2.3  | Example of a StressTest template file.                                                              | 17 |

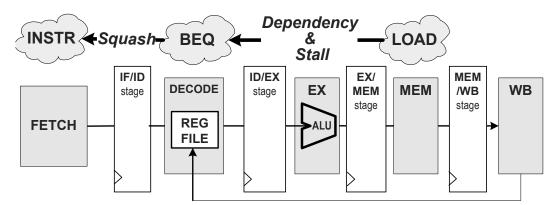

| 2.4  | Dependency variable functional block.                                                               | 19 |

| 2.5  | Example of an extended StressTest template file                                                     | 21 |

| 2.6  | Impact of activity monitors.                                                                        | 23 |

| 2.7  | Depth-driven activity monitors.                                                                     | 25 |

| 2.8  | Pipeline snapshot for case study.                                                                   | 26 |

| 2.9  | Results of two sample runs with different values of cacheSize and lambda.                           | 30 |

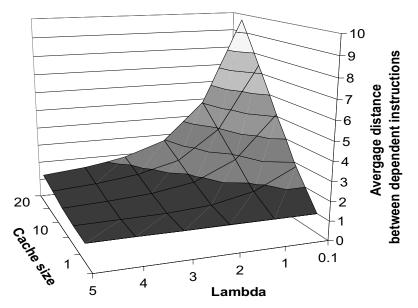

| 2.10 | Average distance between dependent instructions                                                     | 31 |

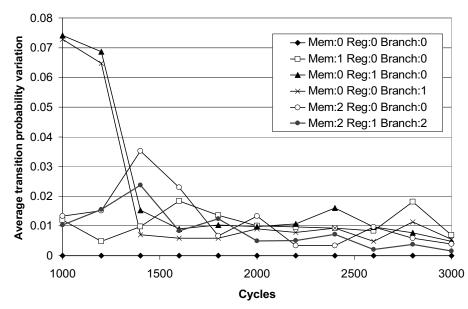

| 2.11 | Impact of activity monitor's weights on the Markov model stability                                  | 32 |

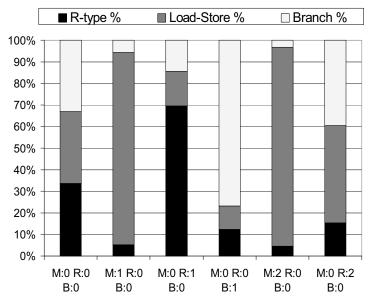

| 2.12 | Impact of the monitor's weight on stimuli generated                                                 | 33 |

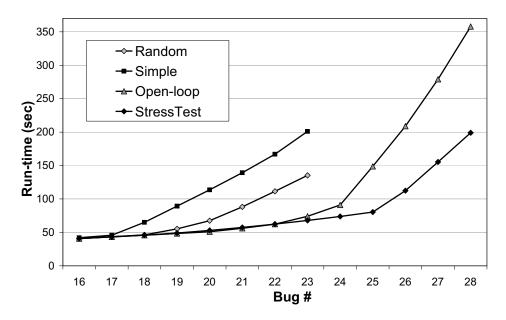

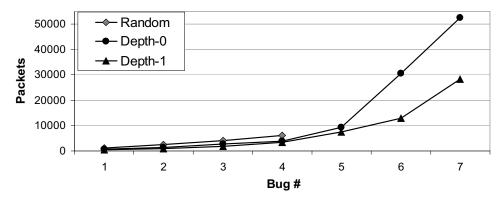

| 2.13 | Effort versus bugs covered for the DLX processor                                                    | 35 |

| 2.14 | Effort versus bugs covered for the Alpha processor.                                                 | 36 |

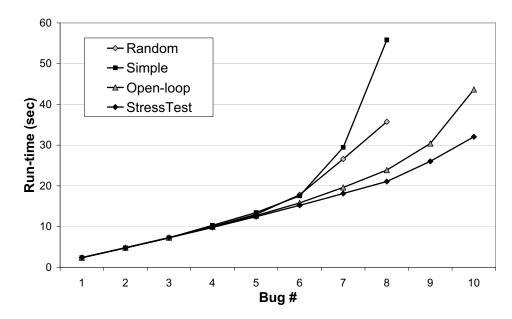

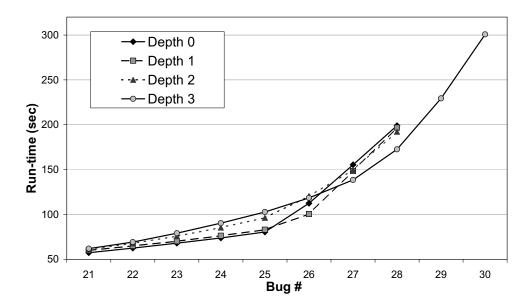

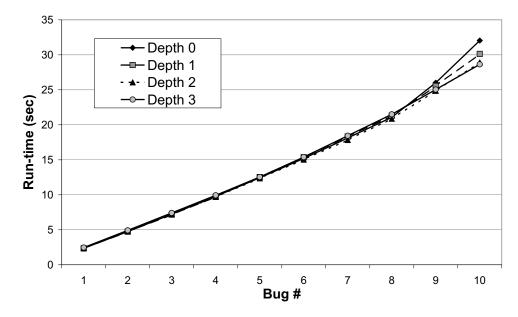

| 2.15 | Effort versus bugs covered for StressTest with depth-driven activity mon-<br>itors (DLX processor). | 38 |

| 2.16 | Effort versus bugs covered for StressTest with depth-driven activity mon-<br>itors (Alpha processor) | 38 |

|------|------------------------------------------------------------------------------------------------------|----|

| 2.17 | Effort vs. Bug coverage for the switch design                                                        | 39 |

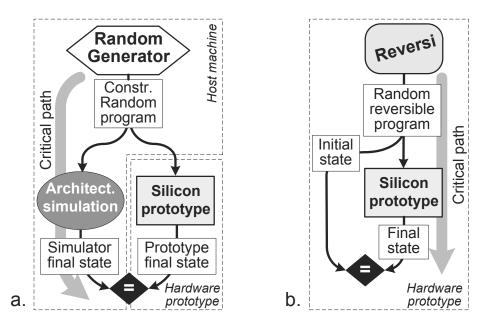

| 3.1  | A typical post-silicon validation flow vs. a Reversi-based flow                                      | 44 |

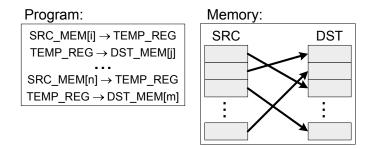

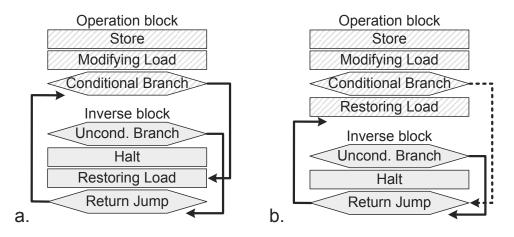

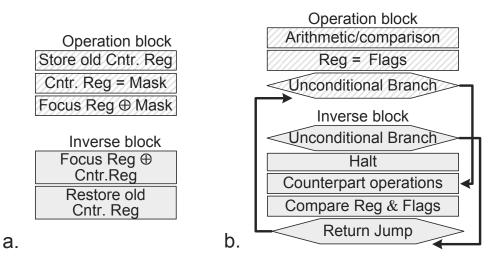

| 3.2  | Blocks for load and store instructions.                                                              | 47 |

| 3.3  | Branch operations.                                                                                   | 48 |

| 3.4  | Handling of instructions affecting control flags                                                     | 49 |

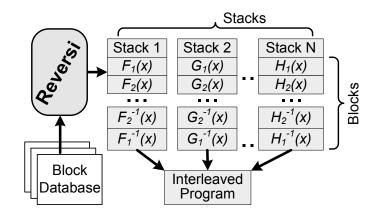

| 3.5  | Reversi operation.                                                                                   | 51 |

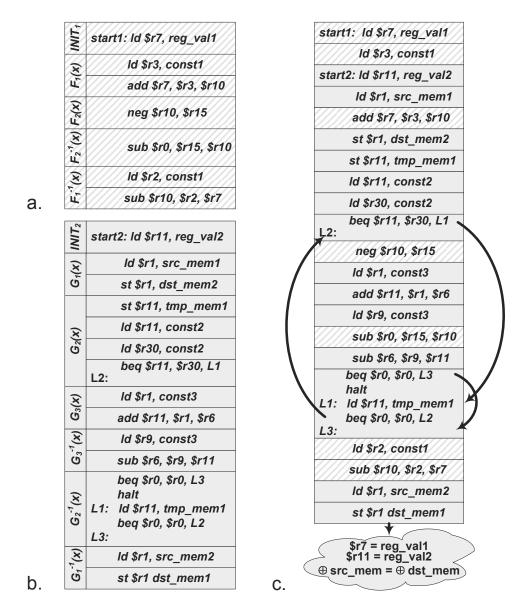

| 3.6  | Test program for the example ISA                                                                     | 53 |

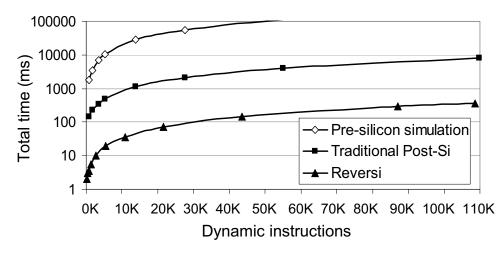

| 3.7  | Total testing time for a traditional post-si flow and Reversi: Alpha in-<br>struction set            | 55 |

| 3.8  | Total testing time for a traditional post-si flow and Reversi: x86 instruc-<br>tion set              | 55 |

| 3.9  | Average time to discover bugs in the traditional post-silicon flow and Reversi.                      | 56 |

| 4.1  | Classification of escaped bugs found in commercial processors                                        | 61 |

| 4.2  | Field-repairable control logic usage flow                                                            | 65 |

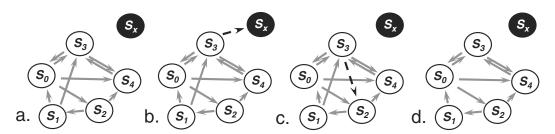

| 4.3  | Error representation in the state transition graph (STG) framework                                   | 66 |

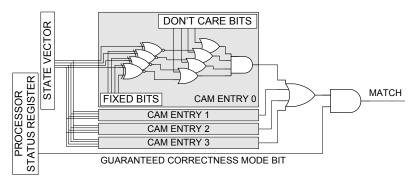

| 4.4  | State matcher structure                                                                              | 66 |

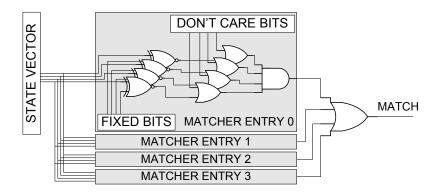

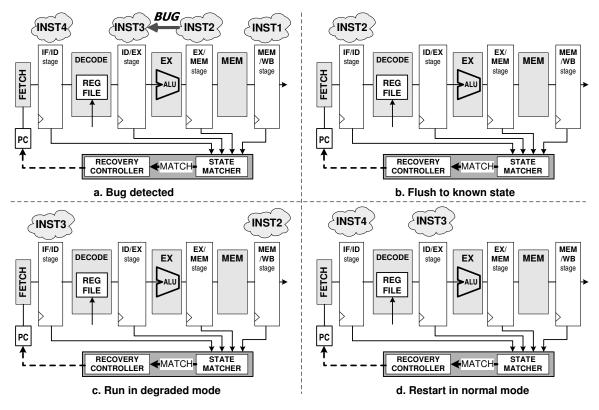

| 4.5  | Pattern compression example                                                                          | 68 |

| 4.6  | Pattern compression algorithm.                                                                       | 70 |

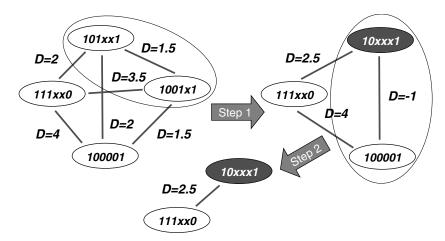

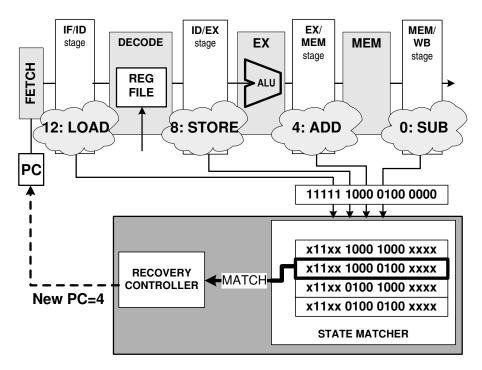

| 4.7  | Field-repairable control logic (FRCL) in operation.                                                  | 71 |

| 4.8  | FRCL for a memory access bug.                                                                        | 72 |

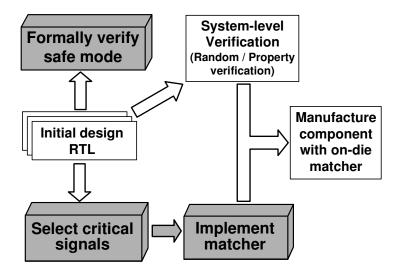

| 4.9  | Field-repairable control logic design flow.                                                          | 73 |

| 4.10 | RTL checkers to verify the correctness of the ADD instruction with Synopsys's Magellan.                                 | 76  |

|------|-------------------------------------------------------------------------------------------------------------------------|-----|

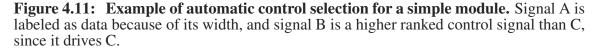

| 4.11 | Example of automatic control selection for a simple module                                                              | 77  |

| 4.12 | A state matcher for performance-critical execution.                                                                     | 78  |

| 4.13 | Trusted hardware design flow.                                                                                           | 79  |

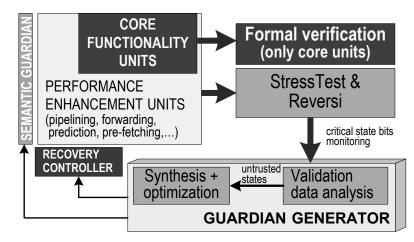

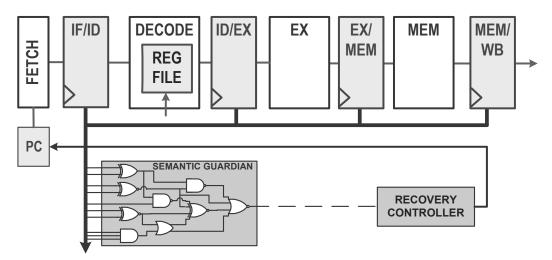

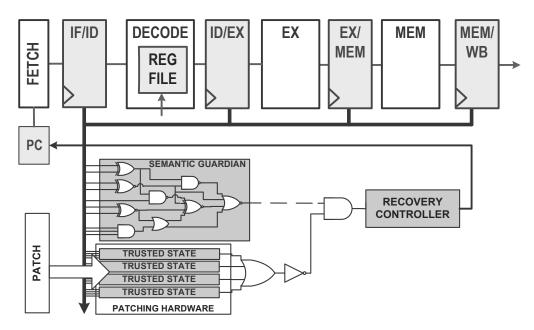

| 4.14 | Trusted execution model with a semantic guardian.                                                                       | 79  |

| 4.15 | Semantic guardian and patching hardware working in synergy                                                              | 81  |

| 4.16 | Specificity of detection for a range of bugs in the in-order pipeline                                                   | 83  |

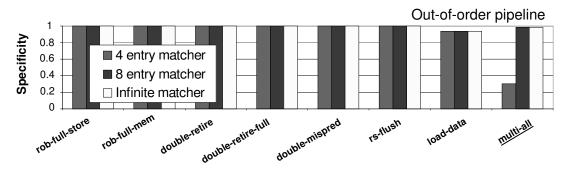

| 4.17 | Specificity of detection for a range of bugs in the out-of-order pipeline                                               | 85  |

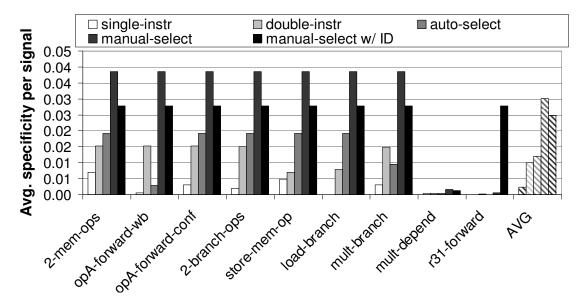

| 4.18 | Average specificity per signal for a range of critical signal sets in the FRCL implementation of the in-order pipeline. | 88  |

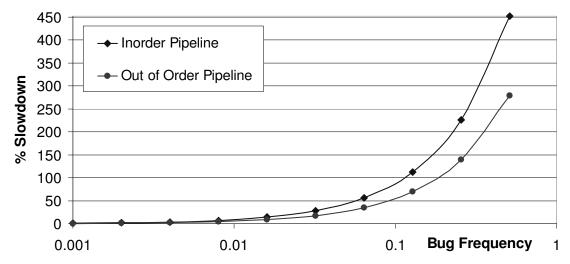

| 4.19 | Impact of recovery on processor performance                                                                             | 90  |

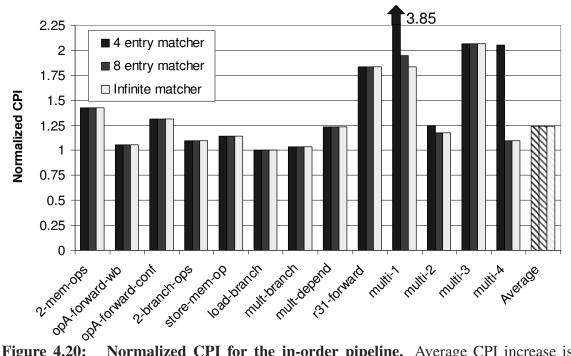

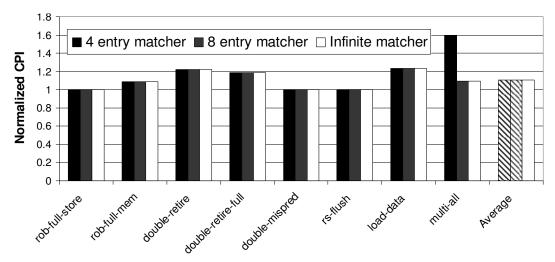

| 4.20 | Normalized CPI for the in-order pipeline.                                                                               | 90  |

| 4.21 | Normalized CPI for the out-of-order pipeline                                                                            | 91  |

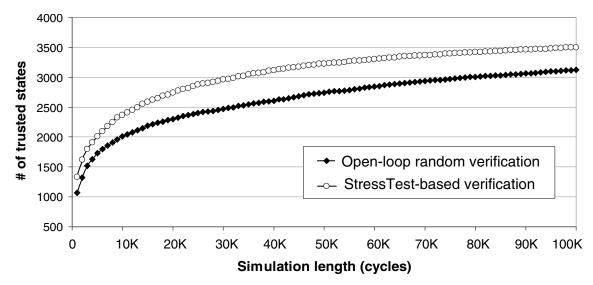

| 4.22 | Trusted states vs. simulation effort                                                                                    | 91  |

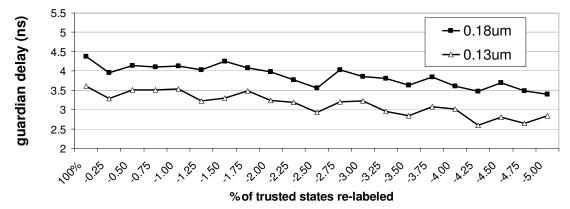

| 4.23 | Impact of trusted state re-labeling on the guardian circuit delay                                                       | 93  |

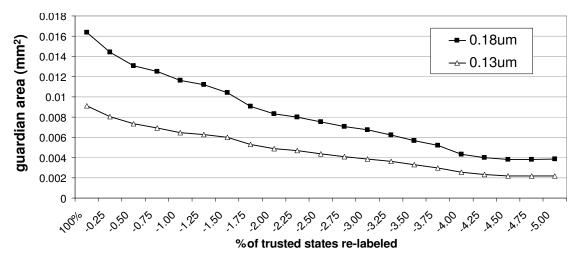

| 4.24 | Impact of trusted state re-labeling on the guardian circuit delay                                                       | 94  |

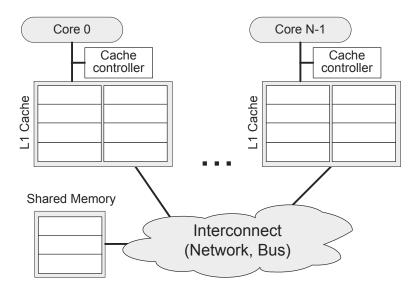

| 5.1  | Structure of a multi-core/multi-processor system.                                                                       | 97  |

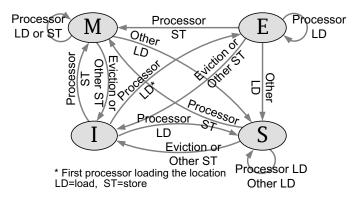

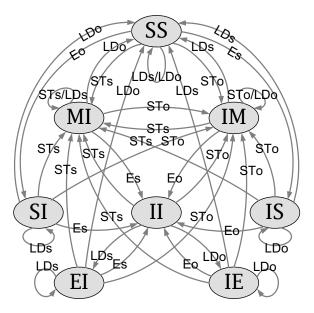

| 5.2  | MESI cache coherence protocol.                                                                                          | 98  |

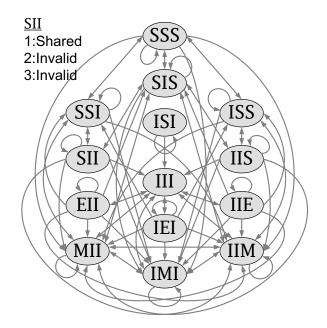

| 5.3  | Finite state machine for the full system cache coherence protocol for a three processor MESI-based system.              | 99  |

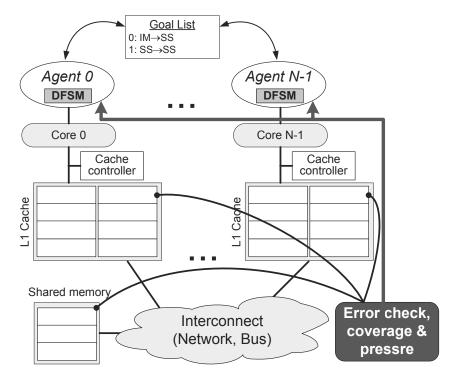

| 5.4  | Structure of MCjammer.                                                                                                  | 100 |

| 5.5  | Dichotomic Finite State Machine for MESI protocol.                                                                      | 102 |

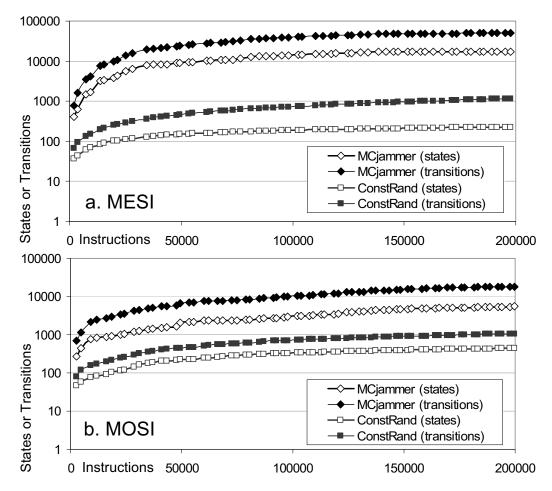

| 5.6  | Comparison of state and transition coverage vs. effort for MCjammer and constrained-random simulation.   | 107 |

|------|----------------------------------------------------------------------------------------------------------|-----|

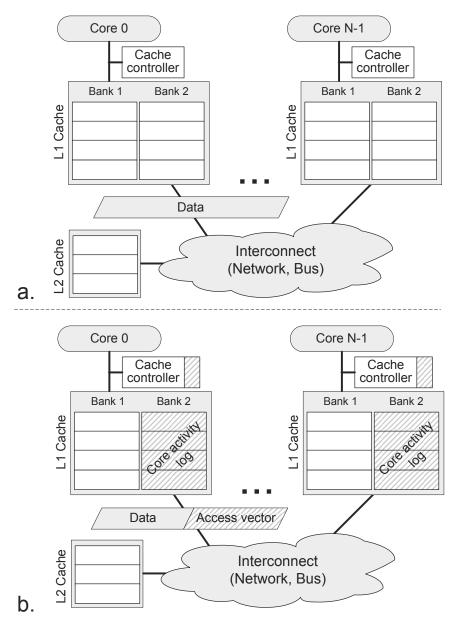

| 6.1  | Typical multi-core processor architecture and system reconfiguration for Dacota post-silicon validation. | 111 |

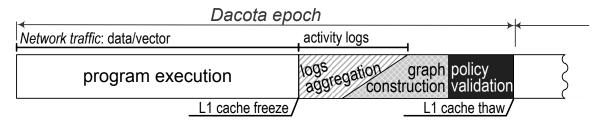

| 6.2  | Dacota execution flow.                                                                                   | 112 |

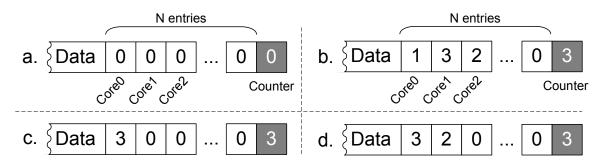

| 6.3  | Dacota access vector.                                                                                    | 114 |

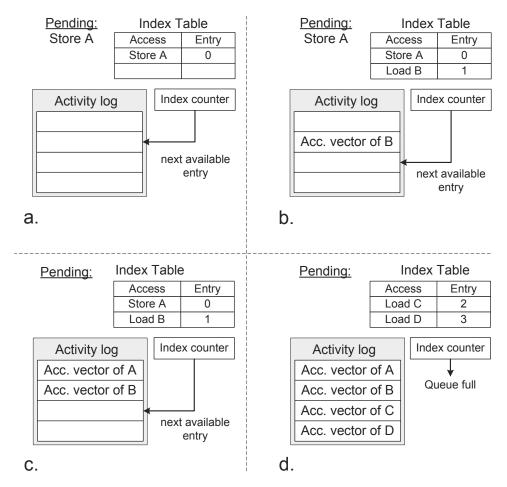

| 6.4  | Dacota activity log operation.                                                                           | 116 |

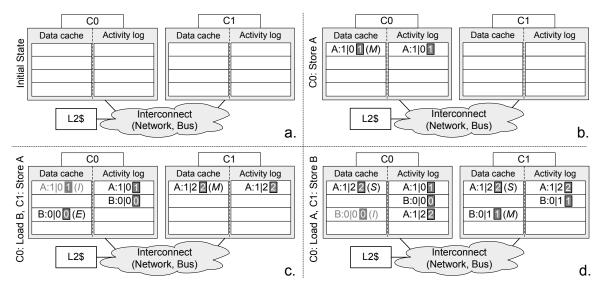

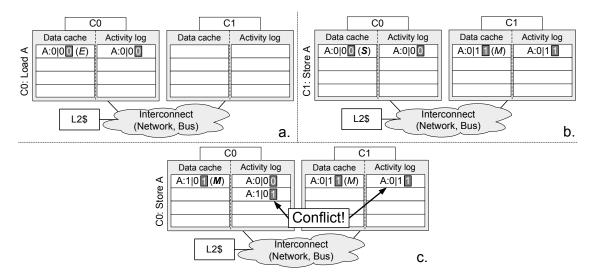

| 6.5  | Example of Dacota activity logging system.                                                               | 117 |

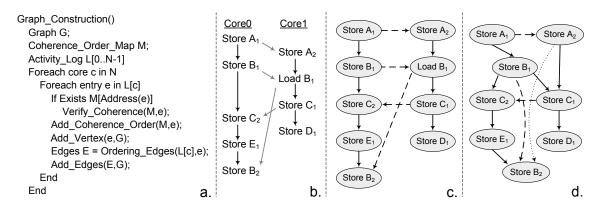

| 6.6  | Graph construction algorithm for systems implementing Sequentially Consistency and TSO                   | 120 |

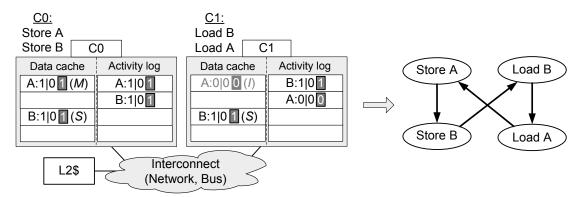

| 6.7  | Example of coherence conflict detected by Dacota.                                                        | 122 |

| 6.8  | Example of consistency violation detected by Dacota                                                      | 123 |

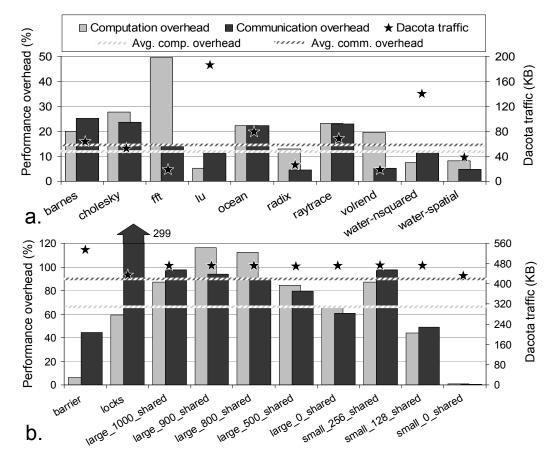

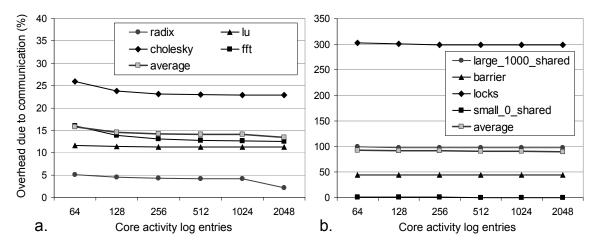

| 6.9  | Dacota performance overhead and additional traffic for activity log size of 256 entries.                 | 128 |

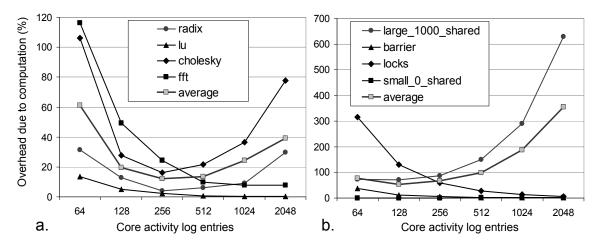

| 6.10 | Dacota computation overhead.                                                                             | 129 |

| 6.11 | Dacota communication overhead.                                                                           | 129 |

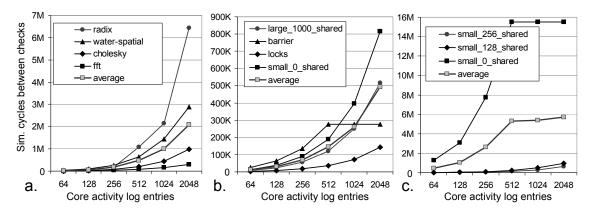

| 6.12 | Number of simulation cycles between checks.                                                              | 130 |

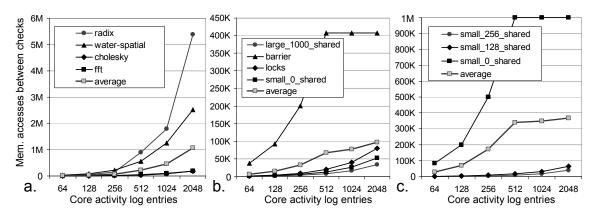

| 6.13 | Number of memory accesses between checks.                                                                | 130 |

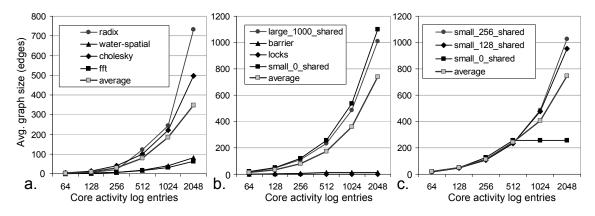

| 6.14 | Average size of consistency graph.                                                                       | 131 |

| 7.1  | Architecture of a multi-core system augmented with Caspar hardware                                       | 135 |

| 7.2  | Timeline of Caspar operation                                                                             | 136 |

| 7.3  | Synchronization for checkpointing in Caspar.                                                             | 137 |

| 7.4  | Structure of Caspar hardware event detector.                                                             | 138 |

| 7.5  | Overhead of Caspar checkpointing                                                                         | 141 |

| 7.6 | Execution time breakdown.     | 143 |

|-----|-------------------------------|-----|

| 7.7 | Performance vs. bypass length | 144 |

# LIST OF TABLES

# **Table**

| 3.1 | Reversi blocks for arithmetic and logic instructions                                                                                                              | 46  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.2 | Example instruction-set architecture                                                                                                                              | 52  |

| 3.3 | Bugs introduced in Alpha design                                                                                                                                   | 57  |

| 4.1 | Control state bits monitored in the in-order processor pipeline                                                                                                   | 83  |

| 4.2 | Control state bits monitored in the two-way super-scalar out-of-order processor pipeline.                                                                         | 84  |

| 4.3 | Bugs introduced in in-order and out-of-order pipelines                                                                                                            | 86  |

| 4.4 | Area overheads and propagation delays for a range of FRCL implemen-<br>tations on the in-order and out-of-order pipeline when synthesized on<br>180nm technology. | 89  |

| 4.5 | Area and delay of the semantic guardian generated with different design optimizations                                                                             | 93  |

| 5.1 | Bug coverage for MCjammer and ConstRand                                                                                                                           | 107 |

| 6.1 | Design error coverage by Dacota                                                                                                                                   | 127 |

| 7.1 | Design errors for Caspar resiliency analysis study                                                                                                                | 142 |

## **CHAPTER I**

# Introduction

Over the past four decades microprocessors have permeated our world, ushering in the digital age and enabling numerous technologies, without which today's life style would be all but impossible. Processors are microscopic circuits printed onto silicon dies and consisting of hundreds of millions of transistors and wires interconnecting them. What distinguishes microprocessors from other silicon circuits is their ability to execute arbitrary programs written in software. In other words, processors make digital devices programmable and flexible, so one device can efficiently perform various operations, depending on the program. In our every day activities we encounter and use these tiny devices hundreds of times, often without even realizing it. Processors allowed us to untether our phones from the wired network and enabled mobile communications, while their counterparts deployed by the phone companies made communications richer and much more reliable. Processors monitor the health of hospital patients, control airplanes, tally election votes and predict weather. And, of course, they power millions of personal computers of all shapes and sizes, as well as the infrastructure of the Internet, a vital and inseparable part of the modern life. The computational power of these devices grows every year at an astonishing pace: not long ago processors were only capable of executing just a few thousands operations per second, while today they can perform billions of complex computations per second. Moreover, in the last two years many chip companies have introduced *multi-core* processors, which can execute several programs concurrently, thereby multiplying the overall performance of computer-based systems.

However, to be so powerful, processors have become extremely complex systems, making the design and manufacturing of these devices a major challenge for the semiconductor industry. Companies such as Intel, IBM and AMD are forced to dedicate hundreds of engineers for years at a time to continue to advance microprocessor technology and deliver better performance to end-users. Moreover, as these designs grow in complexity, it becomes increasingly harder to *verify* them and ensure that they operate properly. Design houses report that today verification efforts significantly overweigh design activities, and that they often staff their teams with two verification engineers for each design engineer. We can only expect the situation to exacerbate with future performance demands, to the point that high-quality verification of processors will no longer be possible with traditional means. Unless the demands of verification of the modern processor are answered, chips released to the public and used all around us will become more and more unreliable.

The impact of bugs in production microprocessors can range widely from innocuous to devastating, for several reasons. For instance, it is possible for a computer system to become compromised, in terms of safety and security, because of a hardware bug. As a result, a system with a buggy processor becomes vulnerable to security attacks. Attacks of this type could be perpetrated even on systems running completely correct software, since they rely exclusively on an underlying hardware flaw. Moreover, bugs can have a disastrous financial impact on the company that designed the processor and may trigger a costly recall of faulty hardware, as was the case in a past Intel processor, or a significant delay in product release, similar to what happened with AMD's latest chip. The impact in both cases is estimated in billions of dollars, due to the large volume of defective components that a functional bug always entail. To prevent devastating errors from seeping into the released chips, a variety of techniques have been devised to detect them during system's design and manufacturing. Conceptually, these verification approaches can be divided into three families, based on where they intervene in a processor life-cycle: *pre-silicon*, *post-silicon* and *runtime verification solutions*.

*Pre-silicon techniques* are heavily deployed in the early stages of a processor's design, before any silicon prototype of the device is available, and can be classified as simulation-based or formal solutions. Simulation-based methods are the most common approaches to locate design errors in microprocessors. Random instruction sequences are generated and fed into a detailed software model of a chip, results are computed by simulating this model and then checked for correctness. This approach is used extensively in the industry, yet it suffers from a number of drawbacks. First, the simulation speed of the detailed software model is orders of magnitude slower than the actual processor's performance. Therefore, only relatively short test sequences can be checked in this phase; for instance, it is almost impossible to simulate an operating system boot sequence or the complete execution of an application. More importantly, simulation-based verification is a non-exhaustive process: the number of configurations and possible behaviors of a modern microprocessor is too large to allow for the entire system to be fully exercised in a reasonable time.

The other family of pre-silicon solutions, formal verification techniques, solves the non-exhaustive nature of simulation using sophisticated mathematical derivations to reason about the design. If all possible behaviors of the processor could be described with

mathematical formulas, then it would be possible to prove the correctness of the device's operation as a theorem. In the best scenarios, it is possible to guarantee that a design will not exhibit a certain erroneous behavior, or that it will never produce a result that differs from a known-correct reference model. The primary drawback of formal techniques, however, is that they are far from capable of dealing with the complexity of modern designs, and thus their use is limited to only a few, small components within the processor.

After a microprocessor is sufficiently verified at the pre-silicon stage, a silicon prototype is manufactured and subjected to *post-silicon validation*, where tests can, for the first time, be executed on the actual hardware. The key advantage of post-silicon validation is that its raw performance enables significantly faster verification than pre-silicon softwarebased simulation, thus it could deliver much better correctness guarantees. Unfortunately, post-silicon validation is plagued by the problem of limited observability, because at this stage it is impossible to monitor the internal components of the hardware prototype. Therefore, errors cannot be detected until they generate an invalid result, or cause the system to hang. The limited observability leads to extremely involved debugging procedures, with the result that today post-silicon validation and debugging has become the single largest cost factor for processor companies such as Intel.

Due to the limitations of pre- and post-silicon verification, and shrinking timelines for product delivery, processor manufacturers have started to accept the fact that bugs do slip into production hardware and thus they are beginning to explore *runtime verification solutions* that can repair a device directly at the customer's site. "Patching" microprocessor bugs, however, is a non-trivial task, since the functionality of the chip is already embodied in microscopic transistors on the silicon die, and thus it cannot be easily modified at this point. To enable in-the-field patching, designers create special processor components dedicated to detecting erroneous behaviors and recovering from them. Runtime verification is currently in its early stage: a few techniques have been recently proposed by academic research, while problem-specific solutions are starting to appear in commercial products.

**Contributions of this thesis**. This work presents a family of novel verification techniques targeting specifically modern complex microprocessors. They can address all phases of processor verification, pre- and post-silicon, and can handle a wide variety of hierarchical levels, from individual sub-modules to large multi-core chips. They also share several common traits, including scalability to high complexity designs, and the usage of self-tuning techniques, which lead to minimize the engineering effort required for verification. Moreover, this work dramatically improves the performance of post-silicon verification solutions, unlocking the full performance potential of this approach. Our post-silicon

techniques are also tailored to provide very high verification quality, while minimally affecting the processor's characteristics of performance and area. Finally, this work presents a methodology that allows to patch escaped bugs in manufactured components that are already deployed in the field at an extremely low cost, and can guarantee the correctness of execution even on buggy designs. Therefore, the framework introduced by this thesis has the potential to solve the daunting challenge of verifying a modern processor and to enable vendors to shorten their design timelines, while delivering more reliable and correct designs to the customers.

### **1.1** Microprocessor design and verification: a short tutorial

A traditional microprocessor's design and manufacturing flow (Figure 1.1) consists of a series of steps that considers a high-level description of processor operation (spec*ification*), refines and transforms it, and, finally, implements the specified functionalities on a piece of silicon die. After each step, the design is progressively verified, to ensure that after all transformation and concretization steps the behavior of the device still adheres to the original specification. The process starts with a high-level specification of the microprocessor's required characteristics and functionalities, often described in natural language, and/or diagrams describing its basic structure and how the device should interface to other digital systems. This specification is then converted to an *architectural* model of the device, often written in a high-level programming language (such as C). This model represents the first formalized reference of the final system's behavior. Implementation in a hardware description language (HDL) can then start. The HDL description of the design describes the operation of individual sub-modules of the processor, as well as their interactions, and is also known as the register-transfer level (RTL) model of the chip. This RTL model is then verified to establish its equivalence to the architectural model through simulation-based and formal techniques. The outcome of simulation-based tests is compared to those of the known-correct (or "golden") architectural model and discrepancies, indicators of errors, are identified and fixed. In addition to simulation-based techniques, in pre-silicon phase of verification, engineers often employ formal methods, which can check correctness of a design using mathematical proofs and can thus guarantee the absence of certain types of errors. Unfortunately, formal methods cannot handle complex RTL models due to their limited scalability, thus their usage in pre-silicon verification is limited to a few, small critical blocks.

Once the RTL model is sufficiently validated, designers use synthesis software that maps HDL into individual logic gates, registers and wires, generating a *netlist* of the cir-

**Figure 1.1:** Modern microprocessor design and verification flow. In the pre-silicon phase an architectural, written based on the original design specification, is converted into an RTL implementation in a hardware description language (HDL). The RTL model then can be synthesized, producing design netlist. Placing and routing software calculates how individual gates and connections of the netlist could be placed on a silicon die and from this description a prototype of the processor is manufactured. Once a hardware prototype becomes available it is subjected to post-silicon testing. When hardware becomes sufficiently stable, the chip is released to the market.

cuit. Since conversion from an RTL model to a netlist may incur errors, specialized verification solutions intervene again to check that this new transformation is still equivalent to the previous model. Routing and placing software applications then calculate how individual logic elements in the netlist can be placed on the silicon die to produce a design that fulfills the required characteristics of power, are, delay, *etc.* After placement, the final description of the design is *taped-out*, *i.e.*, sent to a fabrication facility to be manufactured. When the first hardware prototypes become available they can be inserted into a computer system for *post-silicon* validation (as opposed to the pre-silicon verification that occurs before a prototype is available). One of the distinguishing features of post-silicon verification is its high speed; it is the same speed as the final product, which is orders of magnitude higher than simulation speeds in the pre-silicon domain. Typically, at this stage engineers try to use the hardware in real life-like settings, such as booting operating systems, executing legacy programs, *etc.* The prototype is also subjected to additional random tests, in an attempt to create a diverse pool of scenarios where differences between the hardware and the architectural model can be identified to flag any remaining errors. When a bug is found at this stage, the RTL model is modified to correct the issue and the chip often must be manufactured again (this process is called *re-spin*).

A processor design usually goes through re-spin several times, as bugs are progressively found in manufactured prototypes. Ultimately, the design is stabilized and it can go into production. Unfortunately, due to the complexity of any modern processor, it is impossible to exhaustively verify its behavior neither at the pre-silicon nor at the post-silicon level, thus subtle bugs often slip through all validation stages. Until recently, if bugs were found in the end-user's hardware, manufacturers had no other choice but to recall the device. Today vendors are starting to develop measures to avoid such costly recalls and allow chips to be patched in the field. Researchers in academia have also proposed solutions to ensure correctness of processor operation with special on-die checkers. Patching- and checker-based techniques are cumulatively classified as *runtime verification* approaches.

#### **1.2** Overview of this Thesis

The goal of this thesis is to provide a scalable solution to the challenges of modern processor verification. We address the verification problem comprehensively throughout chip's life and, specifically, we leverage division the various phases of a processor's life-cycle (Figure 1.2) to attack bugs at all levels: *i*) in pre-silicon, where designs exist as hardware descriptions and are verified primarily with simulation-based techniques, *ii*) in post-silicon, where hardware prototypes are available for testing; and *iii*) at runtime in components deployed in customer's systems.

In our pre-silicon solutions, we use the architectural description of the design as the golden model to verify the implementation of individual blocks, ranging in size from small components (*e.g.*, ALU, register file, a single pipeline stage) to entire processor cores. *StressTest* [76, 77, 79] is the best suited technique for this task, for it delivers high-coverage verification with minimal human involvement. This solution can be applied to various processor modules, including blocks with multiple parallel interfaces (*e.g.*, arbitres, network switches), which are becoming an integral part of modern multi-core chips. When individual modules are integrated into an RTL description of the full multi-core system, our *MCjammer* [73] solution can be invoked to validate communication between the cores and on-chip interconnect. Unfortunately, due to the large number of design behaviors, simulation-based verification cannot provide complete coverage, therefore, in spite of the best efforts of pre-silicon tools, some design behaviors would be left unchecked. Moreover, in real-life industrial settings, the verification timeline is often shrunk due to

**Figure 1.2:** Verification throughout a processor's life-cycle. A processor's life-cycle can be divided into three phases: *pre-silicon verification, post-silicon validation* and *run-time verification* (hardware patching). The picture shows the phases of a processor's life-cycle in the inner circle, and our proposed verification solutions corresponding to each phase in the outer circle. Solutions presented in this thesis, enable efficient pre-silicon verification at different levels of the design's hierarchy: from individual sub-blocks and processor cores (using *StressTest*) to a full multi-core system (*MCjammer*). After the design is manufactured, cores are thoroughly validated with *Reversi* and, once the basic level of functionality of the cores is achieved, their communication is checked by *Dacota*. When sufficient level of coverage is reached the device can enter the production stage. If errors have escaped into production silicon, patching techniques (*FRCL, Semantic Guardians and Caspar*) allow for them to be corrected in the end user's system.

high time-to-market pressure. In these situations, processor vendors employing our approach may choose to augment the chip with additional small hardware components aimed for high-speed post-silicon validation, as well as hardware for patching escaped errors in manufactured devices.

After a design is sufficiently verified during the pre-silicon phase, a processor prototype is manufactured and subjected to thorough post-silicon validation. Recall that postsilicon validation can achieve orders of magnitude higher throughput and, therefore, can reach much higher coverage than simulation-based pre-silicon approaches. On the other hand, the drawback of post-silicon validation lies in its inability to monitor individual signals buried deep inside of the chip. The *Reversi* [74] and *Dacota* [26] solutions that we have developed to this end require access only to visible architectural state to detect and diagnose problems in individual cores and in the memory system of multi-core processors, respectively. More importantly, these solutions carry over the verification leveraging only minimal user guidance and exploit the inherent speed of the hardware prototype. Once an acceptable level of system coverage is reached, the device moves to production, where post-silicon validation features are disabled, while patching hardware is turned on. Patching, or runtime verification, allows vendors to remotely change the functionality of the processor in the third phase of its life-cycle, *i.e.*, when devices are deployed in endcustomer's system. To achieve this, our techniques (FRCL [78, 80], Semantic Guardians [72] and Caspar [75]) augment the design with small bug detection components. When deployed in the field, this programmable detectors are capable of recognizing functional errors in processor operation and reconfiguring the chip to avoid buggy states, guaranteeing correctness of execution. Altogether, the integrated system of solutions described in this work creates a novel verification framework, which comprehensively addresses the challenge of validating a modern multi-core microprocessor.

#### **1.3** Guiding Principles in Developing the Verification Solutions

This section outlines the common guiding principles that we adopted throughout our research work in investigating novel solutions.

#### **1.3.1** Adherence to Traditional Flow

All techniques in this thesis were specifically developed to fit well in a traditional industrial verification flow. In particular, as mentioned above, formal approaches are not used in industry is very limited due to their limited scalability and requirement of a formal design specification. Therefore, the pre-silicon tools described here rely in their core on simulation, which can easily scale to handle the design sizes of modern processors and is well understood by processor manufacturers. Moreover, all of our solutions have modular structure and can be easily integrated into the simulation environment of developer's choice. Likewise, post-silicon solutions presented in this thesis fit well into traditional post-tape-out validation, and improve it by unlocking the full potential of hardware execution's performance. Finally, our runtime techniques rely on novel methods for hardware patching and can effectively utilize traditional patch distribution schemes, such as BIOS updates.

#### 1.3.2 Minimization of Human Involvement

Another common aspect of all of these solutions, is that they try to minimize the effort demanded from verification engineers, a major bottleneck of traditional verification flows. Obtaining guidance from a human is very time consuming, and often automatic reasoning and learning techniques can achieve comparable results much faster and at a fraction of the cost.

Our framework uses several solutions that stem from machine learning: In StressTest we employ a technique, based on Markov models, that is able to evaluate the quality of test stimuli based on the stress observed in key design points and dynamically generate higher-quality sequences with reinforcement learning. Our approach to verification of multi-core processors (MCjammer) uses distributed intelligent agents that cooperate with each other trying to achieve their own verification goals and help other agents do the same. In MCjammer we also use closed feedback loops at fine granularity to direct tests towards interesting corner cases of processor behavior while trying to expose bugs.

Similarly to pre-silicon verification solutions, our approaches for post-silicon validation try to minimize the time a designer spends creating high-quality test stimuli and acquiring design's state to check for correctness. For example, Reversi, a post-silicon validation solution for individual processor cores, automatically produces test sequences with known correct final state. As a result, the validation process is dramatically simplified and streamlined, becoming virtually a push-button operation. Likewise, Dacota, a solution for post-silicon validation of cache-coherence and memory consistency uses inherent resources of the design under test to log and analyze memory accesses. Only when an error is detected, the engineer is alerted and must become engaged in the debugging activity.

#### **1.3.3** Minimization of Area and Performance Overhead

In the post- and runtime verification approaches presented in this thesis we strived to minimize the hardware overhead to make these solution practical and attractive for processor designer companies. Since verification features do not add to the device's performance, manufacturers are less likely to deploy them in production hardware, preferring features increasing the throughput of the chip. Thus, to be adopted, the impact of validation and patching features on the processor area and performance must be minimal. To this end, the post-silicon techniques described in this work step aside from traditional state acquisition techniques, and attempt to either discover errors through an architectural state mismatch (as it is the case for Reversi) or use portions of on-chip caches to record information for error detection and analysis (as was done with Dacota). Likewise, runtime approaches

(Field-Repairable Control Logic, Semantic Guardians, and Caspar) incur minimal area overhead, trading off for it either error coverage or device's performance. The first one of these approaches, Field-Repairable Control Logic (FRCL), augments the device with a small programmable matching hardware that is pre-loaded at start-up with descriptions of the known bugs, making it possible to detect and bypass errors in the control logic of processor pipelines. An extension of this work introduces semantic guardians, combinational matcher circuits, synthesized automatically based on the results of design verification. In this case, the matching hardware encodes all of the verified configurations of the design and switches the processor to a safe mode when an un-verified, and therefore potentially buggy, configuration is encountered at runtime.

In the next six chapters of the thesis we uncover the proposed approaches following the flow of Figure 1.2. We start with verification of individual processor cores at pre-silicon level with StressTest in Chapter II, followed by post-silicon validation of such designs with Reversi. Chapter IV presents the field-repairable control logic solution for patching processors, as well as the extension of this solution to semantic guardians. We then review in detail the multi-core processor verification flow with MCjammer at pre-silicon and with Dacota at post-silicon level in Chapters V and VI respectively. An approach to memory subsystem patching in multi-core processors, called Caspar, is then detailed in Chapter VII. Finally, in Chapter VIII we briefly summarize the contributions of this thesis, draw conclusions, and outline future research directions.

### **CHAPTER II**

# **Pre-silicon Verification of a Single Core**

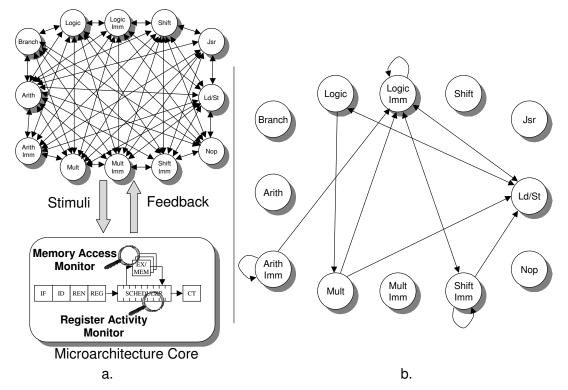

In this chapter we begin our journey through the pre-silicon verification solutions that are used in the early stages of the processor life-cycle to verify the adherence of the design model to the specification. In particular we will focus on the validation of single core processors, a type of design that has been developed for many decades, yet is still extremely difficult to verify due to the complexity of the computational core. To tackle the challenge of pre-silicon verification of single core microprocessors we introduce a novel test generator tool called StressTest. This solution uses a form of machine learning technique to dynamically obtain feedback from the design under test and progressively create better test sequences, which stress various design behaviors and expose complex bugs within a processor core. StressTest requires minimum interaction and control from the user, and it is easily fine-tuned and highly portable, since it considers the design under test at a very high abstraction level. Our approach only requires the engineering team to provide a simple *template* describing the interface protocol of the design. To assist the engineer in describing concise and meaningful programs, our template language includes a number of helpful features, including parameterized dependency variables. Using this template, StressTest generates a very broad spectrum of testing programs to verify the design. The underlying generation engine of StressTest uses a dynamically-adjusted *Markov* model representing the set of valid inputs for the design. This engine implicitly limits the generator to only produce valid test sequences, excluding the risk of false-negatives. Additionally, this approach combines advantages of both probabilistic and self-guiding stimulus generation techniques, which allows us to improve design coverage while lowering the overall verification effort. Finally, the template-based approach allows for a very compact representation, even for designs with complex input constraints, and increases the portability and flexibility of StressTest.

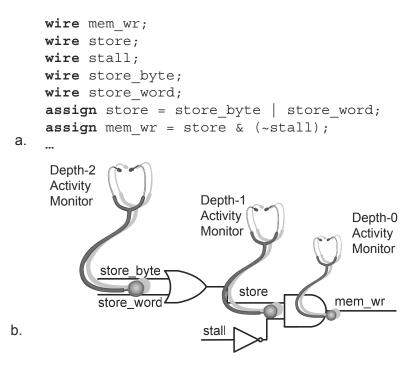

For guidance in the test generation, StressTest uses a novel technique based on *activity monitors*, which are simulation monitors that probe the internal state of the design at specific points. A first selection of probing nodes is made by the user, based on the key aspects or components which he wants to test. These nodes typically include key internal signals that reflect major changes in the design's state or outputs (for instance, a write-enable signal to the register file). StressTest complements this user selection with additional probing nodes highly related to the first ones so to achieve better performance and coverage. During simulation, StressTest observes the activity of all the probing nodes. Closed-loop feedback techniques are used to direct the test generator engine towards stimuli generating higher switching activity at the probing points. Unlike previous approaches, which usually adjust the stimuli generator based on results of a full, completed test run, StressTest is capable of adjusting the Markov model dynamically during the test. The use of activity monitors enables StressTest to gradually increase the stress on the automatically selected probing nodes and, subsequently, on the user-specified nodes themselves. We find that our approach achieves better coverage for complex bugs in fewer cycles than constrained open-loop random generation techniques. Moreover, the addition of automatically selected probing points is key in boosting StressTest's performance and in generating effective tests in an assertion-based verification methodology.

### 2.1 StressTest Structure

StressTest provides a convenient platform for specifying the set of valid inputs for a design under test by mean of templates. A number of activity monitors observe a small set of relevant circuit's internal signals and drive the generator toward scenarios that excite those signals. StressTest's self-guiding generation engine consists of two major components: a Markov model and a set of activity monitors (see Figure 2.1). The Markov model encapsulates the set of legal inputs of the design as well as probabilities of generating different sequences of inputs. The activity monitors bind to several key nodes, or signals, of the design and evaluate the "stress" on the design based on the switching activity of these signals. The information collected by the activity monitors is used as feedback to the Markov model, which adjusts the probability to generate stimuli which maximize the stress on these nodes. The signals selected for the activity monitors drive the focus of the test generation and, consequently, which components of the design will be most thoroughly tested. Therefore, in order to locate bugs within a critical component, activity monitors should be selected from key signals which activate the component, and within the component itself.

As with other RTGs, the stimuli generated by StressTest are supplied to both the design under test (DUT) and a golden model, which is a functional description of the design usually provided in a high-level language. The output and the architectural state of the two

**Figure 2.1: StressTest structure.** Templates are used to create a Markov model which generates valid stimuli: templates' transactions are mapped to the vertices of the model. Stimuli are fed in parallel to the design under test (DUT) and the golden model. Activity monitors observe the behavior of the DUT during the simulation and adjust the Markov model improving the quality of the stimuli. The outputs of DUT and golden model are compared to expose bugs.

descriptions are monitored and discrepancies are flagged as potential design errors. For instance, in our tests on microprocessor pipelines, the golden model was a single-cycle functional model, and StressTest was connected to the external instruction bus interface of DUT and golden model. Hence, neither model could detect that the instructions were provided by a test generator instead of main memory. This greatly simplifies the test setup, allowing StressTest to reuse the framework of directed tests. When the correctness monitor detects a mismatch in the architectural states of the two descriptions, it halts simulation and outputs a trace leading to the problem.

### 2.2 Stimulus Generator

The stimulus generator engine of StressTest comprises an adaptive Markov model whose vertices describe monolithic blocks of stimuli, or transactions. The transactions cor-

responding to each vertex are generated based on the template files provided by the user. Template files are loaded by StressTest at the beginning of each simulation run and are used to generate the initial Markov Model. The probabilities associated with the model's edges are then adjusted over time based on the direction from the activity monitors. Several reasons led us to choose Markov models as the underlying engine for stimulus generation. First of all, Markov models are simple to implement, and straightforward to train; second, they provide a convenient abstraction for modeling instruction generation: Instructions (or classes of instructions) constitute the vertices of the Markov model, while programs correspond to paths in the model's graph. In contrast, structures such as Bayesian networks must be "trained" on an actual circuit to determine the cause/effect relation between inputs and observed outcomes; therefore, unlike Markov models, they depend on the circuit's implementation. On the other hand, a noticeable drawback of Markov models is their lack of "memory". Each generated stimulus is independent from past stimuli and relates only to the last vertex visited in the model. Therefore, we introduced the concept of dependency variables to provide deterministic dependencies between past stimuli and present input, as discussed later in this section.

#### 2.2.1 Markov Model

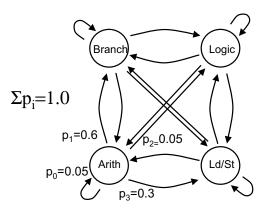

StressTest uses a Markov Model as the main engine for generation of stimuli to the design. In general, a Markov model is a directed graph, where each edge has an associated probability of transitioning from the its source vertex to its sink vertex. In StressTest, the nodes of the Markov model corresponds to valid stimuli or groups of stimuli for the design. During the simulation, a stimulus associated with the current node is generated and supplied to both DUT and golden model. Within the framework of microprocessor verification, the stimuli corresponding to a single vertex can be individual instruction, or groups of instructions forming a program fragment. A single vertex can represent a range of similar individual instructions by parameterizing the various instruction fields. An example of a simple Markov model for an abstract instruction set architecture (ISA) is shown in Figure 2.2. The vertices in this case represent different types of assembly instructions, such as branches, arithmetic instructions, and so on. Edges are labeled with the probability of being traversed. For instance, the probability of generating a branch instruction after an arithmetic instruction is  $p_1$  which is equal to 0.6. Note that the sum of the probabilities associated with the outgoing edges from each vertex must be equal to 1.

This Markov model-based approach is not limited to microprocessors only, and can be used to represent transactions through an interface of any digital circuit. In the experiments we used mutually disjoint and cumulatively exhaustive ISA partitioning, so that we could

**Figure 2.2:** Example of Markov model. The model has 4 vertices, each capable of generating a particular instruction type. The sum of probabilities to transition from a single vertex must be 1.0. In the example, once an arithmetic instruction is generated, a branch has probability of 0.6 to occur, a load/store has probability 0.3, while other instructions are less probable.

generate every instruction type, increasing the possibility of catching a variety of design errors. In simulations aimed at exposing a specific kind of bug, the Markov model can be structured to contain only a small subset of inputs, representing distinct transactions. At the beginning of a simulation the model is a clique, with each transition being equally probable. A starting vertex is selected at random, the system produces the corresponding inputs and randomly selects a transition to the next vertex. During the simulation probabilities associated with the edges are adjusted based on the feedback from the activity monitors. StressTest allows for a sequence of instructions to be associated with a single vertex. When such a vertex is reached, StressTest generates instructions until it reaches the end of the sequence, and only then it transitions forward. This allows for generation of deterministic instruction sequences. For instance, a vertex could map to a sequence of a branch instruction followed by a *noop* to generate legal assembly code for a microarchitecture relying on the compiler to resolve control hazards. Notice that, since the entire sequence is clustered into a single vertex, all the activity observed when executing the sequence will affect the probability of reaching that sequence again.

The probability adjustment algorithm considers a weighted sum of the switching activity reported by the monitors and converts it to a value which we refer to as "score". The score is used to adjust the probability associated with the edge E traversed during the last transition. The update is computed as follows: the score is first scaled as a fraction of the maximum score that all edges could achieve; then the probability of the relevant edge  $P_E$  is adjusted; finally, the probability values on other edges starting from this vertex are adjusted, so that their sum is normalized to 1. The probability increment is then equal to:

$$P_{inc} = \frac{score_{monitor}}{score_{max} * N_{edges}}$$

where  $N_{edges}$  is the number of outgoing edges from the vertex under consideration, and  $score_{max}$  is the maximum score achievable. The adjusted probability is the saturated sum:

$$(2.2) P_{E\_new} = max\{T_{sat}, P_E + P_{inc}\}$$

where  $T_{sat}$  is the saturation threshold unique for the system. We set the saturation threshold  $T_{sat}$  to a value slightly less than 1, so that we can always attribute at least a small probability to any edge. Doing so guarantees that we never eliminate potentially useful transitions from the system. In most of our experiments we set  $T_{sat} = 0.95$ , allowing other edges to have probability in the range  $[0.05/(N_{edges}-1), 0.95]$ . If a vertex has an outgoing edge with probability  $T_{sat}$ , then all other edges are set at  $P_{min} = (1 - T_{sat})/(N_{edges} - 1)$ .

The last phase of the probability adjustment requires that the sum of the outgoing edges' probabilities is re-normalized. We do so by decrementing all eligible edges (the ones with  $P_{edge} > P_{min}$ ) by an amount proportional to  $P_{inc}$ . Specifically, we first compute the "slack" available as

(2.3)

$$slack = \sum_{i \neq E} (P_i - P_{min})$$

where the contributing edges include all but the one we just incremented (note that edges for which  $P_i = P_{min}$  contribute 0). The adjustment is then performed by decrementing each  $P_i$  proportionally to their contribution to the "slack":

(2.4)

$$P_{i\_new} = P_i - \left(\frac{P_i - P_{min}}{slack}\right) * P_{inc} \quad \forall i \neq E$$

This computation normalizes the probability while guaranteeing that each edge has probability  $P_i \ge P_{min}$  associated with it.

#### 2.2.2 Template Files

We use a special template language to describe the stimuli to generate at each vertex of the Markov model. StressTest's templates describe a short sequence of stimuli for each vertex, as shown in the example of Figure 2.3. Stimuli definitions are in binary format, and specify the values of each bit of the input signals. Values can be specified as 0, 1 or through a parametric field. Each bit field is identified by a single alphabetic character repeated for the whole width of the field. Note that the stimulus generator only describes legal inputs, requiring no information about the DUT structure, making template files highly portable among multiple designs. The user must only specify the desired partitioning of the input set and no explicit sequencing control is required. In addition, StressTest templates do not specify the biasing of input stimuli, since this is derived during the simulation. This is different from industry tools, such as Genesys-Pro [3], where sequencing control and biasing information must be provided in the template to achieve high quality test sequences. The structure of StressTest templates is particularly suitable for describing instruction set architectures (ISA) and structured interface protocols.

```

(cacheSize=5,probCache=0.9,lambda=2,

immVal

minVal=-8192, maxVal=8191);

destIndex(cacheSize=30, probCache=0.8, lambda=4,

minVal=0, maxVal=31);

randIndex(probCache=0,lambda=0,minval=0,maxVal=31);

r-funcs(probCache=0,lambda=0,minVal=0,maxVal=63);

i-funcs (probCache=1,lambda=0) =

'b001000 /ADDI/, 'b001001 /ADDIU/,

'b001010 /SLTI/, 'b001011 /SLTIU/,

'b001100 /ANDI/, 'b001101 /ORI/,

'b001110 /XORI/ };

vertex(r-type-inst)

{ input = 'b000000ssssstttttddddd00000ffffff;

field(s) = $destIndex.read();

field(t) = $randIndex.read();

field(d) = $randIndex.read();

$destIndex.write(field(d));

field(f) = $r-funcs.read(); }

vertex(i-type-inst)

field(f) = $i-funcs.read();

field(s) = $destIndex.read();

field(t) = $randIndex.read();

$destIndex.write(field(t));

field(i) = $immVal.read(); }

```

**Figure 2.3: Example of a StressTest template file.** This file defines a Markov model with two vertices: *r-type-inst* (register type instructions) and *i-type-inst* (immediate type instructions). The vertices use five dependency variables declared at the top. In particular, variable *\$dest-Index* creates a potential dependency between consecutive stimuli.

Template files can also force interactions between vertices, allowing StressTest to generate stimuli sequences with complex interdependencies. To describe these interactions, we have created a structure very flexible and easy to use, called dependency variables. Dependency variables, declared at the beginning of a template, generate values for the parametric fields, and include special support for specifying locality and dependency characteristics. These variables and their operation are detailed in Section 2.2.3. Note that edges do not appear anywhere in template files, since our Markov models always starts as a single clique. In designing the template language we strove to keep a simple and intuitive structure, since this is the only part of StressTest which requires user input. In spite of its simplistic structure, the template language retains the ability of describing a very broad range of stimuli, and different interaction constraints.

The template language allows to represent groups of stimuli through multiple vertices, each using different parameters. This enables StressTest to associate distinct probabilities to stimuli with different characteristics. For instance, arithmetic instructions could be highly dependent on previous instructions in one vertex, while nearly always independent in another, allowing the activity monitors to selectively adjust transitions to and from vertices with specific individual properties. An example of a template file is given in Figure 2.3. It defines five dependency variables, each with different sets of parameters. After the declarations, the template file contains the vertices' specifications, which correspond to nodes in the Markov model. In the example we define two vertices: *r-type-inst* and *i-type-inst*, each generating a 32-bit input stimulus. Below the bit structure definition, each of the fields is assigned a value from dependency variables. For instance, vertex *r-type-inst* binds field *f* to dependency variable *r-funcs*, while field *f* of the *i-type-inst* vertex is bound to variable *i-funcs*.

#### 2.2.3 Dependency Variables

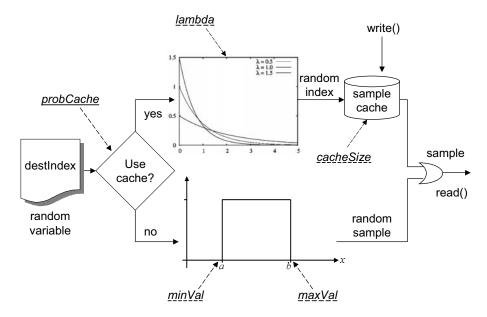

Dependency variables, such as those declared at the top of the template file in Figure 2.3, provide a concise mechanism to specify the generation of values from i) a list of constants, ii) a uniform random distribution, iii) a randomly generated locality set, or iv) some combination of the previous three constructs. The variables are used to pass information between the template's vertices and fields and create complex interactions, such as locality and dependency between generated inputs. All of the variables have global scope and can be accessed from anywhere in a template file. The functional block used to generate a value for a dependency variable is illustrated in Figure 2.4. The underlined labels in the figure represent the five declaration parameters of a variable:

**probCache** is the probability that a *read()* to a dependency variable will retrieve the value from the locality cache.

**cacheSize** is the size of the locality cache, which contains the most recently generated values that can be reused to simulate locality and dependency.

**lambda** represents the length of the locality window, and it corresponds to the rate parameter to an exponential distribution which selects the cache indexes: The larger the value of *lambda*, the greater the probability that the selection is skewed towards recent element inserted, the smaller this value, the more uniform the distribution of selection among all of the cached elements. minVal, maxVal are the bounds over which the uniform random samples are produced when the cache is not used.

Some of the parameters can be omitted when declaring the variables, in which case a default value is used. For example, *minVal* is omitted when declaring variable *i-funcs* in Figure 2.3, hence the value of that parameter defaults to 0. When the variable is *read()*, the returned value is either taken from the sample cache with probability *probCache*, or produced by the random value generator with probability *1-probCache*. Thus, by setting the parameter *probCache* to 0 we can create a perfect random generator, as it is the case for variable *randIndex* in Figure 2.3. On the other hand, we can completely disable the random generator and select values exclusively from a pre-defined list, similar to case of variable *i-funcs*.

**Figure 2.4:** Dependency variable functional block. A *write()* access to the variable inserts a value in the cache. On a *read()*, the parameter *probCache* is used to select whether the value should be generated randomly or retrieved from the cache. In the latter case, the *lambda* parameter affects the distribution of the selection from the cache. In the former, the distribution is uniform between *minVal* and *maxVal*