# Low Voltage Circuit Design Techniques for Cubic-Millimeter Computing

by

# **Scott McLean Hanson**

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 2009

## **Doctoral Committee:**

Associate Professor Dennis M. Sylvester, Chair Professor David Blaauw Professor Kensall D. Wise Assistant Professor David D. Wentzloff Kerry Bernstein, International Business Machines Corporation

To my family

## Acknowledgements

Graduate school has been fascinating, exciting, often exhausting, and ultimately an incredible learning experience. Throughout graduate school, I have been supported by a strong network both inside and outside the University of Michigan.

Inside the University, I have worked with an intelligent, creative group of professors and students. Many of these people have directly contributed to this work. The low voltage overview described in Chapter 2 is drawn from work done originally by Bo Zhai. Mingoo Seok offered valuable feedback about the work covered in Chapter 3. The Subliminal Processor, which is discussed in Chapter 4, was a joint effort by a long list of students including: Bo Zhai, Leyla Nazhandli, Brian Cline, Meghna Singhal, Javin Olson, Michael Minuth, Kevin Zhou, and Mingoo Seok as well as several faculty members: Dennis Sylvester, David Blaauw, and Todd Austin. Mingoo Seok, Yu-Shiang Lin, and I worked closely together to develop the Phoenix Processor (Chapter 5) under the guidance of David Blaauw and Dennis Sylvester. Fellow students Yoonmyung Lee, Rach Liu, Zhiyoong Foo, and Daeyeon Kim also played important roles in the design and test of the Phoenix Processor. Finally, Zhiyoong Foo helped design on-chip test infrastructure for the low voltage image sensor test-chip. I would also like to thank the Semiconductor Research Corporation for funding my fellowship and Kerry Bernstein for serving as my mentor.

Outside the University, my family, fiancée and friends have offered unwavering support. I am fortunate to have such a strong support group, and I thank them all.

# **Table of Contents**

| Dedication                                        | ii  |

|---------------------------------------------------|-----|

| Acknowledgements                                  | iii |

| List of Figures                                   | vi  |

| List of Tables                                    | xi  |

| Abstract                                          | xii |

| Chapter 1: Introduction                           | 1   |

| Chapter 2: Motivating Low Voltage Operation       | 12  |

| Chapter 3: Device Scaling in Low Voltage Circuits | 21  |

| Chapter 4: The Subliminal Processor               | 48  |

| Chapter 5: The Phoenix Processor                  | 74  |

| Chapter 6: An Ultra-Low Voltage CMOS Image Sensor | 101 |

| Chapter 7: Conclusion                             | 116 |

| References                                        | 119 |

# **List of Figures**

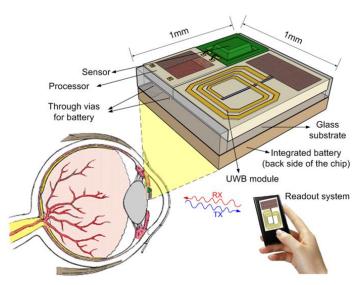

| Figure 1.1: An implantable intra-ocular pressure sensor (courtesy of Y-S. Lin)                                                                                                                                           | 3  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

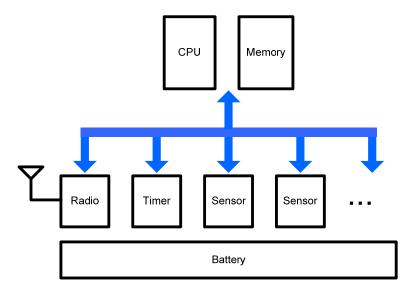

| Figure 1.2: The canonical 1mm <sup>3</sup> computer                                                                                                                                                                      | 4  |

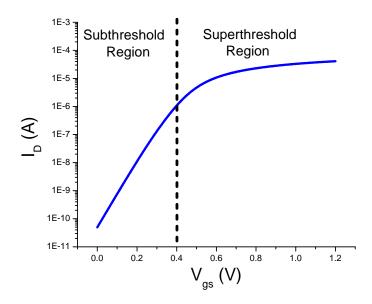

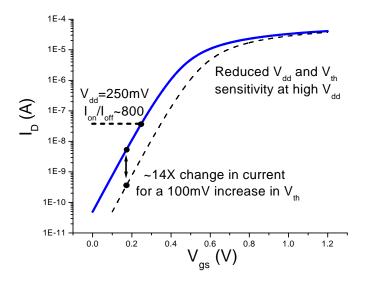

| Figure 1.3: NFET drain current as a function of gate-source voltage                                                                                                                                                      | 5  |

| Figure 2.1: Simulated NFET drain current as a function of gate voltage in a 0.13 technology                                                                                                                              | •  |

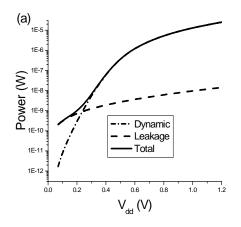

| Figure 2.2: (a) Power consumed by an inverter chain as a function of supply voltage ( $V$ (b) Energy consumed per switching operation by the same inverter chain as a function $V_{dd}$                                  | of |

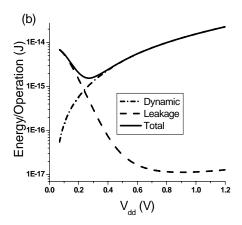

| Figure 2.3.: Delay variability $(\sigma/\mu)$ as a function of supply voltage (65 nm technology)                                                                                                                         | 18 |

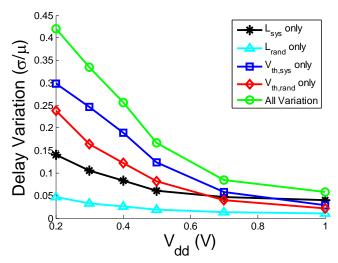

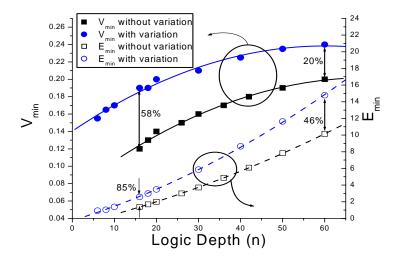

| Figure 2.4: Variation in worst-case ( $\mu$ +3 $\sigma$ ) $V_{min}$ and $E_{min}$ for an inverter chain of lengt gates. The relative increases in $V_{min}$ and $E_{min}$ are less severe at large $n$ (0.13 technology) | μm |

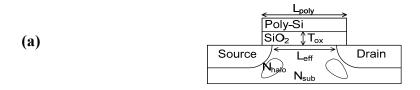

| Figure 3.1: (a) A device cross-section showing scaling parameters (b) Doping profile a 90nm NFET                                                                                                                         |    |

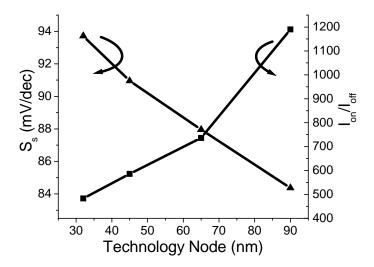

| Figure 3.2: NFET inverse sub-V <sub>th</sub> slope and on-current to off-current ratio                                                                                                                                   | 27 |

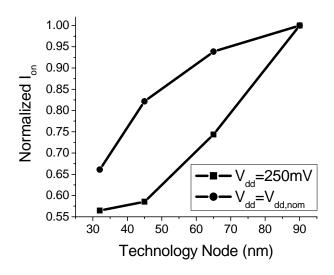

| Figure 3.3: NFET on-current                                                                                                                                                                                              | 28 |

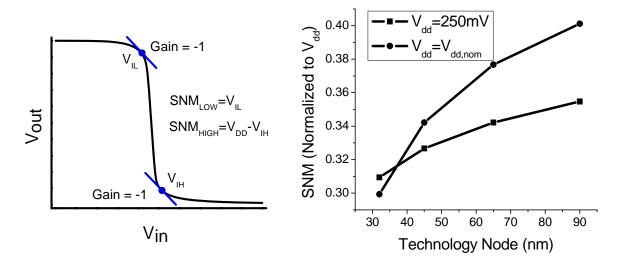

| Figure 3.4: (a) Definition of SNM (b) Simulated SNM for a scaled inverter                                                                                                                                                | 29 |

| Figure 3.5: Simulated delay for a scaled inverter                                                                                                                                                                        | 31 |

| Figure 3.6: Simulated energy/cycle and $V_{min}$ for a chain of 30 inverters with $\alpha$ =0.1                                                                                                                          | 33 |

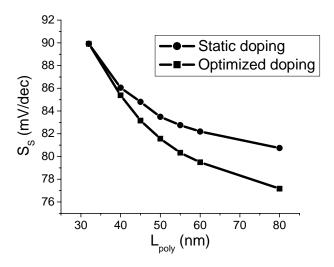

| Figure 3.7: $S_S$ as a function of gate length for a 45nm device                                                                                                                                                         | 34 |

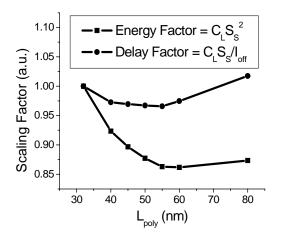

| Figure 3.8: Energy and delay factors for a 45nm device                                                                                                                                                                   | 34 |

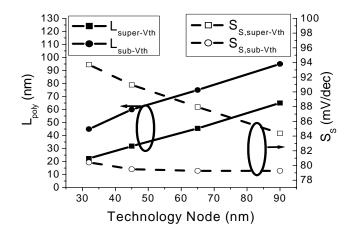

| Figure 3.9: NFET $L_{noly}$ and $S_S$ for sub-V <sub>th</sub> and super-V <sub>th</sub> scaling strategies                                                                                                               | 37 |

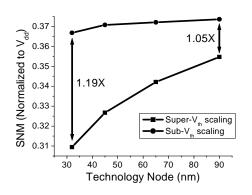

| Figure 3.10: Simulated SNM for an inverter under super-V <sub>th</sub> and sub-V <sub>th</sub> scaling39                                                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

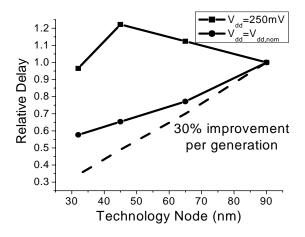

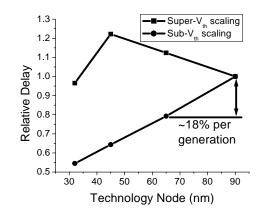

| Figure 3.11: Simulated delay for an inverter at $V_{dd}$ =250mV under super-V <sub>th</sub> and sub-V <sub>th</sub> scaling                                                                                                                                                                                         |

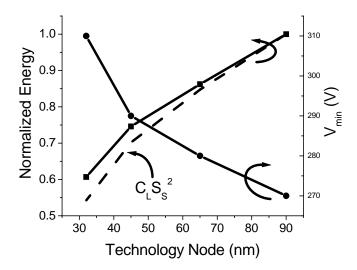

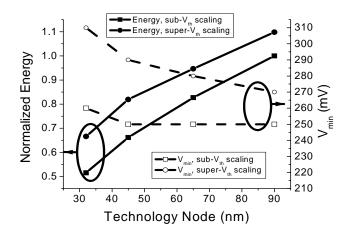

| Figure 3.12: Simulated energy and $V_{min}$ under super- $V_{th}$ scaling and sub- $V_{th}$ scaling41                                                                                                                                                                                                               |

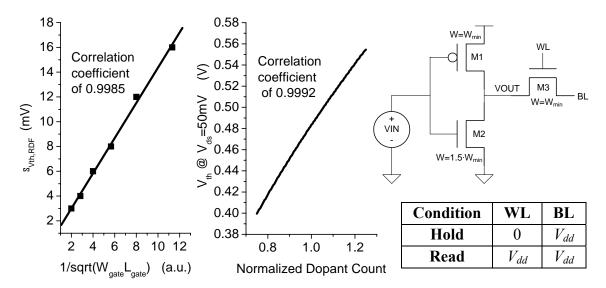

| Figure 3.13: (a) RDF $V_{th}$ variability model in a 65nm device closely matches gate area dependence in Eq. 9. (b) $V_{th}$ is approximately linear with dopant count (c) SRAM test circuit for measuring SNM and $I_{read}/I_{leak}$ . Node voltages during hold and read conditions are also shown               |

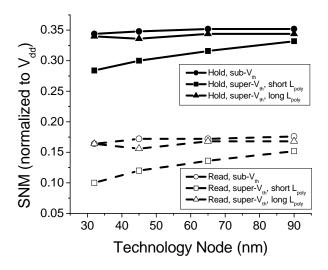

| Figure 3.14: Simulated SNM in a 6T SRAM cell at $V_{dd}$ =250mV under three different device optimization strategies: (1) sub-V <sub>th</sub> optimized device, (2) unoptimized super-V <sub>th</sub> device with minimum length, and (3) unoptimized super-V <sub>th</sub> device with the same length as case (1) |

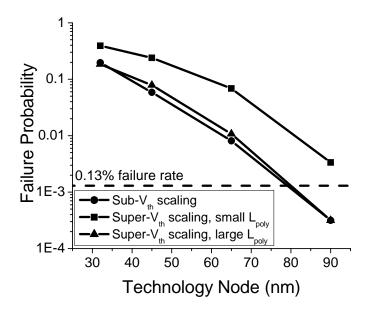

| Figure 3.15: Read failure probability for a single SRAM cell under different device optimization strategies at $V_{dd}$ =250mV. Failure is defined as the point where the read SNM drops below 6% of $V_{dd}$ (15mV                                                                                                 |

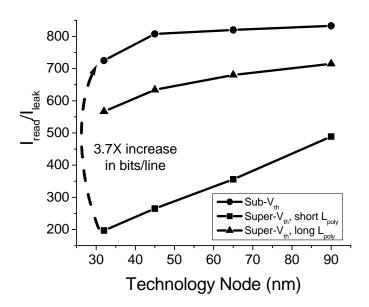

| Figure 3.16: Ratio of read-current to pass-transistor leakage in a 6T SRAM at $V_{dd}$ =250mV under super-V <sub>th</sub> scaling and sub-V <sub>th</sub> scaling. $I_{read}/I_{leak}$ is proportional to the maximum number of bits per bitline and is therefore closely tied to SRAM area46                       |

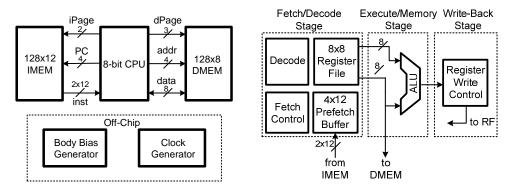

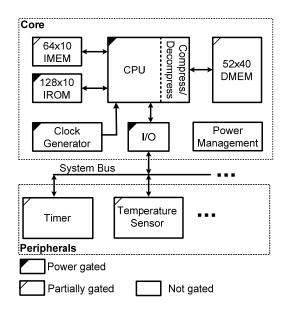

| Figure 4.1: (a) System-level diagram of the 8-bit subthreshold processor (b) CPU implementation details                                                                                                                                                                                                             |

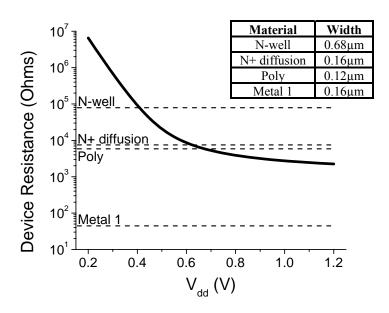

| Figure 4.2: Effective NFET resistance as a function of $V_{dd}$ . The resistances of wires of several alternative materials are included for reference (with $100\mu m$ length and widths from inset)                                                                                                               |

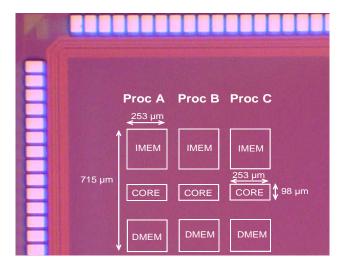

| Figure 4.3: The 8-bit subthreshold processor was fabricated in a 0.13µm technology. Three CPU variants are shown                                                                                                                                                                                                    |

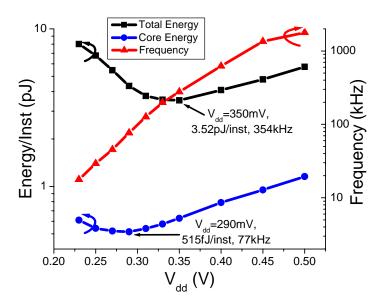

| Figure 4.4: Frequency and energy measurements for a typical die as functions of $V_{dd}$ 54                                                                                                                                                                                                                         |

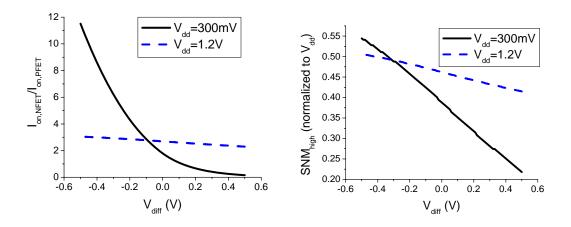

| Figure 4.5: (a) The simulated ratio of NFET on-current ( $I_{on,NFET}$ ) to PFET on-current ( $I_{on,PFET}$ ) at two voltages (b) The simulated high static noise margins (SNM) at two voltages for an inverter with $W_{PFET}=2\cdot W_{NFET}$                                                                     |

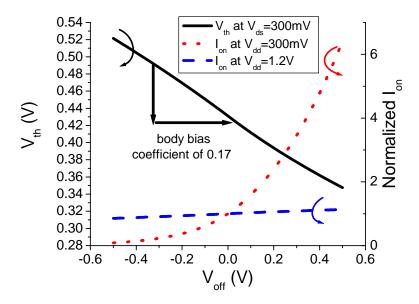

| Figure 4.6: Simulated NFET $V_{th}$ and $I_{on}$ as functions of $V_{off}$                                                                                                                                                                                                                                          |

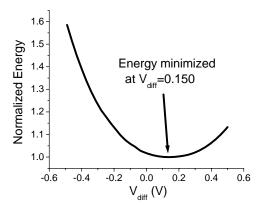

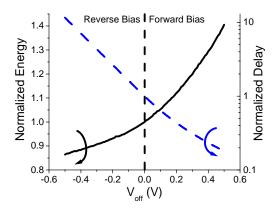

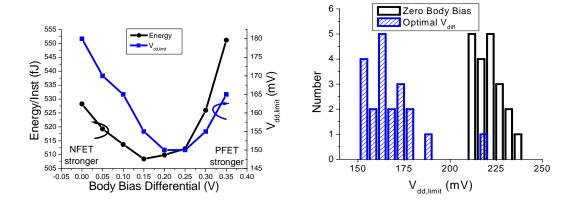

| Figure 4.7: (a) Simulated energy consumption for a chain of 30 inverters at $V_{dd}$ =300mV as a function of $V_{diff}$ (b) Simulated energy and delay for the same inverter chain as functions of $V_{off}$                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4.8: (a) Energy and $V_{dd,limit}$ as functions of $V_{diff}$ for a typical die (b) $V_{dd,limit}$ distribution for 20 dies with and without body biasing. The mean $V_{dd,limit}$ reduces from 221mV to 168mV, a 24% improvement |

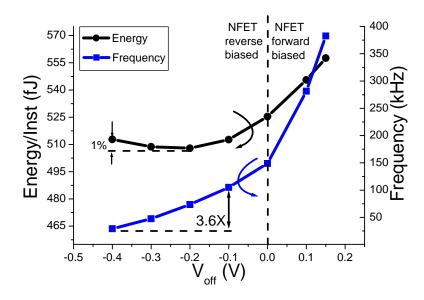

| Figure 4.9: Energy and frequency as functions of body bias offset for a typical die64                                                                                                                                                    |

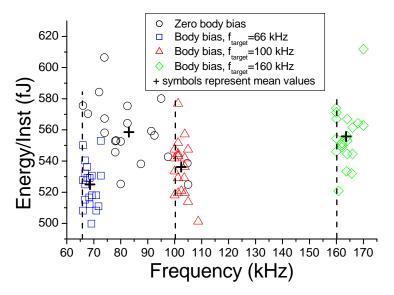

| Figure 4.10: Energy and frequency distributions for 20 dies measured at $V_{dd}$ =300mV64                                                                                                                                                |

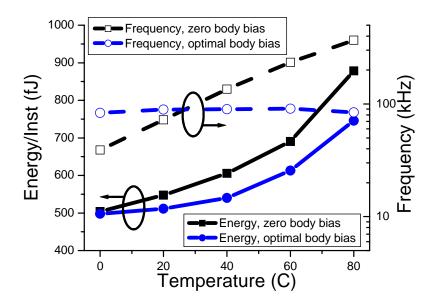

| Figure 4.11: Temperature sensitivity of energy and frequency for a typical die at $V_{dd}$ =300mV                                                                                                                                        |

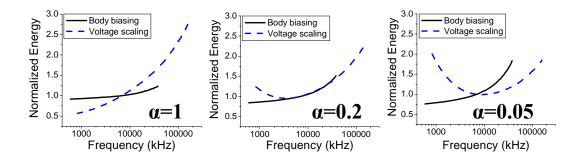

| Figure 4.12: Simulated energy and frequency for an inverter chain subjected to voltage scaling and body biasing. Data is plotted for switching activities of 1, 0.2, and 0.0568                                                          |

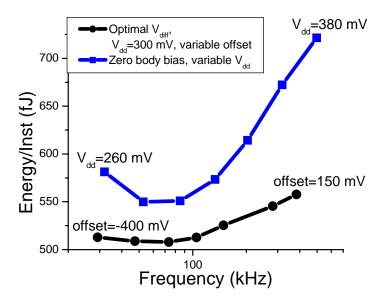

| Figure 4.13: A comparison of energy and frequency measurements for variable body bias and variable $V_{dd}$ systems                                                                                                                      |

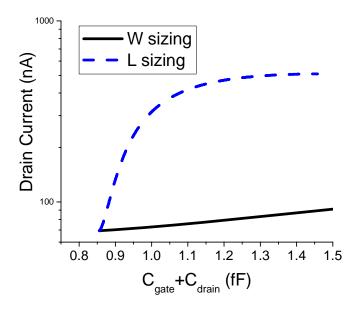

| Figure 4.14: Simulated on-current for an NFET as a function of total device capacitance. The trade-off is shown for both gate width and gate length sizing71                                                                             |

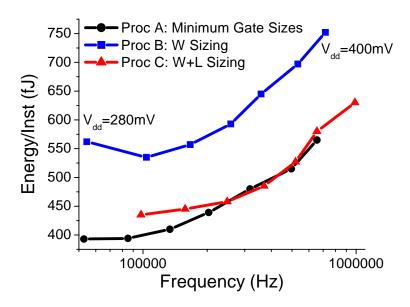

| Figure 4.15: Energy and frequency for three sizing strategies for $V_{dd}$ =280-400mV72                                                                                                                                                  |

| Figure 5.1: The Phoenix Processor                                                                                                                                                                                                        |

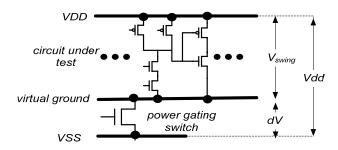

| Figure 5.2: A typical power gating switch                                                                                                                                                                                                |

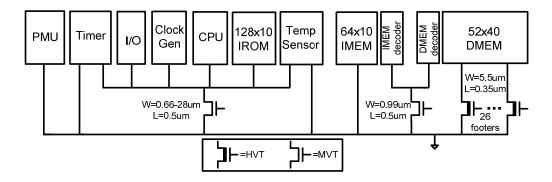

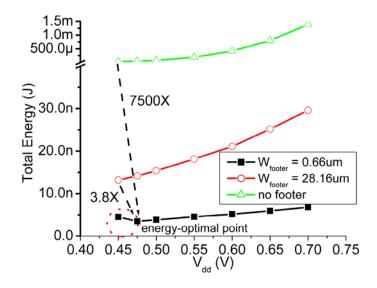

| Figure 5.3: Footer allocation in the Phoenix Processor                                                                                                                                                                                   |

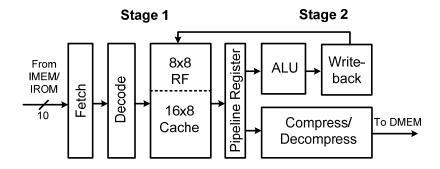

| Figure 5.4: CPU diagram81                                                                                                                                                                                                                |

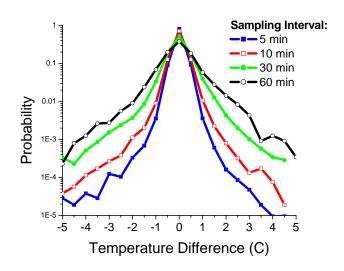

| Figure 5.5: Distribution of temperature in Muskegon, MI in 2006 [75] represented as the difference between temporally adjacent measurements                                                                                              |

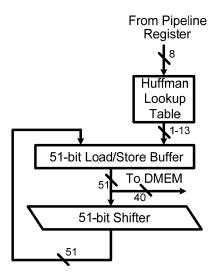

| Figure 5.6: Hardware support for compression                                                                                                                                                                                             |

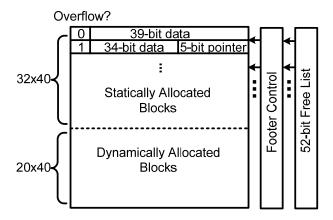

| Figure 5.7: Memory support for compression                                                                                                                                                                                               |

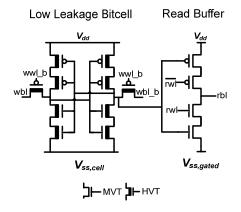

| Figure 5.8: Proposed ultra-low standby power SRAM cell                                                                                                                                                                                   |

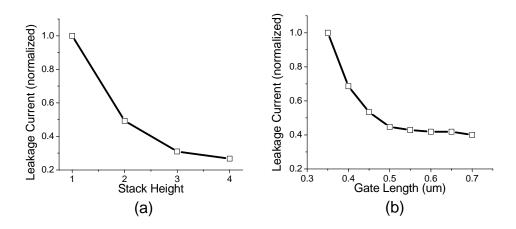

| Figure 5.9: Effectiveness of (a) stack forcing and (b) gate length biasing for leakage reduction                                                                                                                                         |

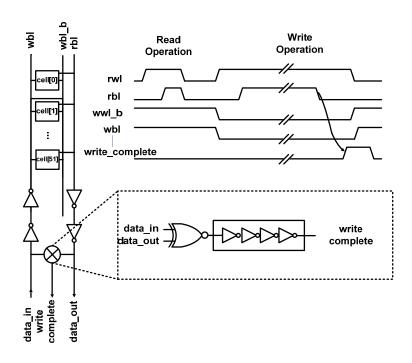

| Figure 5.10: Memory column diagram showing completion detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 90  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

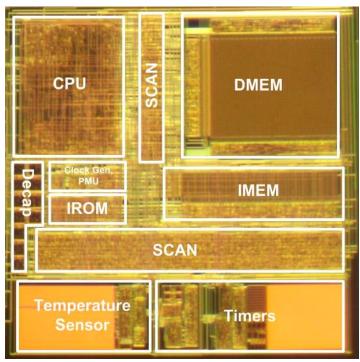

| Figure 5.11: Phoenix Processor die photo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 92  |

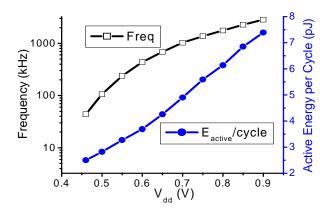

| Figure 5.12: Measured frequency and energy consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 94  |

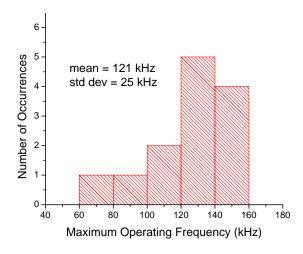

| Figure 5.13: Measured frequency distribution for 13 dies at V <sub>dd</sub> =0.5V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 95  |

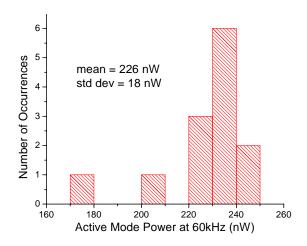

| Figure 5.14: Measured active mode power distribution at 60 kHz for 13 $V_{dd}$ =0.5 $V_{dd}$ 0.5 |     |

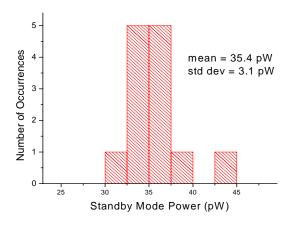

| Figure 5.15: Measured standby mode power distribution for 13 dies at $V_{dd}$ =0.5 $V_{dd}$ 0.5 $V$   | 95  |

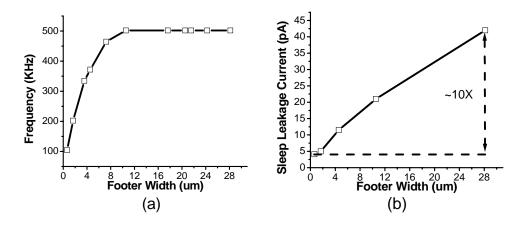

| Figure 5.16: Measured (a) frequency and (b) standby leakage as functions of CP width                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

| Figure 5.17: Total energy consumption assuming 1000 instructions are executed eminutes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

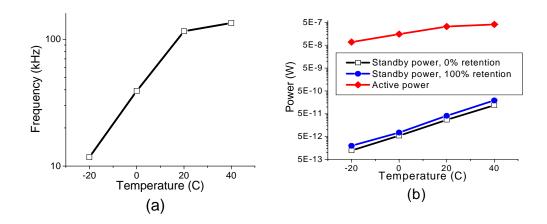

| Figure 5.18: Measured (a) frequency and (b) power as functions of temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 98  |

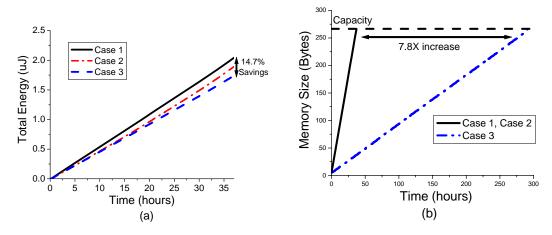

| Figure 5.19: Computed time profiles of (a) energy and (b) memory size for a tem measurement routine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -   |

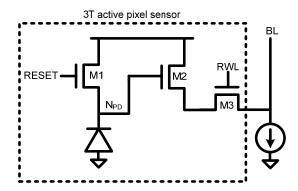

| Figure 6.1: A conventional 3T active pixel sensor design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 103 |

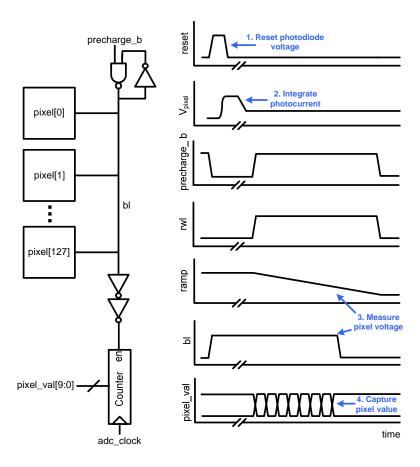

| Figure 6.2: Column architecture and timing diagram for a read operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 104 |

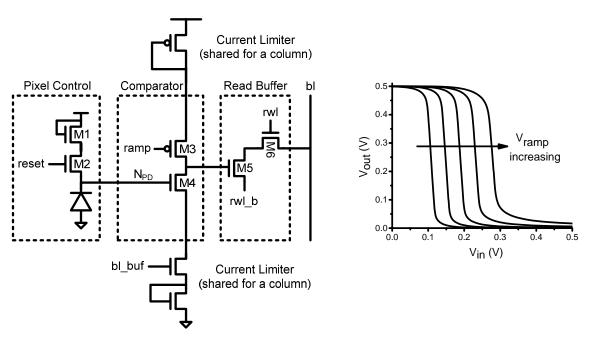

| Figure 6.3: Low voltage pixel architecture and comparator voltage characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

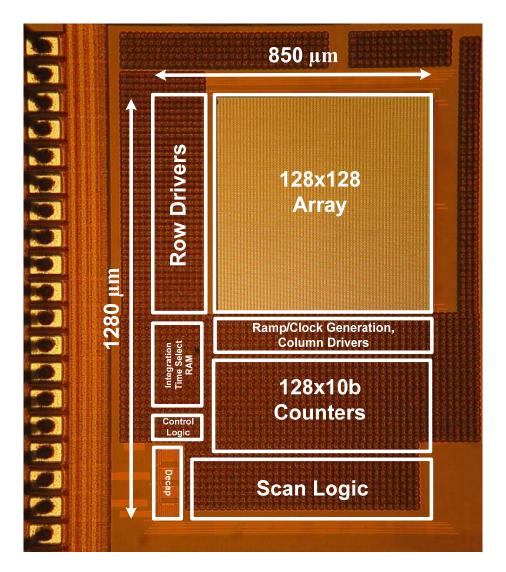

| Figure 6.4: Die photo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 106 |

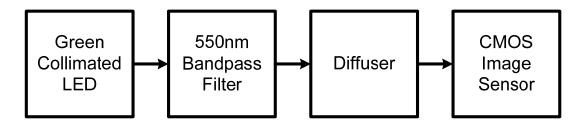

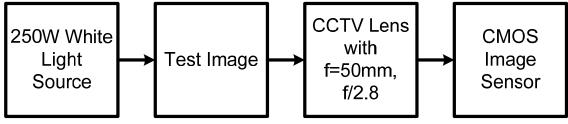

| Figure 6.5: Test setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 107 |

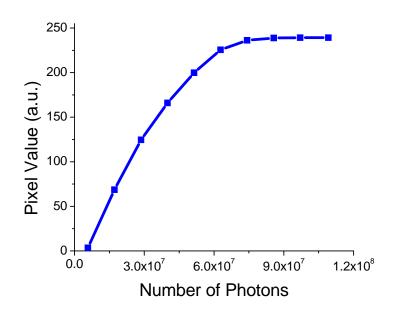

| Figure 6.6: Mean responsivity over 100 frames                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 109 |

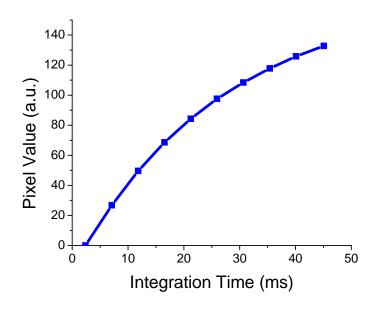

| Figure 6.7: Mean pixel value as a function of integration time over 100 frames                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 109 |

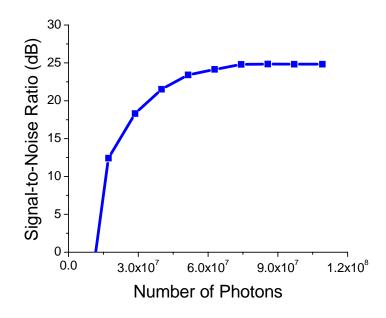

| Figure 6.8: Signal-to-noise ratio as a function of incident light                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 111 |

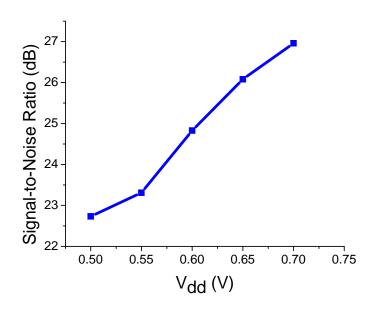

| Figure 6.9: Peak signal-to-noise ratio as a function of V <sub>dd</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 111 |

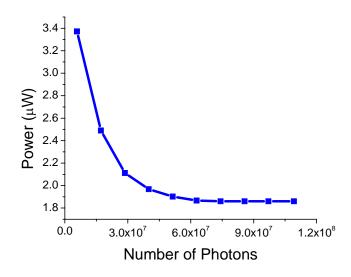

| Figure 6.10: Power at V <sub>dd</sub> =0.6V as a function of incident light                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 113 |

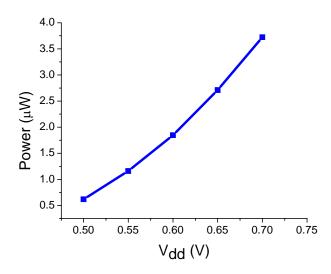

| Figure 6.11: Power at maximum SNR as a function of V <sub>dd</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 113 |

| Figure 6.12: Image capture test setup                                | 114         |

|----------------------------------------------------------------------|-------------|

|                                                                      |             |

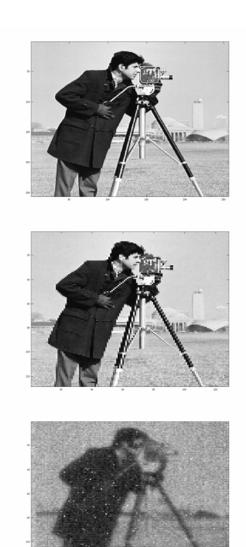

| Figure 6.13: (a) Actual 256x256 8-bit image (b) Image downsampled to | 128x128 (c) |

| Image captured by CMOS image sensor                                  | 115         |

# **List of Tables**

| Table 3.1: NFET parameters under super-V <sub>th</sub> scaling | 25 |

|----------------------------------------------------------------|----|

| Table 3.2: NFET parameters under sub-V <sub>th</sub> scaling   | 36 |

| Table 5.1: Instruction set architecture overview               | 82 |

#### **Abstract**

Cubic-millimeter computers complete with microprocessors, memories, sensors, radios and power sources are becomingly increasingly viable. Power consumption is one of the last remaining barriers to cubic-millimeter computing and is the subject of this work. In particular, this work focuses on minimizing power consumption in digital circuits using low voltage operation.

Chapter 2 includes a general discussion of low voltage circuit behavior, specifically that at subthreshold voltages. In Chapter 3, the implications of transistor scaling on subthreshold circuits are considered. It is shown that the slow scaling of gate oxide relative to the device channel length leads to a 60% reduction in  $I_{on}/I_{off}$  between the 90nm and 32nm nodes, which results in sub-optimal static noise margins, delay, and power consumption. It is also shown that simple modifications to gate length and doping can alleviate some of these problems.

Three low voltage test-chips are discussed for the remainder of this work. The first test-chip implements the Subliminal Processor (Chapter 4), a sub-200mV 8-bit microprocessor fabricated in a  $0.13\mu m$  technology. Measurements first show that the Subliminal Processor consumes only 3.5 pJ/instruction at  $V_{dd}=350 mV$ . Measurements of 20 dies then reveal that proper body biasing can eliminate performance variations and reduce mean energy substantially at low voltage. Finally, measurements are used to

explore the effectiveness of body biasing, voltage scaling, and various gate sizing techniques for improving speed.

The second test-chip implements the Phoenix Processor (Chapter 5), a low voltage 8-bit microprocessor optimized for minimum power operation in standby mode. The Phoenix Processor was fabricated in a  $0.18\mu m$  technology in an area of only  $915x915\mu m^2$ . The aggressive standby mode strategy used in the Phoenix Processor is discussed thoroughly. Measurements at  $V_{dd}$ =0.5V show that the test-chip consumes 226nW in active mode and only 35.4pW in standby mode, making an on-chip battery a viable option.

Finally, the third test-chip implements a low voltage image sensor (Chapter 6). A 128x128 image sensor array was fabricated in a 0.13µm technology. Test-chip measurements reveal that operation below 0.6V is possible with power consumption of only 1.9µW at 0.6V. Extensive characterization is presented with a specific emphasis on noise characteristics and power consumption.

## Chapter 1

#### Introduction

The miniaturization of electronics has launched a wireless sensing revolution that is gaining traction in both industry and academia. Complex wireless systems can be packaged in volumes on the order of several cubic centimeters, enabling pervasive sensing. Companies are marketing wireless soil moisture monitors for crop irrigation [1], compact wireless tire pressure sensors [2], and even tiny pressure sensors for monitoring the integrity of stent grafts [3]. Academic researchers have made more ambitious demonstrations ranging from wireless neural monitoring and stimulation [4][5] to complex gas analysis in ultra-small form factors [6].

Even as new applications emerge for wireless sensing, the miniaturization of electronics continues. Innovations in microprocessors, radios, sensors, actuators, packaging, and power sources will soon take us from the cubic-centimeter domain to the cubic-millimeter (1mm³) domain. In 1mm³ computing, computers may be embedded virtually anywhere. They may be woven into clothing, implanted in the body, and set in construction materials. In light of such flexibility, it becomes critically important to ask: who needs a 1mm³ computer and why?

# 1.1 The Need for the 1mm<sup>3</sup> Computer

The promise of 1mm<sup>3</sup> computing is perhaps most apparent in medicine. Advances in the semiconductor industry have historically been catalysts for tremendous progress in medicine, enabling devices ranging from pacemakers to neurostimulators to continuous blood glucose monitors. Despite this past success, there is a continuing drive for smaller devices to address increasingly delicate problems.

For example, the diagnosis and treatment of glaucoma (open angle glaucoma and angle closure glaucoma are expected to affect 60.5 million people worldwide by 2010 [7]) requires periodic measurements of pressure in the eye (intra-ocular pressure). Intra-ocular pressure is currently monitored directly by a doctor, requiring frequent trips to the doctor's office to ensure sufficient temporal resolution [14]. An intra-ocular pressure sensor (Figure 1.1) with a MEMS pressure sensor, microprocessor, memory, radio and power source implanted in the eye would reduce both cost and time investment and would increase the temporal resolution of pressure measurements. Size is of the utmost importance in this example since implant damage to the patient must be minimized. Miniaturized computers are similarly useful for a wide range of medical monitoring devices including intra-cardiac pressure sensors for patients with congestive heart failure, intra-cranial pressure sensors for patients with hydrocephalus, and stent graft structural monitors for patients affected by abdominal aortic aneurysms.

Figure 1.1: An implantable intra-ocular pressure sensor (courtesy of Y-S. Lin)

The broad field of wireless sensor networks will also be among the primary beneficiaries of 1mm<sup>3</sup> computing. Tiny sensors could be used for widespread battlefield surveillance [8][9], forest fire and flood detection [9], and energy management in buildings and homes [9]. While less volume-constrained than medical applications, these and other wireless sensor network applications will benefit from the low costs associated with small volume and high integration.

# 1.2 Challenges in 1mm<sup>3</sup> Computing

To meet the requirements of the aforementioned applications, 1mm<sup>3</sup> computers will include a microprocessor, a memory, sensors, actuators, wireless communication, and a power source in a compact package (Figure 1.2). Thanks to consistent reductions in transistor size, circuit components for computing and communication easily meet the size requirements set by 1mm<sup>3</sup> computing. Similarly, innovations in MEMS have enabled the design of tiny sensors and actuators well suited to 1mm<sup>3</sup> computing. Despite recent advances in the design of compact batteries [10] and energy scavenging devices [11],

Figure 1.2: The canonical 1mm<sup>3</sup> computer

power sources cannot be easily miniaturized while also serving the power demands of circuit and MEMS components. Consider, for example, a thin film zinc/silver oxide battery with a capacity of 100μAh/cm² and output voltage of 1.55V [15]. Assuming that battery size is restricted to 1mm² and that energy density remains constant at small battery sizes, the average current draw of circuit and MEMS components must be 114pA (for power consumption of 177pW) to guarantee one year of battery life. The power consumption of the most energy efficient commercial microcontrollers (for example, the Texas Instruments MSP430 [12]) exceeds these limits by several orders of magnitude even in standby mode.

In light of power source limitations, power minimization is one of the clear challenges of 1mm<sup>3</sup> computing. Other notable challenges include compact antenna design and compact (and potentially biocompatible) packaging, but the focus of this work is power minimization. Particular emphasis is placed on minimizing power consumption in digital circuits. In the remainder of this chapter, the topic of energy minimization in

Figure 1.3: NFET drain current as a function of gate-source voltage digital circuits is explored and the contributions of our research to the growing field of low voltage circuit design are discussed.

# 1.3 Addressing the Power Problem

The energy consumed by a digital circuit is typically broken into contributions from switching energy ( $E_{switch}$ ) and leakage energy ( $E_{leak}$ ), as shown in Equation 1.1, where  $C_S$  is the switched capacitance,  $V_{dd}$  is the supply voltage,  $\alpha$  is the switching activity,  $I_{leak}$  is the total leakage current of the circuit, and  $t_p$  is the maximum delay across the circuit.

$$E_{total} = E_{switch} + E_{leak} = C_S \cdot V_{dd}^2 \cdot \alpha + I_{leak} \cdot V_{dd} \cdot t_p$$

EQ 1.1

In a typical circuit operating at the nominal supply voltage,  $E_{switch}$  far exceeds  $E_{leak}$  (though  $E_{leak}$  generally grows with subthreshold leakage and gate leakage as technology scales [16]). Given the quadratic dependence of  $E_{switch}$  on  $V_{dd}$ , the most effective technique for reducing energy in a circuit is to reduce  $V_{dd}$ . Though it is clear that reducing  $V_{dd}$  will yield energy reductions, it is not obvious how far  $V_{dd}$  can be scaled. In general,

circuit designers assume that transistors turn off when the gate-source voltage drops below the threshold voltage ( $V_{th}$ ) of the device. This is, of course, a very simplistic assumption since subthreshold leakage is non-negligible, as shown in Figure 1.3. With careful design, subthreshold leakage can be used to charge and discharge nodes in a digital circuit, suggesting that it is possible to use  $V_{dd} < V_{th}$ . Circuits operating in this region are called subthreshold circuits and are the focus of this work.

Aggressive voltage scaling into the subthreshold region poses a number of daunting challenges to circuit designers. The first of these issues is reduced performance (i.e., reduced operating frequency). As shown in Figure 1.3, subthreshold currents are much smaller than the strong inversion currents used in typical superthreshold ( $V_{dd} > V_{th}$ ) circuits, so switching delays are increased by several orders of magnitude [17]. In many 1mm<sup>3</sup> computing applications, this performance penalty is tolerable, but many applications, such as those requiring streaming media processing, may have more stringent deadlines for computation.

The reduced noise margins that come with subthreshold operation are also potentially problematic. Though coupling noise may reduce with voltage [17], noise from external components (for example, coupling noise due to a reference oscillator) may not scale with voltage and will create serious robustness problems.

The most significant problem facing subthreshold designers is an increased sensitivity to variability. Due to the exponential dependence of subthreshold current on  $V_{th}$ ,  $V_{dd}$  and temperature, small process and environmental variations can lead to enormous noise margin, delay and energy fluctuations [18]. This is a particular challenge

for memory designers since dense SRAM arrays require extremely high yield and use small variation-prone devices aggressively [19].

## 1.4 Previous Work in Low Voltage Design

The limits of voltage scaling were first explored in 1972 [20]. Further research in digital subthreshold operation was limited until 1999, when the authors of [21] began to explore logic family selection for subthreshold circuits. Subsequently, a number of research groups have begun to focus their efforts on addressing the challenges of subthreshold operation.

The existence of an energy-optimal voltage (which typically lies in the subthreshold regime) was first noted in [23] and later in [24]. This was an important discovery because it showed 1) that subthreshold operation is typically energy optimal and 2) that scaling to the minimum functional voltage can actually increase energy consumption. Early hardware demonstrations of subthreshold circuits were presented in [25] and later in [26], where operation down to 180mV was achieved. The simulation-based conclusions regarding the energy-optimal voltage [23][24] were confirmed by hardware presented in [27]. The first subthreshold general microcontroller was presented in [28], and was shown to consume only 2.6pJ per instruction. These early research efforts proved that energy efficient subthreshold operation was possible but did not address the more important topics of variability and robust memory design.

Recently, the problems posed by robust memory design have begun to receive more attention. In [29] a simulation-based study explored the key sensitivities of SRAM noise margins in the subthreshold regime. The authors of [19][30] showed that a

modified SRAM cell using 8 transistors could achieve robust operation from nominal superthreshold voltages down to 0.41V. Several alternative SRAM cells have also been proposed with a specific focus on subthreshold operation [31][32][33][71][72].

The recent burst of activity in subthreshold circuits research has not yet addressed several key needs. Variability has still not been explored adequately to permit widespread commercial use. The importance of standby power in low voltage 1mm<sup>3</sup> systems has also not been addressed. Additionally, low voltage research has focused largely on conventional circuits (e.g., microprocessors, memories, etc.) and has not been expanded to include sensors, critical components in any 1mm<sup>3</sup> computer.

#### 1.5 Contributions of this Work

This work explores aggressive voltage scaling for robust energy efficient operation in 1mm<sup>3</sup> computing systems. The study begins in Chapter 2 with a review of basic digital subthreshold circuit concepts. This review gives a detailed overview of the most important prior work in subthreshold circuit design with a particular emphasis on device characteristics, voltage selection, and variability. This work is drawn from several papers that I authored or co-authored, including [17] and [34], though most results are derived from results originally presented by Bo Zhai in [18] and [23].

Chapter 3 discusses the topic of device scaling in subthreshold circuits. MEDICI simulations are used to investigate the implications of transistor scaling on subthreshold circuits. In particular, it is shown that conventional scaling trends lead to sub-optimal noise margins, performance, and energy consumption and that simple changes to channel doping and gate length provide dramatic improvements to these parameters. The work in

Chapter 3 is derived from work originally presented in [77]. I developed each of the experiments described in that chapter, though Mingoo Seok offered valuable feedback throughout.