# Online Low-Cost Defect Tolerance Solutions for Microprocessor Designs

by

Kypros Constantinides

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in The University of Michigan 2009

#### **Doctoral Committee:**

Associate Professor Todd M. Austin, Chair Associate Professor Achilleas Anastasopoulos Associate Professor Scott Mahlke Assistant Professor Valeria M. Bertacco ©  $\frac{\text{Kypros Constantinides}}{\text{All Rights Reserved}}$  2009

To my family

#### ACKNOWLEDGEMENTS

First, I would like to thank my advisor Prof. Todd Austin for his support and guidance that made the completion of this dissertation possible. Over the last five years, under the supervision of Prof. Austin, I had the opportunity to learn a lot from him and acquire the necessary abilities to carry out independent research. During my graduate studies, in multiple occasions where I felt I was loosing focus and direction, Prof. Austin was a constant source of inspiration and guidance that always put me back on truck towards the pursue and completion of my research goals. I feel that my interaction with Prof. Austin provided me with several skills, values, and knowledge that would be very helpful in my future career and life, and I am deeply grateful to him for that.

I would also like to thank the members of my dissertation committee: Prof. Valeria Bertacco, Prof. Scott Mahlke, and Prof. Achilleas Anastasopoulos. First, I appreciate their kindness to serve as members of my dissertation committee and I would like to thank them for the positive feedback, guidance, and support that they provided to me along the process. In particular, I would like to thank Prof. Bertacco that together with my advisor Prof. Austin supervised and supported me for most of my dissertation work. Her help and support was an important cornerstone for the completion of this dissertation. Early in my graduate studies I also enjoyed working with Prof. Mahlke in multiple projects that helped define my dissertation topic.

I am also deeply grateful to all the people that I had the opportunity to collaborate with on many of the projects presented in this thesis: Smitha Shyam, Sujay Phadke, Mojtaba Mehrara, Mona Attariyan, Jason Blome, Stephen Plaza, Bin Zhang, Michael Orshansky, Andrea Pellegrini, Dan Zhang, and Shobana Sudhakar. I would also like to thank my lab-mates, both current ones and those that already graduated and left the lab, for the great working and research environment that they provided: Andreas Moustakas, Joe Greathouse, Jason Clemons, David Ramos, Ilya Wagner, David Meisner, Andrew DeOrio, Leyla Nazhandali, and Michael Minuth.

I am thankful to my mentor from Microsoft Research, Onur Mutlu, for his support and guidance during my graduate studies. My collaboration with Onur started when I interned at Microsoft Research at the summer of 2007 and since then he is been a constant source

for advice that I could rely on. Over the last two years, my discussions with Onur shaped in many ways the work that is presented in this thesis.

I would also like to thank Prof. Yiannakis Sazeides for the early influence that he had on me during my undergraduate studies. While working with him during my undergraduate studies I had the chance to participate for the first time in research-oriented projects. That experience, fueled my interest in computer architecture, and later on, led to my decision to purse a Ph.D. degree in the area of computer architecture. I am deeply grateful to him for all the time that he spent with me in the lab teaching me how to carry out independent research, and for making me believe in myself that I could continue my graduate studies in the States.

Finally, I would like to thank my entire family for their support during my graduate studies. In particular, I would like to thank my parents for always encouraging me to pursue higher education and for raising me up with the values that I needed to complete this dissertation.

#### **PREFACE**

One of the major driving forces of the semiconductor industry is the continuous scaling of the silicon process technology. Over the last four decades, the scaling into a new silicon technology every few years offered to the computer architects smaller, faster, and cheaper transistors that made possible the development of high-performance microprocessors. This technological achievement also fueled the widespread adoption of microprocessor-based products in applications that touch every aspect of our life. However, the challenges in producing reliable devices in extremely dense silicon technologies are growing, with many device experts warning that continued scaling will inevitably result in silicon technology generations that are much less reliable than the current ones. Microprocessors manufactured in future silicon technologies will likely experience failures in the field due to silicon defects occurring during system operation. In the absence of any viable alternative technology, the success of the semiconductor industry in the future will depend on the creation of cost-effective mechanisms to tolerate silicon defects in the field while the microprocessor is in operation.

This thesis is focused on the exploration and evaluation of new alternative defect tolerance techniques that will provide low-cost online mechanisms to protect a microprocessor design from silicon defects. The approach of these novel defect tolerance solutions represents a new thinking in the field of defect-tolerant design. In particular, traditional approaches to defect-tolerant design saddle a system with costly redundant components that continuously verify the integrity of all computation. In contrast, the BulletProof approach, presented in this thesis, provides very low cost defect-tolerance through periodic online hardware checking by combining area-frugal hardware checkers with microarchitectural checkpointing. The use of checkpointing and recovery mechanisms provides computational epochs and a substrate for speculative unchecked execution. At the end of each epoch, the epoch's speculative computation is validated by checking the integrity of the underlying hardware using on-chip hardware checkers. This enables a low overhead solution that only needs to periodically check the integrity of the underlying hardware rather than continuously validate the execution using redundant computation.

To further lower the cost of the BulletProof mechanism and provide more flexible hardware checking strategies a new defect-tolerance approach is developed, called the Access-Control Extension (ACE) Framework, that shifts the silicon defect detection and diagnosis process from hardware to software. This new approach, allows special ISA instructions to access and control virtually any part of the processor's internal state. Based on this framework, special firmware periodically suspends the processor's execution and performs high-quality testing of the underlying hardware to detect defects.

This thesis, also makes the case that the hardware used to implement defect tolerance solutions, like the hardware resources of the ACE framework, can also be used for other applications to amortize their cost and ease the adoption of defect-tolerance mechanisms in future generation microprocessor designs. Specifically, it is demonstrated that the ACE framework hardware resources can also be used for (i) the online detection of design bugs, (ii) as a post-silicon debugging tool, and (iii) for improving the manufacturing testing process.

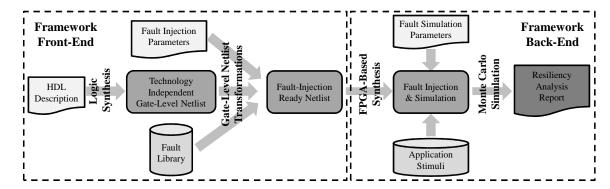

Finally, this thesis presents CrashTest, a novel FPGA-based framework used to assess the threats and the reliability requirements of a microprocessor design. The CrashTest framework differs from other resiliency analysis tools in two ways. First, it can automatically orchestrate a fault injection and analysis campaign on the gate-level netlist of a microprocessor design using an extensive collection of low-level fault models, and second, it employs FPGA-based accelerated hardware emulation to enable a detailed low-level failure analysis of complex full-system designs that can boot an operating system and run applications.

Altogether, the defect tolerance solutions presented in this thesis provide to a microprocessor design the same reliability guarantees as traditional defect tolerance techniques, but at a much lower cost and with higher flexibility and online adaptivity. This cost-effective defect-tolerance framework makes possible the development of reliable microprocessors using unreliable silicon technologies. The ability to use unreliable silicon technologies to manufacture reliable microprocessors will enable the continued silicon process scaling into smaller but less reliable transistors, a key requirement for the development of the next generation microprocessors and the extension of microprocessor-based products into new applications.

## TABLE OF CONTENTS

| DEDICAT    | ION                                                              | ii       |

|------------|------------------------------------------------------------------|----------|

| ACKNOW     | LEDGEMENTS                                                       | iii      |

| PREFACE    |                                                                  | V        |

| LIST OF I  | FIGURES                                                          | X        |

| LIST OF T  | TABLES                                                           | xiii     |

| Chapte     | r I. Introduction                                                | 1        |

| 1.1        | Why Does Silicon Fail?                                           | 2        |

|            | 1.1.1 The Bathtub Curve                                          | 2        |

|            | 1.1.2 Silicon Failure Mechanisms                                 | 4        |

| 1.2        | Defect-Tolerant Microarchitectures                               | 7        |

| 1.3        | The Reliable System Design Space                                 | 8        |

| 1.4<br>1.5 | Contributions of This Thesis                                     | 10<br>12 |

| Chanta     | r II. Traditional Techniques and Recent Research Approaches for  |          |

| •          | Defect-Tolerant Design                                           | 14       |

| 2.1        | Traditional Defect-Tolerance Techniques                          | 14       |

| 2.2        | Fault Avoidance Strategies                                       | 16       |

| 2.3        | Defect-Tolerance Techniques in Research Literature               | 17       |

| -          | r III. Defect Tolerance Through Periodic Hardware Checking - The |          |

|            | BulletProof Pipeline                                             | 21       |

| 3.1        | Online Periodic Hardware Checking                                | 22       |

|            | 3.1.1 Online Hardware Testing Techniques                         | 24       |

|            | 3.1.2 Microarchitectural Checkpointing                           | 28       |

|            | 3.1.3 Checkpointing with Two-Phase Commit                        | 30       |

|            | 3.1.4 System Fault Recovery                                      | 31       |

|        | 3.1.5     | Repairing the BulletProof Pipeline                          | 31  |

|--------|-----------|-------------------------------------------------------------|-----|

|        | 3.1.6     | Handling Input/Output Requests                              | 32  |

|        | 3.1.7     | Assumptions and Limitations                                 | 33  |

| 3.2    | Bullet    | Proof Protection from Transient Faults                      | 33  |

| 3.3    | Experi    | imental Evaluation                                          | 36  |

|        | 3.3.1     | Experimental Framework                                      | 36  |

|        | 3.3.2     | Testing Performance and Design Coverage                     | 38  |

|        | 3.3.3     | Run-time Performance                                        | 39  |

| 3.4    | Relate    | d Work                                                      | 42  |

| 3.5    | Chapte    | er Summary                                                  | 45  |

| Chapte | r IV. A   | Software-Based Periodic Hardware Checking Solution - The    |     |

| _      |           | amework                                                     | 47  |

| 4.1    | Softwa    | are-Based Periodic Defect Detection and Diagnosis           | 49  |

| 1.1    | 4.1.1     | An ACE-Enhanced Architecture                                | 49  |

|        | 4.1.2     | ACE-Based Online Testing                                    | 53  |

|        | 4.1.3     | ACE Testing in a Checkpointing and Recovery Environment .   | 56  |

|        | 4.1.4     | Putting it Together: Algorithmic Flow of ACE-Based Testing. | 56  |

|        | 4.1.5     | ACE Testing Execution Models                                | 57  |

|        | 4.1.6     | Flexibility of ACE Testing                                  | 59  |

| 4.2    |           | imental Methodology                                         | 60  |

| 4.3    |           | imental Evaluation                                          | 63  |

|        | 4.3.1     | Basic Core Functional Testing                               | 63  |

|        | 4.3.2     | ACE Testing Latency, Coverage, and Storage Requirements     | 65  |

|        | 4.3.3     | Full-Chip Distributed Testing                               | 67  |

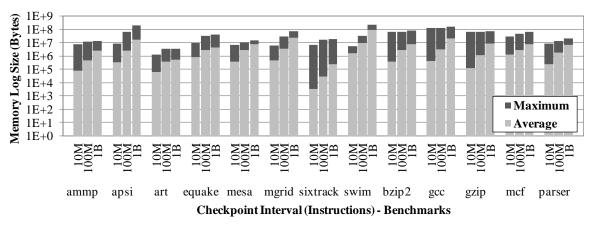

|        | 4.3.4     | Memory Logging in Coarse-grained Checkpointing              | 68  |

|        | 4.3.5     | Performance Overhead of ACE Testing                         | 69  |

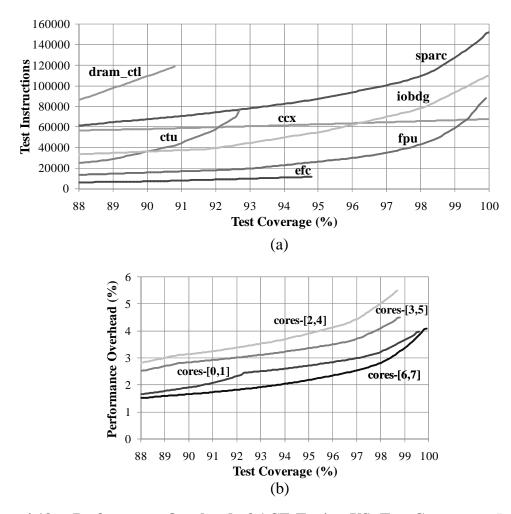

|        | 4.3.6     | Performance-Reliability Trade-off                           | 73  |

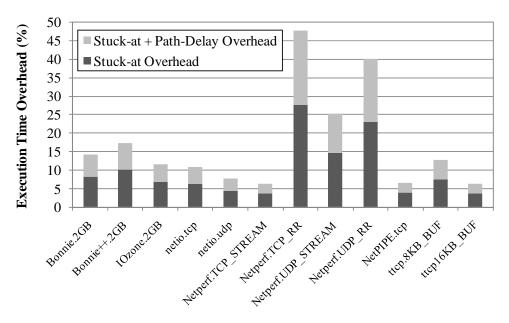

|        | 4.3.7     | Overhead of ACE Testing in I/O-intensive Applications       | 75  |

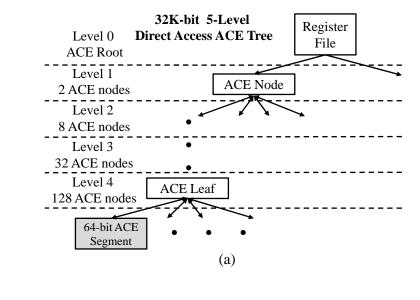

|        | 4.3.8     | ACE Tree Implementation and Area Overhead                   | 76  |

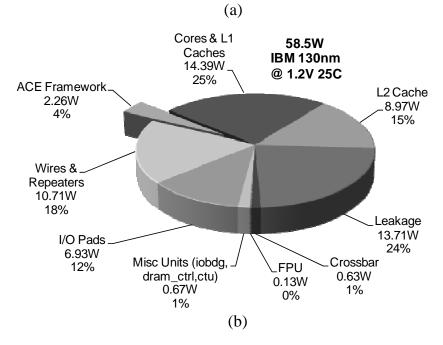

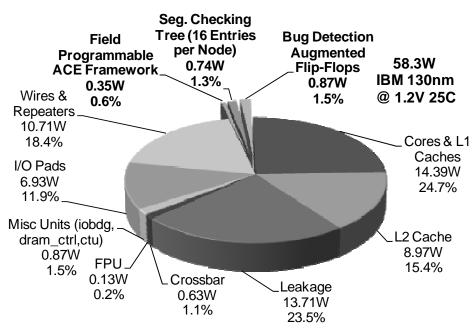

|        | 4.3.9     | Power Consumption Overhead of the ACE Framework             | 78  |

| 4.4    | Relate    | d Work                                                      | 80  |

| 4.5    | Chapte    | er Summary                                                  | 85  |

| Chapte | r V.   A( | CE Framework Extensions - Adding Value                      |     |

| _      | to Resil  | iency Mechanisms                                            | 87  |

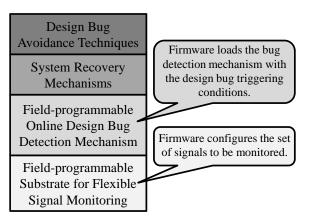

| 5.1    | ACE F     | Framework for Online Design Bug Detection                   | 88  |

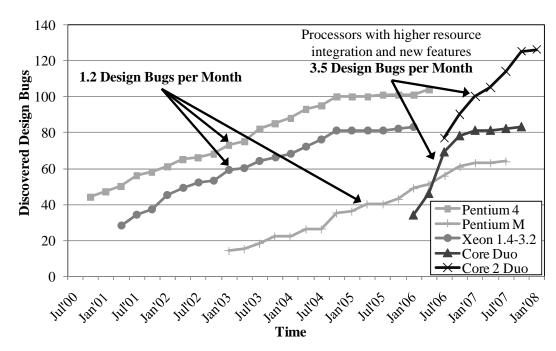

|        | 5.1.1     | The Problem of Design Bugs in Modern Microprocessors        | 88  |

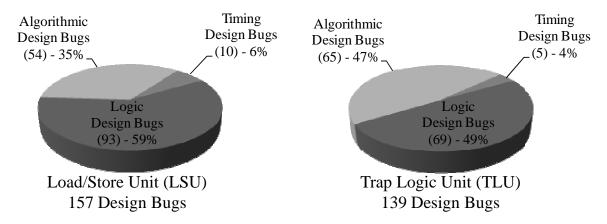

|        | 5.1.2     | Design Bug Analysis                                         | 91  |

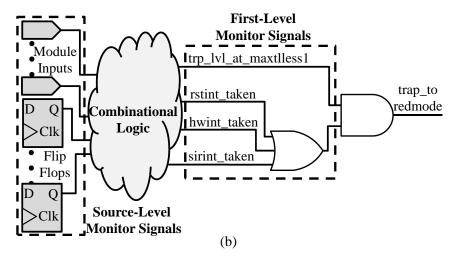

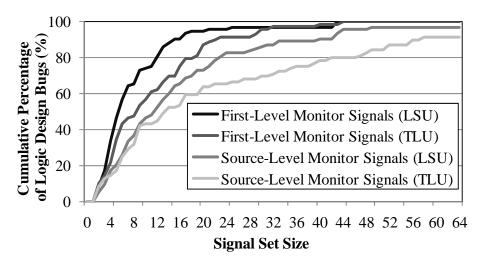

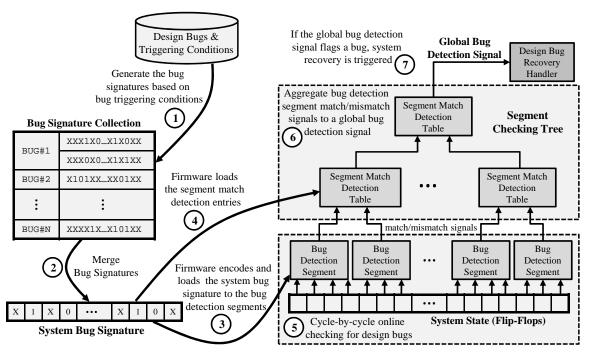

|        | 5.1.3     | Detecting Logic Design Bugs at Runtime                      | 98  |

|        | 5.1.4     | ACE-Based Distributed Online Bug Detection                  | 102 |

|        | 5.1.5     | <del>_</del>                                                | 110 |

|          | 5.1.6 Experimental Evaluation                                   | 113 |

|----------|-----------------------------------------------------------------|-----|

| 5.2      | Related Work                                                    | 118 |

| 5.3      | Other Applications of the ACE Framework                         | 122 |

|          | 5.3.1 ACE Framework Extensions for Post-silicon Debugging       | 122 |

|          | 5.3.2 ACE Framework Extensions for Manufacturing Testing        | 128 |

| 5.4      | Chapter Summary                                                 | 130 |

| Chapte   | r VI. FPGA-Based Accelerated Hardware Resiliency Analysis - The |     |

|          | CrashTest Framework                                             | 132 |

| 6.1      | The Challenges of Hardware Resiliency Analysis                  | 133 |

| 6.2      | Overview of the CrashTest Framework                             | 134 |

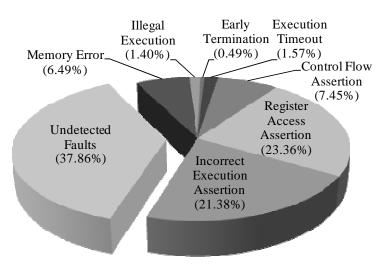

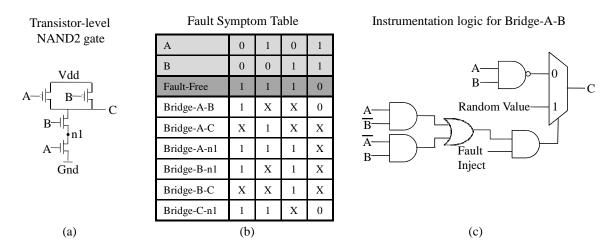

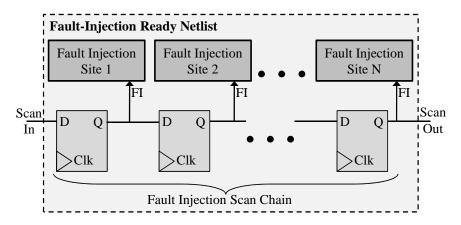

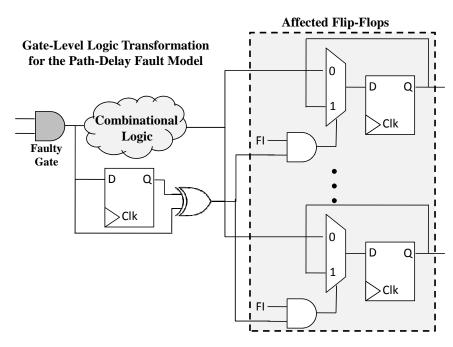

| 6.3      | Gate-Level Fault Injection Methodology                          | 136 |

| 6.4      | FPGA-Based Fault Emulation                                      | 140 |

| 6.5      | Framework Evaluation                                            | 141 |

|          | 6.5.1 Experimental Methodology                                  | 141 |

|          | 6.5.2 Monte Carlo Simulation & Statistical Confidence           | 143 |

|          | 6.5.3 Framework Performance                                     | 143 |

|          | 6.5.4 Experimental Results                                      | 145 |

| 6.6      | Related Work                                                    | 148 |

| 6.7      | Chapter Summary                                                 | 149 |

| Chapte   | r VII. Conclusions and Future Work                              | 150 |

| 7.1      | Thesis Summary                                                  | 151 |

| 7.2      | Thesis Conclusions                                              | 153 |

| 7.3      | Future Work                                                     | 156 |

| BIBLIOGI | RAPHY                                                           | 158 |

## LIST OF FIGURES

| Figure |                                                                   |    |

|--------|-------------------------------------------------------------------|----|

| 1.1    | The Cost of Silicon Reliability:                                  | 2  |

| 1.2    | The Bathtub Curve:                                                | 3  |

| 1.3    | Reliable System Design Space:                                     | 9  |

| 2.1    | Traditional Defect-Tolerance Techniques:                          | 15 |

| 3.1    | High-level System Architecture of the BulletProof Microprocessor: | 23 |

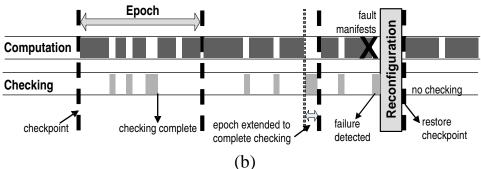

| 3.2    | Component-Specific Online Hardware Testing Techniques:            | 25 |

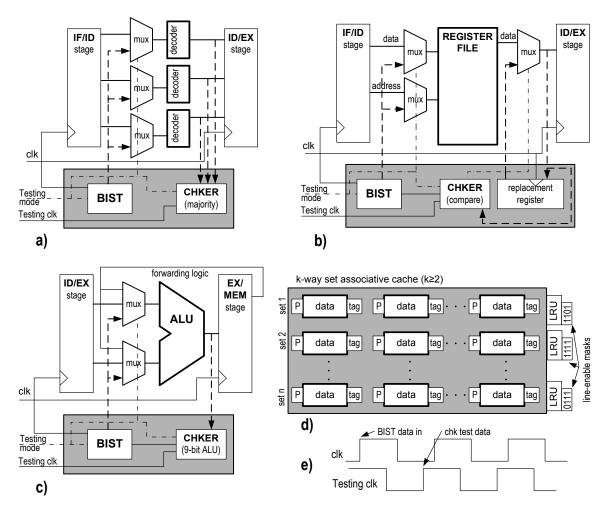

| 3.3    | Control Logic Checker Network:                                    | 27 |

| 3.4    | Microarchitectural Checkpointing System:                          | 29 |

| 3.5    | Incorrect System Recovery Scenario:                               | 30 |

| 3.6    | BulletProof SER-Tolerant Flip-Flop Design:                        | 34 |

| 3.7    | Timing Diagram of a Transient Fault Detection:                    | 35 |

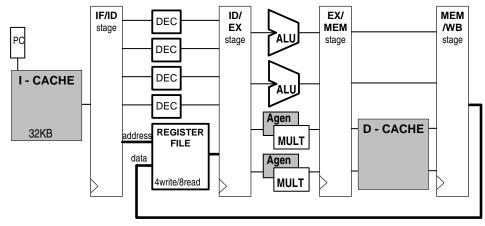

| 3.8    | The BulletProof Baseline Processor:                               | 37 |

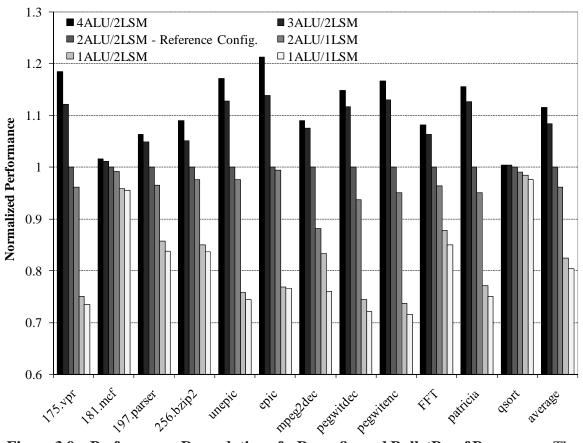

| 3.9    | Performance Degradation of a Reconfigured BulletProof Processor:  | 41 |

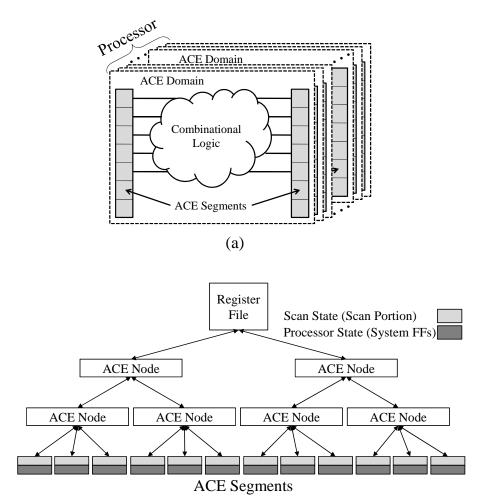

| 4.1    | ACE Framework Overview:                                           | 48 |

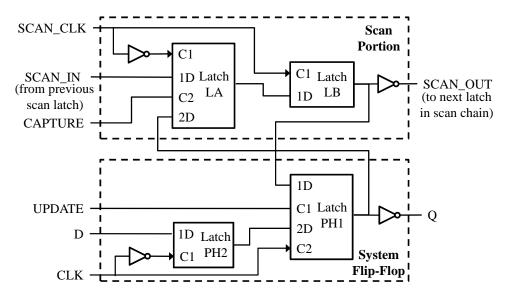

| 4.2    | A Typical Scan Flip-Flop:                                         | 50 |

| 4.3    | The ACE Architecture:                                             | 52 |

| 4.4    | ACE Firmware:                                                     | 54 |

| 4.5  | Different ACE Testing Execution Models:                         | 58 |

|------|-----------------------------------------------------------------|----|

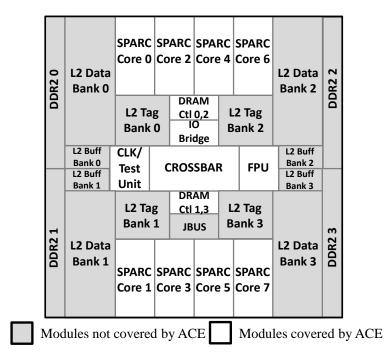

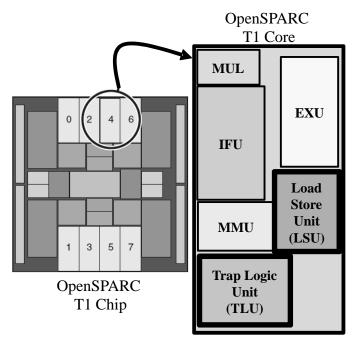

| 4.6  | ACE Coverage of the OpenSPARC T1 Processor:                     | 61 |

| 4.7  | Fault Coverage of Basic Core Functional Testing:                | 64 |

| 4.8  | Memory Logging Storage Requirements:                            | 68 |

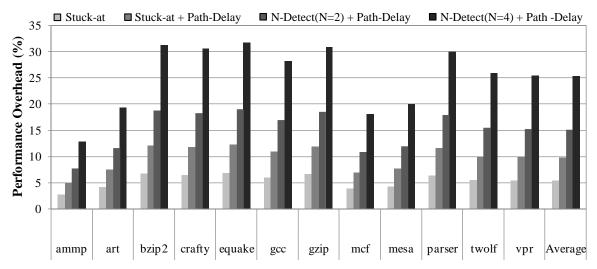

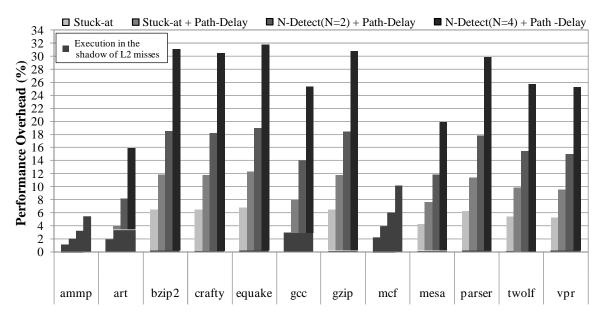

| 4.9  | Performance Overhead of Single-Threaded Sequential ACE Testing: | 69 |

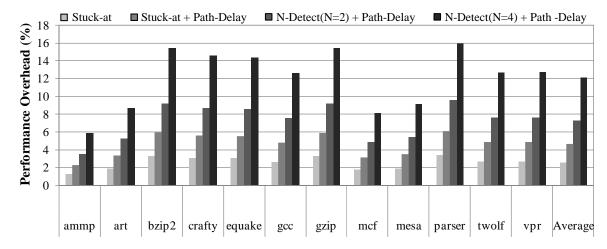

| 4.10 | Performance Overhead of SMT-Based ACE Testing:                  | 71 |

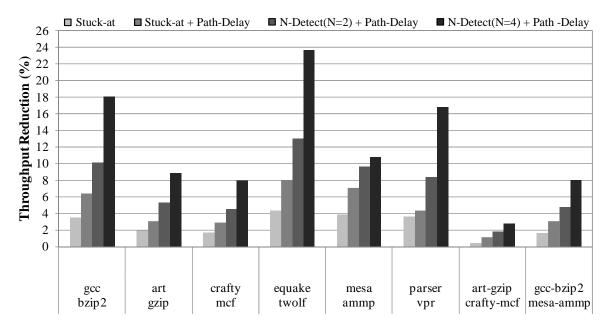

| 4.11 | Throughput Reduction Due to SMT-Based ACE Testing:              | 72 |

| 4.12 | Performance Overhead of Interleaved ACE Testing:                | 73 |

| 4.13 | Performance Overhead of ACE Testing VS. Test Coverage:          | 74 |

| 4.14 | ACE Testing on I/O-Intensive Applications:                      | 76 |

| 4.15 | ACE Tree Implementation:                                        | 77 |

| 4.16 | Power Consumption Overhead of the ACE Framework:                | 79 |

| 5.1  | Design Bugs in Modern Microprocessors:                          | 89 |

| 5.2  | Overview of Online Design Bug Detection and Avoidance:          | 90 |

| 5.3  | Design Bugs Documented in Microprocessor Errata Sheets:         | 92 |

| 5.4  | Logic Design Bug:                                               | 94 |

| 5.5  | Algorithmic Design Bug:                                         | 94 |

| 5.6  | Timing Design Bug:                                              | 95 |

| 5.7  | Design Bugs in the OpenSPARC T1 Core:                           | 96 |

| 5.8  | Design Bug Distribution:                                        | 97 |

| 5.9  | Design Bug Triggering and Source Signals:                       | 98 |

| 5.10 | Design Bugs Source Signal Statistics:                           | 90 |

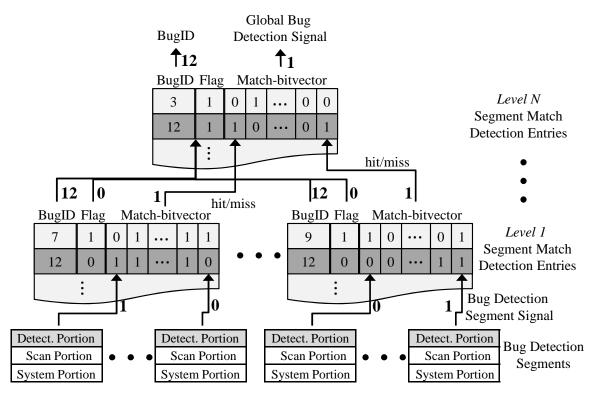

| 5.11 | Overview of ACE-Based Online Design Bug Detection:                  | 103 |

|------|---------------------------------------------------------------------|-----|

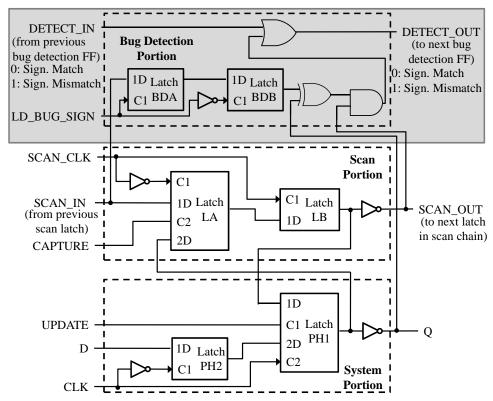

| 5.12 | Bug Detection Flip-Flop:                                            | 105 |

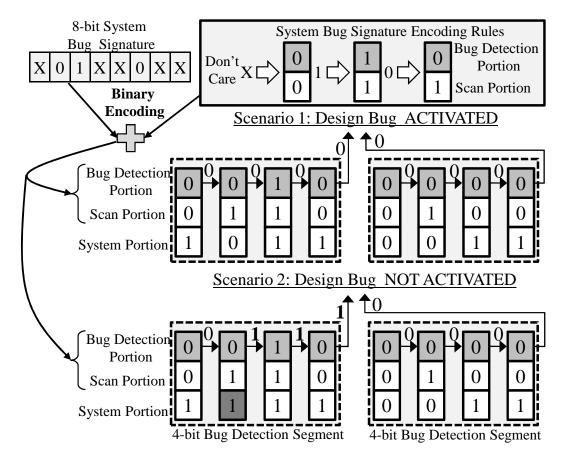

| 5.13 | Bug Detection Example:                                              | 106 |

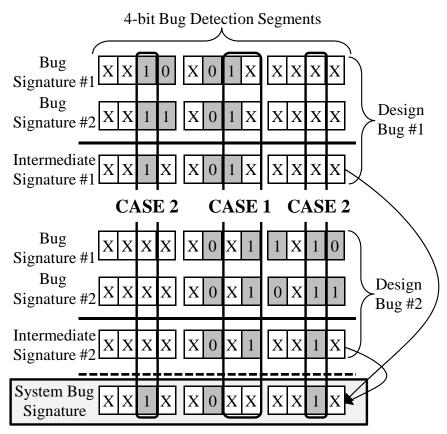

| 5.14 | Bug Signature Merging:                                              | 108 |

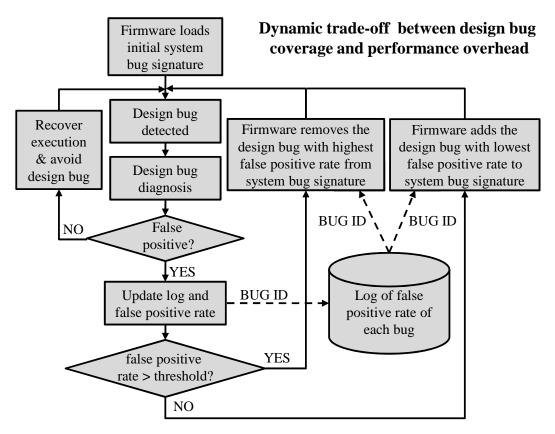

| 5.15 | Performance/Coverage Trade-off Tuning Algorithm:                    | 109 |

| 5.16 | ACE-Based Distributed Bug Detection:                                | 110 |

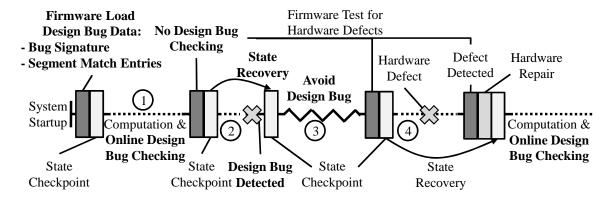

| 5.17 | ACE Framework for Online Design Bug and Defect Detection:           | 112 |

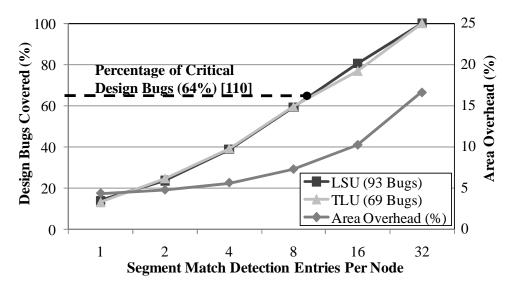

| 5.18 | Area Overhead Versus Design Bug Coverage:                           | 116 |

| 5.19 | Power Consumption Overhead:                                         | 117 |

| 5.20 | ACE Firmware for Post-Silicon Debugging:                            | 127 |

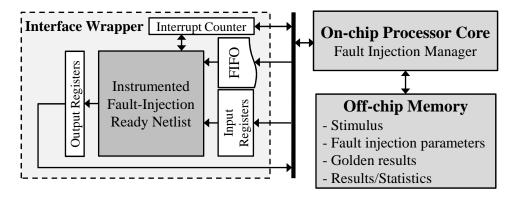

| 6.1  | Overview of the CrashTest Hardware Resiliency Analysis Framework: . | 135 |

| 6.2  | Logic Transformations - Bridge Fault:                               | 138 |

| 6.3  | Fault Injection Scan Chain:                                         | 138 |

| 6.4  | Logic Transformation for the Path-Delay Fault Model:                | 139 |

| 6.5  | FPGA-Based Fault Injection and Simulation:                          | 140 |

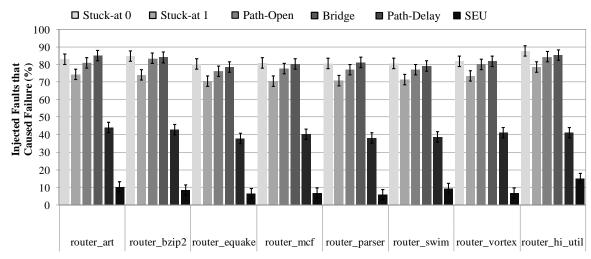

| 6.6  | Design Resiliency vs. Underlying Fault Model:                       | 146 |

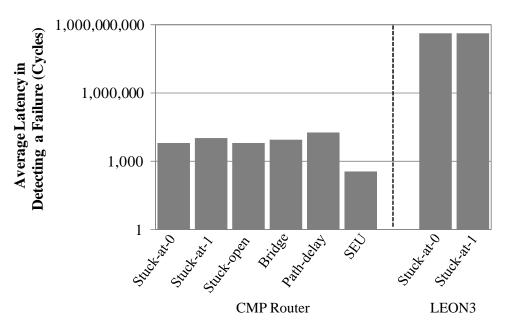

| 6.7  | Failure Detection Latency:                                          | 147 |

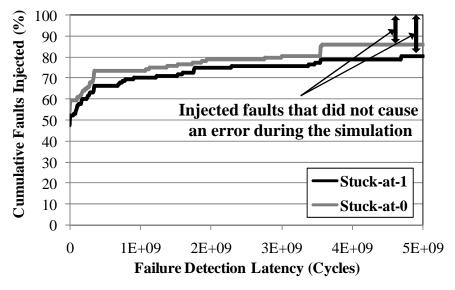

| 6.8  | Application-Level Detection Latency:                                | 147 |

## LIST OF TABLES

| <u>Table</u> |                                                        |     |

|--------------|--------------------------------------------------------|-----|

| 3.1          | Online Test Vectors:                                   | 38  |

| 3.2          | Area Overhead of the BulletProof Technique:            | 39  |

| 3.3          | Epoch Statistics for the Baseline Configuration:       | 40  |

| 3.4          | Comparing BulletProof To Related Work:                 | 43  |

| 4.1          | The ACE Instruction Set Extensions:                    | 51  |

| 4.2          | Algorithmic Flow of ACE-Based Testing:                 | 57  |

| 4.3          | Test Instructions Needed to Test Each Major Modules:   | 65  |

| 4.4          | Storage Requirements for Test Patterns and Responses:  | 66  |

| 4.5          | Full-Chip Distributed ACE Testing:                     | 67  |

| 4.6          | Performance and Memory Log Size Tradeoffs:             | 70  |

| 4.7          | Comparing The ACE Framework To Related Work:           | 82  |

| 5.1          | Logic Design Bug Statistics:                           | 100 |

| 5.2          | Power Consumption Estimation Methodology:              | 114 |

| 5.3          | Data and Control Signals in OpenSPARC T1:              | 115 |

| 5.4          | Overhead of the Extended ACE Framework:                | 117 |

| 5.5          | ACE Instruction Extensions for Post-Silicon Debugging: | 125 |

| 6.1          | Benchmark Designs:                                     | 142 |

| 6.2 | Statistical Confidence:         | 13 |

|-----|---------------------------------|----|

| 6.3 | Fault Injection Logic Overhead: | 44 |

| 6.4 | Fault Simulation Speed:         | 45 |

#### CHAPTER I

#### Introduction

For the last four decades, the semiconductor industry followed a trend known as the Moore's law [92]. Specifically, the Moore's law states that about every two years the transistor density of integrated circuits doubles. This means that about every two years, a microprocessor can have double the number of transistors in the same chip area. Since the release of the first commercial silicon-based microprocessor, almost forty years ago, the semiconductor industry was able to follow Moore's law due to the continued scaling of the silicon process technology that enables the fabrication of transistors with smaller dimensions. The major benefit of following the Moore's law is that with each scaling into a new silicon technology, every couple of years, the computer architects are offered smaller, faster, and cheaper transistors that makes possible the development of high-performance modern microprocessors. This technological achievement, over the last few decades, fueled the widespread adoption of microprocessor-based products in applications that touch every aspect of our life.

Currently, most mainstream consumer electronic devices are being produced with 65 and 45 nm silicon technology processes (that is the size of the smaller dimension in a transistor), and most microprocessor vendors are moving towards the adoption of the 32 nm silicon process technology. However, challenges in producing reliable components in these extremely dense technologies are growing, with many device experts warning that continued scaling will inevitably result in silicon technology generations that are much less reliable than the current ones [15, 123].

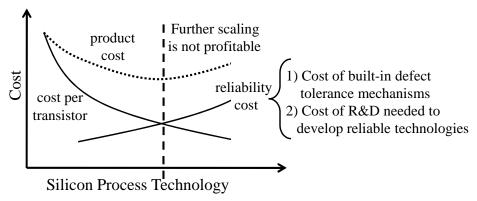

The cost due to the reliability challenges of future silicon process technologies is qualitatively illustrated in Figure 1.1. As shown in the graph, the primary benefit of technology scaling is the reduction in the cost per transistor with each new technology generation [44]. This trend makes the transition to newer technology generations more profitable to microprocessor vendors and it also enables the development of higher-performance microprocessors with more transistors. However, as the inherent reliability of new silicon

**Figure 1.1:** The Cost of Silicon Reliability: The graph shows the cost per transistor and the reliability cost for producing reliable microprocessors as the silicon process technology scales into future less reliable generations.

technologies wanes, we observe an increase in the reliability cost. The increase of the reliability cost can be due to either (i) the cost of shielding the microprocessors with built-in defect-tolerance techniques, or (ii) the cost of research and development (R&D) needed to develop new silicon process technologies that would allow the scaling to smaller feature sizes, but maintain the device reliability characteristics of the previous silicon process technologies. This reliability cost is contributing to the projected overall product cost. Experts warn that if this trend continues, eventually the silicon process technology scaling will reach a point where the reliability cost will overtake any benefits offered by smaller/cheaper transistors and any further scaling will be unprofitable for microprocessor manufacturing companies. This point is the minimum on the projected product cost curve shown in Figure 1.1.

To postpone or even eliminate this technology advancement barrier, the rate at which the reliability cost is increasing must be constrained. Technology experts suggest that this can be achieved by (i) building silicon-based semiconductor products out of unreliable components/technologies, and (ii) providing reliability to these products through online very low cost defect-tolerance techniques [17, 4]. The goal of this thesis is the exploration and evaluation of new, alternative, low-cost defect-tolerance solutions for microprocessor designs that will reduce the reliability cost induced by scaling into smaller and more unreliable silicon process technologies.

## 1.1 Why Does Silicon Fail?

#### 1.1.1 The Bathtub Curve

Since the dawn of silicon processing, it has been recognized that the failure probability distribution function of silicon-based semiconductor electronic products over time is

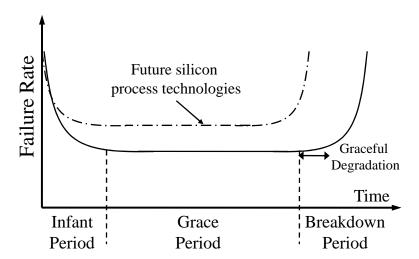

**Figure 1.2:** The Bathtub Curve: The bathtub curve indicates the qualitative trend of device failure rates for the population of a silicon-based semiconductor electronic product over time. The initial operational phase and the "aged-silicon" phase are characterized by much higher failure rates. The bathtub curves of future silicon process technologies are expected to shrink and exhibit higher device failure rates.

shaped like a bathtub. The bathtub-curve failure probability distribution function is characterized by three distinct phases as illustrated in Figure 1.2.

- Infant Period: The beginning of the product's lifetime is characterized by an initial high rate of device failures. These high failure rates are due to latent manufacturing defects that escape the initial product testing. These failures surface quickly when the manufacture-impaired devices are stressed as the products get into operation. However, the initial high failure rate declines rapidly as the remaining devices that pass the initial operating stress are more robust and less likely to fail.

- **Grace Period:** When early device failures are eliminated, the failure rate falls to a constant value where device failures occur sporadically due to the occasional breakdown of weak transistors or interconnect. It is highly desirable that the grace period will dominate a product's lifetime since this is the period where the product exhibits the lowest failure rates and the highest reliability.

- Breakdown Period: After the grace period, device failures start to occur with increasing frequency over time due to age-related wearout. Many devices will enter this phase at roughly the same time, creating an avalanche effect and a quick rise in device failure rates. However, since not all devices will fail at once, it is likely that a short graceful degradation period exists over which a few initial device failures begin to signal the onset of the device breakdown period.

As the silicon process technology scales into smaller transistor feature sizes, the bathtub curve of electronic products fabricated with these silicon process technologies is expected to shrink and exhibit higher failure rates. This will lead to products with shorter expected lifetimes. Furthermore, during their grace period, these products would be characterized by more frequent device failures.

The low-cost defect-tolerance solutions explored in this thesis are addressing the device failures that occur in the first two phases of the bathtub curve, namely, the infant period and the grace period. The objective of these mechanisms is to protect the microprocessor from occasional device failures that might occur early in its lifetime and tolerate the first device failures through the graceful degradation period. This strategy, offers to the user a time window to replace the defective part before the final breakdown.

#### 1.1.2 Silicon Failure Mechanisms

Throughout the lifetime of a silicon-based semiconductor electronic product, its silicon fabric is subject to a variety of failure mechanisms that can cause device failures (leading to the previously mentioned bathtub curve). As the transistor dimensions scale to smaller sizes, these silicon failure mechanisms get aggravated. The following discussion highlights the types of device failures that are expected to characterize future silicon technologies. Each of these failure mechanisms has received significant attention in the silicon process technology literature, and each has been identified as a growing concern for deepsubmicron silicon technologies. The interested reader can refer to [32, 103, 115, 125, 57] for a detailed treatment of these mechanisms.

Transistor Infant Mortality: Extreme device scaling exacerbates early transistor failures. Early transistor failures are caused by weak transistors that escape post-manufacturing validation tests. These weak transistors work initially, but they have dimensional and doping deficiencies that subject them to much higher stress than robust transistors. Quickly (within days to months) they will break down from stress and render the device unusable. Traditionally, early transistor failures have been reduced through aggressive burn-in testing, where, before being placed in the field, devices are subjected to high voltage and temperature testing, to accelerate the failure of weak transistors [23]. Those that survive the burn-in testing are likely to be robust devices, thereby ensuring a long product lifetime. However, in the deep-submicron silicon technologies, burn-in becomes less effective as devices are subject to thermal run-away effects, where increased temperature leads to increased leakage current, which in turn leads to even higher temperatures [87]. The end result is that aggressive burn-in of deep submicron silicon can destroy even robust devices. Manufacturers are forced to either sacrifice yield by deploying aggressive burn-in testing,

or experience more frequent early failures in the field by using less aggressive burn-in testing.

Manufacturing Defects that Escape Testing: Optical proximity effects, airborne impurities, and processing material defects can all lead to the manufacturing of faulty transistors and interconnect [103]. Moreover, deep-submicron gate oxides have become so thin that manufacturing variation can lead to currents penetrating the gate, rendering it unusable [115]. Even small amounts of manufacturing variation in the gate oxide could render the device unusable. The manufacturing defect problem is compounded by the immense complexity of current microprocessor designs. Design complexity makes it more difficult to test for defects during manufacturing. Vendors are forced to either spend more time with parts on the tester, which reduces profits by increasing time-to-market, or risk the possibility of untested defects escaping to the field. Moreover, in highly complex microprocessor designs, many defects are not testable without additional hardware support. As a result, even in today's manufacturing environment, untestable defects can escape testing and manifest themselves later on in the field during operation. All these problems are expected to worsen for future technologies and designs with smaller transistor feature sizes.

**Time-Dependent Wearout:** Technology scaling has adverse effects on the lifetime of transistor devices and interconnect, due to time-dependent wearout. There are three major failure modes for time-dependent wearout:

- *Electromigration*: Due to the momentum transfer between the current-carrying electrons and the host metal lattice, ions in the conductor can move in the direction of the electron current. This ion movement is called electromigration [32]. Gradually, this ion movement can cause clustered vacancies that can grow into voids. These voids can eventually grow until they block the current flow in the conductor. This leads to increased resistance and propagation delay, which in turn leads to possible device failure. Other effects of electromigration are fractures and shorts in the interconnect. The trend of increasing current densities in future technologies increases the severity of electromigration, leading to a higher probability of observing open and short-circuit nodes over time [41].

- *Gate Oxide Wear-out*: Thin gate oxides lead to additional failure modes as devices become subject to gate oxide wear-out (*e.g.*, Time Dependent Dielectric Breakdown, TDDB) [32]. Over time, gate oxides can break down and become conductive. If enough material in the gate breaks down, a conduction path can form from the transistor gate to the substrate, essentially shorting the transistor and rendering it useless

- [41, 57]. Fast clocks, high temperatures, and voltage scaling limitations are well-established architectural trends that aggravate this failure mode [125].

- Hot Carrier Degradation (HCD): As carriers move along the channel of a MOS-FET and experience impact ionization near the drain end of the device, it is possible to gain sufficient kinetic energy to be injected into the gate oxide [32]. This phenomenon is called Hot Carrier Injection. Hot carriers can degrade the gate dielectric, causing shifts in threshold voltage and eventually device failure. HCD is predicted to worsen for future thinner oxide and shorter channel lengths [57].

**Single-Event Upsets (SEU):** There is also a growing concern about providing protection from single-event upsets (also known as transient errors or soft errors) caused by charged particles, such as neutrons and alpha particles, that strike the bulk silicon portion of a die [151]. Although SEUs do not break the silicon, their effect is a logic glitch that can potentially corrupt combinational logic computation or state bits. While a variety of studies have been performed that demonstrate the unlikeliness of such events [144, 142], concerns remain in the architecture and circuit communities. This concern is fueled by the trends of reduced supply voltage and increased transistor budgets, both of which exacerbate a design's vulnerability to SEU.

**Process Variation:** Another reliability challenge designers are expected to face in future silicon technologies is the design uncertainty that is created by increasing process variations. Process variations result from device dimension and doping concentration variation that occur during silicon fabrication. These variations are of particular concern because their effects on devices are amplified as device dimensions shrink [104], resulting in structurally weak and poor performing devices. Designers are forced to deal with these variations by assuming worst-case device characteristics (usually, a 3-sigma variation from typical conditions), which leads to overly conservative designs.

In many systems today, these silicon failure mechanisms are assessed, and the necessary margins and guards are placed into the design to ensure it will meet the intended level of reliability, essentially employing a fault-avoidance design strategy. For example, most transistor failures (*e.g.*, gate-oxide breakdown) can be reduced by limiting voltage, temperature, and frequency [59]. While these approaches have served manufacturers well for many technology generations, many device experts agree that silicon reliability will begin to wane as silicon processing scales in deep-submicron technologies. As devices become subject to extreme process variation, particle-induced transient errors, and transistor wearout, it will likely no longer be possible to avoid these faults. Instead, computer designers will have to begin to directly address system reliability through fault-tolerant design techniques.

#### 1.2 Defect-Tolerant Microarchitectures

To address the concerns of silicon reliability, in this thesis we turn toward the development and application of defect-tolerant microarchitectures. In addition to their base functionality, defect-tolerant microarchitectures must support extra capabilities that will let the microprocessor to continue providing its intended service under the presence of silicon defects. A defect-tolerant microarchitecture, once it becomes aware of a defective part in the design, it needs to invoke a process that will reconfigure and repair the underlying hardware. After a silicon defect manifestation, the system also needs to be recovered from the defect's effects, including the restoration of any corrupted data or machine state. In order to address wearout-related silicon defects, or manufacturing defects that escape manufacturing testing, these capabilities need to be provided online while the product is operating in the field. Online defect tolerance is usually divided into the following four basic phases:

• Error Detection: Error detection is a vital capability for a defect-tolerant microarchitecture. Without error detection the system is unaware of the presence of any defects in the design and can lead to incorrect functionality that violates the system's specifications. Error detection can be accomplished by redundant computation, by error detection codes (*i.e.*, parity and error correction codes), or by checking the hardware for correct functionality. Unlike soft error detection, silicon defect detection through redundant computation requires the computation to be done on different hardware to avoid common mode failures.

Error detection can be performed either at the macro-level or at the micro-level. Macro-level error detection is usually applied at the microprocessor scope by techniques like dual-modular redundancy and execution lock-stepping [118] that monitor the output of the microprocessor for errors. Micro-level error detection is usually applied at microprocessor subcomponents (*e.g.*, functional units, or the register file) by techniques like on-line built-in-self-test (BIST), residue checkers, or error detection codes.

Since execution errors can be caused by both silicon defects and transients faults (due to neutron strikes, electrical noise *etc.*), error detection mechanisms are often required to distinguish the source of the error in order to invoke the necessary repair/recovery process. For example, restoring the processor's state and restarting execution is often adequate to recover from the effects of a transient fault. However, recovering from a permanent silicon defect is a more tedious process involving

defect diagnosis and hardware repair/reconfiguration. The ability of an error detection mechanism to accurately distinguish the source of an execution error is very important, since incorrect decision could disable or reconfigure functionally correct hardware resources that have been victims of transient faults and lead to impaired system functionality and/or performance.

- Online Defect Diagnosis: After an execution error detection, if a permanent silicon defect is indicated as the source of the error, an online defect diagnosis process is triggered in order to identify the defective component in the microprocessor design [20, 111]. During this process, the system needs to stall execution making online defect diagnosis a performance-critical operation.

- Hardware Repair & Reconfiguration: The reconfiguration and repair of hardware resources is an essential phase of defect tolerance for repairing a defective microprocessor and enabling the proper system functionality. Hardware repair can be handled in many ways, including disabling, ignoring, or replacing the defective hardware component. When there is enough hardware resource redundancy in the system, the hardware repair process can exploit this resource redundancy and simply disable the defective component. Alternatively, if there is enough redundant computation in the system (like there is in systems that employ triple-modular redundancy) the hardware repair may just be the ignorance of the defective component. Finally, when the system employs hardware sparing, the repair process replaces the defective component with a spare one.

- System Recovery: The final phase of online defect tolerance is the system recovery. After hardware repair, the system needs to restore any data and machine state that possibly got corrupted by the failure. System recovery essentially makes the manifestation of a silicon defect or a transient fault transparent to the application execution and provides correct system functionality to the user.

## 1.3 The Reliable System Design Space

When designing a defect-tolerant microarchitecture, there are two important design factors that need to be taken into consideration. The first, is the type of device failures that will be covered by the defect-tolerant microarchitecture. As discussed in the previous section, the types of device failures range from transient faults (SEUs) due to energetic particle strikes [151] and electrical noise [138], to permanent silicon wearout-related defects caused by electro-migration [50], stress-migration [59], and dielectric breakdown [147].

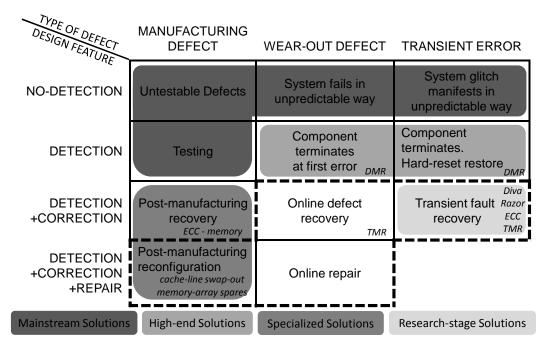

**Figure 1.3: Reliable System Design Space:** The diagram shows a map of device-level fault types in a digital system (horizontal axis) vs. protection techniques against these faults (vertical axis). This thesis addresses the problems/solutions in the dash bordered area of the map.

The second design consideration, is the degree to which the system will be protected from those device failures. Design solutions range from ignoring any possible device failures (as is done in many systems today), to detecting and reporting device failures, to detecting and correcting device failures, and finally failure correction with repair capabilities. This results to a rich design space to be considered, as illustrated in Figure 1.3. Specifically, Figure 1.3 illustrates the current fault-tolerant design space with the horizontal axis listing the type of device failure that systems might experience and the vertical axis listing the design solutions to deal with these device failures. Note that in this design space, the final two design solutions are the only solutions that can address permanent silicon defects, with the final solution being the only approach that maintains efficient operation after encountering a silicon defect.

In recent years, industry designers and academics have paid significant attention to building resistance to transient faults into their designs. A number of recent publications have suggested that transient faults, due to energetic particles in particular, will grow in future technologies [15, 93]. A variety of techniques have emerged to provide a capability to detect and correct these type of faults in storage, including parity or error correction codes (ECC) [117], and logic, including dual or triple-modular spatial redundancy [117] or time-redundant computation [31, 118] or checkers [68, 143].

In contrast, little attention has been paid into incorporating design tolerance for permanent silicon defects, such as transistor and interconnect wearout. The typical approach used today is to reduce the likelihood of encountering permanent silicon defects through post-manufacturing burn-in, a process that accelerates the aging process as devices are subjected to elevated temperature and voltage [147]. The burn-in process accelerates the failure of weak transistors, ensuring that, after burn-in, devices still working are composed of robust transistors. Additionally, many computer vendors provide the ability to repair faulty memory and cache cells, via the inclusion of spare storage cells [121]. Recently, academics have begun to extend these techniques to support sparing for additional on-chip memory resources such as branch predictors [19] and registers [114].

Currently, in the reliable system design space there are no low-cost defect-tolerance techniques that can provide effective mechanisms to online protect a microprocessor design from silicon defects, either those that occur during manufacturing or those that occur when the device is in operation in the field. This thesis will attempt to bridge this gap in the reliable system design space and explore defect-tolerance solutions that would cover the dash bordered area of the reliable system design space map of Figure 1.3.

#### 1.4 Contributions of This Thesis

Traditional approaches to defect-tolerant design saddle a system with costly redundant components that continuously verify the integrity of all computation. Examples of such techniques are Dual Modular Redundancy (DMR) [117], and lockstep systems [64]. These techniques detect silicon defects by validating the execution through independent redundant computation. However, independent redundant computation requires significant hardware cost in terms of silicon area (100% extra hardware in the case of DMR and lockstep systems). Furthermore, continuous checking consumes significant energy and requires part of the microprocessor's power budget to be dedicated to it.

A major contribution of this thesis is a paradigm shift in the way that silicon defects can be detected in defect-tolerant microarchitectures. Rather than *continuously* checking computation for execution errors, the new approach is *periodically* checking the integrity of the underlying hardware without the need of redundant execution. This periodic hardware checking can be done through area-frugal, distributed, online checkers. This new defect-tolerance paradigm is relying on checkpointing and recovery mechanisms that provide computational epochs and a substrate for speculative unchecked execution. At the end of each computational epoch, the hardware is checked by on-chip testers. If the hardware tests succeed, the results produced during the epoch are committed and execution proceeds

to the next computational epoch. Otherwise, the system is deemed defective and system repair and recovery are required. A detailed prototype implementation of this approach, called *BulletProof*, is described and evaluated in Chapter III.

Another key requirement for a successful defect-tolerance solution is to have an ultralow overhead in terms of silicon area, thus driving the overall product reliability cost low. Even though periodic hardware checking eliminates the high area cost of hardware replication required for redundant computation, it still requires a way to periodically check the underlying hardware. This could mean the addition of on-chip checkers and the bearing of their extra hardware cost, as we will observe later in Chapter III in the BulletProof prototype.

The amount of adaptivity and flexibility that defect-tolerance solutions provide, once the microprocessor is shipped and operating at the customer side, is also a central concern in their design. Flexible defect-tolerance solutions that can be modified, upgraded, and tuned in the field are very desirable. Today, many defect-tolerance techniques bind specific testing approaches into silicon, making it impossible to change the testing strategy after the microprocessor in deployed in the field.

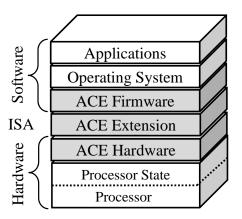

To address both of these requirements and (i) offer low-overhead hardware checkers for periodic checking, and (ii) provide a flexible defect-tolerance mechanism that can be modified, adapted, and tuned to the needs of the microprocessor while it is operating in the field, we developed a new software-based defect-tolerance approach. The novelty of this new defect-tolerance approach is that it shifts the silicon defect detection and diagnosis process from on-chip hardware checkers to software. In this software-based defect-tolerance technique, called the Access-Control Extension (ACE) framework, the hardware provides the necessary substrate to facilitate hardware checking and the software makes use of this substrate to perform the hardware checking. The software nature of this approach offers a low area overhead mechanism for periodic hardware checking and inherently provides a flexible way for upgrading, modifying, and tuning the mechanism in the field. The ACE framework is described and evaluated in detail in Chapter IV.

Another challenge in the domain of defect tolerance for microprocessor designs is to overcome the expense of defect-tolerance mechanisms, which is necessary before they can be deployed in commercial mainstream microprocessor designs. One solution to this challenge is to add value to the defect-tolerance mechanisms by utilizing their hardware resources for more than just defect tolerance. To this extend, this thesis makes the case that the hardware resources used to implement a defect-tolerance solution can also be utilized for other applications. Specifically, as it will be demonstrated in Chapter V, the hardware resources of the ACE framework can be extended to other important applications such

as online design bug detection, a post-silicon debugging tool, and improving hardware manufacturing testing. This approach, adds value to defect-tolerance solutions and it can ease their early adoption in future generation microprocessors.

The last major contribution of this thesis is the development of CrashTest, a highfidelity hardware resiliency analysis infrastructure on an FPGA-based emulation platform. Hardware resiliency analysis tools are used to assess the threats and the reliability requirements of a hardware design. During this process, faults are injected in the design and their impact on the behavior of the design is analyzed. After the fault injection and analysis process, the hardware design can be characterized for its reliability standards. However, the accurate assessment of the robustness of a hardware design is not a trivial process. Accurately modeling the effects of low-level silicon failure mechanisms and monitoring their impact up to the software level places conflicting requirements to the resiliency analysis tools. On the one hand, if low-level detail models of the hardware design are used to faithfully model the silicon failure mechanisms, the simulation performance is very poor and it limits the fault analysis from observing the impact of faults at the software level. On the other hand, if high-level architectural models of the hardware design are used to improve the simulation performance of the tool, the fidelity of the tool is in jeopardy since the effects of silicon failure mechanisms cannot be accurately modeled in high-level architectural models. In Chapter VI, the CrashTest hardware resiliency analysis tool makes an attempt to solve this conundrum by performing fault injection campaigns at the gatelevel and accelerating the fault analysis process using an FPGA-based hardware emulation platform to achieve both accuracy and performance.

#### 1.5 Thesis Outline

The remainder of this thesis is organized as follows:

Chapter II gives an overview of previous work done in the area of defect-tolerant microarchitecture design. It first highlights the traditional defect-tolerance techniques, followed by a discussion of their shortcomings. Chapter II also covers recent related work presented in the research literature.

Chapter III presents the *BulletProof* pipeline, a microprocessor defect-tolerance solution that employs periodic hardware checking coupled with microarchitectural checkpointing to provide low-cost protection from silicon defects. A description of the BulletProof physical-level prototype is provided, as well as a coverage and performance analysis in the context of a low-cost embedded VLIW microprocessor.

Chapter IV introduces the Access-Control Extension (ACE) framework, a software-based technique for online low-cost defect detection and diagnosis. The ACE framework

effectively moves the hardware checking process from the hardware to the software level. The ACE framework is evaluated on a commercial chip-multiprocessor system and experimental results and analysis are presented.

Chapter V extends the ACE framework to other applications. Specifically, it demonstrates that the ACE framework hardware resources can be extended and used for online design bug detection, as a post-silicon debugging tool, and for improving hardware manufacturing testing. Chapter V also provides an RTL-level design bug analysis of a modern commercial microprocessor that motivates the potential benefit of extending the ACE framework into an online design bug analysis mechanism. The chapter concludes with the experimental evaluation of the extended ACE framework.

Chapter VI presents *CrashTest*, an FPGA-based hardware resiliency analysis framework. The chapter starts with a high level overview of the CrashTest framework. Then, the gate-level fault injection methodology employed by the framework is described. The chapter continuous with the details on how CrashTest is implemented using a commercial FPGA. The chapter concludes with the experimental evaluation of the framework's performance and its effectiveness.

Finally, Chapter VII gives conclusions and discusses directions for future work.

#### **CHAPTER II**

## Traditional Techniques and Recent Research Approaches for Defect-Tolerant Design

From the early adoption of computer systems, reliability was, and still is, one of the most important requirements in the design of computer systems. Computer applications ranging from life-critical aviation/ground transportation systems and medical systems, to business-critical applications found in the financial sector, to mission-critical applications like outer space exploration programs, they all place high hardware reliability demands to the computing systems. Furthermore, in applications such as outer space exploration, the computing systems are expected to operate in adversary environments and conditions that are very different from the ones here at Earth, such as very high rates of neutron strikes that cause transient faults.

These reliability requirements and challenges throttled a high research interest in reliable computer system design. This chapter, provides a brief overview of the traditional defect-tolerance techniques employed in high-end computing systems today and discusses their shortcomings. It also highlights the related work that was recently published in the research literature.

The scope of this chapter is to present the previous work that is more relevant to the general topic of this thesis. Other previous work that is related with the specific techniques described in each of the remaining chapters of this thesis is presented in each chapter respectively.

## 2.1 Traditional Defect-Tolerance Techniques

One of the first defect-tolerance approaches used to protect high-end computer systems is dual modular redundancy. Dual modular redundancy, employs spatial redundancy in the form of two microprocessors operating in lockstep. The output of the two microprocessors

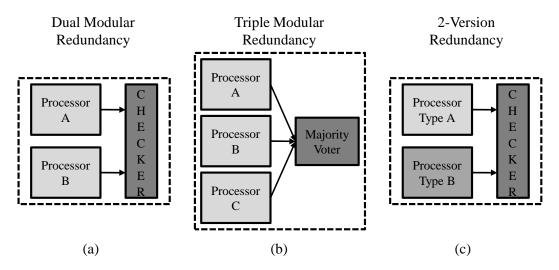

**Figure 2.1:** Traditional Defect-Tolerance Techniques: Part (a) shows a dual redundancy system where two identical processors are operating in lockstep and checked by an external checker. Part (b) shows a triple modular redundancy system where errors are both detected and corrected. Part (c) shows a 2-version redundancy system where two different processors, with the same specifications, are running in lockstep. This approach avoids common mode failures and also detects design bugs.

is checked by an external checker, as shown in Figure 2.1(a). If any deviation at the output of the two microprocessors is detected, a system error is flagged. An early example of a system that employed this approach was Tandem's NonStop system [64].

One shortcoming of dual modular redundancy is that although it can effectively detect single defects in the design, once a defect is detected, it cannot detect which of the two microprocessors is the defective one and continue operating with the other one. Therefore, once a defect is detected, the system halts operation and it requires repair. A way to address this limitation is by adding more hardware redundancy to the system, in the form of triple modular redundancy [117]. In triple modular redundancy, three identical microprocessors are used with an additional majority voter, as shown in Figure 2.1(b). If one of the microprocessors fail, its output is outvoted by the other two microprocessors providing forward system recovery. The system then downgrades into a dual modular redundancy system with the remaining two defect-free microprocessors.

Another similar approach to dual and triple modular redundancy is N-version redundancy. With N-version redundancy, instead of just replicating the microprocessors N times as in modular redundancy, N different microprocessors, with the same specifications, are designed by N different design teams or companies. An example of a 2-version redundancy system is shown in Figure 2.1(c). The N-version redundancy has the additional advantage over modular redundancy of detecting not only hardware failures, but also design bugs and avoiding common mode failures.

The advantage of these hardware redundancy techniques is that they are not intrusive in the microprocessor design and they can be applied to build defect-tolerant computer systems using over-the-shelf processors. Also, these techniques cover uniformly the whole microprocessor and can detect errors caused by any defective structure in the processor. However, the major shortcoming of these techniques is that they add extra hardware into the system leading to significant area and power overheads.

Another traditional defect-tolerance technique used to protect memories, buses, or other microprocessor array structures (*e.g.*, register file) are parity and error correction codes (ECC) [117]. ECC and parity bits provide a lower overhead solution for dataholding hardware structures than modular redundancy. Parity bits are more similar to dual modular redundancy where errors can only be detected but not corrected. On the other hand, ECC resembles triple modular redundancy providing both error detection and forward recovery as the ECC computation masks and corrects the faulty value of a bit. The overhead of parity and ECC bits is relatively low compared to modular redundancy techniques and it comes from the extra storage overhead and the extra logic needed for their computation. However, ECC and parity bits are intrusive in the design of the microprocessor<sup>1</sup> and protect only a limited part of the processor.

In the context of online testing of processors, various concurrent error detection schemes have been proposed [89]. Most schemes incorporate a checker that compares the expected behavior with that of the unit under test. Another solution proposed in the direction of online testing are Berger codes [12] which can detect all unidirectional errors, and Bose-Lin codes [16] which can detect t unidirectional errors (known as t-EC). These codes are suitable for the protection of circuits that are skewed towards one of the two logic values (logic 0 or 1). However, the use of these codes for online testing of datapaths is not trivial as they impose constraints on the way the logic block is designed such that only unidirectional faults occur. As with the parity and ECC bits, concurrent error detection schemes and the Berger codes are intrusive in the design of the microprocessor and protect only some parts of the processor design.

## 2.2 Fault Avoidance Strategies

Today, the defect-tolerance techniques presented in the previous section are only used in high-end systems running critical applications. In contrast, the microprocessors used in most mainstream desktop and laptop computers and embedded systems employ a fault-

<sup>&</sup>lt;sup>1</sup>This means that they need changes at the design phase of the processor, unlike modular redundancy techniques that can be applied to over-the-shelf processors.

avoidance design strategy to achieve their projected failure rate targets. Microprocessor manufacturing companies assess the sources of possible failures, and they place in the design the necessary guards and preventive measures to ensure that their exposure to failing scenarios does not compromise the overall reliability target. The incident of silicon failure mechanism, such as wearout-related silicon defects and transient faults, is proportional to supply voltage, circuit temperature, and transistor activity factors [59], thus, reliability in these microprocessors is typically ensured through the use of safety margins inserted into the clock period and limits on the maximum supply voltage.

If the microprocessor failure rate resulting from ignoring the occurrence of the faults falls within the targeted reliability standards, the sole use of fault avoidance techniques is adequate to provide a relatively reliable population of products. Although previous and current generations of silicon process technologies exhibit sufficiently low device failure rates that silicon defect could be completely ignored, this approach is expected to be ineffective for future silicon technologies where device wear-out, untestable defects, and early transistor failures will increase the in-the-field (*i.e.*, during operation) microprocessor defect rates and necessitate stronger measures of protection.

#### 2.3 Defect-Tolerance Techniques in Research Literature

To date, only a few efforts have explored techniques to provide low-cost defect tolerance to microprocessor designs. This section, provides a brief overview of the previous research work that is more generic to the subject of microprocessor defect tolerance. Previous research works that are more relevant to the specific techniques explored in the remaining chapters of this thesis are described and discussed in those chapters respectively. Also, some of the research work discussed in this section was concurrently developed with the work presented in this thesis.

Defect Tolerance Through Continuous Execution Checking: DIVA, is an online checker component inserted into the retirement stage of a microprocessor pipeline that continuously validates the computation, communication, and control exercised in a complex microprocessor core [6, 143]. The approach unifies all forms of permanent and transient faults, making it capable of detecting computations error due to design bugs, soft errors, and permanent silicon defects. However, a limitation of DIVA is that it does not diagnose the root problem in order to repair the underlying hardware and prevent the errors from occurring again.

To address this limitation, Bower *et al.*, in [20], propose a fault-tolerant microprocessor design that uses DIVA checkers for system-level error detection coupled with a mechanism

for diagnosing silicon defects by tracking the instruction occupancy through the microprocessor's pipeline. After diagnosing a silicon defect, the microprocessor reconfigures (*i.e.*, disables) the defective part and continues operation at a gracefully degraded level of performance.

More recently, Meixner *et al.* presented Argus [85], an error detection technique for simple processor cores. The Argus technique continuously checks invariants to detect execution errors. Specifically, Argus, uses run-time invariant checking to detect errors in four fundamental tasks: the control flow, the dataflow, computation, and memory access. The Argus technique provides error detection for errors caused by both permanent silicon defects and transient faults and offers an alternative low-cost defect-tolerance approach when compared to the traditional defect-tolerance approaches.

Hardware Testing and Built-In-Self-Test: After chip fabrication, microprocessor chips are tested in order to screen out parts with defective or weak devices. Today, most complex microprocessor designs use scan chains as the fundamental design for test (DFT) methodology. During hardware testing, the design's scan chains are driven by external automatic test equipment (ATE) that applies pre-generated test patterns to check the chip under test [23]. Every single microprocessor chip has to go through this testing process multiple times at different voltage, temperature, and frequency levels. This makes the manufacturing testing cost for each chip to be as high as 25-30% of the total microprocessor manufacturing cost [45]. An alternative approach that eliminates the need of external equipment to drive the hardware testing is Built-In-Self-Test (BIST) techniques [23]. BIST techniques use specialized circuitry to generate test patterns and validate the test responses on the chip without the need of any communication with external devices. The way BIST techniques generate test patterns on the chip is either by the use of pseudo-random test pattern generators, or by storing previously generated test vectors in on-chip memories.

**Silicon Defect Prediction:** Blome *et al.* [14], proposed an online technique that detects the performance degradation caused by wearout over time in order to anticipate failures. In particular, the proposed technique leverages the progression of wearout over time and provides a low-overhead self-calibrating hardware structure that identifies increasing propagation delay, which is symptomatic of many forms of wearout, to forecast the failure of microarchitectural structures. Specifically, they propose the implementation of an online latency sampling unit that is capable of sampling and filtering by statistical analysis the propagation latencies of signals to identify significant changes in the latency of a given microarchitectural structure and predict a device failure.

In [129], Sylvester *et al.* propose in the context of the ElastIC architecture the use of in-situ sensors in combination with reliability and power models to predict the lifetime

and wearout of the underlying hardware. This enables the dynamic tradeoff of performance with longer lifetime and reliability using dynamic voltage scaling techniques. A similar approach was employed by Srinivasan *et al.* in [124] where microarchitectural components are swapped by spare ones based on the prediction of their failure. The failure time of microarchitectural components is predicted by monitoring the dynamic activity and temperature of the microarchitectural components in combination with the analytical reliability models proposed in [122].

Resource Redundancy for Hardware Repair & Reconfiguration: Shivakumar *et al.* [114], proposed the use of hardware redundancy and reconfiguration to improve the yield and increase the defect tolerance of future microprocessors. They also suggest that the use of hardware redundancy should not be limited only to memories but that inherent resource redundancy, that is abundant in modern microprocessors, should be exploited in both single-core and multi-core processors. Three primary types of inherent redundancy that can potentially be used in a microprocessor were identified: component level redundancy (replicated functional units *etc.*), array redundancy (spare rows and columns in bit arrays), and dynamic queue redundancy (spare queue entries).

In [42], Gupta *et al.* presented StageNet, a highly reconfigurable multicore architecture. StageNet is a reconfigurable multicore computing substrate designed as a network of pipeline stages, rather than isolated cores in a chip-multicore processor. The StageNet network is formed by replacing the direct connections at each pipeline stage boundary by a crossbar switch. Within the StageNet network, pipeline stages can be selected dynamically from the pool of available stages to form logical processing cores, thus permanent silicon failures can be easily isolated by adaptively routing around defective stages. In essence, the StageNet substrate can effectively exploit the natural resource redundancy of moder multicore processors and reconfigure the hardware resources around a defective component to repair a microprocessor design.

Aggarwal *et al.* [3] introduced the notion of configurable isolation for low-level fault containment and component reconfiguration through cost-effective modifications to commodity designs. Specifically, the proposed mechanism employs dynamic repartitioning of a chip-multiprocessor's hardware resources into multiple fault zones. Silicon defects are detected at the fault-zone granularity and once a defect is detected, the defective component is disabled and the remaining hardware resources are dynamically repartitioned into new fault zones. Furthermore, the power budget of the defective disabled components is re-assigned to the remaining operating components. This enables the voltage/frequency upscaling of the remaining hardware resources in an attempt to mitigate the performance loss due to the disabled components.

Bower *et al.* [19] proposed a hardware mechanism for self-repairing array structures to provide defect detection and repair capabilities for microprocessor array structures such as the reorder buffer and branch history table. The proposed mechanism detects silicon defects by employing dedicated "check rows". Every time an entry is written to the array structure, the same data is also written into a check row. Then, both locations are read out and their values are compared to detect defective rows. To repair defective arrays, the mechanism exploits the inherent resource redundancy of these structures and redirects any accesses to defective rows to other functionally correct rows.

Finally, an algorithmic approach for dynamic hardware reconfiguration and system repair from silicon defects was proposed recently by Fick *et al.* in [34]. Specifically, the work presented in [34] proposes a distributed routing algorithm for networks on chip that allows a network to reconfigure around defective components. The proposed algorithm is able to overcome large number of silicon defects by running in lockstep at each network router and collectively reconfiguring the network's routing tables. It was demonstrated that due to the high hardware resource redundancy of networks on chip, the dynamic reconfiguration algorithm could provide a 99.99% reliability to the on-chip network even after 10% of its interconnect links were defective.

#### **CHAPTER III**

## Defect Tolerance Through Periodic Hardware Checking -The BulletProof Pipeline

This chapter introduces *BulletProof*, an ultra low-cost defect-tolerance mechanism to protect a microprocessor pipeline and on-chip memory system from permanent silicon defects. The traditional approach to defect tolerance saddles a system with redundant components that continuously monitor the microprocessor's execution for errors through redundant computation. This redundant computation leads to significant area and power overheads and constraints the microprocessor's resource budget. The BulletProof technique shifts the traditional defect-tolerance paradigm from continuous checking for execution errors (through redundant computation) to periodic online hardware checking. Specifically, it combines area-frugal periodic online hardware testing with microarchitectural checkpointing to provide the same guarantees of reliability as traditional defect-tolerance techniques, but at a much lower cost.

This approach, utilizes a microarchitectural checkpointing mechanism to create coarse-grained epochs of execution, during which a distributed online hardware testing mechanisms verify the integrity of the underlying hardware. If the hardware is deemed unbroken at the end of a computation epoch, the epoch's speculative computation is allowed to retire to a non-speculative system state, otherwise, the system is rolled back to the beginning of the epoch, and the last known-good system state is restored. At recovery, the system is reconfigured to disable any defective components. This technique relies on the natural resource redundancy that is abundant in ILP-style microprocessors combined with a small amount of carefully-placed control logic redundancy to repair the system such that it can operate in a degraded performance mode. Once repaired, the user can decide whether to replace the system or tolerate the degraded performance. The BulletProof technique also employs a double-sampling flip-flop design to protect the pipeline from transient faults and latch defects.

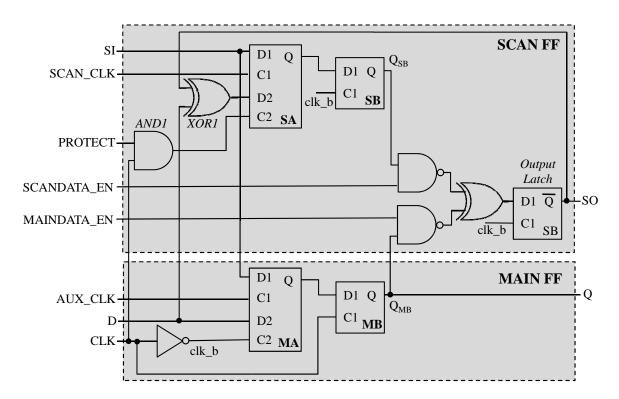

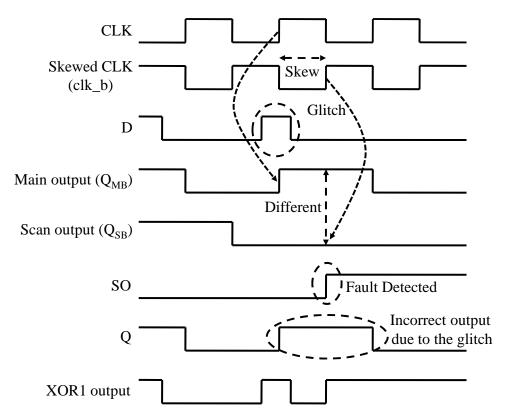

Section 3.1, describes in detail the implementation of the BulletProof defect-tolerance technique, including a detailed coverage of the distributed checkers used to perform the periodic hardware testing. It also explains how the technique employs microarchitectural checkpointing to provide speculative computational epochs and system recovery, how the BulletProof pipeline is repaired, and how input/output operations are handled by the BulletProof mechanism. Next, Section 3.2 describes in detail the double-sampling flip-flop design used to protect the BulletProof pipeline from transient faults. Section 3.3 evaluates the BulletProof mechanism using both detailed circuit-level and architectural simulation. The simulation testbed used for the evaluation of the BulletProof mechanism is based on a low-cost embedded VLIW processor. Finally, Section 3.4 discusses previous research work that is related to the BulletProof technique, and Section 3.5 summarizes the work presented in this chapter.

# 3.1 Online Periodic Hardware Checking

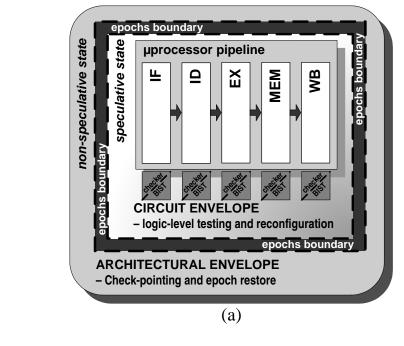

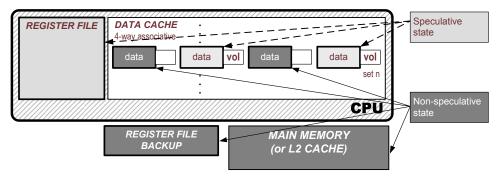

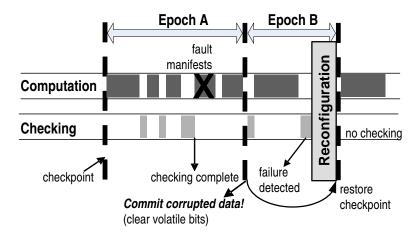

Figure 3.1 illustrates the high-level system architecture of the BulletProof defect-tolerance approach, and it shows a timeline of execution that demonstrates its operation. At the base of the proposed approach is a microarchitectural checkpoint and recovery mechanism that creates *computational epochs*. A computational epoch is a protected region of computation, typically at least 1000's of cycles in length, during which the creation of any errant computation, in this case due to the encountering of a defective device, can be undone by rolling the computation back to the beginning of the computational epoch.

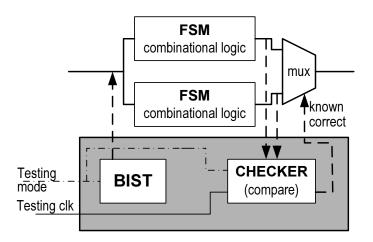

During a computational epoch, online checkers perform hardware built-in-self-test routines in the background, checking the integrity of all system hardware components. Ideally, this hardware checking will occur while functional units, decoders, and other microprocessor components are idle, as is often the case in a processor with parallel resources.

By the end of a computational epoch, there are three possible scenarios that the Bullet-Proof mechanism will need to handle. The first scenario (shown in the first computational epoch of Figure 3.1(b) is when the checking completes before the end of the computational epoch. In this scenario, the hardware is known to be free of defects, thus, the results of the computational epoch are known to be free of defect-induced errors, and it can be safely retired to non-speculative system storage.

In the second scenario (shown in the second epoch of Figure 3.1(b), the computational epoch ends before the online testing infrastructure has completed testing all of the underlying hardware components. This scenario can occur because the microarchitectural