# High-performance Placement and Routing for the Nanometer Scale

by Jarrod Alexander Roy

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in The University of Michigan 2009

#### **Doctoral Committee:**

Associate Professor Igor L. Markov, Chair Professor David Blaauw Professor John P. Hayes Associate Professor Kevin J. Compton Associate Professor Dennis M. Sylvester ©  $\frac{\text{Jarrod Alexander Roy}}{\text{All Rights Reserved}}$  2009

To my family and friends

#### **ACKNOWLEDGEMENTS**

I am grateful to my advisor, Professor Igor Markov, for taking a chance on me when I was a Master's student and supporting me throughout my Ph.D. He has been an unending source of ideas and advice in research and insightful comments when writing all of our papers. I am also thankful to my thesis committee members Professor John Hayes, Professor Kevin Compton, Professor David Blaauw and Professor Dennis Sylvester for reminding me to always think about solving difficult problems from both theoretical and practical points of view. I'd also like to thank Professor Farinaz Koushanfar for her collaboration on our work on hardware piracy and intellectual property protection.

I'd like to thank David Papa for all of our debates on subjects ranging from proper programming practice to finance and for convincing me to get active and lose weight. I want to thank Jin Hu for taking up and improving upon my global routing work. I would be remiss if I did not thank my group at IBM Austin Research Lab who helped with the work I needed to complete my thesis including Charles Alpert, Gi-Joon Nam, Natarajan Viswanathan, Michael Moffitt, Cliff Sze, Zhuo Li and Nancy Zhou. I'm also appreciative of the inordinate hours spent with Robert Barry, George Viamontes, Aaron Ng, Jeff Hao, David Papa and Jin Hu playing video games (WoW, Diablo II, Guild Wars, Guitar Hero, Rock Band, ...) which helped to preserve my sanity. I would like to thank all of the other brilliant people at the University of Michigan that I was fortunate enough to befriend including Kai-Hui Chang, Saurabh Adya, Smita Krishnaswamy, James Lu, Hector Garcia, Andrew DeOrio, Ilya Wagner, Joseph Greathouse and Stephen Plaza. I'd also like to

thank my friends from Carnegie Mellon University who have kept in touch over the years including Ben Burrington, Marc Giogilo and Doug Houston.

Without my family, none of this could have been possible. I thank my sister, Jinger, for moving to Michigan for a few months, convincing me to adopt a cat and keeping me cultured. Lastly and far from least, I'd like to thank my parents, Julius and Diane, for bringing me to early morning MathCounts practices before school; buying my first 80386 which introduced me to the world of computing; letting me go off to college and graduate school 1000 miles from home; moving up to Michigan for a year; and always being there for me.

#### **PREFACE**

Modern semiconductor manufacturing facilitates single-chip electronic systems that only five years ago required ten to twenty chips. Naturally, design complexity has grown within this period. In contrast to this growth, it is becoming common in the industry to limit design team size which places a heavier burden on design automation tools.

Our work identifies new objectives, constraints and concerns in the physical design of systems-on-chip, and develops new computational techniques to address them. In addition to faster and more relevant design optimizations, we demonstrate that traditional design flows based on "separation of concerns" produce unnecessarily suboptimal layouts. We develop new integrated optimizations that streamline traditional chains of loosely-linked design tools. In particular, we bridge the gap between mixed-size placement and routing by updating the objective of global and detail placement to a more accurate estimate of routed wirelength. To this we add sophisticated whitespace allocation, and the combination provides increased routability, faster routing, shorter routed wirelength, and the best via counts of published techniques. To further improve post-routing design metrics, we present new global routing techniques based on Discrete Lagrange Multipliers (DLM) which produce the best routed wirelength results on recent benchmarks. Our work culminates in the integration of our routing techniques within an incremental placement flow to improve detailed routing solutions, shrink die sizes and reduce total chip cost.

Not only do our techniques improve the quality and cost of designs, but also simplify design automation software implementation in many cases. Ultimately, we reduce the time needed for design closure through improved tool fidelity and the use of our incremental techniques for placement and routing.

# TABLE OF CONTENTS

| DEDICAT           | ION .                   | i                                                    |

|-------------------|-------------------------|------------------------------------------------------|

| ACKNOW            | LEDGI                   | EMENTS i                                             |

| PREFACE           |                         |                                                      |

| LIST OF F         | IGURI                   | ES                                                   |

| LIST OF T         | TABLES                  | S                                                    |

| PART I            | Backgro                 | ound                                                 |

| Chapte            | r I. VI                 | SI Physical Design at the Nanometer Scale            |

| 1.1<br>1.2<br>1.3 | Our A                   | enges in VLSI Physical Design                        |

| Chapte            | r II. St                | eate of the Art in Partitioning-based VLSI Placement |

| 2.1               | Top-do 2.1.1            | own Partitioning Framework for Placement             |

|                   | 2.1.2<br>2.1.3<br>2.1.4 | Bipartitioning versus Multi-way Partitioning         |

| 2.2               |                         | cements to the Min-cut Framework                     |

| 2.2               | 2.2.3<br>2.2.4          | Analytical Constraint Generation                     |

| 2.3               | 2.3.1<br>2.3.2          | Floorplacement                                       |

|                   | 2.3.3<br>2.3.4<br>2.3.5 | Fractional Cut for Mixed-size Placement              |

| 2.4        | State-of-the-art Min-cut Placers                | 37         |

|------------|-------------------------------------------------|------------|

|            | 2.4.1 Dragon                                    | 37         |

|            | 2.4.2 FengShui                                  | 38         |

|            |                                                 | 38         |

|            |                                                 | 39         |

| Chapte     | r III. State of the Art in Global Routing       | 40         |

| 3.1        | Global and Detailed Routing                     | 40         |

| 3.2        |                                                 | 43         |

| 3.2        |                                                 | 43<br>43   |

|            | <b>6</b>                                        | 43<br>43   |

|            | $\epsilon$                                      | 43<br>44   |

|            | 8 1 1                                           | 44<br>45   |

|            | r · r · · · · · · · · · · · · · · · · ·         | 43<br>45   |

|            | $\mathcal{C}$                                   |            |

|            | $\mathcal{E}$                                   | 46         |

|            | $oldsymbol{\mathcal{E}}$                        | 47         |

| 2.2        | 1                                               | 48         |

| 3.3        |                                                 | 50         |

|            |                                                 | 50         |

|            |                                                 | 51         |

|            |                                                 | 51         |

| 3.4        | The ISPD '07 Routing Contest                    | 53         |

| PART II    | VLSI Placement                                  |            |

| Chante     | r IV. Fine Control of Local Whitespace          | 54         |

| Chapte     | Tive Time Control of Boen Wintespace            | <i>J</i> 1 |

| 4.1        | Traditional Whitespace Allocation               | 56         |

| 4.2        | Top-down Whitespace Allocation                  | 57         |

| 4.3        |                                                 | 60         |

| 4.4        |                                                 | 67         |

| 4.5        |                                                 | 72         |

| Chapte     | r V. Routability Optimization in Placement      | 73         |

| 5.1        | Previous Work on Routability-driven Placement   | 76         |

| 5.1        |                                                 | 76         |

|            |                                                 | 79         |

|            |                                                 | 80         |

| 5.2        | •                                               | 81         |

| 3.2        |                                                 | 81<br>82   |

|            | e                                               |            |

| <i>5</i> 2 | 1                                               | 84         |

| 5.3<br>5.4 | e                                               | 86<br>93   |

| 5.4        | Defaued Placement Driven by Steiner Tree Length | 7.3        |

| 5.5      | Congestion-based Cut-line Shifting                                 | 96  |

|----------|--------------------------------------------------------------------|-----|

| 5.6      | Steiner-tree Evaluators: Runtime, Accuracy and Fidelity            | 98  |

| 5.7      | Empirical Results                                                  | 100 |

| 5.8      | Conclusions and Further Work                                       | 106 |

| Chapte   | r VI. Incremental Placement and Applications to Physical Synthesis | 108 |

| 6.1      | Previous Work in Incremental Placement                             | 111 |

| 6.2      | Requirements of Incremental Placement                              | 115 |

| 6.3      | Top-down Legalization                                              | 117 |

|          | 6.3.1 General Framework                                            | 118 |

|          | 6.3.2 Fast Cut-line Selection                                      | 119 |

|          | 6.3.3 Scalability                                                  | 120 |

|          | 6.3.4 Handling Macros and Obstacles                                | 122 |

|          | 6.3.5 Controlling Overlaps, Whitespace and Congestion              | 123 |

| 6.4      | Using ECO-system in High-level and Physical Synthesis              | 126 |

|          | 6.4.1 Additional User Controls                                     | 127 |

|          | 6.4.2 Placing New Cells and Macros                                 | 128 |

|          | 6.4.3 An Application to Body Bias Clustering                       | 130 |

| 6.5      | Empirical Results                                                  | 132 |

|          | 6.5.1 Legalization of Resized Netlists                             | 132 |

|          | 6.5.2 ECO-system's Impact on Timing                                | 136 |

|          | 6.5.3 Legalizing Analytical Global Placements                      | 137 |

| 6.6      | Conclusions                                                        | 139 |

|          | 6.6.1 Summary of Our Work                                          | 140 |

|          | 6.6.2 Additional Applications                                      | 141 |

|          | 6.6.3 Our Contributions to Shared Research Infrastructure          |     |

| PART III | <b>Fundamental Techniques for Routing</b>                          |     |

| Chapte   | r VII. Our Framework for Global Routing                            | 144 |

| •        |                                                                    |     |

| 7.1      | High-performance Global Routing                                    | 146 |

|          | 7.1.1 Basic Algorithmic Framework                                  | 146 |

|          | 7.1.2 Congestion Penalty                                           | 149 |

|          | 7.1.3 Interactions Between Single- and Multi-Net Routing           | 150 |

|          | 7.1.4 Overcoming the "Last-gasp" Problem                           | 154 |

|          | 7.1.5 Three-dimensional Routing                                    | 155 |

|          | 7.1.6 Via Pricing and Optimization                                 | 157 |

| 7.2      | Experimental Results                                               | 159 |

|          | 7.2.1 Performance on ISPD '98 and '07 Benchmarks                   | 159 |

|          | 7.2.2 Using Steiner Trees versus Using MSTs                        | 162 |

|          | 7.2.3 Layer Assignment versus Full Three-dimensional Routing       | 163 |

|          | 7.2.4 Selective Net Weighting                                      | 164 |

| 7.3      | Conclusions                                                        | 165 |

| Chapte     | r VIII. Ex | tensions to Our Routing Framework                          | 166        |

|------------|------------|------------------------------------------------------------|------------|

| 8.1        | Data Struc | ctures for Routing                                         | 168        |

|            |            | ranch-free Representation (BFR) for Individual Routed Nets | 169        |

|            |            | Data Structure for Dynamic Global Routing Grid             | 170        |

|            | 8.1.3 Su   | apporting Efficient Rip-up and Reroute                     | 171        |

| 8.2        | Analysis o | of Single-net Routing Techniques                           | 172        |

|            | 8.2.1 Pc   | oint-to-point Maze Routing                                 | 173        |

|            |            | et Splitting                                               | 174        |

|            |            | ontinual Net Restructuring                                 | 175        |

|            |            | andling Multi-layer Routing                                | 175        |

| 8.3        |            | rithms in Sherpa                                           | 176        |

|            |            | ne Sherpa Flow                                             | 176        |

|            |            | Dual Lagrange Formulation                                  | 178        |

|            |            | gh-precision Lagrange Multipliers                          | 180        |

|            |            | ogarithmic Penalty Function                                | 181        |

|            |            | yclical Net-locking                                        | 183        |

| 0.4        |            | ulti-layer Routing                                         | 184        |

| 8.4<br>8.5 |            | Evaluation                                                 | 185<br>187 |

| 8.3        | Coliciusio | 118                                                        | 10/        |

| PART IV    | Placemen   | t and Routing in Modern Design Flows                       |            |

| 9.1        | Industrial | Physical Design                                            | 188<br>189 |

| 9.2        |            | chniques                                                   | 192        |

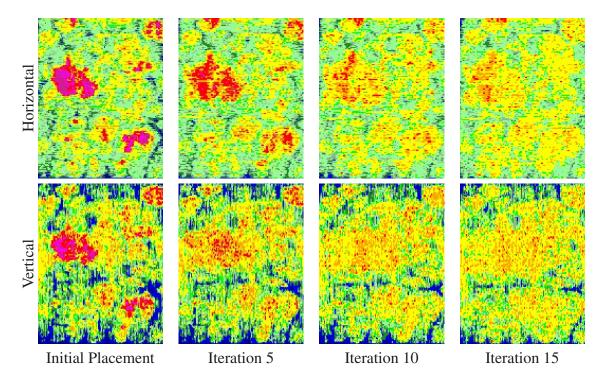

|            |            | odeling Routing Congestion                                 | 193        |

|            |            | emporary Cell Inflation                                    | 195<br>196 |

|            |            | cremental Spreading                                        | 190        |

| 0.2        |            | ne CRISP Flow                                              |            |

| 7.5        |            | ntal Results                                               | 201        |

|            |            |                                                            |            |

| 9.4        |            | ns                                                         |            |

| у.т        | Conclusio  | 115                                                        | 200        |

| PART V     | Summary    |                                                            |            |

| Chapte     | r X. Concl | lusions and Future Work                                    | 210        |

| 10.1       | Summarv    | of Contributions                                           | 211        |

|            | •          | s for Future Work                                          |            |

| BIBLIOG    | RAPHY .    |                                                            | 216        |

# LIST OF FIGURES

| Figure |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1    | Traditional top-down partitioning-based placement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7  |

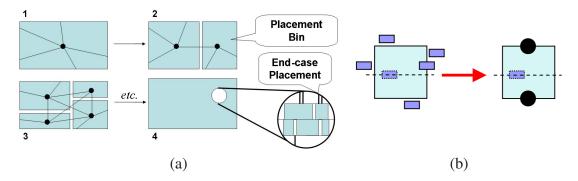

| 2.2    | (a) Top-down bisection-based placement. The placement area and netlist are successively divided into placement bins until the bins are small enough for end-case placement. (b) Terminal propagation is an important enhancement to top-down bisection-based placement. The net has five fixed terminals (four above and one below the cut-line) and movable cells which are represented by the cell with a dashed outline. The fixed terminals above the cut-line are propagated to the black circle at the top of the bin; the fixed terminal below the cut-line is propagated to the black circle below the cut-line; and movable cells remain unpropagated. Note that the net is <i>inessential</i> since terminals are propagated to both sides of the cut-line [116]. | 9  |

| 2.3    | Min-cut floorplacement. Steps 3-11 differ from min-cut placement [115].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 20 |

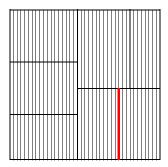

| 2.4    | Progress of mixed-size floorplacement on the IBM01 benchmark from IBM-MSwPins. The picture on the left shows how the cut lines are chosen during the first six layers of min-cut bisection. On the right is the same placement but with the floorplanning instances highlighted by "rounded" rectangles. Floorplanning failures can be detected by observing nested rectangles [115]                                                                                                                                                                                                                                                                                                                                                                                        | 23 |

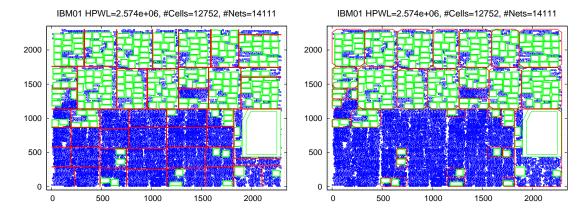

| 2.5    | A placement of the IBM01 benchmark from ${\tt IBM-MSwPins}$ by FengShui before (left) and after (right) legalization and detailed placement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 27 |

| 2.6    | SCAMPI floorplacement flow. Steps 3-10, 12-13, and 22-23 differ from traditional floorplacement [107]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 30 |

|        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

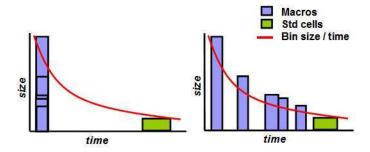

| 2.7 | The plot on the left illustrates traditional floorplacement. Whenever a floorplanning threshold is reached, all macros in the bin are designated for floorplanning. Then, the floorplacement flow continues down until detailed placement, where the standard cells will be placed. The plot on the right illustrates the SCAMPI flow. Macros are selectively placed at the appropriate levels of hierarchy [107]                                                                                                                                                       | 31 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

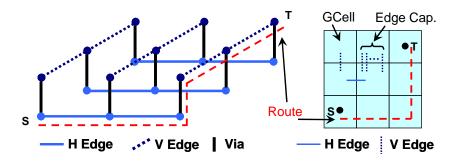

| 3.1 | Pictorial representations of the global routing grid. The image on the right shows how the layout is abstracted into a regular grid of GCells. GCells are represented by vertices, with adjacent vertices connected by graph edges. Capacities on edges that join GCells can be defined as the number of routing tracks that cross GCell boundaries. The image at the left shows horizontal, vertical and via connections on different layers.                                                                                                                          | 41 |

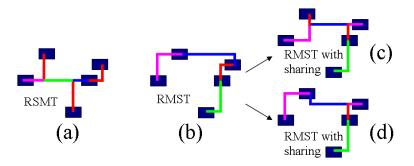

| 3.2 | Decomposition of a 5-pin net by minimal Steiner tree (a), MST (b) and MSTs with sharing (c)&(d). The choice of (c) or (d) depends on congestion. The minimal Steiner tree (a) contains 5 flat subnets and 1 L-shaped subnet, whereas the shared MST (d) has 2 flat subnets and 3 L-shaped subnets which gives it greater flexibility                                                                                                                                                                                                                                    | 45 |

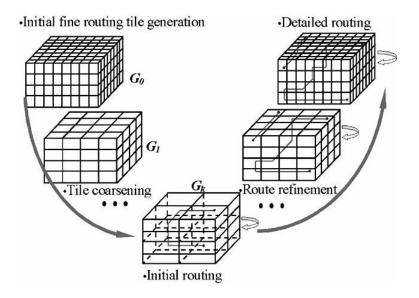

| 3.3 | Multi-level routing progression; image from [53]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 48 |

| 3.4 | BoxRouter ILP formulation for routing nets using only L shapes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 49 |

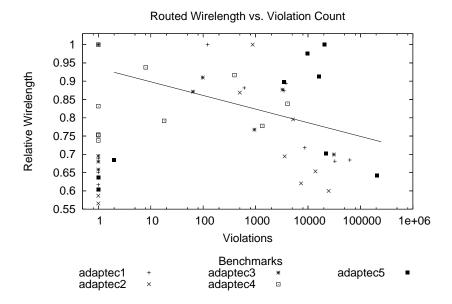

| 3.5 | Routed wirelength versus violations for all competing routers on two-dimensional ISPD '07 benchmarks [71]. Note that violation counts are shown on a log-scale where 0 cannot be plotted, so completely legal solutions are depicted with exactly 1 violation. Relatively few solutions submitted to the contest were legal (35%), but they are generally a cut above the rest. Of the illegal solutions, as violations increase, routed wirelength decreases. To emphasize the trend, a linear least-squares fit of the data has been added for the illegal solutions. | 52 |

| 4.1 | Allocating whitespace in top-down placement to satisfy density constraints using uniform, minimum local and safe whitespace allocation.                                                                                                                                                                                                                                                                                                                                                                                                                                 | 58 |

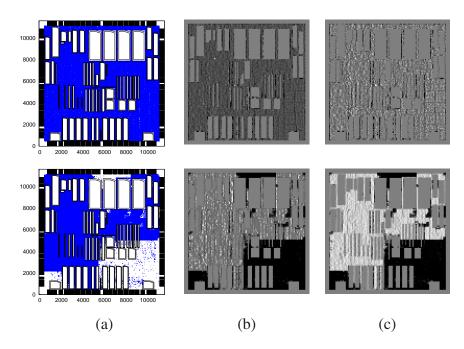

| 4.2 | Column (a) shows Capo 10.5 global placements of the ISPD 2005 placement contest benchmark adaptec1 [104] with uniform whitespace allocation (top) and non-uniform whitespace allocation (bottom). Fixed obstacles are drawn with double lines. To indicate orientation, north-west corners of blocks are truncated. Columns (b) and (c) depict the local utilization of the uniform and non-uniform placements. Lighter areas of the placement signify regions that violate the target placement density whereas darker areas have utilization below the target. Areas with no placeable area (such as those with fixed obstacles) are shaded as if they exactly meet the target density. The target placement density for column (b) is 90% and the target for column (c) is 60%. Adaptec1 has 57.34% utilization. The HPWL for the uniform and non-uniform placements is 10.69e7 and 9.03e7 respectively. As the intensity maps show, when 60% utilization is the target, uniform whitespace allocation is much more appropriate than 12% minimum local whitespace. On the other hand, 12% minimum local whitespace is appropriate in terms of violations when the target is 90% utilization and has much better wirelength | 61 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.3 | Greedy cell movement algorithm to reduce density violations while also taking HPWL into account                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 62 |

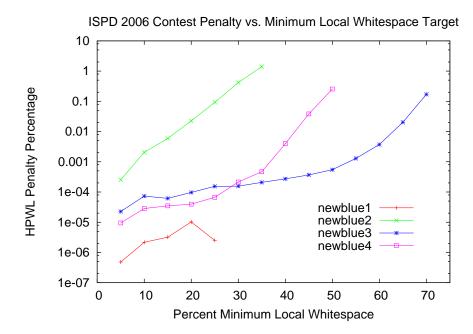

| 4.4 | ISPD 2006 placement contest penalty for requested amounts of minimum local whitespace. The penalty is calculated based on the total amount of density-constraint violations. We test on benchmarks from the ISPD 2006 placement contest suite [102]. These benchmarks have 29%, 38%, 74% and 54% whitespace, respectively. Usually the penalty is very small when using our techniques (always less than 1.5%), but the penalty grows significantly as the requested whitespace approaches the amount of whitespace available in the design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 63 |

| 4.5 | Linear programming formulation (horizontal direction) to optimize HPWL of an existing placement. Further simplification is possible for two- and three-pin nets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 64 |

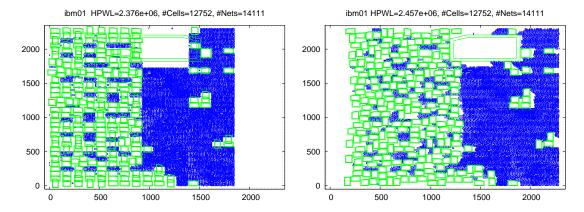

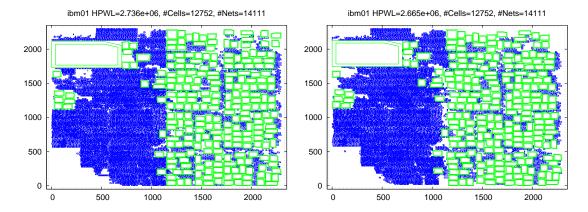

| 4.6 | ICCAD 2004 IBM-MSwPins benchmark [1] ibm01 before (left) and after (right) optimal whitespace allocation via network flows. The HPWL improvement for this placement is 2.61% and takes only 10 CPU seconds to perform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 66 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

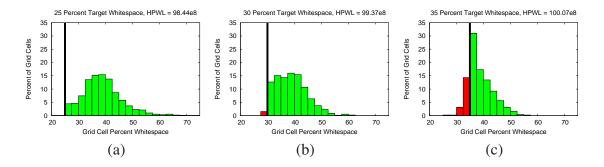

| 4.7 | Controlling whitespace distribution on the ethernet benchmark from the IWLS 2005 benchmark suite [72], which has approximately 38% whitespace. We divide the placement area into a regular grid and report whitespace distribution across grid cells when targeting (a) 25%, (b) 30% and (c) 35% minimum local whitespace. As the minimum whitespace requested approaches the total whitespace, the constraint becomes more difficult to satisfy, but our techniques are successful in producing solutions that are legal or nearly-legal for the majority of grid cells                  | 69  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

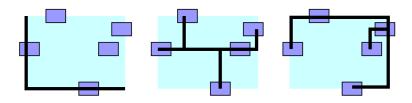

| 5.1 | HPWL (left), Steiner WL (center) and Rectilinear Minimal Spanning Tree (MST) WL (right) for a five-pin net.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 76  |

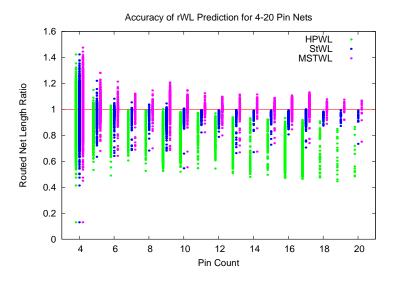

| 5.2 | Comparing the accuracy of routed wirelength (rWL) estimators HPWL (left lines), StWL (middle) and MST WL (right) for nets with 4-20 pins in the vga_lcd design from the IWLS 2005 benchmarks [72]. StWL was calculated using FastSteiner [78]                                                                                                                                                                                                                                                                                                                                             | 82  |

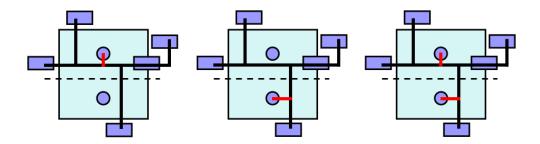

| 5.3 | Calculating the three costs for weighted terminal propagation with StWL: $w_1$ (left), $w_2$ (middle), and $w_{12}$ (right). The net has five fixed terminals: four above and one below the proposed cut-line. For the traditional HPWL objective, this net would be considered inessential. Note that the structure of the three Steiner trees may be entirely different, which is why $w_1$ , $w_2$ and $w_{12}$ must be evaluated independently                                                                                                                                        | 87  |

| 5.4 | Minimizing StWL in top-down min-cut global placement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 90  |

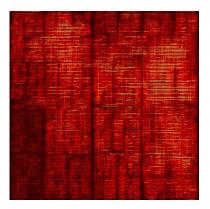

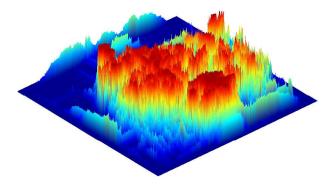

| 5.5 | Congestion maps for the ibm01h benchmark: uniform whitespace allocation (produced with Capo -uniformWS) is illustrated on the left, congestion-driven allocation in ROOSTER is illustrated on the right. The peak congestion when using uniform whitespace is 50% greater than that for our technique. When routed with Cadence WarpRoute, uniform whitespace produces 3.95% overfull global routing cells and routes in just over 5 hours with 120 violations. ROOSTER's whitespace allocation produces 3.18% overfull global routing cells and routes in 22 minutes without violations. | 98  |

| 5.6 | The ICCAD'04-Faraday benchmarks placed by ROOSTER. Macros are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

|     | depicted with double outlines and are fixed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 104 |

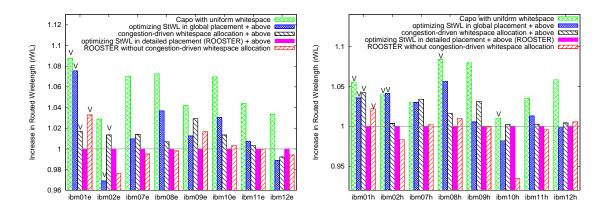

| 5.7 | Impact of individual optimizations on the rWL produced by ROOSTER. "V" indicates violations in routing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 105 |

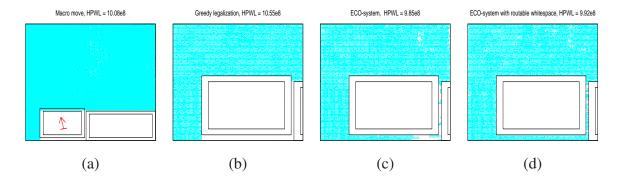

| 6.1 | Legalization of a macro move in the ICCAD'04-Faraday design DSP1 [1]. In (a), the left-most macro is moved toward the north-west corner of the design. This move causes overlap with standard cells and also areas of empty space below and to the right of the macro. The remaining three images are zoomed-in legal placements of this design. In (b), a greedy algorithm which tries to minimize cell movement is applied. Overlap is removed, but the empty space below and to the right of the macro remain unutilized which can be detrimental to routability. (c) shows the placement as legalized by our tool ECO-system. ECO-system improves wirelength and makes use of much of the area vacated by the macro. Lastly, (d) shows how ECO-system can distribute cells and whitespace so as to ensure routability and/or satisfy minimum whitespace constraints. 109 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.2 | Our top-down partitioning-based ECO placement algorithm. Lines 3-21 and 28 differ from traditional min-cut placement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

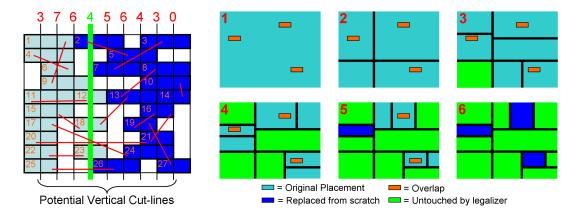

| 6.3 | Fast legalization by ECO-system. The image on the left illustrates choosing a vertical cut-line from an existing placement. Nets are illustrated as red lines. Cells are individually numbered and take 2 or 3 sites each. Cut-lines are evaluated by a left-to-right sweep (net cuts are shown above each line). A cut-line that satisfies partitioning tolerances and minimizes cut is found (thick green line). Cells are assigned to "left" and "right" according to the center locations. On the right, placement bins are sub-divided using derived cut-lines until (i) a bin contains no overlap and is ignored for the remainder of the legalization process or, (ii) the placement in the bin is considered too poor to be kept and is replaced from scratch using min-cut or analytical techniques                                                                 |

| 6.4 | Algorithm for finding the best vertical cut-line from a placement bin. Finding the best horizontal cut-line is largely the same process. Note that the runtime of the algorithm is linear in the number of pins incident to the bin, cells contained in the bin, and possible cut-lines for the bin 121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6.5 | Shifting a cut-line chosen during ECO cut-line selection. Unlike the WSA technique [92,93], cut-line shifting during ECO is not done on geometric cut-lines but instead on those cut-lines which are chosen during fast cut-line selection. The image on the left shows a placement that has been divided into bins during the course of ECO-system. In the image on the right, the chosen cut-line of the bottom-right bin is shifted to the right. The density of vertical lines represents the initial placement and its scaling around the moving cut-line (shown in red)                                                                                                                                                                                                                                                                                                |

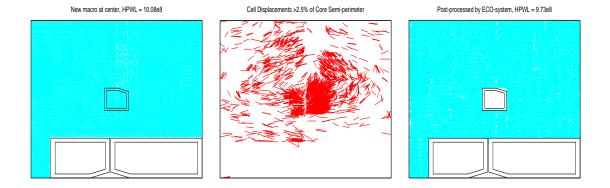

| 6.6 | Legalizing the placement of a new fixed obstacle at the center of the ICCAD'04-Faraday design DSP1 [1]. The picture in the middle shows the movement of standard cells to make room for the obstacle. Many standard cells must move in order to accommodate the obstacle, but ECO-system moves these cells on average only a short distance (1.27% of the core half-perimeter) and is able to improve total HPWL                                                                                                                                                                                                                                                           | 126 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

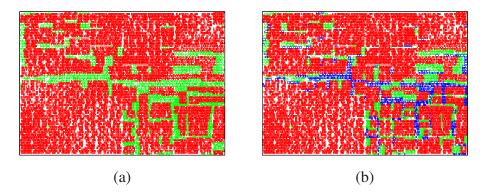

| 6.7 | Using ECO-system to perform body bias clustering. ECO-system refines an initial placement and moves cells with the same bias into contiguous regions to reduce the area overhead of adaptive body biasing while preserving interconnect length. Cells are grouped into (a) 2 and (b) 3 bias clusters based on their power characteristics in an initial placement. Cells with the same bias share the same color                                                                                                                                                                                                                                                           | 130 |

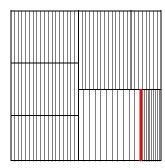

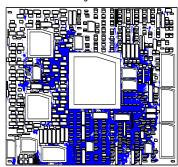

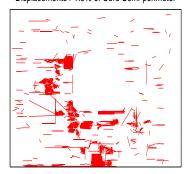

| 6.8 | When applied to resized netlist, ECO-system produces a placement (right) similar to the original placement (left). Fixed objects are outlined in double black lines. The largest cell displacements are shown in red (center). Only displacements larger than 1.5% of the half-perimeter of the design are shown. Average displacement is 0.28% of the design half-perimeter. The majority of the large displacements form around the corners of the large, fixed obstacles. Many of these large displacements appear to be clustered, indicating small groups of modules transported to another region of the core or spread to accommodate area increases                | 138 |

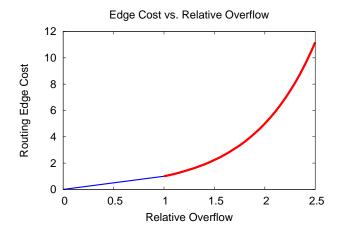

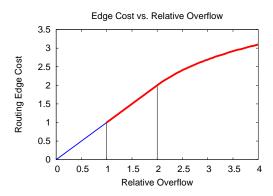

| 7.1 | Cost of a routing edge as a function of relative overflow. Cost is linear while the edge is not overfilled, but grows exponentially once the edge is overfull                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 149 |

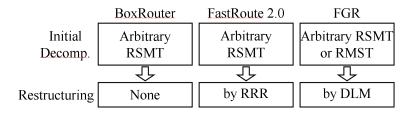

| 7.2 | A comparison of the net decomposition techniques used by BoxRouter [40], FastRoute 2.0 [110] and FGR. In Section 7.2.2, we compare the use of RMSTs and RSMTs in FGR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 150 |

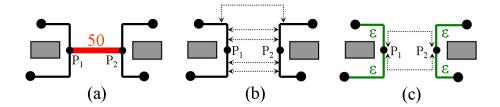

| 7.3 | Re-routing a subnet and changing net topology in FGR. The shaded boxes represent obstacles. The tree in (a) passes through a congested segment in the middle which must be ripped up. The dashed arrows in (b) represent several possible re-routings that a restructuring algorithm may consider. The re-routings shown in (c) are two that FGR will consider during DLM. Paths considered by FGR must start and end along the endpoints of the segment that was removed. Both of these re-routings reuse routing segments from the net and create new Steiner points if chosen. The use of temporary zero-cost edges is required to preserve the efficiency of A*-search | 152 |

| 7.4 | Layer assignment in FGR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 153 |

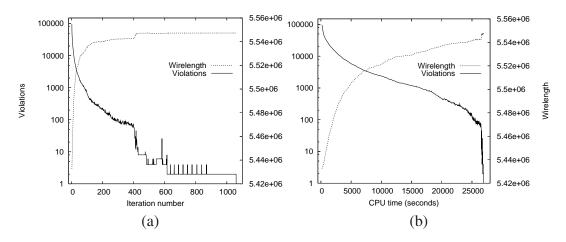

| 7.5 | Violation count and wirelength on the two-dimensional ISPD '07 benchmark adaptec1 plotted as a function of (a) iteration number and (b) time. Violation counts are plotted on a log-scale and decrease, while wirelength is plotted on a linear scale and monotonically increases. Note that the majority of DLM iterations occur when 100 or fewer violations remain, but total wirelength noticeably increases during that phase | 154 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7.6 | Violation count and wirelength plotted as a function of iteration number on two unroutable two-dimensional ISPD '07 benchmarks. In both cases, FGR is stopped after a period of 24 hours                                                                                                                                                                                                                                           | 155 |

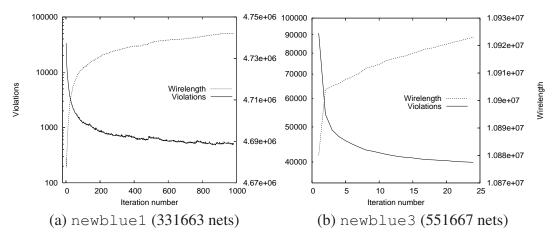

| 7.7 | Cumulative distributions of detouring without (above) and with (below) net weighting on the two-dimensional newblue2 benchmark. Net detours are measured as a ratio of routed net length to Steiner wirelength as given by FLUTE [44]. When weights are applied to a subset of the nets, the detouring on those nets goes down significantly without adverse effects on the detouring of all nets                                  | 165 |

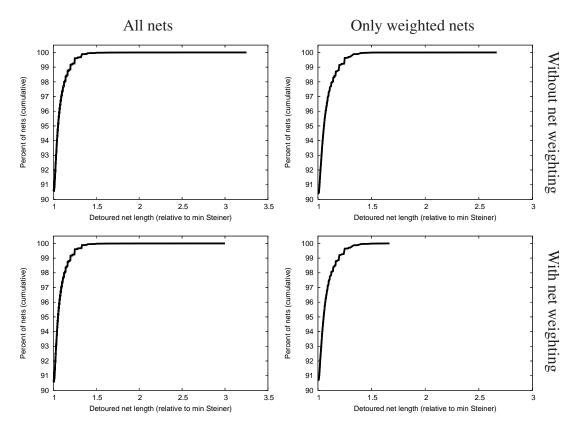

| 8.1 | Congestion map of the newblue1 two-dimensional benchmark as guided by Sherpa                                                                                                                                                                                                                                                                                                                                                       | 168 |

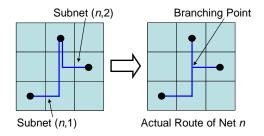

| 8.2 | The branch-free representation (BFR) of routed nets. Subnets are treated separately and, when combined, form a completely routed solution without duplicate edges                                                                                                                                                                                                                                                                  | 169 |

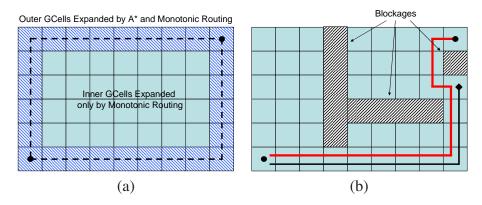

| 8.3 | Boxed A*-search versus monotonic and pattern routing. On the left, we show an instance of the shortest- path problem with high bend costs. Boxed A*-search with a Manhattan lower bound searches fewer grid cells than monotonic routing to find the same solution. On the right, blockages obstruct the path and cause monotonic routing to fail, but boxed A*-search succeeds                                                    | 173 |

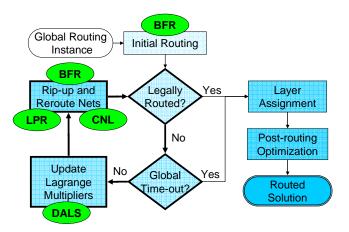

| 8.4 | Global routing in Sherpa and the use of novel techniques such as a branch-free representation (BFR) for routed nets, cyclical net locking (CNL), dynamic adjustment of Lagrange steps (DALS) and a logarithmic penalty function (LPR).                                                                                                                                                                                             | 177 |

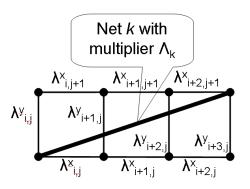

| 8.5 | Relevant multipliers in the dual Lagrange formulation. Like the original formulation, each edge of the routing grid has a multiplier $\lambda$ . In the dual formulation, each net also has its own multiplier $\Lambda$                                                                                                                                                                                                           | 180 |

| 8.6 | New <i>convex</i> penalty function used by Sherpa. The function grows linearly until a routing edge uses 200% of its routing resources and logarithmically thereafter. This radical departure from <i>concave</i> penalty functions used by other routers is made possible by the strength of the underlying global routing algorithm and improves the handling of designs with numerous violations. | 182 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

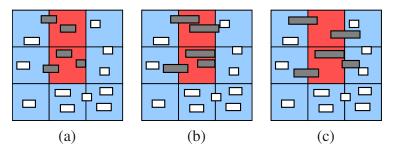

| 9.1 | (a) A placement with two congested areas. (b) CRISP inflates standard cells in these regions, (c) and spreads them                                                                                                                                                                                                                                                                                   | 195 |

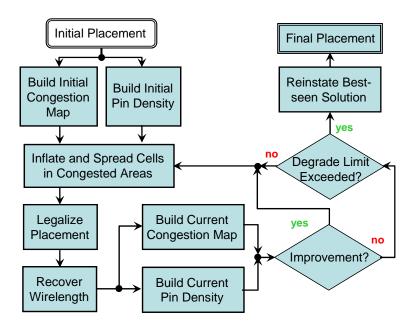

| 9.2 | The CRISP incremental placement flow                                                                                                                                                                                                                                                                                                                                                                 | 198 |

| 9.3 | The CRISP algorithm for determining which cells to inflate per iteration.                                                                                                                                                                                                                                                                                                                            | 199 |

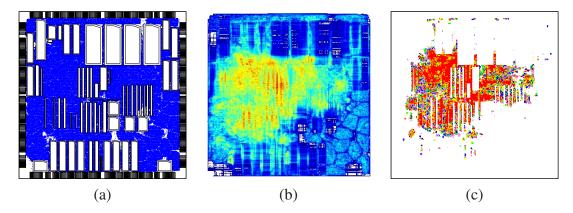

| 9.4 | (a) Placement of adaptec1 with 60% target density and (b) corresponding congestion map. (c) Map of cells inflated during the first five iterations of congestion elimination. Colors in (c) correspond to relative inflation with red cells being the greatest followed by orange, yellow, green, blue and violet                                                                                    | 200 |

| 9.5 | Incrementally relieving congestion problems on a heavily congested industrial design with low whitespace. Areas colored pink and purple have global routing resource usage over 100%. These areas are targeted by CRISP and eliminated                                                                                                                                                               | 206 |

# LIST OF TABLES

| <u> Table</u> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1           | Comparison of Capo's performance at the ISPD 2006 Placement Contest. "Overflow" represents the HPWL penalty for not effectively enforcing density constraints on the benchmarks. Using the SCAMPI improvements, Capo's HPWL is reduced by 7% overall                                                                                                                                                                                                                        | 35 |

| 4.1           | Reallocation of whitespace in mPL6 [27] placements of selected ISPD 2006 contest benchmarks [102]. Local whitespace targets are the same as from the ISPD 2006 placement contest. Density violations are measured as the percentage of total cell area that violates density constraints. Using Capo 10.5 in ECO-system mode [117] in combination with our whitespace allocation techniques, we are able to significantly reduce the density violations of mPL6 placements. | 59 |

| 4.2           | Relevant characteristics of select benchmarks from the IWLS 2005 suite [72]. "Grid size" is the size of the grid used for greedy cell movement.                                                                                                                                                                                                                                                                                                                             | 67 |

| 4.3           | Correction of local density violations by greedy cell movement techniques. Benchmarks are selected from the IWLS 2005 benchmark suite and each have 38% total whitespace [72]. Density violations are measured as the percentage of total cell area that violates density constraints. Greedy cell movement corrects all density violations when requested local whitespace is 25% or less and in many cases improves HPWL as well                                          | 68 |

| 4.4           | HPWL improvement due to flow-based whitespace redistribution on the ICCAD 2004 IBM-MSwPins mixed-size benchmarks [1]. On average, the flows are able to reallocate whitespace and improve HPWL by nearly 3% while scaling well with increasing quantities of movable objects                                                                                                                                                                                                | 71 |

| 5.1 | Objectives of the Place-and-Route process and how they compare with objectives of placement techniques. Traditional work on placement does not optimize or even report the objectives most pertinent for Place-and-Route. It is particularly difficult to optimize objectives that are measured <i>relative</i> to a given industrial router. We improve key objectives by departing from traditional HPWL optimization. Optimizing congestion estimates <i>per se</i> appears of limited use                                                                                                              | 74  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.2 | Fixed-outline floorplanning to minimize HPWL versus Steiner WL. All StWLs were calculated using the Steiner evaluator FLUTE [44]. All wirelength and runtimes are averaged over 50 runs. Optimizing Steiner WL increases runtime by a minimum of 2.43x for n300 and a maximum of 29.53x for ami33                                                                                                                                                                                                                                                                                                          | 84  |

| 5.3 | Runtime breakdown of global placement when minimizing StWL for ibm01-easy of the IBMv2 series of benchmarks [143]. "Partitioning problem construction" includes runtime for Steiner WL evaluators                                                                                                                                                                                                                                                                                                                                                                                                          | 92  |

| 5.4 | Improving Steiner WL with FastSteiner [78]. Average HPWL, Steiner WL and placement runtimes are shown for the IBMv2 benchmarks [143]. Results are the average of five independent runs. All wirelengths are in meters. Optimizing StWL decreases StWL by 2.8%, increases runtime by 36% and HPWL by 1.4%                                                                                                                                                                                                                                                                                                   | 93  |

| 5.5 | Statistics of the IBMv2 benchmarks [143]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 95  |

| 5.6 | Detailed placement improves Steiner WL and routed WL. Average improvements and runtime (as a fraction of total placement time) from five independent runs are shown for the IBMv2 benchmarks [143]                                                                                                                                                                                                                                                                                                                                                                                                         | 96  |

| 5.7 | Impact of Steiner evaluators during global placement (ibm01e). Total StWL and global placement runtime are listed for all combinations of three Steiner evaluators. In such combinations, the minimum Steiner length estimate is used in weighted partitioning                                                                                                                                                                                                                                                                                                                                             | 100 |

| 5.8 | A comparison of our work to best published routing results on the IBMv2 benchmarks [143]. All routed wirelengths (rWL) are in meters. A ratio greater than 1.0 indicates that our results are better on this benchmark suite. For all cases, ROOSTER outperforms best published routing results in terms of routed wirelength and via count. Published routing data for APlace 1.0 for ibm09-ibm12 is unavailable. Routing data for Capo 9.2, Dragon 3.01 and FengShui 2.6 were taken from [115] which did not list via counts. Routing uses a 24-hour time-out. Best legal rWL and via counts are in bold | 100 |

| 5.9  | A comparison of our work to the most recent version of mPL-R + WSA, APlace 2.04 and FengShui 5.1 on the IBMv2 benchmarks [143]. All routed wirelengths (rWL) are in meters. "Time" represents routing runtime in minutes. Note that while APlace 2.04 achieves overall smaller wirelength than ROOSTER, it routes with violations on 2 of the 16 benchmarks. Best legal rWL and via counts are in bold                                                                                                                                          |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.10 | Results when applying various post-processors to our placements for the IBMv2 benchmarks [143]. All routed wirelengths (rWL) are in meters. "Time" represents routing runtime in minutes. WSA shows improvement on some of our placements, but increases routed wirelength and via counts on the largest benchmarks. The detailed placers of Dragon 4.0 and FengShui 5.1 decrease the routability of our placements by increasing rWL and via count on all benchmarks and the addition of violations. Best legal rWL and via counts are in bold |

| 5.11 | A comparison of ROOSTER to Cadence AmoebaPlace on the IWLS 2005 Benchmarks [72]. All routed wirelengths (rWL) are in meters. "Time" represents routing runtime in minutes. ROOSTER is outperforms AmoebaPlace by 12.0% in rWL and 1.1% in via counts (without orientation constraints the improvements are 26.5% and 3.2%, respectively). Best rWL and via counts are in bold                                                                                                                                                                   |

| 5.12 | Routing results on the Faraday benchmarks with movable macro blocks fixed [1]. All routed wirelengths (rWL) are in meters. "Time" represents routing runtime in minutes. Best rWL and via counts are highlighted 10                                                                                                                                                                                                                                                                                                                             |

| 5.13 | The impact of replacing HPWL (for high degree nets) and StWL (for all nets) with MST as the wirelength evaluator for ROOSTER on the IBMv2 benchmarks. All routed wirelengths (rWL) are in meters. "Time" represents routing runtime in minutes. The ratios are with respect to ROOSTER's performance described in Table 5.8. Legal improvements to ROOSTER in rWL and via counts are highlighted in bold                                                                                                                                        |

| 6.1  | A comparison of several legalization and incremental placement techniques. For each of the techniques, its compatibility with fixed objects or macros as well as what general techniques it uses are listed. ECO-system is compared with XDP [52] in Section 6.5. (†) Support of the feature by this technique is unclear. See Section 6.1 for more details. (‡) Recent versions of Capo, the basis of ECO-system, use linear programming and network flows in detailed placement, but they are beyond the scope of this work.                  |

| 0.2 | benchmarks [104]. "Area Ratio" represents the change in total cell area after resizing. Overlap is measured as % of the total movable cell and macro area. Full data for the ISPD'05 benchmarks can be found in [117]. ECO-system requires significantly more runtime than the Capo 10 legalizer [115], and approximately 16% of the original placement time. ECO-system increases HPWL by 0.61% on average while the Capo 10 legalizer increases HPWL by 3.93% on the IBM-MSwPins benchmarks. On the ISPD'05 Contest benchmarks ECO-system decreases HPWL by 1.00% on average while the Capo 10 legalizer increases HPWL by 4.28%. | 133 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.3 | Overlap legalization on the IWLS 2005 Benchmarks [72]. "Area Ratio" represents the change in total cell area after resizing. Overlap is measured as % of the total movable cell area. ECO-system decreases HPWL by 1.81% on average while the Capo 10 legalizer increases HPWL by 1.85%                                                                                                                                                                                                                                                                                                                                             | 135 |

| 6.4 | Overlap legalization of APlace 2.04's [82] global placements of the ISPD'C Contest benchmarks [104]. Overlap is measured as % of the total movable cell area. ECO-system produces legal solutions with nearly the same or better HPWL than APlace 2.04's legalizer. APlace's legalizer increases HPWL by 4.91% while ECO-system increases HPWL by 3.68% and only 2.35% when using shifting. ECO-system with shifting is faster on 7 of the 8 benchmarks and four times faster than APlace's legalizer overall                                                                                                                       | 136 |

| 6.5 | Improving the routability of analytical placements using ECO-system. We compare the routability of mPL6 [27] global placements when using mPL6's detailed placer (XDP [52]) vs. ECO-system with cut-line shifting for detailed placement on the IBMv2 benchmark suite [143]. Best legal routed wirelength (Rt WL) and via counts are highlighted in bold. ECO-system produces routable placements in all cases, reduces routed wirelength by 1.1% and via counts by 7.8%, and cuts routing runtime by more than half                                                                                                                | 139 |

| 6.6 | Improving the routability of analytical placements in the presence of fixed obstacles in the ISPD'04-Faraday benchmark suite [1]. We post-process mPL6 [27] global placements using mPL6's detailed placer and, separately, our ECO-system (with cut-line shifting). The mPL6 detailed placer XDP [52] produces largely unroutable placements                                                                                                                                                                                                                                                                                       | 140 |

| 7.1 | Routed cost breakdown of FGR's solutions to the ISPD '07 Global Routing Contest benchmarks [71]. "FLUTE Ratio" is the ratio of the length of routing segments used to the Steiner tree length of all nets as computed by FLUTE [44]. Vias account for more than 25% of total cost in every two-dimensional benchmark and more than 50% of total cost in each three-dimensional benchmark, highlighting the importance of via minimization.           | 157 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7.2 | Statistics of the ISPD '98 IBM benchmark suite [70]. Runtimes for BoxRouter [40] and FGR are given in seconds. FGR is faster than BoxRouter on 7 of the 10 benchmarks and uses 35% less runtime to solve the entire suite                                                                                                                                                                                                                            | 158 |

| 7.3 | Comparison of FGR to FastRoute 2.0 [110] and BoxRouter [40] on the ISPD '98 IBM benchmark suite [70]. FGR completes all 10 of the benchmarks while BoxRouter and FastRoute 2.0 leave overflow on 4 and 3 of the benchmarks, respectively. In terms of routed wirelength, FGR outperforms BoxRouter by 2.7% and FastRoute 2.0 by 3.6%                                                                                                                 | 159 |