# Physically-Adaptive Computing via Introspection and Self-Optimization in Reconfigurable Systems

by

Kenneth M. Zick

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in The University of Michigan 2010

## **Doctoral Committee:**

Professor John P. Hayes, Co-Chair Professor John H. Holland, Co-Chair Professor Todd M. Austin Associate Professor Robert Dick © Kenneth M. Zick

All rights reserved

2010

To Jie, Mom, and Dad

### ACKNOWLEDGMENTS

I wish to sincerely thank all who enabled this research. Professor Holland, thank you for bestowing the ways of adaptive systems and for our collaboration with NASA; the sky is no limit now. Professor Hayes, thanks very much for the motivation, extensive feedback, important teachings and support. I am extremely grateful to NASA and its Graduate Student Research Program for four years of funding. I benefited greatly from U-M's Center for the Study of Complex Systems; its one-of-a-kind graduate program enabled me to set out on a new path. The Santa Fe Institute Complex Systems Summer School helped foster some important new connections and a swarm of Mars Tumbleweeds. I appreciate the many opportunities provided over the years by CSE/EECS, CoE, Rackham, and the University. Thanks to Xilinx and Sun Microsystems for donations, and thanks to my instructors and colleagues including my committee members Robert Dick and Todd Austin, the CSE staff, Eric Chaisson, Rick Riolo, Jan Gottlin, Marty Waszak, Sandra Myers, Carey Buttrill, Celeste Belcastro, Kevin Somervill, and NASA Langley. Working with Andrea Pellegrini, Joe Greathouse, and Aaron Bramson has been enlightening and fun. Best wishes as well to my classmates Daeyoung Lee, Chien-Chih Yu, Smita Krishnaswamy, Sungsoon Cho, Armin Alaghi, the participants in the Adaptive Hardware & Systems Reading Group, and the many others I've encountered.

For the important roles they have played, special thanks to my brother Matt, my brother Jeff, the Zicks, the Pitrones, my grandparents, Peter Riopelle, Paul Riopelle, Gary

O'Brien, Jim Davies, John Hajkus, Dean Robinette, Tim Gilhool, Tim Strong, Kevin Brandon, Corey Garrow, Kurt Severance, Mike Munichiello, and friends from MI, VT, TX, and MA. I'd like to acknowledge my family and, broadly, my ancestors; I wouldn't be here if not for every one of them across the billions of years. The fortuitous chains of life are worth celebrating, and in my case culminate with my heroic parents. Thanks Mom and Dad. Lastly, I am profoundly grateful to my wonderful wife, Jie; I'm very fortunate that our two paths through the universe have merged happily into one.

# TABLE OF CONTENTS

| DEDICATION.  |                                           | ii   |

|--------------|-------------------------------------------|------|

| ACKNOWLED    | GMENTS                                    | iii  |

| LIST OF FIGU | RES                                       | viii |

| LIST OF TABL | ES                                        | xi   |

| ABSTRACT     |                                           | xii  |

| CHAPTER 1 In | troduction                                | 1    |

| 1.1          | General Background and Problem Definition | 5    |

| 1.2          | FPGA-based Systems                        | 13   |

|              | 1.2.1 Hardware Platforms                  |      |

|              | 1.2.2 Reconfigurability                   |      |

|              | 1.2.3 Design Flow                         |      |

| 1.3          | Related Work                              |      |

|              | 1.3.1 Pre-Manufacturing Approaches        | 18   |

|              | 1.3.2 Manufacturing-Time Adaptation       | 19   |

|              | 1.3.3 Lifetime Adaptation                 | 20   |

| 1.4          | Proposed PAC Framework                    |      |

|              | 1.4.1 PAC Definition                      |      |

|              | 1.4.2 Fitness                             |      |

|              | 1.4.3 Introspection                       |      |

|              | 1.4.4 Self-Optimization                   |      |

|              | 1.4.5 Time Scale                          |      |

|              | 1.4.6 Fine Granularity and FPGAs          |      |

|              | 1.4.7 Assisted Adaptation                 |      |

|              | 1.4.8 Proposed Architecture               |      |

| 1.5          | Dissertation Outline                      | 33   |

| CHAPTER 2 In | trospection for Regional Variations       | 36   |

| 2.1          | Background                                | 37   |

| 2.2          | Instrumentation                           |      |

|              | 2.2.1 Efficient Counting                  |      |

|              | 2.2.2 Ring Oscillator Design              |      |

|              | 2.2.3 Sensor Design and Deployment        |      |

| 2.3         | Measurement Procedures                    | 48  |

|-------------|-------------------------------------------|-----|

|             | 2.3.1 Delay                               |     |

|             | 2.3.2 Leakage                             |     |

|             | 2.3.3 Dynamic Power                       |     |

|             | 2.3.4 Temperature                         |     |

| 2.4         |                                           |     |

|             | 2.4.1 Delay                               |     |

|             | 2.4.2 Leakage                             |     |

|             | 2.4.3 Dynamic Power                       | 61  |

|             | 2.4.4 Temperature                         | 62  |

| 2.5         | S Summary                                 | 64  |

| CHAPTER 3 S | Self-Optimization for Regional Variations | 65  |

| 3.1         | 1 2                                       |     |

| 3.2         |                                           |     |

| 3.3         |                                           |     |

| 3.4         | 1 J                                       |     |

|             | 3.4.1 Fault Model and Soft Error Model    | 74  |

|             | 3.4.2 Proposed Metric                     | 74  |

| 3.5         | Experimental Results                      | 76  |

|             | 3.5.1 Problem Formulation                 |     |

|             | 3.5.2 Applications                        |     |

|             | 3.5.3 Computational Vulnerability         |     |

|             | 3.5.4 Netlist-Level PAC                   |     |

| 3.6         | Summary                                   | 91  |

| CHAPTER 4 I | ntrospection for Local Variations         | 92  |

| 4.1         | Background                                | 92  |

| 4.2         | Local Variations in Latch Reliability     | 94  |

| 4.3         | System-Level Soft Error Model             | 97  |

| 4.4         | In Situ Characterization                  | 98  |

| 4.5         |                                           |     |

| 4.6         |                                           |     |

|             | 4.6.1 Fault Models                        |     |

|             | 4.6.2 Method                              |     |

|             | 4.6.3 Experimental Results                |     |

| 4.7         | 7 Summary                                 | 111 |

| CHAPTER 5 S | Self-Optimization for Local Variations    | 113 |

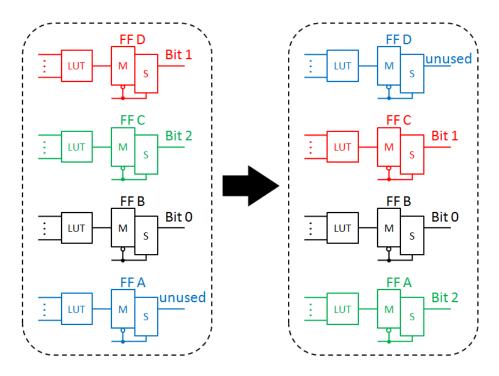

| 5.1         | Variation-Aware Re-Placement              | 113 |

| 5.2         | 2 Statistical Simulation Results          | 115 |

| 5.3         | 3 Case Study                              | 119 |

|             | 5.3.1 Problem Statement                   |     |

|             | 5.3.2 Experimental Results                | 121 |

|                 |             | 5.3.3 Limitations                                 | 126 |

|-----------------|-------------|---------------------------------------------------|-----|

| 4               | 5.4         | Discussion                                        | 127 |

| CHAPTER (       | 6 Co        | onclusions                                        | 129 |

| (               | 5.1         | Summary of Contributions                          | 129 |

|                 |             | Directions for Future Work                        |     |

|                 |             | 6.2.1 PAC-Friendly Tools, APIs, Hardware          | 132 |

|                 |             | 6.2.2 Variations of Physically-Adaptive Computing |     |

|                 |             | 6.2.3 The Problem of Heat                         |     |

|                 |             | 6.2.4 PAC in Space                                | 135 |

| (               | 5.3         | Final Thoughts                                    |     |

| <b>BIBLIOGR</b> | <b>AP</b> H | IY                                                | 138 |

# LIST OF FIGURES

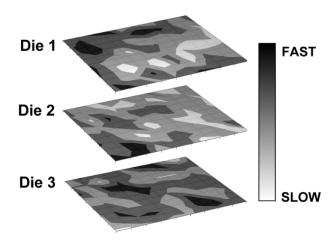

| Figure 1.1: Delay profiles for three different 65 nm dies [28]                                                                                    | 2  |

|---------------------------------------------------------------------------------------------------------------------------------------------------|----|

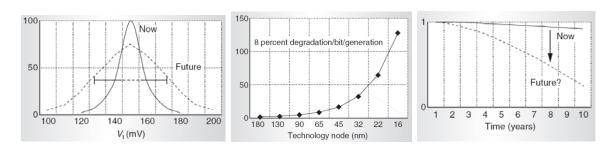

| Figure 1.2: Threats from variability (left, threshold voltage), transient faults (middle), and wearout (right, degrading transistor current) [16] | 2  |

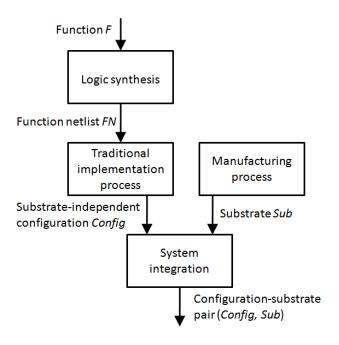

| Figure 1.3: Conceptual view of a conventional system design flow                                                                                  | 7  |

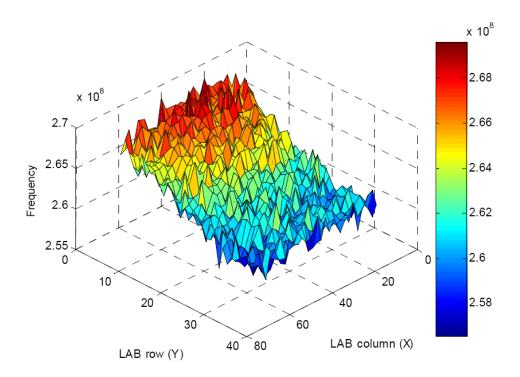

| Figure 1.4: Regional and local variations in ring oscillator frequencies across an FPGA [90]                                                      | 10 |

| Figure 1.5: Taxonomy of computing properties                                                                                                      | 12 |

| Figure 1.6: High-level diagram of an FPGA [76]                                                                                                    | 14 |

| Figure 1.7: Diagram of FPGA reconfigurable logic and interconnect                                                                                 | 15 |

| Figure 1.8: Example of a conventional FPGA design flow                                                                                            | 17 |

| Figure 1.9: Addressing physical variations and uncertainty at different times in a system lifecycle                                               | 17 |

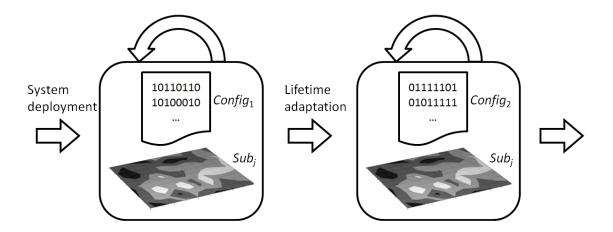

| Figure 1.10: High-level view of the PAC concept                                                                                                   | 25 |

| Figure 1.11: FPGA Compile Cloud Service proposed by National Instruments [58]                                                                     | 30 |

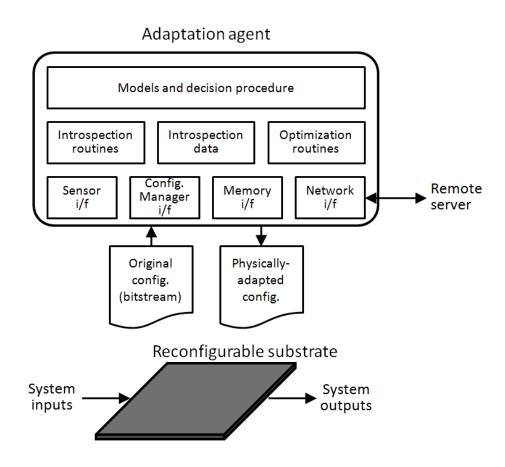

| Figure 1.12: Sketch of a generic PAC system                                                                                                       | 31 |

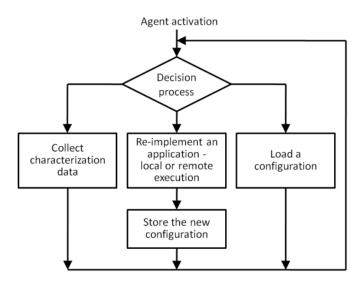

| Figure 1.13: High-level view of the adaptive loop                                                                                                 | 32 |

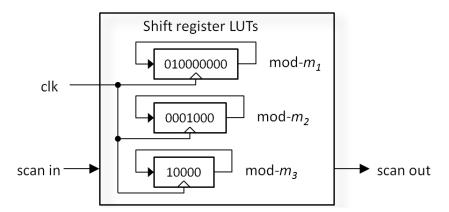

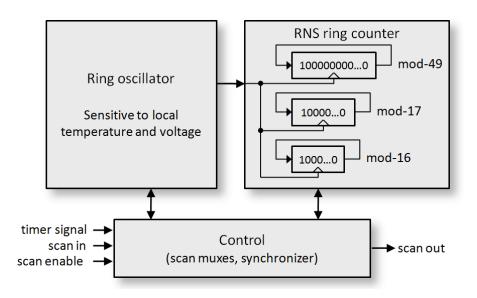

| Figure 2.1: Compact counter design using the residue number system (RNS)                                                                          | 41 |

| Figure 2.2: Sketch of algorithms to recover the count for (a) an LFSR counter [25] and (b) the proposed RNS ring counter                          | 42 |

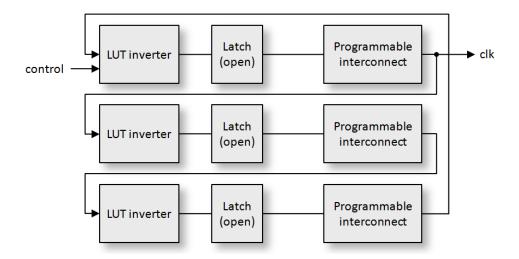

| Figure 2.3: Proposed ring oscillator design                                                                                                       | 44 |

| Figure 2.4: High-level diagram of proposed sensor                                                                                                 | 46 |

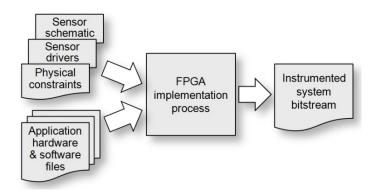

| Figure 2.5: Overview of the proposed design flow for FPGA system instrumentation                                                                  | 47 |

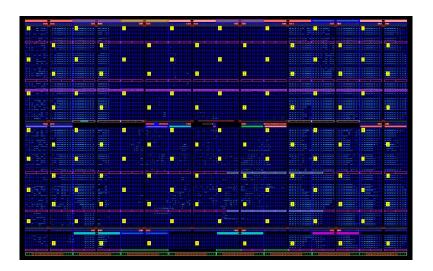

| Figure 2.6: | Floorplan of an FPGA-based system instrumented with an array of compact multi-use sensors (light-colored rectangles) implemented in reconfigurable logic | 47 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

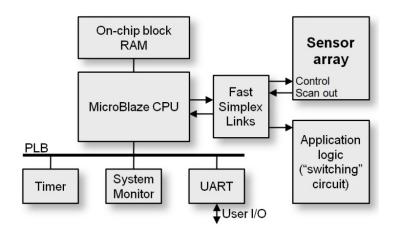

| Figure 2.7: | Block diagram of the experimental system implemented on a Virtex-5 FPGA                                                                                  | 56 |

| Figure 2.8: | Experimental setup in the thermal chamber (left); close-up of an XUPV5 circuit board (right)                                                             | 57 |

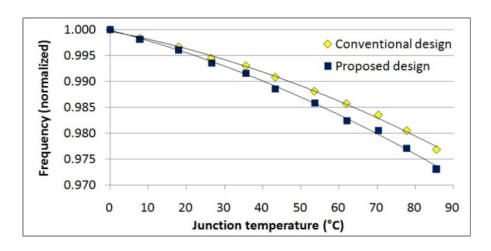

| Figure 2.9: | Frequency dependence on temperature for proposed ring oscillator design and conventional design                                                          | 58 |

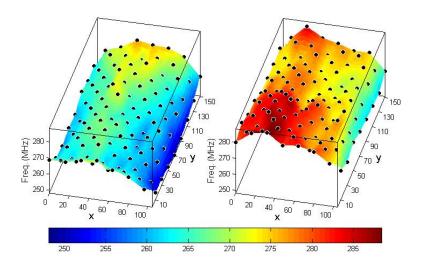

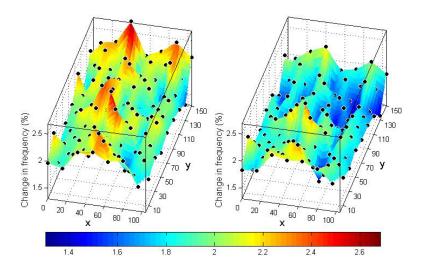

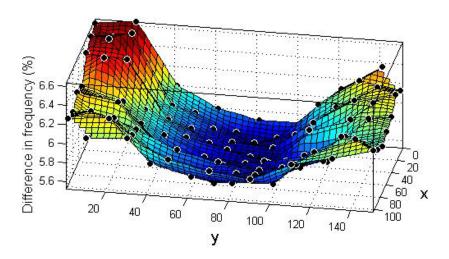

| Figure 2.10 | ): Frequency profile for chip 1 (left) and chip 2 (right) in the idle state at $T_j = 35$ °C                                                             | 59 |

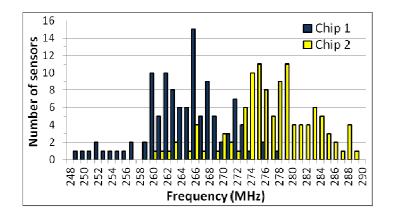

| Figure 2.11 | : Histogram of ring oscillator frequencies for chip 1 (dark) and chip 2 (light) in the idle state at $T_j = 35$ °C                                       | 59 |

| Figure 2.12 | 2: Map of leakage current variations for chip 1 (left) and chip 2 (right)                                                                                | 60 |

| Figure 2.13 | 3: Map of frequency changes due to switching activity                                                                                                    | 61 |

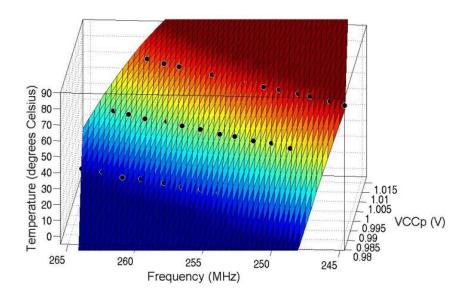

| Figure 2.14 | 4: Measured relationship between temperature, sensor frequency, and supply voltage for the sensor at (48,81)                                             | 63 |

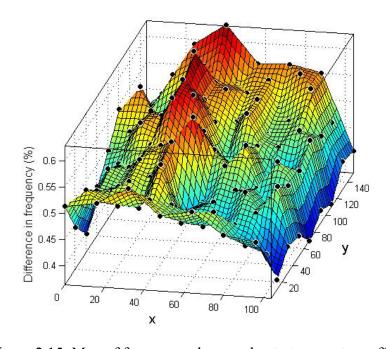

| Figure 2.15 | 5: Map of frequency changes due to temperature effects                                                                                                   | 63 |

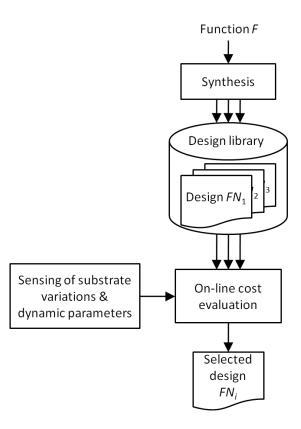

| Figure 3.1: | Dynamic selection of fittest design                                                                                                                      | 70 |

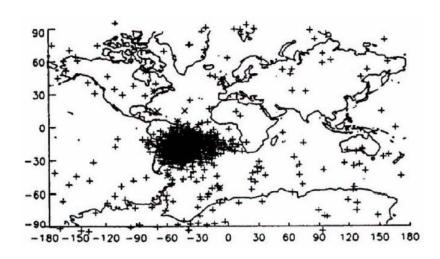

| Figure 3.2: | Large variation in radiation-induced SEUs occurring in the NASA SAMPEX mission in low Earth orbit, due to the South Atlantic Anomaly [108]               | 77 |

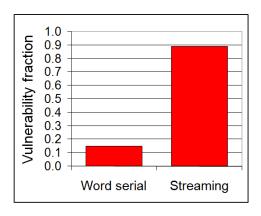

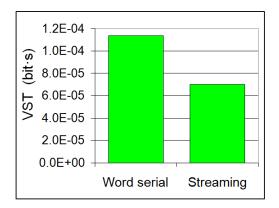

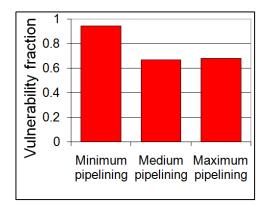

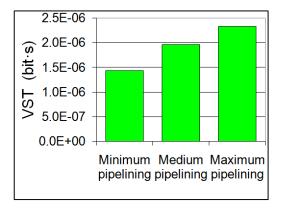

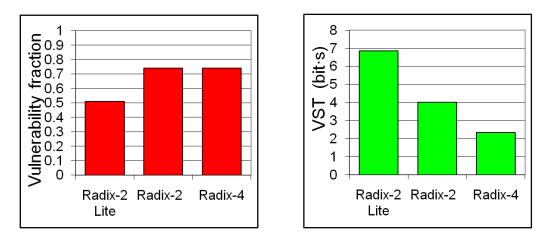

| Figure 3.3: | Traditional vulnerability fraction of CORDIC designs (left); vulnerability for CORDIC computations using the VST metric (right)                          | 81 |

| Figure 3.4: | Traditional vulnerability fraction of floating-point adders (left); vulnerability for floating-point additions using the VST metric (right)              | 82 |

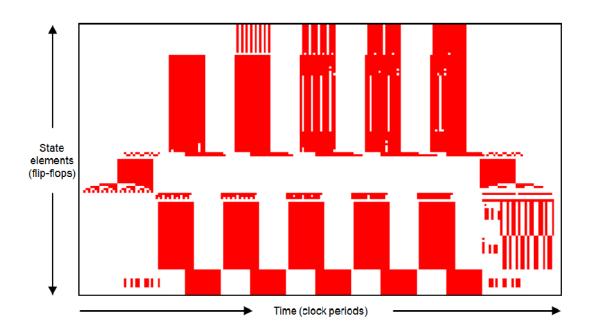

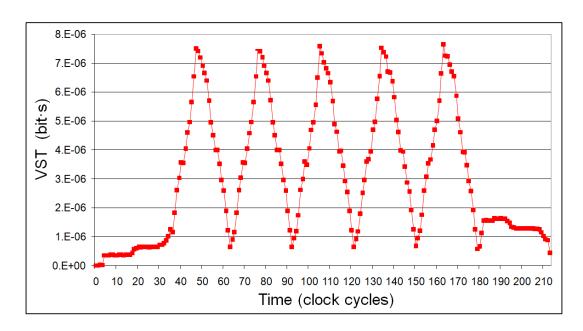

| Figure 3.5: | Portion of the vulnerability map for 32-point Radix-2 FFT                                                                                                | 83 |

| Figure 3.6: | Dynamic behavior of VST for 32-point Radix-2 FFT                                                                                                         | 84 |

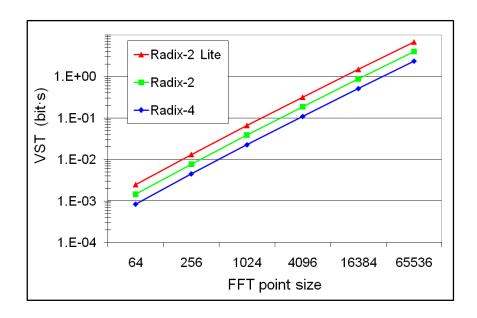

| Figure 3.7: | Projected VST for various FFT sizes                                                                                                                      | 85 |

| Figure 3.8: | Traditional vulnerability fraction for 64K-point FFTs (left); projected vulnerability using the VST metric (right)                                       | 85 |

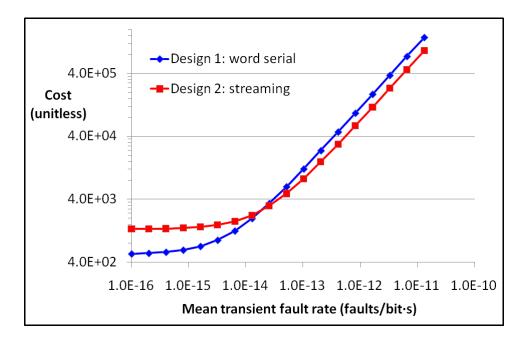

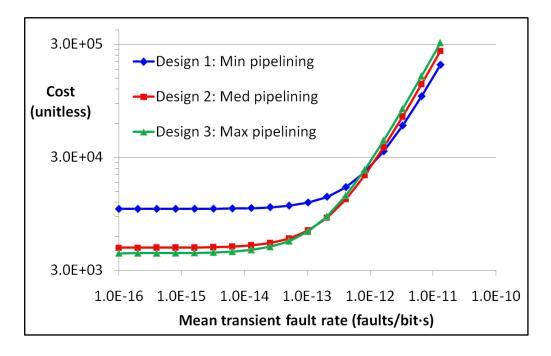

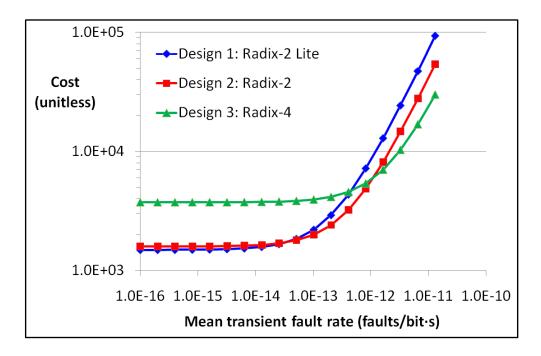

| Figure 3.9: | Cost of CORDIC designs vs. fault rate                                                                                                                                                   | 88  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 3.10 | Cost of floating-point adder designs vs. fault rate                                                                                                                                     | 89  |

| Figure 3.11 | : Cost of FFT designs vs. fault rate                                                                                                                                                    | 90  |

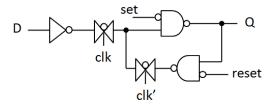

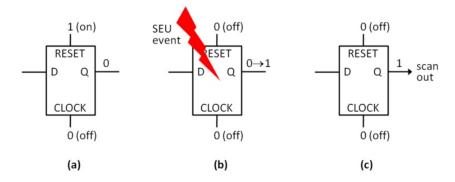

| Figure 4.1: | Example of a CMOS latch [96]                                                                                                                                                            | 96  |

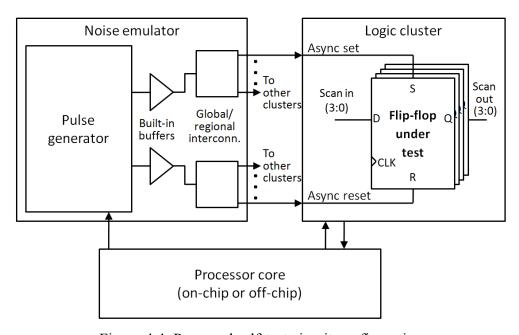

| Figure 4.2: | Example of on-line SEU characterization of level-sensitive latches                                                                                                                      | 99  |

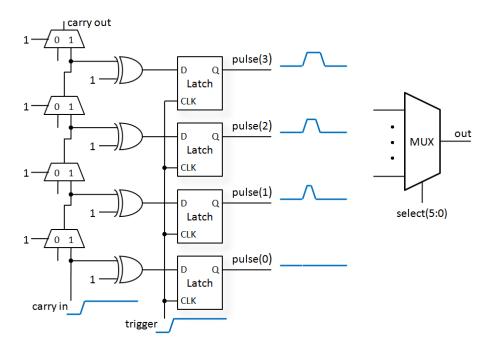

| Figure 4.3: | Portion of pulse generator circuit                                                                                                                                                      | 106 |

| Figure 4.4: | Proposed self-test circuit configuration                                                                                                                                                | 107 |

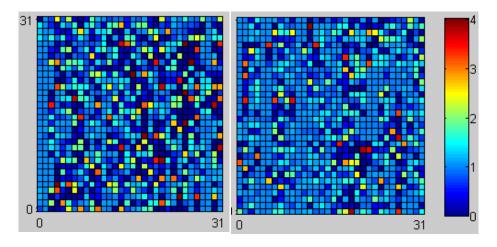

| Figure 4.5: | Local, intra-cluster variations in upsetability for chip 1 (left) and chip 2 (right)                                                                                                    | 110 |

| Figure 4.6: | Coefficient of variation $(\sigma/\mu)$ for latch upsets within a cluster in the tested noise environment, averaged over 256 clusters                                                   | 110 |

| Figure 5.1: | A cluster of logic in its original configuration with state bits (1,2,0) placed at master-slave flip-flops D,C,B (left); the same cluster after reordering of logic (right)             | 114 |

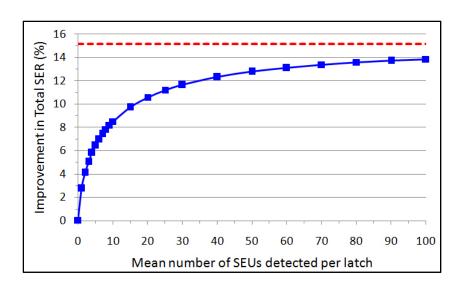

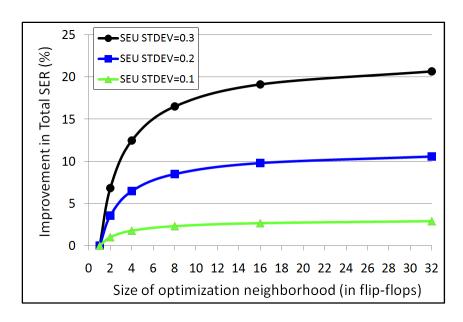

| Figure 5.2: | Improvement in SER vs. amount of SEU characterization                                                                                                                                   | 117 |

| Figure 5.3: | Improvement in SER vs. neighborhood size, for three different amounts of SEU variation                                                                                                  | 118 |

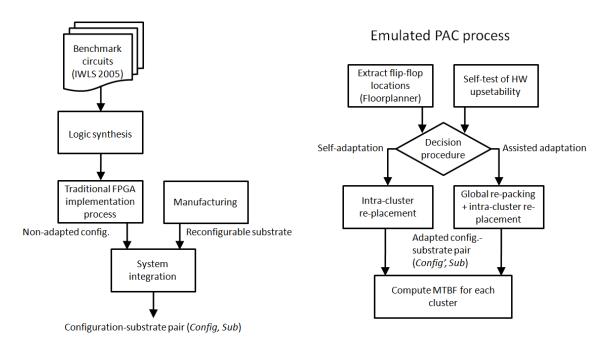

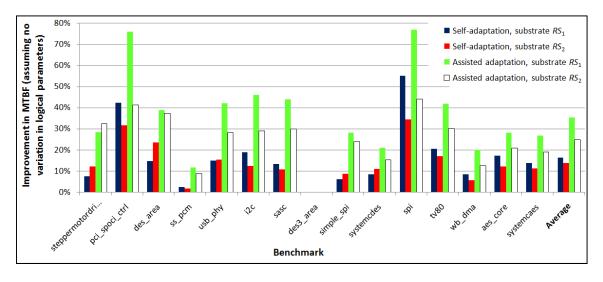

| Figure 5.4: | Traditional design flow (left) and the additional flow used to emulate the PAC process (right)                                                                                          | 124 |

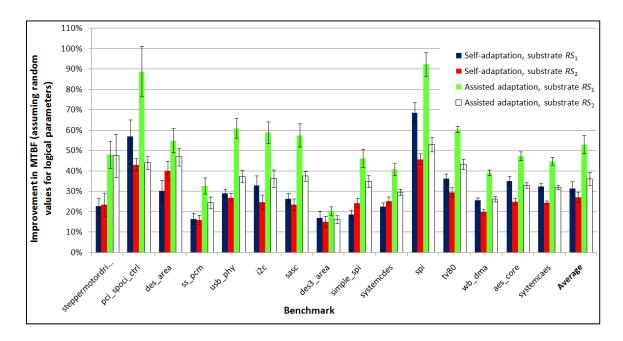

| Figure 5.5: | Results of experiment 1 showing the improvements in MTBF for self-adaptation and assisted adaptation relative to the non-adaptive case, assuming no variation in signal probabilities   | 124 |

| Figure 5.6: | Results of experiment 2 showing the improvements in MTBF for self-adaptation and assisted adaptation relative to the non-adaptive case, assuming uniformly random signal probabilities. | 126 |

# LIST OF TABLES

| Table 1.1: Semiconductor technology outlook [17]                                      | 2   |

|---------------------------------------------------------------------------------------|-----|

| Table 1.2: Organization of middle four chapters                                       | 34  |

| Table 2.1: Comparison of counter designs assuming a maximum period of 2 <sup>13</sup> | 43  |

| Table 2.2: Comparison of reconfigurable-logic-based sensors                           | 46  |

| Table 2.3: Sensor specifications                                                      | 56  |

| Table 3.1: VST of CORDIC computations                                                 | 80  |

| Table 3.2: VST of floating-point additions                                            | 82  |

| Table 3.3: CORDIC design characteristics                                              | 87  |

| Table 3.4: Floating-point adder characteristics                                       | 89  |

| Table 3.5: FFT design characteristics                                                 | 90  |

| Table 3.6: Reduction in cost after selecting fittest design                           | 91  |

| Table 4.1: Example of typical SEU contributions                                       | 102 |

| Table 5.1: Benchmark circuit characteristics                                          | 122 |

#### **ABSTRACT**

Digital electronic systems typically must compute precise and deterministic results, but in principle have flexibility in *how* they compute. Despite the potential flexibility, the overriding paradigm for more than 50 years has been based on fixed, non-adaptive integrated circuits. This one-size-fits-all approach is rapidly losing effectiveness now that technology is advancing into the nanoscale. Physical variation and uncertainty in component behavior are emerging as fundamental constraints and leading to increasingly suboptimal fault rates, power consumption, chip costs, and lifetimes. This dissertation proposes methods of physically-adaptive computing (PAC), in which reconfigurable electronic systems sense and learn their own physical parameters and adapt with fine granularity in the field, leading to higher reliability and efficiency.

We formulate the PAC problem and provide a conceptual framework built around two major themes: introspection and self-optimization. We investigate how systems can efficiently acquire useful information about their physical state and related parameters, and how systems can feasibly re-implement their designs on-the-fly using the information learned. We study the role not only of self-adaptation—where the above two tasks are performed by an adaptive system itself—but also of assisted adaptation using a remote server or peer.

We introduce low-cost methods for sensing regional variations in a system, including a flexible, ultra-compact sensor that can be embedded in an application and implemented on field-programmable gate arrays (FPGAs). An array of such sensors, with only 1% to-

tal overhead, can be employed to gain useful information about circuit delays, voltage noise, and even leakage variations. We present complementary methods of regional self-optimization, such as finding a design alternative that best fits a given system region.

We propose a novel approach to characterizing local, uncorrelated variations. Through in-system emulation of noise, previously hidden variations in transient fault susceptibility are uncovered. Correspondingly, we demonstrate practical methods of self-optimization, such as local re-placement, informed by the introspection data.

Forms of physically-adaptive computing are strongly needed in areas such as communications infrastructure, data centers, and space systems. This dissertation contributes practical methods for improving PAC costs and benefits, and promotes a vision of resourceful, dependable digital systems at unimaginably-fine physical scales.

### **CHAPTER 1**

#### Introduction

Digital systems have advanced remarkably for the past half-century. Semiconductor chips have been manufactured with increasing numbers of components exhibiting near-uniform, predictable behavior. This has allowed system architectures and programs to be designed from the top-down using a "one size fits all" strategy, independent of specific hardware characteristics or lifetime changes. This separation of the logical and physical realms has been an essential aspect of the computer revolution, allowing a single design to be incorporated into millions of systems. However, computation is physical, and as technology advances to nanoscale feature sizes, this long-standing paradigm is under threat. It is time to reconsider the complete separation between "bits and atoms."

One emerging and fundamental problem is physical variation. The spread in physical parameters such as transistor threshold voltage is growing dramatically, leading to chips with unique characteristics. An example is illustrated in Figure 1.1 [17]. Technology forecasts indicate rapidly worsening variability over the next several years, as seen in Table 1.1. The threat worsens even further at the lower supply voltages needed for low-power operation [28]. Another form of variation, wearout that occurs over time, is increasing, as are transient fault rates as illustrated in Figure 1.2 [16]. These trends are adding to the enormous costs required to develop viable manufacturing technologies.

Upon manufacturing, chips are being discarded due to marginal regions and components that fail to meet specifications, increasing costs further. Moreover, the systems built using the remaining chips are increasingly suboptimal.

Figure 1.1: Delay profiles for three different 65 nm dies [28]

Table 1.1: Semiconductor technology outlook [17]

| Date of high volume manufacturing | 2006   | 2008 | 2010 | 2012 | 2014 | 2016 | 2018      |  |  |

|-----------------------------------|--------|------|------|------|------|------|-----------|--|--|

| Technology node (nm)              | 65     | 45   | 32   | 22   | 16   | 11   | 8         |  |  |

| Billions of transistors           | 4      | 8    | 16   | 32   | 64   | 128  | 256       |  |  |

| Variability                       | Medium |      |      | High |      |      | Very High |  |  |

Figure 1.2: Threats from variability (left, threshold voltage), transient faults (middle), and wearout (right, degrading transistor current) [16]

Along with uncontrolled variation there is a second fundamental problem: growing uncertainty in physical parameters and component behavior. At fine scales it is harder to accurately model, predict, or observe subtle and complex physical interactions. During the design phase, the manufacturing process is often poorly understood and variation models are highly questionable. After years of metrology and process learning, the manufacturing models may improve, but often this is far too late to help designers [104]. Premanufacturing models and simulations can show considerable disagreement. One study of thermal gradients across a die suggests a difference of 8.6°C [66], while another sets the number at an alarming 20°C [102]. Even traditional models such as the heavily-used "bathtub" curve are becoming less effective; a large-scale study of memory reliability in Google data centers found that error rates rose unexpectedly after just 10–20 months of operation [89]. Increased integration has led to a widening knowledge gap. Thorough characterization of individual components and regions is costly. When there are over one billion transistors on a chip, the number of outliers is no longer trivial, but rather can number in the tens of millions.

These trends are impacting a wide range of semiconductor applications, especially those needing high levels of efficiency or reliability, which is to say, most applications. One domain is on-board processing in spacecraft [31][41], unmanned aerial vehicles (UAVs), and similar embedded systems. These applications often require low power, reconfigurability, well-understood soft error characteristics, and long lifetimes. Another domain is communications; routers from vendors such as Cisco often require high reliability since soft errors can have unbounded consequences [94]. High-performance computing (HPC) is another domain being impacted. As with embedded systems, there are

constraints on power and temperature. Additionally, the scale of HPC computations is too large to allow for extensive redundancy as protection against soft errors, and there is a large cost associated with frequent checkpointing, so new methods for characterizing and avoiding soft errors are needed [72]. Lastly, these trends are important not only for today's applications using CMOS-based semiconductors, but also for future applications based on emerging reconfigurable nanotechnologies [38].

Most computing systems are non-adaptive; the architectures employed and programs executed are fixed. This differs greatly from naturally occurring complex systems which are often highly adaptive. There are timely opportunities for using some principles, theory, and lessons from natural adaptive systems. At the same time, we should not expect to simply mimic nature, since computing challenges often differ in character from those faced by natural systems. Consider that computing systems are defined not only by what they can compute, but also how they compute. There is an important distinction between the former, which involves mathematical functions and abstractions such as instruction set architectures, and the latter involving physical properties such as noise susceptibility, power consumption, hot spots, and component lifetimes. Whereas the functional level of abstraction is often not amenable to adaptive approaches, there are enormous opportunities for adaptation at the underlying levels.

In this dissertation, we consider a paradigm we define as *physically-adaptive computing* (PAC). With PAC, systems learn about their physical circumstances and perform fine-grained self-adaptation in the field. In doing so, they improve their ability to meet their application-specific, physically-focused objectives, or in other words, they improve their fitness. Work addressing certain aspects of physically-adaptive computing has been

underway for many years, but significant progress has been lacking for a variety of reasons: the absence of significant physical variation in earlier semiconductor technologies, the lack of fine-grained reconfigurability, and the lack of design tool support. All of these reasons are rapidly disappearing, suggesting a prime opportunity for deploying PAC. Currently, one of the critical questions is how systems can adequately characterize fine-grained physical parameters, with little overhead. We contribute several novel, low-cost methods of sensing and self-test. Hardware experiments provide some surprising findings and previously unpublished data. A further question is how systems can feasibly optimize themselves using the information learned. We study a range of optimization mechanisms in two different physical contexts, and conduct case studies which quantify the possibilities. The contributions help to increase the benefits and decrease the costs of physically-adaptive computing, laying the groundwork for a significantly more adaptive, efficient, and reliable paradigm for digital electronic systems.

#### 1.1 General Background and Problem Definition

Here we define the relevant elements of a computing system, including the physical substrate used for computation, the set of computational functions, and the set of system parameters. We then describe the key concepts of variations and adaptation, and define the PAC research problems that we address.

**Substrate.** We define a *substrate* as physical hardware able to support computation, such as an individual microchip or portion of a microchip. We use the notation  $Sub_j$  to represent a particular substrate. Substrates have an associated *platform type*, e.g., a chip model type. Each substrate, even among those of the same platform type, is physically unique. Certain computing platforms allow for fine-grained reconfiguration of the circuit

components and interconnections. Prime examples include field-programmable gate arrays (FPGAs); detailed background on FPGA-based systems is given in Section 1.2. A configuration specifies how to configure and connect the physical elements on a substrate. A particular configuration is denoted Configi. Aside from FPGAs, there is a pronounced trend in microprocessor chips toward higher numbers of processor cores; these many-core platforms provide a form of reconfigurability but are relatively coarsegrained. A third type of reconfigurable platform uses nanoelectronics formed by self-organization rather than traditional lithography. An example is the nanoPLA, though the technology is still in the research stage [38]. Note that we refer to all of these as reconfigurable platforms, and we refer to a specific physical instance as a reconfigurable substrate.

Computational functions. A function that is to be computed will be represented by function F. It can be expressed mathematically in various ways such as with an algorithm or a finite state machine. Representations that are close to the hardware include register-transfer level (RTL) models and behavioral models using a hardware description language (HDL). We define a function netlist FN as a logical realization of F that lists the functional components and their connections. In many hardware-oriented design flows, this is a netlist generated by a synthesis tool. The function netlist in turn is implemented as a substrate configuration. There can be many functionally-equivalent configurations that implement FN. Re-implementation is a process of generating a new configuration that implements FN. Re-implementation can be performed on the original netlist FN or via direct modification of a configuration denoted  $Config_1 \rightarrow Config_2$ . Computations of a function F are performed by a  $configuration-substrate pair (<math>Config_i$ ,  $Sub_j$ ). This pair is

an important entity that will be a focus of the adaptive process. Figure 1.3 illustrates a basic, traditional flow that occurs in the design and implementation of computing systems. Although such a flow is sometimes associated with FPGA-based "hardware" development, the configuration can be considered a type of low-level software (sometimes called firmware). In fact, the flow is general enough that it could be readily modified for "software"-oriented systems, e.g., when computational functions are expressed as instruction-based programs.

Figure 1.3: Conceptual view of a conventional system design flow

**Parameters.** A configuration-substrate pair has an associated set of physical and abstract *parameters*  $\{Par_1, Par_2...\}$ . We separate the parameters into three classes containing those specific to 1) the substrate, 2) the implemented logic, and 3) system operation. The main impetus for PAC is the deep uncertainty at design time of *substrate parameters* such as the inherent performance and reliability of individual transistors and wires. If there were no such uncertainty, then the traditional substrate-oblivious approach to com-

puter engineering would be sufficient. However, uncertainty is growing and is a consequence of technology advancing towards the atomic scale. The sources of variation in substrate parameters include imperfect lithography in manufacturing, fluctuations in the number of dopant atoms or gate oxide atoms, uneven stress during operation, and many others. Logical parameters are those primarily associated with the computational logic and are independent of the substrate. Examples include signal probabilities (i.e., how often a signal is in the 1 state), toggle rates, and error propagation probabilities. Logical parameters can exhibit high levels of variation, such as logical fanouts ranging from one to more than 30 [38], and order of magnitude differences in error propagation probabilities [130]. Operational parameters are those associated with the operation of a computing system. These emerge from the act of computing and depend upon the interaction of logical, substrate, and external environmental factors. Examples include power consumption, temperature, and fault/error rates. Operational parameter variations such as thermal hot spots increase the need for physical adaptation. Certain operational parameters are also important for assessing the overall fitness of a system.

**Parameter variations.** Many of the key parameters in a computing system exhibit some form of variation. There are spatial variations in substrate parameters such as delay, and in operating conditions such as temperature. In addition, parameters can exhibit temporal variations caused by wearout or changes in activity. Wearout mechanisms are manifold and becoming harder to ignore [99], such as negative bias temperature instability (NBTI), hot carrier injection, electromigration, and total ion dose (TID). Due to variations, only a certain number of chips in a group meet the desired parameter specifications; this is the *parametric yield*.

Regional variations are those that are spread over a physical area, for instance when all transistors in a region of a chip have low threshold voltages ( $V_t$ ) due to imperfect manufacturing, or when a high-temperature region (hot spot) emerges due to uneven power consumption. These are also sometimes described as spatially-correlated or systematic variation. The *correlation distance* specifies the size of the region, e.g. a radius of 1 mm [24], for which parameters have a non-negligible correlation. *Inter-die* or *die-to-die* variation affects an entire die globally. It is sometimes considered a separate phenomenon from regional variation, but can also be thought of as a special case in which the correlation distance is much greater than the size of a die.

The second main type of spatial variation is local, spatially-uncorrelated variation, which we abbreviate as *local variation*. This occurs at a single component (transistor, wire, etc.), and has no correlation to parameter values at other locations. It is also sometimes called random variation. With nanoscale technologies, component properties can be dramatically affected by a small number of atoms. In the ubiquitous MOSFET-type transistors, electrical properties depend on the number of dopant atoms implanted during manufacturing. The number of atoms cannot be controlled precisely, leading to random dopant fluctuations that affect  $V_t$  and other parameters. Similar sources of local variation include uneven gate oxide thickness and line edge roughness. Local wearout is possible via electromigration, charge carriers becoming trapped in the gate oxide, atoms being displaced by radiation, and many other sources.

The amount of variation in a parameter is often modeled as being a sum of independent random variables representing the die-to-die, regional, and local variations:

$$\Delta Par = \Delta Par_{D2D} + \Delta Par_{reg} + \Delta Par_{local}. \tag{1.1}$$

Figure 1.4 illustrates both regional variations (e.g., the general dependence of frequency on the row location) and local variations (the spiky fluctuations), and how they combine in a single parameter.

Figure 1.4: Regional and local variations in ring oscillator frequencies across an FPGA [90]

**Transient Faults and Soft Errors.** Advanced digital electronics are prone not only to physical variations but also to transient faults and soft errors. In this context, a *transient fault* is a temporary effect triggered by noise. The fault can lead to a deviation in the state trajectory of the machine; this is known as a *soft error* because it involves an error in information but no hard/permanent damage. A soft error may in turn cause an incorrect result to be returned after a computation, a scenario sometimes called a *system-level soft error* or a *failure*. One common source of transient faults is ionizing radiation, which can take the form of alpha particles, neutrons, solar protons, heavy ions, etc. A

transient current pulse is often called a *single event transient* (SET). A transient fault that changes the value of a state element is known as an *upset* or a bit-flip, and an upset of a single storage cell is often referred to as a *single event upset* (SEU).

**Adaptation.** Adaptation is a process by which a system undergoes structural or parametric changes and becomes better fitted to an environment over time. Adaptive systems are commonly found in nature, ranging from the simplest biological species to complex ecosystems, and including human-related systems such as language, economies, and society. The system environment itself is often dynamic, meaning adaptation is ongoing and the system never settles to an equilibrium.

The general mechanisms for adaptation can include evolution, learning, self-organization, or some combination thereof. Evolution involves key concepts such as natural selection, descent with modification, genetic variations via operators (cross-over, mutation, etc.), and differential reproduction. Learning on the other hand is usually considered a process occurring in a single individual through interaction with an environment over time. Self-organization is the notion of patterns emerging via the interactions of many agents; an example is the cell differentiation that occurs during biological development. Of course, nature is complex and there are many layers, variants, and hybrids of these phenomena.

An open question is the nature of adaptation in engineered/artificial systems [45]. To what extent can such systems adapt autonomously and in a productive manner? A few words need to be said about adaptation in artificial systems. As alluded to earlier, digital electronic systems in particular are defined not only by *what* they can compute, but also *how* they compute. There is an important distinction between the former, which

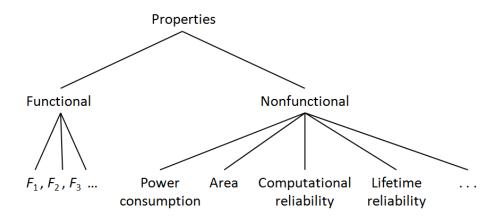

involves mathematical functions and abstractions such as instruction set architectures, and the latter involving *nonfunctional* properties. Much work in adaptive computing systems deals with the former. Examples of functional adaptation include adaptive decision making in robotic controllers, adaptive co-processing [47], some types of adaptive signal processing, and attempts at evolving digital functions in software or hardware. Enabling functional adaptation in computing systems is often a daunting challenge because much of the existing computing environment is very brittle and unforgiving of novelty. In this dissertation, we consider nonfunctional adaptation, and more specifically, adaptation that involves the physical properties of a system. A partial taxonomy of computing system properties is shown in Figure 1.5. A system has a set of functions  $\{F_1, F_2, F_3...\}$  that it can compute, and also has nonfunctional properties that tend to involve physical phenomena such as power consumption, the area used by a circuit, the reliability of computations performed, and the lifetime reliability of the physical components. Even properties such as throughput and real-time performance involve a physical resource (time).

Figure 1.5: Taxonomy of computing properties

Note that adaptation is different than dynamic feedback control. With the latter, a controller generally accepts feedback and modifies a control variable, often to bring the system to a known state. An example in digital systems is dynamic control of a system's voltage and frequency based on temperature feedback. With adaptation, the fitness land-scape is often uncertain, and a system generally finds new states with higher fitness through learning or evolution, carrying information forward via structural or parametric changes. The resources required to find better solutions can be extensive. In some cases the two concepts overlap, as in the fields of adaptive control and intelligent control.

**Problem Definition.** The main problem being addressed in this dissertation is how to foster the fittest digital systems, given spatially unique, time-variant, uncertain physical circumstances. Two of the critical research questions are: How can systems efficiently learn about their physical state and related parameters? How can systems feasibly optimize themselves and re-implement their designs on-the-fly using the information learned, given very limited system resources?

#### 1.2 FPGA-based Systems

Field-programmable gate arrays (FPGAs) are currently the most widespread reconfigurable platform and are discussed often in this dissertation. Therefore, we provide some background information on FPGA-based systems including the hardware, reconfigurability, and design flows.

#### 1.2.1 Hardware Platforms

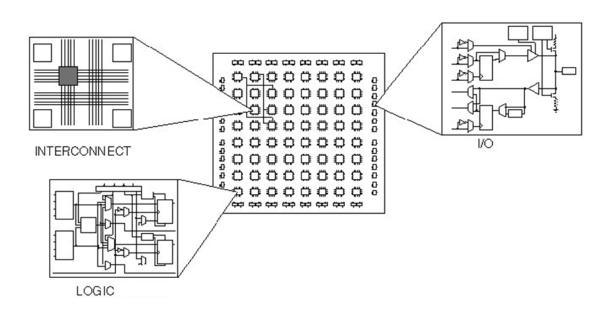

FPGAs are highly-flexible semiconductor platforms that allow many useful algorithms to be implemented efficiently; thus they are popular for signal processing, communications, and a widening range of applications. A generic FPGA platform is illu-

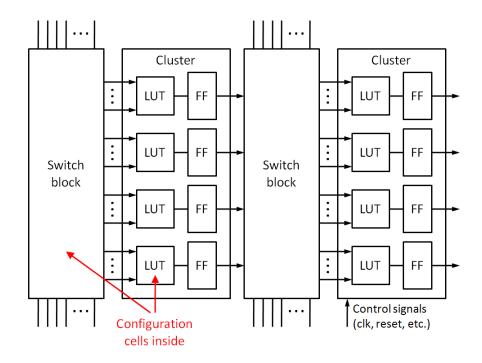

strated in Figure 1.6, with a more detailed view of reconfigurable logic and interconnect in Figure 1.7. FPGAs contain vast arrays of reconfigurable components that can be used to implement logic functions. The logic is interspersed with networks of reconfigurable interconnect, on-chip memories, and I/O blocks. The basic unit of logic is a *lookup table* (LUT) which can implement any *k*-input function; typically the *k* inputs select among 2<sup>k</sup> values stored in SRAM cells. For instance, a 6-input LUT contains 64 SRAM cells. Each LUT is paired with a flip-flop to form a *LUT-FF pair*. Logic is divided into small homogeneous *clusters* containing several LUT-FF pairs. Clusters are sometimes called slices in Xilinx terminology or logic array blocks (LABs) in Altera terminology. The amount of circuitry can be enormous, approaching one million LUT-FF pairs per chip.

Figure 1.6: High-level diagram of an FPGA [76]

Figure 1.7: Diagram of FPGA reconfigurable logic and interconnect

An example of an FPGA type is the Xilinx Virtex-5, which is a fifth-generation, high-performance family. A specific model in this family is the Virtex-5 110T. All Virtex-5 FPGAs have clusters (slices) containing four LUT-FF pairs. Two clusters form what is called a *configurable logic block* (CLB). The interconnect consists of wires and programmable switches inside switch boxes and local connection boxes; many of the routing details are proprietary. In addition to the elements mentioned, the chips include hard macros such as DSP blocks, high-speed network interfaces, and sometimes entire processor cores.

#### 1.2.2 Reconfigurability

FPGAs can be reconfigured by writing a new pattern into the on-chip configuration memory. Most FPGAs such as the Virtex-5 are SRAM-based, meaning the configuration bits are stored in volatile, on-chip static random access memory (SRAM). A configuration is streamed into the chip from an external nonvolatile memory whenever a chip is

powered up; for this reason a configuration is also sometimes referred to as a *bitstream*. Certain FPGAs include nonvolatile configuration memory (e.g., flash memory) right on the chip. A third type of platform uses anti-fuses to represent the configuration, but these platforms are only one-time programmable and of little interest for adaptive computing.

FPGA configurations can contain tens of millions of bits and are streamed into chips at bandwidths on the order of gigabits per second; thus the configuration time can be on the order of milliseconds. This delay has been a persistent roadblock to functionally-adaptive computing intended to operate at the time scale of individual computations and sub-computations. Support for *partial* reconfiguration is improving, creating new opportunities. In any case, low-overhead adaptation at coarser time scales—such as hours, minutes, or even seconds—can already be achieved, which bodes well for physical adaptation.

## 1.2.3 Design Flow

Figure 1.8 depicts a conventional FPGA design flow. The user provides an application description, such as a function F described in HDL, along with application-specific constraints for the various tools. The function is synthesized to a technology-independent netlist FN using an electronic design automation tool. In newer "high-level synthesis" flows, the function is described using a C-like language and synthesized with a separate tool. In any case, the remaining steps are normally performed by FPGA vendor tools. The netlist is mapped into the primitives of a targeted FPGA platform. After this "technology mapping," a placement tool assigns all elements to a physical location. The mapping and placement tools are also responsible for "packing" the logic into cluster-size groups [2]. After placement, a routing tool makes all the necessary connections using the

reconfigurable interconnect. Lastly, a configuration (i.e., bitstream) is generated and stored for eventual download to an FPGA chip of the appropriate type.

Figure 1.8: Example of a conventional FPGA design flow

Figure 1.9: Addressing physical variations and uncertainty at different times in a system lifecycle

#### 1.3 Related Work

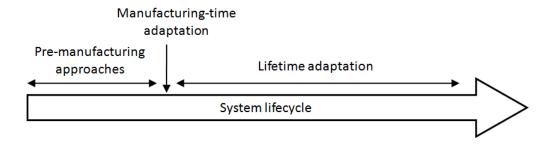

The concept of physically-adaptive computing has connections to research in on-line adaptation of integrated circuits, reconfigurable computing, the general study of adaptation, and many others. We classify the previous work into three broad classes: pre-

manufacturing approaches, manufacturing-time adaptation, and lifetime adaptation (Figure 1.9).

## 1.3.1 Pre-Manufacturing Approaches

As a stopgap measure, there have been efforts to address variability in a nonadaptive way at pre-manufacturing design time. For instance, extra safety margin can be added to a design. The amount of margin required is estimated, based in part on a general model of the expected variability. A second approach involves timing analysis with statistical models of delay rather than worst-case models. The objective is to design a circuit that can be manufactured with higher yield at a given frequency, using the facts that delays are usually better than worst case and that local, normally-distributed variations may cancel out over many components. Two examples of statistical static timing analysis of FPGA applications are given in [91] and [59]. Such efforts are sometimes called "variation-aware design," though in actuality they are only aware that variability will be present and not aware of what the specific variations will be in a manufactured chip. They are better described as variation-tolerant.

Another approach that occurs before chip manufacturing is work to improve the manufacturing process itself. Advanced semiconductor processes are developed over a period of years and require extensive modeling, equipment development, test chips, and new fabrication plants. It is well known that the investments required are enormous and growing. Sizable efforts are needed to minimize parameter variation and uncertainty, since the traditional, non-adaptive paradigm depends on manufacturing consistent and well-behaved components. Part of the rationale for PAC is reducing these costs and making better use of inherently variable substrates.

Pre-manufacturing approaches are inherently oblivious to the unique characteristics of physical substrates. Moreover, they do not address changes that occur in the field to workloads, external environments, or substrate parameters. Therefore we focus on physically-aware approaches, both at manufacturing time and in the field.

#### 1.3.2 Manufacturing-Time Adaptation

Some compensation for physical effects is possible at manufacturing time. At-speed testing of dies on a wafer allows worst-case timing to be determined and chips to be placed into a speed bin or discarded altogether. Testing is also performed for defects. Defects are permanent hardware faults, and can be thought of as an extreme type of highly localized variation. Faulty logic or memory can sometimes be permanently swapped out for spares using fuses [46]. With FPGAs, application-independent methods are pessimistic since many faulty components and worst-case paths would not actually be activated by an application. Moreover, screening for marginalities will not work if *every* manufactured chip has marginalities. The ITRS roadmap warns that the gray area between good and bad will expand, with effects such as "non-catastrophic gate oxide breakdown or highly resistive vias" [52].

A more customized approach is to test chips based on application-specific requirements. The prime example is Xilinx's EasyPath service [115]. A customer submits up to two configurations needed by their application. The configurations are fed into a Xilinx internal tool which generates the appropriate chip tests. For instance, an application typically uses only 1%–10% of a chip's configuration cells, and thus those are the only ones tested. Chip yield greatly improves because many chips with don't-care defects can still be shipped. Since the manufacturing costs can be amortized over more good dies, chip costs are reduced by up to 75%. With the Virtex-6 and entire "7 Series" of FPGAs, Xi-

linx guarantees a cost reduction of at least 35% [115][116]. Application-specific screening does not enable the full benefits of customizing an application to an individual die. In fact, adapting in the field is problematic since faults and marginalities may be lurking in the untested resources.

The next level of manufacturing-time customization is to actually create a map of the variations on each chip and to generate a customized implementation of the application. A proposal for this is presented in [24], using variation-aware place and route and FPGAs. However, the costs are high to use expensive testers for fine-grained characterization, to perform resource-intensive computer-aided design cycles, and to handle large numbers of unique configurations.

A further limitation of all of these manufacturing-time approaches, as with premanufacturing approaches, is that they do not address parameter shifts that occur in the field.

#### 1.3.3 Lifetime Adaptation

The research most closely aligned with this dissertation involves lifetime adaptation in digital systems. Historically, a driver for such approaches was the threat of hard faults appearing in the field and the need for fault tolerance. There have been proposals for handling FPGA defects via self-test and re-routing using a lightweight routing tool that runs in the system itself [62][30][105][83]. These ideas provide a starting point but leave unaddressed important issues such as correlated variations, the role of computational activity (e.g., affecting thermal hotspots or data-dependent wearout), and how to make use of functioning but marginal elements.

One proposed strategy for adapting to unique reconfigurable substrates is to generate a large number of implementations at random and to allow each system to identify the most suitable alternative through trial and error [48][67]. While sufficient for avoiding a small number of defects, this approach does not work well for large systems subject to variations on multiple scales. A randomly generated configuration is unlikely to provide a close fit.

A little preliminary research has addressed the combination of self-characterization of variations, and subsequent optimization of configurations. Some of these studies have focused specifically on the problem of delay variations, in FPGAs [54] or in a non-CMOS reconfigurable technology [38]. Several works have focused just on self-characterization of variations, for instance involving circuit delay [112]. Another set of studies has considered variation-aware optimization techniques using signal polarity inversion [129], technology mapping [92], re-placement [24], and logical-physical mapping in a memory array [79]. A relevant theoretical study of variation-aware optimization is given in [91]. Note that these optimization techniques all depend on accurate characterization data being available.

Some early progress has been made regarding adaptation in integrated circuits [103] and microprocessors [8]. A method of measuring leakage variations on a per-core basis has been proposed [127]. Many of the methods for many-core processors, such as the use of analog sensors and instruction set-based error detectors, are not generally applicable to reconfigurable platforms such as FPGAs, but the goals of introspection and resiliency are consistent with the theme considered here.

Whereas the focus of this dissertation is physical adaptation, related research has been carried out in functional adaptation and adaptive computing. Some of the problems addressed include dynamic switching between previously-generated FPGA configurations implementing different algorithms, finding effective adaptive control policies, and the design of application-specific instruction sets. Some works in functional adaptation share with PAC a need for in-system implementation of computations [107] or on-board decision making. Examples of cognitive architectures for adaptive computing systems include a Bayesian network-based architecture [33], a genetic algorithm-based classifier system [10], and a reinforcement learning-based controller [86]. Autonomic computing is another related area, involving the study of self-management and other so-called self-\* properties in computing systems [29]. Much of the work is conducted in the logical realm [88][68].

Some related work involves coarse-grained feedback control of physical parameters. Examples of control schemes for computer systems include chip-wide dynamic voltage/frequency scaling [51][10] and thermal/power management in data centers [49]. These architectures tend to be dynamic but not adaptive. Methods of voltage/frequency scaling for many-core processors are being developed, where each voltage/frequency domain contains multiple cores [28].

A recent related research topic is cyber-physical systems, where computer and communication technologies are used to control an external physical system. Since PAC is focused on physical phenomena in the computer system itself, it is largely complementary to that work. The autonomous adaptation aspect of PAC suggests connections to the broader fields of engineered adaptive systems and intelligent systems. For instance, a study of self-modeling robotic systems deals with the analogous challenge of adapting to a substrate prone to wearout/damage [15].

In summary, PAC research builds upon and has ties to several other research areas, but at the same time poses some distinct and important research questions of its own.

### 1.4 Proposed PAC Framework

In this sub-section, our approach and general architecture for physically-adaptive computing is proposed. Detailed methods and results follow in the subsequent chapters. Portions of this sub-section were published in [134].

### 1.4.1 PAC Definition

We define a *physically-adaptive computing (PAC)* system as one in which system configurations are optimized to suit the physical landscape, leading to higher fitness. The general approach proposed here is based on periodic, fine-grained introspection and self-optimization controlled by an adaptation agent.

#### 1.4.2 Fitness

In the context of digital electronic systems, *fitness* is a measure of how well a system is meeting its application-specific objectives. It is sometimes more convenient to use the concept of minimizing cost rather than maximizing fitness. We use the terms fitness and cost interchangeably, with the understanding that lower cost corresponds to higher fitness.

Cost functions are used to define the cost for a given solution among the immense space of possible solutions. The cost can be a function of parameters associated with the solution. For example, the FPGA vendor Xilinx uses the following linear weighted cost function to evaluate different implementations of an application [122]:

$$Cost(Config) = w_1 \times (wire\ length) + w_2 \times (timing) + w_3 \times (power)$$

(1.2)

Cost functions are commonly used in computer-aided design but traditionally do not account for the unique characteristics of the substrate. We propose a new approach in which cost is instead defined for a (*Config*, *Sub*) pair:

$$Cost(Config, Sub) = f(Par_1, Par_2, Par_3 ...)$$

(1.3)

# 1.4.3 Introspection

In the context of PAC, introspection is the process of a system learning about its own parameter values and the phenomena affecting its fitness. This generally involves obtaining data, using the data to estimate the related parameters, and sometimes building internal models. One method of obtaining data is internal sensing. This is appropriate for regional variations since the parameter value at the sensor location is correlated to the surrounding region. A second method is self-test of component parameters; this addresses local variations that occur at individual components.

In the domains of intelligent control and more specifically autonomic computing, sensor feedback data tends to be always available. This is considered automatic sensing. Introspection in PAC goes further in that there are more extensive requirements for *active sensing*. An adaptation agent may need to decide which of many parameters to characterize and then take actions to obtain data, for instance by initiating an appropriate self-test procedure.

System configurations, as encoded in bitstreams, act as models of the computing system that can be used to reason about logical structure, physical placement, etc. An agent can also build a model of the physical substrate, by collecting sensor data and estimating the physical parameters. In the case of spatially-correlated variations, the agent can acquire data samples and build a model of a parameter profile across the entire substrate.

For instance, a model could be built that has a quadratic dependence on the x and y positions on the die:  $Par(x,y) = ax^2 + by^2 + cx + dy + e$ . Building and maintaining detailed models can be demanding [44]. It has been claimed that the best model of the world is the world itself. In this sense, the agent can sometimes collect local physical data and immediately perform local self-optimization, without the need for building and maintaining a full variation map.

# 1.4.4 Self-Optimization

Self-optimization in the context of PAC is the process of a system finding new configurations with higher fitness, given a physical substrate and environment (Figure 1.10). This includes generating and validating the configurations. Generally, the generation of alternative configurations cannot be done at random but rather needs to be informed by the fine-grained introspection mentioned above. The opportunities for optimization in reconfigurable systems are many, including local logic swapping, adaptive body bias, selection of new netlist-level designs, LUT input re-ordering, inverted encodings, resynthesis, re-mapping, re-packing, re-placement, and re-routing.

Figure 1.10: High-level view of the PAC concept

#### 1.4.5 Time Scale

The intent with PAC is for self-adaptation to occur periodically as needed. Upon first being deployed, a system can direct a broad set of physical adaptations to account for manufacturing variations. For example, optimizing the circuit placement or body bias may enable a slight reduction in supply voltage, thereby decreasing dynamic and static power consumption. Following this initial period, a system can continue to adapt periodically to match the time scale of significant shifts in parameters. The adaptation loop can require tens of milliseconds for reconfiguration alone, so certain high-frequency dynamic behavior cannot be addressed by PAC in real-time. Dynamic voltage scaling can occur within one hundred microseconds [51]. Similarly, unintended dips in the supply voltage can occur on the order of microseconds. However, many important phenomena can have time scales that are much longer. Temperatures and workloads can sometimes change significantly over seconds and minutes. Solar events can increase the radiation flux by four orders of magnitude for periods of hours or days [35]. Aging effects may occur over a period of weeks. Moreover, even high-frequency phenomena can sometimes be addressed indirectly. For instance, while an adaptation loop is typically not quick enough to respond to a specific voltage transient, it can be used to mitigate systematic problems detected, such as recurring voltage transients in a specific location.

### 1.4.6 Fine Granularity and FPGAs

We define physical phenomena as fine grained if they have a length scale or time scale much smaller than that of an entire computation. This includes most intra-die variations such as various "hot spots" and random local variations. Correspondingly, methods of introspection and self-optimization should be considered fine grained if they have a resolution similar to the phenomena of interest. Examples include the ability to sense

spatial variations at scales much finer than the correlation distance, the ability to perform self-test on small blocks such as individual latches, and the ability to re-arrange logic functions or re-route around individual wires or switches.

Approaches with only chip-level spatial granularity are coarse by comparison. Examples include chip-wide voltage or frequency scaling, and chip-wide adaptive body bias. A middle ground is granularity at the processor core level. As many-core processors become common there is growing use of sensing and control methods affecting one or a small number of cores. It has even been argued that the processor "core has become the new transistor" [78]. While this may be true from a system architect's point of view, it is not sufficient for PAC. Many of the phenomena motivating PAC are much finer than a processor core which can contain millions of transistors. Imagine the vias connecting wires on adjacent layers of a chip; highly-resistive vias are expected to become a common problem according to ITRS projections [52]. If the only compensation method is to turn off an entire processor core, system efficiency will drop precipitously.

For the above reasons we believe the case is strengthening for finely reconfigurable platforms such as FPGAs. These enable sensing on the scale of small clusters, and reconfiguration at the level of LUT, flip-flops, wires and switches. It may even become possible to infer the properties of individual transistors inside latches, as will be seen in Chapter 4.

There is an important additional rationale for FPGA-based implementations. They tend to have a moderate density of power and heat, since the logic is spread across islands surrounded by interconnect, and many resources are left unused. Previously, this low density and higher resulting cost per chip were considered significant disadvantages in

many domains. Application-specific integrated circuits (ASICs) and microprocessor units (MPUs) were much denser, providing higher performance and lower cost per chip at high volumes. However, the situation is changing dramatically as power and heat densities severely constrain the scaling trends. Dense platforms are generating more heat than can be easily removed from a system, forcing much of a chip to be left idle. Some studies of many-core processors have indicated that the majority of the cores must be idle, a problem sometimes called "dark silicon." In a recent keynote address, ARM's Chief Technology Officer Mike Muller projected that by 2020 and the arrival of 11 nm technology, the power budget may only allow 9% of a chip's transistors to be active at any one time [70]. Thus the density advantage of ASICs and MPUs over FPGAs is less compelling. In some domains, the choice will be between a dense, fixed architecture in which most of the logic is idle, and a sparse, reconfigurable architecture capable of much finergrained PAC. For an increasing number of applications the finely-reconfigurable platforms are likely to win out.

# 1.4.7 Assisted Adaptation

We define *self-adaptation* as a process of system adaptation that is controlled and executed by a system itself. We define *assisted adaptation* as a special type of self-adaptation in which some of the resources for the adaptation process are provided by a remote server or peer. A portion of the introspection and/or optimization tasks are offloaded.

With PAC, the time scale of parametric shifts can be very long relative to the timescale of computations. For instance, substrate parameters may change over a period of many days due to wearout. Moreover, some portions of the physical adaptation process can require more resources than are available in the system. This characteristic of needPAC system off-loads portions of the adaptive process to a remote server. For instance, standard place and route tools generally require server-class memory and computing resources and cannot feasibly run on a highly-constrained embedded system. Likewise, estimation of certain logical parameters, such as error propagation probabilities using statistical fault injection, can require high-performance computing.

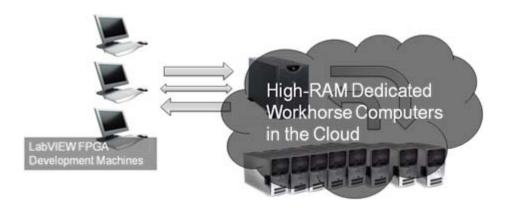

Offloading execution to a remote machine has been realized in more abstract contexts such as "cyber-foraging," in which a highly-constrained system searches over a network for usable resources [39]. Now there are several indications that such an approach holds promise in the PAC context. Embedded systems with network connections are proliferating, and there have been significant advances in "cloud computing." As an example, frameworks are being developed for evaluating the energy efficiency of local vs. remote execution [60]. Second, preliminary studies such as one by Hyder et al. [48] illustrate remote execution for a type of physical adaptation, using multiple systems that are peers instead of using a server. Third, missions such as the Cibola Flight Experiment have demonstrated that many of the pieces are already in place [19]. In that mission, physical data regarding faults and temperature swings on FPGAs is regularly transmitted to the ground. After re-design and refinement on the ground, new FPGA configurations are securely uploaded to the spacecraft. Up to 20 uncompressed configurations can be maintained on-board. Though not fully automated and not as fine grained, the process is analogous to assisted adaptation. Lastly, the first cloud for compiling FPGA applications came into existence in 2010 courtesy of National Instruments [58]; see Figure 1.11. The LabVIEW FPGA 2010 beta tool allows compilation jobs to be farmed out to a cloud.

The jobs are performed in a fault-tolerant fashion by machines with high amounts of RAM and located at data centers operated by Amazon, Microsoft, or others. Advanced security measures are employed just as with other high-security applications. Thus much of the infrastructure needed for assisted PAC is arriving.

Figure 1.11: FPGA Compile Cloud Service proposed by National Instruments [58]

# 1.4.8 Proposed Architecture

We now outline an architecture for a PAC agent. The main objective of the agent is to generate physically-adapted configurations that optimize fitness. It has at its disposal a set of interfaces, a library of routines, a bitstream containing the original configuration, and introspection data. It uses these to build and reason about internal models, and to take appropriate actions.

The actions available to the agent can be categorized as follows. 1) Introspection: the agent must seek out data to help in estimating parameter values. Examples include performing a self-test of the reconfigurable substrate, collecting sensor data, and requesting logical data about an application from a remote server. 2) Optimization: the agent must decide whether to re-implement some or all of an application, and by which method. Examples include performing incremental re-placement or re-routing, inverting signal

polarities [129] to compensate for data-dependent wearout, and requesting a full variation-aware re-implementation cycle from a remote server. 3) Selection of configurations: the agent may need to load a self-test configuration, load a newly implemented configuration so it can be validated on the substrate, or load a validated configuration having the highest fitness.

A generic PAC system is sketched in Figure 1.12. The adaptation agent process executes periodically as needed, either on a separate processor chip, on a hard core that is part of the same substrate (e.g., a PowerPC or ARM core [123] in Xilinx FPGAs), or even on a soft core implemented in the reconfigurable logic.

Figure 1.12: Sketch of a generic PAC system

The decision procedure for the adaptation agent can take a variety of forms. When the adaptation process is straightforward, a rule-based decision procedure may be sufficient. An example of a simple rule is, "If the time since the last self-test is at least 24 hours, run self-test now." This will be the approach used in the case study presented in Chapters 5 and 6. A question for future work is the extent to which the decision procedure itself can be made adaptive. A variety of cognitive algorithms have been proposed for use in adaptive computing systems [33][10][86].

A simplified flow of the adaptation process is shown in Figure 1.13. In contrast with some previous flows of this type [105], the process need not be a linear progression of characterization-optimization-reconfiguration. The agent may need to repeat certain types of actions, schedule actions to be performed remotely, and compete for resources with other agents.

Figure 1.13: High-level view of the adaptive loop

Here is a brief example of a PAC scenario. After a specified time interval, the operating system activates the adaptation agent. The agent decides to collect sensor data

while the rest of the system operates normally. After processing, the data indicates that one region of the substrate is operating much more slowly than average. The agent must query the sensors a second time in case the slowdown was caused by a transient phenomenon such as a voltage "droop." When the problem persists, the agent requests that a self-test of the substrate be performed at the next available opportunity. The self-test data confirms an inherent slow region in the substrate. Since the problem is regional and not highly localized, a global optimization algorithm requiring server resources is in order. The agent sends the relevant data to a remote server and requests that a new configuration be generated. The agent process terminates and the rest of the system continues operating. Within 24 hours the adapted configuration is securely uploaded to the system. The agent is re-activated and requests that the new configuration be loaded and validated. Upon success, the new configuration is put into service and system health is evaluated. The original substrate-independent configuration is maintained as a backup. The agent process then terminates until the next interval.

#### 1.5 Dissertation Outline

The main contributions of this dissertation are a conceptual framework for physically-adaptive computing, new methods of introspection, previously unpublished evidence of physical variations, and new methods of self-optimization.

The middle four chapters of this dissertation are organized along two dimensions as shown in Table 1.2. Chapter 2 covers the problem of estimating regional variations in system parameters. We introduce a flexible, highly-compact sensor that can be implemented with reconfigurable logic and embedded in an application. An array of such sensors can be used by a system to gain useful information about delays, voltage transients,

and even leakage variations. We then cover self-optimization for regional variations in Chapter 3. We demonstrate PAC at the level of function netlists, and conduct case studies of three applications. In the case studies, we suggest using a computational vulnerability parameter in the cost functions, and we introduce a comprehensive soft error metric for this purpose. Results show that by identifying and selecting the design best fitted to a region, fitness can often be improved by 30%–40%.

Table 1.2: Organization of middle four chapters

| Торіс               | Introspection | Self-<br>Optimization |

|---------------------|---------------|-----------------------|

| Regional variations | Ch. 2         | Ch. 3                 |

| Local variations    | Ch. 4         | Ch. 5                 |

Chapter 4 covers introspection for local physical variations. We conduct a unique study of local variations in transient fault reliability and establish limits of conventional characterization. We then propose on-chip noise emulation as a much more feasible method of self-characterization. As a proof-of-concept, we demonstrate an FPGA-based system capable of injecting noise into latches and uncovering previously hidden variations. Chapter 5 is a study of self-optimization for local variations, using the introspection results from Chapter 4. For instance we evaluate the use of re-packing and local replacement on a set of benchmark circuits to compensate for random variations, and show how reliability can be improved via low-cost self-adaptation as well as assisted adapta-

tion using a remote server. Lastly in Chapter 6, we summarize our contributions, identify directions for future research related to PAC, and provide some final thoughts.

# **CHAPTER 2**

# **Introspection for Regional Variations**

Regional variations in physical parameters are leading to excessive power consumption, thermal hotspots, and reduced performance and reliability. Methods of low-cost, *insystem* characterization are needed. This type of introspection is one of the key aspects of PAC

While some FPGA platforms include a single analog temperature and voltage sensor, they do not provide a means of measuring a variety of quantities at arbitrary locations. Thus one challenge is to use the standard digital logic in a reconfigurable fabric to measure as many key physical parameters as possible, and as unobtrusively as possible.

The key research questions include the following: Which types of physical parameters can be measured in reconfigurable systems? How can they be measured, and with what overhead? This chapter addresses these questions. The main contributions of this work, which was originally published in [132], are the following:

- The design of a flexible, compact, and easy-to-use sensor implemented in reconfigurable logic

- Improved procedures for measuring variations in delay, leakage power, dynamic power, and temperature

A case study of a Virtex-5-based experimental system instrumented with over 100 sensors, including results from thermally-controlled experiments

# 2.1 Background