# EFFICIENT MONTE CARLO BASED METHODS FOR VARIABILITY AWARE ANALYSIS AND OPTIMIZATION OF DIGITAL CIRCUITS

by

Vineeth Thazhathu Veetil

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 2010

#### **Doctoral Committee:**

Associate Professor Dennis Michael Sylvester, Chair Professor David Blaauw Professor Marios C. Papaefthymiou Professor Romesh Saigal

#### **ACKNOWLEDGEMENTS**

I am deeply indebted to Prof. Dennis Sylvester and Prof. David Blaauw for their excellent guidance throughout my PhD. Their insights and timely suggestions on numerous occasions have steered many of these projects in the right direction. I have truly learned a lot working with them. I would also like to thank Prof Marios Papaefthymiou for several discussions regarding the project and otherwise.

I am also very thankful to my family - father, mother, Anoop, Deepa and Smitha for their support throughout. Of course, Sharon for her encouragement and company in difficult times. I am grateful to my labmate Yung-Hsu Chang who played a major role in the completion of the project on acceleration of statistical timing analysis using Graphics Processing Units. Also thanks to Kaviraj Chopra, Sanjay Pant, Ravikishore Gandikota, Vivek Joshi, Cheng Zhuo, Mingoo Seok, Ashish Srivastava and Shantanu Gupta for their help and inputs on various occasions. Special thanks to Brian Cline, Matt Fojtik and Dave Fick for always being available to help with computing infrastructure issues.

I also gratefully acknowledge Nvidia Corporation for their donation of the Tesla GPU sytem.

# TABLE OF CONTENTS

| Acknowledgements                                                         | ii  |

|--------------------------------------------------------------------------|-----|

| List of Tables                                                           | vi  |

| List of Figures                                                          | vii |

| CHAPTER I: Introduction                                                  | 1   |

| I.1. Timing Analysis and Optimization                                    | 3   |

| I.1.1. Variability Aware Timing Analysis                                 | 4   |

| I.1.2. Variability Aware Optimization                                    | 7   |

| I.1.3. Gate Delay Modeling                                               | 8   |

| I.2. Standby Power: Leakage Analysis                                     | 10  |

| I.3. Overview of Monte Carlo Variance Reduction                          | 12  |

| I.3.1. Quasi Monte Carlo                                                 | 13  |

| I.3.2. Stratified sampling                                               | 15  |

| I.3.3. Latin Hypercube Sampling                                          | 16  |

| I.4. Thesis Overview and Key Contributions                               | 17  |

| CHAPTER II: Efficient Monte Carlo based Incremental Statistical Analysis | 0   |

| II.1. Introduction                                                       | 20  |

| II.2. Smart sampling based on timing criticality                         | 23  |

| II.2.1. Process variation model                                          | 23  |

| II.2.2. Stratification+Hybrid Quasi Monte Carlo(SH-QMC)                  | 24  |

| II.2.3. Timing criticality Pcrit                                         | 26  |

| II.3. Pruning based algorithm for timing analysis                        | 27  |

| II.4. Incremental Evaluation of a Percentile Delay                       | 29  |

| II.4.1. Algorithm                                                                                                       | 30   |

|-------------------------------------------------------------------------------------------------------------------------|------|

| II.4.2. Computing circuit arrival time bound for samples                                                                | 32   |

| II.5. Results                                                                                                           | 34   |

| II.6. Summary                                                                                                           | 41   |

| CHAPTER III:Efficient Smart Monte Carlo based SSTA on Graphics<br>Processing Units with Improved Resource Utilization   | 43   |

| III.1. Introduction                                                                                                     | 43   |

| III.2. CUDA Platform                                                                                                    | 46   |

| III.3. Smart Sampling based SSTA: SH-QMC                                                                                | 47   |

| III.4. Monte Carlo based Statistical Timing Analysis on GPUs                                                            | 48   |

| III.5. Enhanced resource utilization for implementation of SH-QMC on GP                                                 | U 48 |

| III.6. Critical Graph Analysis for MC SSTA                                                                              | 54   |

| III.6.1. Nominal STA based Critical Graph Identification                                                                | 54   |

| III.7. Results                                                                                                          | 55   |

| III.8. Conclusions                                                                                                      | 62   |

| CHAPTER IV:A Lower Bound Computation Method for Evaluation of Statistical Design Techniques                             | 64   |

| IV.1. Introduction                                                                                                      | 64   |

| IV.2. Exact Deterministic Optimization                                                                                  | 67   |

| IV.3. Lower Bound For Design With Statistical Timing Yield Constraint                                                   | 71   |

| IV.4. Sample Level Optimization in Parallel (SLOP)                                                                      | 75   |

| IV.5. Results                                                                                                           | 77   |

| IV.6. Conclusions                                                                                                       | 81   |

| CHAPTER V: Efficient Smart Sampling based Full-Chip Leakage Analysi<br>Intra-Die Variation Considering State Dependence |      |

| V.1. Introduction                                                                                                       | 82   |

| V.2. Smart Sampling for Leakage Analysis                                                                                | 84   |

| V.2.1. Quasi Monte Carlo                                                                                                | 85   |

| V.3. Leakage Analysis for Inter-Die Variation with Smart Sampling                                                       | 86   |

| V.3.1. Process Variation Model                                          | 86  |

|-------------------------------------------------------------------------|-----|

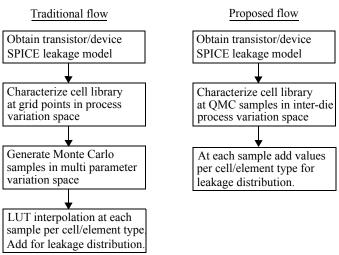

| V.3.2. Traditional Leakage Analysis Flow for Inter-Die Variation        | 87  |

| V.3.3. Proposed Leakage Analysis Flow with Smart Sampling               | 88  |

| V.4. Leakage Analysis for Total Variation with Smart Sampling           | 89  |

| V.5. Results                                                            | 95  |

| V.6. Conclusions                                                        | 100 |

| CHAPTER VI:Fast And Accurate Waveform Analysis With Current S<br>Models |     |

| VI.1. Introduction                                                      | 102 |

| VI.2. Precharacterization                                               | 104 |

| VI.2.1. Bicubic Spline based DC Current Source Model                    | 104 |

| VI.2.2. Modeling Parasitics                                             | 106 |

| VI.3. Weibull-based Runtime Engine                                      | 108 |

| VI.3.1. Basic Concept and Flow                                          | 108 |

| VI.3.2. Enhancing Accuracy                                              | 111 |

| VI.4. Results                                                           | 113 |

| VI.5. Conclusions                                                       | 115 |

| CHAPTER VII:Conclusions and Future Work                                 | 118 |

| VII.1. Smart Monte Carlo SSTA : SH-QMC                                  | 118 |

| VII.2. Acceleration of SH-QMC on Graphics Processing Units (GPUs)       | 119 |

| VII.3. Comparison of Statistical Design Optimization Techniques         | 119 |

| VII.4. Smart Sampling based approach for full-chip leakage analysis     | 120 |

| VII.5. Future Work                                                      | 121 |

| Bibliography                                                            | 124 |

# LIST OF TABLES

| Table II.1  | Comparison of random sampling, LHS based and SH-QMC approaches based on sample size. The last two columns show the speedup of LHS and SH-QMC respectively, over random sampling                                                                           |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table II.2  | Runtime comparison of SHQMC with SSTA. AT = circuit delay36                                                                                                                                                                                               |

| Table II.3  | Comparison of three SH-QMC-based approaches with no pruning, single stage pruning and double stage pruning on benchmark circuits                                                                                                                          |

| Table II.4  | Performance of incremental evaluation of 95th and 99th percentile delay with gate size change for SH-QMC with 80 samples. AT=Arrival Time 42                                                                                                              |

| Table III.1 | Comparison of runtime for SH-QMC (192 samples) vs. random sampling based MC SSTA on GPU. SH-QMC is implemented with (a) sample level parallelism or SP (b) sample + gate parallelism or SGP. (c) SGP + efficient shared memory usage or SGP+S.Mem.        |

| Table III.2 | Comparison of runtime for SH-QMC (192 samples) on GPU vs. CPU. and single STA on CPU. The CPU is a 3.16GHz Intel Xeon processor 59                                                                                                                        |

| Table III.3 | Quality of results for the critical graph analysis technique                                                                                                                                                                                              |

| Table III.4 | Runtime improvement from graph reduction combined with the proposed                                                                                                                                                                                       |

|             | technique. 61                                                                                                                                                                                                                                             |

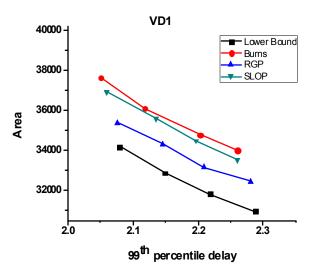

| Table IV.1  | Comparison of Burns, RGP and SLOP approaches against the lower bound for area at benchmark circuits. RGP is implemented on a CPU. Burns and SLOP are implemented on a CPU with a GPU co-processor, to utilize the parallelism available in the algorithms |

| Table V.1   | Comparison of proposed approach with Golden (Monte Carlo 20,000 samples) for benchmarks. * indicates that state probability is considered for instances in the circuit                                                                                    |

| Table V.2   | Comparison of proposed approach with Wilkinson's based approach. * indicates that state probability information is considered for instances in the circuit                                                                                                |

| Table VI.1  | Comparison of stagewise timing analysis for a bicubic spline fit (spline) vs. a fourth order polynomial fit (Poly) for standard cells in an industrial 90nm library                                                                                       |

| Table VI.2  | Error statistics compared to SPICE of delay and slew for proposed and traditional techniques for various benchmark circuits                                                                                                                               |

# **LIST OF FIGURES**

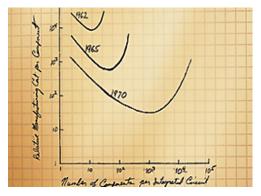

| Figure I.1  | Gordon Moore's original graph from 1965. Source: http://                                                                                                                                                                                                                                                                            |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | www.intel.com/technology/mooreslaw/                                                                                                                                                                                                                                                                                                 |

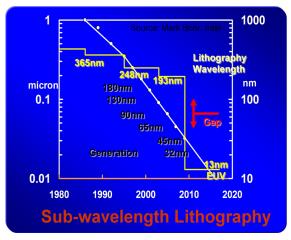

| Figure I.2  | Resolution enhancements in photolithography have stalled due to difficulties associated with EUV (Extreme Ultravioloet lithography). This is a source of variation as transistor geometries shrink at advanced technology nodes. Source: Mark Bohr, Intel                                                                           |

| Figure I.3  | Smart sampling techniques for SSTA can be parallelized on GPUs to achieve significant speed ups in statistical timing analysis                                                                                                                                                                                                      |

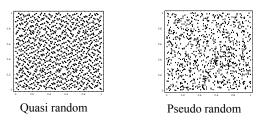

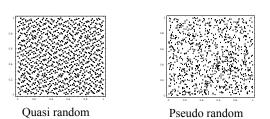

| Figure I.4  | Quasi random and pseudo random sequences                                                                                                                                                                                                                                                                                            |

| Figure I.5  | Stratification of a 2D space. Variable X is divided into 4 bins, thus dividing the sample space into 4 strata                                                                                                                                                                                                                       |

| Figure I.6  | Latin Hypercube Sampling (a) Divide each variable in 8 equal probability bins and sample in bins. (b) Combine randomly to form 8 triplets                                                                                                                                                                                           |

| Figure II.1 | Ordering variables using timing criticality                                                                                                                                                                                                                                                                                         |

| Figure II.2 | Stratified Latin Hypercube Sampling (a) Ordering variables based on timing criticality. (b) One of 16 strata in the sample space. (c) QMC                                                                                                                                                                                           |

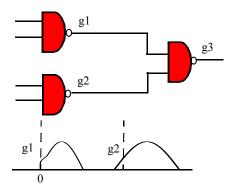

| Figure II.3 | triplets and LHS pairs. (d) These are combined to obtain final samples24 Slack distribution of gates 'g1' and 'g2' obtained by evaluation of minimal SH-QMC set. The threshold percentile for each distribution is plotted as a dotted line. 'g2' is pruned in this case as the criterion of positive slack percentile is satisfied |

| Figure II.4 | (a) Samples are visited in decreasing order of circuit arrival time, starting from the xth percentile (tx). Samples with delta crossing tx are selected, others pruned. (b) Recomputation of circuit arrival time is performed at the selected sample and tx is updated                                                             |

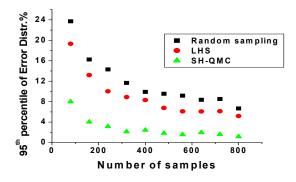

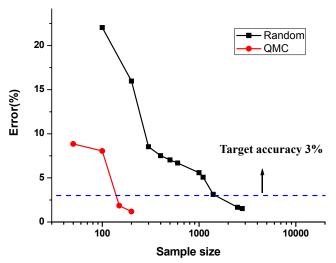

| Figure II.5 | Error comparison of random sampling, LHS and SH-QMC for a VGA circuit (90831 gates) w.r.t. golden of MC count 40,00034                                                                                                                                                                                                              |

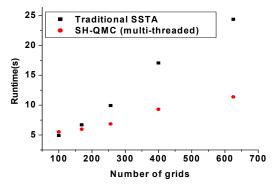

| Figure II.6 | Performance comparison of traditional SSTA with multi-threaded SH-QMC for VGA circuit (90831 gates) as function of number of grids in process variation model.                                                                                                                                                                      |

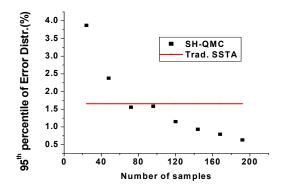

| Figure II.7 | Comparison of 99th percentile error of SH-QMC vs. traditional SSTA w.r.t golden of 40,000 MC count for USB circuit                                                                                                                                                                                                                  |

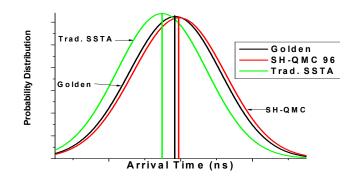

| Figure II.8 | Arrival time distribution of SH-QMC (96 samples) and traditional SSTA w.r.t golden(40,000 MC) for USB circuit                                                                                                                                                                                                                       |

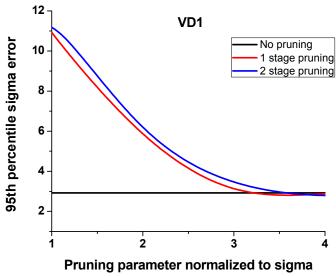

| Figure II.9  | Comparison of the 95th percentile error in s for single stage and two stage pruning for a large benchmark circuit                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

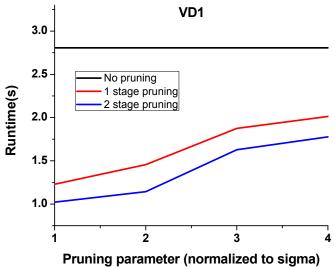

| Figure II.10 | Comparison of runtime vs. pruning parameter for single stage and two stage pruning for a large benchmark circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                |

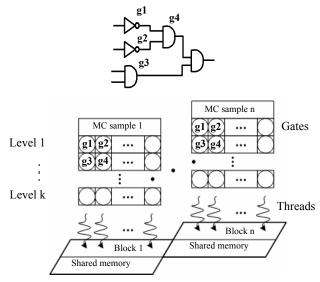

| Figure III.1 | Gate scheduling. Gates in a sample with no dependence are computed in parallel. In graph shown, gates g1,g2,g3 have no dependence and can be assigned to the same level. However, g3 is a 2-input gate which if assigned to the same level as g1 and g2, increases the computational steps in the level. Therefore, g3 is assigned to the next level along with gate g4 50                                                                                                                                                                                      |

| Figure III.2 | Algorithm 1 and Algorithm 2 for gate scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

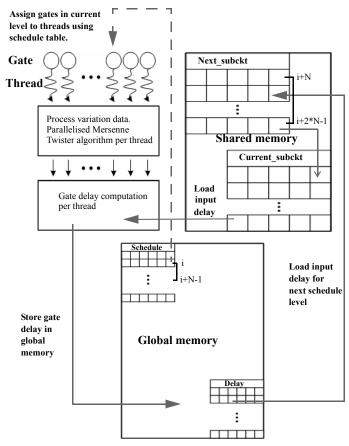

| Figure III.3 | Summary of proposed approaches to improve resource utilization.  Concurrent computation on gates in the same level and use of shared memory are illustrated                                                                                                                                                                                                                                                                                                                                                                                                     |

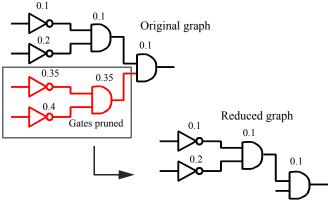

| Figure III.4 | Illustration of graph reduction. Slacks for nodes are indicated next to corresponding gates. Gates with slacks higher than a threshold of 0.3 at output node are removed to obtain the reduced graph in the example 55                                                                                                                                                                                                                                                                                                                                          |

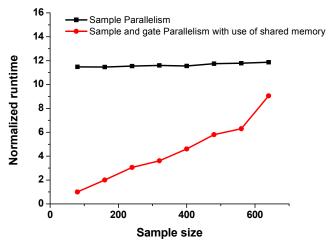

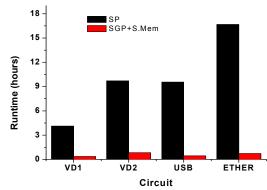

| Figure III.5 | Improvement in runtime due to the techniques proposed for improved resource utilization                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Figure III.6 | Comparison of runtime for SH-QMC performed with successive gate sizing (100,000 sizing steps) on 4 GPU cards for Ether circuit. Runtime for an implementation utilizing sample level parallelism (SP) is compared with the proposed approach (SGP+S.Mem).                                                                                                                                                                                                                                                                                                       |

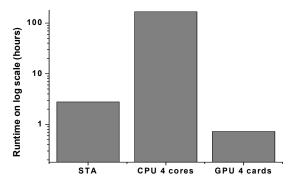

| Figure III.7 | SH-QMC with 192 samples on GPU is compared with SH-QMC on CPU and STA on CPU, on a logarithmic scale, for Ethernet circuit with 57327 gates. SH-QMC on multi-GPU is faster than STA on CPU                                                                                                                                                                                                                                                                                                                                                                      |

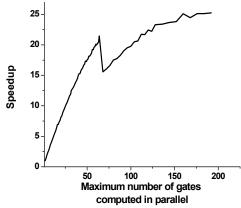

| Figure III.8 | Speedup of SH-QMC algorithm implemented on multi-GPU for a USB circuit (14,503 gates) with smart scheduling algorithm Algorithm 2. X axis indicates the maximum number of gates computed in parallel. A discontinuity in resource requirements above a parallelism of 64 leads to the discontinuity in the graph                                                                                                                                                                                                                                                |

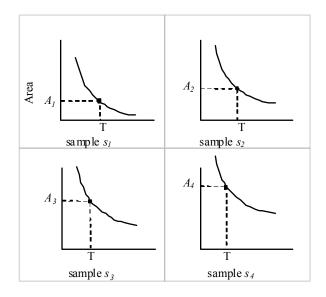

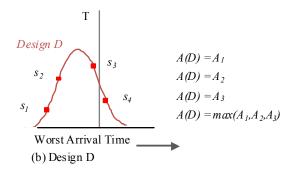

| Figure IV.1  | Illustration of Theorem 1. Ai represents the optimal cost solution at sample si. Design D meets timing constraint T for the 75th percentile of the given sample set. The cost of this design is A(D) and exceeds Ai, i=1,,3 as D meets the timing constraint at samples si, i=1,,3. Therefore, A(D) exceeds the 75th percentile of the distribution Ai, i=1,,4 for the given sample set                                                                                                                                                                         |

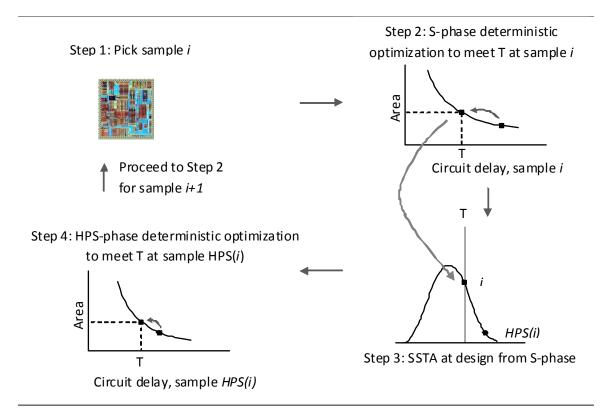

| Figure IV.2  | SLOP overview: Each virtual die i is optimized in parallel. The optimization consists of an S-Phase and an HPS-Phase. In the S-Phase, the virtual die is optimized to meet the timing constraint T using a greedy approach. In the subsequent HPS-Phase, the xth percentile sample of the design i optimized in S Phase, called HPS(i), is selected. If T is already met at HPS(i), optimization terminates. Else, the design is optimized further, this time with sample HPS(i) constrained to meet a timing T. The best among parallel solutions is selected. |

| Figure IV.3 | Comparison of sizing curves for Burns, RGP and SLOP against the lower bound for area computed at varying timing constraints for the 99% timing yield                                                                                                                                                                                                              |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

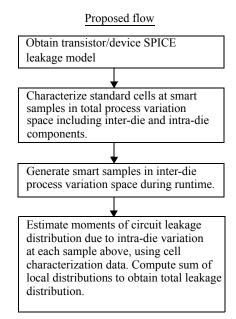

| Figure V.1  | Traditional and proposed leakage analysis flow for global variation with multiple sources.                                                                                                                                                                                                                                                                        |

| Figure V.2  | Quasi random and pseudo random sequences                                                                                                                                                                                                                                                                                                                          |

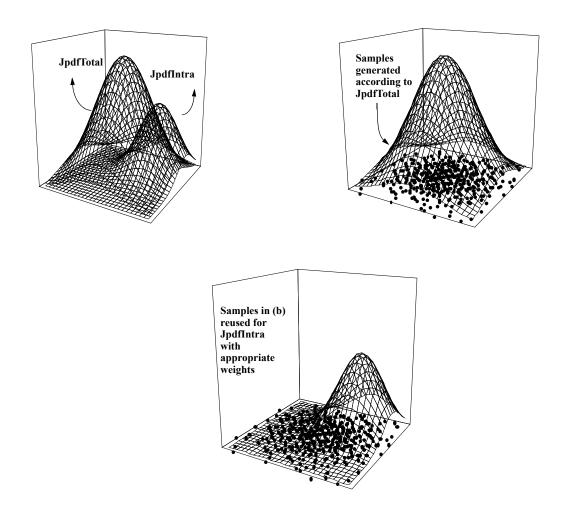

| Figure V.3  | Proposed leakage analysis flow for within-die variation                                                                                                                                                                                                                                                                                                           |

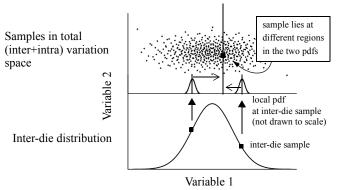

| Figure V.4  | Reusing samples for local distribution computation. Inter-die samples weigh the samples in total variation space according to local probability distribution                                                                                                                                                                                                      |

| Figure V.5  | <ul><li>(a) Total (Inter+Intra die) distribution and local pdf at an inter-die sample.</li><li>(b) QMC based samples are generated according to total variation.</li><li>(c) For computing mean of local pdf the samples generated in</li><li>(b) are weighed according to the ratio of the probabilities in the two distribution functions.</li><li>94</li></ul> |

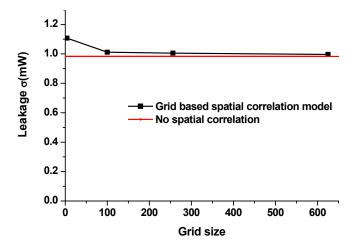

| Figure V.6  | Comparison of sigma of leakage distribution without considering spatial correlation with that of a grid-based spatial correlation model for VGA circuit (43214 gates)                                                                                                                                                                                             |

| Figure V.7  | Comparison of error in estimating s of leakage distribution for inter-die variation using QMC vs. random sampling for VGA circuit(43214 gates) 96                                                                                                                                                                                                                 |

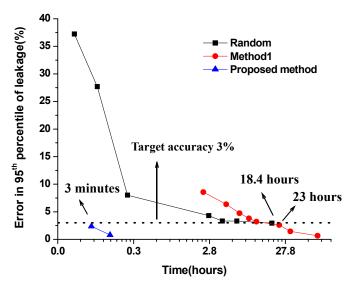

| Figure V.8  | Comparison of accuracy of proposed approach with random sampling based approach vs. runtime. The circuit considered is Chip1 with 200,000 gates                                                                                                                                                                                                                   |

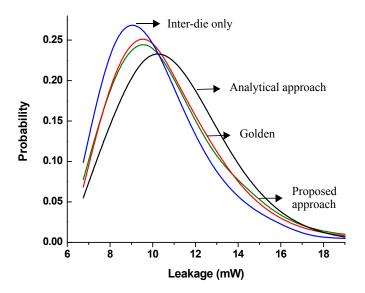

| Figure V.9  | Total leakage distribution considering intra-die variation for Chip1 (200,000 gates). Proposed approach is compared with the analytical approach based on [7] and the golden. The distribution due to inter-die variation is also plotted. The analysis considers state dependence of leakage for the instances in the circuit                                    |

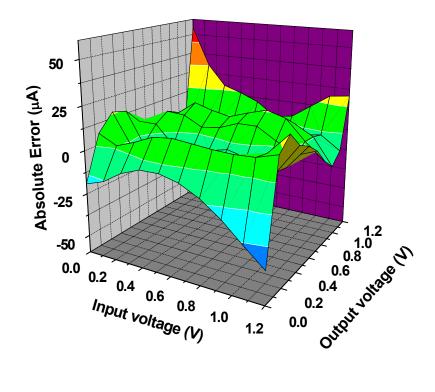

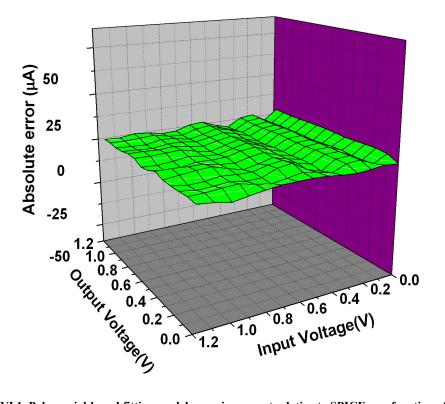

| Figure VI.1 | Polynomial-based fitting model error in current relative to SPICE as a function of input and output voltages. (b) Spline-based fitting model error in current relative to SPICE                                                                                                                                                                                   |

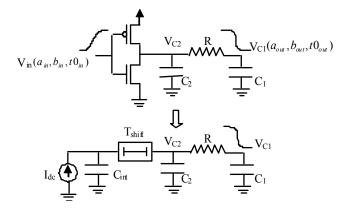

| Figure VI.2 | Schematic of the proposed modified Blade-based model                                                                                                                                                                                                                                                                                                              |

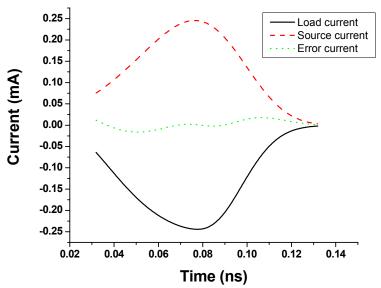

| Figure VI.3 | Typical waveforms for source and load currents as in the proposed model for an output falling case. The difference is the error function (referred to as f (t))                                                                                                                                                                                                   |

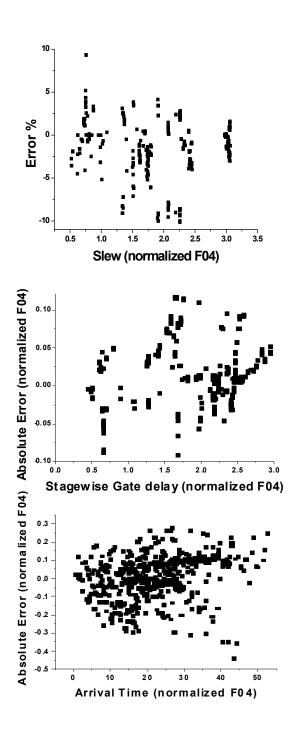

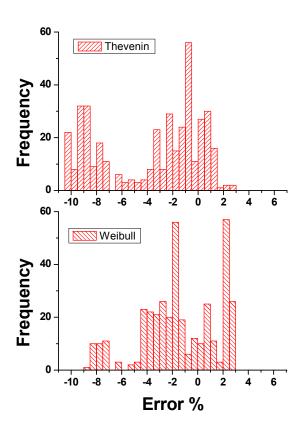

| Figure VI.4 | (a)% error in slew (b) Absolute error in gate delay (c) Absolute error in arrival time                                                                                                                                                                                                                                                                            |

| Figure VI.5 | Error histograms for slew estimations in two large ISCAS85 circuits given a primary input excitation                                                                                                                                                                                                                                                              |

### CHAPTER I

#### Introduction

The number of transistors that can be packed together in semiconductor chips have increased exponentially over the past 50 years. This behavior was first predicted famously by Gordon Moore in 1965 as illustrated in Figure I.1. Moore's law predicts that the number of transistors in semiconductor chips doubles every two years. The trend in the semiconductor industry has been more or less consistent with this prediction. Modern chips contain up to a billion transistors. The dense packing of transistors in a chip is enabled by advances in process technology with the transistor device geometry shrinking at every new technology node. The spatial resolution of transistors can be as low as 32nm in the latest technologies. Thus today's technology enables man to produce powerful computing devices at massive scales by being to able to control the behavior of matter at the level of just a few atoms.

Figure I.1. Gordon Moore's original graph from 1965. Source: http://www.intel.com/technology/mooreslaw/

Figure I.2. Resolution enhancements in photolithography have stalled due to difficulties associated with EUV (Extreme Ultravioloet lithography). This is a source of variation as transistor geometries shrink at advanced technology nodes.

Source: Mark Bohr, Intel

At the same time, these advances in technology are accompanied by novel challenges which are threatening to limit the pace at which we make progress in accordance with the Moore's law. Earlier transistors were much larger and their physical dimensions (e.g. length) and other properties were easier to control. However with shrinking sizes it has become increasingly difficult to control these properties/parameters. Termed process variation, this phenomenon implies that the behavior of a chip has an uncertainty related to the exact manufacturing process and is only known to within bounds during the design phase of the chip. This means that meeting the performance specification becomes more challenging. The complexity of process variations and the uncertainty is increasing with technology scaling. There are different sources for this process variation. Lithography is the process of using light to transfer a geometric pattern to the silicon substrate or thin films on the substrate. The resolution related to the wavelength of light leads to lithographic variation as illustrated in Figure I.2. Other sources of variation are related to the process of doping or intentional addition of impurities to silicon to achieve desired properties. The

final geometric pattern achieved on silicon or the layout affects the distribution of stress in silicon which leads to layout dependent stress variation in certain silicon technologies called strained silicon technologies. It is important to study and model the effect of these sources of variation to enable better knowledge of chip properties in the design phase [1-3]. Timing verification/analysis and power analysis are two key steps in assessing the quality of an integrated circuit design. In the optimization step, insights from timing analysis are used to tune the design to achieve, for example minimum area in silicon while meeting target timing constraints. These are briefly described in the following sections along with the impact of process variations on the accuracy of these analyses.

## I.1 Timing Analysis and Optimization

The aim of timing verification of a chip is to make sure that a chip operates at a specified clock frequency with a desired yield under the specified range of operating conditions. A simple definition of yield is the fraction of chips manufactured which meet the performance specifications. Timing verification involves timing analysis of the network of logic gates in the circuit or the netlist (a description of a circuit in terms of electrical connections of gates). Timing analysis can be static or dynamic. Dynamic timing analysis involves propagation of vectors at the input ports of the network to the output ports and computing the timing behavior of the circuit. Static timing analysis does not consider individual input vector patterns and is therefore more conservative in the timing behavior estimate. However, due to the complexity of usage the standard methods used for processors and ASICs (Application Specific Integrated Circuits) do not involve dynamic timing analysis. Hence we only consider static timing analysis in this work.

The basic steps involved in a static timing analysis on a netlist are summarized here [4-5]

- Output pin timing constraints are determined

- Input pin arrival time is determined.

- Clocks in the netlist are identified.

- Timing constraints are generated at all circuit pins

- Minimum/maximum rising and falling signal timing are propagated from inputs to outputs. Signals may also be propagated from outputs to inputs for certain analyses.

- The delay of each circuit element (transistors, gates) are estimated in the above step.

- Considering clock uncertainty, check if all paths meet the timing constraints.

- If there are violations, these have to be fixed through changes in the netlist. Static timing analysis is performed on the modified netlist.

#### I.1.1 Variability Aware Timing Analysis

With increasing process parameter variations there was a need to incorporate uncertainty into timing analysis. A traditional conservative approach is to perform static timing analysis at multiple process conditions or "corners" for a given circuit. A process corner is a set of values assigned to all circuit parameters with the hope that some combination of the values assigned will elicit worst case performance for the circuit. Process corners are generated by assuming upper and lower bounds for each process parameter independently. The process corners of specific interest include the best, nominal and worst case corner.

For example, the worst case corner is the process corner where the maximum operating frequency of the circuit is the lowest. To find the best and worst corners, all the process corners need to be evaluated. However as the number of process variation sources increases, the number of candidate corners increases exponentially which makes this approach expensive. An alternate approach is to assume worst case behavior for each device which leads to large guard bands and loss of performance. Therefore, rather than using simple corner models, modern CAD tools are moving towards a more probabilistic view of circuit timing behavior. In replacing corner models, there are two primary approaches that incorporate process parameter uncertainty in timing analysis. The first is to perform statistical static timing analysis (SSTA) by modeling gate delay as a function of process parameters and propagating these distribution functions to compute the distribution of circuit delay [6-15]. We refer to these approaches as traditional SSTA. In traditional SSTA it has proven challenging to efficiently model factors such as "skewness" in the arrival time distribution. Skewness is a measure of deviation from an assumed standard fitting function, and can be attributed to factors including non-linear dependence of the gate delays on process variation. Also, a number of modeling issues are still in early stages of development, such as combined analysis of large interconnect structures driven by non-linear drivers, coupling events, and modeling of transparent latches. While some progress has been made in addressing these issues [6-15], it is expected that a fully mature traditional SSTA tool capable of performing timing sign-off may not be widely available in the near future. The second approach is Monte Carlo based SSTA, which involves selection of samples of the process variation space to obtain statistical distributions of circuit timing behavior. The application of Monte Carlo (MC) for statistical timing was dis-

Figure I.3. Smart sampling techniques for SSTA can be parallelized on GPUs to achieve significant speed ups in statistical timing analysis

cussed in [16], where it was shown that Monte Carlo based SSTA is accurate even in scenarios with high dimensionality and non-standard distributions in the process variation space, where traditional SSTA has difficulties. However, there are two main difficulties with this approach. First, the standard MC approach of random selection of samples in the process variation space requires too many samples for sufficient accuracy, resulting in high runtime cost. Second, there is no work to show the applicability of MC based SSTA for incremental statistical timing analysis. We address both concerns in Chapter II.

As important as reducing the sample size for Monte Carlo based SSTA is to exploit the trivial parallelism in the algorithm by performing computations on parallel machines. Fortunately, recent years have seen the rapid scaling of throughput-optimized processors, such as Graphics Processing Units (GPUs). Modern GPUs deliver over 1 TeraFlops of computational power with more than 100 GB/second of memory bandwidth while conventional processors face difficulties with frequency scaling and are increasingly incorporating multiple cores on a chip to keep up with Moore's law. However, to exploit the benefits of throughput-optimized processors such as GPUs, applications need to be rede-

signed to achieve performance and efficiency. We present techniques to speed up statistical timing analysis on throughput processors in Chapter III. Our proposed smart sampling technique, Stratification + Hybrid Quasi Monte Carlo (SH-QMC), is implemented on a GPU based on NVIDIA CUDA architecture. We show that although this application is based on MC analysis with straightforward parallelism available, achieving performance and efficiency on the GPU requires exposing more parallelism and finding locality in computations. This is in contrast with random sampling based algorithms which are inefficient in terms of sample size but can keep resources utilized on a GPU. Results presented provide a compelling case for the adoption of GPUs for SSTA.

#### I.1.2 Variability Aware Optimization

Next, we focus on optimizing a given circuit design to minimize cost metrics such as area on silicon or power consumed by the chip while meeting a specified timing constraint. Optimization takes advantage of the fact that the same logic function can be performed by different implementations of logic gates which trade-off performance for area of power consumed. For example, standard cell libraries are available from vendors, where there is a choice of different gate sizes for a given logic gate. A higher gate size usually means that the gate incurs lower delay to propagate the logic, however with an area penalty or increase in power consumption. Timing optimization can be performed by choosing the appropriate gate type to perform each logic function such that timing constraints are met. However, variability in timing makes this more challenging as the timing constraints in the optimization problem are now probabilistic functions rather than deterministic. As discussed in the case of timing analysis, it is possible to select among differ-

ent process corners (generated by assuming upper and lower bounds for each process parameter independently) and optimize only at the worst case corner. However, increase in variability in the nanometer era has contributed to pessimistic guardbands for circuit design techniques that optimize at worst-case process corners. Smart deterministic approaches have been proposed that employ statistical timing analysis to reduce pessimism in the guardbands while retaining the deterministic nature of the algorithms. In other words, the optimization itself has deterministic objective function and constraints. However, the result obtained from the optimization is analyzed using an SSTA tool to check if the statistical objective is also met. If not, deterministic optimization continues till the statistical objective is attained. Other statistical optimization techniques focus on optimization algorithms which directly work with statistical objective and constraints, where clearly the computational cost is higher. It is not clear how much improvement can be gained using the latter set of approaches over smart deterministic approaches. This work presents a new lower bound to evaluate these statistical optimization techniques, drawing inspiration from recent advances in sampling based SSTA. We also compare several statistical design optimization approaches, including one proposed in this work called SLOP, against the computed lower bound. We show that the existing optimization methods have nearly exhausted the obtainable improvement from being statistically aware and mostly provide trade-offs in runtime speed.

#### I.1.3 Gate Delay Modeling

An important step in timing verification is to calculate the delay of each circuit element. Though we do not provide a detailed treatment of variability effects on gate delay

modeling in this work, we propose a technique to achieve increased accuracy in gate delay modeling compared to conventional techniques. This technique is not currently integrated with the rest of the methods developed in this work for timing analysis and optimization. However, with additional research to incorporate variation effects, this can potentially increase the efficiency of these other techniques further. Hence, we present a discussion of this approach in Chapter VI.

Gate delay depends on several variables, including input signal transition time and the characteristics of the load driven by the gate. Gates drive other gates and their input pin capacitance adds to the capacitive load at the driver gate. Gates may also drive long global wires on the chip with large capacitive and resistive components. Modeling of gate delays has become an important challenge in recent technologies. Traditional standard cell libraries (libraries with pre-designed logic gates to achieve different functionalities and drive strengths) have modeled logic gates as voltage sources based on a Thevenin model. Timing libraries provide data for each logic gate where the delay characteristics are precharacterized as a function of input signal transition time and a simple lumped output capacitive load model (without considering distributed capacitive or resistive effects). The output load of a gate is approximated to a single capacitance to make use of the information in the timing library. This information is used to model the gate itself as a voltage source with a resistance in series, using an iterative approach. The respective parameters for the voltage source and resistor are dependent on the lumped capacitance model. These models are inadequate to capture the timing behavior in modern nanometer scale CMOS. The lumping of load capacitances into an effective capacitance leads to

errors in timing analysis. Also, signal integrity issues require a level of accuracy in waveform shapes which cannot be achieved with these models.

Recently current source models (CSMs) have become popular for use in standard cell characterization and static timing analysis. However, there has not been any detailed study of what aspects of the gate parasitics and DC current source behavior should be modeled for sufficient accuracy, and there have been no results reported incorporating a CSM with the above complexity into a timing analysis flow with reasonable runtime. This work addresses these two limitations by investigating complexity/accuracy trade-offs in CSMs in Chapter VI. We then present a novel technique to perform fast, accurate waveform analysis using current source models. Timing analysis results on benchmark circuits show significantly reduced errors compared to a traditional Thevenin-based flow.

# I.2 Standby Power: Leakage Analysis

Ideally the power consumption of chips with scaling should not be a significant problem. However, in reality the trends in increase in power consumption by digital circuits is

alarming. This can be attributed to the fact that the while device geometry has been scaling

consistently, the corresponding reduction in supply voltage has not been consistent. High

power consumption increases the need for cooling of the chip and beyond a limit this can

be very expensive. The power consumption of a chip can be broadly classified as dynamic

power consumption and static or standby power consumption. Dynamic power consumption is due to charging and discharging of the nodes in the circuit. Static power consumption occurs when there is no switching activity in the circuit. The main component of static

power is leakage power. Power analysis of a design involves estimating the dynamic and

static power consumption of a circuit. The static power consumption of a circuit increases exponentially with leakage current and this is a major concern with process scaling. In this research, we focus on the static component of power consumption.

As in the case of timing analysis, increasing process variation with scaling adds complexity to static power or leakage analysis. A promising solution is to perform statistical analysis of leakage and use this to guide leakage optimization and design changes. Analogous to the case of timing analysis, current approaches to calculate full-chip leakage power can be classified into two main categories. The first category of methods are analytical in nature. These attempt to model full chip leakage using a standard distribution, most commonly a lognormal distribution. The moments of this distribution are computed by matching moments with an expression involving summation of leakage distributions at the gate level [24-27]. In [24] a lognormal distribution is used to approximate the leakage current of each gate and the total leakage is obtained by summing the log normals. A low rank quadratic approximation to capture non-lognormal leakage distributions is proposed in [25]. It is noted that a 20% error is observed when modeling leakage distributions as purely lognormal using a linear approximation. The authors in [26] attempt to capture high level characteristics of a candidate chip design for early mode leakage estimation. In [27] the authors propose a systematic characterization of leakage related parameter variations. A quadratic model of the logarithm of leakage current is also proposed. Traditionally these approaches have provided the desired accuracy. However they make assumptions about either the nature of the statistical distribution of process variation parameters or the nature of the dependence of standard cell leakage on the underlying variables for handling process variation. The process variation parameters are assumed to have a standard distribution, most commonly Gaussian, or the logarithm of standard cell leakage is assumed to be a linear or quadratic sum of the variables modeling process variation. It is not clear that these assumptions will still hold true considering secondary effects in process variation and a growing number of variation sources at technology nodes below 45nm.

The second category of methods fall into the classification of Monte Carlo based techniques involving selection of samples in the process variation space and using these samples to compute leakage distribution. Monte Carlo techniques can handle non-standard distribution of process parameters and lookup tables for dependence of standard cell leakage on process variables. Therefore they do not require simplifying assumptions about the dependence of leakage on process parameters or the nature of process parameter distribution, making them highly scalable. Also the inherent parallelism in evaluating Monte Carlo samples make these techniques amenable to multi-core and Graphics Processing Unit (GPU) computing. However Monte Carlo techniques typically require a large sample size rendering them expensive. There is a need for smart selection of samples to reduce the number of samples that require evaluation without compromising accuracy. In [28] the author describes such techniques, known as variance reduction techniques. These techniques need to be tailored to the system under consideration for efficient reduction in sample size. In the context of integrated circuits it has been shown that a suitable choice of these techniques can lead to significant sample size reduction for statistical timing analysis[29].

Figure I.4. Quasi random and pseudo random sequences.

#### **I.3** Overview of Monte Carlo Variance Reduction

Since the major contributions in this work are based upon a Monte Carlo sampling perspective of the process parameter variation space, an overview of Monte Carlo sampling and variance reduction approaches is in place here. The standard Monte Carlo method addresses the problem of approximating the integral of a function f(x) over the s-dimensional hypercube  $c^s = [0,1)^s$ , where x represents a point in an s-dimensional space. The MC estimate of the integral  $\bar{f}$  is given by the arithmetic mean of  $f_i$ , which are values of the function f(x) evaluated at n samples distributed throughout the hypercube.

MC based statistical timing involves selecting samples of the process variation space to obtain statistical distributions of circuit delay. This is mapped to the standard mathematical problem of MC, which is to estimate the integral of a function, using samples in its domain. There are standard techniques for variance reduction of MC, which include Quasi Monte Carlo techniques, Latin Hypercube sampling, stratified sampling, importance sampling and control variates. In this section, we briefly discuss their applicability to digital circuit analysis.

#### I.3.1 Quasi Monte Carlo

The Koksma-Hlawka inequality relates the error bound of a method to numerically estimate an integral using a sequence of samples, to a mathematical measure of uniformity for the distribution of the points, called "discrepancy" [34]. This inequality suggests that we should use a sequence with the smallest possible discrepancy to evaluate the function in order to achieve the smallest possible error bound. Such sequences constructed to reduce discrepancy are called Low Discrepancy Sequences (LDSs). Quasi monte carlo techniques are characterized by their use of LDSs to generate samples. LDSs are deterministic sequences, in other words there is no randomness in their generation. Intuitively, these sequences are well dispersed through the domain of the function, minimizing any gaps and/or clustering of points. Figure I.4 illustrates that quasi random sequences generate samples with lower discrepancy compared to pseudo random sequences (sequences with properties similar to "truly" random sequences). Sobol[35], Faure and Niederreiter[33] are LDSs that have been studied extensively. In this work, we consider Sobol sequences, which are known to be simple to construct and more resistant to the pattern dependency issue (mentioned below), compared to the other sequences. Interested readers can refer to [35] for a construction of the Sobol sequence, and [36] for an implementation.

In the context of statistical timing analysis, Quasi Monte Carlo techniques have been studied in [33]. The author notes that LDSs are imperfect and as the number of dimensions in the problem increases, there is degraded uniformity. This effect is especially significant among the higher coordinates of LDSs, which show undesirable patterns as opposed to the low discrepancy pattern in Figure I.4. This phenomenon is referred to as *pattern dependency*. The author suggests that in timing analysis the lower coordinates of Sobol

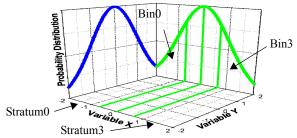

Figure I.5. Stratification of a 2D space. Variable X is divided into 4 bins, thus dividing the sample space into 4 strata.

sequences, which have no significant pattern dependencies, be assigned to the important variables in the sampling procedure. Therefore, a concept of criticality of variables in timing analysis needs to be defined, which can be used to sort the variables in the order of their decreasing importance. The coordinates of the Sobol sequence can then be assigned to variables in this order. We present a technique for ordering the variables based on their criticality to circuit delay in the statistical timing framework.

A related point is that Sobol sequences are not accurate beyond a certain number of dimensions. Hence, in this work, we use Quasi Monte Carlo techniques in conjunction with stratified sampling and Latin Hypercube Sampling (LHS). The next two subsections provide a brief overview of stratified sampling and LHS.

## I.3.2 Stratified sampling

Stratified sampling is a technique to partition the sample space into mutually exclusive strata, and then sample using any of the known variance reduction techniques within each [28]. The stratification method in this work is illustrated for a 2D example in Figure I.5, where random variable X is divided into 4 equal probability bins (X is equally likely to fall in any of the 4 bins), whereas random variable Y is not binned. This method is adopted when X is critical to the function value to be estimated, whereas Y is not. In this way, the

2D space is partitioned into 4 strata as shown in the figure. Throughout the work, we use 'bin' to refer to regions in individual variables, and 'strata' to refer to partitions in the *n*D space, where *n* is the dimensionality. In general in multidimensional space, 1 or more variables are binned, and the permutations of bins across variables define strata. In the case of timing analysis, the timing behavior of the circuit is more sensitive to the critical variables by selection and these variables are binned. Therefore within strata the timing behavior exhibits lower variation and is easier to estimate. The technique leads to accuracy with few samples, however cannot be used over very large dimensions since the number of strata increases exponentially.

#### **I.3.3** Latin Hypercube Sampling

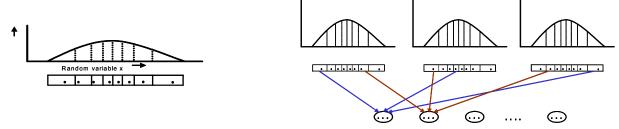

Latin Hypercube sampling is a technique in variance reduction which deals with multidimensional systems [37]. This technique tries to sample each variable involved uniformly by dividing the variable into equal probability bins. The samples from bins in variables are combined across dimensions to obtain faster convergence than random sampling. This is in contrast with taking all permutations of the bins across variables to define strata, and then sampling within each stratum as in stratified sampling described

Figure I.6. Latin Hypercube Sampling (a) Divide each variable in 8 equal probability bins and sample in bins. (b) Combine randomly to form 8 triplets

above. This means that LHS can deal with large dimensions, however with a moderate rate of convergence compared to full stratification.

The LHS procedure is illustrated in Figure I.6. Each random variable is divided into equal probability bins. One sample is generated within each bin. Such samples are combined across variables to obtain Latin Hypercube samples. This is the procedure to obtain k samples, where k is the number of bins per variable. To obtain k number of samples, we repeat the LHS procedure k times.

Two other techniques that have been studied for application to integrated circuit yield estimation are importance sampling and control variates. In general, these methods require more detailed information about the circuit. For literature in statistics about the method, refer to [28]. More work is required to establish the effectiveness of these approaches for use in the modern integrated circuit design process.

## I.4 Thesis Overview and Key Contributions

• We describe methods to improve the efficiency of Monte Carlo-based statistical static timing analysis. We propose a Stratification + Hybrid Quasi Monte Carlo (SH-QMC) approach to reduce the number of samples required for Monte Carlo based SSTA. Our simulations on benchmark circuits up to 90K gates show that the proposed method requires 23.8X fewer samples on average to achieve comparable accuracy in timing estimation as a random sampling approach. Results on benchmark circuits also show that when SH-QMC is performed with multiple parallel threads on a quad core processor, the approach is faster than traditional SSTA with comparable accuracy. SH-QMC scales better than traditional SSTA with circuit size. When the proposed SH-

QMC technique is extended to include a graph pruning method the runtime is further reduced by 48% on average for the benchmark circuits considered. We also propose an incremental approach to recompute a percentile delay metric after ECO. The results show that on average only 1.4% and 0.7% of original samples need to be evaluated for exact recomputation of the 95<sup>th</sup> percentile and 99<sup>th</sup> percentile delays, after sample size reduction using SH-QMC.

- We illustrate possibilities to exploit the parallelism in the SH-QMC algorithm with the implementation of the algorithm on a Graphics Processing Unit (GPU). We show that although straightforward parallelism is available, achieving performance and efficiency on the GPU requires exposing more parallelism and finding locality in computations. This is in contrast with random sampling based algorithms which are inefficient in terms of sample size but can keep resources utilized on a GPU. We show that SH-QMC implemented on a Multi GPU is twice as fast as a single STA on a CPU for benchmark circuits considered. In terms of an efficiency metric, which measures the ability to convert a reduction in sample size to a corresponding reduction in runtime w.r.t a random sampling approach, we achieve 73.9% efficiency with the proposed approaches compared to 4.3% for an implementation involving performing computations on smart samples in parallel. Another contribution of the work is a critical graph analysis technique to improve the efficiency of Monte Carlo based SSTA, leading to 2-9X further speedup.

- We propose a technique to compute a lower bound for the minimum possible area that can be achieved for a design while meeting a particular timing yield, which is the percentage of die that meeting a specified timing constraint. We then compare several

statistical design optimization approaches, including one proposed in this paper called SLOP, against the computed lower bound. We show that even the simplest statistical optimization approaches produce area results which are, on average, within 9.6% of the lower bound while the best ones performed only marginally better, reaching within 3.7% of the bound. This demonstrates that the proposed bound is a close bound.

Leakage power minimization is critical to semiconductor design in nanoscale CMOS. On the other hand increasing variability with scaling adds complexity to the leakage analysis problem. In this work we seek to achieve tractability in Monte Carlobased statistical leakage analysis. A novel approach for fast and accurate statistical leakage analysis considering inter-die and intra-die components is proposed. We show that the optimal way to select samples, to capture intra-die variation accurately, is according to the probability distribution function of total process variation. Intelligent selection of samples is performed using a Quasi Monte Carlo technique. Results are presented for benchmarks with sizes varying from approximately 5,000 to 200,000 gates. The largest benchmark with 198461 gates is evaluated in 3 minutes with the proposed approach compared to 23 hours for random sampling with comparable accuracy. Compared to a conventional analytical approach using Wilkinson's approximation, the proposed technique offers superior accuracy while maintaining efficiency. State dependence and multiple sources of variation are considered and the approach is scalable with number of process parameter variables for standard cell characterization cost. We also show reduction in sample size to meet target accuracy for computing leakage distribution due to the inter-die component only when compared to random selection of samples.

## **CHAPTER II**

# EFFICIENT MONTE CARLO BASED INCREMENTAL STATISTICAL TIMING ANALYSIS

#### **II.1 Introduction**

Process parameter variations have taken on increasing importance in nanometer-scale CMOS. Rather than using simple corner models that capture worst-case behavior at the device level (and lead to large guard bands), modern CAD tools are moving towards a more probabilistic view of circuit timing behavior. Two different approaches exist to capture the timing behavior - (1) analytical approaches which propagate standard distribution functions through the circuit, and (2) Monte Carlo (MC) based approaches which analyze samples of the circuit in the process variation space. Previous work in these areas were overviewed in Chapter I.

Standard techniques to reduce the sample size for MC based approaches exist in statistics literature and are called variance reduction techniques. The application of these techniques for parametric yield estimation has been analyzed in literature [30-33]. In [30], a Latin Hypercube approach for parametric yield estimation is proposed. In [31], mixture importance sampling for statistical SRAM design and analysis is proposed. The approach in [32] uses the control variates technique in conjunction with importance sampling for

timing yield estimation. However, while several approaches are reviewed, no results are presented. In [33], the authors propose to use Quasi Monte Carlo Analysis for yield estimation. However, it is not clear how this approach can be extended to systems with large number of dimensions (variables) which is often the case with process variation. Also, these approaches do not focus on the specific problem of using MC as an alternative to traditional SSTA for timing analysis. Variance reduction relies heavily on information about the system [28], hence it is important to adapt it specifically to timing analysis. To the best of our knowledge this work is the first to directly study variance reduction aimed at improving the efficiency of MC-based SSTA with an accurate process variation model considering intra-die variation with spatial correlation [7] and uncorrelated random variation.

ECO(Engineering Change Order) and synthesis tools require incremental timing analysis techniques for fast recomputation of circuit delay with small changes in the design. To meet time to market, designers need tools capable of performing fast incremental timing analysis, and such tools need to incorporate process variations. While incremental techniques for traditional SSTA exist in literature [6], the lack of such techniques has been a major drawback for MC based approaches to SSTA. We address the specific problem of recomputing a percentile delay metric after incremental circuit sizing. To the best of our knowledge, this work is the first to address incremental timing analysis in MC based SSTA.

This work has three main contributions. First, we introduce a new approach for variance reduction in MC based SSTA, Stratified Sampling + Hybrid Quasi Monte Carlo (SH-QMC). In SH-QMC, we propose to use circuit timing criticality information for

sample size reduction. We use information about the criticality of variables to the circuit delay to order them. For the most critical variables, we then employ techniques that achieve high accuracy with few samples. For the less critical variables, we use techniques that are effective for problems of higher dimensionality. The proposed approach is implemented and tested on benchmark circuits with sizes up to 90,000 gates, and compared to a random sampling approach for selecting samples in the process variation space. In general SH-QMC shows large speedups relative to the random sampling approach: 23.8X on average and up to 44X on the benchmarks studied. Our results also show that the number of samples required does not increase with the number of gates in the circuit. Additionally, when SH-QMC is implemented with multiple threads on a quad core processor, it is faster than traditional SSTA for comparable accuracy. We also observe that the performance of SH-QMC scales better than traditional SSTA with circuit size.

Second, we propose an extension to SH-QMC to consider a graph pruning method. In this method we use the information obtained from the evaluation of a few SH-QMC samples to reduce the circuit graph size. This enables fast evaluation of the remaining samples leading to up to 84% additional reduction in runtime.

Third, we propose a technique to recompute a percentile delay metric after incremental circuit sizing, where individual gates are resized. In this technique, we use information local to the resized gate to prune out most of the samples, leaving only a few samples to be reevaluated. Our results for the incremental computation of the 95<sup>th</sup> percentile and 99<sup>th</sup> percentile delays of benchmark circuits show that on average only 1.4% and 0.7% of original samples need to be evaluated for exact recomputation, even after sample size reduction using SH-QMC.

Figure II.1. Ordering variables using timing criticality.

This chapter is organized as follows. Section II.2 presents our work on variance reduction for MC based SSTA and proposes a graph pruning method to improve the efficiency of SH-QMC. In Section II.4, we propose our approach to incremental statistical timing analysis. We present detailed results in Section II.5 and conclude with Section II.6.

## **II.2** Smart sampling based on timing criticality

In this section, we first describe our process variation model and then go on to discuss our smart sampling approach.

#### **II.2.1 Process variation model**

Our process variation model is based on [7] which takes into account intra-die spatially correlated variation [17-22] by partitioning the die into n \* n grids and assuming identical parameter variations within a grid. Therefore, each source of variation is represented by a set of random variables for all grids. For example, transistor gate length variation is represented by a set of random variables for all grids and the set is of multivariate normal distribution with a covariance matrix  $R_{Lg}$ . Principal component analysis [23] is performed on these correlated random variables to obtain a set of principal components. Similarly, principal components are obtained for other sources of variation.

Let  $p_i$ : i=1,...,m be the principal components of all global sources of variation. In addition to these global sources of variation, we have an independent random variable  $\Delta r$  to account for random variation at the gate level. The delay for a gate is expressed as a linear combination of principal components of  $p_i$ 's and  $\Delta r$ :

$$d = d_0 + k_1 \times p_1 + \dots + k_m \times p_m + k_{m+1} \times \Delta r$$

where  $d_0$  is the gate delay mean,  $k_i$ : i=1,...,m are the coefficients for the principal components.  $p_i$ 's and  $\Delta r$  are independent unit normal random variables after suitably scaling their coefficients.

#### II.2.2 Stratification+Hybrid Quasi Monte Carlo(SH-QMC)

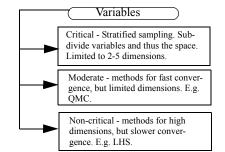

In our smart sampling approach SH-QMC, we propose to use circuit timing criticality information to reduce the sample size for MC based statistical timing analysis. In the previous subsection, we have defined the variables representing process parameter variation. In our proposed approach, we order these variables based on their criticality to the circuit delay using a timing criticality parameter  $P_{crit}$  defined in the next subsection. We then apply Quasi Monte Carlo (QMC), stratified sampling and LHS to variables based

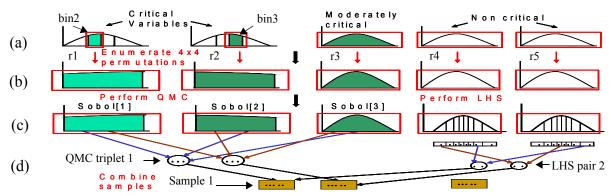

Figure II.2. Stratified Latin Hypercube Sampling (a) Ordering variables based on timing criticality. (b) One of 16 strata in the sample space. (c) QMC triplets and LHS pairs. (d) These are combined to obtain final samples.

on their convergence property and the ability to handle multiple variables (dimensions) as illustrated in Figure II.1. The topmost critical variables guide the stratified sampling approach, which leads to faster convergence. Only the top 2-5 variables are used to guide stratification since the number of strata increases exponentially with the number of variables. QMC method is then employed on the topmost to moderately critical variables for its fast convergence properties. However, QMC can exhibit pattern dependencies with large number of variables, so only a limited number of variables are sampled using QMC. On the non-critical variables, we use Latin Hypercube Sampling which is applicable for large number of variables, but has slower convergence to an accurate result.

The method is illustrated in Figure II.2 using a 5 variable example. As mentioned before, variables are ordered as critical, moderately critical and non-critical. The two most critical variables r1 and r2 are divided into 4 bins each (Figure II.2a). A stratum is defined as a set of points in the 5D space restricted to one bin each in r1 and r2, but unrestricted in r3, r4 and r5. The total number of strata is 16, arising from 4 by 4 permutations of the bins. Figure II.2b illustrates one particular stratum which we use to explain the remaining steps. In this stratum, points are restricted to bin 2 in r1 and bin 3 in r2. As shown in Figure II.2c, QMC method based on Sobol sequence is used to sample r1, r2 and r3 in the stratum and LHS is applied to r4 and r5. Note that since we are only sampling within the stratum, samples of r1 and r2 are restricted to the respective bins. QMC generates triplets as shown in the figure. For performing LHS, r4 and r5 are divided into 8 bins each and one value is selected from each bin as in Figure II.2c. 8 LHS pairs are generated by randomly picking from r4 and r5 in one step of LHS. Two LHS pairs are shown in Figure II.2d. Next, the LHS pairs are combined with the QMC triplets to generate our final

samples. The procedure is repeated: LHS pairs are generated again in r4 and r5, and QMC triplets are generated in the other 3 variables. These are then combined as before. After generating the samples in this stratum, we move to the next stratum and repeat our steps. In this manner, we generate samples in all 16 strata.

Among the variables on which QMC is employed, the lower coordinates of LDSs are assigned to the more critical variables. The order of criticality here is again decided using the parameter  $P_{crit}$ .

# II.2.3 Timing criticality P<sub>crit</sub>

To order the principal components, we employ a timing criticality metric  $P_{crit}$ . To compute  $P_{crit}$ , we perform static timing analysis on the nominal circuit to identify critical paths within a slack of s% of worst-case arrival time, where s is a parameter. This STA run is performed under nominal process conditions. Now, each grid is assigned a weight equal to the number of gates falling in any of the potential critical paths. Let  $w_g^i$  be the weight of the  $i^{th}$  grid. The weight of the  $j^{th}$  principal component is given by

$$r_{j} = \sum_{i} \left( w_{g}^{i} \times k_{ij} \right)$$

where  $k_{ij}$  is the coefficient of the  $j^{th}$  principal component in the  $i^{th}$  grid variation. This empirical technique leads to fast computation of  $P_{crit}$  with sufficient accuracy to guide our proposed SH-QMC.

#### II.3 Pruning based algorithm for timing analysis

In Section II.2.2 above we discussed our Stratification + Hybrid Quasi Monte Carlo (SH-QMC) approach to reduce the sample size using timing criticality information. In this section we propose a technique to further improve the performance of SH-QMC through graph reduction. As explained before, timing criticality information for SH-QMC is obtained by performing STA on the nominal circuit. Clearly as we evaluate the samples for SH-QMC we extract more information about the statistical behavior of the circuit with each additional sample evaluated. The algorithm presented here has two stages. In the first stage of the algorithm, the basic idea is to use slack information for every node in the circuit graph obtained at the nominal sample to identify non-critical nodes. The corresponding gates are excluded from consideration for statistical analysis based on SH-QMC. In the second stage we make use of information obtained from evaluation of successive SH-QMC samples to find bounds on the statistical behavior of timing slack at each node. When enough information is gathered to tag a certain node as having negligible statistical probability to fall in the critical path(s) for any sample, the node is pruned or eliminated from consideration for the SH-QMC samples yet to be evaluated.

The algorithm is explained in more detail here. As explained, the first stage involves eliminating nodes based on nominal STA. Nodes with positive slack exceeding a threshold value are pruned. This threshold value is chosen to be 10% of the nominal case worst arrival time. The choice is such that the likelihood of a path with greater than the threshold slack being critical is very low. The second stage of pruning is performed once a subset of SH-QMC samples is evaluated. The samples generated by SH-QMC can be partitioned into sets such that within a set the samples are complementary in their coverage of the