# On-chip NBTI and Gate-Oxide-Degradation Sensing and Dynamic Management in VLSI circuits

## by

## **Prashant Singh**

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 2011

#### **Doctoral Committee:**

Professor David Blaauw, Chair

Professor Dennis M. Sylvester

Associate Professor Jerome P. Lynch

Associate Professor Scott Mahlke

# © Prashant Singh 2011

To Divine and

My parents

## Acknowledgements

First of all I can't thank my advisor Prof. David Blaauw enough for his guidance all through my graduate studies. He encouraged and helped me to go on even during the most difficult times. Thanks to Prof. Dennis Sylvester for co-advising me and for his invaluable suggestions all through these years. I would like to express my gratitude towards Prof. Scott Mahlke and Prof. Jerome Lynch for agreeing to be a part of my PhD defense committee.

There are several people who have directly or indirectly contributed to my research studies. Eric, thanks for helping me develop a strong footing in the reliability research. I would like to express gratitude towards the senior research students at Michigan, Sanjay, Visvesh, Carlos, who helped me at some point in time during the past five years. There were several people who helped me when I was going through very rough times. Zhiyoong, Matt, Scott and Mike, I can't thank you all enough for your help and patience.

I need to mention my friends at Michigan who made sure that I never had a dull moment here. Kaviraj, Manav, Shantanu, Ravikishore, Vivek, Rach, Animesh, Ayan, Ritesh – Thanks for the great times you all gave me here in Ann Arbor.

I am indebted to my parents for their support all this time while I was away from home. And lastly, no words can express my gratitude to the Lord, who looked after me as His son while I experienced one of the most important period of my life.

## **Table of Contents**

| Dedica  | ition                                                           | ii  |

|---------|-----------------------------------------------------------------|-----|

| Ackno   | wledgements                                                     | iii |

| List of | figures                                                         | vii |

| List of | Tables                                                          | xii |

| Chapte  | er                                                              |     |

| 1.      | Introduction                                                    | 1   |

|         | 1.1. Reliability Management Techniques                          | 2   |

|         | 1.2. Contributions of this Thesis                               | 6   |

| 2.      | Compact Degradation Sensor to Monitor Negative Bias Temperature |     |

|         | Instability                                                     | 7   |

|         | 2.1. NBTI Degradation Mechanism                                 | 8   |

|         | 2.2. Previous Measurement Techniques                            | 10  |

|         | 2.3. Proposed NBTI Sensor                                       | 10  |

|         | 2.3.1. Circuit Design Principle                                 | 10  |

|         | 2.3.2. Oscillator Modeling                                      | 13  |

|         | 2.3.3. Calibration and Measurement Strategy                     | 15  |

|         | 2.3.4. Experimental Results                                     | 16  |

|         | 2.4. Summary                                                    | 26  |

| 3.      | A Unified 45nm NBTI and Oxide Degradation Sensor                | 28  |

|         | 3.1. Gate-oxide Degradation Mechanism                           | 28  |

|         | 3.2. Previous Gate-oxide Degradation Measurement Techniques     | 30  |

|         | 3.3. Proposed Unified Sensor Design and Operation               | 31  |

|         | 3.4. Silicon Measurements from Sensors                          | 34  |

|         | 3.5. Summary                                                    | 43  |

| 4. | Dynamic NBTI Management (DNM) Using the 45nm Unified NBTI              |    |

|----|------------------------------------------------------------------------|----|

|    | and Oxide Degradation Sensor                                           | 44 |

|    | 4.1. Concept                                                           | 44 |

|    | 4.2. Number of Sensors                                                 | 46 |

|    | 4.3. Reliability Model                                                 | 48 |

|    | 4.4. Algorithm                                                         | 49 |

|    | 4.5. Experimental Results                                              | 50 |

|    | 4.6. Conclusion                                                        | 54 |

| 5. | Early Detection of Oxide Breakdown Through In situ Degradation Sensing | 55 |

|    | 5.1. Previous In situ OBD Detection Techniques                         | 56 |

|    | 5.2. Proposed In situ OBD Detection Technique                          | 56 |

|    | 5.3. Test Chip and Silicon Measurements                                | 61 |

|    | 5.4. More Silicon Measurements                                         | 73 |

|    | 5.5. Summary                                                           | 77 |

| 6. | In situ Bias Temperature Instability (BTI) Sensing Technique and       |    |

|    | Dynamic BTI Management Implementation                                  | 78 |

|    | 6.1. Introduction                                                      | 78 |

|    | 6.2. Concept                                                           | 79 |

|    | 6.2.1. Threshold Voltage Shift Computation                             | 82 |

|    | 6.2.2. Simulation Results                                              | 83 |

|    | 6.2.3. Overheads                                                       | 85 |

|    | 6.3.Test-chip Implementation                                           | 86 |

|    | 6.4. Silicon Results                                                   | 89 |

|    | 6.5. Dynamic BTI Management                                            | 93 |

|    | 6.6.Conclusion                                                         | 96 |

| 7. | Summary and the Road Ahead                                             | 97 |

|    | 7.1. Summary                                                           | 97 |

|    | 7.2. Future Work                                                       | 99 |

|    | 7.2.1. Statistical Modeling of NBTI Degradation                        | 99 |

|    | 7.2.2. In situ Gate-oxide Degradation Sensing                          | 99 |

|    | 7.2.3. Gate-oxide Degradation Recovery                                 | 99 |

|    | 7.2.4.       | In situ BTI Sensing                                 | 99  |

|----|--------------|-----------------------------------------------------|-----|

|    | 7.2.5.       | Mapping of Accelerated Stress Conditions to Nominal |     |

|    |              | Conditions                                          | 100 |

|    | 7.2.6.       | Dynamic Gate-Oxide Reliability Management           | 100 |

|    | 7.2.7.       | Dynamic Reliability Management Implementation       | 101 |

| 8. | Bibliography | 7                                                   | 102 |

## **List of Figures**

## Figure

| 1.1 Lifetime distribution of chips under different process, voltage and temperature                                                                |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------|----|

| (PVT) conditions.                                                                                                                                  | 3  |

| 1.2 Conceptual demonstration of DRM.                                                                                                               | 4  |

| 1.3 Block level representation of a DRM controller.                                                                                                | 4  |

| 2.1 NBTI degradation mechanism.                                                                                                                    | 9  |

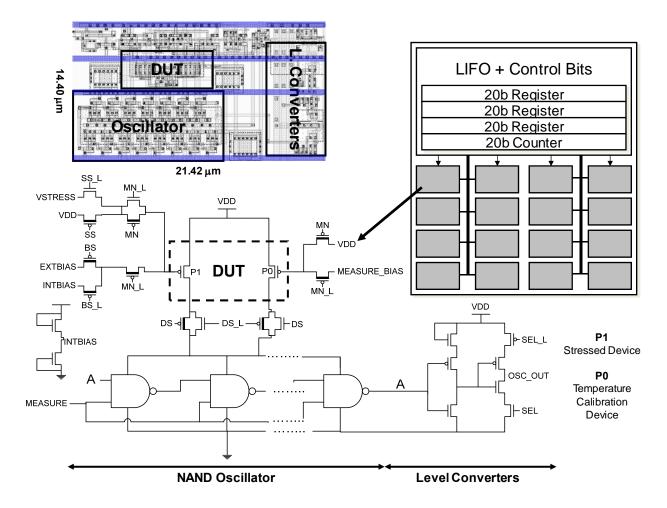

| 2.2 Circuit schematic and layout for the proposed NBTI sensor and the block diagram for a bank of sensors on the test chip.                        | 12 |

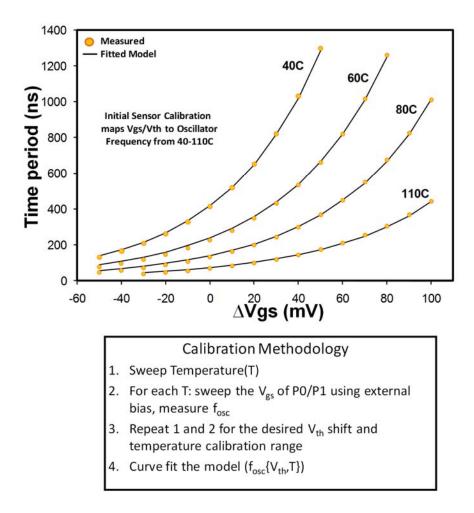

| 2.3 (Top) Discrete experimentally measured frequency and frequency given by calibrated model vs. emulated $\Delta V_{th}$ at several temperatures. | 16 |

| 2.4 NBTI Recovery measured by making four quick measurements.                                                                                      | 17 |

| 2.5 Comparison of sensor output with internal and external bias.                                                                                   | 18 |

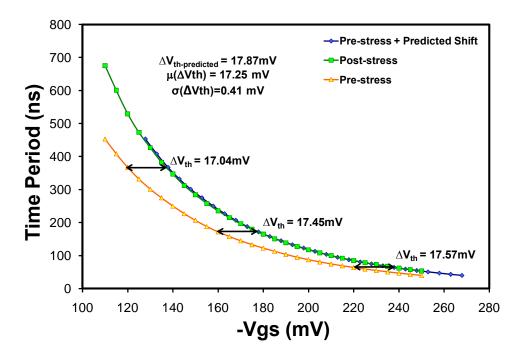

| 2.6 Verification of NBTI measurements.                                                                                                             | 19 |

| 2.7 (Left) Computation of $\Delta V_{th}$ using individual calibration (IC), die calibration (DC)                                                  |    |

| and lot calibration (LC) for 46 sensors on a typical die.                                                                                          | 20 |

| 2.8 Measurement from the NBTI sensor.                                                                                                              | 22 |

| 2.9 (Left) Correlation between amount of $\Delta V_{th}$ post-stress and the amount of                                                             |    |

| recovery.                                                                                                                                          | 22 |

| 2.10 (Left) Intra-die and global variation for 15 dies.                                                                                            | 23 |

| 2.11 (Left) Distribution of NBTI-induced Vth shift across DUTs from 11 dies.                                             | 25 |

|--------------------------------------------------------------------------------------------------------------------------|----|

| 2.12 Distribution of amount of recovery for DUTs recovering under different gate source/drain electric field conditions. | 25 |

| 2.13 Chip microphotograph.                                                                                               | 26 |

| 3.1 (Left) Soft-breakdown.                                                                                               | 29 |

| 3.2 Oxide degradation mechanism.                                                                                         | 30 |

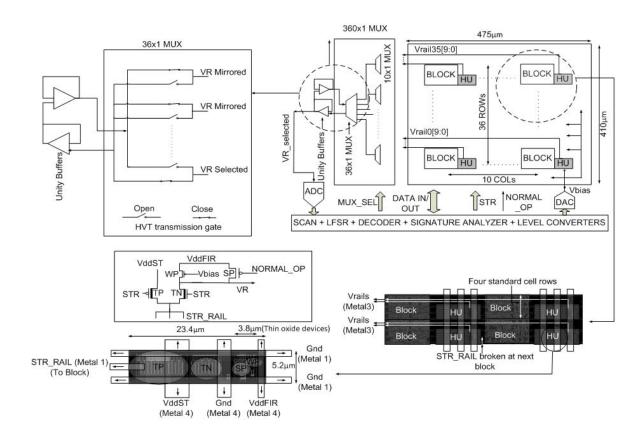

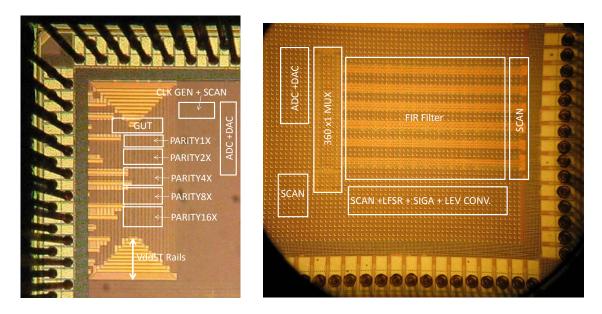

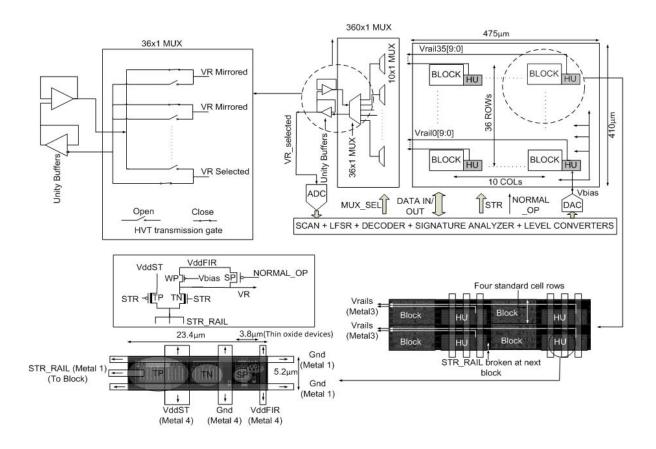

| 3.3 (Top) Sensor circuit, (Left Bottom) Sensor bank Architecture, (Center Bottom) Chip Layout, (Right Bottom) Die shot.  | 32 |

| 3.4 Timing diagram of all the control signals and corresponding sensor modes of operation.                               | 33 |

| 3.5 Gate-oxide stress and measurement results from the sensor.                                                           | 35 |

| 3.6 After a step increase, the gate-leakage becomes noisy and unpredictable.                                             | 36 |

| 3.7 Early soft breakdown detection gives sufficient time for DRM.                                                        | 37 |

| 3.8 No correlation observed between initial gate leakage and time to breakdown.                                          | 38 |

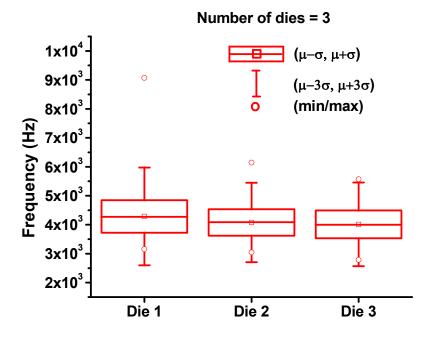

| 3.9 Intra-die distribution of initial gate-oxide sensor frequency of 3 dies.                                             | 38 |

| 3.10  NBTI stress and recovery measurements from the sensor (On:Off = 5:1).                                              | 39 |

| 3.11 NBTI measured under different stress conditions of voltage and temperature.                                         | 40 |

| 3.12 Degradation rate increases as the temperature is increased.                                                         | 41 |

| 3.13 No noticeable change in degradation rate is observed when the temperature is decreased.                             | 41 |

| $3.14\ A$ weak positive correlation is observed between initial $V_{th}$ and NBTI                                        |    |

| degradation.                                                                                                             | 42 |

| 3.15 Short sleep intervals result in 10-15% reduction in $\Delta V_{th}$ and performance                        |    |

|-----------------------------------------------------------------------------------------------------------------|----|

| improvement.                                                                                                    | 43 |

| 4.1 DRM illustrations.                                                                                          | 45 |

| 4.2 Sensor-subset reasonably covers the $\Delta V_{th}$ distribution of 256 devices.                            | 47 |

| 4.3 Chip layout showing the sensor-subset and the 'core' devices.                                               | 48 |

| 4.4 Sampling window of 200 samples gives an accurate model fit.                                                 | 49 |

| $4.5 \; \Delta V_{th}$ distribution after extrapolating the degradation of 32 sensors                           |    |

| (at certain time) to $T_{LT}$ .                                                                                 | 50 |

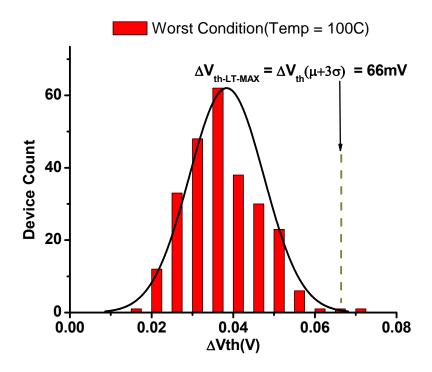

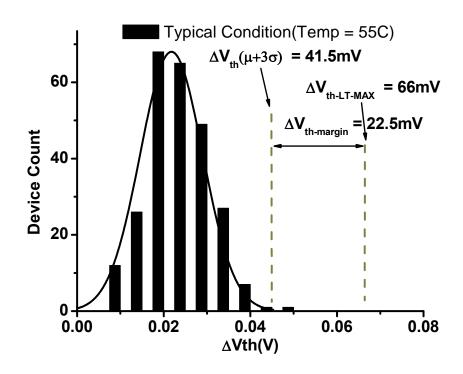

| 4.6 SRM under worst conditions (Temp = 100C, Vstress = 2.2V).                                                   | 51 |

| 4.7 Lowering the temperature increases NBTI margin.                                                             | 52 |

| 4.8 One of the 32 sensors' readings, with model fit and supply voltage                                          |    |

| scaling in a DNM implementation.                                                                                | 53 |

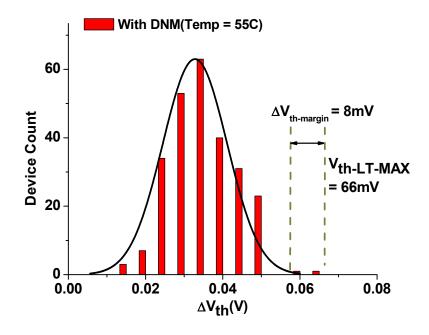

| $4.9 \; \Delta V_{th}$ distribution at $T_{LT}$ with DNM at 55C. The slack was converted into                   |    |

| performance by DNM.                                                                                             | 53 |

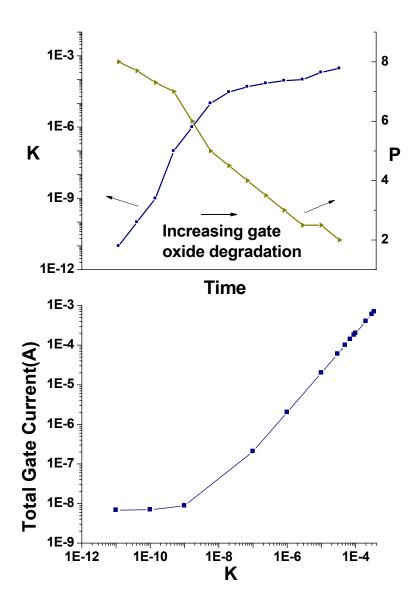

| 5.1 (Top) Increasing gate-oxide degradation can be modeled as an increase in the                                |    |

| value of K and decrease in the value of P.                                                                      | 58 |

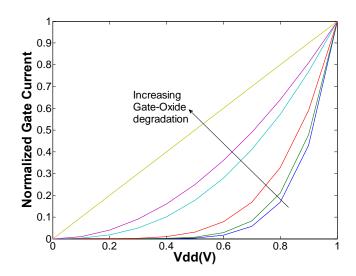

| 5.2 The non linear nature of the Ig-Vgs characteristics of the gate-oxide becomes more linear with degradation. | 59 |

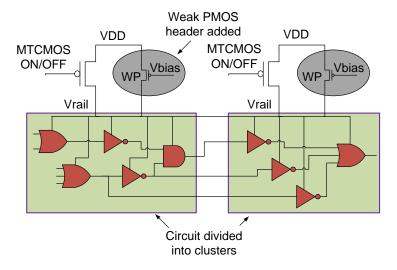

| 5.3 The <i>in situ</i> monitoring technique is implemented by dividing a circuit                                |    |

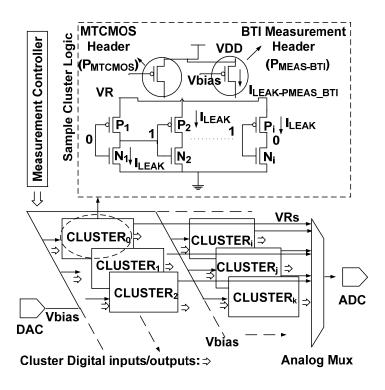

| into clusters using MTCMOS headers.                                                                             | 60 |

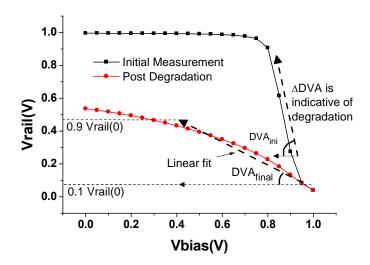

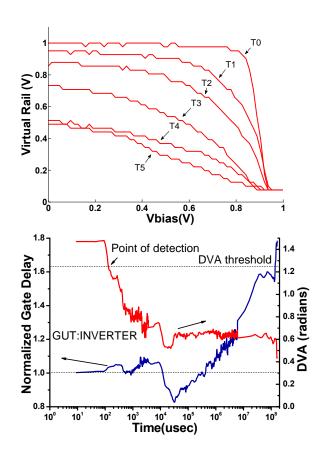

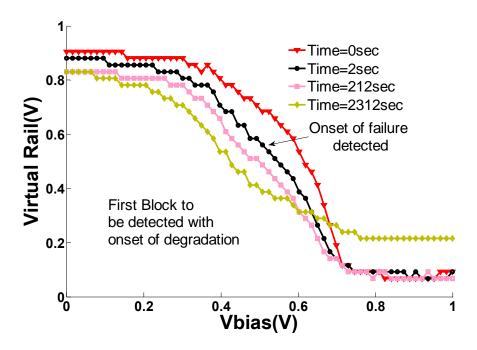

| 5.4 The nature of Vrail vs. Vbias curve changes with degradation.                                               | 60 |

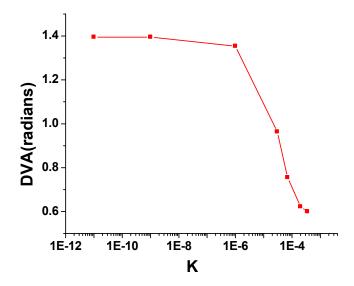

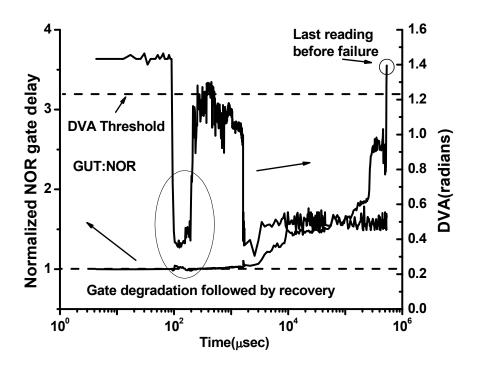

| 5.5 DVA drops sharply with degradation which flags the onset of breakdown.                                      | 61 |

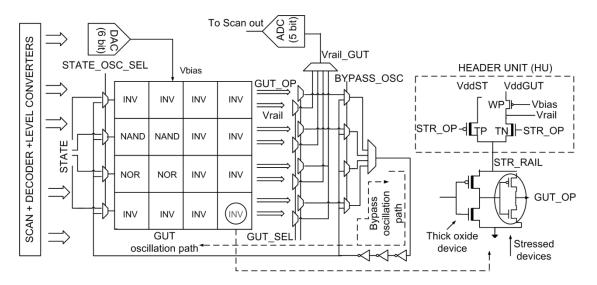

| 5.6 OBD detection technique implemented on GUTs.                                                                                                                                                          | 62 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

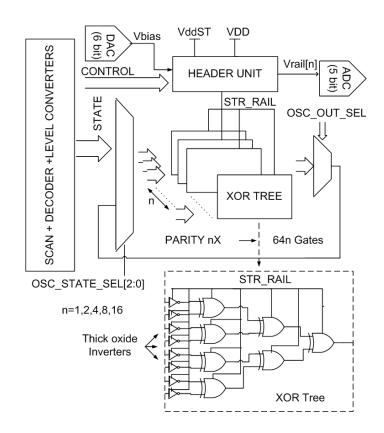

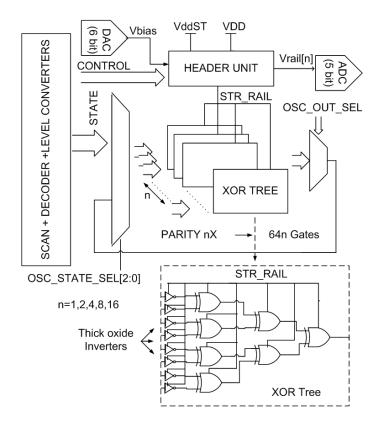

| 5.7 OBD detection technique implemented on XOR Parity trees of different sizes.                                                                                                                           | 63 |

| 5.8 (Top) Silicon measurement of Vrail vs Vbias curve for a stressed INVERTER                                                                                                                             |    |

| at different points of degradation.                                                                                                                                                                       | 64 |

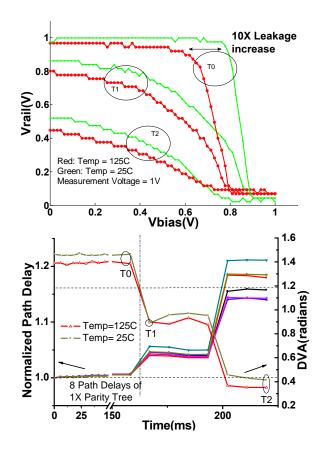

| 5.9 (Top) Silicon measurement of Vrail vs Vbias curves of a 64 gate XOR parity tree at 25C and 125C at three different points in degradation showing immunity of DVA measure to environmental conditions. | 65 |

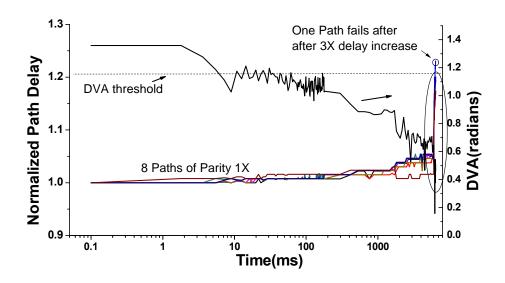

| 5.10 Delay and DVA measurements for an XOR parity tree with 64 gates.                                                                                                                                     | 66 |

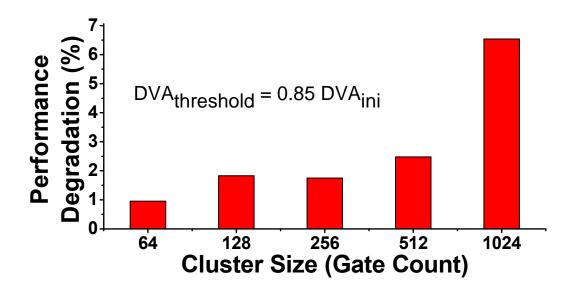

| 5.11 Measurements show that the time to detection of onset of degradation increases with cluster sizes larger than 512 gates.                                                                             | 67 |

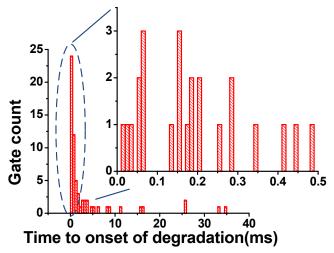

| 5.12 Measurements show a large variation in the time to onset of gate-oxide degradation.                                                                                                                  | 67 |

| 5.13 Sensing circuit implemented on 16 bit, 8-tap FIR filter. 141 blocks were stressed and monitored.                                                                                                     | 68 |

| 5.14 (Top) The performance of the FIR degrades as clusters are detected with onset of gate-oxide degradation.                                                                                             | 70 |

| 5.15 Virtual Rail vs Vbias measurements for the first cluster to be detected with failure, at different points in time.                                                                                   | 71 |

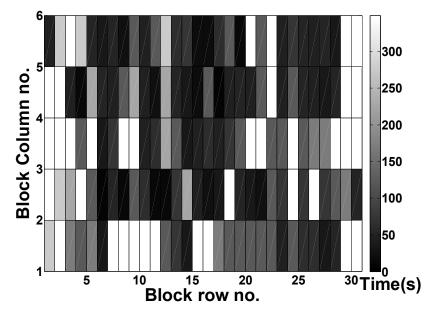

| 5.16 Spatial map of the clusters indicating their time of failure detection.                                                                                                                              | 72 |

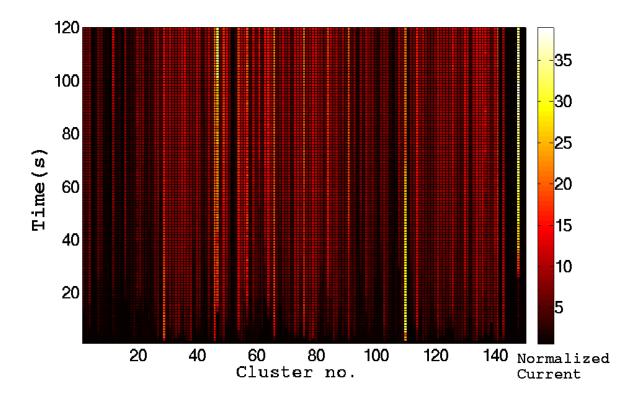

| 5.17 Normalized current of clusters with stressed time.                                                                                                                                                   | 72 |

| 5.18 (Left) Chip 1 microphotograph (Right) Chip 2 microphotograph.                                                                                                                                        | 73 |

| 5.19 Gate-oxide degradation recovery observed.                                                                                                                                                            | 74 |

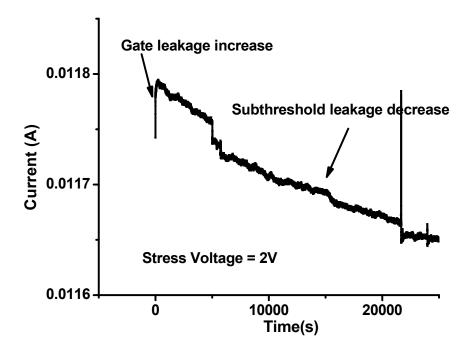

| 5.20 Simultaneous effect of gate leakage increase and threshold voltage shift at lower stress voltage.                                                                                                    | 75 |

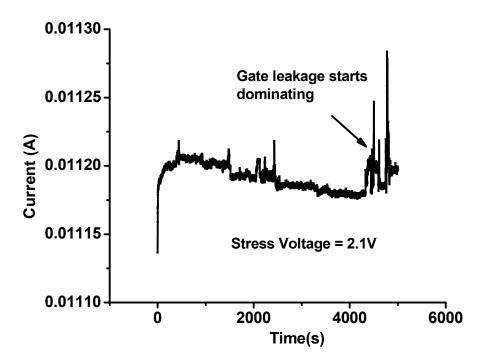

| 5.21 Simultaneous effect of gate leakage increase and threshold voltage shift at lower                    |    |

|-----------------------------------------------------------------------------------------------------------|----|

| higher stress voltage.                                                                                    | 76 |

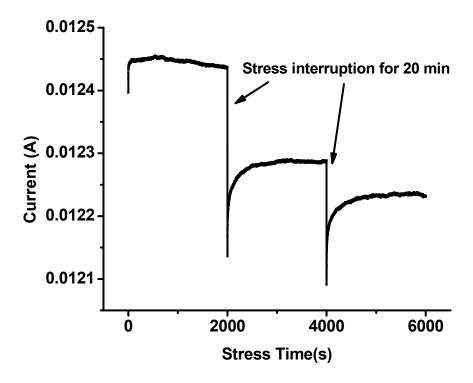

| 5.22 Stress interruption results in lower leakage current.                                                | 77 |

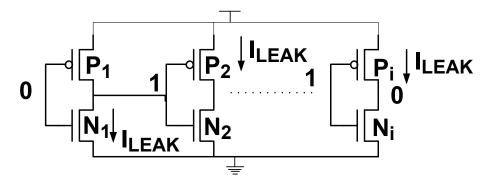

| 6.1 Inverter chain with leaking devices.                                                                  | 79 |

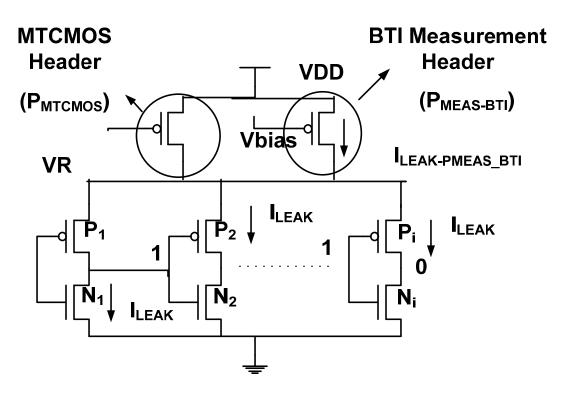

| 6.2 Header based methodology is used to detect BTI.                                                       | 81 |

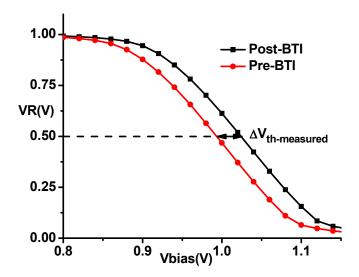

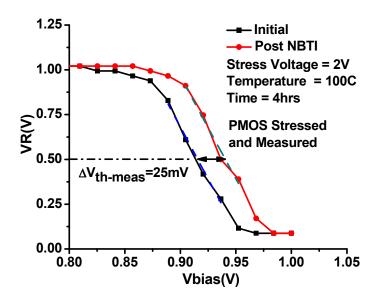

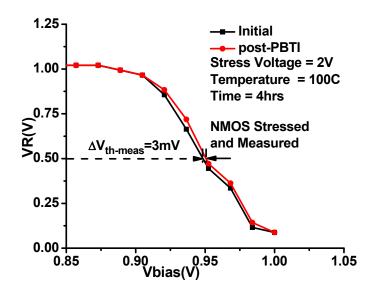

| 6.3 Shift in the VR vs Vbias curve is the measure of threshold voltage shift.                             | 82 |

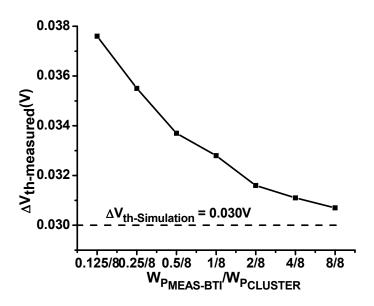

| 6.4 The error in measured threshold voltage shift decreases as the header and cluster widths are matched. | 84 |

| 6.5 A system with BTI measurement technique implemented.                                                  | 86 |

| 6.6 Test-chip with BTI implementation on individual gates.                                                | 87 |

| 6.7 Test-chip with BTI implementation on XOR parity trees.                                                | 88 |

| 6.8 Test-chip with BTI implementation on FIR Filter.                                                      | 89 |

| 6.9 NBTI measurement on an inverter.                                                                      | 90 |

| 6.10 PBTI measurement on an inverter.                                                                     | 91 |

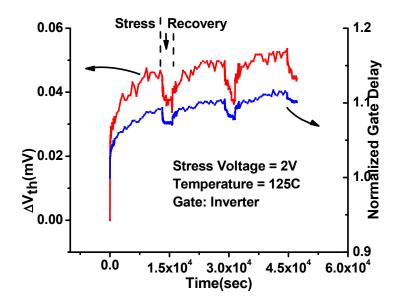

| 6.11 BTI measurement with periodic stress and recovery periods.                                           | 92 |

| 6.12 Threshold voltage shift and leakage measurement for FIR filter cluster.                              | 92 |

| 6.13 Threshold voltage shift distribution among FIR filter clusters.                                      | 93 |

| 6.14 BTI at 125C and 75C leaves margins at the end of life-time.                                          | 94 |

| 6.15 Power law extrapolation used to predict BTI degradation till the end of life-time.                   | 95 |

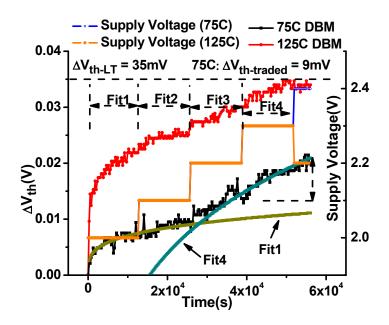

| 6.16 DBM trades excess BTI budget with performance by boosting the supply voltage                         |    |

| at 75C and 125C.                                                                                          | 96 |

### **List of Tables**

| Table                                                                        |    |

|------------------------------------------------------------------------------|----|

| 2.1 (Right) Mean and standard deviation of $\Delta V_{th}$ for 15 dies.      | 23 |

| 4.1 Comparison of $\Delta V_{th}(\mu + 3\sigma)$ of different sensor-subsets | 47 |

## Chapter 1

## Introduction

Silicon industry has come a long way since the invention of integrated circuits in 1958. It has contributed immensely to the improvement of life standards by advancing the field of research, computing, education, entertainment etc. This has been made possible by Moore's Law which allows for more and more transistors to be packed in a given area [1.1]. This in turn enables high level of integration on a single die. But Moore's Law has been sustained only by the technological advancement in lithography which has allowed reduction in the critical dimensions of the transistor or technology scaling. Technology scaling improves the performance of the transistor but at the same time compromises its reliability. Since scaling mainly targets high performance applications, to further boost the performance the supply voltage is not reduced in the same proportion as the critical dimensions are. As a result electric field increases across the transistor gate-oxide, channel, and interconnects which exacerbates transistor degradation mechanism such as gate-oxide wear-out, Hot Carrier Injection (HCI), Bias Temperature Instability (BTI) and Electromigration [1.2]. In older process nodes (above 100nm) the rate of degradation processes was low enough that it did not raise concern over end-of-lifetime failures. But in advanced process nodes (sub 100nm) the aforesaid degradation mechanisms threaten the fulfillment of reliability specifications of the chips. This makes it indispensable to

explore existing reliability management techniques to find out the most suitable of those for advanced process nodes.

#### 1.1 Reliability Management Techniques

Designers have traditionally used static reliability management to meet reliability specifications. This method limits the supply voltage to a fixed maximum value for all fabricated chips such that a chip lifetime of the required level is attained. The lifetime of a chip, however,

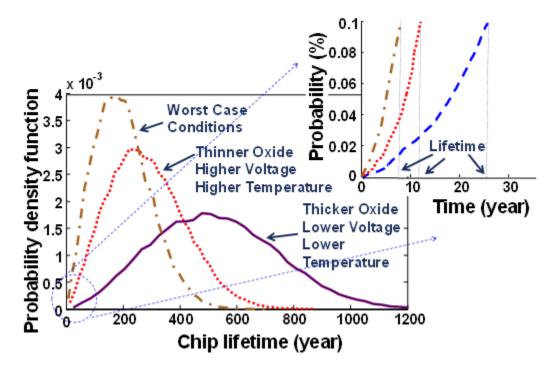

is a statistical variable due to the innate randomness in the degradation process. Moreover, process variation, fluctuations in environmental conditions such as voltage and temperature, and state dependence of the oxide degradation also add to the randomness in lifetime [1.3]. Hence the voltage limit is set so that the *weakest* chip meets the lifetime requirements under worst-case conditions. But In reality these conditions will not be experienced by all chips at all times, making such assumptions very conservative. Hence, many chips will fail much later than the desired lifetime. Fig. 1.1 depicts the aforesaid situation with gate-oxide failure under consideration. A percolation-based oxide degradation model was used in this simulation [1.4]. It shows the lifetime distribution of an ensemble of chips under different process, voltage, and temperature conditions. As the voltage and temperature are lowered and the oxide thickness reduced, the mean and spread in the lifetime of the chips decrease [1.5].

If a lifetime of ten years and a yield of 99.9% are desired, then not more than 0.1% of the chips should fail at the end of ten years. As shown in Fig. 1.1 this does not hold true under the conservative worst process and operating condition assumptions. Hence, the voltage would have to be scaled down until the above mentioned criterion is

met. This results in reduced performance of the chips and a lifetime much greater than the specification for many chips, or a *reliability slack*, owing to pessimistic assumptions. This slack can potentially be traded with performance enhancement by increasing the supply voltage.

Fig 1.1 Lifetime distribution of chips under different process, voltage and temperature (PVT) conditions. The desired lifetime of 10 years is not met under worst PVT conditions [1.5].

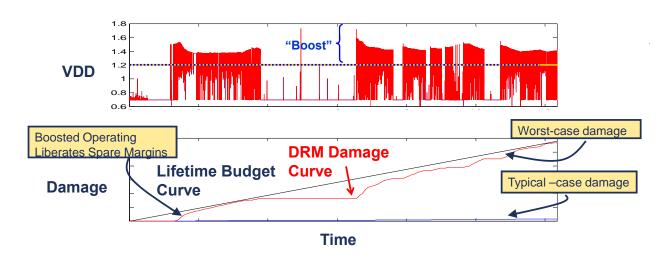

However, this requires that the system is self-aware of its reliability. Such a system is then capable of dynamically adjusting the operating conditions of the chip (in particular, supply voltage and the maximum temperature limit) to achieve peak performance benefits while just meeting the lifetime specification. This approach has been referred to as Dynamic Reliability Management (DRM) [1.6, 1.7, 1.8]. Fig. 1.2 demonstrates the concept behind DRM. The figure shows the lifetime budget curve computed under worst case conditions, with the maximum supply voltage limit of 1.2V. This budget is completely used up under worst conditions. But under typical operating

conditions, the supply voltage is either less than the maximum limit due to less workload or is equal to the maximum allowed supply voltage at the time of maximum workload. Hence at the end of life-time lot of lifetime budget remains unutilized. But a system provided with DRM can exceed the maximum supply voltage limit at the time of peak workload. And hence the lifetime budget is used up to get performance enhancement. Fig. 1.3 shows a block level representation of a DRM controller.

Fig. 1.2 Conceptual demonstration of DRM[].

Fig. 1.3 Block level representation of a DRM controller

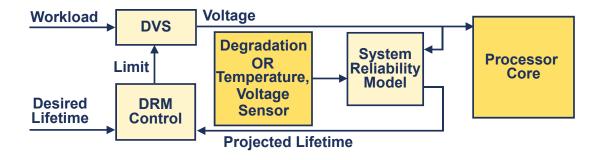

DRM can be implemented in three ways: model based, degradation sensor based, and *in situ* monitoring based.

In the degradation model-based approach, on-chip voltage and temperature sensors are employed to sense the operating conditions of the chip. The data from these sensors is

fed to a degradation model which is used to compute the expected reliability state of the chip [1.6]. DRM systems based on this approach must account for inaccuracies in the sensors and the degradation models themselves by adding margins that make this approach more conservative. In addition, this approach does not address any innate sources of variation in lifetime such as those due to process variation, state-dependence and the inherent randomness of oxide breakdown, and hence has to be used with considerable margins.

The degradation sensor-based approach obviates the need for voltage and temperature sensors as well as degradation models. Instead, it relies on special sensors that directly monitor the degradation of replicated transistor oxides. Degradation sensors are distributed across the core in large numbers so that the sensors experience the same environmental conditions as the devices in the actual circuit. Degradation data from these sensors is then used to estimate the degradation of the actual devices in the chip [1.3]. Since such degradation sensors experience the same process conditions as the actual devices and also do not incur model inaccuracies, they can operate with tighter margins. However, degradation sensors do not account for lifetime variations due to innate randomness of degradation mechanisms, process mismatch between the replicated oxides that are monitored and the functional oxides of devices in the chip, and state dependence of stress. Thus, considerable margins remain.

The *in situ* monitoring-based DRM scheme employs a direct approach to monitor degradation. In this methodology the actual devices used in the circuit are measured directly to determine their degradation. This approach addresses all sources of lifetime variation and hence provides the most accurate observation of degradation, resulting in

almost complete margin elimination. The key challenge is to achieve this with minimal invasiveness and overhead.

#### 1.2 Contributions of this Thesis

So far DRM has been discussed in literature but not implemented or demonstrated in hardware. This work focuses on realizing DRM in hardware and demonstrating its effectiveness. We focus on developing sensor and *in situ* sensing based approaches to DRM. For this work we focused only on BTI and gate-oxide wear-out degradation mechanism. Other degradation mechanisms such as electromigration and HCI need to be addressed in future work.

Degradation sensors have been proposed in past to characterize the degradation mechanisms. These sensors have large area and power overhead and hence are not very well suited for degradation sensor based DRM. Keeping these factors in mind, in this work we propose two versions of NBTI and oxide degradation sensors with low area and power overhead numbers (Chapter 2 and Chapter 3). These sensors are based on standard cell design which reduces the effort in its integration with the core. Furthermore we implement Dynamic NBTI Management (DNM) using the NBTI component of the degradation sensors and quantify its benefits over traditional Static Reliability Management (Chapter 4). We then discuss our work on *in situ* degradation sensing techniques. In Chapter 5 we propose a method to do *in situ* gate-oxide wear-out detection which is capable of sensing the onset of gate-oxide wear-out of the actual core circuitry. We then propose an *in situ* BTI sensing technique and use it to perform Dynamic BTI Management (Chapter 6 and Chapter 7). Finally we conclude with the unanswered questions and the future work in this direction (Chapter 8).

## Chapter 2

## Compact Degradation Sensor to Monitor Negative Bias Temperature Instability

Semiconductor reliability is a growing issue as device-critical dimensions shrink and transistor integration continues to roughly double every 24 months. Aggressive oxide thickness scaling has led to large vertical electric fields in MOSFET devices in which Negative Bias Temperature Instability (NBTI) is a critical issue. Due to NBTI the threshold voltage of PMOS devices increase with time because of which the core logic gets slower and the SRAM bit-cells might become instable. Since NBTI is highly sensitive to operating conditions it is extremely hard to characterize a design with respect to NBTI during design time. This supports the case for on-chip structures to be used for real-time estimation of NBTI degradation in devices and circuits. Since the degradation is a statistical process, hundreds or even thousands of sensors are required to estimate bounds on overall chip performance degradation [1.3]. Hence it is essential that the sensors are small with low power consumption.

This work introduces a new compact structure to quantify the change in performance of devices undergoing NBTI [2.1]. The small size of the sensors makes them amenable to use in a standard cell design with minimal area and power overhead. Compact sensors can be implemented in large numbers to collect high-volume data on device degradation. For instance, based on results from the test chip in this chapter we

observe the effect of initial threshold voltage on the  $V_{th}$  shift due to NBTI and the correlation between amount of  $V_{th}$  shift and the amount of recovery, among other effects.

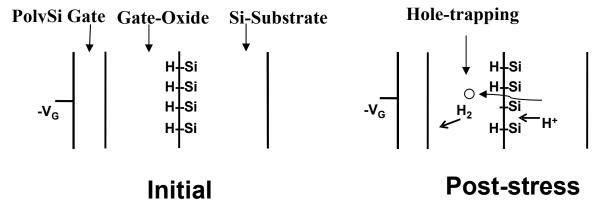

#### 2.1 NBTI Degradation Mechanism

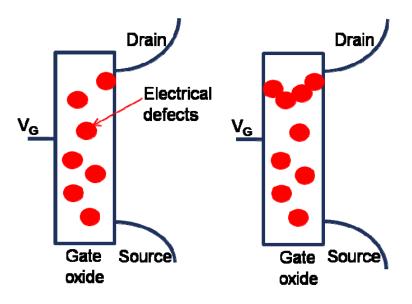

NBTI results in an increased absolute threshold voltage of p-channel MOSFETs, and hence a degradation in drain current and performance. Although NBTI is not a new phenomenon, it has recently become a major reliability issue due to high gate electric fields resulting from scaling, high operating temperatures due to large power consumption on-chip, and the addition of nitrogen to thermally grown SiO2 (since hydrogen diffusion is enhanced in nitride-oxides) [2.2]. Most research on NBTI attributes the threshold shift to the creation of interface traps and oxide charge by a negative gate bias at elevated temperatures (Fig. 2.1). The mechanism involves breaking of Si-H bonds at the Si/SiO<sub>2</sub> interface by a combination of electric field, temperature, and holes. It results in dangling bonds or interface traps at that interface and positive oxide charge that may be due to H<sup>+</sup> [2.2]. The threshold voltage shift due to this mechanism is permanent and cannot be recovered upon removal of stress. The second mechanism involves holetrapping due to electric field in the gate-oxide. Upon removal of the negative stress there is an immediate partial recovery from the threshold shift that occurred during stress. It is due to hole-detrapping in the gate-oxide [2.3].

Fig. 2.1 NBTI degradation mechanism. Interface traps are created by breaking Si-H bonds due to negative gate voltage stress. Positively charged interface traps contribute to threshold voltage shift. Hole-trapping also contributes to vth shift.

NBTI poses a serious threat to chip reliability since significant  $\Delta V_{th}$  can lead to marginal circuit operation (e.g., timing failures in digital logic or bias point drift in analog circuitry) [2.4, 2.5]. Additionally, NBTI degradation in PMOS devices has been shown to cause a reduction in the static noise margin of SRAM cells, leading to read-induced cell stability issues [2.6].

Upon removal of the negative stress, there is an immediate partial recovery from the threshold voltage shift that occurred during the stress [2.7]. This recovery arises due to the partial passivation of the interface traps when the hydrogen diffuses back to SiO<sub>2</sub>-Si interface, as well as the removal of the holes trapped in the oxide defects when the negative stress is removed. NBTI recovery adds to the complexity of measuring NBTI effects. If the measurement interrupts the stress state of the device, the measurement time needs to be sufficiently small (on the order of ms) to avoid masking the actual V<sub>th</sub> shift by inadvertent recovery. This poses the biggest challenge to any experiment seeking to characterize NBTI. The recovery effect also makes it difficult to assess the lifetime of a device undergoing NBTI since the behavior of a device under stress changes once it has been subjected to recovery.

#### 2.2 Previous Measurement Techniques

The aim of most previous work in NBTI measurement has been in the direction of characterizing NBTI. In the past, researchers have used invasive probing methods that require direct access to the device-under-test (DUT) to monitor currents. One large class of work [2.8-2.14] employs a direct current probing approach. Ring oscillator based structures have been proposed in references [2.15, 2.16, 2.17]. All these structures consist of a pair of ring oscillators, one of which experiences accelerated stress. The structure proposed in references [2.15, 2.17] measures the beat frequency (i.e., difference of the two oscillator frequencies) which is attributed to the V<sub>th</sub> shift due to NBTI. These structures produce a digital output which makes it easier to collect and process it. The structure proposed in reference [2.16] requires a controllable external analog bias to map the change in beat frequency to V<sub>th</sub> shift. In reference [2.18] this analog bias is generated on-chip using a delay-locked loop and the ring oscillators is replaced with a voltage controlled delay line. The analog output makes it harder to collect the data from these two approaches [2.16, 2.18]. All of these four proposed structures [2.15-2.18] require a large number of delay stages to get high sensitivity to V<sub>th</sub> change and hence are costly in terms of area and not ideal for use in large numbers (hundreds or thousands) as on-chip sensors.

#### 2.3 Proposed NBTI Sensor

#### 2.3.1. Circuit Design Principles

Fig. 2.2 shows the full schematic of the proposed NBTI sensor, its layout, and the placement scheme for sensors on the test chip. The NBTI measurement technique relies on a PMOS device (P1) to starve the current supplied to a 15-stage NAND gate ring oscillator. There are three modes of operation for this sensor: stress mode, measurement

mode, and recovery mode. In the stress mode, P1 is stressed with negative bias by grounding the input. The change in oscillation frequency during the lifetime of the sensor quantifies the change in  $V_{th}$  of P1. In the measurement mode, P1 is biased in subthreshold to exponentially sensitize the oscillation frequency to  $\Delta V_{th}$ . Experimental results show that biasing P1 in subthreshold leads to a 53% change in oscillator frequency ( $f_{osc}$ ) for 10%  $\Delta V_{th}$ . During recovery mode, the gate of P1 is tied to VDD to allow NBTI recovery.

Subthreshold current is highly sensitive to temperature; therefore, we implemented a control PMOS header P0 to correct for temperature variation. Any change in the P0-starved oscillation frequency gives a measure of this variation. A mathematical model, explained in Section IV.B, maps  $\Delta V_{th}$  and temperature to oscillation frequency.

Fig. 2.2 Circuit schematic and layout for the proposed NBTI sensor and the block diagram for a bank of sensors on the test chip. The sensor operates in i) Measurement mode or ii) Stress/Recovery mode. In i) P1/P0 are biased by EXTBIAS or INTBIAS ( $\sim$ 1V), while in ii) P1 is biased with VSTRESS ( $\leq$ 0) or VDD (recovery mode) and P0 is biased with VDD.

The estimated temperature and the P1-starved oscillation frequency are used to quantify the  $\Delta V_{th}$  of P1 after stress. The additional circuitry consists of an internal bias generator (for measurement mode), four multiplexers (to switch between different modes of operation), and a level converter (at the oscillator output). Multiplexers selectively put 1.) P1 in stress or recovery mode (which allows the application of AC stress on P1), while P0 is always in the unstressed mode 2.) Enable switching from stress/recovery mode to measurement mode, 3.) Select between the internal bias generator and external

bias (from pads), and 4.) Select either P0 or P1 to starve the oscillator. Since the oscillator is strongly current starved, the oscillation amplitude is small. Thus a level converter is used to restore the amplitude of oscillations.

The sensors are arranged in an array and form a bank. The bank also includes one 20-bit counter and three subsequent serially connected 20-bit storage units. The counter and three storage units together allow four quick measurements when a stress cycle is interrupted to conduct measurements, and allow quantifying the fast recovery process. In total, a die contains 96 NBTI sensors.

#### 2.3.2. Oscillator Modeling

The oscillation frequency of the NBTI sensor oscillator can be approximately formulated as

$$\frac{1}{f_{osc}} = \frac{KCV_{amp}}{I_{DUT}} \tag{1}$$

Where K is a fitting constant, C is the capacitance at each stage of the oscillator,  $V_{amp}$  is the amplitude of oscillations, and  $I_{DUT}$  is the average current through the DUT. Simulations show that the peak charging current,  $I_{charge}$ , for a stage of the ring oscillator is roughly equal to  $I_{DUT}$ . This helps to arrive at an expression for  $V_{amp}$ . Since P0 is strongly starved so that the ring oscillator operates in subthreshold,  $I_{DUT}$  and  $I_{charge}$  are governed by the subthreshold current equation:

$$I_{sub} = AT^{2}e^{\frac{V_{GS} - V_{TH} - \gamma V_{BS} + \eta V_{DS}}{nT}} (1 - e^{-\frac{V_{DS}}{V_{T}}})$$

(2)

Here A is a constant that is dependent on device parameters W, L,  $\mu$ , and  $C_{ox}$ . Using (2),

$$I_{DUT} = A_{DUT}T^2e^{\frac{V_{DD} - V_{bias} - V_{thDUT} + \eta(V_{DD} - V_{amp})}{nT}}$$

(3)

Where  $V_{bias}$  is the bias voltage at the gate of the DUT.

Since  $V_{BS}$  is 0, the  $\gamma V_{BS}$  term is dropped. Also, with  $V_{DS} \gg V_T$  the last term can be dropped.

Similarly,

$$I_{charge} = A_{charge} T^2 e^{\frac{V_{amp} - V_{thROSC} + \eta V_{amp}}{nT}}$$

(4)

Where  $V_{thROSC}$  refers to the effective  $V_{th}$  of the devices in the ring oscillator.

Here also the same two terms are dropped by the same reasoning. Based on the previous argument,

$$I_{DUT} = I_{charge} (5)$$

Using (3), (4), and (5), the expression for  $V_{amp}$  becomes

$$V_{amp}(V_{thDUT}, T) = A_1 T + A_2 V_{thDUT} + A_3$$

(6)

where

$$A_1 = \frac{n}{1+2\eta} \ln \left( \frac{A_{DUT}}{A_{charge}} \right)$$

,

$$A_2 = -\frac{1}{1+2\eta}$$

$$A_3 = \frac{V_{DD}(1+\eta) - V_{bias} + V_{thROSC}}{1+2\eta}$$

Furthermore,  $V_{thROSC}$  can be modeled as

$$V_{thROSC}(T) = V_{tho} - T_{coff} \log \left[\frac{T}{T_i}\right]$$

(7)

where  $V_{tho}$  is the threshold voltage at  $T = T_i$ . The value for  $V_{tho}$  and the corresponding  $T_i$ , are taken from SPICE device models. After reducing the number of required fitting constants, (1), (4), (6), and (7) form a system of equations to give

$$f_{osc} = AT^2 e^{\frac{A_1T + A_2V_{thDUT} + A_3(1+\eta) - V_{tho}}{nT}} \frac{1}{A_1T + A_2V_{thDUT} + A_3}$$

$$= g(V_{thDUT}, T, \{A, \eta, n, A_1, A_2, A_3\})$$

(8)

Here  $V_{tho}$  is taken from SPICE models,  $V_{thDUT}$  is the threshold voltage of the DUT, T is the temperature, and A,  $\eta$ , n,  $A_1$ ,  $A_2$ ,  $A_3$  are fitting parameters.

#### 2.3.3. Calibration and Measurement Strategy

The mathematical model developed in the last section must be calibrated, i.e., the fitting parameters need to be calculated. The calibration steps are shown in Fig. 2.3. The temperature and gate bias of the DUT are swept, and frequency is measured. The effect of sweeping gate bias is equivalent to varying threshold voltage. This data is used to curve-fit the model given by Equation 8. Results of the curve fitting at different temperatures are also shown in Fig. 2.3.

The values of the fitting parameters will differ across DUTs due to process variation. Using a particular fixed set of parameters for all DUTs leads to error in the computation of temperature and  $\Delta V_{th}$ . This error varies with the calibration methodology employed. This work investigates three different methodologies and examines the resulting error in each case: 1) individual, 2) die, and 3) lot calibration. Using individual calibration, the fitting parameters are calculated separately for each DUT. This gives the minimum error in temperature and  $\Delta V_{th}$  but at the cost of greatly increased test time and post-test computational requirements. Die calibration involves calibrating the model for only one DUT on each die and then using these derived parameters to model all other DUTs on the chip. With small intra-die variations, this method delivers very reasonable accuracy with a significant reduction in test/calibration time. With lot calibration, just one DUT is examined for the entire wafer lot and fitting

parameters from that device are used for other DUTs within that lot. Experiments were performed to quantify the incurred error when different calibration methodologies are adopted; the results are discussed in the following sub-section.

Fig. 2.3 (Top) Discrete experimentally measured frequency and frequency given by calibrated model vs. emulated  $\Delta V_{th}$  at several temperatures. The model fits the experimental data to minimize the actual  $\Delta V_{th}$  and  $\Delta V_{th\text{-predicted}}$  by sensor. (Bottom) Overview of the calibration methodology.

#### 2.3.4. Experimental Results

The test chip, fabricated in 1.2V/3.3V 130nm CMOS technology, contains 96 NBTI sensors arranged in six banks. Each bank contains 16 NBTI sensors, which are individually addressable for measurement using a 20-bit counter. The threshold voltage in

this technology has a nominal value of 355/-325mV for NMOS and PMOS devices, respectively.

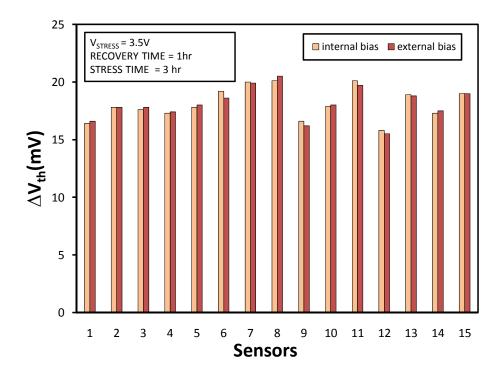

The area of each NBTI sensor is 308  $\mu m^2$  with a stress mode power consumption of 4.5nW and a measurement power of 500nW. A measurement time of 100 $\mu$ s is achieved for results presented. The three serially connected 20-bit storage registers were used to perform four quick  $V_{th}$  measurements at the interval of 100 $\mu$ s, to see the effect of the measurement time on amount of recovery induced by measurements. The results shown in Fig. 2.4 indicate that the measurement period of 100 $\mu$ s induces minimal  $V_{th}$  recovery.

Fig. 2.4 NBTI Recovery measured by making four quick measurements.

Further, the measurement time can be vastly improved by using a high-speed clock for the counter and using the sensor output as an enable signal for the counter. This high speed clock can be as slow as 500MHz to give a high counter count. This clock can

be easily tapped off the system clock with miniscule area and power overhead over the system's area and power consumption. An internal bias generator is included in the design that incurs a maximum of 2.2% error in  $\Delta V_{th}$  measurement relative to the external bias (Fig 2.5). The external bias is used for the results presented here.

Fig. 2.5 Comparison of sensor output with internal and external bias. Internal bias incurs a maximum error of 2.2% over the external bias for the shown sample.

Fig. 2.6 shows results from an experiment to verify that the proposed method of NBTI  $\Delta V_{th}$  estimation measures the actual shift in  $V_{th}$  of the device P1. In this experiment, the gate voltage of the DUT is swept, showing frequency vs.  $V_{gs}$  (Curve A). The DUT is then stressed and subsequently relaxed (allowing some recovery to occur). After the recovery saturates, the gate voltage of the DUT is again swept to obtain Curve B. The horizontal shift between the two curves gives the residual  $\Delta V_{th\text{-sweep}}$ . Then the sensor is used to find  $\Delta V_{th\text{-predicted}}$  based on oscillation frequency. The sensor predicts  $\Delta V_{th}$

accurately with a  $3\sigma$  error of 1.23 mV. Thirteen different points on Curves A and B are used to compute the mean and standard deviation for  $\Delta V_{th\text{-sweep}}$ .

Fig. 2.6 Verification of NBTI measurements.  $V_{gs}$  for P1 is swept before stress and after stress under constant conditions of  $V_{dd}$  and T; the horizontal shift in the two profiles is equal to  $\Delta V_{th\text{-sweep}}$ . The pre-stress profile shifted horizontally by  $\Delta V_{th\text{-predicted}}$  overlaps very well with the post-stress profile.

We also measured the error introduced by using die or lot calibration methodologies. Here the error is computed and normalized with respect to individual calibration. As shown in Fig. 2.7,  $\mu(\Delta V_{th\text{-error}}) = 1.95\%$  and  $\sigma(\Delta V_{th\text{-error}}) = 1.28\%$  for die calibration and  $\mu(\Delta V_{th\text{-error}}) = 2.11\%$  and  $\sigma(\Delta V_{th\text{-error}}) = 1.5\%$  for lot calibration. The confidence interval analysis shows that the margin of error in estimation of mean for die calibration is 0.31% and for lot calibration is 0.36% with confidence level of 90%.

These small errors imply that die and lot calibration provide a good trade-off between accuracy and calibration/testing effort. This has enormous implications on the usability of these sensors in actual chips. For a particular process-technology the sensor can be extensively calibrated and that calibration can be used for the sensors deployed on

chips in that process-technology. In that view the sensors would not need an external bias (primarily required for calibration process) which will reduce the routing overhead of this signal all over the chip. This study was extended to test for temperature correction (Fig. 2.7) and measurements were taken for a wide range of temperatures (10°C to 110°C). The estimates derived from the individual calibration methodology vary the least ( $\sigma/\mu$ = 1.1 %) across the range, followed by die calibration ( $\sigma/\mu$ = 2.1 %) and then lot calibration( $\sigma/\mu$ = 3.1 %).

Fig. 2.7 (Left) Computation of  $\Delta V_{th}$  using individual calibration (IC), die calibration (DC) and lot calibration (LC) for 46 sensors on a typical die. The maximum error incurred by lot calibration  $\sim\!\!6\%$ , which makes it quite reliable to use and simplifies the calibration procedure drastically. (Right) Temperature sensitivity of different calibration methods. IC varies the least across the temperature range, followed by DC and then LC.

Fig. 2.8 shows the characteristic saw-tooth curve generated by alternately stressing and then removing the stress with  $V_{\text{stress}} = 1.7V$  and  $T = 130^{\circ}\text{C}$ . The jitter in oscillations of the sensor due to power supply and bias voltage noise results in noise in the  $\Delta V_{th}$  estimate. Fig. 2.8 also shows the NBTI degradation for different stress conditions.

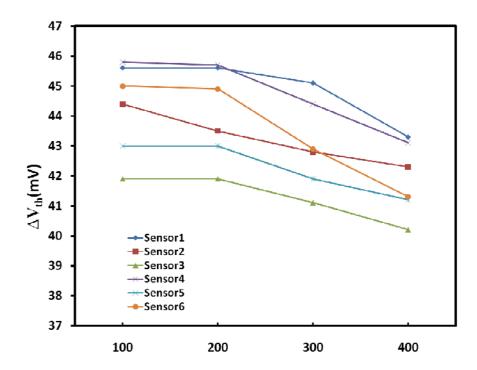

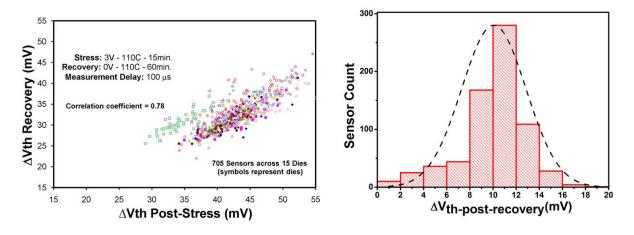

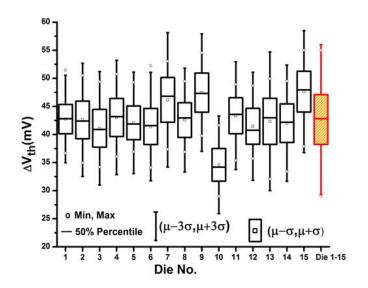

The statistical nature of NBTI degradation is one aspect that has been largely overlooked in the literature. To investigate the probabilistic nature of NBTI, we collected stress/recovery data for 705 sensors across 15 dies with  $V_{stress} = 3V$  and T = 120°C (Fig. 2.9). A measurement time of 100µs is used. We observed a strong positive correlation (correlation coefficient = 0.78) between the amount of  $\Delta V_{th}$  during stress and the amount of recovery. Fig. 2.9 shows the distribution of  $\Delta V_{th}$  post recovery. This shows that the devices suffering more NBTI degradation also recover more significantly if given sufficient recovery time. This finding can be used to dynamically mitigate the severity of NBTI by allocating sufficient recovery time for the blocks suffering higher threshold shifts. Fig. 2.10 shows intra-die distribution of  $\Delta V_{th}$  across 15 dies after NBTI stress and the global distribution. The intra-die variation of  $\Delta V_{th}$  across the dies is fairly consistent. The mean value of four dies (die 7, 9, 10, 15) is off from the cluster of mean  $\Delta V_{th}$  cluster of other dies. The intra-die variation is much more pronounced as compared to inter-die variation. Due to this the global distribution looks very much similar to the intra-die distribution. Table 2.1 shows the mean and standard deviation of  $\Delta V_{th}$  for each die and the global distribution. The statistical data shows that the impact of NBTI on circuit performance is more complex than previously considered. These findings also make the traditional reliability solution such as delay margining, more pessimistic and corroborate the case for dynamic reliability monitoring using NBTI sensors.

Fig. 2.8 Measurement from the NBTI sensor. (Left) Measurement for 15 cycles of periodic stress and recovery mode. (Right) NBTI measured from the sensor under various stress conditions

Fig. 2.9 (Left) Correlation between amount of  $\Delta V_{\text{th}}$  post-stress and the amount of recovery.

(Right) Distribution of  $\Delta V_{th}$  post recovery

| Die no.  | μ(Δ Vth) (mV) | σ(Δ Vth) (mV) |

|----------|---------------|---------------|

| 1        | 42.74787      | 2.597079      |

| 2        | 42.60326      | 3.357749      |

| 3        | 41.11042      | 3.364006      |

| 4        | 43.02913      | 3.393327      |

| 5        | 42.07383      | 3.010861      |

| 6        | 41.4275       | 3.215041      |

| 7        | 46.15894      | 3.987419      |

| 8        | 42.56688      | 3.081232      |

| 9        | 47.46043      | 3.487033      |

| 10       | 34.5934       | 2.89541       |

| 11       | 43.35128      | 3.199631      |

| 12       | 41.46396      | 3.20498       |

| 13       | 42.34354      | 4.112596      |

| 14       | 42.00958      | 3.445013      |

| 15       | 47.63091      | 3.620797      |

| Die 1-15 | 42.67         | 4.44          |

Fig. 2.10 (Left) Intra-die and global variation for 15 dies. Table 2.1 (Right) Mean and standard deviation of  $\Delta V_{th}$  for 15 dies.

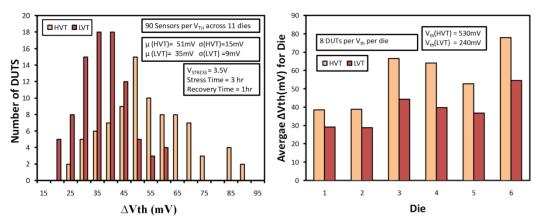

The test chip also allowed the investigation of DUTs with two different (high and low) threshold voltages to examine differences in their NBTI characteristics. Fig. 2.11 shows that high-Vth DUTs exhibit larger NBTI degradation overall. To our knowledge, this is the first time such an observation has been made. A possible explanation could be based on the NBTI model proposed by Tsetseris *et al.* [2.19]. According to this model the following chemical reaction occurs at the Si-SiO<sub>2</sub> interface under stress conditions:

$$Si_3 \equiv SiH + H^+ \rightarrow Si_3 \equiv Si \cdot + H_2$$

Here  $Si_3 \equiv SiH$  is a hydrogen-terminated interface trap and  $Si_3 \equiv Si \cdot$  an interface trap with the dot representing a dangling bond. The hydrogen is believed to originate from the phosphorus-hydrogen bonds in the n-type Si substrate. The P-H bonds dissociate and the hydrogen attracts a hole as it moves to the  $SiO_2/Si$  interface, becoming H+, then reacts with the H from the SiH bond to form  $H_2$ . The net result is a positively charged Si dangling bond (or trapping center) that contributes to the Vth shift. Since the phosphorus

doping is larger for high Vth devices, there is a higher concentration of H+ available for the reaction, resulting in more traps and a consequently greater Vth shift. Another possible explanation could be that due to higher doping there are more Si atoms in the lattice which are not at the Si lattice centers. These dangling Si bonds are passivated by hydrogen. Since there are more number of SiH bonds which could be broken during NBTI stress, it would lead to higher Vth shift.

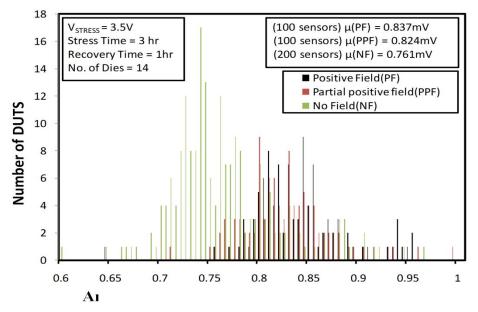

We also investigated the impact of electric field on recovery by designing DUTs to recover in three different conditions of gate bias: 1) zero gate-source/drain bias, 2) positive gate-source/drain bias, 3) and positive gate-drain bias with zero gate-source bias. Fig. 2.12 shows a significant difference in the mean  $\Delta V_{th}$  of zero and positive bias conditions, indicating that the recovery rate is enhanced in the presence of positive electric field. As explained in section II, positive holes trapped in oxide defects also contribute to the threshold shift during negative stress. These charged species are neutralized when the negative stress is removed, which contributes to threshold voltage recovery. When a positive bias is applied at the gate, more of these trapped holes are neutralized, resulting in larger recovery.

Fig. 2.11 (Left) Distribution of NBTI-induced Vth shift across DUTs from 11 dies. HVT devices show higher degradation. (Right) The mean Vth shift of HVT devices is larger across dies. The respective  $V_{th}$  of devices are 530mV (HVT) and 240mV (LVT).

Fig. 2.12 Distribution of amount of recovery for DUTs recovering under different gate source/drain electric field conditions. Application of a positive field increases the amount of recovery in a given time.

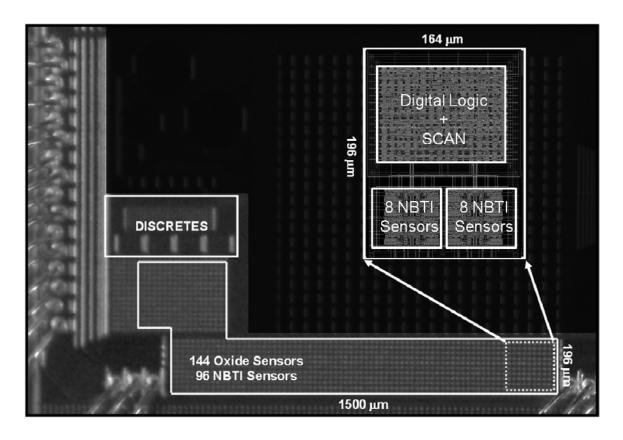

Fig. 2.13 Chip microphotograph

# 2.4 Summary

This work presents compact NBTI degradation sensor with digital outputs. Due to their small size and simple frequency outputs they are amenable for use in standard cell-based designs. The sensors enable high-volume data collection and the monitoring of chip reliability throughout system lifetime. The degradation data supplied by these sensors also aids in understanding and modeling the complex degradation mechanisms. For example, results from a test chip in 130nm CMOS provide new insight concerning the statistical nature of NBTI and gate oxide degradation, the impact of electric field on NBTI recovery, and the relationship between initial  $V_{th}$  and NBTI-induced  $V_{th}$  shift.

The NBTI sensor (308  $\mu$ m<sup>2</sup>) is based on a subthreshold ring oscillator concept and is 110X smaller than previous work. We propose a simple calibration method to process

the sensor output data. We observed a maximum error of 2.2% for the NBTI sensor under process/voltage/temperature variations, yielding  $\Delta V_{th}$  measurements with  $3\sigma$  accuracy of 1.23mV from 40-110°C.

# Chapter 3 A Unified 45nm NBTI and Oxide Degradation Sensor

Process engineers have continuously pushed gate-oxide thickness limits to gain performance. In the advanced process nodes the gate-oxide thickness is less than 15Å, which is approximately 3-4 atomic layers. Since the supply voltage is not scaling proportionately due to performance needs the electric field across the gate-oxide is increasing. In Chapter 2 we discussed how high electric fields exacerbate degradation mechanism such as NBTI. In this chapter in our discussion we will encompass the gate-oxide wear out mechanism as well. Gate-oxide wear-out can be critical than NBTI in the sense that gate-oxide failure of even one transistor can lead to failure of a chip.

In this chapter we propose a unified NBTI and gate-oxide wear-out sensor designed in a 45nm process node. The integration of NBTI and oxide degradation sensing enables efficient reliability monitoring with reduced sensor-deployment effort and overhead. We will discuss the mechanism of gate-oxide wear-out, the previous works on techniques to measure it, and finally we give details on the proposed unified NBTI and oxide degradation sensor and experimental results.

# 3.1 Gate-oxide Degradation Mechanism

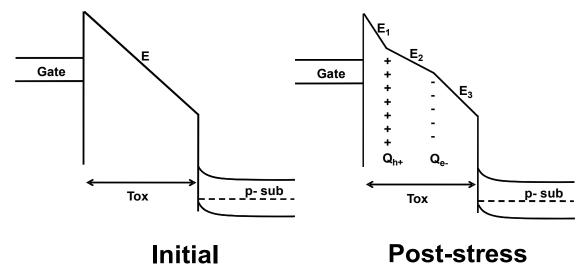

When a voltage is applied across the gate-oxide of a transistor, current flows through it due to quantum-mechanical tunneling. The magnitude of current is determined by the energy barrier offered by the gate-oxide dielectric [3.1]. As carriers flow through the oxide, they are trapped in the free energy-state traps and consequently alter the electric field inside the oxide. This leads to the formation of more energy-traps. When a chain of defects connects the two sides of gate-oxide there is a sudden increase in the gate-oxide current. This condition is called *soft-breakdown* (Fig. 3.1). As more defects paths are formed and they reach a critical density, a step increase in current is observed which leads to catastrophic break-down of the gate-oxide and as a result the oxide no longer behaves as an insulator (Fig. 3.1). Fig. 3.2 illustrates this phenomenon using energy band diagrams.

It is very critical to sense the gate-oxide wear-out early in its onset so that sufficient time is available to manage its reliability and avoid the catastrophic breakdown of the gate-oxide.

Fig. 3.1 (Left) Soft-breakdown. (Right) Hard-breakdown

Fig. 3.2 Oxide degradation mechanism. Electrons flowing through the oxide generate defects which increase the local electric field in the oxide, causing more electrons to tunnel through that region and generating new defects. This positive feedback eventually causes the defects to reach a critical density, leading to destructive breakdown [3.1].

# 3.2 Previous Gate-oxide Degradation Measurement Techniques

As in the case of NBTI, all previous oxide breakdown measurement techniques have been invasive, requiring direct access to DUTs and peripheral circuitry. Uraoka [3.2] evaluates gate oxide reliability using a luminescence method. The set-up requires an optical microscope, photon counting camera, and image processor. References [3.3] and [3.4] propose statistical methods to monitor the yield of gate oxide layers in a manufacturing production line. This technique can be useful in statistically binning the oxide reliability of ICs at manufacturing time but cannot dynamically monitor chip reliability throughout its lifetime.

Gate oxide reliability for high voltage analog power transistors is addressed in [3.5]. A power amplifier (PA) is designed with an oxide reliability monitor for the output stage. The monitoring circuit uses the elements already present in the PA, such as resistors and a pre-driver stage, to measure the conductance of output stage transistors.

Extending this approach to digital circuits would result in large silicon area and power overheads due to analog components. Also, the output of the monitor is an analog voltage, increasing testing costs.

To characterize gate-oxide breakdown reference [3.6] proposed array based test structures in which the gate-oxide of the test devices are stressed. This approach is useful to characterize hard-breakdowns but has limitations measuring the initial gate-oxide wear-out early in its life time due to spurious leakage currents which overwhelm the gate-oxide current. For DRM enabled systems it is important to capture the early on-set of gate-oxide degradation so that the system can take appropriate measures soon enough to increase the remaining life-time of the chip. Finally, in [2.1] oxide degradation sensor was proposed which was smaller in area but consumed high power. In the proposed work we improve upon the oxide-degradation sensor design in [2.1] and reduce its power approximately by 10<sup>5</sup>. Also the design of the sensor is less complicated than the one proposed in [2.1].

# 3.3 Proposed Unified Sensor Design and Operation

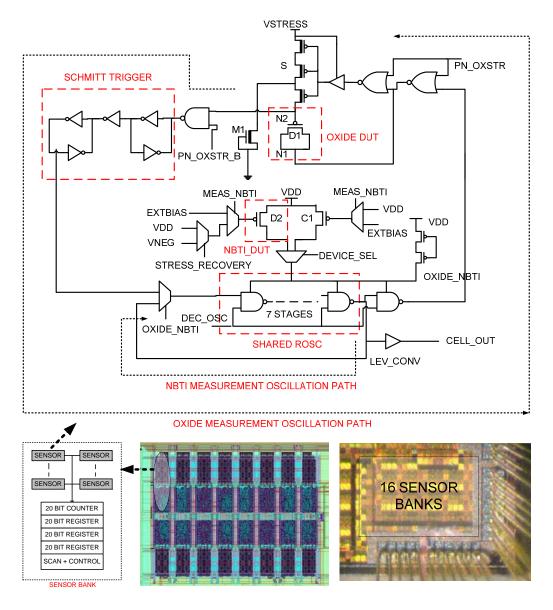

The proposed sensor consists of 2 DUTs (D1, D2), which are stressed and then measured for gate oxide and NBTI degradation, respectively. The other components of the circuit include: 1) muxes, to switch the sensor between stress and measurement modes, 2) a ring oscillator, which is shared between oxide and NBTI sensing circuitry, 3) a Schmitt trigger, to improve the slew of the signal originating from node *N*2, 4) level converters, to output NBTI measurements (Fig. 3.3).

To monitor the gate-leakage of a device it is critical to isolate it from other dominant sources of leakage such as sub-threshold leakage. This made the design in [2.1]

complicated as it had to use oxide-stack divider to isolate the critical node from any source and drain connections. In 45nm the gate leakage is comparable to sub-threshold leakage and we took advantage of this fact to simplify the sensor design by using a transistor stack (S) to stress the node N2. This also obviates the amplifier used in [2.1], which results in power reduction of the proposed sensor design.

Fig. 3.3 (Top) Sensor circuit, (Left Bottom) Sensor bank Architecture, (Center Bottom) Chip Layout, (Right Bottom) Die shot.

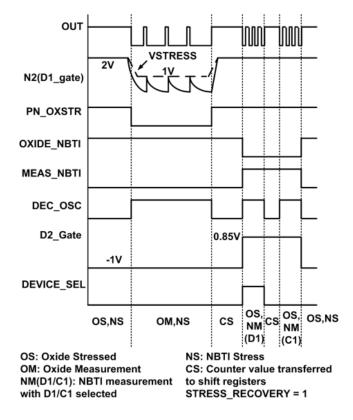

The modes of operation and respective timing diagram of all the control signals and critical nodes are shown in Fig. 3.4. D1's gate oxide is stressed by charging *N2* to *VSTRESS* through the transistor stack S while *N1* is held at ground. During gate-oxide leakage measurement S is cut-off, allowing *N2* to be discharged through the gate leakage of D1. To prevent subthreshold leakage from affecting the discharge time, a cut-off device M1 is added to sink the stack subthreshold current. N2 drives a cross-coupled inverter-based Schmitt trigger to improve the slew of the signal originating from *N2*. The Schmitt trigger drives the ring oscillator, which is shared with the NBTI sensing circuitry. As D1's oxide degrades, its gate leakage increases and N2 is discharged faster, increasing the sensor frequency.

Fig. 3.4 Timing diagram of all the control signals and corresponding sensor modes of operation.

For NBTI sensing, D2 is stressed by muxing in a negative voltage at its gate. In the measurement mode D2 is biased in subthreshold so that any change in its  $V_{th}$  impacts the starved ring oscillator frequency exponentially. Since subthreshold circuits are extremely sensitive to temperature changes, a control header C1 is added to correct for any temperature change. A temperature calibration scheme as described in [2.1] is used.

To record the frequencies a 20 bit counter, along with three 20 bit parallel registers are used. The counter and the storage registers collectively enable four consecutive fast—frequency measurements. This feature is particularly useful to capture the phenomenon of NBTI recovery when the stress is interrupted to make measurements [2.9].

#### 3.4 Silicon Measurements from Sensors

The sensor is implemented in a 45nm CMOS process. The test chip consisted of 16 banks, each bank containing 16 sensors, 80-bit storage which includes 20-bit counter, control and scan logic (Fig. 3.3). The area of the sensor is  $77.3\mu\text{m}^2$  (6 Flip-flops). Sensor stress mode power is 8.6nW (>100,000X lower than [2.1]) while measurement mode power is 84.7nW. Hence the power overhead of laying out thousands of sensors would only be a few hundreds of  $\mu\text{W}$  at maximum, which is a small fraction of power relative to a microprocessor core. The area and power overhead of the storage and other logic can be amortized by inculcating more sensors in a bank.

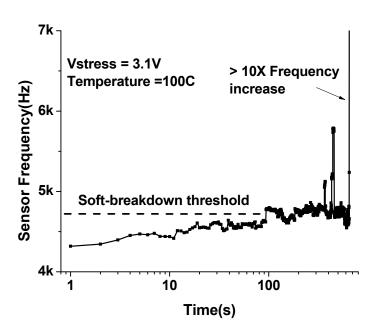

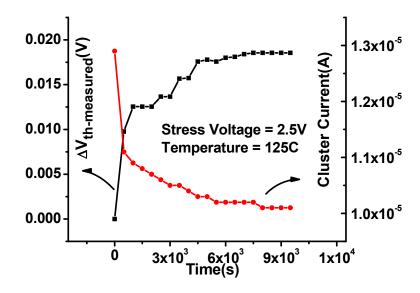

Fig. 3.5 shows the sensor output during gate oxide stress measurement results. The sensor captures the initial gradual increase in the gate-oxide leakage as the oxide wears out. This data would be used by the DRM system to detect onset of gate-oxide wear-out or *soft* breakdown, and raise an alert.

Soft breakdown was defined as a 10% increase in gate leakage. In nominal conditions soft breakdown will occur over years. This is followed by a phase where the leakage remains relatively constant with occasional fluctuations. The fluctuation in gate-leakage occurs because defects are continuously being injected and neutralized during the process of degradation [3.7]. This noisy behavior of the gate-leakage is also indicative of the worn-out oxide as it allows more defect formation. At this point the DRM system would take measures to reduce the rate of wear-out. Finally there is a *hard breakdown* of the oxide marking the end of life of transistor, as a result of which there is a step increase of more than 10X in gate leakage and sensor frequency. The DRM system would ensure that hard breakdown does not occur in the core circuitry, by introducing some pessimism in its analysis while adjusting the supply voltage and temperature limit on the core.

Fig. 3.5 Gate-oxide stress and measurement results from the sensor.

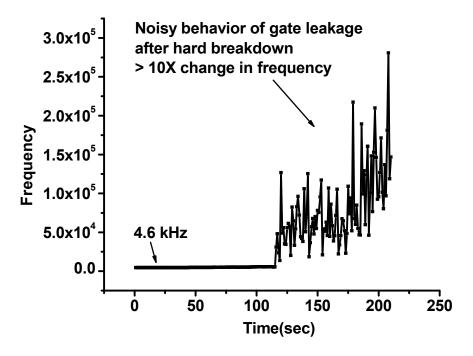

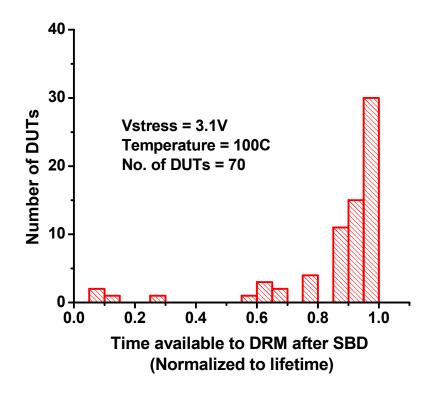

Fig. 3.6 shows the noisy and unpredictable behavior of the gate leakage once it reaches hard breakdown. Fig. 3.7 shows the distribution of time available to the DRM

system after soft-breakdown detection (SBD), normalized to total life time. In this experiment 256 sensors were stressed out of which only 70 had hard breakdown at the end of the experiment. For 95% of the oxides soft breakdown occurred at less than half of their life time. This means that significant time is available to DRM system for reliability management. In remaining 5% of oxides, it can occur as late as up to the last 10% of their lifetime. Even though this number appears small, at nominal conditions it could translate to years which is still a significant time for reliability management.

Fig. 3.6 After a step increase, the gate-leakage becomes noisy and unpredictable.

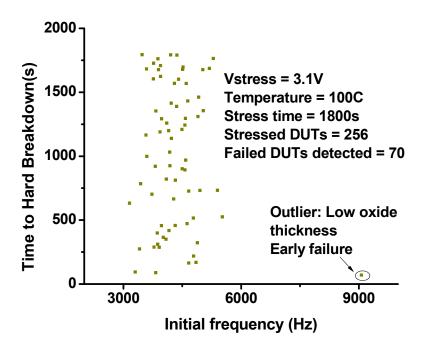

Fig. 3.8 shows little correlation between pre-stress oscillation frequency and time to hard failure. The pre-stress frequency is indicative of the initial gate leakage, or gate oxide thickness. An outlier with high frequency or low oxide thickness will fail early, however similar failure times are observed even for nominal oxide thickness sensors. This confirms the significant randomness inherent in the formation of oxide defects that lead

to failure [3.8] and supports the need for a larger number of low-power and compact reliability sensors on a chip to construct statistical bounds on expected lifetime.

Fig. 3.7 Early soft breakdown detection gives sufficient time for DRM.

Fig. 3.9 shows the intra-die distribution of initial gate-oxide sensor frequency for 3 dies. Die 1 has a clear outlier with low gate-oxide thickness. Knowing that the gate-leakage is exponentially dependent on gate-oxide thickness, it can be seen in general the gate-oxide thickness is very well controlled in this process.

Fig. 3.8 No correlation observed between initial gate leakage and time to breakdown.

This shows inherent random nature of oxide breakdown.

Fig. 3.9 Intra-die distribution of initial gate-oxide sensor frequency of 3 dies.

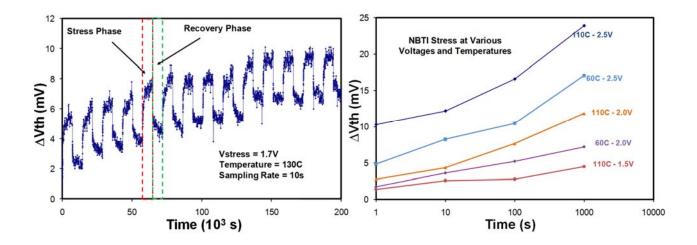

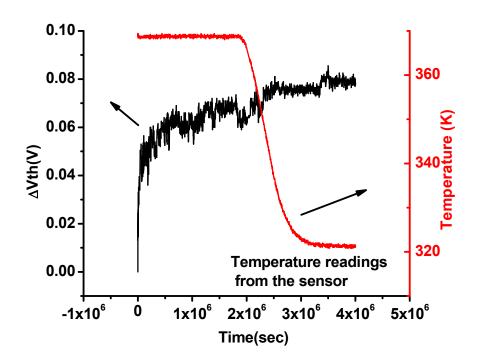

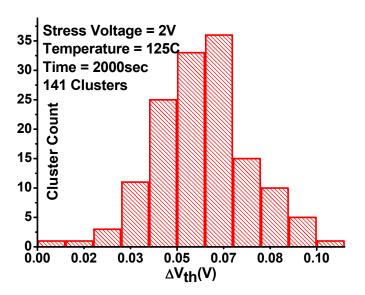

Fig. 3.10 shows typical saw-tooth curve for NBTI degradation of device D2. The measurement time in all NBTI measurements is  $100\mu s$ , which is same as in [2.1]. Fig. 3.11 shows  $\Delta V_{th}$  of D2 due to NBTI, determined using sensor frequency measurements under different accelerated conditions of temperature and voltage. Comparing these threshold shifts in 45nm with results in [2.1] (in 130nm) under similar stress conditions confirms that scaling has significantly increased NBTI effects.

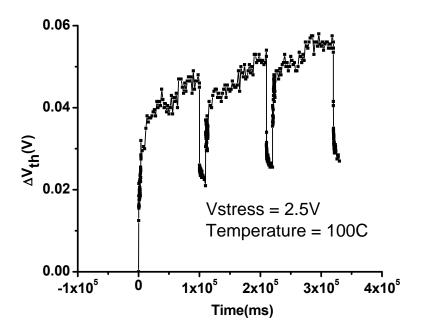

Fig. 3.10 NBTI stress and recovery measurements from the sensor (On:Off = 5:1).

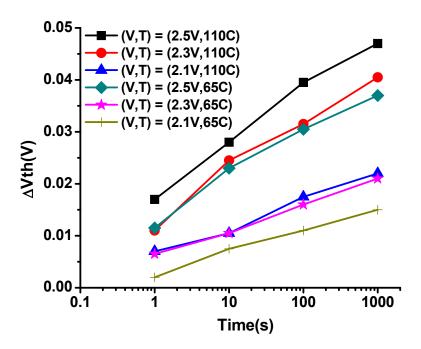

Fig. 3.11 NBTI measured under different stress conditions of voltage and temperature. As expected the degradation shows power law dependence on time.

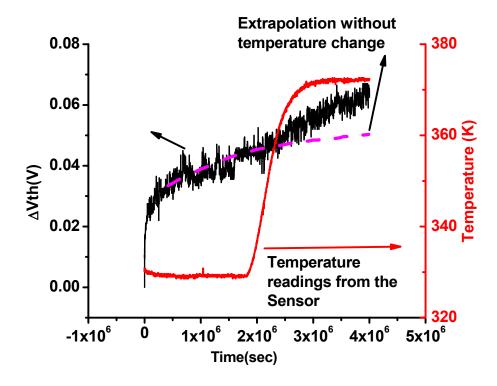

We experimented to see the effect of dynamic temperature variation on NBTI. Fig. 3.12 shows the experiment in which the sensor was stressed at 55C for some time and then the temperature was increased to 100C. The result shows that the degradation rate increases as the temperature is increased. This happens because the number of SiH bonds broken is a strong function of temperature. So the major contribution to the change in V<sub>th</sub> due to temperature mostly comes from the breaking of SiH bonds. The contribution of hole-trapping to V<sub>th</sub> shift is weakly dependent on temperature and strongly dependent on the stress voltage [2.3]. It must be noted that the Si-H bonds cannot be passivated once broken. This is more evident from another experiment, in which we stressed the sensor at high voltage for some time and then reduced the temperature (Fig. 3.13). No change in degradation curve was observed as the SiH bonds cannot be passivated once they are broken and the hole-detrapping/detrapping is a weak function of temperature.

Fig. 3.12 Degradation rate increases as the temperature is increased.

Fig. 3.13 No noticeable change in degradation rate is observed when the temperature is decreased.

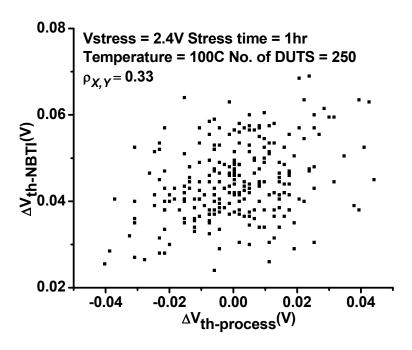

The pre-NBTI  $V_{th}$  differs among devices due to process variation. Fig. 3.14 shows weak positive correlation between pre-NBTI relative  $V_{th}$  and  $\Delta V_{th}$  post-stress due to NBTI. Higher  $V_{th}$  devices are more likely to have large  $V_{th}$  shifts compared to low  $V_{th}$  devices. This indicates that slow corner chips degrade at a higher rate than nominal or fast corner chips. Furthermore, slower chips may operate at higher voltages to meet performance, further accelerating their degradation.

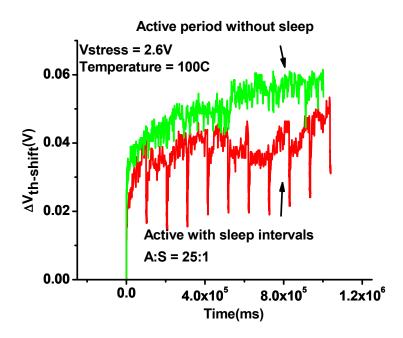

Fig. 3.15 shows results for an implemented reliability scheme where a single active period (DC stress) is divided into ten active periods, each separated by a short sleep (recovery) time with an active: sleep ratio of 25:1. The recovery intervals reduce the degradation rate and hence can improve the overall performance and reliability of the chip.

Fig. 3.14 A weak positive correlation is observed between initial  $V_{\text{th}}$  and NBTI degradation.

Fig. 3.15 Short sleep intervals result in 10-15% reduction in  $\Delta V_{\text{th}}$  and performance improvement.

# 3.5 Summary

A low power unified oxide and NBTI degradation sensor is proposed. Cell power consumption is 10<sup>5</sup> lower than previously proposed sensors. The unified nature enables efficient reliability monitoring with reduced sensor deployment effort and overhead. The sensor sheds insight into key degradation concepts, enabling and potentially improving dynamic reliability management.

# Chapter 4 Dynamic NBTI Management (DNM) Using the 45nm Unified NBTI and Oxide Degradation Sensor

# 4.1 Concept

As described previously due to pessimism adopted in *Static Reliability Management* excess reliability slack is present in the design. This slack can be reduced by *Dynamic Reliability Management*. To implement DRM a system must be able to estimate its reliability. This can be done in a few ways. One proposed approach involves monitoring the voltage and temperature (V, T) of the chip and then estimating its reliability using statistical models [1.6]. But these models become inaccurate and difficult to calibrate under time varying conditions of (V, T) and hence considerable margins remain.

Sensors that directly measure degradation improve on this by eliminating the need for models, thereby enabling greater accuracy of DRM. The degradation sensors lie alongside the core circuitry and the test devices embedded in the sensor are exposed to the same environmental conditions as the core. The measurement circuitry in the sensor then detects the degradation of the test device. Since the environmental conditions vary spatially across the chip, the sensors need to be sprinkled across the chip. Moreover, since the degradation is statistical in nature, hundreds or even thousands of sensors are

required in each locality to capture the statistics of the wear-out. This imposes severe constraints on the area and power of the sensors.

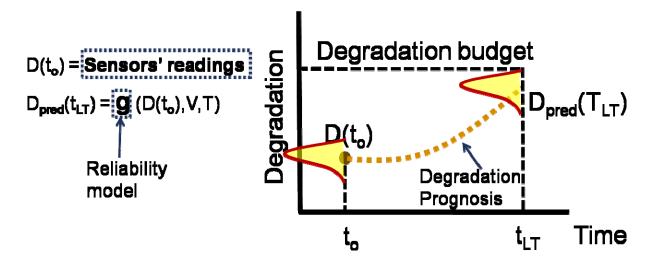

As shown in Fig. 4.1,  $D(t_0)$  is the degradation statistics of the chip at time  $t_0$ . Using a reliability model g for a particular mechanism,  $D(t_0)$  is extrapolated to  $t_{LT}$  to find  $Dpred(t_{LT})$ . If  $Dpred(t_{LT})$  is less than the degradation budget, based on the workload requirements the supply voltage is boosted and/or operation at higher temperature is allowed. On the other hand if  $Dpred(t_{LT})$  is higher than the degradation budget the supply voltage is lowered. Apart from designing sensors with low area and power overhead, another challenge in this approach is to come up with accurate reliability model g. Inaccuracy in g will allow more pessimism to creep in, and the benefits from DRM would be reduced.

Fig. 4.1 DRM illustrations.  $D(t_0)$  is the degradation distribution at time  $t_0$ . Reliability model g uses  $D(t_0)$ , voltage and temperature as input to extrapolate it to  $t_{LT}$ .

$D(t_o)$  is the degradation distribution at time  $t_o$ . Reliability model g uses  $D(t_o)$ , voltage and temperature as input to extrapolate it to  $t_{LT}$ .

Another approach to degradation sensing is to measure the degradation of the actual core devices rather than estimating it from sensors lying beside the core devices. Though this approach removes a layer of uncertainty and pessimism, the technique is more intrusive and complicates the design methodology.

#### 4.2 Number of Sensors

We used the NBTI sensor component of the proposed sensor to perform Dynamic NBTI Management. We performed SRM using worst conditions of temperature and voltage. Since NBTI varies strongly with temperature, we found out the NBTI slack resulting from the operation at a lower temperature. We then use DNM to convert this slack to supply voltage boost and consequently to performance

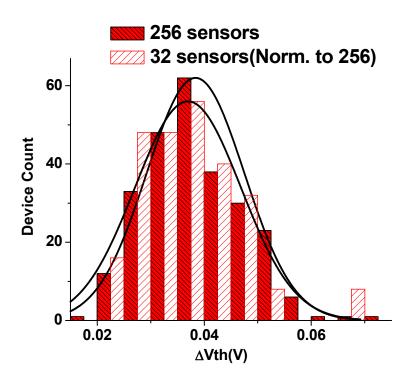

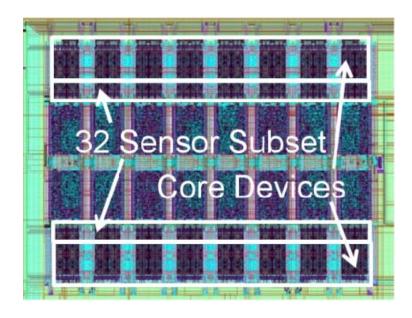

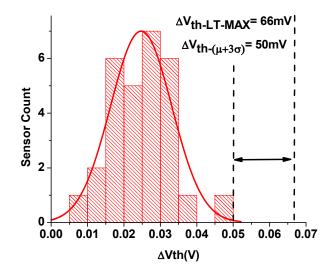

Since there was no actual core implemented in our test-chip, we selected a subset of sensors from the 256 sensors to monitor NBTI while the rest of the sensors are treated as core devices. The challenge in selecting the subset was that it should be small so that the area overhead is small but at the same time it should be able to encompass the  $\Delta V_{th}$  distribution of all the 256 sensors. We compared the ' $\mu$ +3 $\sigma$ ' of sensor subsets of different sizes to the ' $\mu$ +3 $\sigma$ ' of the 256 devices (Table 4.1). Based on that study we selected the size of the sensor subset to be 32 sensors. The normalized distribution of 32 sensor-subset and 256 devices is compared in Fig. 4.2. The subset reasonably covers the distribution of 256 devices. The location of the subset is shown in Fig. 4.3.

| Sensor-subset size(n) | $\Delta V_{th} (\mu + 3\sigma) (mV)$ |

|-----------------------|--------------------------------------|

| 256                   | 66                                   |

| 128                   | 67.5                                 |

| 64                    | 69.3                                 |

| 32                    | 67.1                                 |

| 16                    | 61.5                                 |

Table 4.1 Comparison of  $\Delta V_{th}(\mu + 3\sigma)$  of different sensor-subsets

Fig. 4.2 Sensor-subset reasonably covers the  $\Delta V_{\text{th}}$  distribution of 256 devices.

Fig. 4.3 Chip layout showing the sensor-subset and the 'core' devices.

# 4.3 Reliability Model

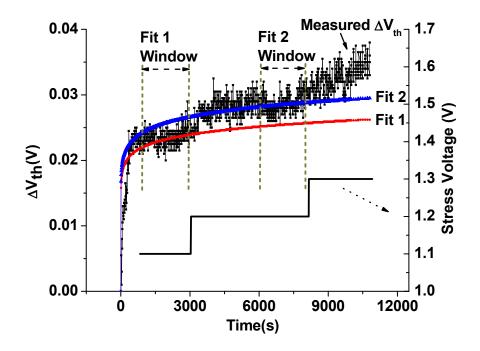

The next step is to come up with an accurate reliability model which can extrapolate the reliability history to the end of life-time. We used a power law model for this purpose which is represented by

$$\Delta V_{th}(t) = K t^{n} \tag{1}$$

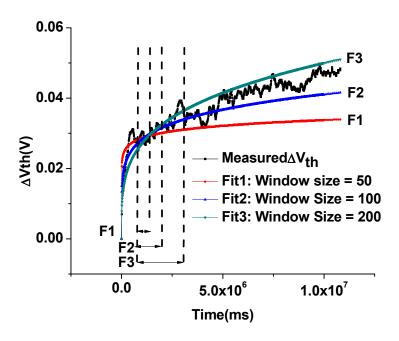

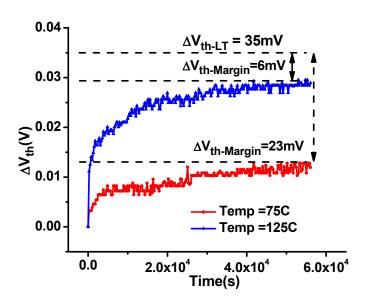

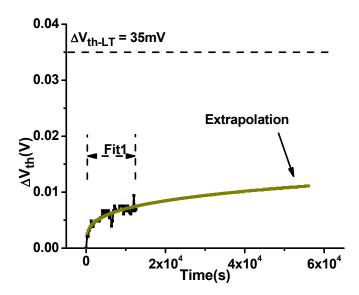

where K and n fitting coefficients. We used a generic power law model because to our knowledge no work has been published which models NBTI with dynamic stress voltage variation. The model is fit over the slow-saturation regime of  $\Delta V_{th}(t)$  curve because that regime gives more information about the long-term prognosis of NBTI. Fig. 4.4 shows the effect of the size of fitting- window on the accuracy of predicted  $\Delta V_{th}$  at the end of life-time ( $\Delta V_{th-LT-PRED}$ ). As shown, a sampling window of 200 samples, as used in this paper, results in an accurate fit. The frequency of sample measurement is 10 seconds.