# Compiling Stream Applications for Heterogeneous Architectures

by

Amir H. Hormati

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in The University of Michigan 2011

#### **Doctoral Committee:**

Associate Professor Scott Mahlke, Chair Professor Todd M. Austin Professor Trevor N. Mudge Professor Dennis M. Sylvester Rodric Rabbah, IBM T.J. Watson © Amir H. Hormati 2011

All Rights Reserved

To my family

#### **ACKNOWLEDGEMENTS**

First, I would like to express my sincerest gratitude to my adviser Prof. Scott Mahlke. I consider myself truly lucky to have worked with him these past years. He has shown incredible patience, served as an excellent mentor, and provided me every opportunity to succeed in this field.

I also owe thanks to the remaining members of my dissertation committee, Prof. Austin, Prof. Mudge, Prof. Sylvester and Dr. Rodric Rabbah. They all donated their time to help shape this research into what it has become today. I would particularly like to thank Rodric for his insightful comments and invaluable advice during my internships at IBM T.J. Watson that helped me in finding an interesting research path.

I was lucky to be part of a research group whose members not only assisted me intellectually in my research but were also a comfort during those long nights before each deadline. Nathan Clark helped me in the first two of years of my PhD. His patience and technical help was the reason I survived those years. Mark Woh spent a countless number of hours discussing new ideas with me and helping me write my papers. Shuguang Feng, Shantanu Gupta, Ganesh Dasika, and Mojtaba Mehrara also helped in proof reading the papers and refining my ideas. Mehrzad Samadi did a great deal of work on the part of this thesis presented in Chapter V.

More importantly than the technical assistance, I would like to thank all the members of the CCCP research group who I've ever shared an office with over the years for their social support: Kevin Fan, Mike Chu, Manjunath Kudlur, Amin Ansari, Hyoun Kyu Cho, Ganesh Dasika, Shuguang Feng, Shantanu Gupta, Po-Chun Hsu, Mojtaba Mehrara, Yongjun Park, Hyunchul Park and Jeff Hao. You folks made coming to work a lot more fun, and I would never have made it through without you. I also want to thank Ganesh Dasika for letting me beat him in Quake. Finishing a PhD without playing Quake would have not been possible.

Finally and most importantly, my family deserves major gratitude. My parents and my sister provided their unconditional love and support through this whole process. I also want to thank my brother who helped me all the way through middle school and high school. My cousin, Abbas, was the reason I chose computer engineering as my major in the first place and I want to thank him for showing me this path. And above all, I really appreciate the love and support of my wife, Mona. Getting through the PhD program, especially in a foreign country, would have not been possible without her.

## TABLE OF CONTENTS

| DEDICATION     |            |      |      |      |             |     |            |     |     |     |   |    |    |   |       |   |   |   |   |   |   |   |   |  | ii   |

|----------------|------------|------|------|------|-------------|-----|------------|-----|-----|-----|---|----|----|---|-------|---|---|---|---|---|---|---|---|--|------|

| ACKNOWLED      | GEMENT     | ſS   | •    |      |             |     | •          |     |     | •   |   |    | •  |   |       |   |   | • |   |   |   |   |   |  | iii  |

| LIST OF FIGURE | RES        |      |      |      |             |     |            |     |     |     |   |    |    |   |       |   |   |   |   |   |   |   |   |  | viii |

| LIST OF TABL   | <b>ES</b>  |      |      |      |             |     |            |     |     | •   |   |    |    | • |       |   |   | • |   |   |   |   |   |  | xii  |

| ABSTRACT       |            |      |      |      |             |     |            |     |     | •   |   |    |    | • |       |   |   | • |   |   |   |   |   |  | xiii |

| CHAPTER        |            |      |      |      |             |     |            |     |     |     |   |    |    |   |       |   |   |   |   |   |   |   |   |  |      |

| I. Introd      | uction     |      |      |      |             |     | . <b>.</b> | •   |     |     |   |    |    |   |       |   |   |   |   |   |   |   |   |  | 1    |

| 1.1            | Streaming  | g t  | o F  | FP(  | ЗA          | s.  |            | •   |     |     |   |    |    |   |       |   |   |   |   |   |   |   |   |  | 4    |

| 1.2            | Streaming  |      |      |      |             |     |            |     |     |     |   |    |    |   |       |   |   |   |   |   |   |   |   |  |      |

| 1.3            | Streaming  | _    |      |      |             |     | _          |     |     |     |   |    |    |   |       |   |   |   |   |   |   |   |   |  |      |

| 1.4            | Flexible ( | _    |      |      |             |     |            |     |     |     |   |    |    |   |       |   |   |   |   |   |   |   |   |  |      |

| II. Input      | Language   |      | •    |      | •           |     |            | •   | •   | •   |   | •  | •  | • |       | • | • |   | • | • | • | • | • |  | 11   |

| III. Mappi     | ng Stream  | ns 1 | to I | FP   | <b>'G</b> A | As  | ٠          |     | •   | •   |   | •  | •  | • | <br>• | • | • |   | • | • |   |   | • |  | 15   |

| 3.1            | Introducti | tior | n    |      |             |     |            |     |     |     |   |    |    |   |       |   |   |   |   |   |   |   |   |  | 15   |

| 3.2            | From Stre  | ear  | mIt  | t to | Н           | arc | lw         | are | •   |     |   |    |    |   |       |   |   |   |   |   |   |   |   |  | 19   |

|                | 3.2.1      | S    | yn   | the  | esiz        | zin | g a        | ı S | tre | ear | n | Gı | ap | h |       |   |   |   |   |   |   |   |   |  | 19   |

|                | 3.2.2      |      | -    | ithe |             |     | _          |     |     |     |   |    | _  |   |       |   |   |   |   |   |   |   |   |  |      |

|                | 3.2.3      |      | •    | dw   |             |     | _          |     |     |     |   |    |    |   |       |   |   |   |   |   |   |   |   |  |      |

| 3.3            | Stream O   |      |      |      |             |     |            |     |     |     |   |    |    |   |       |   |   |   |   |   |   |   |   |  |      |

|                | 3.3.1      | -    |      | eue  |             |     |            |     |     |     |   |    |    |   |       |   |   |   |   |   |   |   |   |  |      |

|                | 3.3.2      |      | _    | eue  |             |     |            |     |     |     |   |    |    |   |       |   |   |   |   |   |   |   |   |  |      |

|                | 3.3.3      |      | _    | o-fl |             |     |            |     |     |     |   |    |    |   |       |   |   |   |   |   |   |   |   |  |      |

| 3.4            | Experime   |      |      |      |             |     |            |     |     |     |   |    |    |   |       |   |   |   |   |   |   |   |   |  |      |

|     | 3.5     | Related Work                                       |

|-----|---------|----------------------------------------------------|

|     | 3.6     | Summary                                            |

| IV. | SIMD    | ization of Stream Graphs                           |

|     | 4.1     | Introduction                                       |

|     | 4.2     | Macro-SIMDization                                  |

|     |         | 4.2.1 Single-Actor SIMDization                     |

|     |         | 4.2.2 Vertical SIMDization                         |

|     |         | 4.2.3 Horizontal SIMDization                       |

|     |         | 4.2.4 Architecture Support for Tape SIMDization 62 |

|     |         | 4.2.5 Implementation                               |

|     | 4.3     | Comparison To Traditional SIMDization              |

|     | 4.4     | Experiments                                        |

|     | 4.5     | Related Work                                       |

|     | 4.6     | Summary                                            |

|     |         | Summary                                            |

| V.  | Portab  | ole Stream Compilation for GPUs                    |

|     | 5.1     | Introduction                                       |

|     | 5.2     | CUDA and GPUs                                      |

|     | 5.3     | Portable Stream Compilation                        |

|     |         | 5.3.1 Actor Reorganization and Classification 92   |

|     |         | 5.3.2 Memory Layout and Optimization               |

|     |         | 5.3.3 Graph Restructuring                          |

|     |         | 5.3.4 Register Optimization                        |

|     |         | 5.3.5 A Stream Compilation Example 105             |

|     | 5.4     | Experiments                                        |

|     |         | 5.4.1 Methodology                                  |

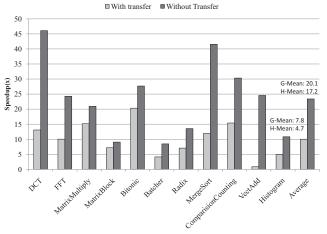

|     |         | 5.4.2 Techniques Performance                       |

|     |         | 5.4.3 Overall performance                          |

|     |         | 5.4.4 Portability                                  |

|     | 5.5     | Case Study and Future Work                         |

|     | 0.0     | 5.5.1 Black-Scholes                                |

|     |         | 5.5.2 Histogram                                    |

|     | 5.6     | Related Work                                       |

|     | 5.7     | Summary                                            |

|     |         |                                                    |

| VI. | Flexib) | le Compilation for Dynamic Resource Changes        |

|     | 6.1     | Introduction                                       |

|     | 6.2     | Background                                         |

|     |         | 6.2.1 Architecture                                 |

|     |         | 6.2.2 Multicore Streaming Layer                    |

|     | 6.3     | Compiler Framework                                 |

|             | 6.3.1     | Static Compilation |      | <br> | <br>  |   | <br> | <br>. 126 |

|-------------|-----------|--------------------|------|------|-------|---|------|-----------|

|             | 6.3.2     | Online Adaptation  |      | <br> | <br>  |   | <br> | <br>. 134 |

| 6.4         | Experime  | ents               | <br> | <br> | <br>  |   | <br> | <br>. 146 |

| 6.5         | Related V | Work               | <br> | <br> | <br>  |   | <br> | <br>. 151 |

| 6.6         | Summar    | y                  | <br> | <br> | <br>  |   | <br> | <br>. 152 |

| VII. Conclu | ısion and | Future Directions  | <br> | <br> | <br>  | • | <br> | <br>. 154 |

| BIBLIOGRAPI | <b>IY</b> |                    |      | <br> | <br>• |   | <br> | <br>158   |

## LIST OF FIGURES

| <u>Figure</u> |                                                                                                                                                                                                                                                                                                                        |    |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

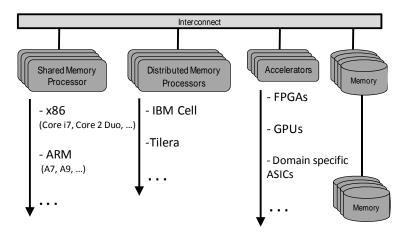

| 1.1           | This figure shows a template for future heterogeneous systems                                                                                                                                                                                                                                                          | 2  |

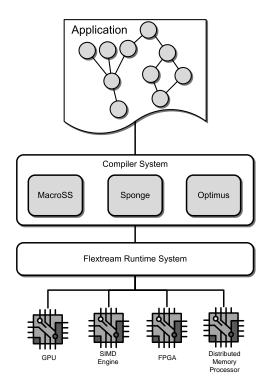

| 1.2           | Overview of our heterogeneous compilation system                                                                                                                                                                                                                                                                       | 4  |

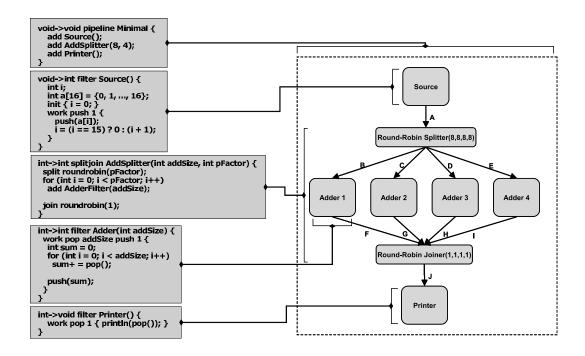

| 2.1           | A sample StreamIt program is shown on the left. The corresponding stream graph with all the filters instantiated is shown on the right                                                                                                                                                                                 | 12 |

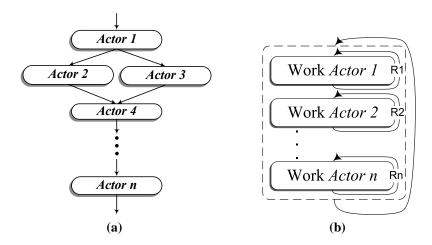

| 2.2           | This figure shows an example stream graph and also the intermediate code template for executing steady state schedule. $R_i$ is the repetition number for actor $i$                                                                                                                                                    | 13 |

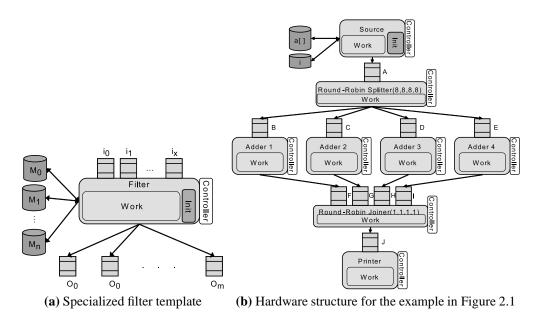

| 3.1           | (a) The specialized template used for synthesizing filters. (b) The complete hardware for the stream graph shown in Figure 2.1                                                                                                                                                                                         | 19 |

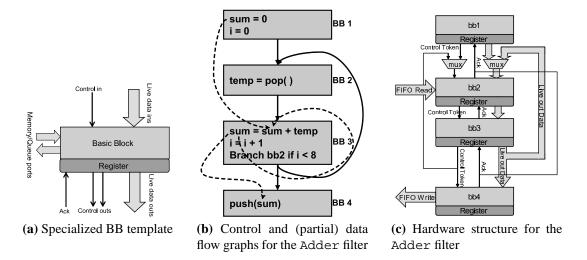

| 3.2           | (a) The template used for synthesizing basic blocks. (b) Control flow graph and partial data flow graph for the Adder filter. (c) The complete hardware generated for the Adder filter                                                                                                                                 | 21 |

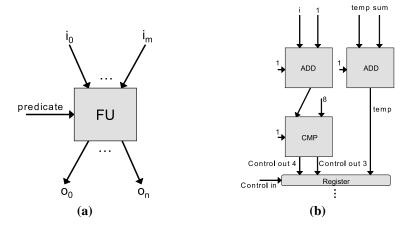

| 3.3           | (a) Template for synthesizing operations. (b) Simplified hardware structure for BB 3 in Figure 3.2b.                                                                                                                                                                                                                   | 23 |

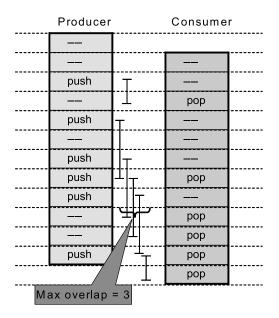

| 3.4           | Overlapped producer-consumer schedules showing maximum number of overlapping lifetimes.                                                                                                                                                                                                                                | 26 |

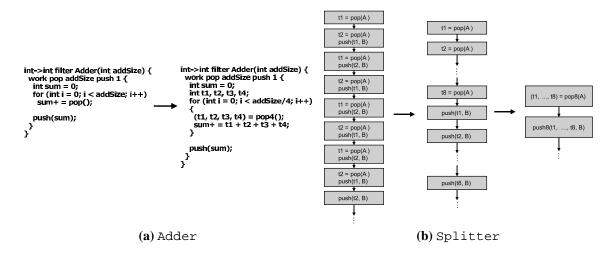

| 3.5           | An example of access fusion using the stream program in Figure 2.1                                                                                                                                                                                                                                                     | 28 |

| 3.6           | Various configuration of queues used by queue access fusion optimization.                                                                                                                                                                                                                                              | 31 |

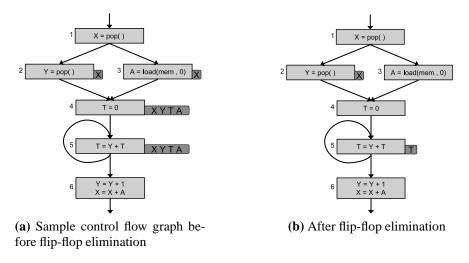

| 3.7           | An example of flip-flop elimination                                                                                                                                                                                                                                                                                    | 32 |

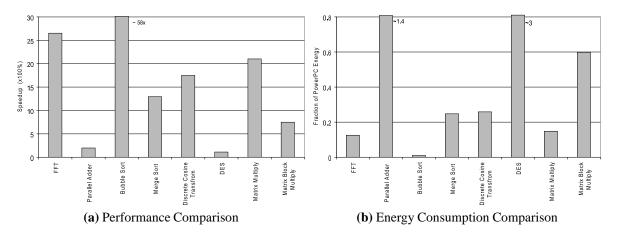

| 3.8           | Figure 3.8a illustrates the speedup comparison between the hardware designs and a 300 mW PowerPC 405 running at 300 MHZ. Figure 3.8b shows the energy consumption of the FPGA as a fraction of PowerPC                                                                                                                 |    |

|               | energy use for various benchmarks                                                                                                                                                                                                                                                                                      | 33 |

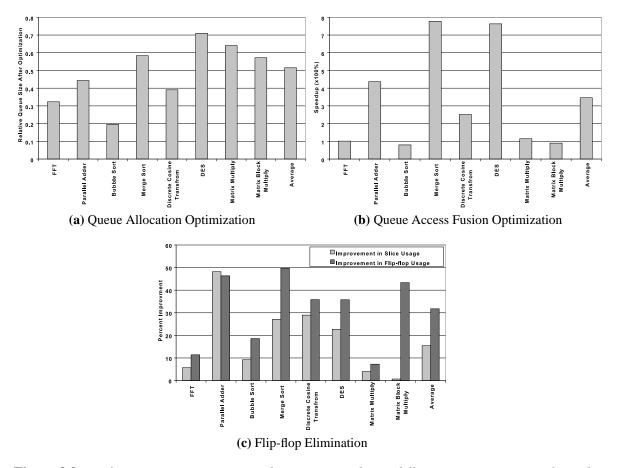

| 3.9           | Performance improvements and area savings due to different optimizations performed by Optimus                                                                                                                                                                                                                          | 34 |

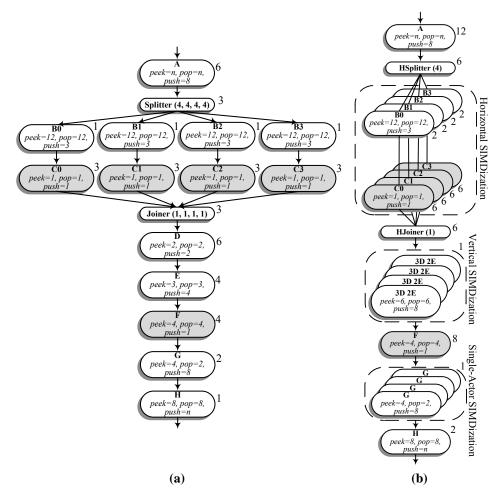

| 4.1           | Part (a) of this figure shows the stream graph used as a running example.  Part (b) shows the same stream graph after MacroSS has SIMDized it                                                                                                                                                                          | 46 |

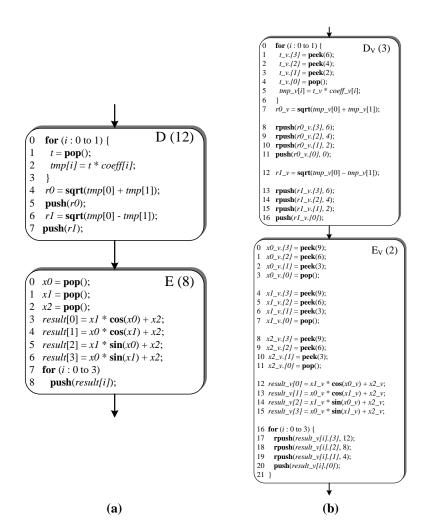

| 4.2           | This figure shows how single-actor SIMDization transforms actors $D$ and $E$ into $D_V$ and $D_E$ . All the vector variables are concatenated with $\_v$ at the end. Part (a) of this figure shows the code for actors $D$ and $E$ in scalar mode. Part (b) illustrates the vectorized version of actors $D$ and $E$ . | 50 |

| 4.3  | Part (a) of this figure shows the stream graph in Figure 4.1a after vertical fusion of $D$ and $E$ . Part (b) illustrates the vectorized code for the fused actor, $3D-2E$                                                                                                                                                                                                                                                                                                                                                                                                                                         | 53 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

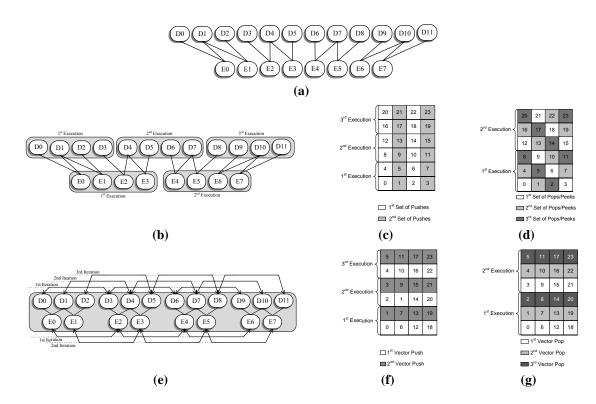

| 4.4  | Part (a) shows scalar execution of actors D and E. Part (b) shows the execution of D and E after performing single-actor SIMDization. Part (c) illustrates the order that data elements are written to the tape in the main memory from D. The elements with the same colors are written in one set of push operations. Part (d) is similar to (c) but for the reads in actor E. Part (e) shows how vertical SIMDization changes the execution order of actors D and E. Parts (f) and (g) illustrate the order that the elements are written to and read from the internal buffer between the inner actors D and E | 54 |

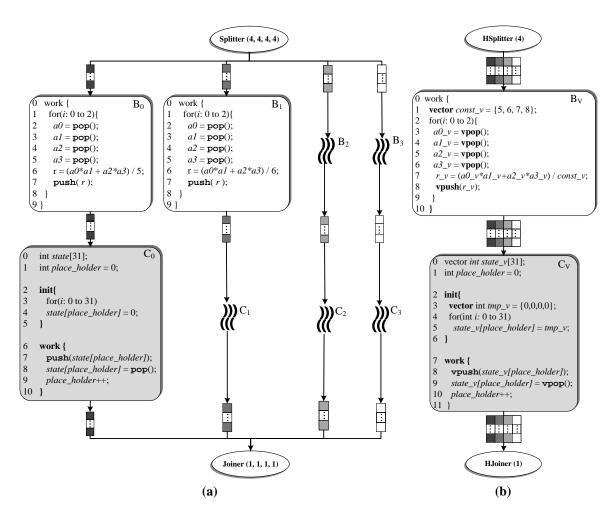

| 4.5  | Part (a) and (b) show the graph before and after horizontal SIMDization, respectively                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 60 |

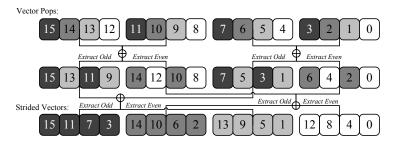

| 4.6  | This graph shows how 16 stride-4 tape reads in an actor are replaced with 4 vector pops and 8 permutation instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 63 |

| 4.7  | This code shows the address calculation in a scalar actor which is the consumer of a vectorized actor with vector pushes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 65 |

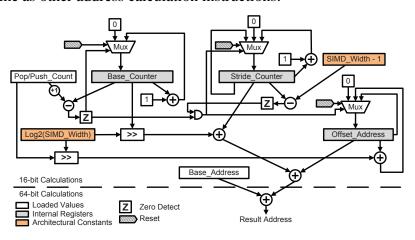

| 4.8  | This figure shows the hardware for the SAGU. $\dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 66 |

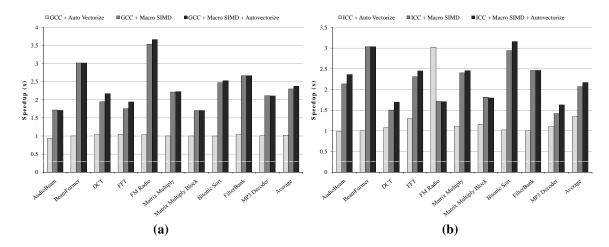

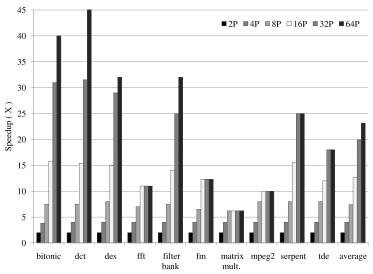

| 4.9  | In this graph the performance benefits of applying traditional auto-vectorization, macro-SIMDization, and both of them together are compared. Part (a) shows the speedups when GCC is used as the intermediate compiler. Applications in part (b) are compiled with Intel Compiler (ICC)                                                                                                                                                                                                                                                                                                                           | 71 |

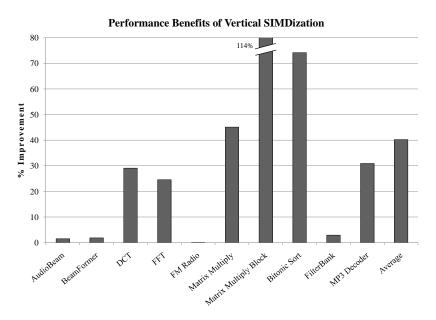

| 4.10 | This graph shows percent speedup due to vertical SIMDization compared to single-actor SIMDization.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 75 |

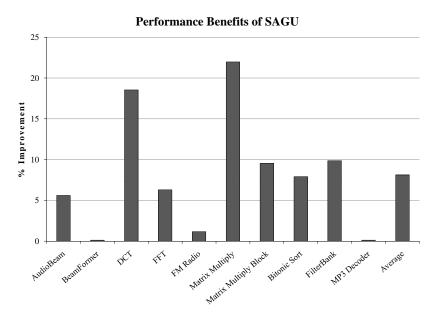

| 4.11 | This graph shows how SAGU can improve the performance of a macro-SIMDized graph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 77 |

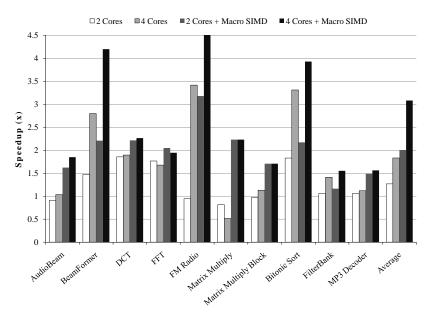

| 4.12 | The performance benefit of SIMDization in case a graph is scheduled for multi-core is shown in this graph.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 78 |

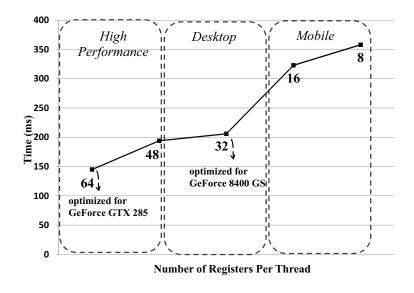

| 5.1  | This graph shows the runtime of a kernel optimized for architectures with different number of registers on a GeForce GTX 285 which has the most number of registers. The kernel used in this graph is organized in 128 blocks each with 256 threads.                                                                                                                                                                                                                                                                                                                                                               | 83 |

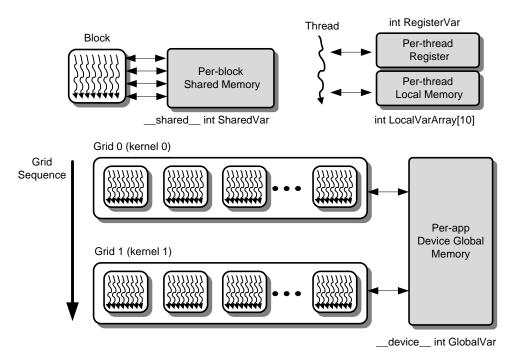

| 5.2  | CUDA/GPU Execution Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 87 |

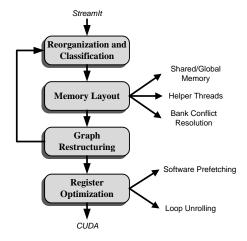

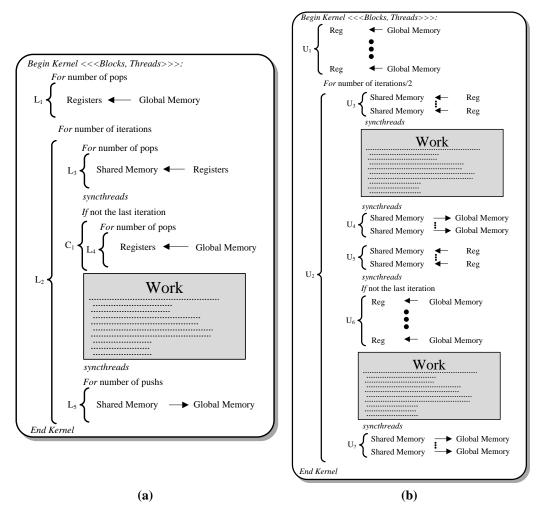

| 5.3  | Compilation flow in Sponge.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 90 |

| 5.4  | In this Figure, equations for calculating execution cycles of both HiT and LoT actors are shown. Equations 5.1 and 5.2 can be used for both HiT                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

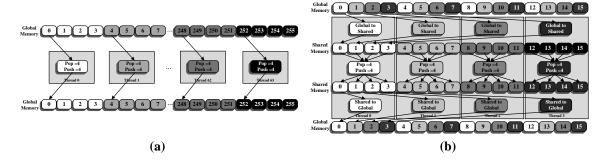

| 5.5  | and LoT actors. The table summarizes what each variable means This figure shows how HiT and LoT threads access their buffers. Part (a) illustrates the memory access pattern for a sample HiT actor with four page and four pushes. Part (b) shows the gages pattern for a LoT actor.                                                                                                                                                                                                                                                                                                                              | 91 |

| 5.6  | pops and four pushes. Part (b) shows the access pattern for a LoT actor. Part (a) shows the baseline translation for a HiT actor. How shared memory is used in a LoT actor is illustrated in part (b). In part (c) the way Sponge generates CUDA code to divide threads as helpers and workers                                                                                                                                                                                                                                                                                                                     | 93 |

|      | is shown.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 96 |

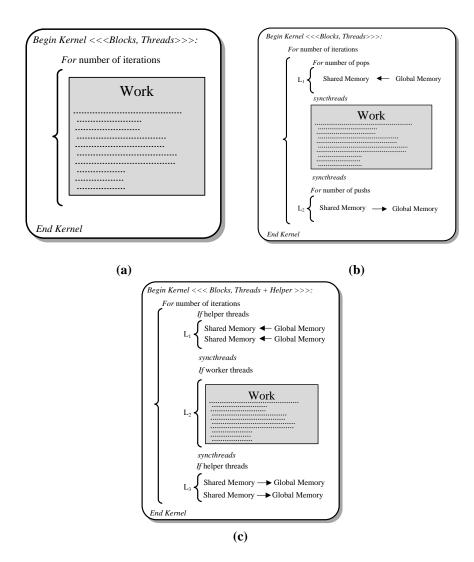

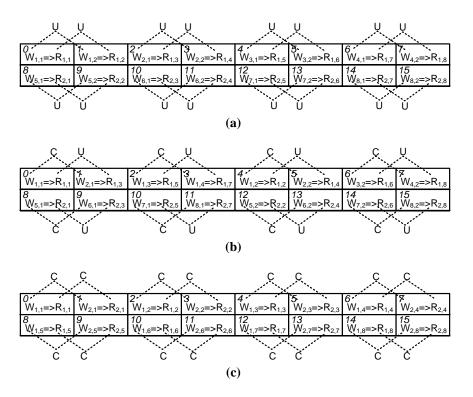

| 5.7        | This figure shows the memory accesses between actors $A$ with 2 pushes and 8 threads and $B$ with 8 pops and 2 threads. $W_{i,j}(R_{i,j})$ shows $j$ th memory write (read) performed by $i$ th thread running actor $A$ ( $B$ ). $U$ and $C$ denote uncoalesced and coalesced. Part ( $a$ ) shows the accesses in the base case. Part ( $b$ ) illustrates the same accesses when the buffer for $A$ is allocated such that its writes are coalesced. Part ( $c$ ) shows coalesced accesses between these two actors when they are fused as $c$ 0 and $c$ 1 are same accessed as $c$ 1 and $c$ 2 are the top left corner of each have |       |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|            | executed with two threads. The number on the top left corner of each box                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 101   |

| 5.8        | shows the memory address of that location                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 101 |

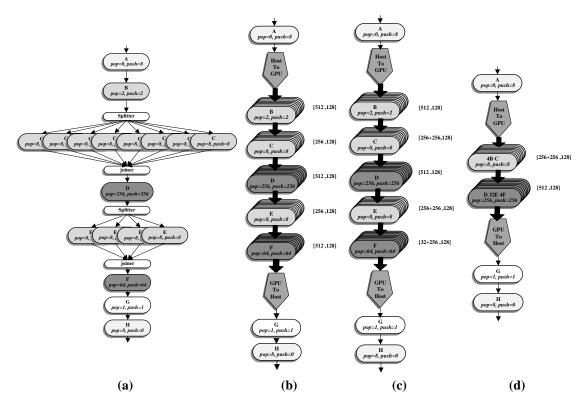

| 5.9        | Part (a) shows a stream graph with 12 unique actors. Part (b) is about how actor classification and graph reorganization affects this graph. In this part, shaded actor are HiT actors. Part (c) illustrates the result of the helper thread optimization. Part (d) depicts the same graph after applying graph restructuring. $[i, j]$ next to each GPU actor shows number of threads $(i)$ and number of blocks $(j)$ that will run that actor. If $i$ is written as $w + h$ , $w$ is number of worker threads and $h$ is the number of helper                                                                                      | . 102 |

|            | threads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 104 |

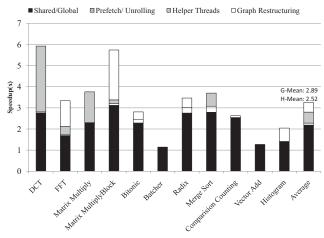

| 5.10       | Effectiveness of Sponge optimization techniques on StreamIt benchmarks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 108   |

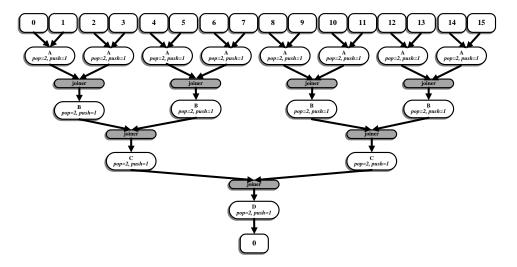

| 5.11       | This graph shows the stream graph of a generic stream reduction kernel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 111 |

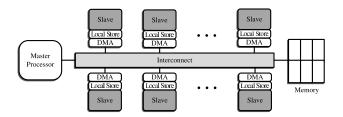

| 6.1        | General architecture template                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 123 |

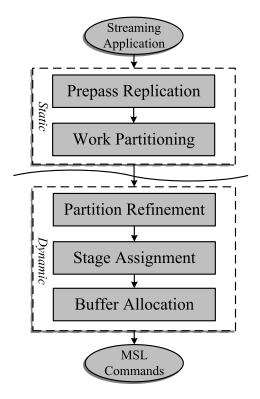

| 6.2        | General flow of the Flextream framework                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 125 |

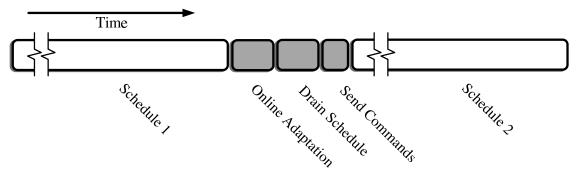

| 6.3        | Overall execution flow at runtime in the case of resource changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 126 |

| 6.4        | Theoretical speedup in the absence of replication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 127 |

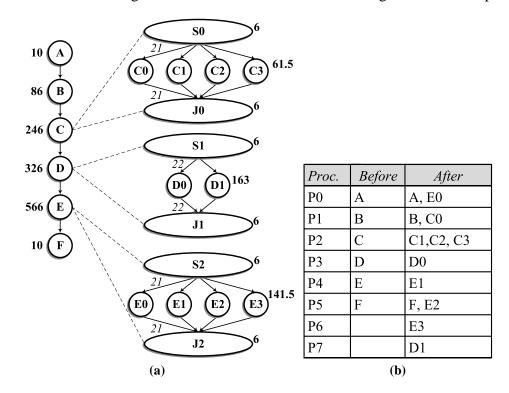

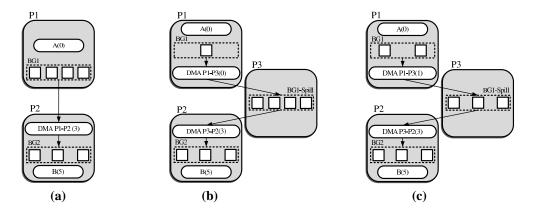

| 6.5        | This figure shows an example stream graph and how replication is performed. Part (a) shows the original graph and the version after replication.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 100   |

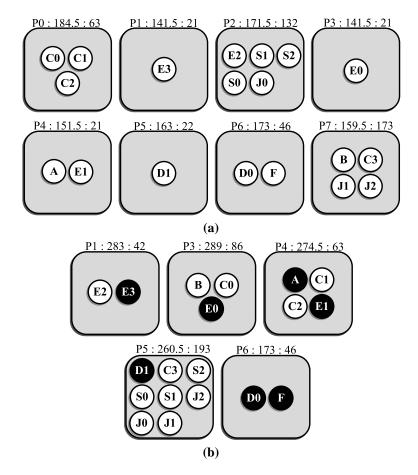

| 6.6        | tion. In part (b), the partitions before and after replication are shown. Part (a) shows the solution of the work partitioning onto 8 cores for the example shown in Figure 6.5a. Part (b) illustrates the solution of the partition refinement if number of cores changes to 5. The actors shaded in black exist in the related processors in the original solution(a) as well as final solution(b).                                                                                                                                                                                                                                 |       |

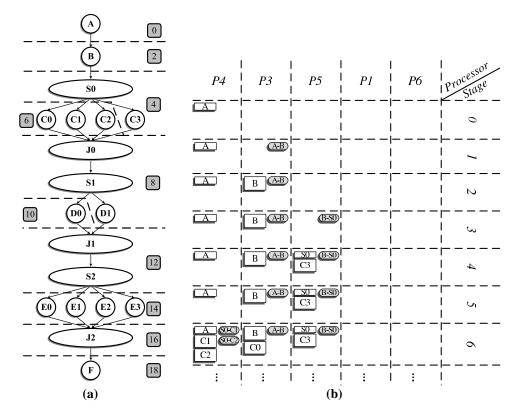

| 6.7        | as final solution(b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 138 |

| 6.8        | first 6 stages of the schedule found by Flextream                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 140 |

| <i>(</i> 0 | schedule and memory consumption is illustrated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 142 |

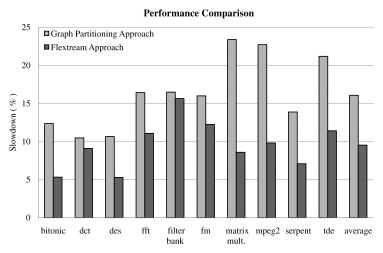

| 6.9        | This graph shows performance degradation when online adaptation is carried out using two different strategies.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 147 |

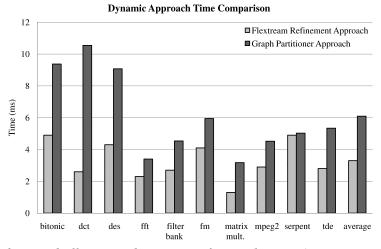

| 6.10 | This graph illustrates the amount of time Flextream's partition refinement       |

|------|----------------------------------------------------------------------------------|

|      | takes and compares it with the graph partitioning approach 147                   |

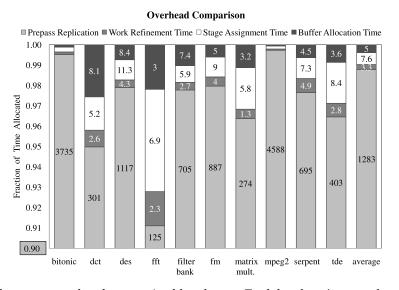

| 6.11 | Flextream overhead categorized by phases. Each bar has 4 parts, show-            |

|      | ing the relative (Y-axis) and absolute (labels within the bars) times spent      |

|      | in each of the static and online phases. Note that the Y-axis starts at 90%. 148 |

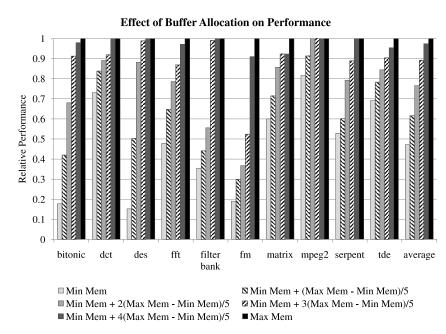

| 6.12 | Effect of buffer allocation on benchmark throughput. For each bench-             |

|      | mark, the amount of memory is increased from a minimum to a maximum              |

|      | capacity. Throughput is recorded for 6 uniformly distributed memory              |

|      | sizes per benchmark                                                              |

## LIST OF TABLES

| <u>Table</u> |                                                                                                                                            |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 3.1          | Area and delay for different queue configurations                                                                                          |

| 5.1          | This table shows how Sponge optimizes each benchmark differently for two GPU targets. For each benchmark and target, the percentage of ac- |

|              | tors that are optimized by each optimization is shown                                                                                      |

| 6.1          | Performance comparison between Flextream and optimal for a runtime scenario in which number of cores varies in this order: 32, 16, 10, 6.  |

|              | Each configuration runs for 250 seconds                                                                                                    |

**ABSTRACT**

Compiling Stream Applications for Heterogeneous Architectures

by

Amir H. Hormati

Chair: Scott Mahlke

Heterogeneous processing systems have become the industry standard in almost every seg-

ment of the computing market from servers to mobile systems. In addition to employing

shared/distributed memory processors, the current trend is to use hardware components

such as field programmable gate arrays (FPGAs), single instruction multiple data (SIMD)

engines and graphics processing units (GPUs) in heterogeneous systems.

As a result of this trend, extracting maximum performance requires compilation to

highly heterogeneous architectures that include parts with different memory and computa-

tion models. Although there has been significant amount of research on programing each of

these architectures individually, targeting a heterogeneous system without specializing an

application to each component separately is still an open problem. Besides performance,

the portability of an application between different pieces of a system and retargetability

to various heterogeneous architectures is a significant challenge for programmers. To effi-

xiii

ciently exploit the heterogeneity, it is necessary to have a programming model that provides a higher-level of abstraction to the programmer and the related compilation framework.

In this thesis, we first focus on enabling a write-once programming paradigm in the context of the stream programming model for various components of heterogeneous systems. We mainly focus on FPGAs, SIMD engines and GPUs as these architectures will play an important role in accelerating various parts of applications on heterogeneous systems. We introduce several compiler optimizations that facilitate portability and retargetability while achieving high performance. As a result of our compilation system, programmers can write a program once and efficiently run it on different components of a system.

Second, we focus on an important challenge that arises in heterogeneous systems when there are dynamic resource changes. The ability to dynamically adapt a running application to a target architecture in the face of changes in resource availability (e.g., number of cores, available memory or bandwidth) is crucial to a wider adoption of heterogeneous architectures. In this work, we introduce a hybrid flexible compilation framework that facilitates dynamic adaption of applications to the changing characteristics of the underlying architecture.

#### CHAPTER I

## Introduction

Support for parallelism in hardware has greatly evolved in the past decade as a response to the ever-increasing demand for higher performance and better power efficiency in different application domains. Various companies have introduced vastly different solutions to bridge the performance and power gap that many applications are facing. These solutions include shared-memory multicore systems (Intel Core i7 [43]), distributed-memory multicore processors (IBM Cell [40]), tiled architectures (Tilera [80]) and in some cases a combination of these (Intel Larrabee [72] and Intel Stellarton [45]). Among these solutions, heterogeneous architectures, as shown in Figure 1.1, not only achieve higher performance and efficiency by combining multiple cores into one die, but they are also equipped with acceleration engines to enable more efficient parallelism support for certain application domains. For example, SIMD engines (e.g., Altivec [73], Neon [6], SSE4 [42]) integrated into multi-core systems enable more efficient data-level parallelism support for several important application domains such as multimedia, graphics, and encryption. Although acceleration engines, such as SIMD units or FPGAs, are not suitable for all applications, if an application can be tailored to efficiently exploit them, the performance and power benefits

**Figure 1.1:** *This figure shows a template for future heterogeneous systems.*

can often be superior to the gains from other general purpose architecture solutions.

Programming heterogeneous architectures is an important problem that is impeding the wider adoption of such systems. Traditional sequential programming languages are ill-suited for heterogeneous architectures because they have a single instruction stream and a monolithic memory. Extracting task/pipeline/data-level parallelism from these languages needs extensive and often intractable compiler analysis. Using a different programming model and compilation framework for each component of the system is also undesirable because it limits the portability and retargetability of the program requiring *each program to be rewritten and optimized for a specific architecture*. Architecture-specific programming models and languages, such as Verilog and CUDA [65], that target specific components, such as FPGAs and GPUs, expose parallelism to the compiler, but in their current form fail to provide portable code and do not present a unified model to the programmer. The main problem with these languages is that explicitly-programmed parallelism in each application has to be tuned for different targets based on the parameters of each hardware component and interfacing between different parts of an application written in different architecture-

specific languages is non-trivial.

A higher level of programming abstraction along with intelligent static and dynamic compiler optimizations can solve the issues of programming heterogeneous systems while maintaining portability and retargetability. One such abstraction is offered by the streaming paradigm. This programming paradigm provides an extensive set of compiler optimizations for mapping and scheduling applications to various parallel architectures ([25, 26]). The retargetability of streaming languages, such as StreamIt [79], has made them a good choice for parallel system programmers. Streaming language retargetability and the resulting performance benefits on multi-core systems are mainly due to having well-encapsulated constructs that expose the parallelism and communication without depending on the topology or granularity of the underlying architecture. Compilers for these languages take advantage of the high-level information available at the program level to efficiently map the exposed parallelism to the target architecture.

Most of the work on stream compilation has so far focused on how to compile streaming applications to homogeneous multi-core systems. However, compiling stream programs to other important components of heterogeneous architectures, such as FPGAs, SIMD engines and GPUs, is still an open question. In this thesis, we propose new techniques and compilation frameworks for static and dynamic compilation of programs in the streaming domain, specifically those implemented in synchronous data flow (SDF, see Chapter II) model, to various components of heterogeneous systems. Our techniques further extend the retargetability and portability of streaming applications by enabling programmers to write a streaming application once and efficiently run it on various parts of a system. An overview of our system is shown in Figure 1.2. The following sections briefly explain the

**Figure 1.2:** Overview of our heterogeneous compilation system.

four parts of our compiler and runtime system: Optimus, Macross, Sponge and Flextream.

## 1.1 Streaming to FPGAs

In the world of heterogeneous systems, especially embedded architectures, there are many devices that offer increasingly powerful computing capabilities. It is predicted that mobile computing devices with embedded processors will ultimately change the industry much as laptops supplanted desktops as the primary commodity processing platform. However, the power and frequency concerns that plague the microprocessor industry effectively mean architects have to find new ways to provide increasing performance since conventional frequency scaling methodologies no longer apply. As a result, there is a significant opportunity to explore alternate architectures that can enable the next evolutionary step in

computing.

One significantly promising approach is to provide automatic customization of hardware according to the applications they run. An application-customized architecture can offer extremely high performance with very low power compared to a more general-purpose design. Furthermore, the increasing availability of reconfigurable field-programmable gate arrays (FPGAs) as co-processors and processing ingredients in heterogeneous systems-on-a-chip [1, 2, 45] means emerging architectures can offer enormous flexibility and adaptability in the face of rapidly changing software standards and customer needs.

In the first part of this thesis, we introduce *Optimus* [37], an optimizing synthesis framework for streaming applications. The main contribution of Optimus is generating hardware by shifting the focus from micro-functional details to macro-functional ones. Specifically, our work does not focus so much on how individual modules are synthesized (i.e., microfunctional), but rather on how modules are composed to assemble an overall design (i.e., macro-functional). As a result, we can synthesize entire applications onto a hardware substrate, and not just individual loops and kernels as is the case with a lot of existing work. Thus, our work is complementary to existing work on high level synthesis while offering new opportunities for efficient assembly of streaming applications in hardware.

### 1.2 Streaming to SIMD Engines

In recent years, almost every single-core or multi-core system has been equipped with one or more single-instruction-multiple-data (SIMD) engines to enable more efficient datalevel parallelism support for several important application domains such as multimedia, graphics, and encryption. SIMD engines are not the right choice for all applications, but in cases where an application can efficiently exploit them, the performance and power gains can be significant. Therefore, SIMD engines like Altivec [73], Neon [6], SSE4 [42] are now an essential part of most architectures on the market. With SIMD width expanding in future architectures, such as Intel's Larrabee, under-utilization of the SIMD units will translate into a significant loss in performance and increase in power consumption.

In general, utilizing SIMD engines is preferred, even for applications where multi-core speedup is close to the theoretical maximum, because SIMD engines can improve performance without increasing communication overhead and memory/cache traffic. Exploiting SIMD engines, in some cases, can achieve greater performance than multi-core while using less area and power.

To exploit SIMD engines in streaming applications, current streaming compilers translate the streaming languages down to an intermediate language, such C++ or Java, and then apply vectorization<sup>1</sup> techniques to generate SIMD-enabled code. The most common techniques are hand-optimizing the code and traditional auto-SIMDization [3, 4, 64, 5, 51]. Both of these solutions have proven difficult to apply in real world scenarios. Hand-optimizing the binary or sequential code using architecture-specific instructions or intrinsic functions is a time-consuming and error-prone task which results in an inflexible and unportable binary. Auto-vectorization is, at this stage, still impractical and far from being able to universally utilize the various kinds of available SIMD facilities. Also, performing SIMDization on streaming applications after intermediate-level code generation may result in an inefficient schedule and mapping of the stream graph since the schedule is already

<sup>&</sup>lt;sup>1</sup>In this work, we use SIMD(ize) and Vector(ize) interchangeably.

fixed and information that is available in the high-level stream graph is lost. Extracting this information from the generated code is predicated on performing complex compiler analysis and transformations which are impossible in some cases. In summary, *the lack of global knowledge about the program, the inability to adjust the schedule*, and also *the loss of data flow information* are the main reasons behind inefficiency of traditional auto-vectorization techniques in dealing with streaming applications.

To address these issues, we introduce *MacroSS* [36]; a streaming compiler for streaming applications that is capable of performing macro-SIMDization on stream graphs. Macro-SIMDization uses high-level information such as the valid set of schedules and communication patterns between actors to transform the graph structure, vectorize actors of a streaming program, and generate intermediate code (C++ in this work). Then, it uses the host compiler to compile the generated intermediate code to binary for a specific target processor. The information that is used by MacroSS is deduced from the high-level program structure and is not available to low-level traditional compilers that are used to compile the intermediate code. As a result, MacroSS has a broader understanding of the program structure and macro-level characteristics of the streaming application that allows the compiler to utilize SIMD engines more efficiently.

## 1.3 Streaming to GPUs

Recently, heterogeneous systems that combine traditional processors with powerful GPUs have become standard in all systems ranging from servers to cell phones. GPUs achieve their high performance and efficiency by providing a massively parallel architec-

ture with hundreds of in-order cores while exposing parallelism mechanisms and the memory hierarchy to the programmer. Recent works have shown that in the optimistic case, speedups of 100-300x [67] and in the pessimistic case, speedups of 2.5x [54] have been achieved between the most recent versions of GPUs compared to the latest processors. Maximizing the utilization of the GPU in heterogeneous systems will be key to achieving high performance and efficiency.

While GPUs provide an inexpensive, highly parallel system for accelerating parallel workloads, the programming complexity posed to application developers is a significant challenge. Graphics chip manufacturers, such as NVIDIA, have tried to alleviate the complexity problem by introducing user-friendly programming models, such as CUDA [65] and OpenCL [48]. Although such programming models abstract the underlying GPU architecture by providing a unified processor model, managing the amount of on-chip memory used per thread, the total number of threads per multiprocessor, and the pattern of off-chip memory accesses are examples of problems that developers still need to manage in order to maximize GPU utilization [70]. Often the programmer must perform a tedious cycle of performance tuning to extract the desired performance.

Another problem of developing applications in CUDA is the lack of efficient portability between different generations of GPUs and also between the host processors and GPUs in the system. Different NVIDIA GPUs vary in several key micro-architectural parameters such as number of registers, maximum number of active threads, and the size of global memory. These parameters will vary even more when newer high performance cards, such as NVIDIA's Fermi [66], and future resource-constrained mobile GPUs with less resources are released. These differences in hardware lead to a different set of optimization choices

for each GPU. As a result, optimization decisions for one generation of GPUs are likely to be poor choices for another generation.

One solution to the complexity of GPU programming is to adopt a higher level programming abstraction such as the stream programming model. The higher level domain information exposed as a result of employing the streaming programing model can guide the compiler optimizations in generating high-quality code for GPUs. Therefore, using stream programming model, programmers can implement their application without worrying about the parameters of the underlying hardware and the compiler can perform intelligent optimizations to tune the available parallelism in a streaming application to a specific GPU.

In this thesis, we introduce *Sponge* [38], a compiler for the StreamIt language that is capable of producing customized CUDA code for a wide range of GPUs. Sponge consists of stream graph optimizations to optimize the organization of the computation graph and an efficient CUDA code generator to express the parallelism for the target GPU. Producing efficient CUDA code is a multi-variable optimization problem and can be difficult for software programmers due to the unconventional organization and the interaction of computing resources of GPUs. Sponge is equipped with a set of optimizations to handle the memory hierarchy of GPUs and also to efficiently utilize the processing units.

## 1.4 Flexible Compilation for Streaming

As the number of applications that can effectively use multiple cores increases, it will become necessary to develop strategies that can adequately manage the allocation of resources between applications. Resource allocation is a challenging problem because application behavior (and hence resource requirements) can often vary in unpredictable ways, depending on factors that include dynamic workloads and variability in end-user scenarios. The issue is made more challenging by the numerous heterogeneous architectural resources that are already exposed to software (e.g., the compiler). We believe that managing the allocation of resources effectively requires many non-trivial tradeoffs, and we introduce Flextream [35] as a means to address this issue.

Flextream provides a compilation and runtime adaptation system for distributed memory heterogeneous systems. It is aimed at addressing the challenges described above in the context of streaming applications. The main innovation in Flextream is an *adaptive stream graph modulo scheduling* algorithm that combines the benefits of static scheduling with the advantages of dynamic adaptation. The strategy of using an adaptive hybrid (static-dynamic) compilation approach can lead to significantly better resource utilization, and can help deliver the promise of many-cores to end-users.

The rest of this thesis is organized as follows. The streaming model used throughout this thesis is explained in Chapter II. Then, Optimus, our synthesizing compiler is introduced in Chapter III. In Chapter IV, we demonstrate how streaming applications can be mapped to SIMD engines using MacroSS compiler. Then, Chapter V explains our compilation system, Sponge, for mapping streaming applications to GPUs. In Chapter VI, details of static compilation and online adaptation in Flextream for adjusting the schedule of stream programs in the presence of runtime resource changes is discussed. Finally, we conclude in Chapter VII and talk about future steps to extend the applicability of this work for future heterogeneous systems.

#### **CHAPTER II**

## **Input Language**

We use the StreamIt [79] language as the input language to the compiler. The emphasis on stream programs is self-evident as recent years have witnessed the proliferation of streaming applications in many areas including digital signal processing, graphics, multimedia, network processing, and encryption. There are several new streaming languages and the area currently commands considerable attention from academia and industry. The stream programming paradigm offers a promising approach for programming multicore architectures. Examples of relatively new streaming languages include StreamIt, Brook [13], CUDA [61], SPUR [89], Cg [55], Baker [16], and Spidle [19].

StreamIt is an architecture-independent programming language for high-performance streaming applications [79]. Programs in StreamIt are represented as graphs where nodes, called *filters* or *actors* encapsulate computation, and edges represent FIFO communication. StreamIt is based on the synchronous dataflow (SDF) [52] model of computation. Each filter consists of a *work* function that repeatedly executes when sufficient data is available on its input FIFO (queue). The work function reads data from its input queue using *pop* operations, and writes data to its output queue using *push* operations. The work function

**Figure 2.1:** A sample StreamIt program is shown on the left. The corresponding stream graph with all the filters instantiated is shown on the right.

can also inspect input without removing them from the FIFO using a *peek* operation. Peek operations are critical for exposing data parallelism in sliding-window filters (e.g., FIR filters), as they elide the need for internal filter state. StreamIt provides three hierarchical stream primitives for composing filters into larger stream graphs: *pipeline*, *splitjoin*, and *feedback loop*. A pipeline connects streams sequentially. A splitjoin specifies task or data parallel streams that diverge from a common splitter and merge into a common joiner. A feedback loop creates a cycle in the dataflow graph.

A simple StreamIt program and its corresponding stream graph are illustrated in Figure 2.1. This example consists of five streams: Minimal, Source, AddSplitter, Adder, and Printer. Minimal is a top level pipeline with three-stages. The middle stage, AddSplitter, consists of a splitter, 4 parallel Adder filters, and a joiner. The splitter distributes data to each of its connected filters in a roundrobin fashion. Each Adder

**Figure 2.2:** This figure shows an example stream graph and also the intermediate code template for executing steady state schedule.  $R_i$  is the repetition number for actor i.

receives eight data elements at a time. StreamIt allows stream graphs to be described programmatically, and affords the compiler the ability to fully elaborate the graph at compile time by instantiating and connecting instances of the filters.

Filters in StreamIt are self-contained, and can only access their locally declared variables and fields. Hence, data exchange between filters is accomplished using explicit transfers across inter-filter FIFOs (queues) using the push and pop operations. StreamIt filters may be either stateful or stateless. In Figure 2.1, the Source filter is stateful; all the other filters are stateless. Source is stateful because the i field carries a dependence from one execution of the work function to the next. In addition to the work function, filters may also define an *init* function to initialize local fields.

A crucial consideration in StreamIt programs is to create a steady state schedule which involves rate-matching of the stream graph. Rate-matching guarantees that, in the steady state, the number of data elements that is produced by an actor is equal to the number of data elements its successors will consume. Rate-matching assigns a static repetition number to each actor. In the implementation of a StreamIt schedule, an actor is enclosed

by a *for-loop* that iterates as many times as its repetition number. The steady state schedule is a sequence of appearances of these *for-loops* enclosed in an outer-loop whose main job is to repeat the steady schedule. The template code in Figure 2.2b shows the intermediate code for the steady state schedule of the streaming graph shown in Figure 2.2a.

#### **CHAPTER III**

## **Mapping Streams to FPGAs**

#### 3.1 Introduction

In the world of embedded systems, there are many devices that offer increasingly powerful computing capabilities. It is predicted that mobile computing devices with embedded processors will ultimately change the industry much as laptops supplanted desktops as the primary commodity processing platform. However, the power and frequency concerns that plague the microprocessor industry effectively mean architects have to find new ways to provide increasing performance since conventional frequency scaling methodologies no longer apply. As a result, there is a significant opportunity to explore alternate architectures that can enable the next evolutionary step in computing.

One significantly promising approach is to provide automatic customization of hard-ware according to the applications they run. An application-customized architecture can offer extremely high performance with very low power compared to a more general-purpose design. Furthermore, the increasing availability of reconfigurable field-programmable gate arrays (FPGAs) as co-processors and processing ingredients in heterogeneous systems-on-

a-chip [1, 2] means emerging architectures can offer enormous flexibility and adaptability in the face of rapidly changing software standards and customer needs.

This part of the thesis describes a methodology and a set of complementary optimizations to efficiently realize stream graphs directly in hardware. Our ultimate goal is to automatically refine a high level stream program into either software or hardware. In the case of the former, a program can run on a conventional processor or a multicore architecture. In the case of the latter, the application is realized as an efficient customized circuit design mapped onto FPGAs.

As previously discussed in Chapter II, We adopt a stream programming model where applications can be naturally described as dataflow graphs where nodes embody computation and edges imply communication. Such a streaming model is attractive from a multicore perspective because it makes the abundant parallelism inherent to streaming applications quite explicit. As a result, compilers can more readily derive concurrent implementations from high level applications, with relatively less effort compared to automatic parallelization starting from imperative sequential languages such as C [77, 25, 49]. In the same way, mapping a high-level stream program to hardware (e.g., FPGAs) becomes more practical and productive—compared to using a hardware description language such as Verilog or VHDL, or HDL derivatives of C such as SystemC or Handel-C—if a compiler can readily generate efficient hardware implementations from the programs described in a streaming language.

The idea of mapping high level programs directly into hardware is not a new one. Indeed, there is a lot of work on automatic synthesis of hardware starting from C and its many HDL-oriented derivatives. This work differs from most existing work on the topic of high level synthesis (Section 3.5) by shifting the focus from micro-functional details to macro-functional ones. Specifically, our work does not focus so much on how individual modules are synthesized (i.e., micro-functional), but rather on how modules are composed to assemble an overall design (i.e., macro-functional). As a result, we can synthesize entire applications into a hardware substrate, and not just individual loops and kernels as is the case with a lot of existing work. Thus, our work is complementary to existing work on high level synthesis while offering new opportunities for efficient assembly of streaming applications in hardware.

This chapter describes Optimus, our optimizing synthesis framework for streaming applications. Optimus uses a canonical intermediate representation to describe streaming programs. A program is comprised of interconnected *filters*, derived from the dataflow graph representation of the program. Each filter is comprised of blocks that contain statements. The blocks are themselves interconnected based on control and dataflow dependences. Our set of optimizations that deal with inter-filter details address macro-functional concerns. Similarly, our micro-functional optimizations address synthesis issues that arise from dataflow dependences between blocks. The Optimus model allows us to leverage decades of classic compiler research studied by others in their work to generate highquality circuits, while also offering the ability to apply macro-functional optimizations that are specifically targeted for streaming applications. Macro-functional optimizations, which address how filters (modules) are assembled to implement an application tend to be tedious and time-consuming to perform manually, and require expertise in hardware design. An important example of a macro-functional optimization is deciding on how much buffering to allow between a pair of communicating modules: if too little buffering is provided, then throughput decreases as modules stall to send or receive data; whereas too much buffering incurs substantial space overheads. Macro-functional optimizations require careful consideration of area and performance tradeoffs to judiciously maximize application throughput at the lowest costs.

Our results (Section 3.4) using eight streaming benchmarks, including FFT, DCT, DES, sorting, and matrix multiplication, show that we can achieve significant performance advantages compared to an embedded processor for a fraction of the energy. It is not surprising that a custom hardware design is better than a general-purpose processor. We also found that Optimus-generated designs are performance-competitive and incur small area overhead in comparison to some of the benchmarks that we also implemented in Handel-C.

The primary emphasis of Optimus is on the salient macro- and micro-functional optimizations for streaming programs. We use the StreamIt programming language as our input language although other languages that embody the same streaming model are equally applicable. Optimus compiles StreamIt programs to Verilog. We then use standard synthesis tools to generate FPGA designs. Optimus uses its own hardware models to characterize space-time tradeoffs, and performs many optimizations including critical path balancing and memory allocation. It is built on top of the Trimaran compiler [81], and hence it inherits a rich suite of ILP optimizations (for micro-functional efficiency). The compiler also admits profile-guided optimizations to simplify circuit models for streaming applications. Profiling data provides a cheap and practical alternative to otherwise difficult and intractable optimization problems. The core optimizations are described in Section 3.3, and Section 3.2 describes our overall stream-oriented synthesis framework with both macro- and micro-functional emphasis.

**Figure 3.1:** (a) The specialized template used for synthesizing filters. (b) The complete hardware for the stream graph shown in Figure 2.1.

#### 3.2 From StreamIt to Hardware

Optimus is a compiler and synthesizer that takes as input a streaming application and generates an efficient FPGA (hardware) implementation. We designed a hardware template capable of representing fairly optimized circuits for streaming applications. The template captures the salient properties of streaming codes, and is malleable enough that it can be used in many different circuit designs we generate. This section details our approach using a simple example illustrated in Figure 2.1.

#### 3.2.1 Synthesizing a Stream Graph

Optimus uses a specialized filter template to synthesize the filters that appear in the input stream graph. The template is shown in Figure 3.1a. The template consists of five main components: input queues, output queues, memories, the filter itself, and the controller. Input and output queues are used to send and receive data. The template supports an arbitrary

number of input and output queues to implement splitters and joiners. Memory modules are used to store the state for stateful filters. Each filter can be connected to several memory components. All the memory modules are local to each filter. For each memory module, there are dedicated read and write buses between the module and the corresponding filter. The buses are shared between the accessors of the memory in the filter. The hardware block implementing the filter consists of the work module and an optional init module. Both init and work modules will be connected to a memory module in case that module needs initialization. The controller makes sure that the init function gets executed only once before the first invocation of the work function. Depending on the way that the circuit is scheduled, the controller may have other responsibilities to orchestrate the execution.

After instantiating the template for all filters in a stream graph, the next step is to connect them. This step is straightforward based on the stream graph and the way data flows through the graph. Whenever Optimus connects the template for two filters together, it merges their input and output queues together. In other words, those two filters will share one FIFO queue for transferring data between them. Figure 3.1b shows the top-level hardware for the stream graph in Figure 2.1. As it is illustrated, the only stateful filter with memory components is the Source filter. The Source filter also is the only filter with an init component.

#### 3.2.2 Synthesizing Filters

Each filter is organized as a control flow graph (CFG) with an overlayed data flow graph (DFG). Basic blocks (BBs) of instructions are used as the core building units for each filter. The template for the BBs is shown in Figure 3.2a. Each BB module has four

sets of input/output signals. The first set includes the control signals. All BBs have one control input signal and one or more control output signals. A control input signal will activate a BB as long as the signal is active. A control output signal will be connected to the inputs of the other BBs in order to activate them in the right order. Connecting these control signals is done based on the edges in the corresponding CFG. The second set of input/outputs consists of data signals which carry operand values. Optimus uses a DFG for connecting these signals. The third set of input/output signals helps each module to communicate with external resources such as queues, memories, and other types of IP (intellectual property) cores. These signals provide a unified interface in which any IP core can be connected to the hardware. The last set of signals, marked as *Ack* in Figure 3.2a, is meant for flow control. The Ack signals are useful when a BB cannot perform its operations in the associated clock cycle and needs to wait one or more cycles. This mainly happens when a BB accesses an external resource (e.g., memory) and the resource is not ready to respond within the same cycle.

**Figure 3.2:** (a) The template used for synthesizing basic blocks. (b) Control flow graph and partial data flow graph for the Adder filter. (c) The complete hardware generated for the Adder filter.

Generally, each BB ends with one or more registers to store live-out data and control signals. In the baseline design, it is assumed that all the live-out values are registered to control the wire latency in the final design. Since all the live values are latched at the basic block outputs, one clock cycle is needed to transfer data from one BB to its successors. In other words, the execution of each BB takes at least one cycle.

After the hardware module for each BB is generated, Optimus will connect the modules based on the CFG and DFG for each work or init function. Connecting the control signals is based on the CFG. The control outputs of all BBs are connected to the control inputs of the immediate successor BBs. In case a BB has more than one control input signal, MUXes are used to select the right control input signal. The DFG is used for connecting the data signals, such that the live-out signals of each BB are connected to the live-ins of the immediate successor. MUXes are again used in case a value can reach a BB from two different paths.

We will use the Adder filter as an example to clarify the main points. Figure 3.2b shows the CFG and DFG for Adder. The solid lines show the control flow and the dashed lines show the data flow for *sum*. This graph has four BBs and there is a backedge from BB 3 to BB 2. Based on the DFG, a data signal is needed for transferring the value for the variable *sum* from BB 1 to BB 3 through BB 2. All the control flow signals in the figure are connected based on the CFG for the Adder filter. Since BB 2 is the target of two branches (the fall through from BB 1 and the loop target from BB 3), a MUX is added to its inputs for selecting the appropriate control signal. The execution of the Adder filter will take 18 cycles (2 cycles for each of the 8 iterations, and 2 cycles for the rest of BBs).

The only remaining task is to generate hardware to fill each BB module based on the

**Figure 3.3:** (a) Template for synthesizing operations. (b) Simplified hardware structure for BB 3 in Figure 3.2b.