# ANALOG TO DIGITAL CONVERSION TECHNIQUES FOR NANOMETER CMOS

by

Jorge A. Pernillo

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in the University of Michigan 2013

## **Doctoral Committee:**

Professor Michael P. Flynn, Chair Professor Zhong He Professor Dennis Sylvester Professor David D. Wentzloff  $\frac{\text{© Jorge A. Pernillo}}{2013}$

#### **ACKNOWLEDGEMENTS**

I want to first thank the big guy above for giving me the strength to stay focused and strength to complete what was a challenging and intense but gratifying PhD program. Thanks big guy for listening to me every night and for looking after my family and friends.

I also would like to thank Intel Corporation, Ian Young and William Yee for support of this work.

I'm fortunate and very grateful to have had the opportunity to work with, and to learn from my advisor Professor Michael P. Flynn. It took him a while but he finally made an analog designer out of me...but on a serious note, thank you Professor Flynn for your guidance, your knowledge and your patience. I'd also like to thank the other committee members Professor Sylvester and Professor Wentzloff for their input and help over the years and thanks to Professor He for being on my committee.

I've enjoyed working with each of my group members and have enjoyed the many conversations both technical and random I've had with them at all crazy and odd hours of the day. Thank you Hyugil Chae, Nick Collins, Batuhan Dayanik, Jeffrey Fredenburg, Mahammad Ghahramamani, Jaehun Jeong, Yong Lim, Hyo Gyuem Rhew, Chunyang Zhai, David Lin, Li Li, Aaron Rocca, Shahrzad Naraghi, Andres Tamez, Chun Lee, Dan

Shi, Ivan Bogue, Jongwoo Lee, Joshua Kang, Junyoung Park, Sunghyun Park, Mark Ferriss for sharing your technical expertise and your friendship.

I was also fortunate enough to benefit personally and professionally from the friendships, goodies (cookies, candy etc.), technical expertise and help of students outside the group. I'd like to thank Jae-sun Seo and David Fick from the VLSI group, Jonathan Brown, Sang Wook Han, Muhammad Faisal and Seunghyun Oh from the RF group, Razi Haque, Daniel Egert, Jay Mitchell, Jae Yoong Cho and Jeff Gregory from the MEMS group for sharing your technical expertise, knowledge of the CAD tools, and for allowing me access to equipment and labs over the years. Also, thank you to all my folks (slang for peers/colleagues/friends) in the VLSI, RF and MEMS groups. Whether it was in 1<sup>st</sup> floor EPB, EECS 2001 or EECS 2435, I've had a blast being office mates and friends with all of you. I'd like to thank Brendan Casey for his wire-bonding expertise and Kinly Ming-Hao Wang for his help with prototype testing. I'd also like to thank Joel VanLaven, for the countless hours of CAD support he has given me over all these years and the side conversations on anything from what's hot in computer equipment to chit chats on science fiction. Furthermore, thank you Don Winsor and Liz Zaenger in DCO for excellent computing support whether it was during the week or on weekends, disk failures or backups, they were on point.

I'd like thank my Ann Arbor friends for keeping me sane, for getting me out of the office/lab from time to time, and for putting a smile on my face for all these years. Although one doesn't get to see their friends as often as one would like, it's nice to know that shoulder to cry on is there for you if you need it. Thank you Wonbin Hong, Mathew Malcolm, Joselyn Torres, Jae-Sun Seo, Nate Falkiewicz, Jay Mitchell, Stephanie

DeBosch, Daniel Egert, Shahrzad Naraghi, Mehrnoosh Vahidpour, Angelique Johnson, Aftin Ross, Astin Ross, Amir Borna, Mohammad Ghahramani, Aaron Rocca, Danial Ehyaie, Devan Donaldson, Stephon Owens, Cristin McCarty, Allan Evans, Scott Wright, Muhammad Faisal, Ryan Rogel, Razi Haque, Michael Logue, Seow Yuen Yee, Nick Collins, Jeffrey Fredenburg and SMES-G for all the adventures.

Lastly I would like to acknowledge my family for making all this possible. I'd like to thank mi Mama, mi tia Ella, mi Corazon (abuelita) and mi tia Thelma for their love, their support and for raising me right and keeping me in check from the get go. When you have four mamas raising you, you have belts and slippers coming at you from four different directions so even the worst kid has got to come out right at the end. I know it wasn't easy and I just want to say that I love you with all my heart. I'd like to thank my old man for being my hero and my role model. Thanks dad for always being there. I'd also like to thank my tio Manuel, my brother Mune, and my cousin's Jeanette and Yvonnecita for their love and support.

Yeah I know it was long but it was sincere. Enjoy...

## **TABLE OF CONTENTS**

| ACKNOW    | LEDGEMENTS                                                | ii    |

|-----------|-----------------------------------------------------------|-------|

| LIST OF T | ABLES                                                     | ix    |

| LIST OF F | FIGURES                                                   | x     |

| LIST OF A | ABBREVIATIONS                                             | xvi   |

| ABSTRAC   | CT                                                        | xviii |

| CHAPTER   | R 1 Introduction                                          | 1     |

| 1.1 E     | Background                                                | 1     |

| 1.2 A     | Analog to Digital Converters for Broadband Communications | 3     |

| 1.3 F     | Flash ADCs                                                | 6     |

| 1.3.1     | Architecture                                              | 7     |

| 1.3.2     | Random Offset                                             | 8     |

| 1.3.3     | Bandwidth-Accuracy-Power Tradeoff                         | 11    |

| 1.3.4     | Area                                                      | 14    |

| 1.3.5     | Resistive Offset Averaging                                | 15    |

| 1.3.6     | Comparator Redundancy and Reassignment                    | 18    |

| 1.4 F     | Recent work on flash-based ADCs                           | 25    |

| 1  | .5    | Recent work on Time-Interleaved ADCs                                | 25 |

|----|-------|---------------------------------------------------------------------|----|

| 1  | .6    | Thesis Outline                                                      | 27 |

| СН | APTE  | ER 2 Deliberate and Random Offset for Setting Comparator Thresholds | 28 |

| 2  | 2.1   | Introduction                                                        | 28 |

| 2  | 2.2   | Architecture and Implementation                                     | 29 |

|    | 2.2.1 | Comparator Bank                                                     | 30 |

|    | 2.2.2 | 2 Comparator                                                        | 30 |

|    | 2.2.3 | Boot-strapped Track-and-Hold                                        | 33 |

|    | 2.2.4 | Encoder                                                             | 35 |

|    | 2.2.5 | Calibration Algorithm                                               | 36 |

| 2  | 2.3   | Comparator Analysis                                                 | 36 |

| 2  | 2.4   | Measurement Results                                                 | 41 |

| СН | APTE  | ER 3 A High Feedback Factor Approach for GS/s Pipelining            | 45 |

| 3  | 5.1   | Introduction                                                        | 45 |

| 3  | 3.2   | Comparator redundancy in flash-based pipeline ADCs                  | 46 |

|    | 3.2.1 | High feedback factor approach to pipelining                         | 47 |

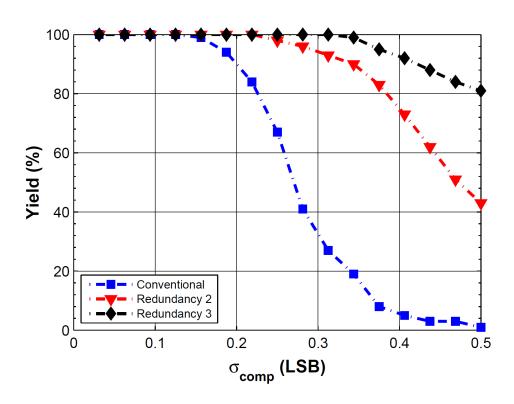

|    | 3.2.2 | 2 Comparator redundancy                                             | 50 |

|    | 3.2.3 | A new combination of pipelining and redundancy                      | 54 |

| 3  | 3.3   | Proposed ADC Architecture                                           | 58 |

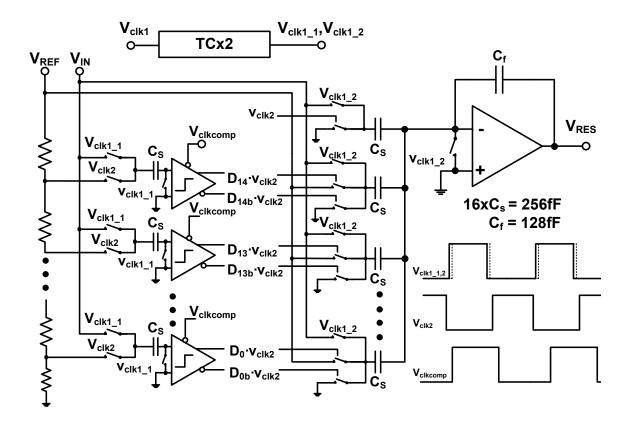

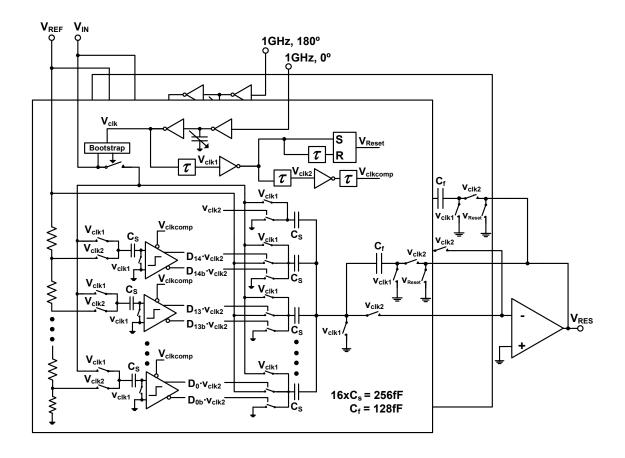

|    | 3.3.1 | 1 <sup>st</sup> stage 4b flash-based MDAC                           | 59 |

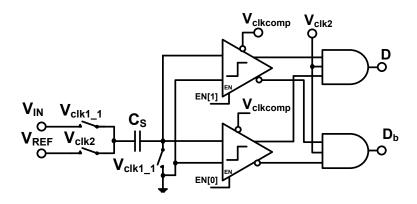

|    | 3.3.2 | 1 <sup>st</sup> stage 4b flash sub-ADC                       | 61 |

|----|-------|--------------------------------------------------------------|----|

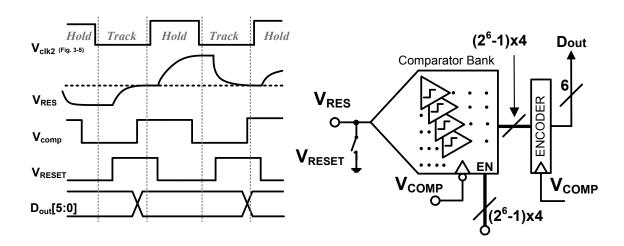

|    | 3.3.3 | 2 <sup>nd</sup> stage 6b redundancy-based flash sub-ADC      | 63 |

|    | 3.3.4 | Elimination of SAH                                           | 66 |

|    | 3.3.5 | Calibration                                                  | 70 |

|    | 3.3.6 | Encoder                                                      | 74 |

| 3  | .4    | Circuit Details                                              | 75 |

|    | 3.4.1 | 1st Stage Op-Amp                                             | 75 |

|    | 3.4.2 | Sub-ADC Comparators                                          | 76 |

| 3  | .5    | Measurement Results                                          | 80 |

| СН | APTE  | R 4 A Technique for sub-ADC Sharing in Time-Interleaved ADCs | 86 |

| 4  | .1    | Introduction                                                 | 86 |

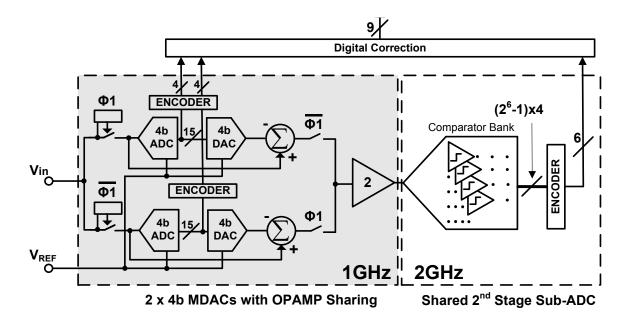

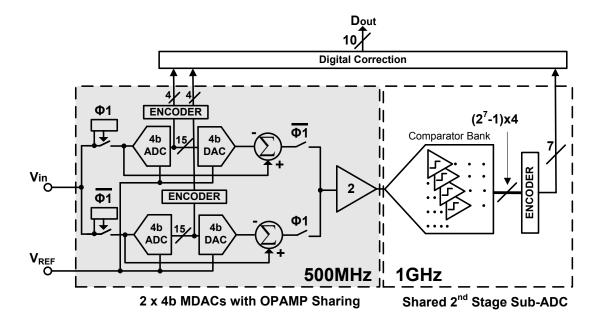

| 4  | .2    | Proposed ADC Architecture                                    | 87 |

|    | 4.2.1 | 2X-Interleaved 1 <sup>st</sup> stage 4b MDACs                | 88 |

|    | 4.2.2 | Shared 2 <sup>nd</sup> Stage sub-ADC                         | 91 |

| 4  | .3    | Measurement Results                                          | 92 |

| СН | APTE  | R 5 Conclusion                                               | 96 |

| 5  | .1    | Summary                                                      | 96 |

| 5  | .2    | Contributions                                                | 96 |

| 5  | .3    | Comparison with State of the Art                             | 98 |

| 5  | 4     | Future Research Directions 1                                 | 02 |

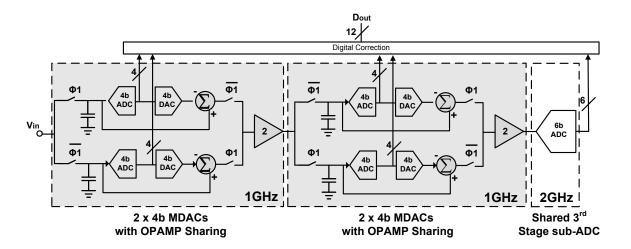

| 5.4.1       | A 10b 1GS/s 2X-Interleaved Pipeline ADC | 102 |

|-------------|-----------------------------------------|-----|

| 5.4.2       | A 12b 2GS/s 2X-Interleaved Pipeline ADC | 104 |

| Bibliograph | у                                       | 106 |

# LIST OF TABLES

| TABLE I Comparator input capacitance $C_{in}$ as a function of matching requirements for | 5- |

|------------------------------------------------------------------------------------------|----|

| 9b flash ADCs with 1V input range in recent CMOS technologies.                           | 13 |

| TABLE II Reassignment for comparators of Figure 1-17a                                    | 19 |

| Table III Reassignment for comparators of Figure 1-17b.                                  | 20 |

| Table IV ADC ADC PERFORMANCE SUMMARY                                                     | 42 |

| TABLE V INPUT PAIR WIDTHS AND TOTAL INPUT CAPACITANCE OF A                               | 6b |

| FLASH ADC WITH 5.5 ENOB FOR DIFFERENT INPUT RANGES                                       | 52 |

| TABLE VI ADC PERFORMANCE SUMMARY                                                         | 81 |

| Table VII ADC PERFORMANCE SUMMARY                                                        | 93 |

| Table VIII Comparable GS/s+ ADCs with ≥ 7b resolution                                    | 99 |

# LIST OF FIGURES

| Figure 1-1 Production efficiency and scaling in the semiconductor industry [1]                    |

|---------------------------------------------------------------------------------------------------|

| Figure 1-2 System on Chip (SoC) technology combines multiple chips into one chip 2                |

| Figure 1-3 Relative Cost decreases with time and technology introductions (T) [2] 3               |

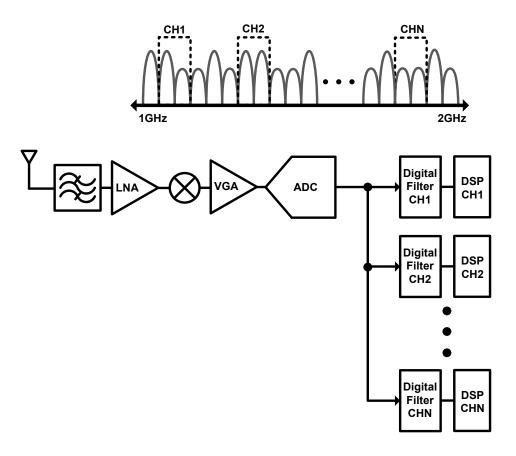

| Figure 1-4 Example of a multi-channel receiver for cellular base stations. In this                |

| implementation, an analog front end, a narrowband ADC and DSP is required for each                |

| channel4                                                                                          |

| Figure 1-5 Example of a multi-channel receiver for cellular base stations. In this                |

| implementation, a single analog front end and wideband ADC is utilized and channel                |

| selection is done in the digital domain                                                           |

| Figure 1-6 N-bit flash ADC architecture.                                                          |

| Figure 1-7 Source-coupled pair. 9                                                                 |

| Figure 1-8 Simulation data for minimum length NFET in recent CMOS technologies 10                 |

| Figure 1-9 Simulation data on the effects of V <sub>T</sub> mismatch in recent CMOS technologies. |

| Data corresponds to minimum length NMOS source-coupled pairs biased at                            |

| $V_{dsat}$ =150mV. 11                                                                             |

| Figure 1-10 Simulation data on yield vs. comparator offset for 5-9b flash ADCs with 1V            |

| input signal range.                                                                               |

| Figure 1-11 Speed-Power-Accuracy tradeoff for flash ADCs in 90nm CMOS with                        |

| $V_{dsat}=150$ mV                                                                                 |

| Figure 1-12 Resistive offset averaging.                                          | 15       |

|----------------------------------------------------------------------------------|----------|

| Figure 1-13 Resistive Interpolation.                                             | 16       |

| Figure 1-14 Over-ranging.                                                        | 16       |

| Figure 1-15 Termination.                                                         | 17       |

| Figure 1-16 Triple-Cross connection                                              | 18       |

| Figure 1-17 Comparator Redundancy and Reassignment. (a) 3b ADC ideal and         | l actual |

| with reassignment. (b) 3b ADC ideal with redundancy and actual with reassignment | nt 22    |

| Figure 1-18 Trip-points for 3b flash ADC with offsets. (a) No reassignment. (b   | ) With   |

| reassignment. (c) With reassignment and redundancy.                              | 23       |

| Figure 1-19 Code search algorithm.                                               | 23       |

| Figure 1-20 Example of an ADC comparator search where three comparators trip     | on the   |

| sixth search. Noise averaging will result in the selection of comparator "a"     | 24       |

| Figure 1-21 (a) Conventional encoding scheme for flash ADCs where bubbles        | in the   |

| thermometer code lead to errors in the ADC output. (b) Encoding scheme ba        | ised on  |

| Wallace tree architecture                                                        | 24       |

| Figure 2-1 N-bit ADC architecture with redundancy of R comparators per code      | 29       |

| Figure 2-2 Comparator circuit with programmable offset.                          | 32       |

| Figure 2-3 Waveforms illustrating regions of operation of the comparator         | 32       |

| Figure 2-4 Differential boot-strapped TAH.                                       | 34       |

| Figure 2-5 Differential boot-strapped TAH waveforms and linearity for ~1GH       | z input  |

| signal sampled at 2GHz.                                                          | 34       |

| Figure 2-6 Encoder block diagram.                                                | 35       |

| Figure 2-7 Spectre simulated comparator (a) offset, (b) noise and (a & b) power (@                 |

|----------------------------------------------------------------------------------------------------|

| 2GHz, 1V VDD) vs. comparator FET widths for the comparator in Figure 2-2 38                        |

| Figure 2-8 Monte-Carlo simulation of ENOB vs. FET widths for 7-bit ADCs using data                 |

| from Fig. 4 and a redundancy of 5.                                                                 |

| Figure 2-9 Die micrograph of 90nm CMOS ADC. 42                                                     |

| Figure 2-10 Experimental data on comparator cumulative noise distribution and Gaussian             |

| fit                                                                                                |

| Figure 2-11 Measured DNL and INL. 43                                                               |

| Figure 2-12 4096 point FFT for 750.36 MHz input and 16X decimation                                 |

| Figure 2-13 SNDR & SFDR vs. Fin (Fs = 1.5GS/s)                                                     |

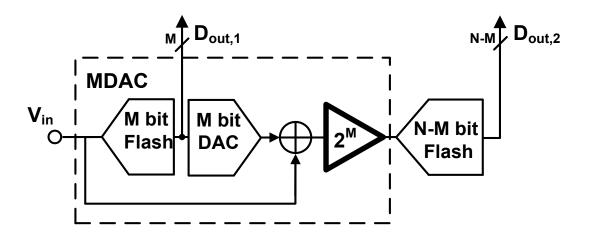

| Figure 3-1 Conventional N bit two-stage flash-based pipeline ADC                                   |

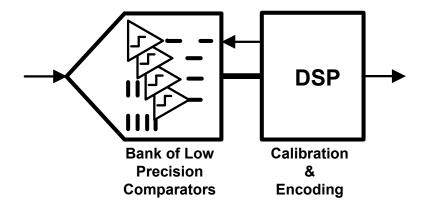

| Figure 3-2 Conceptual block diagram of comparator redundancy                                       |

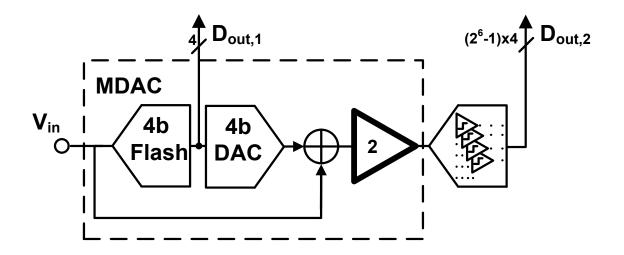

| Figure 3-3 A 9b two-stage pipeline ADC with reduced MDAC gain and redundancy-                      |

| based flash sub-ADC. 55                                                                            |

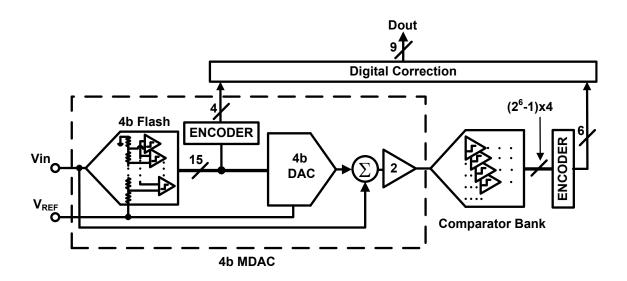

| Figure 3-4 Simplified single-ended representation of proposed ADC architecture 58                  |

| Figure 3-5 Simplified single-ended representation of differential 4-bit MDAC                       |

| Figure 3-6 Simplified single-ended representation of 1 <sup>st</sup> stage sub-ADC comparator with |

| a redundancy of two comparators per code                                                           |

| Figure 3-7 Monte-Carlo simulation of Yield of a 4bit MDAC vs. Comparator Offset 62                 |

| Figure 3-8 Simplified single-ended representation of 2 <sup>nd</sup> stage 6b sub-ADC architecture |

| with redundancy of four comparators per code                                                       |

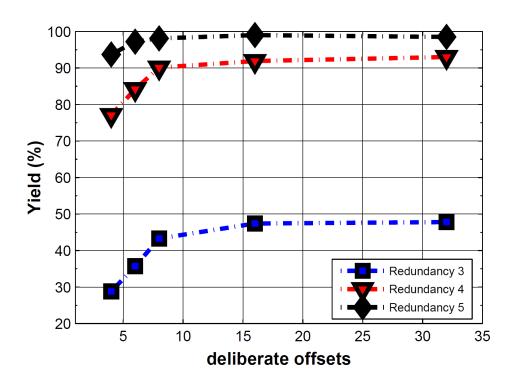

| Figure 3-9 Monte-Carlo simulation of Yield of a 6bit redundancy-based flash ADC vs.                |

| number of deliberate offsets for setting comparator trip-points                                    |

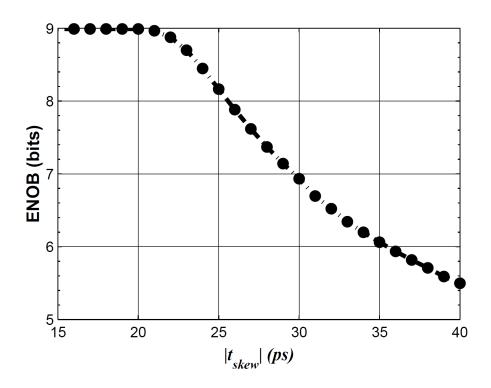

| Figure 3-10 ADC ENOB versus clock skew for an otherwise ideal 9bit two-stage SAH-                |

|--------------------------------------------------------------------------------------------------|

| less pipeline ADC with a 4bit 1st stage and 6bit 2nd stage with 1bit over-range. The data is     |

| with respect to a 502MHz input signal sampled at 1GHz. 68                                        |

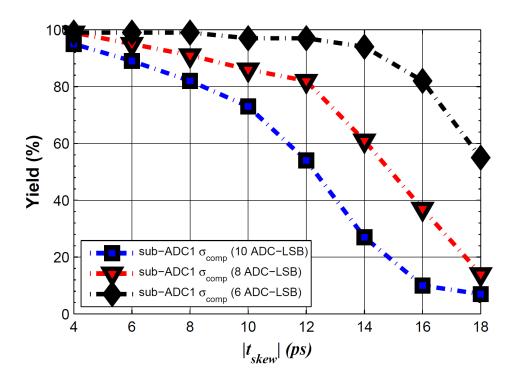

| Figure 3-11 Monte Carlo simulation of Yield versus clock skew for the same ADC                   |

| architecture as in Figure 3-10 but incorporating comparator redundancy in the sub-ADCs.          |

| The 1st stage 4bit sub-ADC and the 2nd stage 6bit sub-ADC incorporates a redundancy of           |

| two and four respectively. Yield is defined as the percentage of 100 randomly generated          |

| ADCs whose ENOB is greater than 8.5.                                                             |

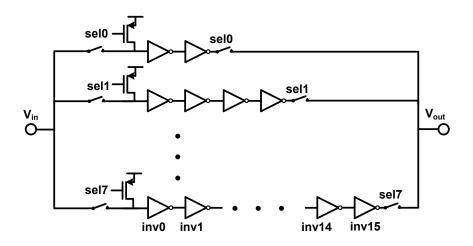

| Figure 3-12 Tunable Delay Circuit used for 1 <sup>st</sup> stage Clock Skew Correction           |

| Figure 3-13 Calibration scheme for 2 <sup>nd</sup> stage redundancy-based flash sub-ADC to       |

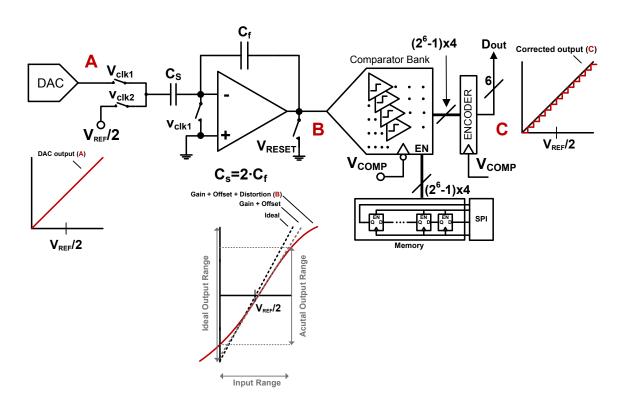

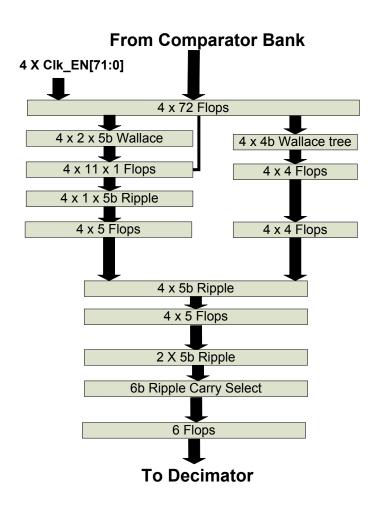

| account for op-amp non-linearity, finite gain and offset                                         |

| Figure 3-14 (a) Transfer function of an ideal and non-ideal 4b MDAC with nominal gain            |

| of 2. (b), (c) Spectral analysis of a Matlab-simulated 9bit two-stage pipeline ADC with          |

| (b) and without (c) the non-Ideal MDAC in the calibration path of the $2^{nd}$ stage 6bit        |

| redundancy based flash sub-ADC                                                                   |

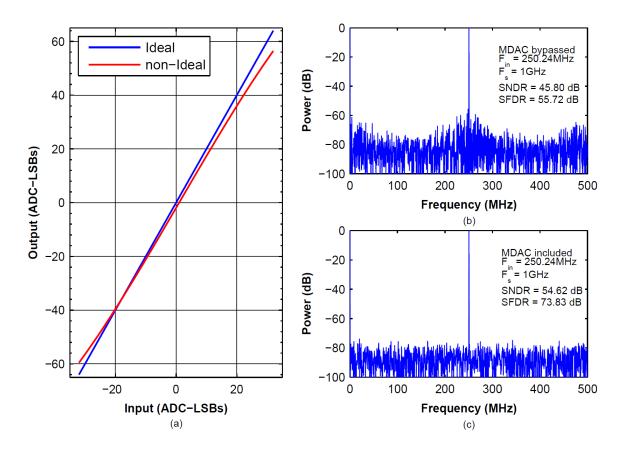

| Figure 3-15 2 <sup>nd</sup> stage sub-ADC Encoder block diagram. 74                              |

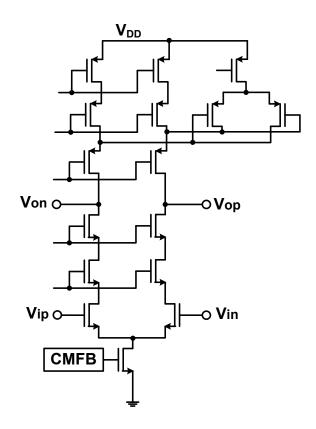

| Figure 3-16 1 <sup>st</sup> stage MDAC op-amp with gain enhancement                              |

| Figure 3-17 $2^{\text{nd}}$ stage sub-ADC comparator with MOS-capacitor for deliberate offset 77 |

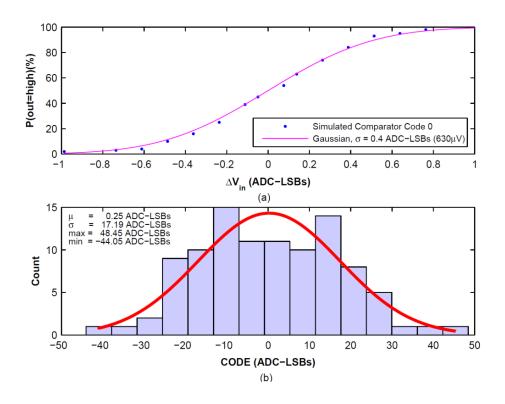

| Figure 3-18 Simulation data on 2 <sup>nd</sup> stage sub-ADC comparator (a) cumulative noise     |

| distribution and Gaussian fit and (b) random offset                                              |

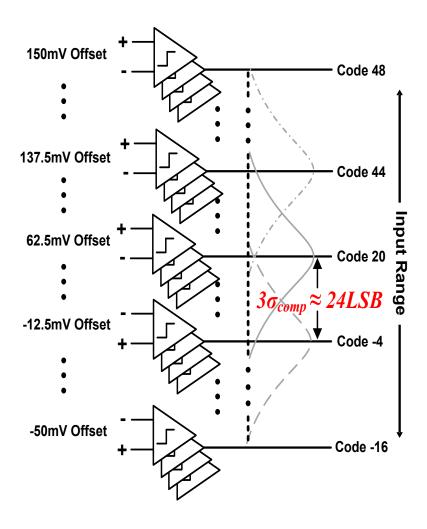

| Figure 3-19 Deliberate and Random offset scheme for setting 2 <sup>nd</sup> stage sub-ADC input  |

| range                                                                                            |

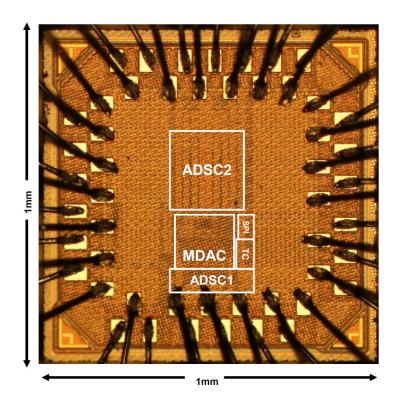

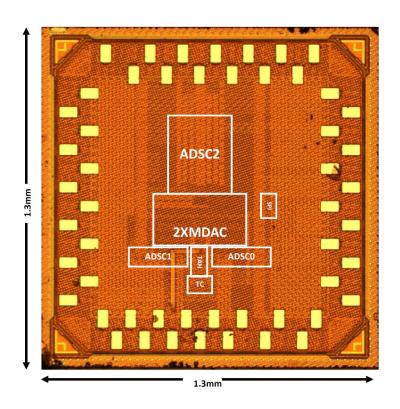

| Figure 3-20 45nm CMOS-SOI prototype ADC die microphotograph                                      |

| Figure 3-21 Measurement data of 2nd stage sub-ADC comparator random offset 82               |

|---------------------------------------------------------------------------------------------|

| Figure 3-22 Measured 2nd stage sub-ADC DNL and INL 83                                       |

| Figure 3-23 Measured ADC DNL and INL 83                                                     |

| Figure 3-24 Output spectrums for a 500.49MHz input and 16X decimation without and           |

| with (b) clock skew correction                                                              |

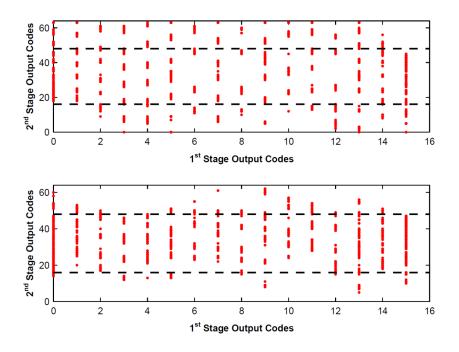

| Figure 3-25 Measured data of 1st and 2nd stage sub-ADC output codes during conversion       |

| of a 750MHz input signal sampled at 1GHz without (top) and with (bottom) 1st stage          |

| clock skew correction. The dashed lines indicate the 2 <sup>nd</sup> stage correction range |

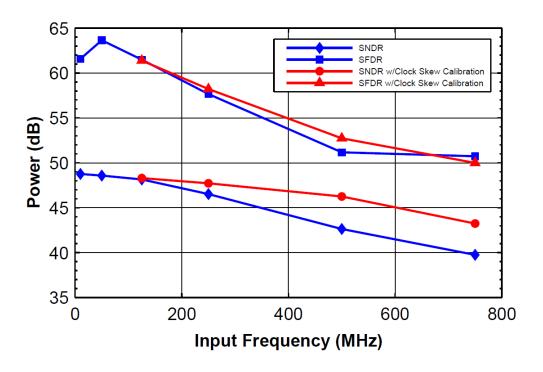

| Figure 3-26 Measured SNDR & SFDR vs. Fin (Fs = 1.0GS/s) with and without clock              |

| skew correction. 85                                                                         |

| Figure 4-1 Simplified single-ended representation of proposed ADC architecture 87           |

| Figure 4-2. Simplified single-ended representation of two time interleaved 4-bit MDACs      |

| with op-amp sharing.                                                                        |

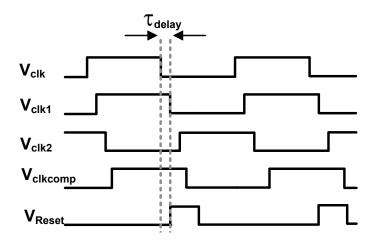

| Figure 4-3 Timing waveforms for one of two time-interleaved 1st stage 4-bit MDACs in        |

| Figure 4-2                                                                                  |

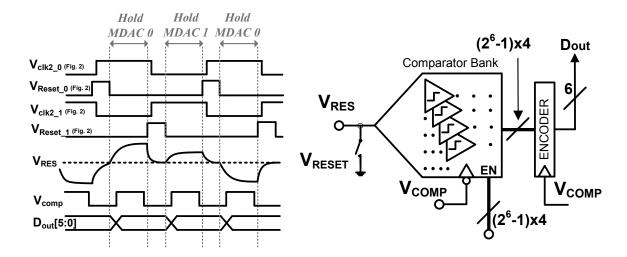

| Figure 4-4 Simplified single-ended representation and timing waveforms for the shared       |

| 2 <sup>nd</sup> stage 6b sub-ADC with redundancy of four comparators per code               |

| Figure 4-5 45nm CMOS-SOI prototype ADC die microphotograph                                  |

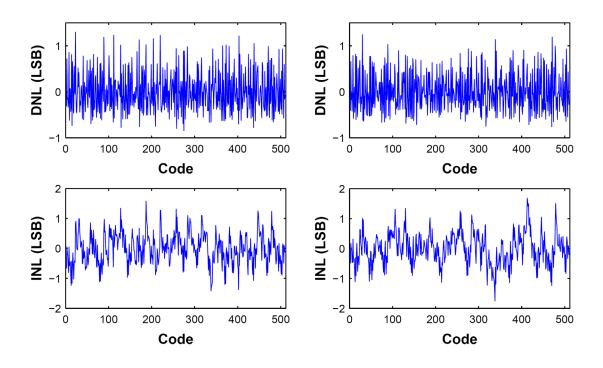

| Figure 4-6 DNL (top) and INL (bottom) of channel 1 (right) and channel 2 (left) 94          |

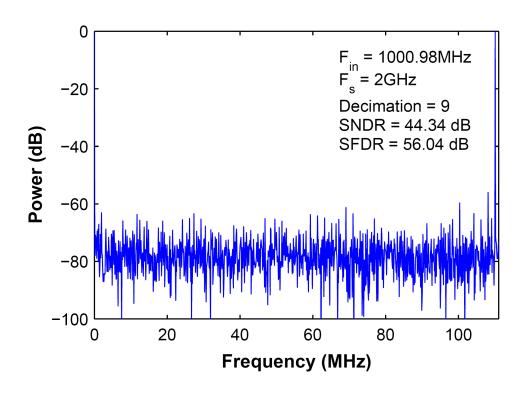

| Figure 4-7 Output spectrums for a 1000.98MHz input and 9X decimation                        |

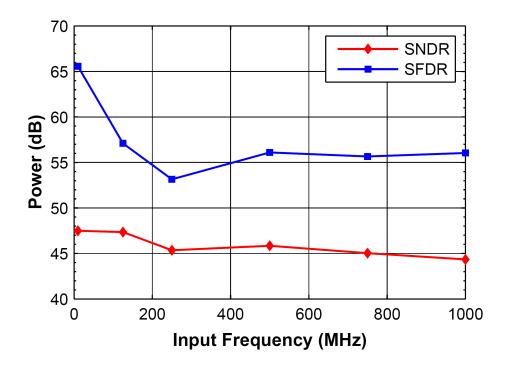

| Figure 4-8 Measured SNDR & SFDR vs. Fin (Fs = 2.0GS/s). 95                                  |

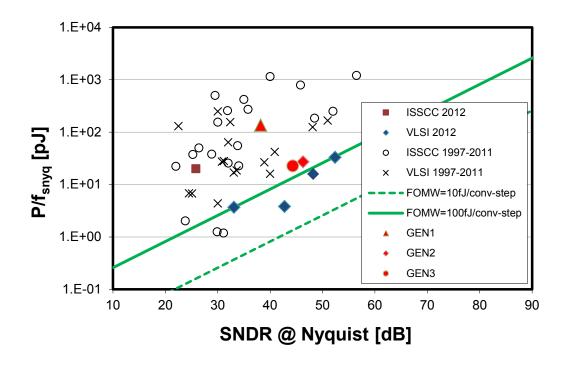

| Figure 5-1 Energy vs. SNDR for comparing this work (i.e. GEN1-3) with other state of        |

| the art GS/s+ ADCs.                                                                         |

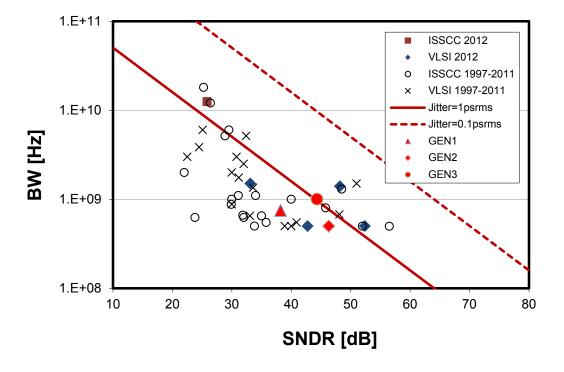

| Figure 5-2 Bandwidth vs. SNDR for comparing this work (i.e. GEN1- | 3) with other state |

|-------------------------------------------------------------------|---------------------|

| of the art GS/s+ ADCs.                                            | 101                 |

| Figure 5-3 Proposed 10b 1GS/s ADC architecture.                   | 102                 |

| Figure 5-4 Proposed 12b 2GS/s ADC Architecture                    | 104                 |

#### LIST OF ABBREVIATIONS

ADC analog-to-digital-converter

BER bit error rate

CLSA current latch sense amplifier

CMFB common mode feedback

CMOS complementary metal-oxide-semiconductor

DAC digital-to-analog-converter

DNL differential non-linearity

DSP digital signal processor

ENOB effective number of bits

FET field effect transistor

GS/s giga-samples per second

IC integrated circuit

INL integral non-linearity

LDO low drop-out regulator

LSB least significant bit

LTE-A Long Term Evolution Advanced

MDAC multiplying digital-to-analog-converter

MS/s mega-samples per second

RMS root mean square

SAH sample and hold

SAR successive approximation register

SFDR spurious free dynamic range

SNDR signal-to-noise and distortion ratio

SNR signal-to-noise ratio

SoC System on Chip

SOI silicon on insulator

TAH track and hold

**ABSTRACT**

ANALOG-TO-DIGITAL CONVERSION TECHNIQUES

FOR NANOMETER CMOS

by

Jorge Pernillo

Chair: Michael P. Flynn

This work investigates new approaches to analog-to-digital conversion that are suited

for end-of-the-roadmap CMOS, and which also deliver orders-of-magnitude

improvements in speed and energy efficiency. We break analog-to-digital conversion

down to its essence and simplify the process of analog-to-digital conversion to its most

basic form. This allows us to take advantage of the tremendous digital capability of

nanometer processes and then implement the analog circuitry in the simplest way. We

propose three ADC structures that enable high performance with low transistor gain and,

low-precision comparators aided by digital processing.

First, a 1.5GS/s 7b flash ADC is presented. We advance a comparator redundancy

technique by employing random and deliberate mismatch to set the comparator

thresholds and eliminate the need for a low-impedance high-precision resistor reference

ladder. Unusually, the proposed technique exploits large random variation in comparator

offset. This enables the use of low precision dynamic comparators that can be optimized

xviii

for speed. The ADC prototype, fabricated in 90nm digital CMOS process, achieves an ENOB and SFDR of 6.05 bits and 46.6dB at Nyquist and consumes a total of 204mW from 1.2V analog and 0.9V digital supplies.

Second, a 9b 1GS/s two-stage pipeline ADC is presented. This architecture achieves high performance with a low-gain op-amp and low accuracy comparators. A reduced MDAC gain relaxes the op-amp gain and bandwidth requirements and trades MDAC output swing for reduced op-amp power. This technique is assisted by a comparator redundancy scheme that decouples the 2<sup>nd</sup> stage sub-ADC performance from comparator matching requirements. A simple code-search algorithm calibrates the redundancy-based sub-ADCs and at the same time eliminates the need for complex calibration techniques to correct ADC errors from finite op-amp gain, offset and non-linearity. Digital trimming of a delay chain eliminates mismatch in the sampling paths to provide a simple, low power alternative to a dedicated front-end S/H. The prototype ADC, fabricated in a 45nm SOI-CMOS process, achieves an ENOB and SFDR of 7.4 bits and 52.7 dB at Nyquist and consumes a total of 27mW from a 1V supply.

Finally, a 9b 2GS/s two-times interleaved pipeline ADC is described. This architecture leverages op-amp sharing as well as 2<sup>nd</sup> stage sub-ADC sharing between two time-interleaved MDACs to reduce power and area. Furthermore, this technique eliminates the need for complex calibration algorithms that correct ADC errors due to gain and offset mismatch between channels. Digital trimming corrects for timing mismatch between channels. The prototype ADC, fabricated in a 45nm SOI-CMOS process, achieves an ENOB and SFDR of 7.07 bits and 56 dB at Nyquist and consumes a total of 45mW from a 1V supply.

## **CHAPTER 1 Introduction**

## 1.1 Background

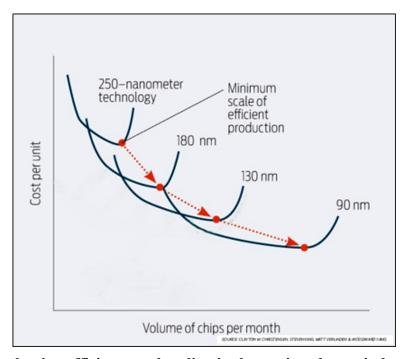

The goal of this research is to develop new approaches to analog-to-digital conversion that are suited for sub-micron, digital complementary metal oxide semiconductor (CMOS) processes. Semiconductor economics dictate that digital CMOS processes follow the trend towards finer line-widths to increase the number of transistors that can be fabricated on a silicon wafer. This results in increased production efficiency at finer line-widths [1] as illustrated in Figure 1-1.

Figure 1-1 Production efficiency and scaling in the semiconductor industry [1].

Decreasing line-widths are accompanied by increased transistor speed, density and power efficiency all which are conducive to system-on-chip (SoC) integration of digital

integrated circuits (ICs). SoC design (see Figure 1-2) is a concept where chips are designed with increasing amounts of functionality to reach a point where one chip represents an entire "system". One chip means lower manufacturing costs, lower power consumption, smaller area and enhanced performance.

Figure 1-2 System on Chip (SoC) technology combines multiple chips into one chip.

However, the trend towards finer line-widths is not conducive to the advancement of analog integrated circuit design where accuracy requirements are more stringent. Finer line-widths lead to increased process variation. When coupled with the reduction in power supply levels, short-channel effects and temperature gradients, this makes robust analog circuit designs difficult to achieve. The drawbacks of technology scaling are more significant for analog circuits and impede the advancement of mixed-signal SoCs. Therefore, analog chips are manufactured using tailored analog manufacturing technologies that are more expensive than standard digital manufacturing technologies.

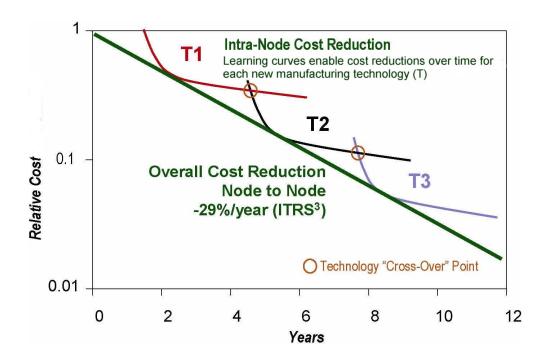

Figure 1-3 Relative Cost decreases with time and technology introductions (T) [2]. NOTE: As a given technology matures, it becomes the most cost effective solution until the next technology introduction passes the "Cross-Over" point.

SoCs can be implemented in older digital manufacturing technologies. However, although this solution allows proven analog design techniques to be employed, it is neither as cost effective (see Figure 1-3) nor does it scale with volume (see Figure 1-1). Reducing the complexity of analog functions by substituting them with digital processing greatly reduces the required accuracy. This concept is explored in this work and applied in the context of high-speed analog-to-digital converters (ADCs).

#### 1.2 Analog to Digital Converters for Broadband Communications

Future high-speed communications systems and emerging communication standards require analog to digital converters with both high bandwidth and high dynamic range. For example, emerging broadband wireless technologies such as LTE-Advanced (LTE-A) [3] and 60GHz [4] will deliver Giga-bit per second data rates as early as 2015 and

require Giga-Sample per second (GS/s) ADCs with resolution of 8 bits and above. Incorporating GS/s ADCs will enable sufficient receiver performance to deliver these data rates.

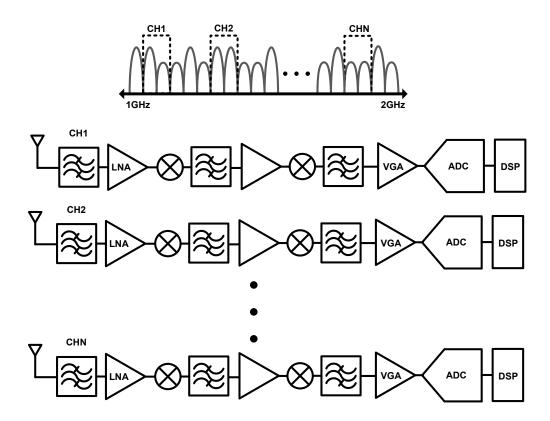

In current macro-cell base stations, a receiver is required for each channel and the RF-band-pass filtering, channel-selection and image rejection are all done in analog domain. Furthermore multiple analog-to-digital converters (ADCs) and digital signal processors (DSPs) are required as shown in Figure 1-4. Furthermore, since a receiver is duplicated once for each channel, this results in an overly redundant design. Also, each added analog stage in receiver increases cost due to yield and therefore the sooner the signal is digitized the better.

Figure 1-4 Example of a multi-channel receiver for cellular base stations. In this implementation, an analog front end, a narrowband ADC and DSP is required for each channel.

With a fast and accurate ADC, it would be possible to digitize the whole spectrum of interest and channel selection can then be done in the digital domain as shown in Figure 1-5. This implementation eliminates the multiple front-ends and lowers cost and complexity. Furthermore, it would be desirable to implement the ADC in nanometer CMOS for SOC integration with digital filter and signal processor. This requires an ADC architecture that scales with advanced CMOS and that is fast enough to digitize the entire spectrum of interest. However, current ADCs are not power efficient at the multi Giga-Sample per second (GS/s) speeds required to digitize the Gigahertz bandwidths and rely on architectures that do not scale well to advanced CMOS processes.

Figure 1-5 Example of a multi-channel receiver for cellular base stations. In this implementation, a single analog front end and wideband ADC is utilized and channel selection is done in the digital domain.

Micro-cell base stations aim to alleviate the cell bandwidth capacity crunch due to increased demand for picture and video intensive networking and social networking [5]. A high speed (i.e. GS/s+), low power ADC would enable multiple channels to be digitized simultaneously so that channel selection can be done in the digital domain. This results in a reduced component count and reduced complexity in receiver design, both of which reduce cost and size of the micro-cell. However, current, commercial GS/s ADCs are not energy efficient and consume considerable die area.

The flash ADC architecture offers the best solution for Giga-sample per second conversion rates. Furthermore, at its core are circuits whose speed improves with CMOS scaling. However, the exponential dependence of power and area on resolution limits efficient GS/s operation to 6 bits and below. This makes it unsuitable for future broadband communications systems where resolutions of 8 bits and above are required. Therefore new techniques or architectures that decouple this speed-power-resolution tradeoff are needed.

#### 1.3 Flash ADCs

The Flash ADCs is one the fastest types of ADC converter and is well suited for high bandwidth applications. However, power and area implications due to the nature of the architecture put a limit on the maximum practical resolution. Typical applications where flash converters are employed include disk-drive read channels, satellite communication, radar/sonar and oscilloscopes. This section discusses the flash ADC architecture, its speed-accuracy-bandwidth tradeoff and techniques that are employed relax this tradeoff.

## 1.3.1 Architecture

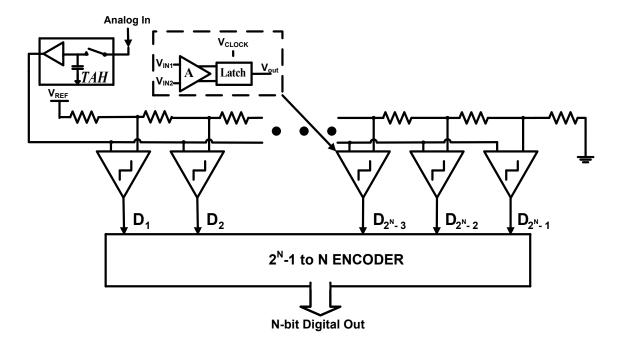

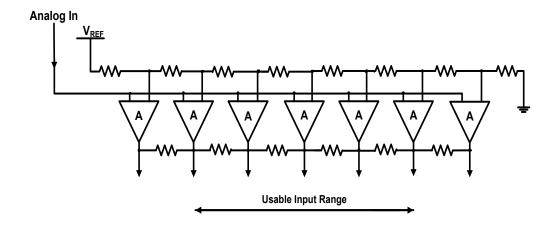

In a traditional N-bit flash converter,  $2^N$ -1 comparators are employed to compare an input signal with  $2^N$ -1 known references and outputs  $2^N$ -1 one-bit digital signals, which are subsequently encoded into an N-bit digital output. It has the unique advantage of doing a full conversion in a single clock cycle. Figure 1-6 shows the general architecture. The comparator element consists of a latch, and a pre-amplifier that attenuates the input referred offset and noise of the latch. A track-and-hold (TAH) circuit tracks the analog input and holds a sampled input on a capacitor while a buffer drives the comparator inputs and the comparators make a decision.

Figure 1-6 N-bit flash ADC architecture.

#### 1.3.2 Random Offset

One of the main disadvantages of the flash ADC architecture is the exponential dependence of the number of comparators with respect to resolution. Additionally, these comparators need to be properly matched and biased in order to convert an analog signal to a digital signal with good linearity.

The current-voltage behavior of MOSFETs shows random variation after fabrication. This random variation is called device mismatch. In the Pelgrom model [6] there are two mismatch terms, one for current factor  $K=\mu \cdot C_{ox} \cdot W/L$  mismatch and a second for threshold voltage  $V_T$  mismatch. Both terms are given below and are modeled as a normal distribution with zero mean and a variance that is dependent on device dimensions and distance between the devices.

$$\sigma^2(\Delta K) = \frac{A_K^2}{WL} + S_K^2 D^2$$

1.1

$$\sigma^2 \left( \Delta V_T \right) = \frac{A_{V_t}^2}{WL} + S_{V_T}^2 D^2$$

1.2

Coefficients  $A_K$ ,  $A_{V\tau}$ ,  $S_K$ , and  $S_{V\tau}$  are process dependent parameters. The current factor mismatch term accounts for the variation in drawn width and length as well as variation in gate oxide  $C_{ox}$  and mobility  $\mu$ . The  $V_T$  mismatch term accounts for variation in the threshold voltage of a device primarily caused by statistical variation of the number of dopants under the gate. The second term in equations 1.1 and 1.2 models the long distance effect. Devices that must match are generally laid out close together so D becomes small and will be neglected.

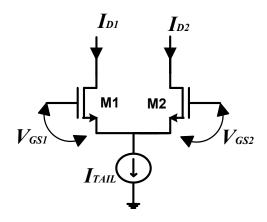

The input referred offset of a comparator is the differential input voltage that causes the currents in each leg of the source-coupled pair in Figure 1-7 to be equal to half the tail current.

Figure 1-7 Source-coupled pair.

This voltage can be approximated using equation 1.3 below which gives the variance of the offset.

$$\sigma^{2}(\Delta V_{GS}) = \sigma^{2}(\Delta V_{T}) + \frac{V_{dsat}^{2}}{4} \frac{\sigma^{2}(\Delta K)}{K^{2}}$$

1.3

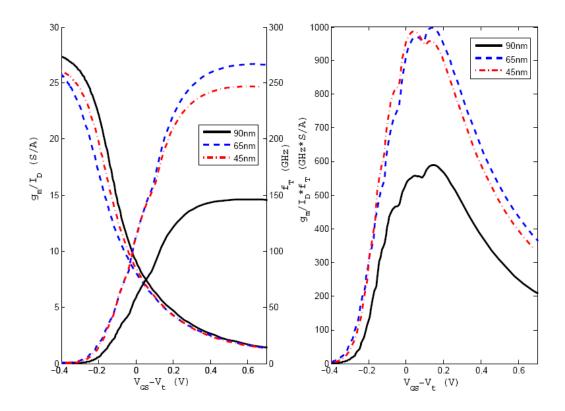

In practice the  $V_T$  mismatch term is dominant in most analog design. This is generally the case for overdrive voltage  $V_{dsat}$  values less than 200mV. In [7], the impact of scaling on analog performance is addressed. Considering the fundamental tradeoff between "transconductor efficiency" (i.e.  $g_m/I_D$ ) and intrinsic bandwidth (i.e.  $f_T$ ) of a transistor reveals an optimum biasing point. Figure 1-8 below illustrates this tradeoff and shows an optimum biasing point between 100mV and 150mV for 90nm, 65nm and 45nm digital CMOS technologies.

Figure 1-8 Simulation data for minimum length NFET in recent CMOS technologies

Therefore, the second term in equation 1.3 is neglected and the input referred offset of a comparator can be approximated by equation 1.4 below:

$$\sigma_{comp} \approx \frac{A_{V_T}}{\sqrt{(WL)}}$$

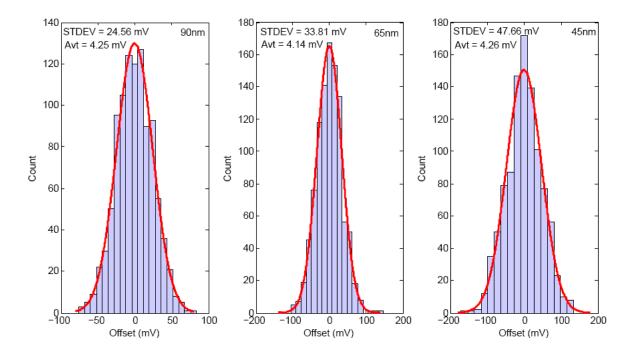

Figure 1-9 illustrates the effects of  $V_T$  mismatch in recent CMOS technologies. The data corresponds to minimum length NMOS source-coupled pairs biased at  $V_{dsat}$ =150mV. Although Figure 1-9 shows that the process dependent mismatch coefficient factor  $A_{V_T}$  does not vary much from one nanometer process node to the next, the effect of scaling on

comparator offset is apparent and an increase in the standard deviation is observed as we go to finer line-widths.

Figure 1-9 Simulation data on the effects of  $V_T$  mismatch in recent CMOS technologies. Data corresponds to minimum length NMOS source-coupled pairs biased at  $V_{dsat}$ =150mV.

## 1.3.3 Bandwidth-Accuracy-Power Tradeoff

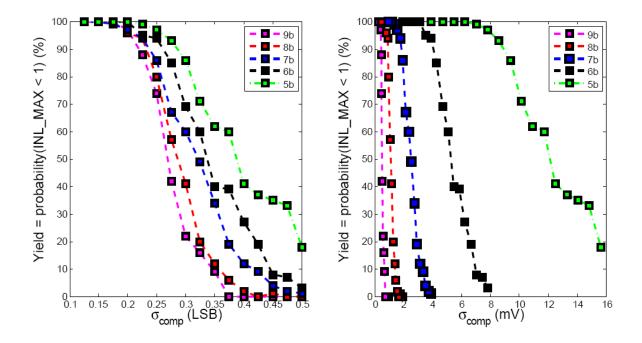

Device mismatch limits the accuracy of ADCs because of its effect on comparator offsets. Figure 1-10 illustrates the impact of device mismatch on yield of ADCs ranging from 5 to 9 bits of resolution. The data shows that for each additional bit, the maximum offset  $\sigma_{comp}(mV)$ , required to maintain a ~90% yield goes down by approximately 1/2X.

Figure 1-10 Simulation data on yield vs. comparator offset for 5-9b flash ADCs with 1V input signal range.

A traditional N-bit flash ADC requires 2<sup>N</sup>-1 comparators which means that the number of comparators roughly double for each additional bit. The large number of comparators required at higher resolutions coupled with more stringent matching requirements, create a tradeoff between bandwidth and accuracy in flash ADCs.

The bandwidth of flash ADCs is limited by comparator input capacitance and is typically dictated by the gate capacitance of the source coupled pair shown in Figure 1-7. Assuming devices are properly biased in saturation, the total comparator input capacitance of an N-bit flash ADC is given by,

$$C_{in} = \frac{2}{3}C_{ox}WL(2^{N} - 1) + C_{Wire}$$

1.5

where  $C_{ox}$  is the gate oxide capacitance per unit area, W and L are the width and length of the comparator input pair, respectively and  $C_{wire}$  is the interconnect capacitance. TABLE I

below shows that for resolutions greater than 6 bits, the device widths required for 90% yield results in an input capacitance  $C_{in}$  in the tens to hundreds of pico-farads. To drive such a large capacitance, a buffer would be required. An on-chip buffer would be difficult to design and would undoubtedly consume a lot of power.

TABLE I Comparator input capacitance  $C_{in}$  as a function of matching requirements for 5-9b flash ADCs with 1V input range in recent CMOS technologies.

| Resolution | σ (LSB) | σ (m V) | W (μm) 90nm | W (μm) 65nm | W (μm) 45nm | Cin (pF) 90nm | Cin (pF) 65nm | Cin (pF) 45nm |

|------------|---------|---------|-------------|-------------|-------------|---------------|---------------|---------------|

| 9          | 0.22    | 0.43    | 978         | 1547        | 2457        | 333.27        | 474.37        | 669.69        |

| 8          | 0.23    | 0.91    | 220         | 348         | 552         | 37.39         | 53.22         | 75.13         |

| 7          | 0.24    | 1.86    | 52          | 83          | 131         | 4.42          | 6.30          | 8.89          |

| 6          | 0.26    | 4.08    | 11          | 17          | 27          | 0.46          | 0.65          | 0.92          |

| 5          | 0.29    | 8.94    | 2           | 4           | 6           | 0.05          | 0.07          | 0.09          |

In [8] it was shown that for a full-scale input to settle within 1/2LSB at an N-bit level requires  $N \cdot ln(2)$  time constants. The time constant is a function of the transconductance (Gm) of the buffer and input capacitance of the comparators. To relax the jitter requirements on the sampling clock, the buffer is typically preceded by a sampling switch and a hold capacitor to form a Track-and-Hold (TAH) circuit (Figure 1-6). The TAH circuit tracks the analog input and holds the sampled input on a capacitor for half the clock period  $T_{clk}$  while the comparators make a decision. Assuming a unity gain buffer for the TAH, the settling requirement  $t_{settle}$  at the buffer output is given by,

$$\frac{T_{clk}}{2} \ge t_{settle} = N \left( \frac{C_{in}}{G_m} \right) \ln(2). \quad 1.6$$

Assuming the  $G_m$  of the buffer is equal to the small signal  $g_m = 2 \cdot I_D / V_{dsat}$  of a device, for a fixed  $V_{dsat}$ =150mV, the plot in Figure 1-11 gives the total current requirements for the buffer as a function of resolution at various sample rates. The plot uses data from TABLE I for a 90nm CMOS process and assumes no slewing. Setting a current budget of

10mA, the tradeoff between power, bandwidth and accuracy in flash ADCs limit sample rates at 1GHz and above to 6bit converters and below.

Figure 1-11 Speed-Power-Accuracy tradeoff for flash ADCs in 90nm CMOS with  $V_{dsat}$ =150mV.

Figure 1-9 and Figure 1-10 illustrates that the bit accuracy of flash ADCs in CMOS is related to the matching quality of the technology. Furthermore, to achieve good accuracy requires large devices for the input pair of the comparator. As a result, the comparator input capacitance increases and more power is needed to achieve high bandwidth.

#### 1.3.4 Area

For resolutions greater than 6bits, TABLE I shows that the accuracy requirements for the comparators require device widths greater than 50µm. Furthermore, TABLE I also shows that for the same accuracy, device widths increase at finer line-widths. Since the

number of comparators approximately doubles for each additional bit of resolution, the flash ADC architecture presents area implications for moderate resolutions and above.

In conclusion, matching requirements limit the performance of flash ADCs and high speed and high accuracy can only be achieved by consuming large amounts of power and area. Therefore, decoupling comparator performance from device matching requirements is desirable.

## 1.3.5 Resistive Offset Averaging

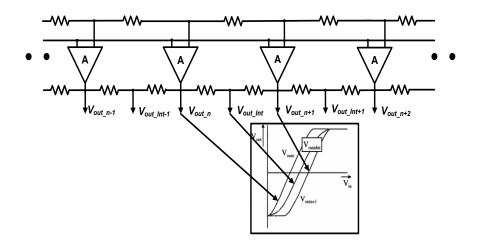

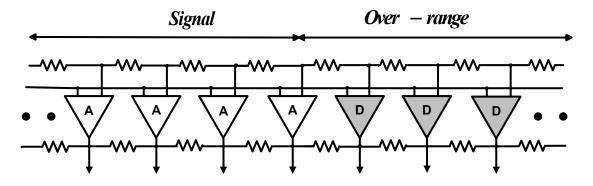

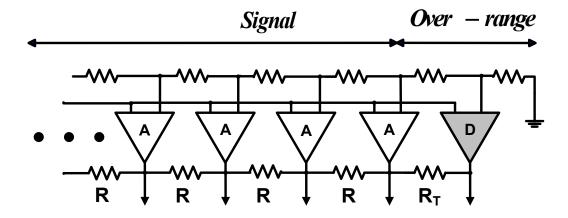

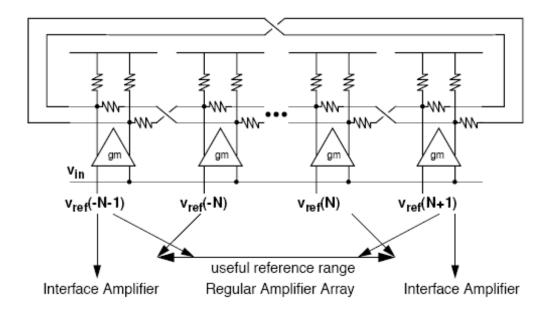

To relax comparator offset requirements in flash ADCs, resistive offset averaging [9] and interpolation [10] have been used to average out mismatch error sources and to reduce the number of pre-amplifiers at the ADC input. Resistive averaging involves connecting resistors between adjacent pre-amplifier outputs as shown in Figure 1-12. Interpolation involves generating zero crossings between two reference levels as shown in Figure 1-13.

Figure 1-12 Resistive offset averaging.

Figure 1-13 Resistive Interpolation.

Although these techniques reduce power and ADC input capacitance, averaging causes a boundary effect, where systematic nonlinearity at the edges of the ADC transfer curve degrades INL [11]. To circumvent these boundary effects, an over-ranging technique [12] incorporates dummy pre-amplifiers at the edges that connect to reference taps extending beyond the input signal range as shown in Figure 1-14. A resistive termination technique in [13] alters the values of the averaging resistors at the edges to reduce the over-range voltage required as shown in Figure 1-15. However, the requirement for the value of the termination resistor limits the value of averaging resistors which in turn limits the allowable offset reduction.

Figure 1-14 Over-ranging.

Figure 1-15 Termination.

Both methods however, require dummy pre-amplifiers which result in a loss of usable voltage range, increased power, input capacitance and area. A triple-cross connection method in [14], cross-connects the outputs of the dummy pre-amplifiers with adjacent preamplifiers and with dummy preamplifiers at opposite edges as shown in Figure 1-16. This eliminates the over-range references and maintains uniform averaging over the entire input range. However, this method introduces negative transconductance at the edges reducing the effective transconductance, gain and bandwidth at the edges. In [15], a reference voltage extrapolation technique eliminates the over-ranging requirements but still requires the use of dummy pre-amplifiers. Area and power constraints limit these techniques to 6 bits and offset requirement can be relaxed by up to 3X [12].

**Figure 1-16 Triple-Cross connection**

# 1.3.6 Comparator Redundancy and Reassignment

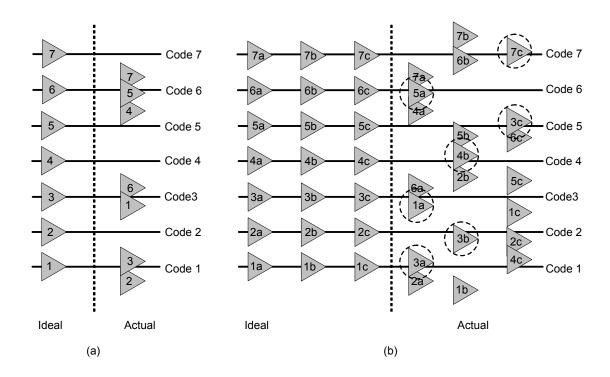

By exploiting the effects of  $V_T$  mismatch with digital correction, the accuracy requirements for comparators can be significantly relaxed to allow flash ADCs to leverage the benefits of scaling. In [16], digital calibration in combination with comparator redundancy and reassignment are used to decouple comparator performance from device matching requirements. This enables the use of low precision comparators that were optimized for speed, power and area.

# Reassignment

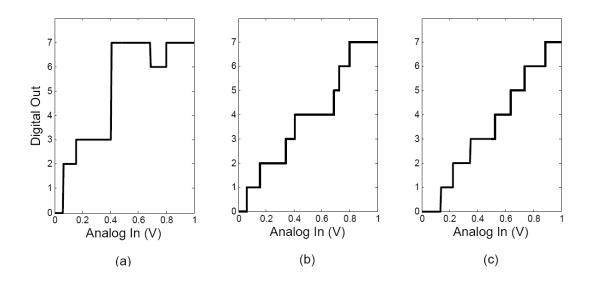

Comparator reassignment involves reassigning a comparator that was originally designated to a specific code, to one in which it is more suited to. This guarantees monotonicity regardless of the offset magnitude. Figure 1-17a shows the trip points for an ideal and actual 3-bit flash ADC with offsets. In the latter case, large comparator offsets

have caused the trip-points of all the comparators to deviate significantly from their nominal trip-points. Furthermore, comparators one and six have become interchanged with three and four respectively. The sequence of trip-points is no longer monotonic. This causes large DNL errors, missing codes and results in poor linearity when employing basic encoding schemes. Figure 1-18a illustrates the resulting transfer curve.

With reassignment, all comparators are reassigned to codes that are close to their actual trip-points. The comparators for the actual case in figure 2.2.a will therefore be reassigned as follows:

TABLE II Reassignment for comparators of Figure 1-17a

| Comparator | Reassignment |  |  |

|------------|--------------|--|--|

| 1          | 3            |  |  |

| 2          | 1            |  |  |

| 3          | 2            |  |  |

| 4          | 5            |  |  |

| 5          | 6            |  |  |

| 6          | 4            |  |  |

| 7          | 7            |  |  |

Figure 1-18b illustrates the resulting transfer curve. Reassignment has ensured monotonicity however large DNL errors still exist.

### Redundancy

To correct for DNL errors, redundancy is introduced. Redundancy involves assignment of multiple comparators to each code. This increases the probability of finding a comparator close to each ideal trip-point. Figure 1-17b shows the trip points for an ideal and actual 3-bit flash ADC with redundancy. In the actual case, large comparator offsets have caused the trip-points of all the comparators to deviate significantly from

their nominal trip-points. However, because more than one comparator was assigned to each code, there exist comparators with actual trip-points near every nominal trip-point. A search can performed to find the trip-point closest to each nominal trip-point. The comparators for the actual case in Figure 1-17b will therefore be assigned as follows:

Table III Reassignment for comparators of Figure 1-17b.

| Comparator | Reassignment |  |  |

|------------|--------------|--|--|

| 1a         | 3            |  |  |

| 3a         | 1            |  |  |

| 3b         | 2            |  |  |

| 3c         | 5            |  |  |

| 4b         | 4            |  |  |

| 5a         | 6            |  |  |

| 7c         | 7            |  |  |

Figure 1-18c illustrates the resulting transfer curve. Reassignment has ensured monotonicity and redundancy has reduced DNL errors.

# **Degree of Redundancy**

Yield is a function of comparator offset and redundancy. Comparator offsets cause non-uniform quantization that degrades signal-to-noise ratio (SNR). Therefore, to achieve good performance based on a target SNR, sufficient comparator redundancy must be employed. In [17], it was shown that redundancies of 4 and greater exhibit yields greater than 90% for comparator offsets up to 10LSB. The yield criteria used was a maximum of 3dB attenuation in SNR of an ideal flash ADC.

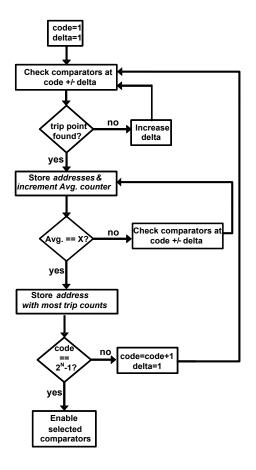

### **Calibration Algorithm**

At power-on, a calibration engine (i.e. finite state machine) initiates a search algorithm. With aide from a digital-to-analog converter (DAC), known references

spanning the ideal trip voltages are applied to the input of the comparator bank. Changing the input voltage about an ideal trip-point triggers near-by comparators. The calibration engine processes the outputs of each comparator and allows the most suitable comparators to be selected. Un-selected comparators are powered off. For an N-bit ADC, the search finishes when 2<sup>N</sup>-1 comparators are selected. Figure 1-19 shows the state-diagram for the code search algorithm.

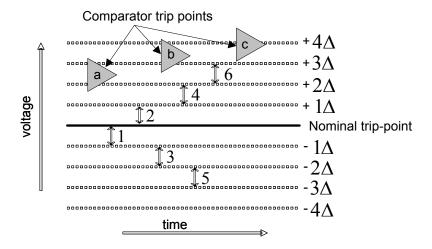

Figure 1-20 illustrates an example of a comparator search. Here comparators "a", "b" and "c" are within " $4\Delta$ " of the desired "nominal trip-point". The calibration engine coordinates the DAC to output voltages within the range: "Nominal trip-point"  $\pm$  " $4\Delta$ " in " $\Delta$ " increments beginning at the nominal trip-point. Therefore, on the sixth search comparator "a" triggers and will be detected by the calibration engine. However, because of circuit noise, comparators "b" and "c" may also trigger even though their trip-points were not reached. To compensate for circuit noise, the calibration engine will coordinate multiple sweeps at the same DAC output. In this case the region " $+2\Delta \rightarrow +3\Delta$ " will be searched multiple times. The calibration engine will record all triggers and select the comparator that triggered the most number of times. This effectively averages out the noise.

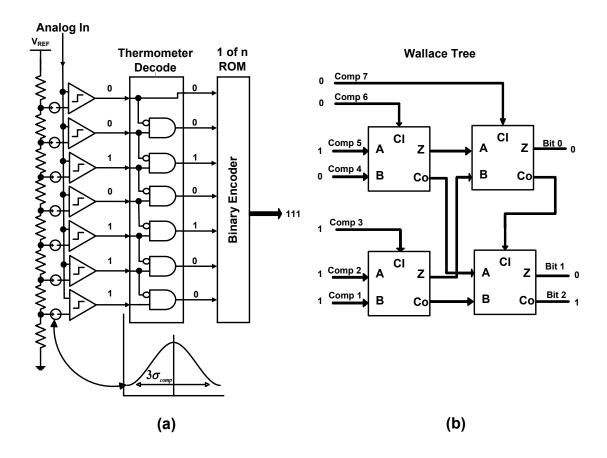

# **Encoding**

Conventional encoding schemes for flash ADCs are susceptible to comparator offsets which cause errors at the thermometer decoder output. Figure 1-21a shows a 3-bit flash ADC where comparator offsets lead to a "bubble" in the thermometer code. The result is an error of 3LSBs at the binary encoder output. Such errors result in non-monotonic behavior like the one observed in Figure 1-17a. An encoding scheme that achieves local

and global bubble suppression to limit the maximum error to one LSB was presented in [18]. It is based on a "Wallace tree" architecture [19] used to implement high-speed multipliers. Figure 1-21b shows the architecture and gives an example where a bubble in the thermometer code output of the comparators is corrected by simply counting the number of logical ONEs present at the output of the comparators.

The encoding scheme is inherently independent of comparator assignment. Therefore it is suitable for flash ADCs incorporating redundancy and reassignment since unselected comparators are powered off, and do not contribute to the summation.

Figure 1-17 Comparator Redundancy and Reassignment. (a) 3b ADC ideal and actual with reassignment. (b) 3b ADC ideal with redundancy and actual with reassignment.

Figure 1-18 Trip-points for 3b flash ADC with offsets. (a) No reassignment. (b) With reassignment. (c) With reassignment and redundancy.

Figure 1-19 Code search algorithm.

Figure 1-20 Example of an ADC comparator search where three comparators trip on the sixth search. Noise averaging will result in the selection of comparator "a".

Figure 1-21 (a) Conventional encoding scheme for flash ADCs where bubbles in the thermometer code lead to errors in the ADC output. (b) Encoding scheme based on Wallace tree architecture.

#### 1.4 Recent work on flash-based ADCs

GS/s, moderate resolution ADCs incorporating a flash architecture with statistical selection [20] or a sub-ranging architecture that eliminates the reference switching network [21], employ small, compact comparators to leverage the speed, area and power advantages of nanometer CMOS. Furthermore, they can rely on statistical selection or offset calibration techniques to limit SNR degradation from non-uniform quantization noise. However, the advantages of small device sizes for speed, power, area and low input capacitance are offset by circuit noise which limits overall ADC performance to less than 7 bits in [21] and less than 6 bits in [20].

#### 1.5 Recent work on Time-Interleaved ADCs

The time-interleaved architecture is popular for high sample-rates because it shifts the speed requirement to the sampled-and-hold circuits. For moderate resolution, Giga-Sample per second conversion (GS/s) the time-interleaved pipeline and SAR architectures are extensively employed. However, interleaving of sampling is challenging, and complex calibration algorithms are required to correct for gain, offset [22], [23], [24], [25] and sometimes timing mismatch between channels [22], [25].

Time-interleaved pipeline ADCs with both GS/s performance and moderate resolution have been achieved using conventional op-amp designs in 0.13µm CMOS. In [23], a double sampling technique is leveraged to reduce the number of T/Hs, maximize active op-amp power with op-amp sharing, and increase the throughput of each sub-ADC. In [26], extensive interleaving was employed to relax the op-amp bandwidth requirements. However, the high op-amp gain required even in conventional moderate-

resolution pipeline ADCs is challenging in 45nm CMOS and below where the transistor self-gain is ~10 and supply voltage is 1V.

In [15], both high gain and bandwidth are achieved in the MDAC op-amp with increased levels of cascoding, gain boosting and the leveraging the  $f_T$  of 40nm thin-oxide MOS transistors in the differential pair. Although this technique enables greater than 9 bit linearity and 1.5GS/s operation in each pipeline ADC, thick-oxide devices and a 2.5V supply were required to maximize the op-amp signal swing. Furthermore, low drop-out regulators (LDOs) were required to adapt the subsequent circuit blocks, which employed thin-oxide devices, to the common mode of the op-amp. A dual-residue technique in [27] relaxes the op-amp gain and bandwidth requirements enabling simple gain stages in a 40nm CMOS with a 1V supply to achieve greater than 9 bit linearity. However, 4X interleaving was required for only 800MS/s performance. In [28], 1-bit folding sub-ADCs incorporating open loop amplifiers enabled single-channel 7b GS/s performance in 45nm CMOS. However, settling errors from full-scale transitions severely degrade SNDR at high frequencies.

On the other hand, the power efficiency of the SAR ADC architecture, coupled with advances in CMOS, has enabled moderate resolution SAR ADCs up to 100 Mega-Samples per second (MS/s) when incorporating error compensation techniques [29]. For GS/s performance and moderate amount of interleaving, the resolution is limited to around 7 bits [25], [30]. For higher resolutions, recent architectures leverage the power efficiency of SAR ADCs either with extensive parallelization [26] or in a hierarchical structure by connecting many SAR sub-ADCs to a single track and hold (TAH) [31]. A hierarchical structure maintains the interleaving factor and number of Track and Hold

(TAH) circuits to moderate levels. However, these approaches yield a large active area, require gain and offset calibration, and consume power in the hundreds of milli-Watts.

#### 1.6 Thesis Outline

This work focuses on power efficient, Giga-Sample per second (GS/s), moderate resolution ADCs in nanometer CMOS technologies. The following chapters describe the theoretical background, describe circuit prototypes and present measurement results for three ADC architectures. Chapter 2 describes work on the advancement of a comparator redundancy scheme based on probability and digital correction techniques to compensate for accuracy in flash ADCs [32]. Chapter 3 describes a high feedback factor approach to the pipeline ADC architecture to relax the gain and bandwidth requirements in the multiplying digital to analog converter (MDAC) [33]. Chapter 4 describes a novel technique that employs op-amp and sub-ADC sharing in a 2X time-interleaved pipeline ADC to increase throughput, and at the same time reduce power dissipation and area [34]. Finally, chapter 5 offers concluding remarks, a comparison with state of the art and suggests future research projects.

# **CHAPTER 2 Deliberate and Random Offset for Setting Comparator Thresholds**

#### 2.1 Introduction

For flash ADCs, the bandwidth-accuracy-power tradeoff becomes more stringent in finer line-width technologies, because this relationship is determined by process-dependent parameters that characterize transistor matching [35]. Unlike conventional designs, this work exploits the effects of V<sub>T</sub> mismatch. The accuracy requirements for comparators can be significantly relaxed, allowing the ADC design to leverage the benefits of digital scaling. In [16] [17] [36], a comparator redundancy scheme is introduced to decouple performance from matching requirements. We advance this technique by employing random and deliberate mismatch to set the desired trip-points of the comparators and thus eliminate the need for a low-impedance high-precision resistor ladder. Unusually, the proposed technique exploits large random variation in comparator offset. This enables the use of low precision dynamic comparators that can be optimized for speed.

Section 2.2 presents an outline of the ADC architecture and discusses the implementation of key blocks. A challenge in this design is to achieve a large random variation in comparator offset and at the same time, satisfy the input-referred noise requirement of the comparators. Section 2.3 considers this tradeoff and the implications for energy efficiency of the comparator. Measurement results are presented in section 2.4.

# 2.2 Architecture and Implementation

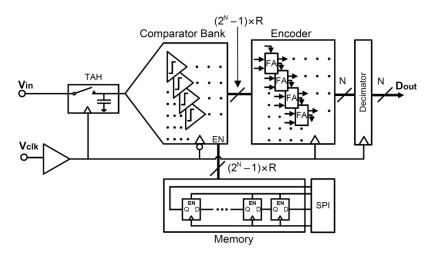

Figure 2-1 shows a block diagram of the proposed ADC architecture. A track-and-hold (TAH) circuit samples a differential input signal (single-ended shown), which is subsequently processed by a subset of a bank of redundant comparators. No reference ladder is required since the comparator trip-points are set by a combination of deliberate and random mismatch. At startup, a calibration routine finds the comparators closest to the desired trip points. Sufficient redundancy ensures that enough variation exists about a pre-defined set of deliberate mismatches to ensure the comparator bank spans the desired input range. Furthermore, because this technique decouples comparator performance from matching requirements, the comparators can be made small and fast. Only useful comparators are enabled. Each comparator can be enabled or disabled independently and a memory element associated with each comparator stores the comparator on/off states. The memory elements are connected serially forming a memory block that is accessible through an SPI interface. An encoder block, comprised of full adders, resolves the comparator outputs to the 7-bit ADC output code.

Figure 2-1 N-bit ADC architecture with redundancy of R comparators per code.

### 2.2.1 Comparator Bank

The comparator bank incorporates redundancy and reassignment to correct DNL errors [16], [17]. A conservative value of ten was chosen for comparator redundancy in this proof of concept design. In this scheme, multiple redundant comparators are assigned to each code to increase the probability of finding a comparator with a trip-point close to each ideal trip-point. Furthermore, by allowing comparators with large random offsets, originally designated to specific codes, to be reassigned to more suitable codes, offset do not compromise ADC accuracy, regardless of their magnitude.

Since this ADC architecture does not employ a resistor ladder, comparator thresholds are determined by a combination of deliberate and random offsets. Random offsets alone would limit the dynamic range of the ADC. This is because large random offsets require small devices, which in turn leads to higher noise, degrading SNR. Therefore, deliberate offsets are introduced to the comparators to increase dynamic range. Increasing the dynamic range increases the LSB size for a given resolution therefore improving SNR. The minimum input range is dictated by the input referred noise value that allows the ADC design to meet a target SNR. On the other hand, it is also necessary that random offsets adequately cover the desired range between deliberate offsets and this limits the maximum input range. In section 2.3 we show that only a small number of deliberate offsets needs to be introduced.

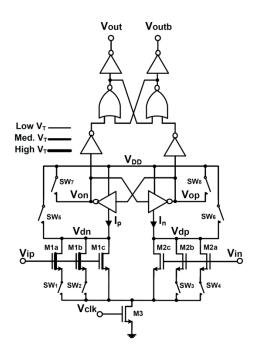

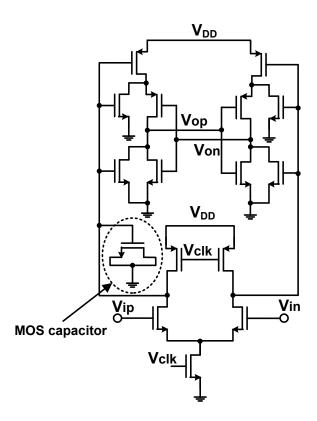

# 2.2.2 Comparator

The comparator, based on [37], is modified to introduce a deliberate offset. This current latch sense amplifier (CLSA), shown in Figure 2-2, leverages small devices for

power and speed and also exhibits large offsets suited for redundancy and reassignment. Deliberate offsets are introduced by asymmetric sizing of the input pair and by the use of FETs with differing threshold voltages. The input differential pair of the comparator is formed as composite devices, M1a-c and M2a-c. M1a-c and M2a-c are formed by combinations of low, medium and high V<sub>T</sub> devices. The use of devices with different threshold voltages for the input pair limits the amount of asymmetrical sizing needed for a given offset. Different V<sub>T</sub> combinations are assigned to different comparators during layout. Furthermore, asymmetric sizing is introduced with switches SW1-4 which hardwire the programming of the widths of the input pair. A standard unit cell (Figure 2-2) is used to implement all comparators in the comparator bank. This allows programming of the deliberate offsets to be achieved with automated schematic design, layout and simulation. Increasing the input range by adding branches to the composite devices M1-2 of the comparator in Figure 2-2 increases the input capacitance of the comparator bank and puts a heavier burden on the input sampling switch for a given settling time requirement. Therefore comparator input capacitance, along with noise and offset, dictate the input range and 600mVpp was found to be optimal.

The comparator, including the SR latch, buffers and enable/disable functionality, occupies an area of 100µm<sup>2</sup>, of which 30% is the input FETs, SW1-4 and M3.

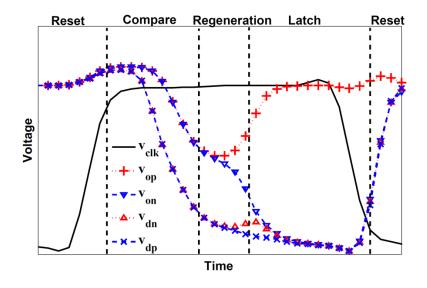

Figure 2-3 shows the circuit waveforms for the comparator in Figure 2-2. The circuit operation is as follows: When  $V_{clk}$  is low, all internal nodes including  $V_{dn-p}$  and  $V_{op-n}$  are preset to  $V_{DD}$  by switches SW5-8. When  $V_{clk}$  goes high, the input pair senses the input voltages,  $V_{ip}$  and  $V_{in}$ , and induces differential currents  $I_p$  and  $I_n$  through M1a-c and M2a-c respectively. The current difference is converted to a large voltage difference through

regeneration and latching of the cross-coupled inverters at nodes  $V_{op-n}$ . The final output voltage difference,  $V_{op}$ - $V_{on}$ , reaches  $\pm V_{DD}$  and is subsequently latched by an SR latch to retain the decision during the reset phase.

Figure 2-2 Comparator circuit with programmable offset.

Figure 2-3 Waveforms illustrating regions of operation of the comparator.

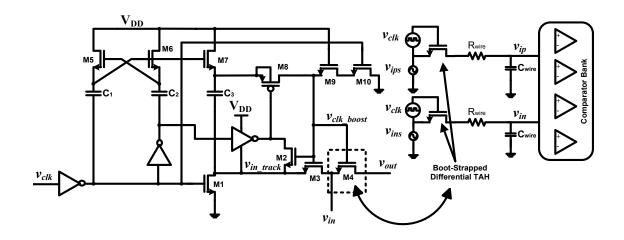

# 2.2.3 Boot-strapped Track-and-Hold

A track-and-hold (TAH) circuit is used to reduce the jitter requirements for the comparator sampling clock and to minimize the effects of skew in the clock-path of the comparator bank. The TAH circuit consists of an NMOS switch and a hold capacitor, comprised of the routing capacitance and the input capacitance of the comparator bank. Furthermore, the TAH is boot-strapped [38] in order to operate at a 1.2V supply and to reduce input signal dependence.

The circuit, shown in Figure 2-4, uses a charge pump consisting of capacitors  $C_{1-2}$  and devices M5-6, to charge capacitor  $C_3$  to  $V_{DD}$  during the hold mode (i.e.  $v_{clk}$  is low). In track mode, the gate of switch M3 is coupled to capacitor C3 via M8. During this time, M3 allows the gate of M4 to track the input signal  $v_{in}$  offset by  $V_{DD}$  and thus allowing a constant voltage across its gate-source during the entire track mode.

By maintaining a constant Vgs, switch linearity is improved and signal-dependent charge-injection is reduced. A differential TAH is used for suppression of second order effects [11]. Figure 2-5 shows extracted simulation waveforms and switch linearity for a ~1GHz input signal sampled at 2GHz. The simulation use a 1V V<sub>DD</sub> and uses load models based on extracted data on the comparator bank and signal path. The lower plot corresponds to ENOB vs. Time based on 512 point FFTs over one clock cycle. Data shows that 10-bit linearity is maintained during the hold phase and up to 13-bit linearity is seen during the track phase.

Figure 2-4 Differential boot-strapped TAH.

Figure 2-5 Differential boot-strapped TAH waveforms and linearity for  $\sim\!\!1GHz$  input signal sampled at 2GHz.

#### 2.2.4 Encoder

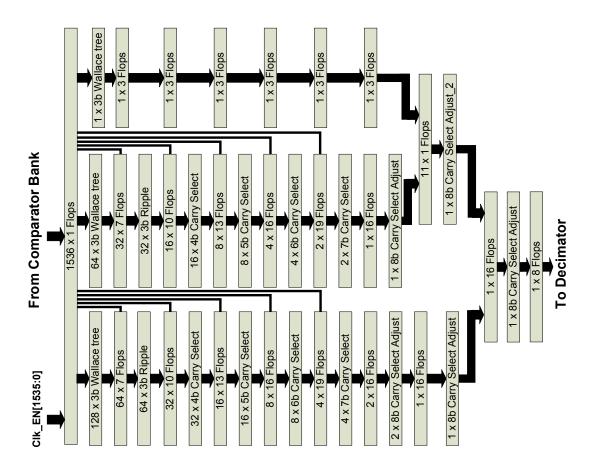

The outputs of all the comparators are routed to an encoding block and summed to form a 7-bit output word. Addition permits comparators to be easily reassigned to any code and eliminates non-monotonicity. The encoder uses a Wallace tree architecture [18], in combination with carry-select adders and pipelining, to resolve ~1500 comparator outputs at 1.5GS/s. Figure 2-6 shows the block diagram. This encoding scheme is inherently independent of comparator assignment since it adds the number of logic highs present at its input. Furthermore, since only 127 comparators are enabled after calibration and disabled comparators do not contribute to the encoded result, 7-bit encoding is guaranteed.

Figure 2-6 Encoder block diagram.

# 2.2.5 Calibration Algorithm

At power-on, an off-chip calibration engine initiates a comparator search algorithm [36]. With the aid of an off-chip digital-to-analog converter (DAC), input voltages spanning the desired trip voltages are applied to the input of the comparator bank to search for the optimum comparator to assign to each code. During the search, the calibration engine enables a trial comparator. Comparators that have already been selected during earlier searches are also enabled. This mimics the effects of comparator kickback seen during normal operation and minimizes any differences between IR drops on the supply lines during calibration and normal operation. The calibration engine then instructs the DAC to sweep the input voltage about the desired trip-voltage. If the trial comparator is suitable its output will toggle causing the output of the encoder to transition between X and X-1 where X is the total number of comparators enabled. For a 7-bit ADC, the search finishes when 127 (i.e. 2<sup>7</sup>-1) comparators are selected. Unselected comparators remain powered off<sup>1</sup>. Finally, it should be noted that the input range is set by the maximum deliberate comparator offset and is hardwired into the design. Sweeping the calibration DAC beyond this input range reduces the effectiveness of random comparator offset and degrades DNL.

### 2.3 Comparator Analysis

A challenge in the design of the comparators is to achieve a large random variation in offset, beneficial for redundancy and reassignment, and at the same time to satisfy the input-referred noise requirement. This design employs small, low-precision comparators

<sup>&</sup>lt;sup>1</sup> The clock input to each comparator is preceded by a series switch that disconnects the local clock buffer to any disabled comparator.

with large random offsets. Equation (1.4) shows that the use of small devices results in a large random offset which in turn enables a wider distribution of trip voltages for the redundancy and reassignment scheme. However, the use of small devices also tends to increase the input referred noise of the comparators which in turn limits the ADC SNR. In [39] it is shown that thermal noise from the input pair and kT/C noise from switches SW7-8 during reset are the dominant sources of noise. To first order, the input-referred noise equivalents of these sources, validated with Spectre transient noise simulations, are given by [39],

$$\overline{\delta v_{eq\_M\,l-2}^2} \approx \frac{2kT\gamma \cdot v_{dsatl}}{C_{\perp}V_{TN}} \qquad 2.1$$

$$\overline{\delta v_{eq\_sw7-8}^2} \approx \frac{kT \cdot v_{dsatl}^2}{2C_o V_{TN}^2} \qquad 2.2$$

where  $v_{dsat1}$  is the overdrive voltage of the input pair,  $V_{TN}$  is the threshold voltage of the NFETs of the cross-coupled inverter pair,  $\gamma$  is the MOS noise factor, and  $C_d$  and  $C_o$  are the capacitances at nodes  $V_{dn-p}$  and  $V_{op-n}$ , respectively. Equations 2.2 and 2.3 show that increasing the capacitance at nodes  $V_{dn-p}$  and  $V_{op-n}$  or reducing  $v_{dsat1}$  by increasing the widths of the input pair, reduces noise.

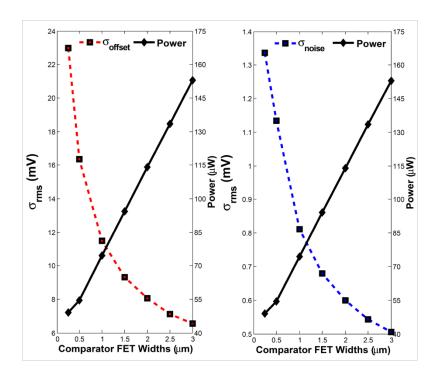

Figure 2-7 plots comparator input-referred offset and noise versus device width, using data obtained from Spectre simulations. The x-axis is the width of M1-3 and of the cross-coupled inverters of the comparator in Figure 2-2 $^2$ . The comparator is clocked at 2GHz and the circuit uses a 1V V<sub>DD</sub>. Power is plotted alongside noise and offset to illustrate the tradeoff between power, offset and accuracy. Figure 2-7a shows the advantages of small

$^2$  These simulations consider composite devices M1a,b,c and M2a,b,c as single nominal  $V_{\rm T}$  devices. Switches SW5-8 are sized to ensure reset functionality at 2GHz. Switches SW1-4 are not included.

width in terms of power consumption and increased spread of input offset which is beneficial for comparator redundancy and reassignment. On the other hand, Figure 2-7b shows the input referred noise also increases for small transistor widths. Figure 2-7 illustrates a tradeoff between noise and offset that is unique to the proposed ADC architecture. The use of large device widths results in lower noise, which improves ADC SNR but also reduces comparator random offset. A smaller random offset requires the ADC to utilize more deliberate offsets, to compensate for the lack of spread from random offset, to achieve sufficiently small granularity for a given dynamic range. In doing so, the amount of SNR degradation due to both thermal noise and non-uniform quantization noise can be minimized but at the expense of increased complexity in comparator design. The choice of device dimensions therefore depends on the target ADC SNR and the number of deliberate offsets employed.

Figure 2-7 Spectre simulated comparator (a) offset, (b) noise and (a & b) power (@ 2GHz, 1V VDD) vs. comparator FET widths for the comparator in Figure 2-2.

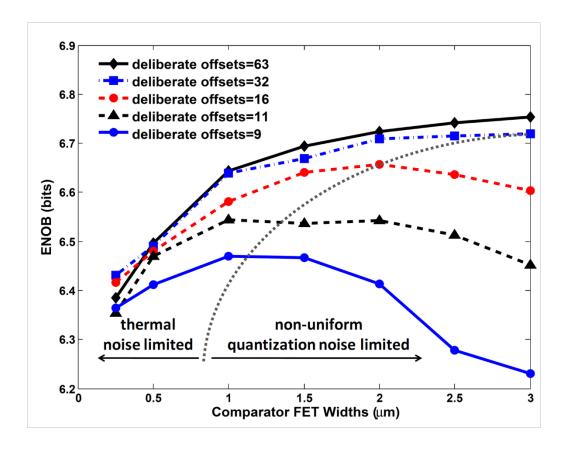

Figure 2-8 shows a plot of the effective number of bits (ENOB) of a 7-bit Flash ADC versus the comparator device widths. The data is generated by a Monte-Carlo model of a bank of comparators with a redundancy of five comparators per code and with the most suitable comparator selected for each code. The offset and noise data from Figure 2-7 are used in this model. Each data point in Figure 2-8 is the average ENOB observed for 100 randomly generated ADCs and each of the five curves corresponds to a different number of deliberate offsets employed. For small device widths, the plot shows a low ENOB that is largely independent of the number of deliberate offsets used. A low ENOB at small device widths indicates that ADC performance is dominated by thermal noise. On the other hand for large widths, insufficient random variation in offset results in fewer tripvoltages between deliberate offsets so that ENOB degradation from non-uniform quantization dominates. This effect is more apparent for ADCs employing a small number of deliberate offsets

For a given target ENOB there exists an optimum combination of the number of deliberate offsets and comparator device size. Figure 2-7 shows that increasing the comparator device widths to mitigate noise and random offset also increases power consumption. Furthermore, Figure 2-8 shows that for a given number of deliberate offsets, there exists a device width that maximizes ADC ENOB. Beyond this point, the power consumption increases with increased device width and unlike traditional flash ADCs, the ADC accuracy for the proposed architecture degrades. This is because there is no longer a large enough random variation in comparator offset to cover the gap between deliberate offsets, causing an increase in quantization noise.

As an example, for device widths of 1µm, Figure 2-7 shows that there is sufficient random variation in comparator offset to require only 16 deliberate offsets to achieve an average ENOB of 6.58 bits. Simulations also indicate that 90% of ADCs achieve an ENOB greater than 6.5 bits. Increasing device widths up to 2µm further improves ENOB but also increases power consumption. Beyond 2µm as shown in Figure 2-8, ADC ENOB degrades because of increasing non-uniform quantization noise. In conclusion, for a target ENOB there exists an optimum combination of the number of deliberate offsets and comparator device size that minimizes design complexity and power.

Figure 2-8 Monte-Carlo simulation of ENOB vs. FET widths for 7-bit ADCs using data from Fig. 4 and a redundancy of 5.

#### 2.4 Measurement Results

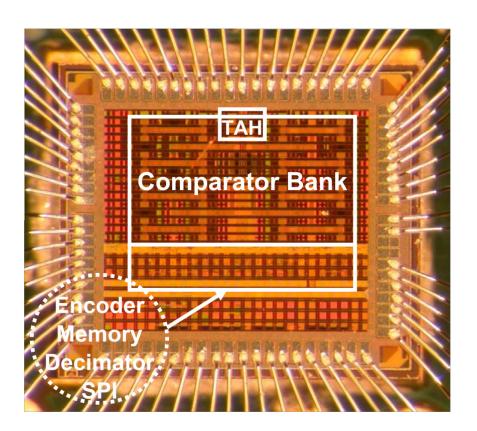

The prototype, fabricated in a 90nm digital CMOS process, occupies a core area of 1.2mm<sup>2</sup>. A die micrograph is shown in Figure 2-9. The prototype is tested as a chip-on-board device to reduce the effects of bond-wire inductance. The prototype ADC has a differential input signal range of 600mVpp and 700mV common mode<sup>3</sup>.

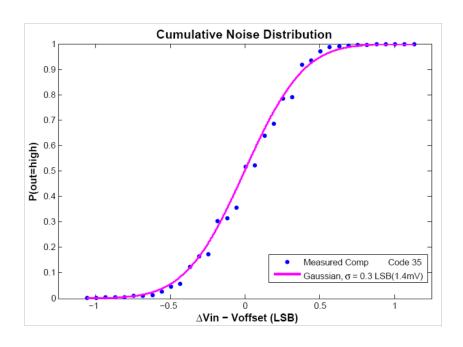

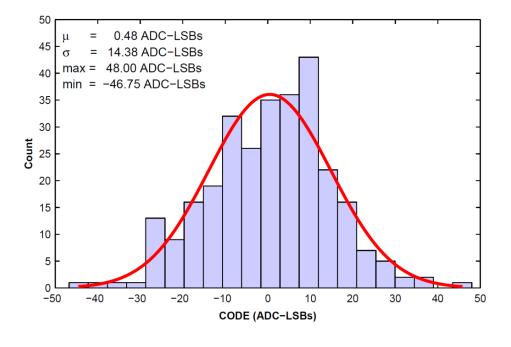

Figure 2-10 shows the experimentally measured input referred noise of the proposed comparator. The equivalent input noise is determined by sweeping a differential voltage at the ADC input about a comparator's threshold and averaging the number of logic ones. The data are fitted to a Gaussian distribution. The measurements show 0.3LSB of input-referred RMS comparator noise.

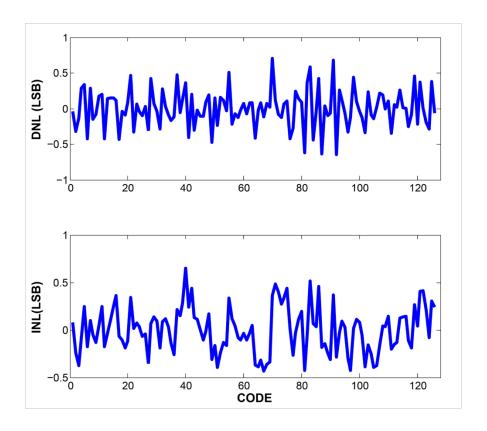

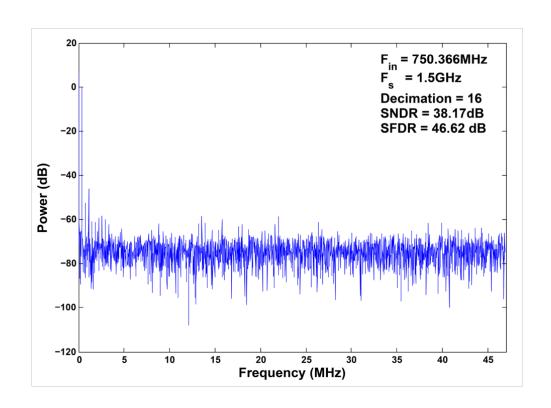

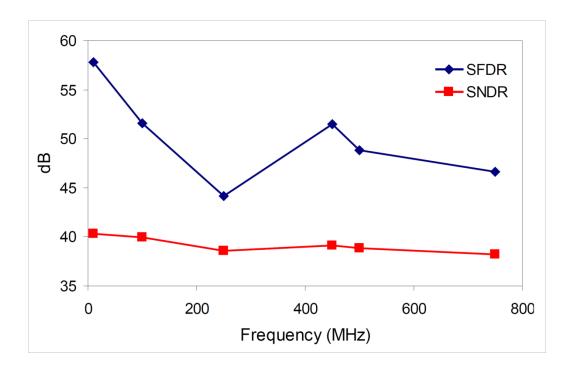

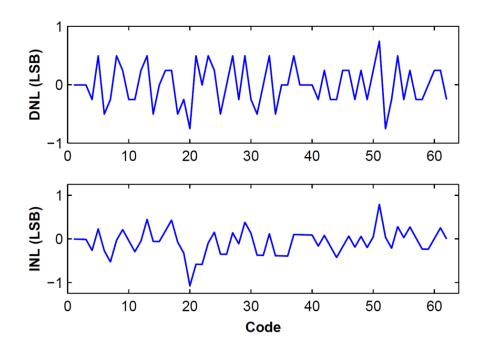

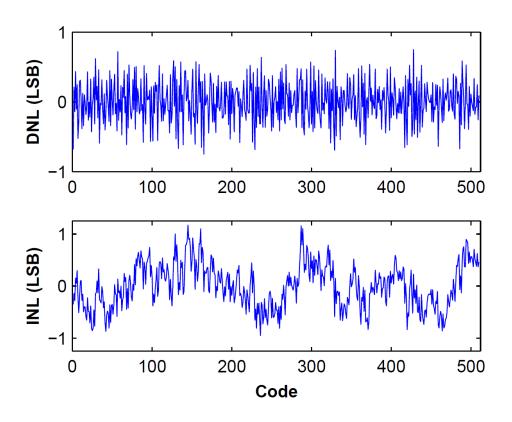

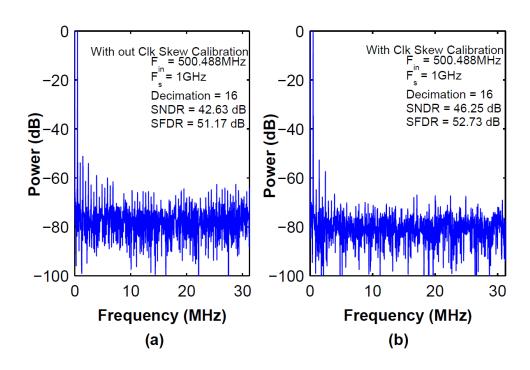

The maximum measured DNL/INL values are 0.70/0.64LSB (Figure 2-11). Figure 2-12 shows a 4096 point FFT spectrum for an input frequency of 750.4MHz sampled at 1.5GHz<sup>4</sup>. Figure 2-13 shows the measured SNDR and SFDR as a function of input frequency at 1.5GS/s. The ADC achieves an ENOB and SFDR of 6.4 bits and 57.7dB at low frequency and 6.05 bits and 46.6dB at Nyquist. There is no measurable degradation in SNDR over 24 hours of operation and the measured BER at 1.5GS/s is less than 2.7x10<sup>-15</sup>. The ADC consumes a total of 204mW at Nyquist from 1.2V analog and 0.9V digital supplies. The comparator bank and repeaters, TAH and clock buffers, and encoder consume 23%, 25% and 52% of the power, respectively. Table IV shows the performance summary of the prototype ADC.

<sup>&</sup>lt;sup>3</sup> The common mode is set by a single off-chip ADC driver that conditions the input signal from both the test equipment and off-chip calibration DAC. This eliminates any common-mode variation between normal operation and calibration.

<sup>&</sup>lt;sup>4</sup> The output data is decimated by 16X for reliable transmission off-chip. Decimation also explains why the near Nyquist tone falls in a low numbered bin in Figure 2-12.

Table IV ADC ADC PERFORMANCE SUMMARY

| Technology                 | 90nm CMOS                       |  |  |

|----------------------------|---------------------------------|--|--|

| Supply Analog/Digital      | 1.2V/0.9V                       |  |  |

| Resolution                 | 7bit                            |  |  |

| Input Range (Differential) | $600 \mathrm{mV}_{\mathrm{PP}}$ |  |  |

| Sampling Rate              | 1.5GS/s                         |  |  |

| Power Consumption          | 204mW                           |  |  |

| DNL/INL                    | 0.7/0.64LSB                     |  |  |

| SFDR @ Nyquist             | 46.6dB                          |  |  |

| SNDR @ Nyquist             | 38.2dB                          |  |  |

| ENOB @ Nyquist             | 6.05                            |  |  |

| FOM                        | 2pJ/Conv-step                   |  |  |

Figure 2-9 Die micrograph of 90nm CMOS ADC.

Figure 2-10 Experimental data on comparator cumulative noise distribution and Gaussian fit.

Figure 2-11 Measured DNL and INL.

Figure 2-12 4096 point FFT for 750.36 MHz input and 16X decimation.

Figure 2-13 SNDR & SFDR vs. Fin (Fs = 1.5GS/s).

# **CHAPTER 3 A High Feedback Factor Approach for GS/s Pipelining**

#### 3.1 Introduction