## Low Power Continuous-time Bandpass Delta-Sigma Modulators

by

## **Hyungil Chae**

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 2013

#### **Doctoral Committee:**

Professor Michael P. Flynn, chair Assistant Professor David D. Wentzloff Assistant Professor Zhengya Zhang Associate Professor Jerome P. Lynch © Hyungil Chae

All rights reserved

2012

To Dad, Mom, my brother, and friends...

## **ACKNOWLEDGEMENTS**

I would like to thank my advisor Prof. Michael Flynn for guiding and encouraging me technically and personally during the whole time in Ann Arbor. He inspired and motivated me with his passion and intelligence, and I would never have been able to finish my research without his care and support. I also would like to thank my committee members, Prof. David Wentzloff, Prof. Zhengya Zhang, and Prof. Jerome Lynch, for their interest and support for this research.

I would like to acknowledge Dr. Gabriele Manganaro, Dr. Jipeng Li, and other people in Analog Devices. I learned a lot from them while my internship in Analog Devices, and my research was successful thanks to their advice and generous support.

And I would like to acknowledge my best friend Dr. Sungwook Chang who always showed the best of friendship for 15 years and other friends: Seunghyuck Hong, Myunghwan Kim, Jaehoo Lee, Seunghyun Oh, Dr. Dongjin Lee, Changwook Min, Wonseok Lee, Dr. Wonseok Huh, Dr. Bongsoo Kyung, Hakjin Chung, Seungjun Oh, Dongyup Nam, Wontae Kim, Hyuckjae Sung, Dr. Yoonmyung Lee, Dr. Daeyeon Kim, Hyungjun Ahn, Sungwon Lee, Sanghyun Chang, Dr. Junseok Huh, Kyuwon Hwang, Dongseok Jeon, Dongmin Lee, Daeyeon Jung, Jungkuk Kim, Hyunjung Park, Dr. Jaehyuck Choi, Yongjun Park, Dr. Jaesun Seo, Dr. Mingoo Seok, Taejun Seok, Yonghyun Sim, Donghun Song, Hyunjung Cho, Jaeyoung Park, Kyungah Kim, and Kihyuk Son. All of them not only gave me unforgettable memories in Ann Arbor but also helped my research greatly.

I would like to thank my former and current research group members who are always good mentors as well as sincere friends: Dr. Hyogyuem Rhew, Dr. Joshua Kang, Dr. Junyoung Park, Dr. Sunghyun Park, Dr. Jongwoo Lee, Dr. Shahrzad Naraghi, Dr. Dan Shi, Dr. Chun Lee, Dr. Mark Ferriss, Dr. David Lin, Dr. Li Li, Andres Tamez, Jorge Pernillo, Nick Collins, Jeff Fredenburg, Mohammad Mahdi Ghahramani, Jaehun Jeong, Aaron Rocca, Chunyang Zhai, Yong Lim, and Batuhan Dayanik.

I have to say thanks to the help of all EECS department staffs, Mrs. Beth Stalnaker, Mrs. Francis Doman, Mrs. Deborah Swartz, Joel VanLaven, and others.

And I am also very grateful to Korean Foundation for advanced studies (KFAS) for providing me with a fellowship and other supports.

Finally, I would like to thank my family. My father, mother, and brother gave me their endless love and support, and they are a big part of my success.

## TABLE OF CONTENTS

| Dedication                                                      | ii   |

|-----------------------------------------------------------------|------|

| Acknowledgements                                                | iii  |

| List of figures.                                                | ix   |

| List of tables                                                  | xiii |

| List of abbreviations                                           | xiv  |

| Abstract                                                        | xvi  |

| Chapter 1. Introduction                                         | 1    |

| 1.1 Software Defined Radio (SDR)                                | 1    |

| 1.2 $\Delta\Sigma$ Modulators (DSM)                             | 3    |

| 1.2.1 Oversampling ADC                                          | 3    |

| 1.2.2 Discrete-time $\Delta\Sigma$ Modulator                    | 6    |

| 1.2.3 Continuous-time $\Delta\Sigma$ Modulator                  | 7    |

| 1.2.4 Bandpass $\Delta\Sigma$ Modulator                         | 8    |

| 1.3 Continuous-time Bandpass $\Delta\Sigma$ Modulator (CTBPDSM) | 10   |

| 1.3.1 CTBPDSM in SDR                                            | 10   |

| 1.3.2 Conventional CTBPDSM Architectures                        | 12   |

| 1.4 Single On amp Resonator                                     | 1.4  |

| 1.5 Ap     | plication Specifications                                              |

|------------|-----------------------------------------------------------------------|

| 1.6 Re     | search Contributions                                                  |

| 1.7 Re     | search Overview16                                                     |

| Chapter 2. | CTBPDSM with a Reduced Number of DACs and Single Op-amp Resonators 18 |

| 2.1 Sys    | stem Architecture                                                     |

| 2.1.1      | Overview                                                              |

| 2.1.2      | Reduction of the number of current-mode DACs                          |

| 2.1.3      | Noise Transfer Function (NTF)                                         |

| 2.2 Cir    | cuit Blocks25                                                         |

| 2.2.1      | Single Op-Amp Resonator                                               |

| 2.2.2      | Current-steering DAC                                                  |

| 2.2.3      | Quantizer                                                             |

| 2.2.4      | Summing Amplifier                                                     |

| 2.2.5      | System Implementation                                                 |

| 2.3 Pro    | ototype Test Results                                                  |

| 2.3.1      | Power Spectral Density                                                |

| 2.3.2      | Dynamic Range                                                         |

| 2.3.3      | Two-tone Test                                                         |

| 2.3.4      | Power Consumption 4                                                   |

| 2.3.5      | Performance Summary and State of the Arts | 46 |

|------------|-------------------------------------------|----|

| Chapter 3. | CTBPDSM with DAC Duty Cycle Control       | 48 |

| 3.1 Ne     | w Architecture                            | 50 |

| 3.2 Fre    | equency Tuning                            | 50 |

| 3.3 Du     | ty Cycle Control                          | 53 |

| 3.4 Inp    | out Signal Filtering                      | 56 |

| 3.5 Cir    | cuit Blocks                               | 57 |

| 3.5.1      | Op-amp                                    | 57 |

| 3.5.2      | DAC                                       | 61 |

| 3.5.3      | DAC Latch                                 | 65 |

| 3.5.4      | Level Shifter                             | 66 |

| 3.5.5      | Clock Generator                           | 68 |

| 3.5.6      | Quantizer                                 | 70 |

| 3.5.7      | Global Bias Circuit                       | 70 |

| 3.5.8      | System Implementation                     | 71 |

| 3.5.9      | Output Buffer                             | 72 |

| 3.6 Me     | easurement                                | 73 |

| 3.6.1      | SNDR                                      | 74 |

| 362        | STF                                       | 75 |

| 3.6.3       | IM3                                       | 76  |

|-------------|-------------------------------------------|-----|

| 3.6.4       | Frequency Tuning                          | 76  |

| 3.6.5       | Power Consumption                         | 77  |

| 3.6.6       | Performance Summary and State of the Arts | 78  |

| Chapter 4.  | Future Work                               | 81  |

| Chapter 5.  | Conclusions                               | 83  |

| Bibliograph | V                                         | .85 |

## LIST OF FIGURES

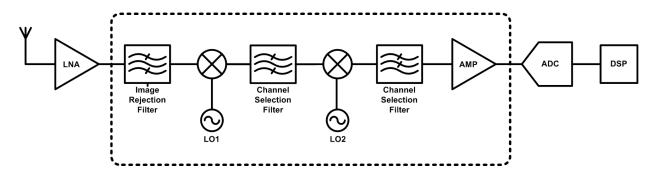

| Figure 1. Super-heterodyne receiver architecture                                       | 1  |

|----------------------------------------------------------------------------------------|----|

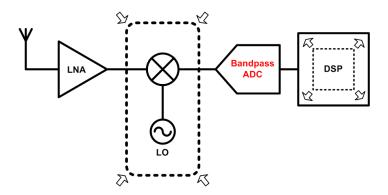

| Figure 2. Software-defined radio                                                       | 2  |

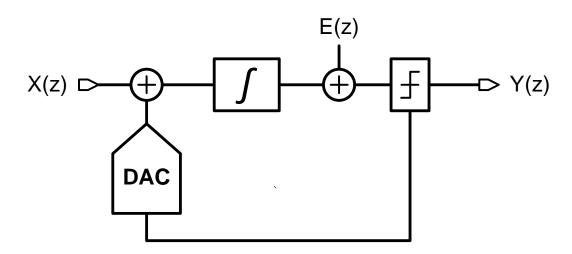

| Figure 3. $\Delta\Sigma$ ADC                                                           | 4  |

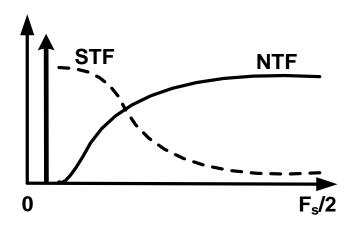

| Figure 4. STF and NTF of $\Delta\Sigma$ modulators                                     | 5  |

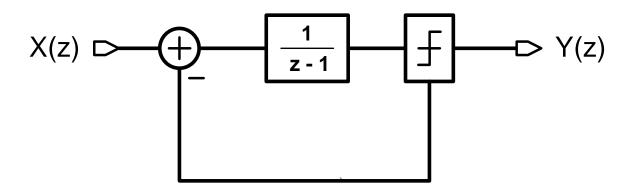

| Figure 5. $1^{st}$ -order discrete-time $\Delta\Sigma$ modulator                       | 6  |

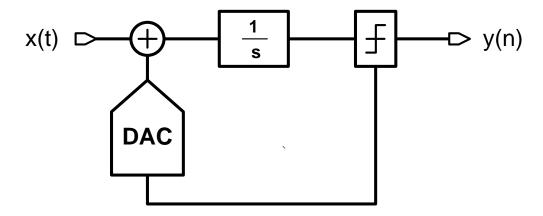

| Figure 6. $1^{st}$ -order continuous-time $\Delta\Sigma$ modulator                     | 7  |

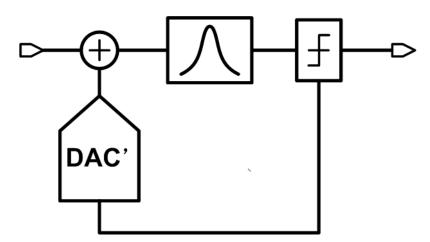

| Figure 7. Bandpass $\Delta\Sigma$ modulator                                            | 8  |

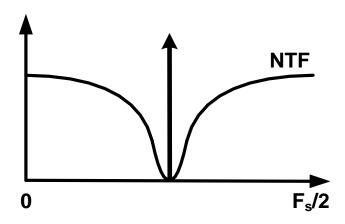

| Figure 8. NTF of bandpass $\Delta\Sigma$ modulator                                     | 9  |

| Figure 9. Discrete-time bandpass $\Delta\Sigma$ modulator                              | 10 |

| Figure 10. Power efficiency of CTLPDSMs vs. CTBPDSMs                                   | 11 |

| Figure 11. Conventional CTBPDSM architectures                                          | 12 |

| Figure 12. Single op-amp resonators                                                    | 14 |

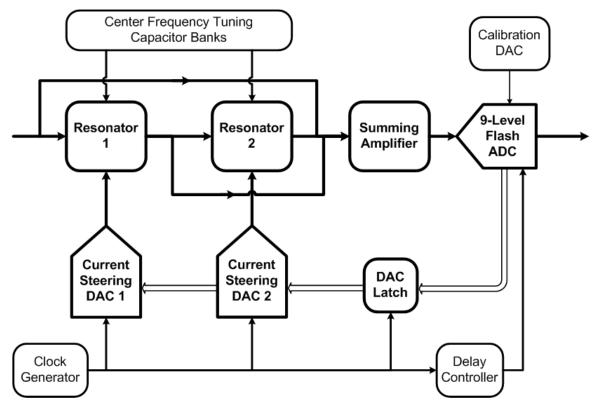

| Figure 13. System block diagram                                                        | 18 |

| Figure 14. 4 <sup>th</sup> -order CTBPDSM architecture (a) conventional (b) simplified | 20 |

| Figure 15. Noise transfer function of the modulator                                    | 24 |

| Figure 16. Quality factor enhancement by positive feedback                             | 25 |

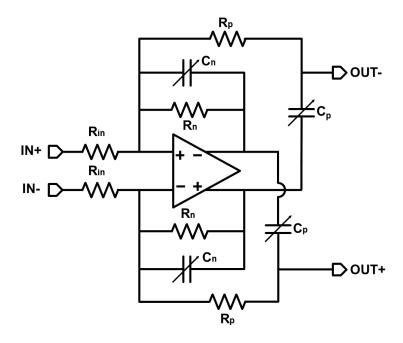

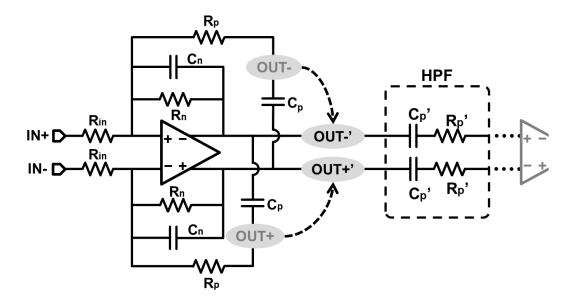

| Figure 17. Differential-mode implementation of single op-amp resonator                 | 27 |

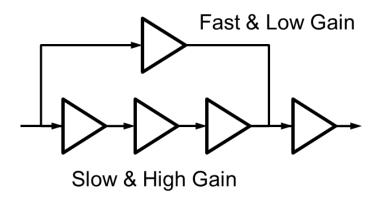

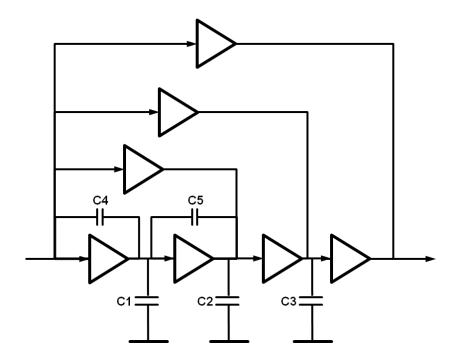

| Figure 18. Multi-path amplifier                                                        | 28 |

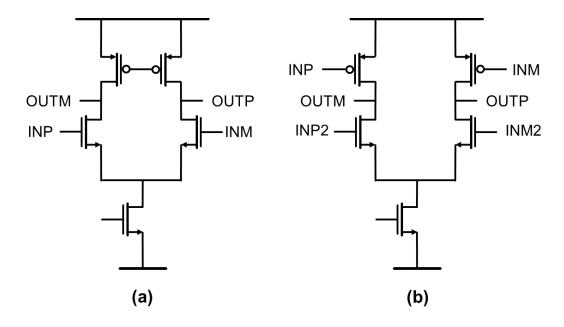

| Figure 19. Stage units of the amplifier (a) w/o summing (b) w/ summing | 29 |

|------------------------------------------------------------------------|----|

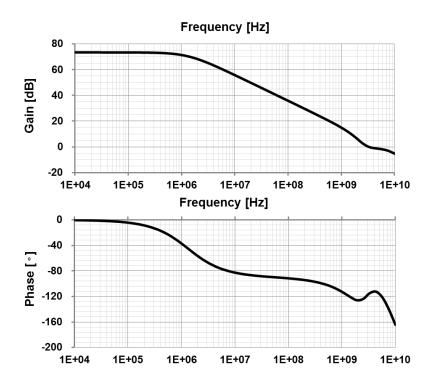

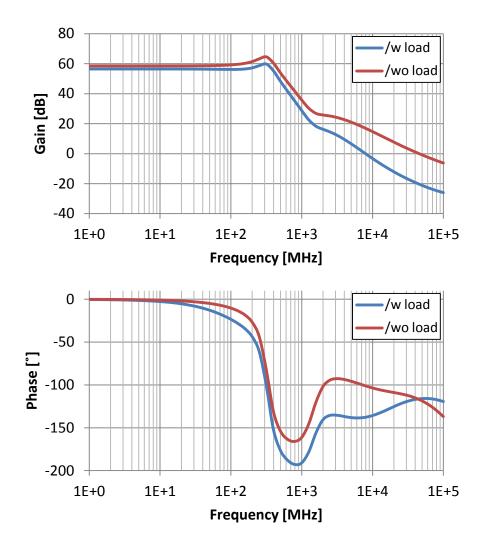

| Figure 20. Gain and phase response of the amplifier                    | 30 |

| Figure 21. Resonator RC tuning with capacitor banks                    | 31 |

| Figure 22. Quality factor and center frequency tuning                  | 32 |

| Figure 23. Output node change                                          | 33 |

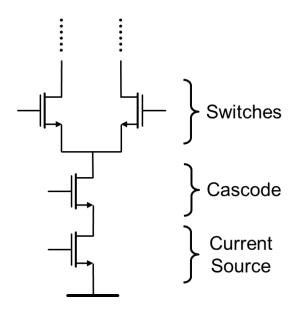

| Figure 24. Triple cascode structure for DAC                            | 34 |

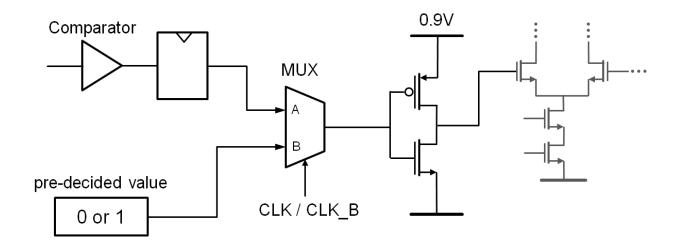

| Figure 25. Return-to-zero pulse DAC latch                              | 36 |

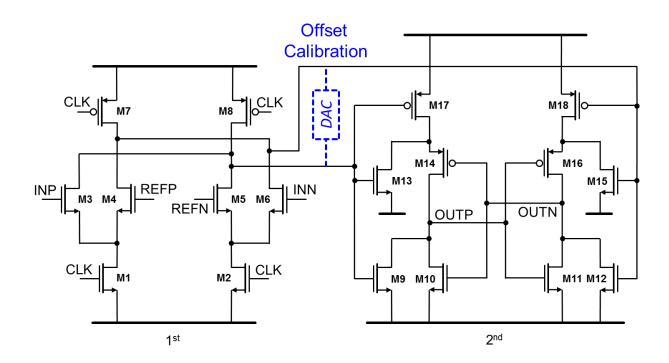

| Figure 26. Comparator of the flash ADC                                 | 37 |

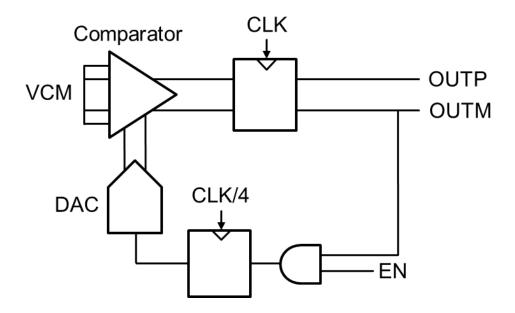

| Figure 27. Comparator input offset calibration                         | 38 |

| Figure 28. Clock delay controller                                      | 39 |

| Figure 29. Effect of clock path mismatch                               | 40 |

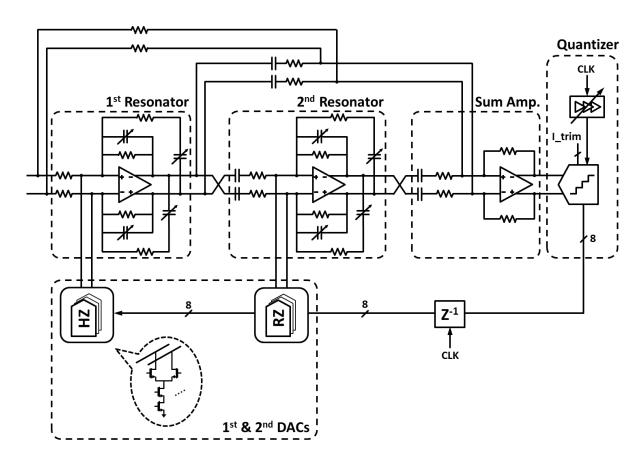

| Figure 30. System implementation                                       | 41 |

| Figure 31. Die micrograph of the prototype                             | 42 |

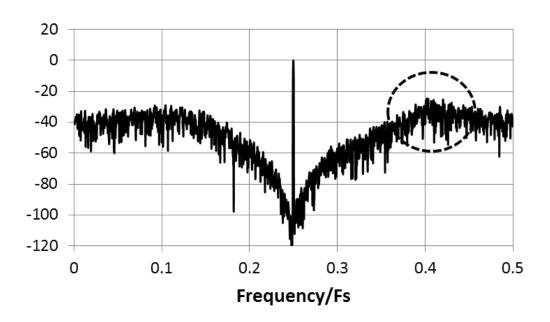

| Figure 32. Power spectral density                                      | 43 |

| Figure 33. Dynamic range                                               | 44 |

| Figure 34. Power spectral density with two-tone inputs                 | 44 |

| Figure 35. Power consumption details                                   | 46 |

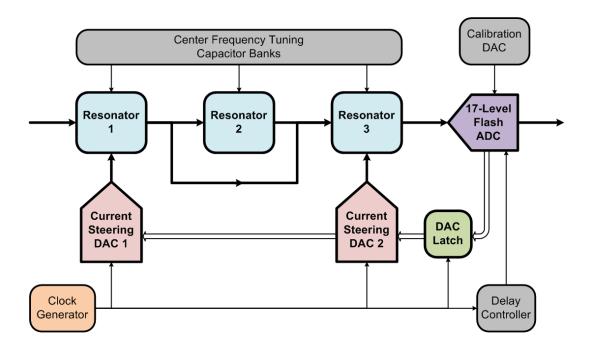

| Figure 36. System block diagram                                        | 49 |

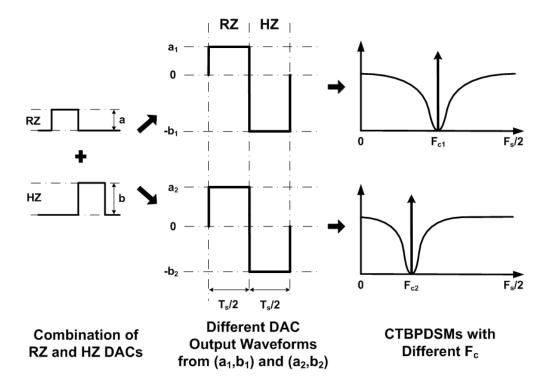

| Figure 37. Center frequency tuning with RZ and HZ DACs                 | 51 |

| Figure 38. Replacement of two DACs with one duty-cycle-controlled DAC  | 54 |

|------------------------------------------------------------------------|----|

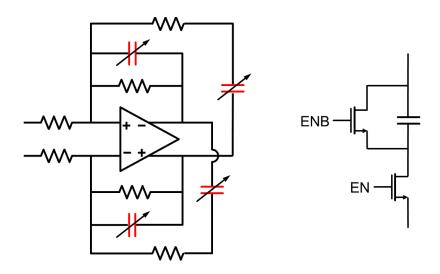

| Figure 39. Multi-stage amplifier with gm-C compensation                | 58 |

| Figure 40. Gain and phase response of the amplifier                    | 59 |

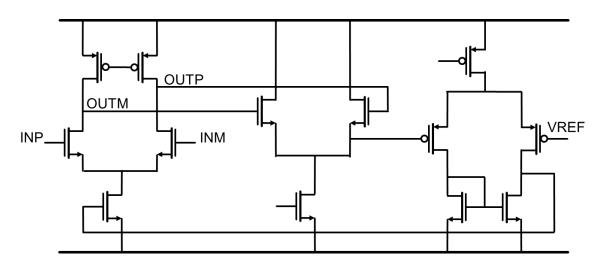

| Figure 41. First stage of the amplifier with CMFB                      | 60 |

| Figure 42. Triple-cascode PMOS DAC and counterpart NMOS current source | 61 |

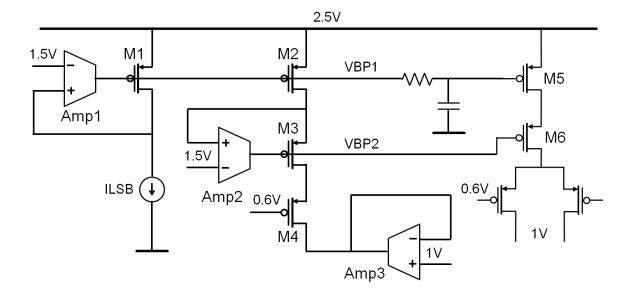

| Figure 43. DAC bias circuit                                            | 62 |

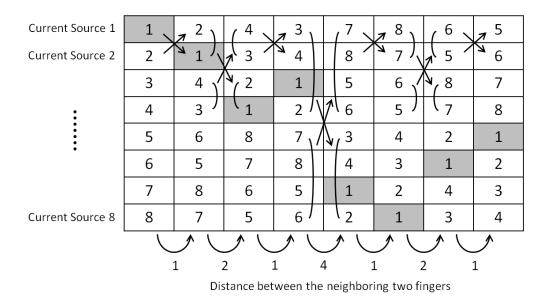

| Figure 44. Layout of the DAC current sources                           | 64 |

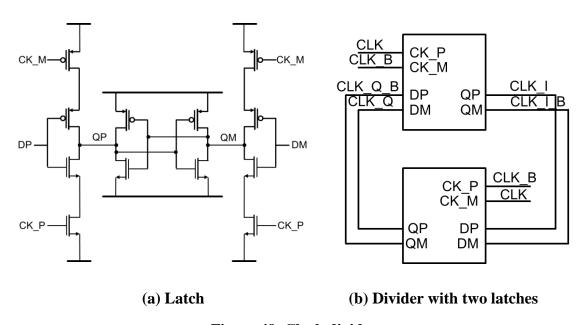

| Figure 45. DAC latch with duty cycle control                           | 65 |

| Figure 46. Level shifter                                               | 66 |

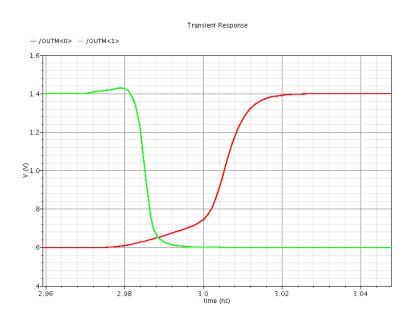

| Figure 47. Level shifter output waveform                               | 67 |

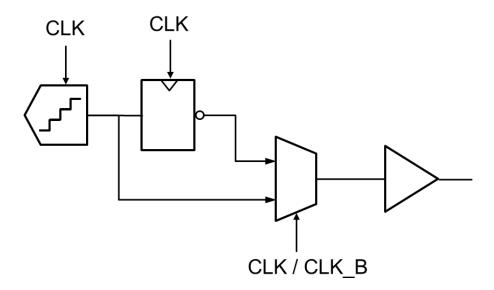

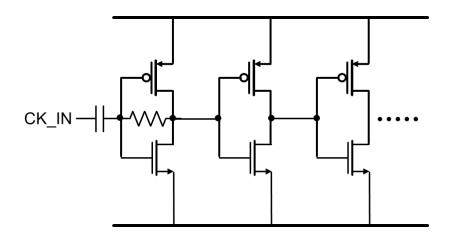

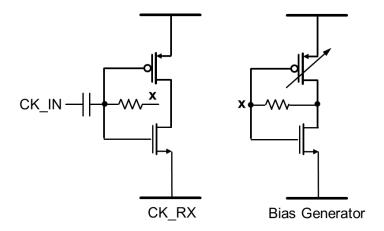

| Figure 48. Clock receiver                                              | 68 |

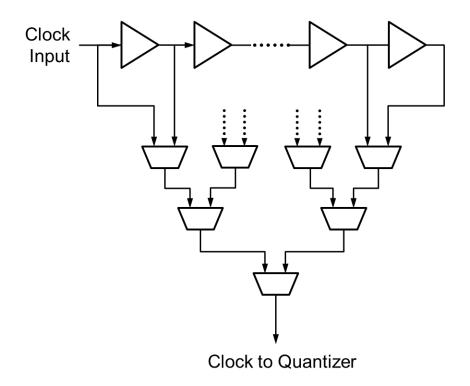

| Figure 49. Clock divider                                               | 68 |

| Figure 50. Clock receiver bias circuit                                 | 69 |

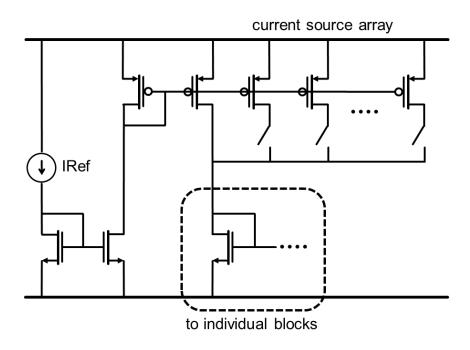

| Figure 51. Global bias circuit                                         | 70 |

| Figure 52. System implementation                                       | 71 |

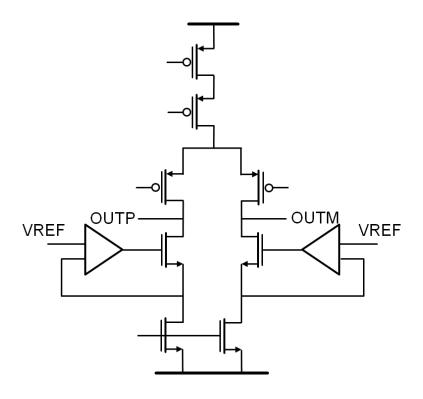

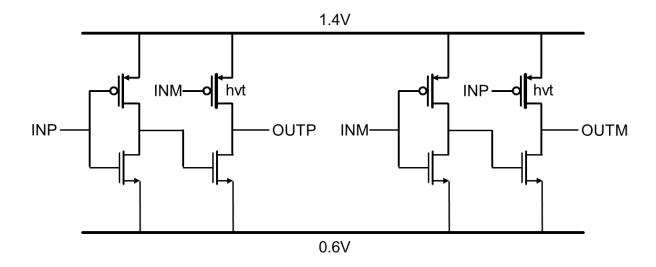

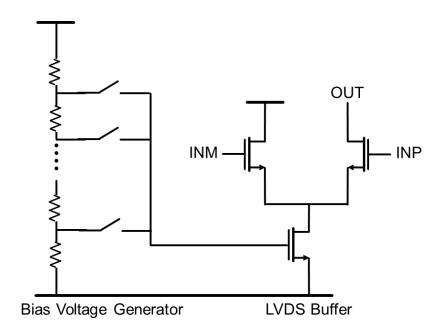

| Figure 53. LVDS buffer for output                                      | 72 |

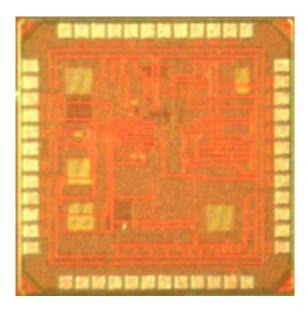

| Figure 54. Die micrograph                                              | 73 |

| Figure 55. Power spectral density                                      | 75 |

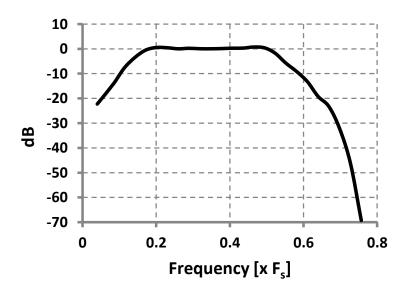

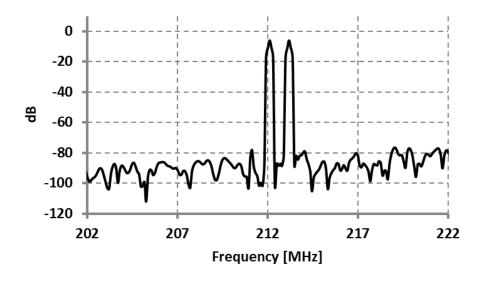

| Figure 56. Measured signal transfer function                           | 75 |

| Figure 57. Power spectral density with a two-tone input     | 76 |

|-------------------------------------------------------------|----|

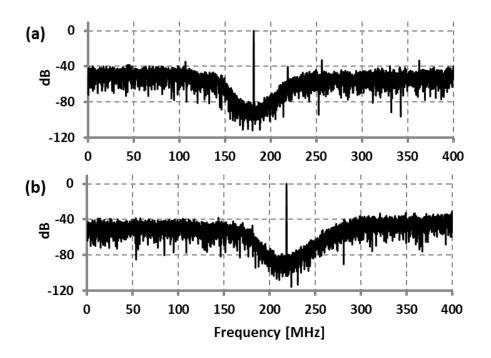

| Figure 58. Different center frequency (a) 180MHz (b) 220MHz | 77 |

| Figure 59. Power consumption details                        | 77 |

## LIST OF TABLES

| Table 1. Supply voltage and power consumption by blocks | 45 |

|---------------------------------------------------------|----|

| Table 2. Performance summary                            | 46 |

| Table 3. State of the arts                              | 47 |

| Table 4. Target spec of the new prototype               | 49 |

| Table 5. Supply voltage and power consumption by blocks | 78 |

| Table 6. Performance summary                            | 79 |

| Table 7. State of the arts                              | 80 |

#### LIST OF ABBREVIATIONS

ADC Analog-to-digital converter

BPDSM Bandpass delta-sigma modulator

BPF Bandpass filter

CTBPDSM Continuous-time bandpass delta-sigma modulator

CTDSM Continuous-time delta-sigma modulator

CTLPDSM Continuous-time lowpass delta-sigma modulator

DAC Digital-to-analog converter

DEM Dynamic element matching

DSM Delta-sigma modulator

DSP Digital signal process

DTBPDSM Discrete-time bandpass delta-sigma modulator

DTDSM Discrete-time delta-sigma modulator

FOM Figure of merit

HPF Highpass filter

HZ Half-clock-delayed return-to-zero

LPF Lowpass filter

LVDS Low voltage differential swing

NRZ None-return-to-zero

NTF Noise transfer function

RZ Return-to-zero

SDR Software defined radio

SNDR Signal to noise and distortion ratio

SNR Signal to noise ratio

STF Signal transfer function

## **Abstract**

Low power techniques for continuous-time bandpass delta-sigma modulators (CTBPDSMs) are introduced. First, a 800MS/s low power 4<sup>th</sup>-order CTBPDSM with 24MHz bandwidth at 200MHz IF is presented. A novel power-efficient resonator with a single amplifier is used in the loopfilter. A single op-amp resonator makes use of positive feedback to increase the quality factor. Also, a new 4<sup>th</sup>-order architecture is introduced for system simplicity and low power. Low power consumption and a simple modulator structure are achieved by reducing the number of feedback DACs. This modulator achieves 58dB SNDR, and the total power consumption is 12mW.

Second, a 6<sup>th</sup>-order CTBPDSM with duty cycle controlled DACs is presented. This prototype introduces new architecture for low power consumption and other important features. Duty cycle control enables the use of a single DAC per resonator without degrading the signal transfer function (STF), and helps to lower power consumption, low area, and thermal noise. This ADC provides input signal filtering, and increases the dynamic range by reducing the peaking in the STF. Furthermore, the center frequency is tunable so that the CTBPDSM is more useful in the receiver. The prototype second modulator achieves 69dB SNDR, and consumes 35mW, demonstrating the best FoM of 320fJ/conv.-step for CTBPDSMs using active resonators.

The techniques introduced in this research help CTBPDSMs have good power efficiency compared with the other kinds of ADCs, and make the implement of a software-defined radio

| architecture easie | r which is approp | riate for the future | e multiple standard | radio receivers | without a |

|--------------------|-------------------|----------------------|---------------------|-----------------|-----------|

| power penalty.     |                   |                      |                     |                 |           |

## **Chapter 1. Introduction**

#### 1.1 Software Defined Radio (SDR)

Our daily lives depend on the mobile devices such as cellphones and tablets more than ever as these devices are absorbing the features of other individual wireless devices. This means that mobile devices need to utilize several RF transceiver chips with different RF frequencies and bandwidths. Having more ICs on the board tends to increase the power consumption of mobile devices, and hence also increases the battery size. Therefore, a single receiver that supports multiple standards is very attractive for wireless communication since low power and small size are essential for handheld devices. The RF front-end not only has to be reconfigurable but also has to have wide bandwidth. However, most current wireless receivers rely on several inflexible analog blocks and at most support only a few standards.

One of the most popular receiver architectures is the super-heterodyne architecture, shown in Figure 1. This architecture is very good for frequency selectivity and sensitivity in an environment with strong interferers[1]. However, this architecture suffers from the complexity of receiver chain and the lack of reconfigurability. It also requires several stages of filtering,

Figure 1. Super-heterodyne Receiver Architecture

mixing and amplification, which leads to a large area and high cost. In addition, the power consumption increases as more blocks are needed in the receiver. Furthermore some of the blocks such as SAW filters are off-chip, and this increases a board area needed.

A software-defined radio (SDR) is a good choice for future receivers. SDR is not a new concept, and was introduced in the 1980s[2]. However, SDR is currently used mainly for military applications which require flexible wireless communication for to a variety of protocols. Also, SDR can help enable cognitive radio, where the receiver is configured depending on the current usage of the channels to utilize the limited bandwidth efficiently[3].

Figure 2. Software-defined radio

Currently, SDR is not practical due to the difficulties of implementation and the large power consumption[4]. Thanks to recent improvements in analog-to-digital converters (ADCs) and to the scaling of technology, SDR is again being strongly considered. As in Figure 2, an SDR omits many blocks in the super-heterodyne architecture by digitizing a wide band signal without down-converting to the baseband. Once the ADC passes the digitized signal to the digital signal processor (DSP), the DSP takes care of filtering, channel selection and mixing in the digital domain[5][6]. In most cases, digital processing costs less in terms of area and power because it is

not affected by thermal noise and mismatch, and therefore if the performance of the ADC can be addressed then SDR architecture is attractive for future mobile devices.

#### 1.2 $\Delta\Sigma$ Modulators (DSM)

#### 1.2.1 Oversampling ADC

ADCs convert analog inputs to digital signals based on sampling. Microprocessors are designed to process digital signals but every real signal exists in the analog domain[7]. Therefore, it is necessary to convert analog signals into the digital equivalents to make use of computing systems and to process data effectively. The quality of A-D conversion is very important in order not to lose the original information during the conversion, and it is mostly related with the resolution of the ADC. Due to the truncation, quantization noise is added to the original signal. This truncation error or quantization noise usually behaves like white noise. The quantization noise decreases the quality of the original signal by decreasing the signal-to-noise ratio (SNR). It is known that the fundamental limit of SNR in dB when one sample has 2<sup>N</sup> possible levels which are evenly spaced is:

$$SNR = 6.02N + 1.76 \text{ [dB]}$$

This assumes that the quantization noise is uniformly distributed between the levels[8][9]. The quantization noise is summed up between DC and  $F_{s/2}$  which is the highest frequency in discrete-time domain.  $F_{s/2}$  is called Nyquist-rate. Nyquist-rate ADCs convert signals with frequencies up to Nyquist-rate and the quantization noise floor is flat in terms of the output power spectral density.

However, Nyquist-rate ADCs have shown limitations as technology develops and struggle to meet the requirements of high speed and high resolution for many applications. For Nyquist-rate ADCs, it is difficult to have both high speed and high resolution due to analog component imperfections[10][11]. For example, the mismatch between the passive components such as capacitors in SAR ADCs causes harmonics and distorts the signal. As CMOS technology scales, it gets more difficult to have good matching between components and the maximum resolution is becoming saturated[12].

Instead, an oversampling ADC improves resolution by increasing the sampling rate instead of increasing the number of sampled levels[13]. The higher sampling rate can cause more power consumption, but oversampling easily achieves high resolution. Thanks to the scaling of CMOS technology, high speed sampling is more feasible and oversampling ADCs are becoming attractive in many applications.

Figure 3.  $\Delta\Sigma$  ADC

A  $\Delta\Sigma$  modulator is commonly used in oversampling ADCs, and it cancels out the error coming from the analog component imperfections with the help of excessive sampling and

feedback loops[14]. The basic configuration is a feedback loop with filters, a local low-resolution ADC and feedback digital-to-analog converter (DAC) as shown in Figure 3. The transfer function from the input X to the output Y is called signal transfer function (STF), and the transfer function from the quantization noise E to the output Y is noise transfer function (NTF). Both STF and NTF are determined by the loop transfer function, but they differ since the summing nodes are different. Through the feedback loop, the quantization noise e(n) is reduced by e(n-1), which is the quantization noise from the previous sample. This makes the NTF highpass, and causes the quantization noise distribution over frequency to be non-uniform. In other words, the feedback loop generates a notch at DC in the NTF and shapes the quantization noise, decreasing the in-band noise floor level as in Figure 4. The STF is not affected by this noise shaping since STF and NTF are different as mentioned and STF can be flat in-band with appropriate loop configurations. A high SNR can be achieved by considering the signal and the noise only in a specific frequency range where the noise floor level is lowered through noise shaping.

Figure 4. STF and NTF of  $\Delta\Sigma$  modulators

The advantage of  $\Delta\Sigma$  modulators is their immunity to the analog component imperfections which is a problem even in modern CMOS technology[15]. For example, a coarse ADC can be used because the imperfections of the coarse ADC are also frequency-shaped by the same feedback loop as the quantization noise, and therefore do not affect the SNR. Also, the input offset of the filters are dithered out by a large amount of sampling and averaging. Recent development in  $\Delta\Sigma$  modulators has lead to high resolution, wide bandwidth and good power efficiency, so  $\Delta\Sigma$  modulators are becoming more important in wireless systems[16]-[20].

#### 1.2.2 Discrete-time $\Delta\Sigma$ Modulator

The first time  $\Delta\Sigma$  modulators were implemented in the discrete-time domain by using switched-capacitor circuits in standard CMOS technology[21]. The system is represented in z-domain, so the analysis of pole-zero in the STF and NTF is apparent as in the example in Figure 5. Therefore, fine tuning is possible even in a higher order modulator since every block can be expressed with linear model.

Figure 5. 1<sup>st</sup>-order discrete-time  $\Delta\Sigma$  modulator

While a discrete-time  $\Delta\Sigma$  modulator (DTDSM) is suited to optimization[22], the circuit implementation brings up some problems. Although the use of switched-capacitors can easily

map the transfer functions to circuits, switched-capacitors are very slow due to the required settling time[23]. The settling error at the frontend of the modulator causes nonlinearity and decreases SNDR (signal-to-noise and distortion ratio)[24]. Also, switched-capacitor circuits have issues such as charge injection and clock feed-through and require a very accurate sample-and-hold circuit at the front. Therefore, although they provide high resolution, DTDSMs are not appropriate for high speed applications.

#### 1.2.3 Continuous-time $\Delta\Sigma$ Modulator

Figure 6. 1<sup>st</sup>-order continuous-time  $\Delta\Sigma$  modulator

A continuous-time  $\Delta\Sigma$  modulator (CTDSM) uses continuous-time analog filters instead of switched capacitors as in Figure 6. For example, an active RC integrator can be used in the place of the discrete-time integrator which is based on the feedback with a delay. The sampling occurs only at the local ADC, and the sampling error is not critical as mentioned in 1.2.1. The use of continuous-time analog filters allows the modulator to operate at higher frequency and have a wider bandwidth since the filter does not need to settle within the clock period[25]. Also, the power consumption is lower[26] compared to discrete-time counterparts, since the switching circuitry requires a lot of power. Another important advantage is the intrinsic anti-alias filtering,

which is important because it makes the anti-alias filter at the input of the ADC unnecessary, saving power and area[27].

However, the CTDSM architecture has two critical drawbacks, namely, excess loop delay[28] and high clock jitter sensitivity[29]-[31]. The excess loop delay is the delay from the quantizer output to the output of DACs, and causes the loop to be instable. The problem is that it is impossible to totally remove the excess loop delay in a continuous-time system. And clock jitter varies the charge amount from the DAC to the filter. The change in the charge amount appears as input noise, and decreases SNR. The effect of clock jitter becomes severe as the sampling frequency goes higher. However, these problems are becoming easier to tackle with scaling and the use of new CTDSM architectures[32][33]. Therefore, CTDSMs are becoming more attractive than DTDSMs for mobile environment because of the high speed and good power efficiency.

#### 1.2.4 Bandpass $\Delta\Sigma$ Modulator

Figure 7. Bandpass  $\Delta\Sigma$  modulator

The DSMs explained previously are lowpass modulators which use integrators in the loopfilter. Lowpass modulators have notches around DC in the NTF, thus the signal band is located at low frequency as in Figure 4. By using another kind of filters in the loopfilter, it is

possible to modify the STF and NTF to provide different noise shaping to that of lowpass modulator. The use of a resonator in the loopfilter leads to the bandpass  $\Delta\Sigma$  modulator (BPDSM) in Figure 7, which has notches in the NTF at a mid or high frequency region[34][35]. This means that the noise shaping lowers the noise floor level at RF or IF as shown in Figure 8. Accordingly, the signal band can be at RF or IF, and in this way it becomes possible to digitize the signal directly without down-converting when the signals are transmitted with modulation[36].

Figure 8. NTF of bandpass  $\Delta\Sigma$  modulator

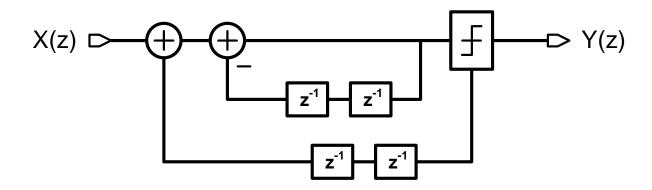

We can easily get the transfer function for discrete-time bandpass  $\Delta\Sigma$  modulators (DTBPDSMs) by replacing z with  $-z^2$  in the discrete-time transfer function of LPDSMs[37], as in Figure 9. The discrete-time resonator consists of two-delay block in the feedback path. The continuous-time resonator can be an LC resonator or a bi-quadratic resonator, but the feedback DAC topology requires some modification since the continuous-time resonator is not mapped to the discrete-time transfer function correctly[38]-[40].

Figure 9. Discrete-time bandpass  $\Delta\Sigma$  modulator

## 1.3 Continuous-time Bandpass $\Delta\Sigma$ Modulator (CTBPDSM)

#### 1.3.1 CTBPDSM in SDR

The bottleneck in the realization of SDR is the design of an ADC with wide bandwidth, high resolution, and reasonable power consumption[4]. The use of Nyquist-rate ADCs is not a good solution, since it is difficult to achieve a very high sampling rate at high resolution because of component mismatches and power consumption[41]. Furthermore there is no channel selectivity with a Nyquist ADC since it digitizes the entire spectrum below the Nyquist frequency. A continuous-time lowpass  $\Delta\Sigma$  modulator (CTLPDSM) is better in terms of power efficiency, but its lowpass nature is not appropriate for SDR. On the other hand a CTBPDSM has features that make it very attractive for SDR. A CTBPDSM digitizes RF or IF signals directly, and the frequency band can be tuned in some architectures [42].

Figure 10. Power efficiency of CTLPDSMs vs. CTBPDSMs

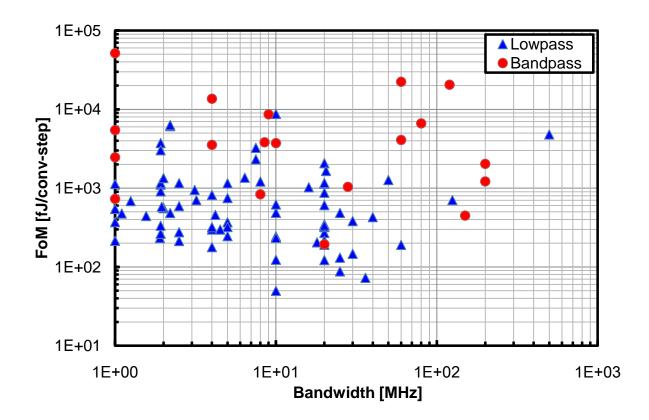

Although noise shaping enables high resolution, CTBPDSMs still consume a lot of power. Continuous-time operation helps achieve good power efficiency, however state-of-the-art CTBPDSMs show worse energy efficiency compared to other kinds of ADCs. The poor energy efficiency of CTBPDSMs limits their use in receivers.

CTLPDSMs are dominant in many applications due to their performance and simplicity as well as power efficiency. Figure 10 compares the power efficiency of recently published lowpass and bandpass  $\Delta\Sigma$  modulators[43]-[56]. There is a big difference between the best figure-of-merit (FoM) for CTLPDSMs and CTBPDSMs. While the CTLPDSM architecture is not suitable for SDR because it cannot digitize signals at RF or IF, it is very power-efficient and is an attractive ADC architecture for the complex super-heterodyne architecture. However, CTBPDSMs still

have enormous potential considering that the SDR architecture is more desirable for the future wireless communication systems.

#### 1.3.2 Conventional CTBPDSM Architectures

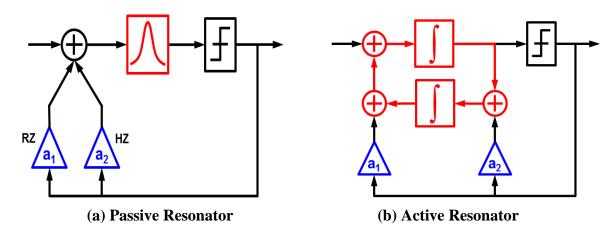

Figure 11. Conventional CTBPDSM architectures

An LC tank resonator can be used as the filter in a CTBPDSM[57]. Figure 11(a) shows the conventional CTBPDSM architecture using an LC tank resonator[58]. It requires two DACs per resonator. These DACs are a return-to-zero (RZ) DAC and a half-clock-delayed return-to-zero (HZ) DAC. Two kinds of DACs with different phases are used in the feedback loop to map the discrete-time transfer function to the continuous-time transfer function correctly regardless of the reduced number of summing nodes.

For example, in second-order modulation, the discrete-time loop transfer function of the modulator is:

$$\frac{z^{-2}}{1+z^{-2}}\tag{1}$$

The transfer function of a continuous-time resonator is expressed as:

$$\frac{s\omega}{s^2 + \omega^2} \tag{2}$$

and the impulse response of the resonator is:

$$h(n) = \begin{cases} 0 & n = 0,1\\ \cos\left(\frac{(n-2)\pi}{2}\right) & n = 2,3,... \end{cases}$$

(3)

An RZ DAC has a transfer function in the continuous-time domain of:

$$\frac{1 - e^{-sT_S/2}}{s} \tag{4}$$

Then, the loop transfer function coming from the resonator and the RZ DAC can be transformed into a discrete-time form by sampling the impulse response with  $F_s$ .

$$T_{res} \times T_{RZ} = \frac{z^{-1}((1 - 1/\sqrt{2}) - 1/\sqrt{2}z^{-1})}{1 + z^{-2}}$$

(5)

$$T_{res} \times T_{HZ} = \frac{z^{-1} (1/\sqrt{2} - (1 - 1/\sqrt{2})z^{-1})}{1 + z^{-2}}$$

(6)

(5) and (6) are the sampled loop transfer function using RZ DAC and HZ DAC, respectively. The goal is to get (1), and this can be achieved by a linear combination of (5) and (6). Therefore, the perfect mapping from the discrete-time domain to the continuous-time domain is possible thanks to the use of two DACs with different phases.

The main advantages of this architecture are low power, low noise and the high quality factor of the resonator. However, this approach requires two feedback DACs per resonator, and this increases both the silicon area and the overall power consumption. In contrast there is one feedback DAC per integrator in a CTLPDSM. Also, the chip is large due to the size of the inductors and the inductors do not get smaller as the technology scales.

A bi-quadratic resonator can be used instead of LC tank resonators[59][60]. A bi-quadratic resonator consists of two integrators in a loop. A bi-quadratic resonator provides two summing

nodes, which allows a different CTBPDSM architecture as shown in Figure 11(b). This architecture is from the direct mapping from a discrete-time transfer function to a continuous-time transfer function since both need two integrators to implement a resonator. Two feedback DACs are connected to each summing node, and these are both non-return-to-zero (NRZ) DACs. The use of an active resonator avoids large inductors, but each integrator uses an op-amp which is power hungry and contributes thermal noise to the modulator.

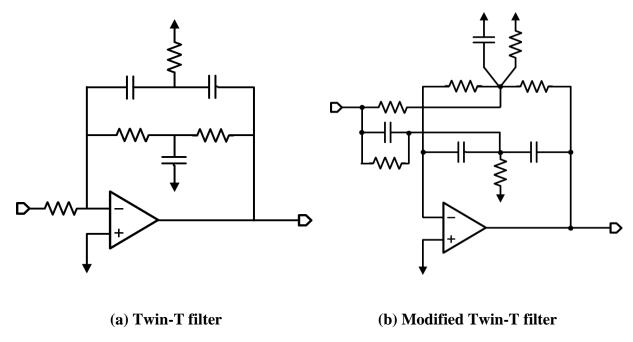

### 1.4 Single Op-amp Resonator

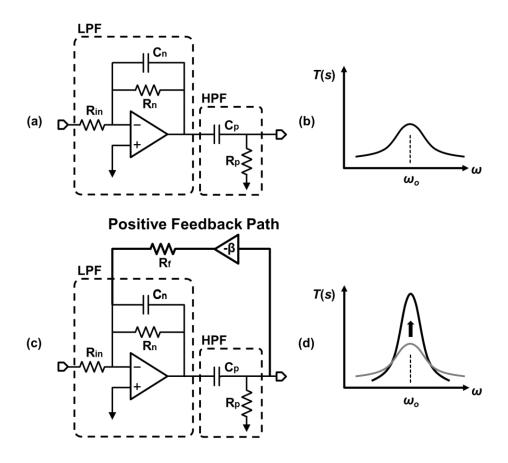

Figure 12. Single op-amp resonators

A single op-amp resonator can replace conventional resonators in CTBPDSMs, and achieve both low power consumption and small silicon area. In this way, only one op-amp generates thermal noise into the loop, so that the total noise is lower. This means lower power consumption for a given noise requirement. Also, the use of a single op-amp makes the chip design easier due

to the reduced number of components and reduced silicon area.

Several single op-amp resonators have been reported[61][62]. The twin-T filter in Figure 12(a)

has two feedbacks which cause resonance, but this filter is not suitable for CTBPDSMs because

the transfer function is different to that of an ideal resonator. It resonates at a certain frequency,

but it does not filter the low frequency perfectly. The modified twin-T filter in Figure 12(b) is

based on the twin-T filter, and the transfer function is improved and also flexible. However, the

input stage is not purely resistive, and it is difficult to be integrated with current-mode DACs

because the summing nodes for the two feedback DACs see a different transfer function to the

inputs. Also, this resonator has many passive components that contribute to the total thermal

noise. Therefore, a new single op-amp resonator with an appropriate transfer function and

summing nodes, as well as fewer passive components, is the key for low power CTBPDSMs.

1.5 **Application Specifications**

The target of this research is to design a CTBPDSM modulator which can cover the following

standards:

• UMTS (US): 5MHz @ 2100MHz with 12b

• CDMA2000 (Europe): 1.25MHz @ 2100MHz with 13b

• 802.11b/g : 22MHz @ 2400MHz with 6b

The carrier frequencies of these three standards are close to each other, and a receiver with a

tunable CTBPDSM can be reconfigured for them without standard-specific analog components.

15

The prototype does not include the LNA and mixer, and the modulator converts input signals at 200MHz with 24MHz bandwidth and 10bit (1<sup>st</sup> prototype) or 12bit (2<sup>nd</sup> prototype) resolution. This modulator specification is enough for the standards above, and it can also support more standards between 2GHz-2.4GHz.

#### 1.6 Research Contributions

A single op-amp resonator with positive feedback is used for lower power consumption and area. This new single op-amp resonator can replace the existing resonators which have either large area or high power consumption.

Also, new CTBPDSM architectures are presented; one reduces the number of feedback DACs and achieves good power efficiency, while the other uses duty-cycle-controlled DACs for low power consumption and other features. The duty cycle control enables the modulator to have frequency tuning and to bandpass-filter input signal. And the redesign of op-amps and DACs provides the latter architecture 11dB more SNDR in the test compared with the first one by reducing the noise from the circuits.

#### 1.7 Research Overview

By improving the power efficiency of CTBPDSMs to that of CTLPDSMs, SDR can be made practical receiver architecture for mobile platforms. The goal of this research is to reduce the power consumption of CTBPDSMs by adopting a new architecture and a new single op-amp resonator. In Chapter 2, a new CTBPDSM architecture, which minimizes the number of

components in the feedback loop, is introduced. This architecture lowers the total power consumption and the silicon area. Also, the circuitry for each block, including the new single opamp resonator, is explained. Chapter 2 also presents the evaluation results of the CTBPDSM prototype. Chapter 3 introduces an improved prototype with a higher-order CTBPDSM architecture and better performance. This chapter also describes new blocks that improve the noise and linearity performance of the modulator, and presents measurement results. Chapter 4 suggests future work and Chapter 5 summarizes the research contributions.

# Chapter 2. CTBPDSM with a Reduced Number of DACs and Single Op-amp Resonators

## 2.1 System Architecture

Figure 13. System block diagram

#### 2.1.1 Overview

The modulator performance mostly depends on the modulator architecture. There are many factors for the architecture such as the modulation order, the quantizer bit number, and the feedback or feedforward topology. Therefore, the architecture design is important to achieve the required performance with the best power efficiency. This new CTBPDSM has a 4<sup>th</sup>-order architecture with 3bit quantization as shown in Figure 13. Two resonators and two DACs are

used to achieve 4<sup>th</sup>-order bandpass noise shaping. Both resonators are single op-amp resonators and capacitor banks tune both the resonant frequencies and the quality factor. As discussed in the next section (2.1.2), the modulator has two DACs instead of four DACs. The DACs are both current-steering DACs. *DAC1* connected to *Resonator 1* is a half-clock-delayed return-to-zero (HZ) DAC while *DAC2* connected to *Resonator 2* is a return-to-zero (RZ) DAC. *Resonator 1* and *DAC1* are more critical in regards to noise performance. The summing amplifier sums the output of *Resonator 2* and the feedforward paths (which are the modulator input) and the *Resonator 1* output. A 9-level flash ADC quantizes the output of the summing amplifier. An auxiliary current DAC, dedicated to the flash ADC, calibrates the offset of the comparators. The clock generator receives a sine wave from off-chip and generates a square clock waveform appropriate for this modulator. To compensate for the clock timing difference between the DACs and the flash ADC, a clock delay controller is used to clock the flash ADC.

#### 2.1.2 Reduction of the number of current-mode DACs

As discussed in 2.2.1, we use a single op-amp resonator as the resonator in this CTBPDSM. This single-opamp resonator has only one summing node for the feedback loop paths. As with LC resonators in other CTBPDSMs, which similarly present only one summing node, this motivates the use of a multi-path feedback design for the modulator shown in Figure 14(a), which perfectly transforms a DTBPDSM into a CTBPDSM with LC resonators. However, the use of multiple feedback paths per resonator increases static power and adds more noise to the first resonator. Adding feedforward paths can replace the feedback DACs since it leads to the same loop transfer function as when only feedback paths exist[63]. Therefore, a feedforward path from the first resonator output to the quantizer removes two feedback DACs in a 4<sup>th</sup>-order

CTBPDSM, but even with a feedforward path, the two DACs at the front of the modulator remain the same and still add noise to the first resonator input which is critical to the total modulator input referred noise. In this work, a different analysis of a multi-path feedback design leads to noise reduction as well as power consumption reduction by using only one feedback DAC per resonator along with signal feedforward paths around the resonators.

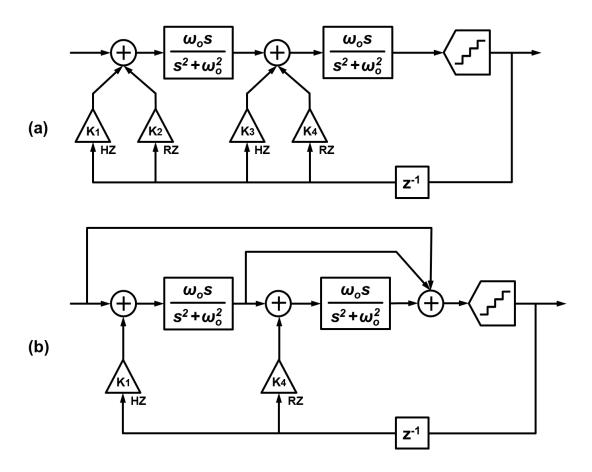

$Figure~14.~4^{th}\hbox{-}order~CTBPDSM~architecture~(a)~conventional~(b)~simplified$

Due to the delay block and the excess loop delay a classic discrete-time to continuous-time pole-zero mapping to synthesize a continuous-time transfer function from a discrete-time transfer function is not easy and the final pole-zero needs to be tweaked after the transformation[64]. Also, imperfections of system blocks, including the finite quality factor of the resonators, make

the tweaking necessary. Therefore the use of ideal modulator coefficients might not lead to optimal performance in a real system. However, this characteristic also provides the possibility for the modulator coefficients to be flexible to some degree. Even though one of the feedback coefficients varies slightly due to any analog imperfections, a small change of the other coefficients can compensate for this to keep the stability and the performance. With the original coefficients of the two DACs connected to the first resonator (Figure 14(a)),  $K_2$  is much smaller than  $K_1$  when the coefficients are calculated as in [58] and optimized for 3bit quantization. And the result of the removal of  $K_2$  does not lead to instability, but it causes peaking in the NTF and degrades the SNDR. However, the original value of  $K_2$  is small, and  $K_1$ ,  $K_{3-4}$  can be tuned to compensate for the nulling of  $K_2$ . Suitable tuning of  $K_1$ ,  $K_{3-4}$  removes the NTF peaking and provides essentially the same noise shaping as with a non-zero  $K_2$ . The only difference is the symmetry of the overall power spectral density centered at the quarter of the sampling frequency: zeroing  $K_2$  makes the slopes of the NTF on the left and right side of the center frequency slightly different, as shown in Figure 15. However this asymmetry does not affect the noise shaping within the passband and the performance in the in-band, including the maximum SNDR, is the same. The key point is that  $K_2 < K_1$  allows removal of  $K_2$ . On the other hand, removing  $K_1$ instead of K2 is difficult since in this case coefficients' sensitivity introduces instability and performance degradation.

Similarly,  $K_3$  or  $K_4$  cannot be nulled once  $K_2$  is zeroed or two other coefficients, instead of three, have to be tuned to compensate, and this leads to a large variation in the coefficients and ultimately to a significant performance degradation. Thus a feedforward path is used to remove another feedback DAC,  $K_3$ . The feedforward path from the first resonator output to the quantizer

provides the same feedback loop represented by one HZ DAC,  $K_3$  and the second resonator because the loop consisting of the first resonator and the feedforward path also contains one HZ DAC and one resonator. Figure 14(b) shows the architecture after the modifications.

Next we show that by using a half-width DAC[66] instead of a NRZ DAC, the NTF in the passband does not change for the architecture introduced here.

Traditionally, an NRZ DAC is represented by a constant coefficient in a z-domain representation of the modulator. But in a continuous-time system, an NRZ pulse with a sampling period of  $T_s$  has a transfer function of

$$(1 - exp(-sT_s))/s \tag{7}$$

At lower frequencies, the exponential term can be approximated as:

$$exp(-sT_s) \approx 1 - sT_s \tag{8}$$

This is because, for a high oversampling ratio,  $sT_s$  is very small in the frequency range of interest. Hence (7) is close to  $T_s$ , leading to a constant value as required. On the other hand, this approximation is not accurate for the passband (e.g. at  $F_s/4$ ) of a bandpass modulator.

Instead, a half-width RZ or HZ pulse represented by

$$(1 - exp(-sT_s/2))/s \tag{9}$$

can be approximated by the exponential term  $exp(-sT_s)$  giving a much better approximation to a constant value within the passband of a bandpass system thanks to the halved exponential term.

$$NTF(s) = \frac{(s^2 + \omega_o^2)^2}{s^4 - c_2 \omega_o s^3 + (2 - c_1)\omega_o^2 s^2 - c_2 \omega_o^3 s + \omega_o^4}$$

(10)

where

$$c_1 = (k_1 + k_2)$$

,  $c_2 = (k_3 + k_4)$  (11)

Equation (10) is the NTF of the 4<sup>th</sup>-order multi-path feedback design in Figure 14(a), and we get the NTF around the center frequency by assuming that the DAC coefficients are constants.

$$NTF(s) = \frac{(s^2 + w_o^2)^2}{s^4 - (k_1 + k_4)w_o s^3 + (2 - k_1)w_o^2 s^2 - (k_1 + k_4)w_o^3 s + w_o^4}$$

(12)

And (12) is the NTF of the new architecture in Figure 14(b) with the same assumption on the DAC coefficients. A key observation about the two NTFs is that they can have the same noise shaping around the center frequency if the coefficients are properly chosen. This is why this new architecture can keep the same SNDR as the conventional CTBPDSMs even though the number of DACs is reduced.

The feedforward path from the input to the quantizer decreases signal swing through the analog signal path[67][68], which is helpful for low power consumption and for the linearity of resonators. As a result, this modulator architecture is advantageous in terms of power, complexity, and silicon area compared to existing architectures.

#### 2.1.3 Noise Transfer Function (NTF)

The sampling frequency of the prototype modulator is 800MHz, and the center frequency is 200MHz. The required bandwidth is 24MHz as specified in the previous chapter, so the OSR is 16.7. Based on a target SNDR of 70dB and this OSR, at least a 4<sup>th</sup>-order architecture with 3bit quantization or a 6<sup>th</sup>-order one with 2bit quantization is required[10]. A 2<sup>nd</sup>-order architecture or an 8<sup>th</sup>-order one is not suitable due to higher power consumption and instability[69]. The 4<sup>th</sup>-order architecture is adopted for this modulator because it is more stable even with analog component mismatches but the total power requirement is similar to the 6<sup>th</sup>-order one.

The two notches generated by the two resonators are located at the same frequency as in Figure 15 and the simulation of this modulator shows 70dB SNDR when the input is a 200MHz tone. The STF is flat because the feedforward paths are used in this architecture[67], but there is still attenuation at higher frequency region for anti-aliasing.

Figure 15. Noise transfer function of the modulator

# 2.2 Circuit Blocks

# 2.2.1 Single Op-Amp Resonator

## 2.2.1.1 Positive Feedback

Figure 16. Quality factor enhancement by positive feedback

In this work, by applying positive feedback[70] to a conventional active filter, a high quality-factor resonator is realized with a single amplifier, replacing the LC or bi-quadratic resonators in a conventional CTBPSDM. We begin with the low-quality-factor single-amplifier bandpass filter (BPF) consisting of a lowpass filter (LPF) and a passive highpass filter (HPF) in series shown in Figure 16(a). The transfer function of this BPF is expressed as:

$$T(s) = k_o \frac{\omega_o s}{s^2 + 2\omega_o s + \omega_o} \tag{13}$$

where

$$\omega_o = 1/R_p C_p R_n C_n$$

(14)

The first-order term in the denominator decides the quality factor, which is very low for this BPF as in Figure 16(b). To enhance the quality factor we add a positive feedback path (Figure 16(c)) to the BPF. The positive feedback path boosts the low quality-factor BPF output, therefore it resonates around the resonant frequency  $\omega_o$  while suppressing the out-of-band signals. The positive feedback path results in the transfer function:

$$T(s) = k_o \frac{\omega_o s}{s^2 + 2 \cdot (1 - \beta) \cdot \omega_o s + \omega_o}$$

(15)

The quality factor of this filter can be increased to the level required for this modulator depending on the feedback gain  $\beta$ . As  $\beta$  approaches 1, the first-order term in the denominator approaches zero and the quality factor goes to infinity making this filter have the same transfer function as that of an ideal 2<sup>nd</sup>-order resonator. However, this requires the positive feedback of -1 (= $\beta$ ) and another resistor  $R_f$ . The HPF outputs are directly fed back to inputs not to add these components. The gain of -1 can be easily realized in the differential mode, and  $R_p$  can replace  $R_f$ .  $R_p$  is located between the resonator output and the ground while  $R_p$  is between the resonator output and the virtual ground node. This similarity enables the replacement and prevents the use of additional resources for the resonator implementation.

A differential mode circuit implementation of the resonator is shown in Figure 17. The feedback gain is fixed to -1, and the resonance condition and quality factor now depend only on passive component values. The transfer function of this circuit is expressed as :

Figure 17. Differential-mode implementation of single op-amp resonator

$$T(s) = k_o ' \frac{\omega_o s}{s^2 + 2 \cdot k \cdot \omega_o s + \omega_o}$$

(16)

where

$$k = R_n C_n + R_p C_p - R_n C_p$$

(17)

$$\omega_o = 1/R_n C_n = 1/R_p C_p \tag{18}$$

The resonance condition of the differential circuit is k=0 from (16). There are innumerable solutions for k=0, and a solution of  $C_p=2C_n$ ,  $R_n=2R_p$  is chosen so that the filter has the best noise performance and the smallest passive area since this solution minimizes the resistors and the capacitors while the resonant frequency is fixed.

The main advantage of this resonator in CTBPDSMs is that it consumes 40% less power compared to the traditional bi-quadratic resonator, which has two amplifiers while keeping the same noise performance. The power and area savings are significant, especially in higher order modulators. The block linearity of this type of resonator may be inferior to a more traditional circuit with negative feedback, but this is significantly mitigated when the resonator is used in a

modulator with a feedforward architecture since the latter reduces the swing where the nonlinearity occurs. That is the case of the modulator presented here.

## 2.2.1.2 Op-Amp

Figure 18. Multi-path amplifier

A high-gain op-amp is required for the resonator to get good linearity and a small error in the resonant frequency. However, it is difficult to use a cascode structure to achieve the required high gain because the supply voltage has become low in advanced CMOS process nodes[71]. A multi-stage amplifier is a good alternative for a continuous-time modulators[72]-[75]. Cascading of individual low gain amplifiers can provide high overall gain and also achieve a sufficient voltage swing even with a low supply voltage. As shown in Figure 18, there are two paths in parallel; one is a high-gain narrow-bandwidth amplification path with four amplifying stages (slow path) while the other is a low-gain high-bandwidth one consisting of a single stage (fast path). The fast path provides the wide bandwidth of the op-amp. At high frequencies, the gain of the fast path, which has a much higher bandwidth than the slow path, dominates because the gain of the slow path falls off at lower frequency. Furthermore, the fast path also helps the stability

compensation. The phase of the fast path dominates the total phase response at high frequency and more phase margin is achieved because this path does not have a cascode structure.

Figure 19. Stage units of the amplifier (a) w/o summing (b) w/ summing

In the multi-stage amplifier described here, each stage is a single common-source amplifier with a current source as the load (Figure 19(a)). Even when the circuit is implemented in a differential manner, there is still a signal headroom of more than half the supply voltage, for a 1.25V supply. The amplifier on the fast path is a single common-source amplifier for fast operation. The technology used in this work is 65nm CMOS, and considering the balance between the speed and the gain, the optimal gain for each stage is estimated to be 15-20dB in simulation. In total, four stages are used to provide enough gain, and the fourth amplifier stage uses a different scheme to sum the fast path and the slow path. As in Figure 19(b), a push-pull structure enables the summing of two paths and each PMOS or NMOS common-source amplifier sees the other as the load. To get a 60 degree phase margin, nested Miller-compensation is used[76]. The total gain and phase margin response of this amplifier is shown in Figure 20. The

DC gain is 73dB and the phase margin is 65 degrees. The gain at 200MHz is 30dB. The total power consumption is 2mW, and half of the power is consumed by the last stage. The first stage consumes one quarter of the total power to achieve a low thermal noise. In addition the input devices are very large for good matching and low input referred noise.

Figure 20. Gain and phase response of the amplifier

### 2.2.1.3 Center Frequency and Quality Factor Tuning

Both the mismatch of the passive components and process variation change the resonant frequency. The resonant frequency of the resonators decides the center frequency of the CTBPDSM, so calibration is required for the passive components to get the exact center frequency. Calibration of the capacitors  $R_p$  and  $R_n$  in the positive and negative feedbacks in Figure 17 enables the calibration of both the center frequency and quality factor. Calibrating only capacitors is enough to correctly set the center frequency. Digitally controlled capacitor

banks[65] are placed in parallel with the main capacitors in Figure 21. The quality factor of this resonator is also related to the capacitances since they decides the first order coefficient in the numerator, therefore fine tuning of the capacitance is required to have a good control on the quality factor. 4bit capacitor banks are used for each capacitor. It is clear that the capacitances are inversely proportional to the center frequency  $\omega_o$  in (18). And from (17),  $C_p$  is proportional to the quality factor while  $C_n$  is the opposite. So the change of each capacitor affects both the center frequency and the quality factor as in Figure 22.

Figure 21. Resonator RC tuning with capacitor banks

The center frequency has to be accurate while the quality factor just needs to be above a certain threshold. So the center frequency is calibrated first, and then the quality factor is adjusted by the two capacitors keeping the same center frequency. A quality factor of 20 is sufficient for the target modulator performance and is used in test, even though a higher Q can be achieved.

And due to the mismatch and process variation or depending on the calibration activity, (17) can have a negative value. This means that the resonator becomes unstable, but this does not lead

to the instability of the modulator because the feedback loop of the delta-sigma modulator cancels out the resonating signal. Therefore, this resonator is robust in the delta-sigma modulator regardless of the calibration accuracy of the quality factor, but has to have a sophisticated calibration method in other systems without the feedback loop.

Figure 22. Quality factor and center frequency tuning

## 2.2.1.4 Resonator Outputs

Although the original resonator outputs are OUT+' and OUT-' in Figure 17 an alternative configuration gives more flexibility and reduces kickback. When this resonator feeds a block with resistive inputs, the time constant of the feedback paths changes and this also changes the resonant frequency and the quality factor. In Figure 23 the amplifier outputs OUT+ and OUT- directly feed the next block through another RC HPF formed by  $R_p$ ' and  $C_p$ '. This HPF does not

affect the feedback around the amplifier and enables the connection with any other blocks with resistive inputs in CTBPDSMs.

The time constant of this HPF is the same as  $R_pC_p$ . This helps reduce kickback and improve flexibility. Kickback from other blocks can be injected to the inputs through the resistor in the original configuration, but the new configuration suppresses it with the help of the HPF. An advantage is that here,  $R_p$ ' which is bigger than  $R_p$  is used to reduce the amplifier's load without affecting the total noise performance. Furthermore, these capacitors are not calibrated since they barely change the resonance characteristic of the feedback loops.

Figure 23. Output node change

### 2.2.2 Current-steering DAC

#### 2.2.2.1 Current Sources

The current-steering DAC is connected to the virtual ground nodes of the resonator, so the output impedance of the DAC has to be very high for good linearity[77]. The triple cascode

structure in Figure 24 provides high output impedance and isolates the current source at the bottom from the switches. Without this isolation, the current source is affected by switching noise and generates a data dependent current output instead of constant one, which causes nonlinearity.

Figure 24. Triple cascode structure for DAC

The thermal noise from the current source is directly injected to the resonator. Due to the switching, the differential mode implementation does not cancel the thermal noise. The thermal noise from the current source in *DAC1* significantly contributes to the total noise[78], thus it has to be minimized so as not to limit the maximum SNDR. On the other hand, flicker noise is filtered by the resonator, so can be ignored. By increasing the overdrive voltage of the current source, the thermal noise can be reduced. However, the headroom for the triple cascode structure is not enough for strong overdrive with a 1.25V supply voltage, and so a certain amount of noise being fed into the modulator is inevitable. In this work, the total voltage headroom for the triple cascode is 750mV and 400mV out of this is assigned to the current source.

The device size is also important for the linearity. Mismatch between the current sources can modulate the output current and introduce nonlinearity, regardless of the resonator performance[79][80]. Dynamic element matching (DEM) can cancel this nonlinearity by shuffling the mismatch, but DEM is complex and increases the power consumption. Here, the target SNDR is met by increasing the device sizes and achieving sufficient matching by design. By using very large devices for the current sources while maintaining the *W/L* ratio, the mismatch is minimized. Monte-Carlo simulations indicate a 0.2% mismatch, which is sufficient for the target performance.

The current source of *DAC2* does not need to be as large as that of *DAC1*. Any nonlinearity caused after the *Resonator1* barely appears at the output. The same is true for the thermal noise, and a large overdrive is not necessary in *DAC2*.

#### 2.2.2.2 DAC Switches

The switching devices change the current direction to the resonator, so they are sized as small as possible for fast switching. This is also helpful in reducing the clock injection to the resonator by decreasing the parasitic capacitance. Also, small switch size reduces the parasitic capacitance at the interface with the resonator, which can affect the feedback gain of the amplifier. The voltage headroom is slightly larger than  $V_{DSAT}$  to give more overdrive to the current source while keeping the switching devices in saturation. With a gate voltage of 900mV, the switching device is turned on and fully saturated, which gives the maximum output impedance. The two switching devices are completely symmetric in the layout since any mismatch can cause nonlinearity[82]. The cascode device is also sized small for fast operation.

#### 2.2.2.3 DAC Latch

Figure 25. Return-to-zero pulse DAC latch

Both the RZ DAC and HZ DAC require a return-to-zero pulse, and both the outputs are zero for half of the clock period. We use an even number of current sources to implement this pulse. The differential-mode current output of the DAC is zero when the same amount of current flows on both sides of the output. There are total eight current sources, and four current sources are directed to each of the differential outputs when the overall differential output returns to zero. Figure 25 shows the bitwise implementation, which is one side of the differential implementation. The mux has two inputs; the comparator output from the quantizer and the pre-decided value '0' or '1' that refers the current direction since '1' turns on the switch and '0' turns off the switch. Four of the eight DAC latches have a pre-decided value of '0', and the others have '1'. The clock controls the mux output, and therefore the mux passes the comparator output for half a clock period and passes the pre-decided value for the other half clock period. While the mux outputs are at the pre-decided values, the current flow on both sides of the DAC output is equal, and this becomes the return-to-zero phase. The mux output drives an inverter which controls the switching devices coming after the inverter. The inverter is supplied with 900mV. The switches

are intended to be in saturation and go into the linear region if the gate voltage goes higher than 900mV. The use of the dedicated supply voltage also helps to set the exact switching timing. If the supply rail becomes noisy because of other digital blocks, the transition timing changes and this is considered as a kind of clock jitter noise[83].

## 2.2.3 Quantizer

#### 2.2.3.1 Comparator

Figure 26. Comparator of the flash ADC

The quantizer is a flash ADC with 8 comparators and generates a 9-level digital output. The comparator is shown in Figure 26, and consists of two stages[81]. When the clock is low, M1-2 are off and M7-8 reset the first stage outputs to high. These first stage outputs also reset the nodes in the second stage, and the comparator outputs go low. When the clock goes high, M7-8 are turned off and M1-2 discharge the first stage output nodes. The discharge speed differs for

both sides depending on the input and reference voltages, and this makes the output voltage different. As both of the first stage outputs go low with a small voltage difference between them, *M17-18* are turned on and *M9*, *M12* are turned off. This makes the second stage a back-to-back latch, and the small voltage difference from the first stage is regenerated by this latch. The comparator outputs are valid only for half a clock period, so there is an SR latch after the comparator to hold the value for the rest half clock period.

## 2.2.3.2 Input Offset Calibration

Figure 27. Comparator input offset calibration

M3 and M6 in Figure 26 are sized minimum to reduce the load of the summing amplifier which drives this quantizer. Large input devices are good for matching and reduce the input offset of the comparator[84], but the summing amplifier has to drive 8 comparators. A big load causes a pole at the output of the summing amplifier and this limits the bandwidth[85]. For this reason, minimum size input devices are used for fast operation, but this causes a large input offset, even with careful layout. An auxiliary current-mode DAC[65] is assigned to each

comparator to calibrate the input offset. This 4bit DAC is between the first stage outputs, and sinks a different amount of current from both sides. Figure 27 shows how this DAC cancels the input offset. During the startup, all inputs and references are tied together and the digital logic slowly varies the DAC current and finds the current value which flips the comparator output. The input offset is compensated by keeping this auxiliary DAC current fixed at this value during normal operation.

## 2.2.3.3 Clock Delay Controller

Figure 28. Clock delay controller

The clock generator has to feed the DACs as well as the quantizer. However, there is a clock path mismatch between these blocks, and more timing difference is caused because the clock receiving devices have different sizes. Also, the summing amplifier is not ideal and causes a slight delay. A clock delay controller compensates all of these mismatches and aligns the

sampling and the current triggering. The clock delay controller in Figure 28 is placed between the clock generator and the quantizer, and consists of a series of buffers and muxes. Each buffer is two inverters in series, and makes a delay of approximately 30ps. The mux selects one of the delayed clocks and sends it to the quantizer. The total tuning range is 210ps with 7 buffers. This block is controlled manually from off-chip. Tuning is based on the measured power spectral density of this modulator. The difference in the clock timing shows up as a noise peak in the power spectral density as in Figure 29.

Figure 29. Effect of clock path mismatch

### 2.2.4 Summing Amplifier

A summing amplifier is necessary before the quantizer to sum the second resonator output and the feedforward paths. Nonlinearity or thermal noise added at this position hardly affects the modulator performance, so the op-amp can have very simple design. A multi-stage amplifier is also used, but without a feedforward path. The amplifier has three stages and no feedforward

path, and Miller-compensation is used. Miller-compensation is sufficient for this three-stage amplifier because the third stage is low gain high swing stage. The open-loop gain of this amplifier is 120, and the phase margin is 50 degree. Resistive feedback is applied to achieve a gain of 1, and the HPF at the output of the resonator is connected to the virtual ground nodes. Large resistors are used for low power consumption, since the thermal noise from these resistors is not significant.

## 2.2.5 System Implementation

Figure 30. System implementation

Figure 30 shows the circuit implementation of the core loop. The first resonator drives the second resonator through an HPF, and the second resonator drives the summing amplifier in the

same way. There are two feedforward paths, and they also consist of HPFs due to the characteristic of the resonator. The current-mode DAC outputs are connected to the virtual ground nodes of the amplifiers. The extra delay coming from the resonators and the summing amplifier is also compensated by the clock delay controller connected to the quantizer.

# 2.3 Prototype Test Results

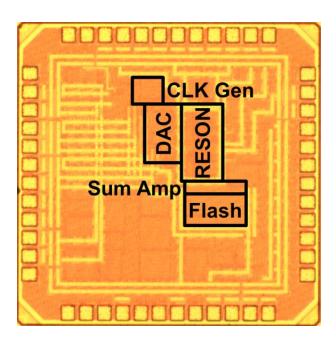

The prototype[86] is fabricated in 65nm CMOS with 9 metal layers and the active die area is 0.2mm<sup>2</sup>. Figure 31 shows the die micrograph. The two resonators take the most of the area due to the passive components. The first DAC occupies most of the DAC block area since the current sources are very large. A 48-pin QFN package is used for this test.

Figure 31. Die micrograph of the prototype

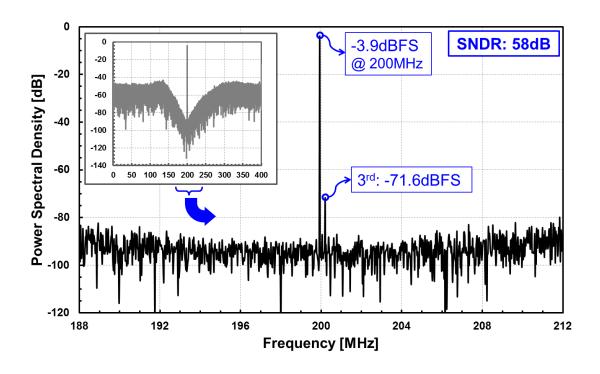

## 2.3.1 Power Spectral Density

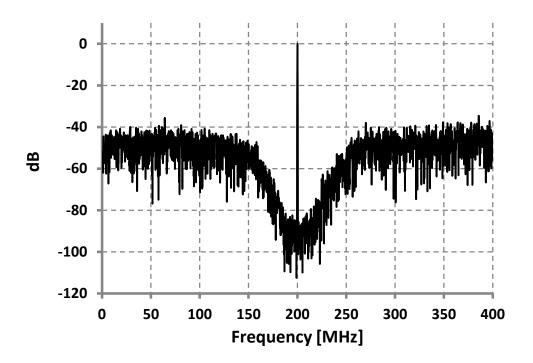

Figure 32 shows the measured power spectral density of this modulator output. The top-left graph shows the entire spectrum from DC to  $F_s/2$ . And the main graph is in-band spectrum over a 24MHz bandwidth. A 200MHz tone with -3.9dBFS amplitude is used as an input, and the measured SNDR of 58dB while operating with 1.25V supply. The third harmonic is next to the fundamental tone because it is folded down from higher frequency. The third harmonic is mainly caused by the amplifier and the DAC nonlinearity, but it is comparable to the in-band noise and does not reduce the SNDR.

Figure 32. Power spectral density

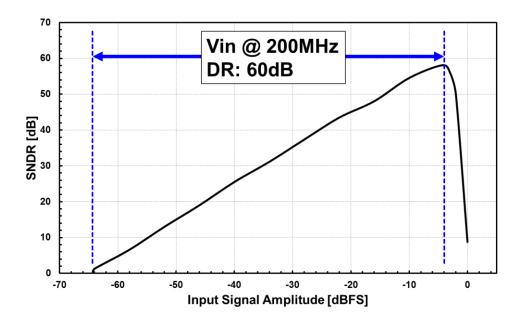

## 2.3.2 Dynamic Range

The dynamic range is also tested with a 200MHz tone, and the minimum detectable signal amplitude is -63.9dBFS. The input amplitude showing the maximum SNDR is -3.9dBFS, and the

dynamic range of this modulator is 60dB as in Figure 33. The dynamic range is limited by the thermal noise from the first resonator and the first DAC.

Figure 33. Dynamic range

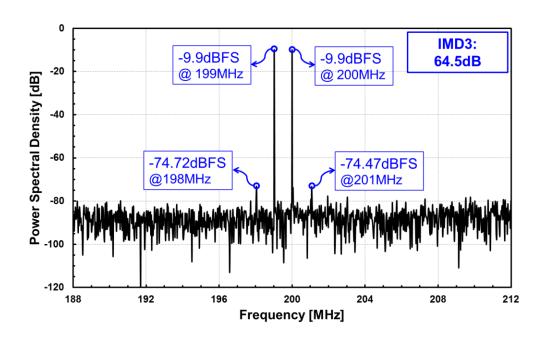

## 2.3.3 Two-tone Test

Figure 34. Power spectral density with two-tone inputs

A two-tone test is done with two tones 1MHz apart, and amplitudes are -9.9dBFS. In Figure 34, the inter-modulated tones are -74.72dBFS and -74.47dBFS, and this indicates a modulator IM3 of 65dB.

### 2.3.4 Power Consumption

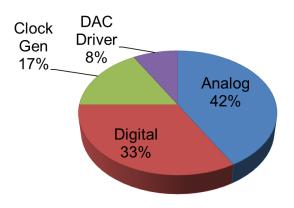

Table 1. Supply voltage and power consumption by blocks

| Analog     | 1.25V | 5mW  |

|------------|-------|------|

| Digital    | 1V    | 4mW  |

| Clock Gen  | 1V    | 2mW  |

| DAC Driver | 0.9V  | 1mW  |

| Total      |       | 12mW |

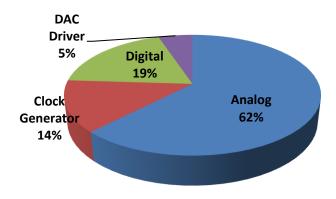

The total power consumption including that of the clock generator is 12mW. Table 1 shows the power consumption of each block. The analog part, including the resonators, the DAC current sources and the summing amplifier, consumes 5mW. A 1.25V supply voltage is used to ensure headroom for the triple cascode structure of the DAC current source. The first resonator consumes 2mW, and the second resonator consumes 1.5mW. The two DACs consume 1mW, and the summing amplifier consumes 0.5mW. The digital part consists of the quantizer and the DAC latch. The DAC latch consumes most of the digital power due to the switching, and the calibration circuits do not consume any power during normal operation. The DAC driver uses 0.9V supply voltage, and consumes 1mW. The clock generator includes the clock delay controller, and consumes 2mW. Figure 35 compares the power consumption of the different blocks in a pie graph.

Figure 35. Power consumption details

# 2.3.5 Performance Summary and State of the Arts

Table 2 shows a performance summary of this prototype. The sampling rate is 800MHz, and the center frequency is 200MHz, which is the quarter of the sampling frequency. The FoM is 385fJ/conversion which to our knowledge is the best for CTBPDSMs using active resonators.

Table 3 compares this work with the state-of-the-art.

**Table 2. Performance summary**

| Sampling Rate    | 800MHz             |  |  |

|------------------|--------------------|--|--|

| Center Frequency | 200MHz             |  |  |

| BW               | 24MHz              |  |  |

| Power            | 12mW               |  |  |

| SNDR             | 58dB               |  |  |

| DR               | 60dB               |  |  |

| IMD3             | 64.5dB             |  |  |

| Area             | 0.2mm <sup>2</sup> |  |  |

| FoM              | 385fJ/conv         |  |  |

Table 3. State of the arts

| Author               | Schreier        | Thandri         | Chalvatzis      | Ryckaert        | Lu              | This work       |

|----------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| Publication          | JSSC 2006       | JSSC 2007       | JSSC 2007       | JSSC 2009       | JSSC 2010       |                 |

| Order                | 4 <sup>th</sup> | 4 <sup>th</sup> | 4 <sup>th</sup> | 6 <sup>th</sup> | 6 <sup>th</sup> | 4 <sup>th</sup> |

| Resonator            | active-RC       | LC              | LC              | LC              | active-RC       | new RC          |

| DR [dB]              | 90              | 65              | 53              |                 | 70              | 60              |

| F <sub>s</sub> [MHz] | 264             | 3800            | 40000           | 3000            | 800             | 800             |

| F <sub>c</sub> [MHz] | 44              | 950             | 2000            | 2400            | 200             | 200             |

| BW [MHz]             | 8.5             | 0.2/1           | 60/120          | 60              | 10              | 24              |

| SNDR [dB]            |                 |                 | 55/52           | 40              | 68.4            | 58              |

| SNR [dB]             | 77              | 63/59           |                 |                 |                 |                 |

| Power [mW]           | 375             | 75              | 1600            | 40              | 160             | 12              |

| Area [mm²]           | 2.5             | 1.08            | 2.4             | 0.8             | 2.5             | 0.2             |

|                      | 0.18            | 0.25            | 0.13            | 0.09            | 0.18            | 0.065           |

| Process              | смоѕ            | BiCMOS          | BiCMOS          | CMOS            | смоѕ            | CMOS            |

| FoM<br>[pJ/step]     | 3.81            | 162/51          | 29/20           | 4.08            | 3.72            | 0.385           |

<sup>\*</sup>  $FoM = Power/(2 \cdot BW \cdot 2^{ENOB})$ , ENOB = (SNDR - 1.76)/6.02

# Chapter 3. CTBPDSM with DAC Duty Cycle Control

The first prototype achieves good power efficiency, but the SNDR and dynamic range are not enough for practical SDR. Considering that a higher resolution and a wide bandwidth, such as 12bit resolution at 24MHz, is required in mobile environments[91], the first prototype can achieve 2 more bits by increasing the modulation order or the quantizer resolution. Also, the first resonator and the first DAC need to have lower in-band thermal noise to reduce the noise floor and improve SNDR.

Bandpass filtering of the input signal also makes CTBPDSMs more suitable for SDR since this filtering suppresses interferers and prevents saturation of the modulator [92]-[95]. Furthermore, filtering helps to increase the dynamic range. The STF of the first prototype is almost flat due to the feedforward paths, and a modification of this architecture adds a bandpass characteristic to the STF. To keep the power consumption low, another new technique reduces the number of feedback DACs.

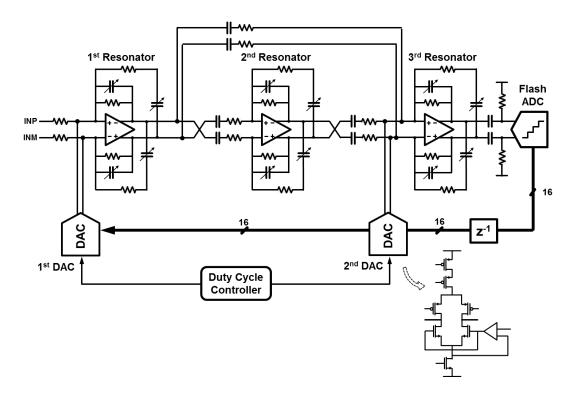

We introduce a 6<sup>th</sup>-order CTBPDSM architecture with 4bit quantization in this chapter. This device has better resolution than the first prototype and also provides bandpass filtering of the input signal. This new architecture has total two DACs thanks to DAC duty cycle control. With the help of a new duty-cycle-controlled feedback DAC scheme, we can make an architecture that is both simple and reconfigurable. A single, duty-cycle-controlled DAC replaces the conventional combination of RZ and HZ DACs that usually feed each resonator. This new scheme does not rely on feedforward paths to eliminate feedback DACs, and importantly this enables input signal filtering without peaking in the STF. Also, the duty-cycle controlled DAC enables the center frequency to be easily reconfigurable.

Table 4. Target spec of the new prototype

| Sampling Rate    | 800MHz |  |  |

|------------------|--------|--|--|

| Center Frequency | 200MHz |  |  |

| BW               | 24MHz  |  |  |

| Power            | 40mW   |  |  |

| SNDR             | 75dB   |  |  |

| DR               | 80dB   |  |  |

Table 4 shows the new target specifications. The target SNDR and dynamic range are 75dB and 80dB, respectively. The amplifiers and the DAC current sources are newly designed for lower thermal noise and the better linearity to achieve the target performance. Other peripheral circuits are also modified appropriately. Although it introduces reconfigurability and STF filtering, the prototype achieves the best energy efficiency of any CTBPDSM using active resonators.

Figure 36. System block diagram

#### 3.1 New Architecture

The 6<sup>th</sup>-order CTBPDSM architecture in Figure 36 has three resonators, and there is no summing amplifier. Single-opamp resonators are used for low power consumption. The two DACs are connected to *Resonator1* and *Resonator3*, and one feedforward path exists between the *Resonator1* output and the *Resonator3* input for low power. The quantizer is expanded to a 17-level flash ADC, and this, together with the 6<sup>th</sup>-order modulation, increases the SNDR. The feedforward path from the input is removed, and *Resonator3* drives the quantizer directly. The absence of the feedforward path in front of the quantizer helps the bandpass filtering.

The two DACs are not RZ DACs, but change the current direction depending on the preset duty cycle. This makes one DAC look like two DACs, and this helps to further reduce the total number of DACs in this modulator.

The simulation results with this architecture show 75dB SNDR with the STF peaking minimized. The maximum SNDR with 6<sup>th</sup>-order modulation and 4bit quantization is higher than this, but it causes STF peaking when there is a feedforward path in the modulator. The degrade in the SNDR can lead to the STF with the minimum peaking, and this still satisfies the original target SNDR.

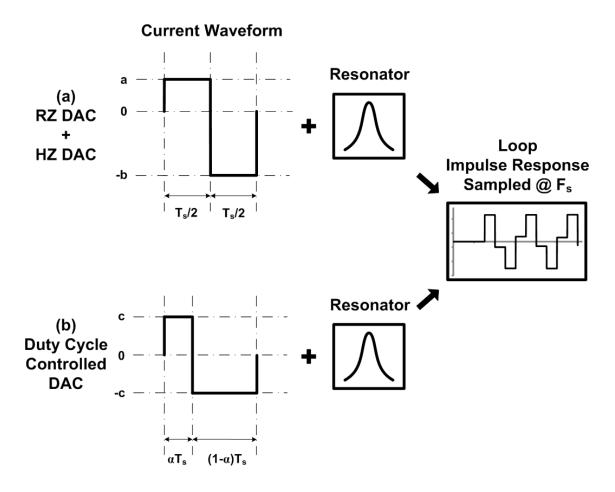

### 3.2 Frequency Tuning

A flexible modulator center frequency[96] requires adjustment of both the feedback and/or feedforward coefficients, as well as modification of the resonant frequency of resonators. [58] transforms a DTBPDSM to a CTBPDSM with RZ and HZ DACs. This transformation is not