### FULLY INTEGRATED HIGH-PERFORMANCE MEMS LUMPED ELEMENT FILTERS FOR RECONFIGURABLE RADIOS

by

**Yonghyun Shim**

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 2013

Doctoral Committee:

Assistant Professor Mina Rais-Zadeh, Chair Professor Kamal Sarabandi Professor Euisik Yoon Associate Professor Katsuo Kurabayashi © Yonghyun Shim All rights reserved 2013 To my parents

#### ACKNOWLEGEMENTS

I would like to thank everyone who has helped me throughout my Ph.D. years. First, I wish to express my most sincere gratitude and appreciation to my advisor, Professor Mina Rais-Zadeh, for giving me the opportunity to pursue my Ph.D. degree and supporting me throughout the years. Since I joined the Resonant MEMS group, she has trained and guided me with a lot of motivation, enthusiasm, and encouragement. Also, she did not restrict the scope of my work and has always driven me to consider various research directions, not limited to the RF MEMS area.

I also thank my thesis committee members, Professor Kamal Sarabandi, Professor Euisik Yoon, and Professor Katsuo Kurabayashi for their guidance of my research. Their advice has been always helpful and led me to think about my research work from a different point of view. Also, attending academic conferences with them has been a great pleasure and I felt that I belong to a strong academic circle here at the University of Michigan.

I thank my group mates in the resonant MEMS group. Zhengzheng has always been a good friend, supporter, and mentor. His experience in RF MEMS has been a great resource and we have done a lot of good work together. As early members of Resonant MEMS group, Vikrant and Vikram have been good friends with whom I have discussed research issues and also spent time outside of work. Although they have not spent too much time here, Azadeh and Adam got acquainted with their work pretty fast and did a lot of support for my research. I would like to mention about Jeff and Muzhi as well, who spent countless hours in the clean room with me and did a lot of fundamental characterizations.

I would like to thank the colleagues working at the University of Michigan LNF. They have been of great help and support, especially during my early time getting trained in the clean room. I would also like to thank Dr. Jae Yoong Cho, Dr. Razi-ul Haque, Dr. Il Joo Cho, Edward Tang, Dr. Sangwoo Lee, Dr. Jaehoon Chung, Dr. Ethem E. Aktakka, Ali Besharatian, Dr. Zongliang Cao, Dr. Sang Won Yoon, Dr. Seunghyun Lee, Seow Yuen Yee, Dr. Sung Hyun Jo, Dr. Kuk-Hwan Kim, Fatih M. Ozkeskin, Victor Lee, Kyunghoon Lee, Siddharth Gaba, Kyusang Lee, Girish S. Kulkarni, Fan Wu, Seungdo An, and Dr. Gwang Hyun Baek for their advice and helpful discussion.

My Korean friends also gave me a lot of support whenever I wanted and I have had a great time with them. Dr. Dae Young Lee, Dr. Sangwook Han, Dr. Junseok Heo, Dr. Seunghyun Oh, Jiwon Kim, Shinhyun Choi, Hyun Jeong Cho, Jae Young Park, Jaesang Lee, Jung Kuk Kim, Daeyon Jung, Dongmin Yoon, Dongsuk Jeon, Young Jae Shin, Dr. Sun-Il Chang, Dr. Hyun Kum, Seokjun Park, Se-Un Park, Sung-Yun Park, Seungku Lee, Kyoungwan Na, and Dr. Jaehyuk Choi have been good friends and mentors for my graduate school life.

Last, but not least, I want to express my appreciation to my parents and sister in Korea, who have always encouraged and supported me. I could not finish my Ph.D. work without their care and attention.

# TABLE OF CONTENTS

| DEDICATION                                                                         | ii           |

|------------------------------------------------------------------------------------|--------------|

| ACKNOWLEGEMENTS                                                                    | iii          |

| LIST OF FIGURES                                                                    | ix           |

| LIST OF TABLES                                                                     | xix          |

| LIST OF ABBREVIATIONS                                                              | xxi          |

| ABSTRACT                                                                           | XXV          |

| CHAPTER 1. INTRODUCTION TO TUNABLE RF MEMS                                         | 1            |

| 1.1. Reconfigurable Radios                                                         | 1            |

| 1.2. Tunable Passives                                                              | 6            |

| 1.3. State-of-the-Art Tunable Bandpass Filters for Lower UHF Range                 | 9            |

| 1.3.1. Combline Filters with Continuous Control of Frequency as<br>Bandwidth       |              |

| 1.3.2. Tunable Filter Using Vertically Integrated Evanescent Mo                    |              |

| 1.3.3. PCB-Embedded Tunable Lumped Element Filter                                  | 14           |

| 1.3.4. Five-Pole Lumped Element Filter, Monolithically Integrat<br>MEMS Technology |              |

| 1.4. Fully Integrated Tunable Filters using a Silver Micromachining Te             | echnology 17 |

| 1.4.1. Design                                                                      | 17           |

| 1.4.2. Measurement Result - Individual Filters                                     |              |

| 1.4.3. Measurement Result - Filter Array                                           |              |

| 1.5. Research Objectives                                              |        |

|-----------------------------------------------------------------------|--------|

| 1.6. Organization of Thesis                                           |        |

| CHAPTER 2. HIGH PERFORMANCE, CONTINUOUSLY TUNED                       |        |

| 2.1. Design                                                           |        |

| 2.2. Fabrication Technology                                           |        |

| 2.3. Measurement Result                                               | 41     |

| 2.4. Analysis on Power Handling Capability                            | 47     |

| 2.5. Discussion about Reliability and Tuning Control                  |        |

| CHAPTER 3. HIGH-PERFORMANCE CONTINUOUSLY TUNABLI<br>BANDPASS FILTER   |        |

| 3.1. Design                                                           |        |

| 3.2. 3-D Electromagnetic Simulation                                   | 63     |

| 3.3. Linearity Analysis                                               | 66     |

| 3.4. Measurement Result - Tunable Capacitor Bank                      |        |

| 3.5. Measurement Result - Tunable Filter                              | 71     |

| CHAPTER 4. OTHER PROCESS CONSIDERATIONS FOR TUNAE<br>BANDPASS FILTERS |        |

| 4.1. Packaging of Tunable MEMS Bandpass Filter                        |        |

| 4.1.1. Packaging Technologies for RF Tunable MEMS Devices             |        |

| 4.1.2. Hermetic Packaging with Surface Micromachining                 |        |

| 4.1.3. Packaging Process Using a Liquid Crystal Polymer Lid           |        |

| 4.2. Trap-Rich High-Resistivity Silicon Substrates                    |        |

| 4.2.1. Low Loss Substrates for RF Passives                            |        |

| 4.2.2. Modeling for Trap-Rich High-Resistivity Silicon Substra        | tes 91 |

| 4.2.2.1. Lumped Element Model                                         |        |

| 4.2.2.2. 3D Electromagnetic Simulation                                |        |

| 4.2.2.3. Substrate Loss vs. Metal Loss                             |     |

|--------------------------------------------------------------------|-----|

| 4.2.3. Fabrication Process                                         |     |

| 4.2.4. Measurement Result                                          | 101 |

| 4.2.4.1. Inductors                                                 | 101 |

| 4.2.4.2. Capacitive Switch                                         | 104 |

| 4.2.4.3. Capacitive Switch Bank                                    | 106 |

| 4.3. Process Variation of Tunable RF MEMS Platform                 | 109 |

| CHAPTER 5. RF SWITCHES USING PHASE-CHANGE MATERIALS                | 112 |

| 5.1. Overview of PC Materials                                      | 112 |

| 5.2. Characterization Result of Thin-Film GeTe                     | 120 |

| 5.3. PC Switch Structure                                           | 122 |

| 5.4. Phase Transition Analysis and Simulation                      | 123 |

| 5.5. Measured RF Performance of GeTe Switches                      | 124 |

| 5.5.1. Intrinsic RF Properties                                     | 125 |

| 5.5.2. Power Handling Capability and Linearity                     | 130 |

| 5.5.3. Switching Speed                                             | 135 |

| CHAPTER 6. CONCLUSIONS AND FUTURE DIRECTIONS                       | 138 |

| 6.1. Summary                                                       | 138 |

| 6.2. Future Work - Tunable RF MEMS Platform                        | 139 |

| 6.2.1. Capacitive Switch with Multiple Tuning Steps                | 140 |

| 6.2.2. Tunable Bandpass Filter with Bandwidth Tunability           | 141 |

| 6.3. Future Work - PC Switches and Applications                    | 142 |

| 6.3.1. Phase Change Switch with Separate Heat Bias and Signal Elec |     |

| 6.3.2. Design of Tunable Filters Using PC Switches                 | 144 |

| BIBLIOGRAPHY                                                       | 147 |

## LIST OF FIGURES

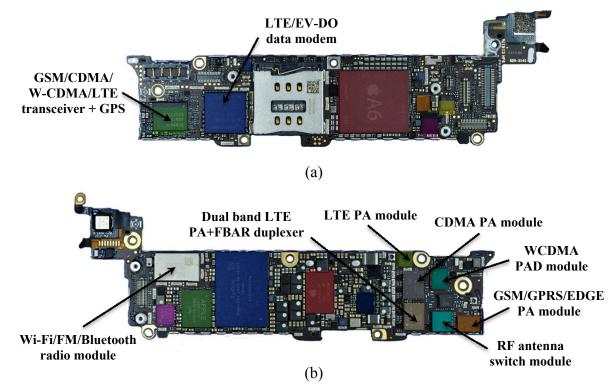

| Figure 1.1. The PCB layout of the iPhone 5 [7]; (a) front side; (b) back side 2                                                                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

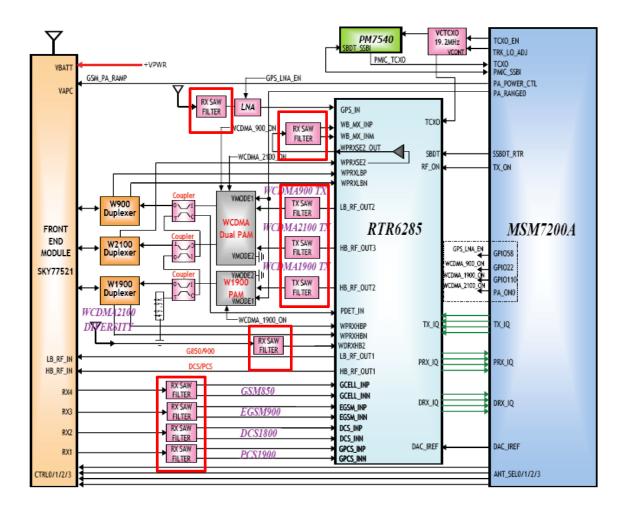

| Figure 1.2. The transceiver architecture of LG GM730 [12]                                                                                                                                                                                         |

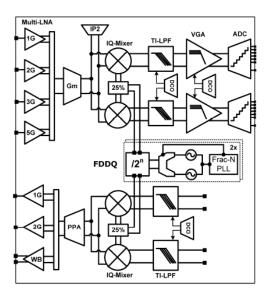

| Figure 1.3. Transceiver block diagram of the multi-standard software defined radio [13].                                                                                                                                                          |

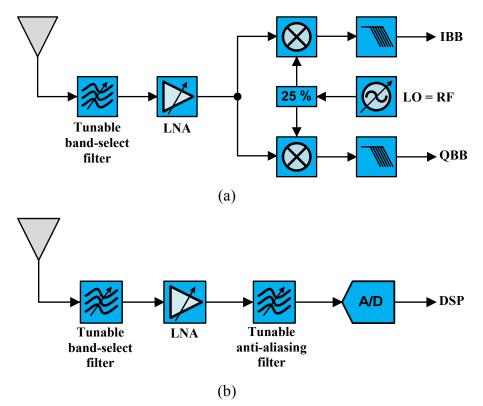

| Figure 1.4. Candidate cognitive radio architectures with tunable preselect filters; (a) direct conversion architecture; (b) RF bandpass sampling architecture; reprinted from [16]                                                                |

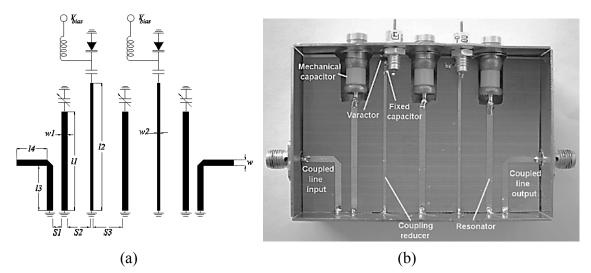

| Figure 1.5. (a) a schematic and (b) photographic view of a combline bandpass filter [81].                                                                                                                                                         |

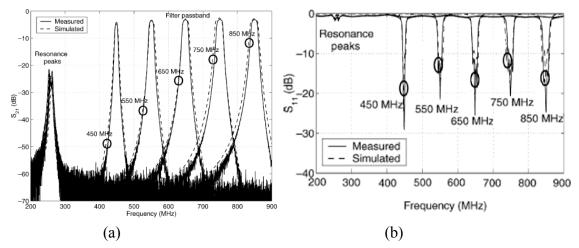

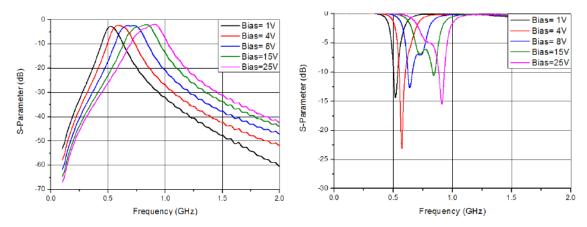

| Figure 1.6. Measured response in each tuned state; (a) insertion loss; (b) return loss [81].                                                                                                                                                      |

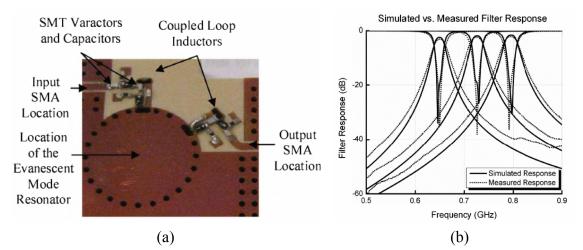

| Figure 1.7. (a) Photographic view, and (b) measured vs. simulated response of a tunable filter using vertically integrated evanescent mode resonator [82]                                                                                         |

| Figure 1.8. (a) cross-sectional view of organic package substrate; (b) photographic view of the second-order coupled resonator with magnetic coupling [80]                                                                                        |

| Figure 1.9. Measured filter response in each tuned state; (a) insertion loss; (b) return loss [80]                                                                                                                                                |

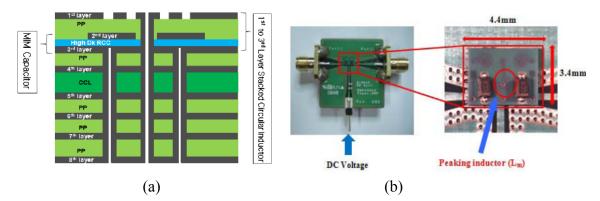

| Figure 1.10. (a) A schematic view and (b) a microscope image of a five-pole tunable bandpass filter [67]                                                                                                                                          |

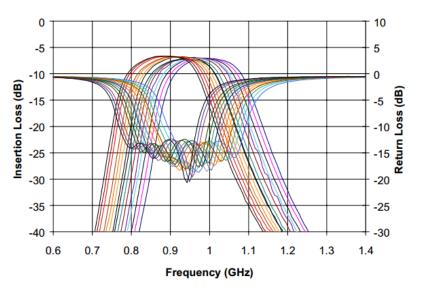

| Figure 1.11. Measured frequency response of tunable bandpass filter in Fig. 1.10 [67] 16                                                                                                                                                          |

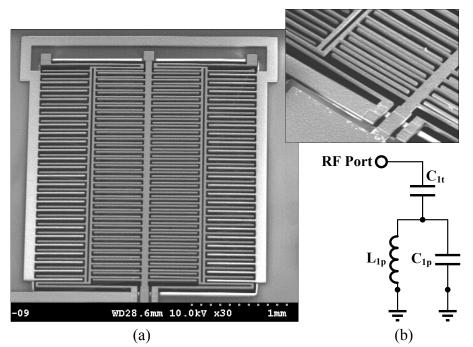

| Figure 1.12. (a) SEM view of the tunable capacitor, and (b) the electrical model of the tunable capacitor. The inset shows a close-up SEM view of the interdigitated fingers. The actuation gap is $20 \ \mu m$ and the sense gap is $10 \ \mu m$ |

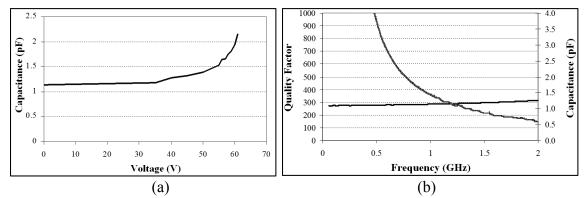

| Figure 1.13. (a) Measured tuning and (b) embedded characteristic of the tunable silver capacitor. The trade-line of the measured data is shown for the quality factor                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

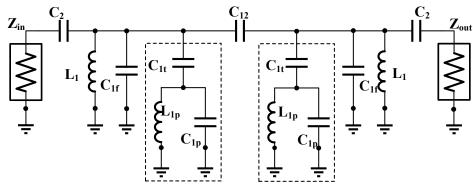

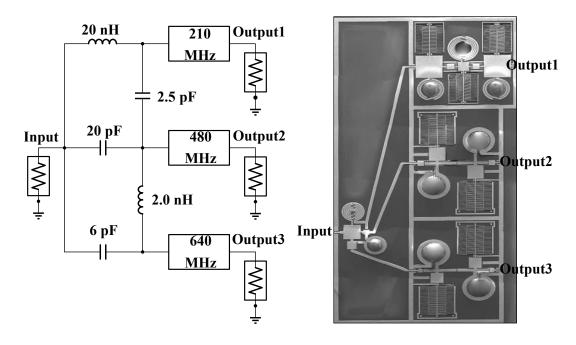

| Figure 1.14. Electrical model of a tunable band-pass filter exploiting inductive parasitics for improved out-of-band rejection                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

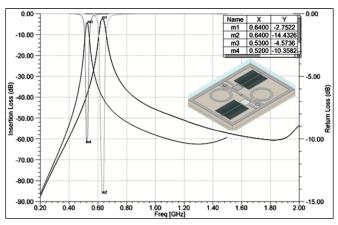

| Figure 1.15. Simulated response and HFSS model of a filter at 480 MHz, showing an IL of 2.79 dB and out-of-band rejection of better than 50 dB                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Figure 1.16. Simulated response and HFSS model of a filter at 640 MHz at the initial state and the maximum tuned state (520 MHz). The IL increases from 2.7 dB to 4.6 dB when the filter is tuned. The out-of band rejection is ~60 dB                                                                                                                                                                                                                                                                                                                                                       |

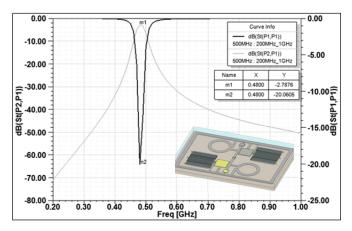

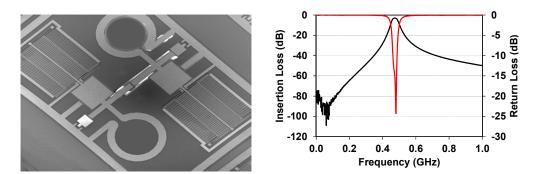

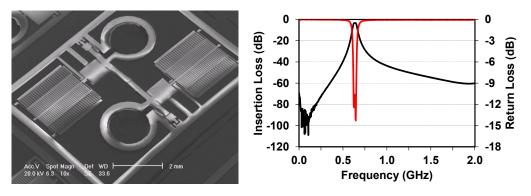

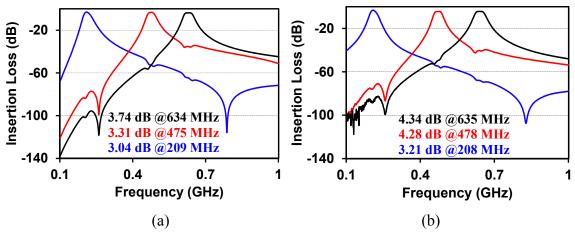

| Figure 1.17. A SEM view (left) and measured response (right) of the filter, initially centered at 480 MHz. The transmission zero is at 1.5 GHz (not captured in this image). The unloaded $Q$ of the filter is 44                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 1.18. A SEM view (left) and measured response (right) of the silver filter at 640 MHz with out-of-band rejection of > 60 dB. The unloaded $Q$ is 50, the highest reported for integrated MEMS filters on silicon. 22                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

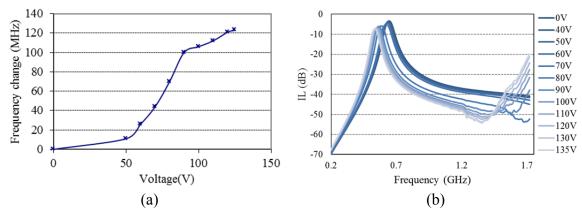

| Figure 1.19. Measured tuning characteristic of a silver filter (coated with Parylene-C for improved tuning. The frequency of the transmission zero decreases as the filter is tuned.                                                                                                                                                                                                                                                                                                                                                                                                         |

| improved tuning. The frequency of the transmission zero decreases as the filter is tuned.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

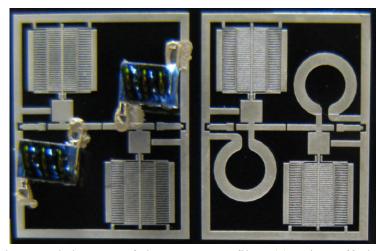

| improved tuning. The frequency of the transmission zero decreases as the filter is tuned.<br>23<br>Figure 1.20. Micrograph images of the 640 MHz filter (a) using off-chip inductors and                                                                                                                                                                                                                                                                                                                                                                                                     |

| improved tuning. The frequency of the transmission zero decreases as the filter is tuned.23Figure 1.20. Micrograph images of the 640 MHz filter (a) using off-chip inductors and<br>(b) fully integrated on silicon.23Figure 1.21. Measured response of the filter at 640 MHz using off-chip inductors from<br>coil-craft, showing significantly lower performance compared to the integrated<br>counterpart (compare to Fig. 1.18). This is due to the capacitive and resistive parasitics of                                                                                               |

| improved tuning. The frequency of the transmission zero decreases as the filter is tuned.23Figure 1.20. Micrograph images of the 640 MHz filter (a) using off-chip inductors and<br>(b) fully integrated on silicon.23Figure 1.21. Measured response of the filter at 640 MHz using off-chip inductors from<br>coil-craft, showing significantly lower performance compared to the integrated<br>counterpart (compare to Fig. 1.18). This is due to the capacitive and resistive parasitics of<br>the silver paste and the pads used to connect the off-chip inductors on the silicon die 23 |

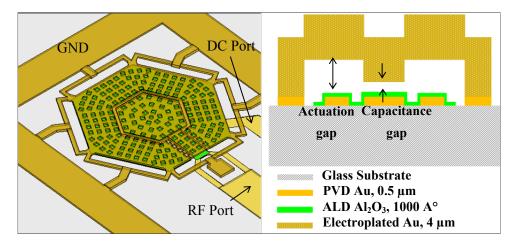

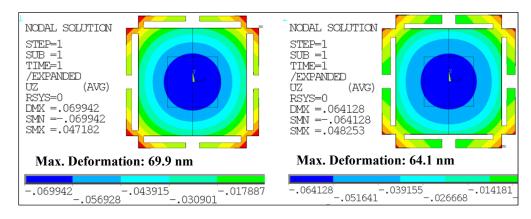

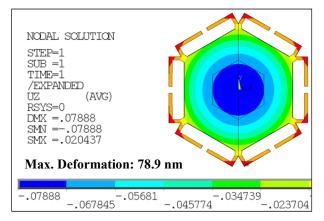

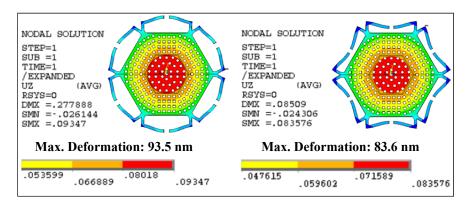

| Figure 2.2. Deformation of the top membrane upon 40 MPa of residual stress and 2                                                                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MPa/ $\mu$ m of stress gradient; square Membrane I with f <sub>M</sub> of 17 kHz (left) and square                                                                                                                                                             |

| Membrane II with $f_M$ of 23 kHz (right)                                                                                                                                                                                                                       |

| Figure 2.3. Deformation of the hexagonal membrane upon 40 MPa of residual stress and 2 MPa/µm of stress gradient at room temperature (300 K)                                                                                                                   |

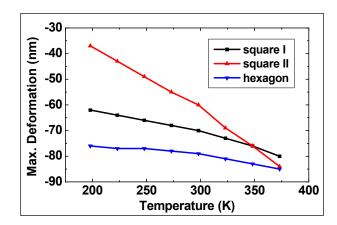

| Figure 2.4. Maximum deformation of the square-shape membranes upon 40 MPa of residual stress and 2 MPa/µm of stress gradient when temperature is varied from 198 K to 373 K                                                                                    |

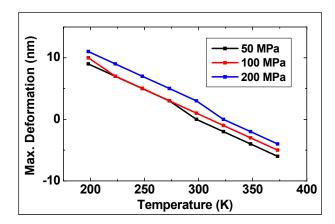

| Figure 2.5. Maximum deformation of the hexagonal membrane upon 50, 100, and 200 MPa of residual stress when temperature is varied from 198 K to 373 K                                                                                                          |

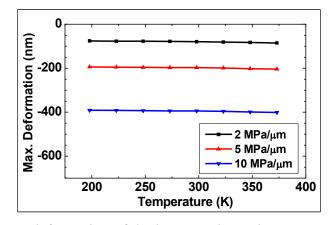

| Figure 2.6. Maximum deformation of the hexagonal membrane upon 40 MPa of residual stress and 2, 5, and 10 MPa of stress gradient when temperature is varied from 198 K to 373 K                                                                                |

| Figure 2.7. Deformation of the top membrane upon 40 MPa of residual stress and 2 MPa/µm of stress gradient at 223K (left) and 333K (right)                                                                                                                     |

| Figure 2.8. Deformation of the top membrane upon 40 MPa of residual stress and 4 MPa/µm of stress gradient at 223K (left) and 333K (right)                                                                                                                     |

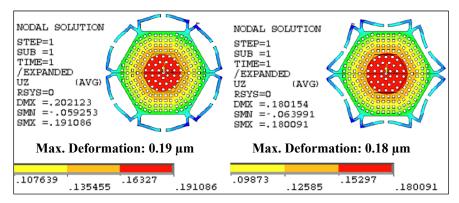

| Figure 2.9. Initial capacitance, maximum capacitance, and $Q$ at initial and final states extracted using the HFSS tool                                                                                                                                        |

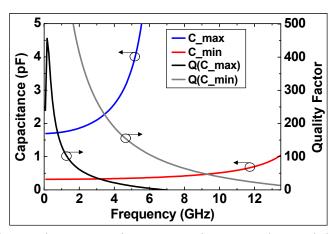

| Figure 2.10. Schematic diagram of the tunable RF MEMS platform applicable for a variety of RF passive components; (a) tunable capacitor; (b) switch; (c) tunable filter; (d) high- <i>Q</i> inductor                                                           |

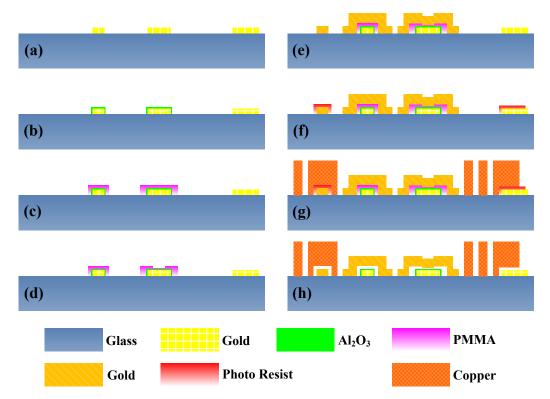

| Figure 2.11. The fabrication process flow; (a) Au lift-off; (b) Al <sub>2</sub> O <sub>3</sub> deposition; (c) PMMA patterning; (d) PMMA thinning; (e) Au electroplating; (f) S1813 lithography; (g) Cu electroplating; (h) release in Acetone followed by CPD |

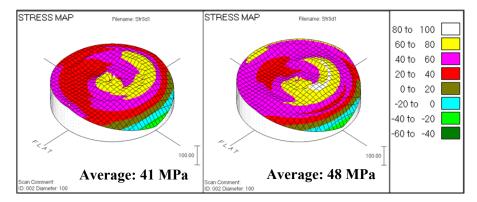

| Figure 2.12. Residual stress distribution of a 2 $\mu$ m thick gold layer electroplated on a silicon wafer after 30 cycles (left) and after 90 cycles of XeF <sub>2</sub> etch (right)                                                                         |

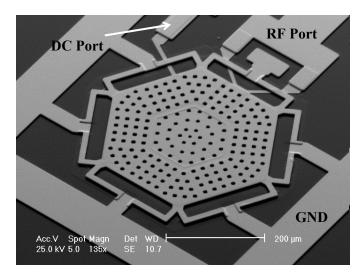

| Figure 2.13. A SEM image of a fabricated tunable capacitor                                                                                                                                                                                                     |

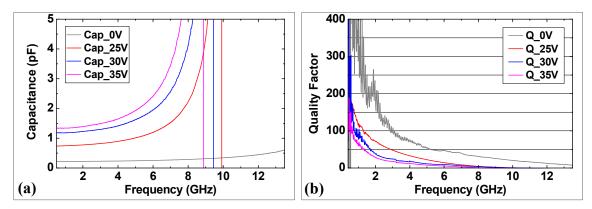

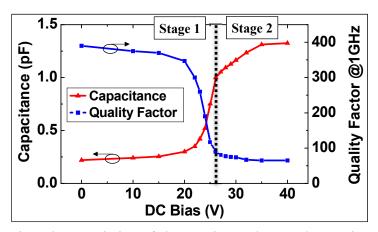

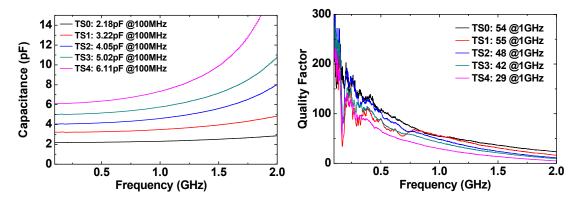

| Figure 2.14. (a) Measured capacitance and (b) quality factor of the varactor at different tuning bias                                                                                                                                                          |

| Figure 2.15. Tuning characteristics of the continuously tuned capacitor. At Stage 1 the air gap closes uniformly. At Stage 2 (after touch-down at 26 V) the membrane conforms to the substrate                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.16. Tuning characteristics of the switched capacitor. At Stage 1 the air gap closes uniformly. At Stage 2 (after touch-down) the membrane conforms to the substrate.                                                             |

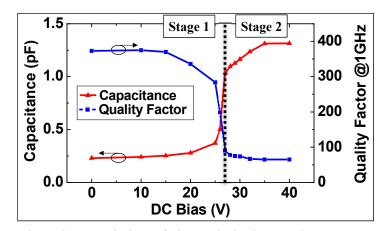

| Figure 2.17. Measured initial and final capacitance values as well as the maximum DC bias are stable within 5%, 7%, and 9% of their room temperature values                                                                               |

| Figure 2.18. Measured initial and final capacitance values as well as the maximum DC bias are stable within 5%, 7%, and 9% of their room temperature values                                                                               |

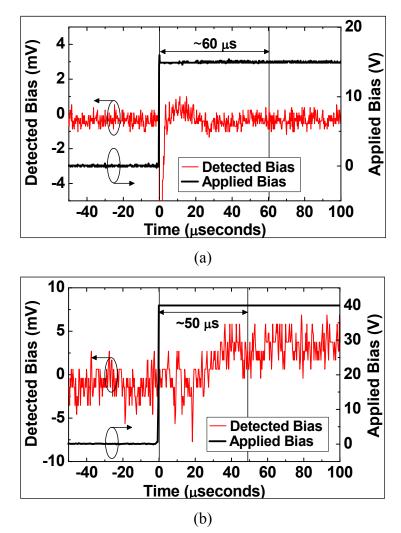

| Figure 2.19. Tuning speed measurement; (a) with 15 V of tuning bias; (b) with 40 V of tuning bias                                                                                                                                         |

| Figure 2.20. Schematic view of the non-linear electro-mechanical model for the varactor.<br>                                                                                                                                              |

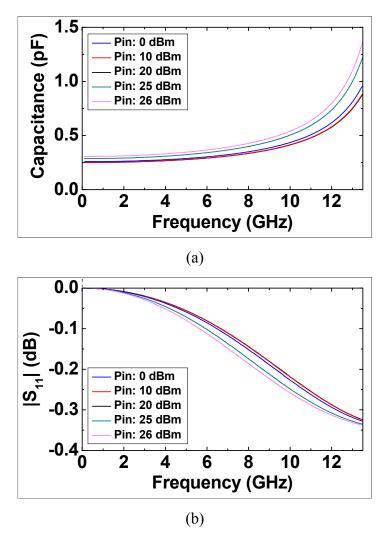

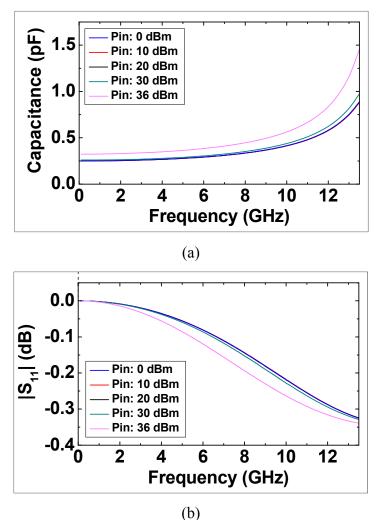

| Figure 2.21. Simulated (a) capacitance and (b) S-parameters $(S_{11})$ at each RF power level when the varactor is at the initial state. The non-linear electro-mechanical model in Figure 2.20 is utilized for this simulation. 49       |

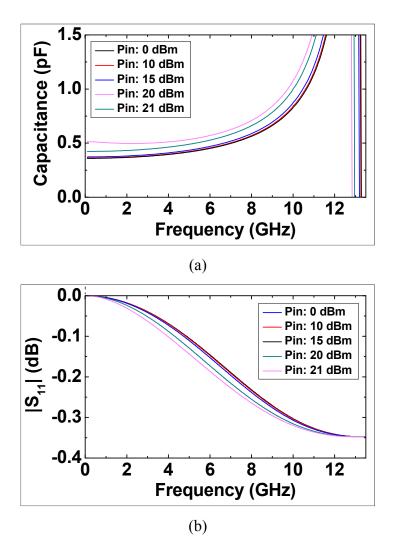

| Figure 2.22. Simulated (a) capacitance and (b) S-parameters $(S_{11})$ at each RF power level when the varactor is tuned with 25 V of DC bias. The non-linear electro-mechanical model in Figure 2.20 is utilized for this simulation     |

| Figure 2.23. Simulated (a) capacitance and (b) S-parameters $(S_{11})$ at each RF power level when no DC bias is applied to the capacitive switch. The non-linear electro-mechanical model in Figure 2.20 is utilized for this simulation |

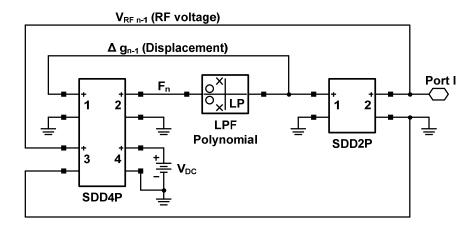

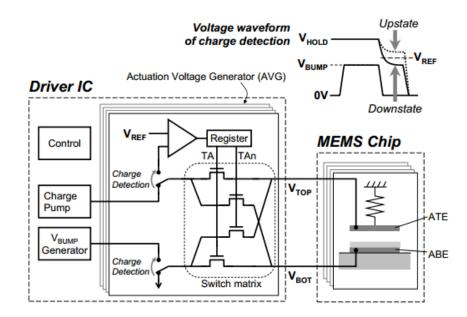

| Figure 2.24. Block diagram of intelligent bipolar actuation circuit [98]53                                                                                                                                                                |

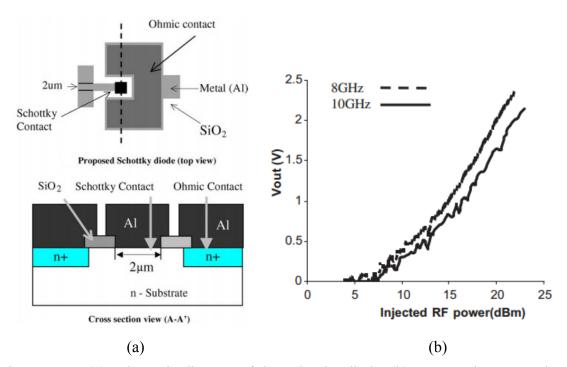

| Figure 2.25. (a) Schematic diagram of the Schottky diode; (b) Measured output voltage when power level is swept from 0 to 25 dBm at 8 and 10 GHz [99]                                                                                     |

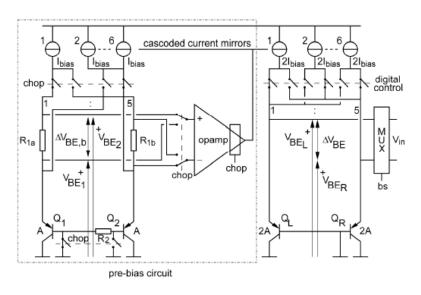

| Figure 2.26. Circuit diagram of the sensor front-end, included in the integrated CMOS temperature sensor [100]                                                                                                                            |

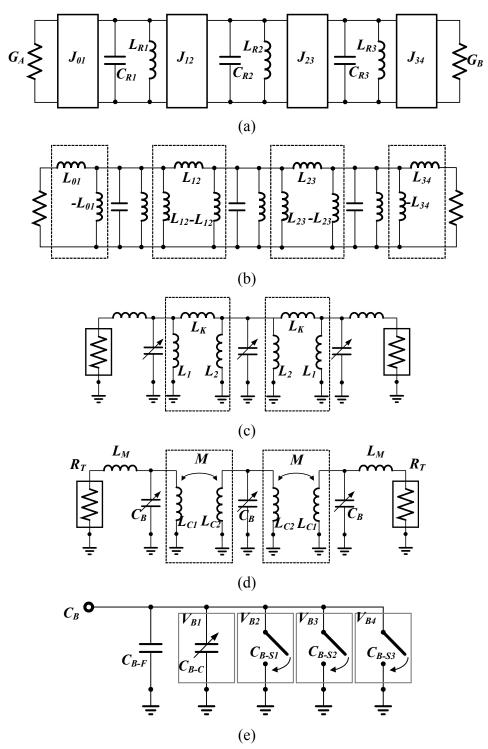

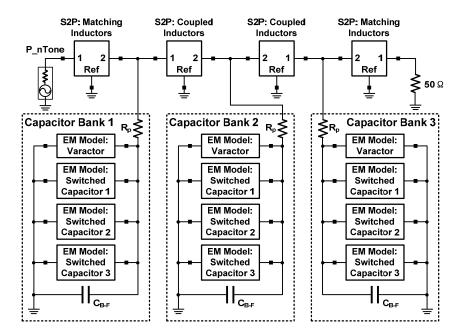

| Figure 3.1. Schematic views showing the design procedure of the third-order bandpass filter in this work; (a) generalized bandpass filter using admittance inverter (b)                                                                   |

| conversion into inductive coupling (c) arrangement of inductance for mutual-inductive coupling (d) the final schematic view of the filter. Detail composition of the tunable bar included in each resonator (e).              |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

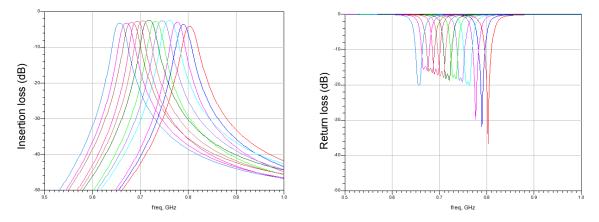

| Figure 3.2. Simulated insertion loss and return loss of the third-order tunable bandpass filter at each tuned stage, based on the schematic view in Fig. 3.1 (d)                                                              |    |

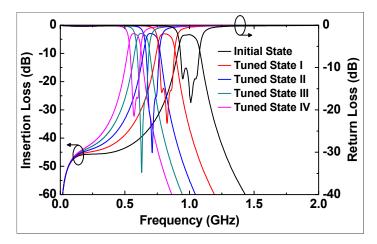

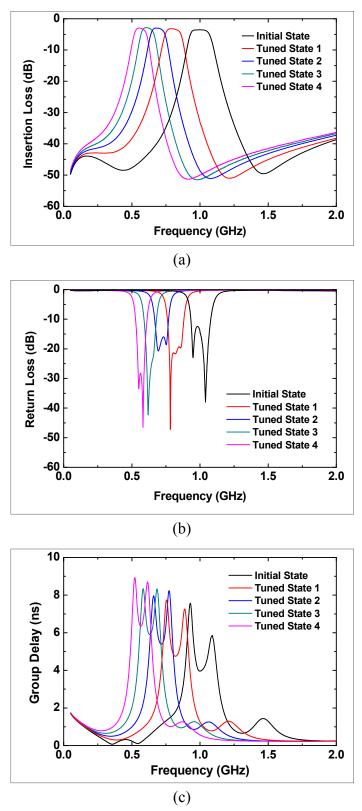

| Figure 3.3. Layout of the MEMS tunable filter.                                                                                                                                                                                | 64 |

| Figure 3.4. Simulation results of the MEMS filter. (a) Insertion loss; (b) return loss; (c) group delay                                                                                                                       |    |

| Figure 3.5. Schematic view of the non-linear electro-mechanical model for (a) the varactor, and (b) the entire filter.                                                                                                        | 68 |

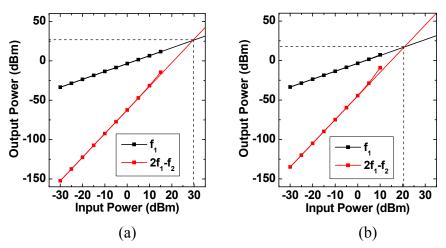

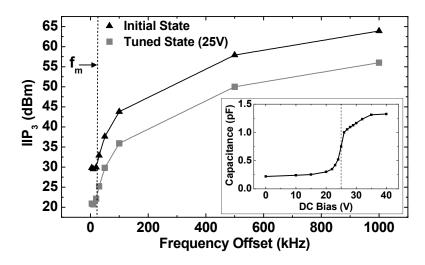

| Figure 3.6. IIP <sub>3</sub> value extracted from the non-linear electro-mechanical model at frequency offset of 20 kHz (a) without DC bias (b) with 25 V of DC bias                                                          | 69 |

| Figure 3.7. IIP <sub>3</sub> value extracted from the non-linear electro-mechanical model at different frequency offsets with and without DC bias. Tuning characteristics of the tunable capacitor is shown in the inset.     | 69 |

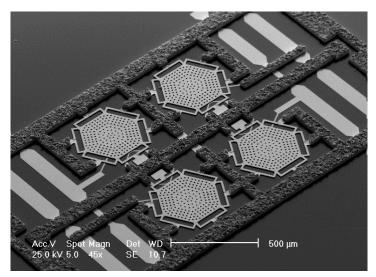

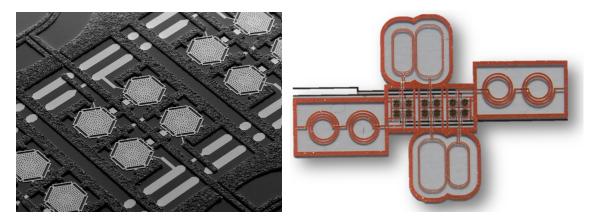

| Figure 3.8. A SEM view of the fabricated tunable capacitor array.                                                                                                                                                             | 70 |

| Figure 3.9. Measured capacitance (left) and $Q$ of the tunable capacitor array (right)                                                                                                                                        | 70 |

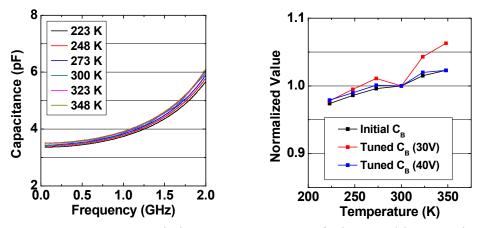

| Figure 3.10. Temperature variation measurements of the tunable capacitor bank; measured capacitance under 40 V of DC bias (left); normalized value of the initial and tuned capacitance with 30 V and 40 V of DC bias (right) | 71 |

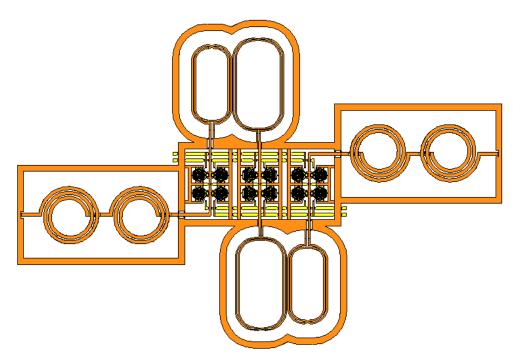

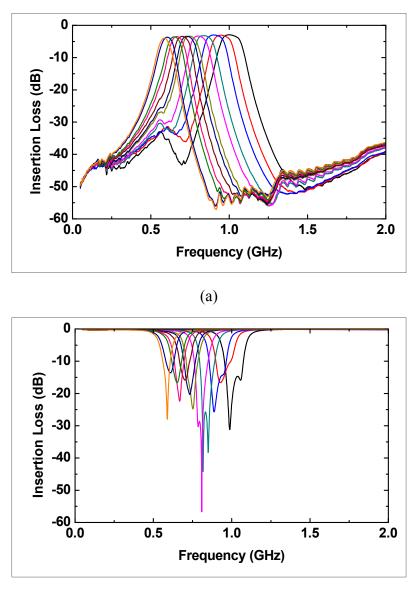

| Figure 3.11. A SEM view (left) and a photo image (right) of fabricated filter                                                                                                                                                 | 72 |

| Figure 3.12. Measured filter response at each tuned stage; (a) insertion loss, and (b) return loss                                                                                                                            | 73 |

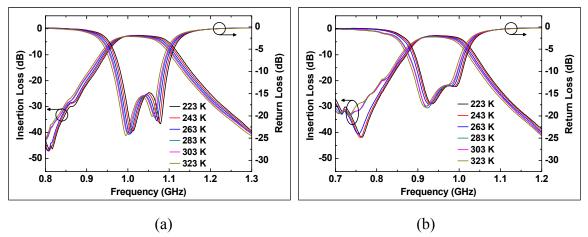

| Figure 3.13. Measured filter response at different temperatures; (a) at initial state; (b) when a DC bias of 25 V is applied to $C_{B-C}$ .                                                                                   | 75 |

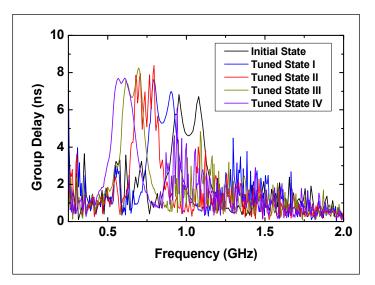

| Figure 3.14. Measured group delay at each tuned stage                                                                                                                                                                         | 75 |

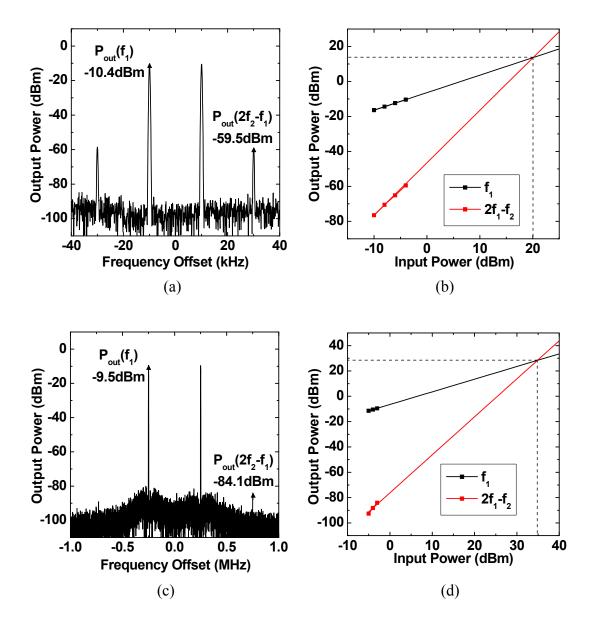

| Figure 3.15. Measured power spectrum when all tunable capacitors are at the initial                                                                                                                                           |    |

states; (a) output power spectrum with frequency offset of 20 kHz and input power of -4 dBm; (b) extracted IIP<sub>3</sub> with frequency offset of 20 kHz; (c) output power spectrum with

| frequency offset of 500 kHz and input power of -3 dBm; (d) extracted IIP <sub>3</sub> with frequency offset of 500 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

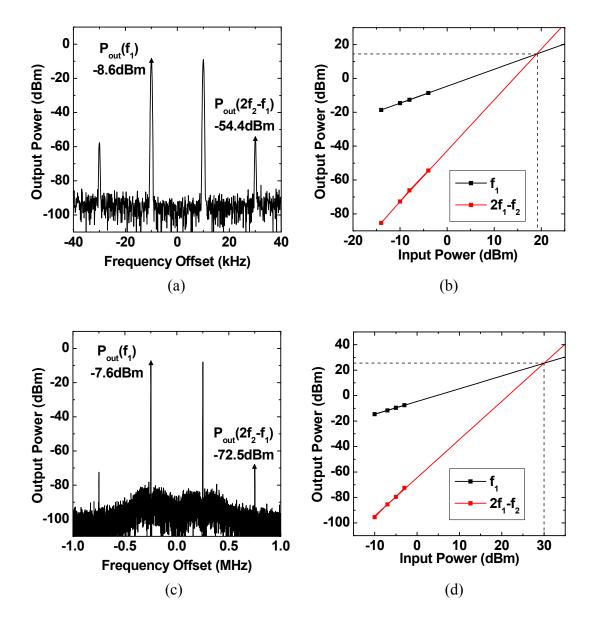

| Figure 3.16. Measured power spectrum when 25 V of DC bias is applied to the continuously tunable capacitor; (a) output power spectrum with frequency offset of 20 kHz and input power of -4 dBm; (b) extracted IIP <sub>3</sub> with frequency offset of 20 kHz; (c) output power spectrum with frequency offset of 500 kHz and input power of -3 dBm; (d) extracted IIP <sub>3</sub> with frequency offset of 500 kHz                                                                                                                                                                                              |

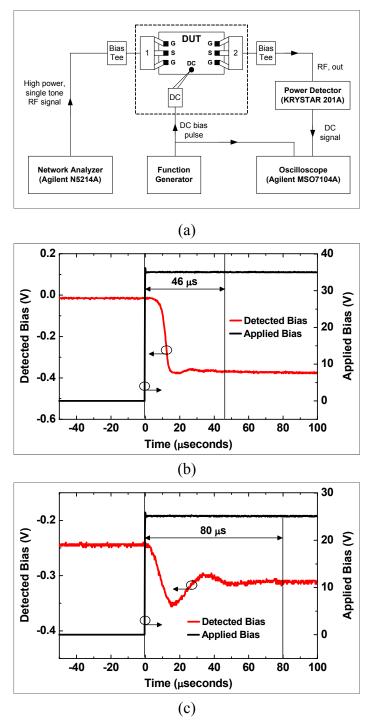

| Figure 3.17. (a) The setup used for tuning-speed measurements. The measured time response when (b) 40 V and (c) 25 V is applied to the tunable capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

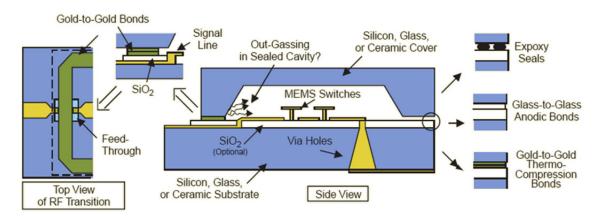

| Figure 4.1. Packaging and interconnect schemes for RF MEMS switches [105]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 4.2. Schematic diagram of hermetically glass-frit sealed packaging approach [111]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

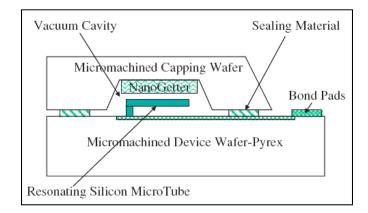

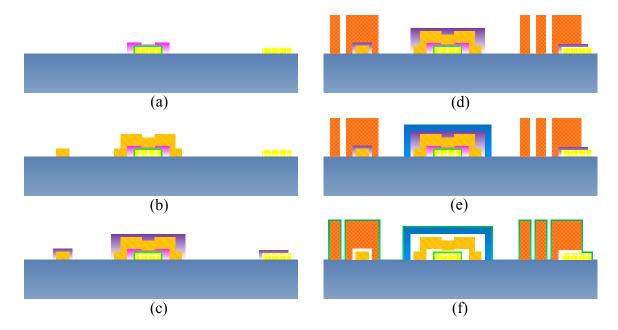

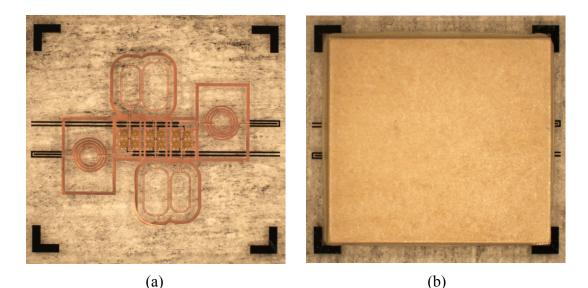

| Figure 4.3. Surface micromachining process of tunable MEMS bandpass filter including<br>the hermetic packaging steps; (a) bottom electrode, dielectric layer, and polymer<br>sacrificial layer are processed; (b) top membranes of tunable MEMS devices are<br>electroplated; (c) the second sacrificial layer used for hermetic packaging and<br>interconnect insolation is processed; (d) inductor and routing layer are electroplated; (e)<br>low temperature dielectric layer is deposited and patterned for packaging; (f) MEMS<br>devices are released and subsequently sealed with a second dielectric layer |

| (a) top-down view before packaging step; (b) top-down after packaging step                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

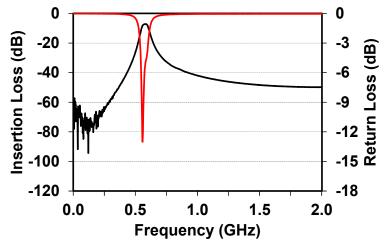

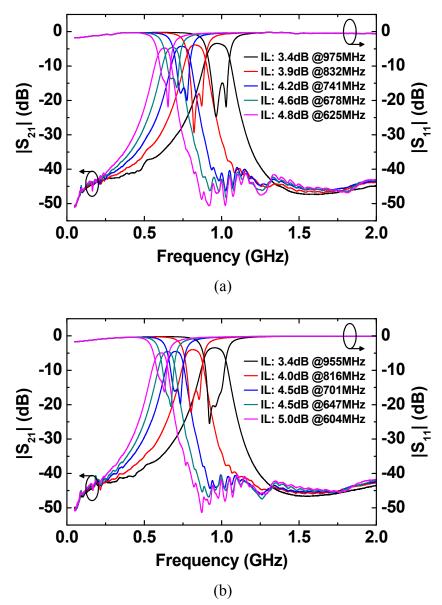

| Figure 4.5. Measurement results of tunable MEMS bandpass filter at each tuned state; (a) before packaging; (b) after packaging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

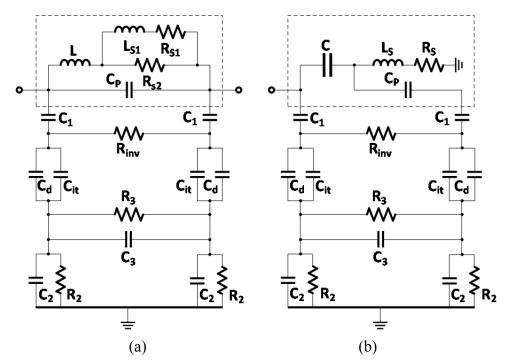

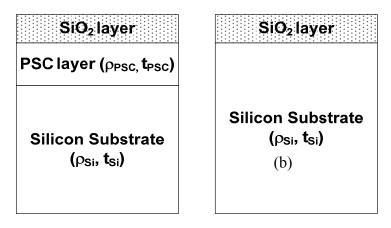

| Figure 4.6. Lumped element equivalent model reflecting the effect of PSC and the trap-<br>rich layers of (a) an inductor and (b) a one-port MEMS capacitive switch on a trap-rich<br>HR-Si substrate. 92                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 4.7. Lumped element equivalent model reflecting the effect of PSC and the trap-<br>rich layers of (a) an inductor and (b) a one-port MEMS capacitive switch on a trap-rich<br>HR-Si substrate [130]                                                                                                                                                                                                                                                                                                                                                                                                          |

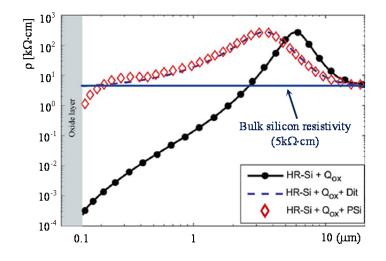

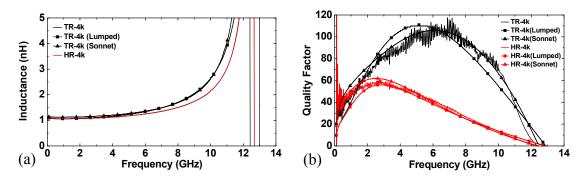

| Figure 4.8. Approximated substrate assignment of HR-Si for RF simulation; (a) with a PSC layer; (b) with a trap-rich layer after PSC compensation                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 4.9. Comparison of measurement result with EM simulation and lumped element model. The measurement data is from IND1 on $4k\Omega \cdot cm$ HR-Si with and without a traprich layer; (a) inductance; (b) $Q$                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

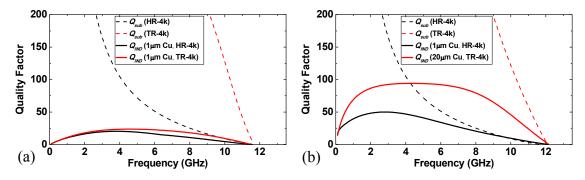

| Figure 4.10. Illustration of quality factor difference as condition of loss mechanism is changed; (a) when substrate loss is improved (HR-4k to TR-4k); (b) when both substrate and ohmic loss are improved (1 $\mu$ m Cu to 20 $\mu$ m Cu)                                                                                            |

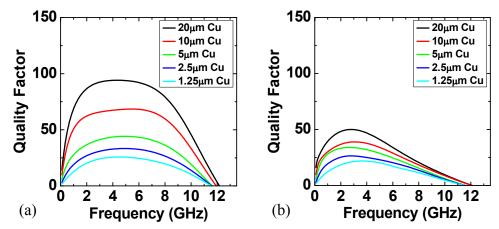

| Figure 4.11. Simulation result of 1nH inductor on (a) trap-rich $4k\Omega \cdot cm$ HR-Si (TR-4k) and (b) standard $4k\Omega \cdot cm$ HR-Si (HR-4k) with different Cu layer thickness; 20 $\mu$ m, 10 $\mu$ m, 5 $\mu$ m, 2.5 $\mu$ m, and 1.25 $\mu$ m. 98                                                                           |

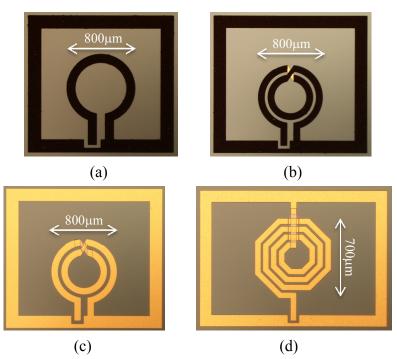

| Figure 4.12. Microscope images of the fabricated inductors; (a) <i>IND1</i> , composed of a single-turn, 40 µm thick copper layer; (b) <i>IND2</i> , composed of a two-turn, 40 µm thick copper layer; (c) <i>IND3</i> , composed of a two-turn, 5 µm thick gold layer; (d) <i>IND4</i> , composed of a 3.5-turn, 5µm thick gold layer |

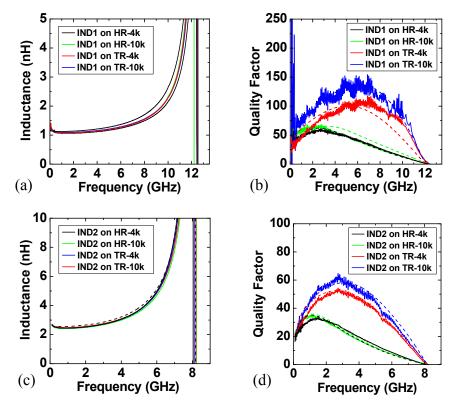

| Figure 4.13. Measurement results of inductors on four different substrates listed in Table II; (a) inductance of <i>IND1</i> ; (b) <i>Q</i> of <i>IND1</i> ; (c) inductance of <i>IND2</i> ; (d) <i>Q</i> of <i>IND2</i> 102                                                                                                           |

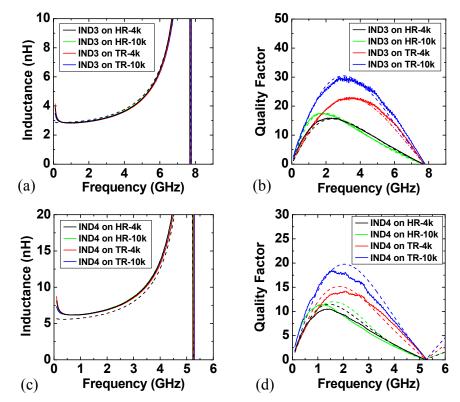

| Figure 4.14. Measurement results of inductors on four different substrates listed in Table II; (a) inductance of $IND3$ ; (b) $Q$ of $IND3$ ; (c) inductance of $IND4$ ; (d) $Q$ of $IND4$ ; The dashed line is the EM simulation result using each inductor layout and the substrate models.                                          |

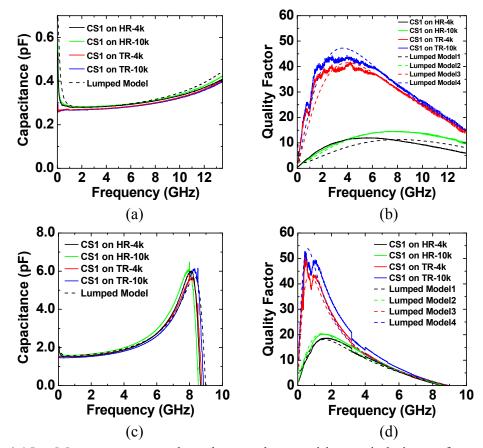

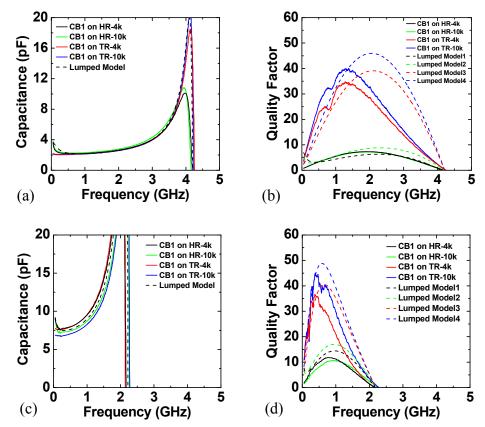

| Figure 4.15. Measurement results when each capacitive switch is on four different substrates in Table II. (a) capacitance at initial state; (b) $Q$ at initial state; (c) capacitance at touch-down state; (d) $Q$ at touch-down state                                                                                                 |

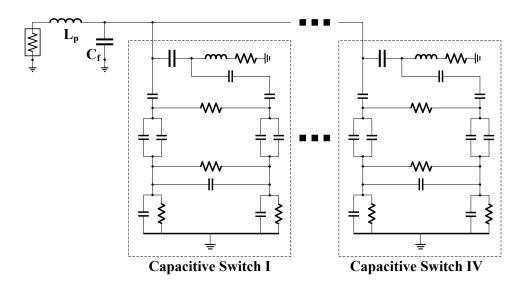

| Figure 4.16. Equivalent lumped model of capacitive switch bank                                                                                                                                                                                                                                                                         |

| Figure 4.17. Extracted capacitance and quality factor of the capacitive switch bank, compared with the lumped model shown in Fig. 6; (a) capacitance at the initial state; (b) quality factor at the initial state; (c) capacitance when all switches are tuned; (d) quality factor when all switches are tuned. 107                   |

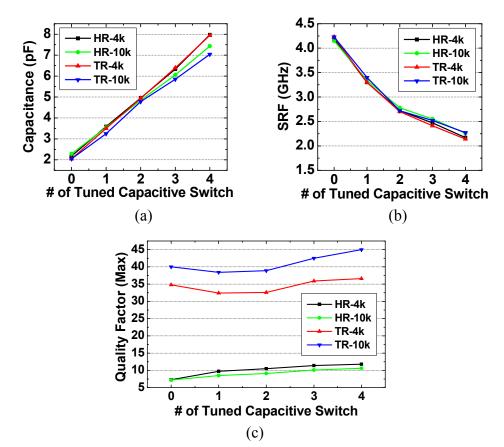

| Figure 4.18. Extracted parameters of capacitive switch bank for the four different substrates; (a) capacitance vs. tuned state; (b) SRF vs. tuned state; (c) $Q_{max}$ vs. tuned state. 108                                                                                                                                            |

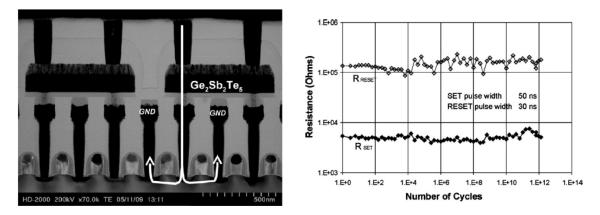

| Figure 5.1. 256 MB PRAM using 100nm technology with a cell size of 0.166 μm <sup>2</sup> (left) [137]; cycling performance of the set and reset states of a single PC memory cell (right) [138]                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

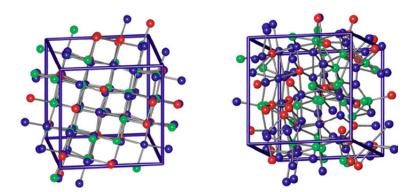

| Figure 5.2. 63-atom models of crystalline Ge <sub>2</sub> Sb <sub>2</sub> Te <sub>5</sub> (left) and amorphous Ge <sub>2</sub> Sb <sub>2</sub> Te <sub>5</sub> (right) [139]                                                         |

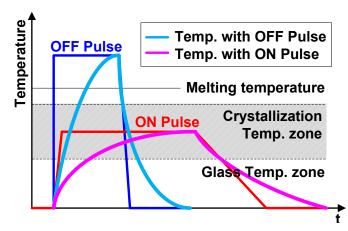

| Figure 5.3. Transient temperature distribution of PCM when a required heat pulse for each transition is applied; OFF pulse is for amorphization and ON pulse is for crystallization.                                                 |

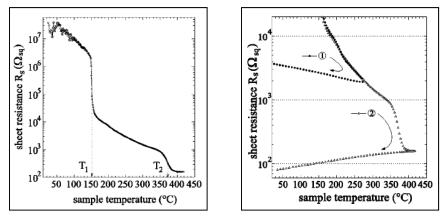

| Figure 5.4. Temperature dependence of the sheet resistance in 80 nm thick Ge <sub>2</sub> Sb <sub>2</sub> Te <sub>5</sub> (left); sheet resistance change upon heating up to 270 °C and 420 °C, and subsequent cooling (right) [140] |

| Figure 5.5. (a) PC vias with direct heating structure [143]; (b) PC vias with indirect heating structure [144]                                                                                                                       |

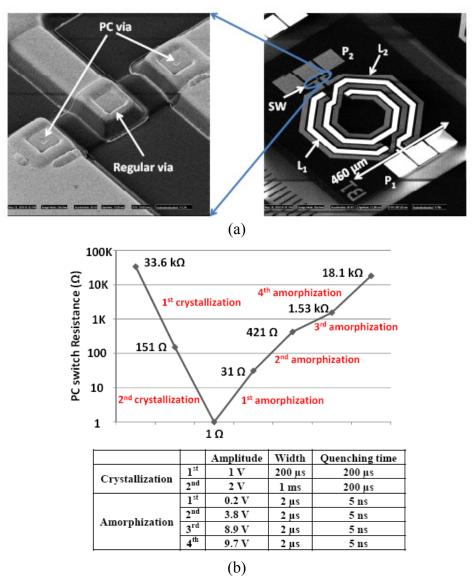

| Figure 5.6. (a) SEM view of the tunable inductor with the PC switch; (b) resistance change of PC switch and voltage pulse conditions in crystalline and amorphous phases [143]                                                       |

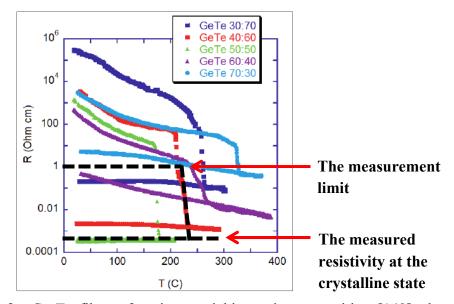

| Figure 5.7. R vs. T for Ge-Te films of various stoichiometric composition [142]; the measured on-resistivity and the tool measurement limit are also indicated                                                                       |

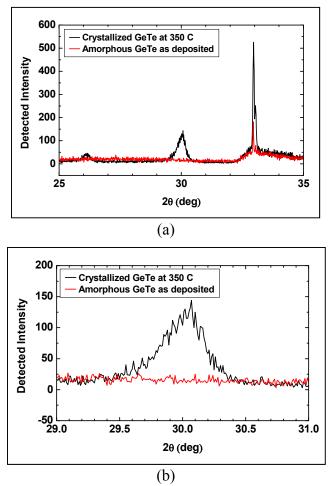

| Figure 5.8. (a) XRD data scanned from 25° to 35° of 2 $\Theta$ range; (b) enlarged XRD data from 29° to 31° of 2 $\Theta$ range                                                                                                      |

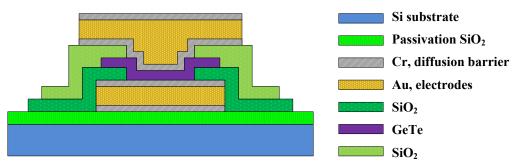

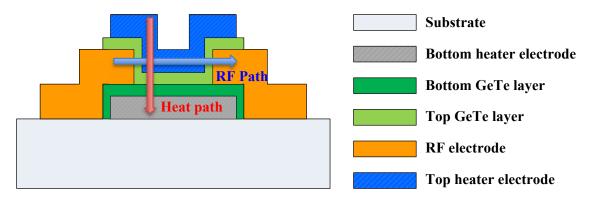

| Figure 5.9. A schematic diagram showing the cross-section of a PC switch 122                                                                                                                                                         |

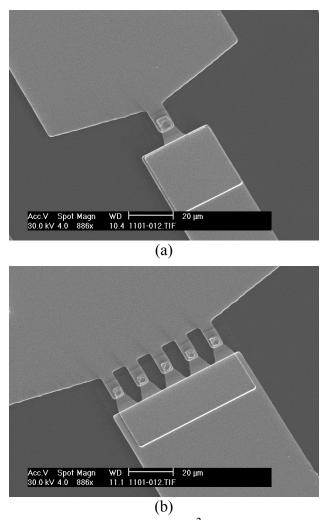

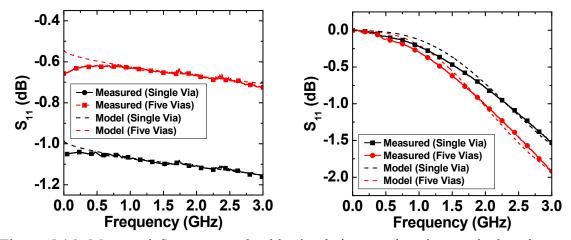

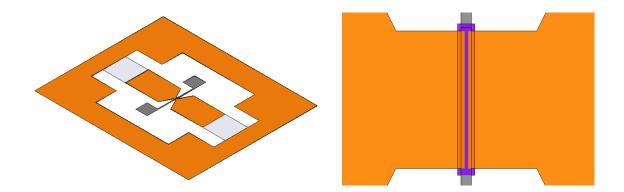

| Figure 5.10. SEM views of (a) a single $3 \times 3 \mu m^2$ via (Design 1) and (b) five parallel-<br>connected $2 \times 2 \mu m^2$ vias (Design 2)                                                                                  |

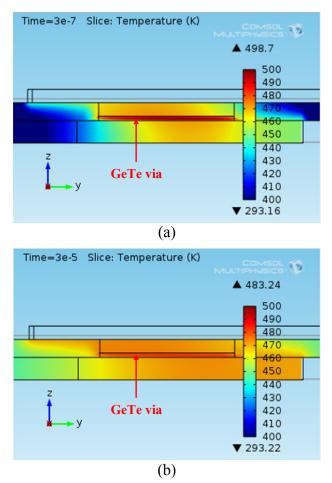

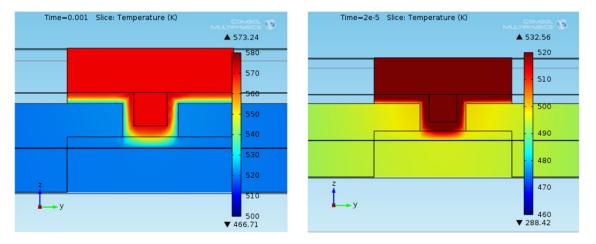

| Figure 5.11. Temperature distribution across the PC switch stack when (a) 3.5 V is applied for 300 ns to amorphize and (b) 2 V is applied for 30 µs to crystallize the switch.                                                       |

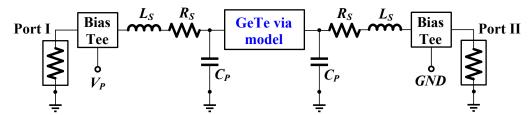

| Figure 5.12. Equivalent electrical model of a GeTe switch; the entire model including electrodes and bias control                                                                                                                    |

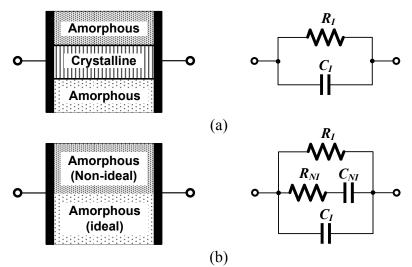

| Figure 5.13. Illustrated diagram and equivalent model of GeTe via at (a) crystalline state<br>and (b) amorphous state                                                                                                                |

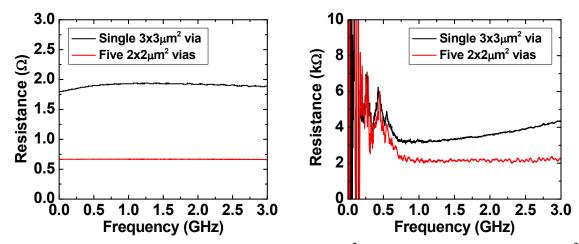

| Figure 5.14. Measured resistance of a single $3 \times 3 \mu m^2$ via (Design 1) and five $2 \times 2 \mu m^2$ parallel vias (Design 2); R <sub>I</sub> at the crystalline state (left); R <sub>NI</sub> at the amorphous state (right)                                                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5.15. Measured intrinsic capacitance (C <sub>1</sub> ) of the single $3 \times 3 \mu m^2$ via and five $2 \times 2 \mu m^2$ vias at the amorphous state                                                                                                                                                                                          |

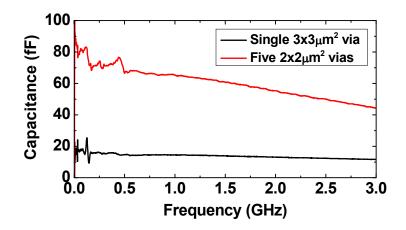

| Figure 5.16. Measured S <sub>11</sub> compared with simulation result using equivalent lumped element models; (left) crystalline state; (right) amorphous state                                                                                                                                                                                         |

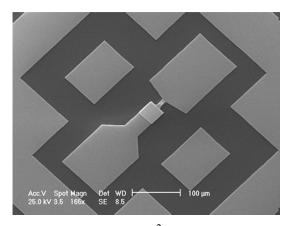

| Figure 5.17. SEM view of a two port $3 \times 3 \ \mu m^2$ PC via                                                                                                                                                                                                                                                                                       |

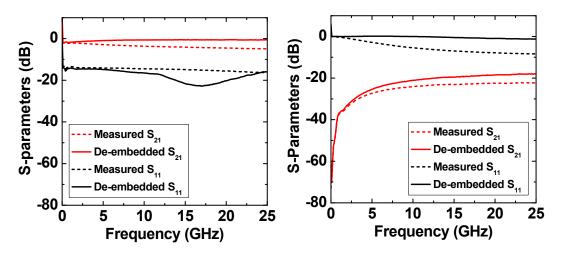

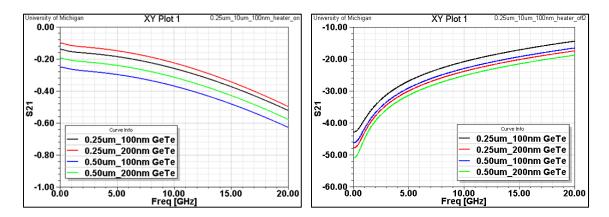

| Figure 5.18. Measured and de-embedded S-parameters at the (left) crystalline and (right) amorphous state                                                                                                                                                                                                                                                |

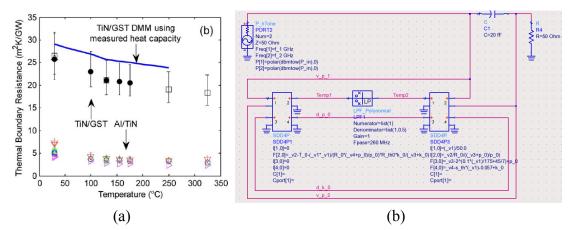

| Figure 5.19. (a) Thermal resistance of GST vs. temperature [148]; (b) ADS schematic with electro-thermal model of a GeTe switch for non-linearity analysis                                                                                                                                                                                              |

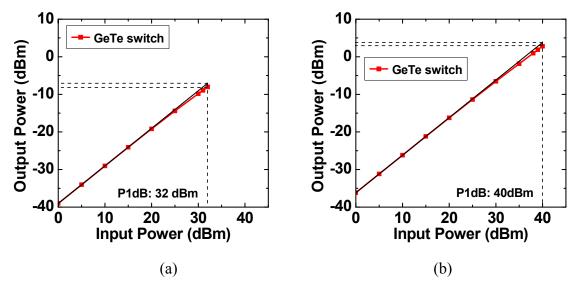

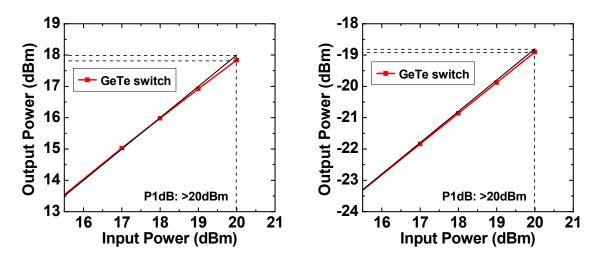

| Figure 5.20. Simulated $P_{1dB}$ of a 3 × 3 $\mu$ m <sup>2</sup> GeTe switch in the amorphous state; (a) 500 MHz and (b) 1 GHz                                                                                                                                                                                                                          |

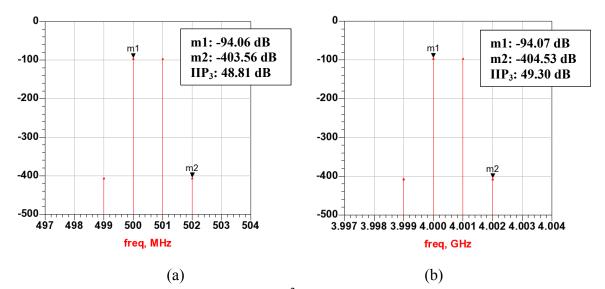

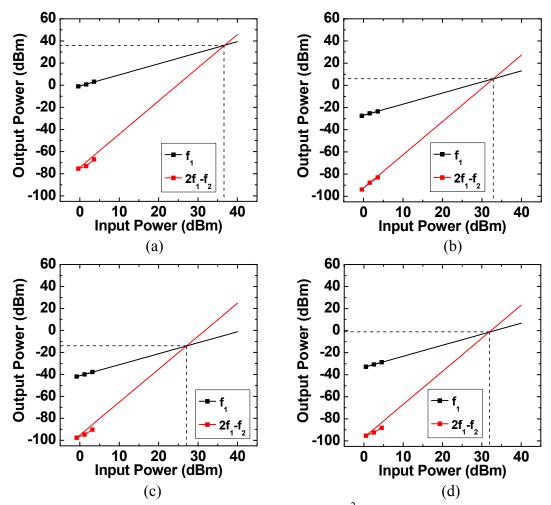

| Figure 5.21. Simulated IIP <sub>3</sub> of a $3 \times 3 \ \mu m^2$ GeTe switch in the amorphous state; (a) 500 MHz with 1 MHz offset and (b) 4 GHz with 1 MHz offset of two-tone input signal 132                                                                                                                                                      |

| Figure 5.22. Measured $P_{1dB}$ of a directly heated $3 \times 3 \ \mu m^2$ PC via; (a) crystalline and (b) amorphous states at 1GHz                                                                                                                                                                                                                    |

| Figure 5.23. Measured IIP <sub>3</sub> of a directly heated $3\times3 \ \mu m^2$ PC via; (a) crystalline state with 50 kHz of frequency offset at 3.9 GHz; (b) amorphous state with 50 kHz of frequency offset at 3.9 GHz; (c) amorphous state with 50 kHz of frequency offset at 500 MHz; (d) amorphous state with 50 kHz of frequency offset at 2 GHz |

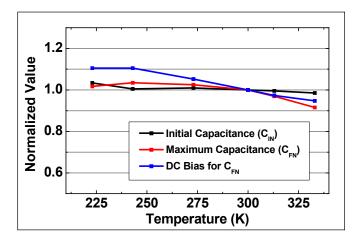

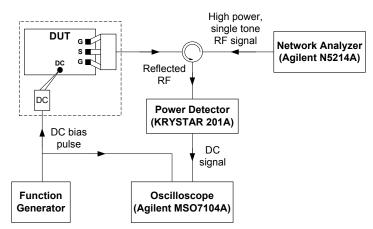

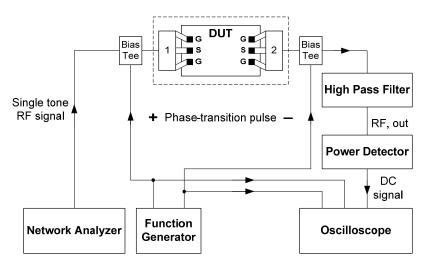

| Figure 5.24. Equipment setup diagram for switching speed measurement of two-port<br>GeTe switch                                                                                                                                                                                                                                                         |

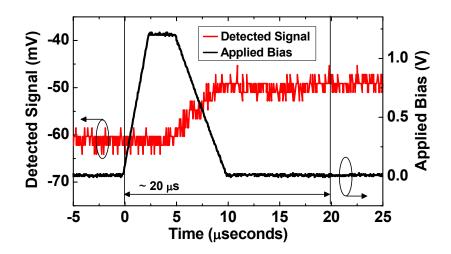

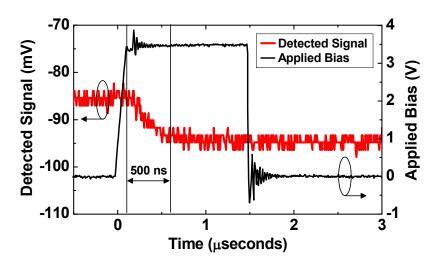

| Figure 5.25. Timing diagram when a 1.2 V pulsed bias with duration of 5 $\mu$ s and falling time of 5 $\mu$ s is applied to the switch for crystallization; the total switching time including stabilization is around 20 $\mu$ s                                                                                                                       |

| •                                                                                                                                                                                                                                                                                                                                                       |

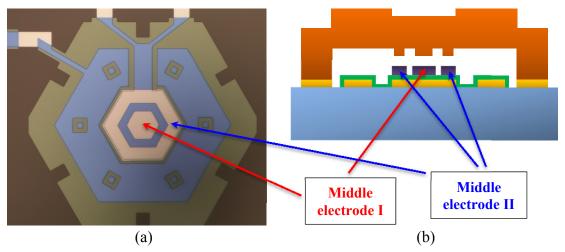

| Figure 6.1. (a) Microscope image of capacitive switch after deposition of the middle electrode layer; (b) cross-section view of a capacitive switch with multiple tuning steps          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

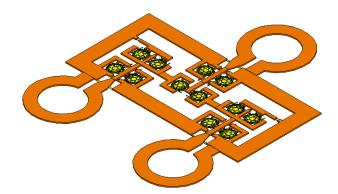

| Figure 6.2. 3D view of a third-order tunable bandpass filter with bandwidth tunability.<br>                                                                                             |

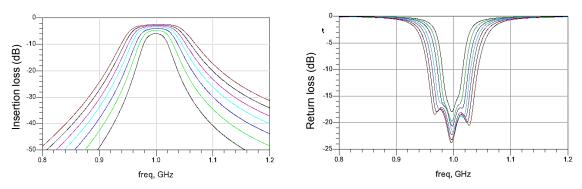

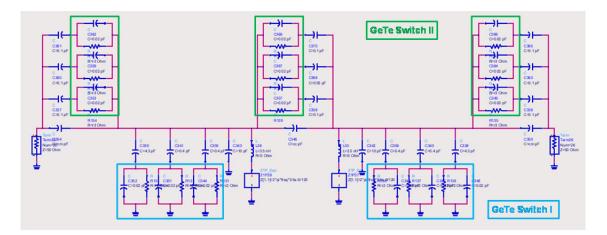

| Figure 6.3. Simulated filter response using the lumped element model; insertion loss (left); return loss (right)                                                                        |

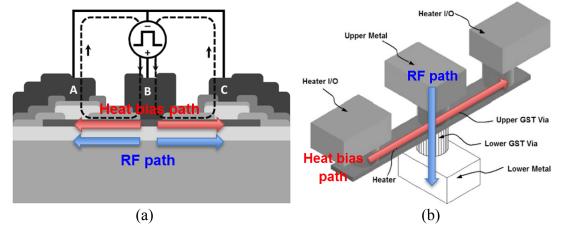

| Figure 6.4. A schematic showing the cross-sectional view of a directly heated phase change switch with separate lines for the heater bias and RF signals                                |

| Figure 6.5. 3D layout of the phase change switch shown in Figure 6.4; 3-D view (left) and top-down view (right)                                                                         |

| Figure 6.6. Simulation result with different overlapped size and GeTe layer thickness; insertion loss at crystalline state (left); isolation at amorphous state (right)                 |

| Figure 6.7. Heat simulation result of the PC switch; when 4 mA is applied for 1 ms in the amorphous state (left); 250 mA is applied for 20 $\mu$ s in the crystalline state (right) 144 |

| Figure 6.8. Equivalent circuit model for a 2nd-order coupled resonator filter initially centered at 800 MHz. Tuning is achieved using GeTe capacitive switches                          |

| Figure 6.9. ADS simulation results for the insertion loss (left) and return loss (right) of a phase change filter                                                                       |

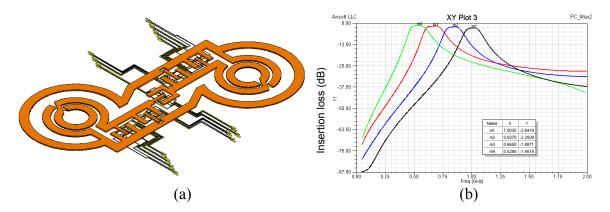

| Figure 6.10. (a) 3D layout of a second-order tunable bandpass filter using phase change switches; (b) HFSS EM simulation result at each tuning stage                                    |

## LIST OF TABLES

| Table 1.1. | Existing wireless standards in UHF and SHF range [1–6].                                                                                             | 2 |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Table 1.2. | Comparison of different tuning mechanisms used to reconfigure RF passives.                                                                          | 7 |

| Table 1.3. | Specifications of tunable front-end filters in the UHF range                                                                                        | 1 |

| Table 2.1. | Target specifications of the tunable capacitor                                                                                                      | 1 |

| Table 2.2. | Parameters of the varactor used in non-linear simulations                                                                                           | 3 |

| Table 3.1. | Tuning configuration of the filter                                                                                                                  | 1 |

| Table 3.2. | Design values of the proposed filter                                                                                                                | 1 |

| Table 3.3. | Simulated filter specifications from 3D EM model                                                                                                    | 3 |

| Table 3.4. | Simulated filter specifications using HFSS 3D EM tool                                                                                               | 5 |

| Table 3.5. | Measured filter specifications at each tuned stage                                                                                                  | 4 |

| Table 3.6. | Comparison between tunable front-end filters in the UHF range                                                                                       | ) |

|            | Maximum $Q$ of inductors with each Cu layer on HR-4k and TR-4k substrates.<br>98                                                                    |   |

| Table 4.2. | Specifications of the HR-Si substrates                                                                                                              | ) |

| Table 4.3. | RF performance and lumped model parameters of capacitive switches 108                                                                               | 3 |

|            | Average, standard deviation, and relative standard deviation of capacitance from initial state of capacitive switches on different HR-Si substrates | 0 |

|            | Electrical parameters of different stoichiometric composition of GST [140],<br>110                                                                  | 5 |

| Table 5.2. | Resistivity vs. maximum heating temperature in 150 nm thick GeTe 120                                                                                | ) |

| Table 5.3. | Resistivity vs. maximum heating temperature in 150 nm thick GeTe | 127 |

|------------|------------------------------------------------------------------|-----|

| Table 6.1. | Simulated filter specifications at each tuned stage.             | 146 |

## LIST OF ABBREVIATIONS

| ACP                            | Air coplanar probe                      |

|--------------------------------|-----------------------------------------|

| ADC                            | Analog-to-digital converter             |

| ADS                            | Advanced design system                  |

| Ag                             | Silver                                  |

| ALD                            | Atomic layer deposition                 |

| AlN                            | Aluminum nitride                        |

| Al <sub>2</sub> O <sub>3</sub> | Aluminum oxide                          |

| BaTiO <sub>3</sub>             | Barium titanate                         |

| BST                            | Barium strontium titanate               |

| BW                             | Bandwidth                               |

| BW <sub>3dB</sub>              | 3dB-bandwidth                           |

| BW <sub>30dB</sub>             | 30dB-bandwidth                          |

| C                              | Capacitance                             |

| CDMA                           | Code division multiple access           |

| CMOS                           | Complementary metal-oxide-semiconductor |

| CPD                            | Critical point dryer                    |

| Cr                             | Chromium                                |

| Cu                             | Copper                                  |

| DC                             | Direct current                          |

| DSP                            | Digital signal processor                |

| DRIE                           | Deep reactive-ion etching               |

| EM                             | Electromagnetic                         |

|                                |                                         |

| $f_c$            | Center frequency                          |

|------------------|-------------------------------------------|

| $f_m$            | Mechanical resonant frequency             |

| GeTe             | Germanium tellurium                       |

| GPS              | Global positioning system                 |

| GSG              | Ground-signal-ground                      |

| GSM              | Global system for mobile communications   |

| GST              | Germanium antimony tellurium              |

| HFSS             | High frequency structural simulator       |

| HR-Si            | High-resistivity silicon                  |

| IF               | Intermediate frequency                    |

| IIP <sub>3</sub> | Third-order input intercept point         |

| ISM              | Industrial, scientific, and medical       |

| КОН              | Potassium hydroxide                       |

| L                | Inductance                                |

| LCP              | Liquid crystal polymer                    |

| LNA              | Low-noise amplifier                       |

| LPCVD            | Low-pressure chemical vapor deposition    |

| LTE              | Long-term evolution                       |

| MEMS             | Microelectromechanical systems            |

| MIM              | Metal-insulator-metal                     |

| NiCr             | Nichrome                                  |

| P <sub>1dB</sub> | 1dB compression point                     |

| PC               | Phase change                              |

| РСВ              | Printed circuit board                     |

| РСМ              | Phase change material                     |

| PECVD            | Plasma-enhanced chemical vapor deposition |

|                  |                                           |

| PNAProgrammable network analyzerPRAMPhase-change random-access memoryPSCParasitic surface chargePtPlatinumPZTLead zirconate titanateQQuality factorRFRadio frequencyRTARapid thermal anneaSAWSurface acoustic waveSDRSoftware defined radioSEMScanning electron microscopeSHFSuper high frequencySiSilicon dioxide |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PSC Parasitic surface charge<br>Pt Platinum<br>PZT Lead zirconate titanate<br>Q Quality factor<br>RF Radio frequency<br>RTA Rapid thermal annea<br>SAW Surface acoustic wave<br>SDR Software defined radio<br>SEM Scanning electron microscope<br>SH Sample and hold<br>SHF Super high frequency<br>Si Silicor     |

| PtPlatinumPZTLead zirconate titanateQQuality factorRFRadio frequencyRTARapid thermal anneatSAWSurface acoustic waveSDRSoftware defined radioSEMScanning electron microscopeSHFSuper high frequencySiSilicor                                                                                                        |

| PZTLead zirconate titanateQQuality factorRFRadio frequencyRTARapid thermal anneatSAWSurface acoustic waveSDRSoftware defined radioSEMScanning electron microscopeSHFSuper high frequencySiSilicor                                                                                                                  |

| QQuality factorRFRadio frequencyRTARapid thermal annealSAWSurface acoustic waveSDRSoftware defined radioSEMScanning electron microscopeSHSuper high frequencySHFSuper high frequencySiSilicor                                                                                                                      |

| RFRadio frequencyRTARapid thermal annealSAWSurface acoustic waveSDRSoftware defined radioSEMScanning electron microscopeSHSample and holdSHFSuper high frequencySiSilicor                                                                                                                                          |

| RTA Rapid thermal anneal<br>SAW Surface acoustic wave<br>SDR Software defined radio<br>SEM Scanning electron microscope<br>SH Sample and hold<br>SHF Super high frequency<br>Si                                                                                                                                    |

| SAWSurface acoustic waveSDRSoftware defined radioSEMScanning electron microscopeSHSample and holdSHFSuper high frequencySiSilicor                                                                                                                                                                                  |

| SDRSoftware defined radioSEMScanning electron microscopeSHSample and holdSHFSuper high frequencySiSilicor                                                                                                                                                                                                          |

| SEMScanning electron microscopeSHSample and holdSHFSuper high frequencySiSilicore                                                                                                                                                                                                                                  |

| SH     Sample and hold       SHF     Super high frequency       Si     Silicor                                                                                                                                                                                                                                     |

| SHF Super high frequency<br>Si Silicor                                                                                                                                                                                                                                                                             |

| Si Silicor                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                    |

| Silicon diovide                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                    |

| SOLT Short-open-load-through                                                                                                                                                                                                                                                                                       |

| SOI Silicon-on-insulator                                                                                                                                                                                                                                                                                           |

| SRF Self-resonant frequency                                                                                                                                                                                                                                                                                        |

| TCB Tunable capacitor bank                                                                                                                                                                                                                                                                                         |

| TaN Tantalum Nitride                                                                                                                                                                                                                                                                                               |

| Ti Titanium                                                                                                                                                                                                                                                                                                        |

| TiN Titanium Nitride                                                                                                                                                                                                                                                                                               |

| UHF Ultra high frequency                                                                                                                                                                                                                                                                                           |

| VHF Very high frequency                                                                                                                                                                                                                                                                                            |

| W Tungsten                                                                                                                                                                                                                                                                                                         |

| WRAN             | Wireless regional area network |

|------------------|--------------------------------|

| XeF <sub>2</sub> | Xenon difluoride               |

| XRD              | X-ray diffraction              |

#### ABSTRACT

### FULLY INTEGRATED HIGH-PERFORMANCE MEMS LUMPED ELEMENT FILTERS FOR RECONFIGURABLE RADIOS

by

#### Yonghyun Shim

#### Chair: Mina Rais-Zadeh

In this research, we present RF MEMS filters which address the most challenging performance requirements of modern RF front-end systems, namely multi-band processing capability, low energy consumption, and small size. These filters not only provide a wide tuning range for multiple-band selection, but also offer low loss, high power handling capability, fast tuning speed, and temperature stability. Two different technologies are considered for tunable lumped element filter targeting UHF range. The first technology is a tunable RF MEMS platform based on surface micromachining, enabling fabrication of continuously tuned capacitors, capacitive and ohmic switches, as well as high-*Q* inductors, all on a single chip. The filter is in a third-order coupled resonator configuration. Continuous electrostatic tuning is achieved using three tunable capacitors with pull-in voltage of less than 40 V. The center frequency of the filter is tuned from 1 GHz to 600 MHz while maintaining a 3 dB-bandwidth of 13 to 14 % and

insertion loss of < 3.5 dB. The temperature stability of the center frequency from 223 K to 323 K is > 2 %. The filter occupies a small size (1.5 cm  $\times$  1.0 cm). This filter shows the best published performance yet in terms of insertion loss, out-of-band rejection, temperature stability, and tuning range.

The second technology is based on a new tuning mechanism utilizing phase-change (PC) materials. PC technology has been investigated and adopted in memory industry due to its fast transition time in nano second range, small size, and high resistance change ratio. Although PC materials offer several benefits, they have not been considered for RF applications because of their limited power handling capability and relatively higher on-resistance in their current form. In this work, germanium tellurium (GeTe) is considered as it offers a low on-resistivity and pronounced resistance change ratio of up to 10<sup>6</sup>. To characterize RF properties of GeTe, different types of RF switches have been fabricated and compared. For improvement of reliability and power handling capability, new structural configurations are proposed and analyzed. Such PC switches can be monolithically integrated with other micromachined components to implement reconfigurable front-end modules, potentially offering high tuning speed, low loss, high linearity, and small size.

### CHAPTER 1.

### **INTRODUCTION TO TUNABLE RF MEMS**

#### **1.1. Reconfigurable Radios**

The largest commercial market in RF MEMS area is currently the wireless handset market, which includes smart phones and tablets, mobile phones, and portable computers. To provide high-end mobile services including video streaming and fast web browsing, frequency allocation and other regulations for wireless communications are constantly updated or amended for high-bit rate and energy-efficient data transmission. Future mobile handsets should support a number of wireless standards with different frequencies, such as WIFI [1], GSM [2], CDMA [3], LTE [4], BLUETOUTH [5], GPS [6], and any newly released standards (Table 1.1). Using existing technologies, a RF signal from each standard is processed separately by a dedicated RF front-end system. Therefore, a number of antennas, switches, phase arrays, and front-end filters are needed, increasing the overall size and cost of the system. This is well shown in Figure 1.1, which is the PCB layout of the iPhone 5 [7].

Recently, the National Broadband Plan [8] has been announced, calling for utilization of multiple channels within a wide range of frequencies (225 MHz - 3.7 GHz).

|                         | 0                     |                                                           |                              |                                       |  |

|-------------------------|-----------------------|-----------------------------------------------------------|------------------------------|---------------------------------------|--|

| Standard Classification |                       | Allocated Frequencies                                     | Channel<br>Bandwidth         | Spectrum Type                         |  |

| Wi-Fi                   | IEEE 802.11<br>(WLAN) | 5.25, 5.6, 5.8 GHz                                        | 20 or 40 MHz                 | Unlicensed<br>802.11a and ISM<br>band |  |

| Bluetooth               | IEEE 802.15<br>(WPAN) | 2.4 GHz                                                   | 1 MHz                        | Unlicensed ISM band                   |  |

| WiMAX                   | IEEE 802.16<br>(WMAN) | 2.3, 2.5, 3.5, 3.7, 5.8 GHz                               | 20 MHz                       | Licensed                              |  |

| EV-DO, EV-DV            | CDMA 2000             | 450, 850, 900 MHz, 1.7,<br>1.8, 1.9, 2.1 GHz              | 1.25 MHz                     | Licensed                              |  |

| UMTS W-CDMA             | UMTS/3GSM             | 0.85, 1.7, 1.9, and 2.1 GHz                               | 10 MHz                       | Licensed                              |  |

| UMTS TDD                | UMTS/3GSM             | 450, 850 MHz, 1.9, 2, 2.5,<br>3.5 GHz                     | 5 MHz                        | Licensed                              |  |

| GPRS, EDGE GSM          |                       | 850, 900 MHz, 1.8, 1.9<br>GHz                             | 200 kHz                      | Licensed                              |  |

| LTE                     | 3GPP                  | 700, 750, 800, 850, 900<br>MHz, 1.7, 1.8, 1.9, 2.1<br>GHz | 1.4, 3, 5, 10,<br>15, 20 MHz | Licensed                              |  |

| GPS GPS                 |                       | 1.2276, 1.57542 GHz                                       | 10.23 MHz                    | Licensed                              |  |

Table 1.1. Existing wireless standards in UHF and SHF range [1–6].

Figure 1.1. The PCB layout of the iPhone 5 [7]; (a) front side; (b) back side.

The purpose of this plan is to provide all Americans with access to the broadband wireless with high data rates exceeding one gigabit per second. To achieve this, a plan similar to the IEEE 802.22 standard [9], [10] for wireless regional area network (WRAN) could be utilized. The 802.22 standard uses cognitive radio techniques; any available channels in UHF/VHF TV bands between 54 and 862 MHz are processed with adaptable radios sensing the spectrum change. However, it is impossible to incorporate several tens of front-end filters for new wireless standards as the size and cost of the handset will increase significantly. This is where RF MEMS can play a unique role; tunable components implemented using the RF MEMS technology can decrease the number of necessary front-end components, reducing the overall handset size, cost, and energy consumption.

For multi-band transceiver implementation, a variety of architectures have been proposed. These architectures can be classified into several categories based on the type of the front-end filters and the topology of the transceivers. The most conventional approach uses multiple surface acoustic wave (SAW) filters and follows the superheterodyne, zero-IF, or low-IF transceiver [11], as shown in the RF transceiver architecture of a commercialized handset, LG GM730 (Figure 1.2 [12]). However, this approach is not applicable to flexible multi-band standards, such as IEEE 802.22, as the number of the required SAW filters will increase, enormously. To cope with this, SAW-less radios [13–15], or so called software defined radios (SDR), have been proposed.

SDR is based on wide-band signal processing in the digital domain after directconversion into the baseband (Figure 1.3) [13]. However, SDR requires high-bit rate analog-to-digital converters (ADC), and as such is power hungry and requires high-end, costly digital signal processors (DSP) as well as ADCs. It also suffers from blocking or saturation issues from strong interfering signals or jammers.

Figure 1.2. The transceiver architecture of LG GM730 [12].

Figure 1.3. Transceiver block diagram of the multi-standard software defined radio [13].

Since SAW filters are hardly tunable and the tuning range is very limited if at all possible, a more practical approach to address the lack of reconfigurability is to integrate tunable passive filters in the transceiver front-end (Figure 1.4 (a)). Using this approach, strong interferences or blocking signals located near the target signal can be removed, to prevent the saturation of following RF circuits, such as the low noise amplifier (LNA) or mixer. This also reduces the stringent dynamic range requirement of the ADC. However, it is still challenging to generate a variety of local oscillators with different frequencies. Another candidate is the RF bandpass filtering transceiver shown in Figure 1.4 (b). In this technique, RF sampling replaces the down-conversion stage and multiple channels can be processed simultaneously. Depending on the bandwidth of the preselect filter, the ADC sampling rate can be from several tens to hundreds of MHz. Even though the required sampling rate is reduced compared to the original SDR architecture, this rate