# Finding and Tolerating Concurrency Bugs

by

Jie Yu

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in The University of Michigan 2013

Doctoral Committee:

Assistant Professor Satish Narayanasamy, Chair Associate Professor Robert Dick Associate Professor Jason Nelson Flinn Professor Scott Mahlke Cristiano Pereira To my family.

#### ACKNOWLEDGEMENTS

First and foremost, I would like to thank my advisor Professor Satish Narayanasamy, for his endless support during the past five years. It has been an honor to work with him and to be one of his first batch of PhD students. From him, I have learnt how to write papers, make presentations, and most importantly, be confident and strong. Satish has given me the freedom to pursue various projects that match my interests. He has also provided countless insightful discussions about my research during our weekly meetings. I appreciate all his contributions of time, ideas, and funding to make my PhD experience productive and stimulating.

I also would like to thank other members of my PhD dissertation committee, Professor Robert Dick, Professor Jason N. Flinn, Professor Scott Mahlke and Dr. Cristiano Pereira. It is no easy task, reviewing a thesis, and I am grateful for their invaluable comments and constructive criticisms that greatly improved my dissertation.

This dissertation is partially funded by National Science Foundation (NSF) and Intel Corporation, and I would like to thank both organizations for their generous support. I would like to thank Dr. Cristiano Pereira and Dr. Gilles Pokam from Intel for their valuable discussions and insights from industry perspectives.

I also would like to thank all my labmates. I would like to thank Dongyoon Lee for sharing ideas and brainstorming with me throughout my PhD studies, Abhayendra Singh for clarifying my uncertainties about memory consistency issues in many occasions, and Chun-Hung Hsiao for working with me on the smartphone project offering me unremitting assistance. Thanks also go to other members in the lab, including Shaizeen Aga and Gaurav Chadha, for making the lab such a comfortable home for me.

My time at Michigan was made enjoyable in large part due to the many friends and groups that became a part of my life. I would like to thank Lujun Fang and Yunjing Xu for always hanging out with me, sharing their visions and big ideas. Special thanks go to Yunjing for taking me to the hospital in midnight when I was bleeding badly. I would like to thank Lujun Fang and Yudong Gao for being my roommates for years, making a sweet home for me. Special thanks go to Yudong for playing basketball with me all the time. Thanks also go to my friends who have not been mentioned yet, including Junxian Huang, Yi Li, Feng Qian, Li Qian, Zhiyun Qian, Zhaoguang Wang, Qiang Xu and Xinyu Zhang, for providing support and friendship that I needed.

Lastly, I would like to thank my family for their unconditional love and support. My hard-working parents, Jianzu Yu and Shuyan Li, have sacrificed their lives for me and provided unconditional love and care. I love them so much, and I would not have made it this far without them. And most of all, I would like to thank my loving, supportive and encouraging wife Panmei Chen. For this PhD, we have been apart for almost three years. This dissertation would not be possible without the love and support from her.

# TABLE OF CONTENTS

| DEDICATIO   | N                                                              |

|-------------|----------------------------------------------------------------|

| ACKNOWLE    | DGEMENTS iii                                                   |

| LIST OF FIG | URES vii                                                       |

| LIST OF TAI | BLES                                                           |

| ABSTRACT    | xi                                                             |

| CHAPTER     |                                                                |

| I. Intro    | duction                                                        |

| 1.1         | Two Hypotheses and Interleaving Idioms                         |

| 1.2         | Finding Concurrency Bugs by Exposing Untested Interleavings    |

| 1.3         | Tolerating Concurrency Bugs by Avoiding Untested Interleavings |

| 1.4         | Contributions                                                  |

| 1.5         | Structure                                                      |

| II. Backg   | ground and Related Work                                        |

| 2.1         | Detecting Concurrency Bugs                                     |

|             | 2.1.1 Data Race Detection                                      |

|             | 2.1.2 Atomicity Violation Detection                            |

| 2.2         | Exposing Concurrency Bugs 14                                   |

|             | 2.2.1 Coverage Driven Testing                                  |

|             | 2.2.2 Stress Testing and Random Testing                        |

|             | 2.2.3 Systematic Testing                                       |

|             | 2.2.4 Active Testing                                           |

|             | 2.2.5 Test Input Generation                                    |

| 2.3         | Tolerating Concurrency Bugs 17                                 |

| III. Encod  | ding Tested Interleavings Using Interleaving Idioms            |

| 3.1         | Two Hypotheses about Concurrency Bugs                          |

| 3.2         | Interleaving Idiom                                             |

| 3.3         | Canonical Idioms                                               |

| 3.4<br>3.4  | Relation with Concurrency Bugs     25                          |

| -           |                                                                |

| 3.5         | Empirical Analysis                                             |

| IV. Expos   | sing Untested Interleavings: Maple 30                          |

| 4.1         | Overview                                                       |

| 4.2        | Online Profiling For Predicting iRoots                                                                     |

|------------|------------------------------------------------------------------------------------------------------------|

|            | 4.2.1 Notations and Terminology 34                                                                         |

|            | 4.2.2 Naive Approach                                                                                       |

|            | 4.2.3 Non-Mutex Happens-Before Analysis                                                                    |

|            | 4.2.4 Mutual Exclusion Analysis                                                                            |

|            | 4.2.5 Online Profiling Algorithm                                                                           |

|            | 4.2.6 Predicting iRoots for Compound Idioms                                                                |

| 4.3        | Actively Testing Predicted iRoots 43                                                                       |

|            | 4.3.1 A Naive Approach                                                                                     |

|            | 4.3.2 Non-preemptive and Strict Priority Scheduler                                                         |

|            | 4.3.3 Complementary Schedules                                                                              |

|            | 4.3.4 Watch Mode Optimization                                                                              |

|            | 4.3.5 Candidate Arbitration                                                                                |

|            | 4.3.6 Dealing with Asynchronous External Events                                                            |

|            | 4.3.7 Compound Idioms                                                                                      |

|            | 4.3.8 Exposing Pre-conditions                                                                              |

| 4.4        | Memoization of iRoots                                                                                      |

| 4.5        | Evaluation                                                                                                 |

|            | 4.5.1 Maple Configuration                                                                                  |

|            | 4.5.2 Usage Scenario 1: Exposing Bugs with Bug Triggering Inputs 56                                        |

|            | 4.5.3     Usage Scenario 2: Coverage-Driven Testing     61       4.5.4     Characteristics of Maple     66 |

| 4.6        | 4.5.4     Characteristics of Maple     60       Summary     68                                             |

| 4.0        |                                                                                                            |

| V. Avoid   | ling Untested Interleavings I: PSet                                                                        |

| 5.1        | Overview                                                                                                   |

| 5.1<br>5.2 |                                                                                                            |

| 0.2        | Encoding Tested Interleavings735.2.1Predecessor Sets (PSets)73                                             |

|            | 5.2.1 Fredecessor Sets (FSets)                                                                             |

|            | 5.2.2 Enertheness of 1 Sets in Avolding Concurrency Bugs                                                   |

|            | 5.2.5 Deriving and Encoding Poets constraints                                                              |

| 5.3        | Enforcing Tested Interleavings                                                                             |

| 0.0        | 5.3.1 Detecting and Enforcing PSet Constraints                                                             |

|            | 5.3.2 Architectural Support                                                                                |

| 5.4        | Evaluation                                                                                                 |

|            | 5.4.1 Bug Avoidance Capability                                                                             |

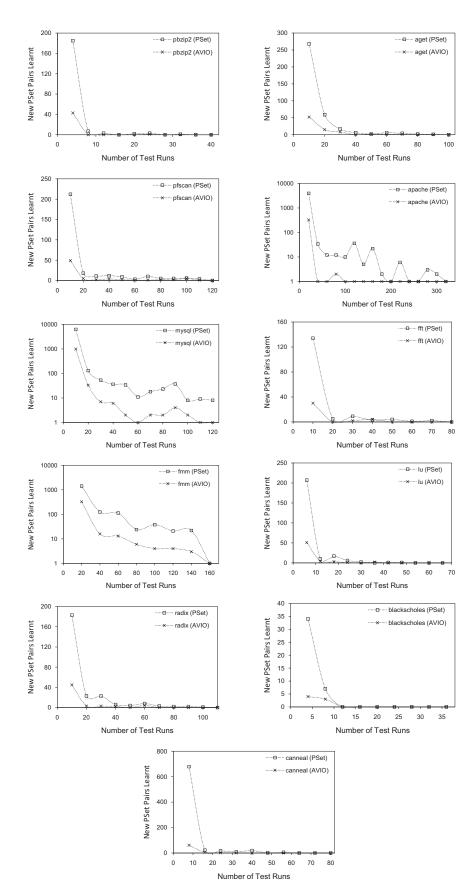

|            | 5.4.2 Learning PSet Constraints                                                                            |

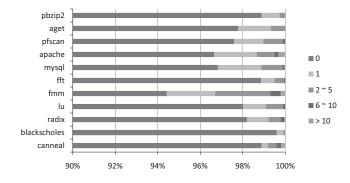

|            | 5.4.3 PSet Constraint Violations in Bug Free Executions                                                    |

|            | 5.4.4 Memory Space Overhead                                                                                |

| 5.5        | Summary                                                                                                    |

| VI. Avoid  | ling Untested Interleavings II: LifeTx                                                                     |

| 6.1        | Overview                                                                                                   |

| 6.2        | Algorithm for Determining LifeTxes                                                                         |

| 0.2        | 6.2.1 Lifeguard Transactions (LifeTxes) and Profiling Algorithm Overview 98                                |

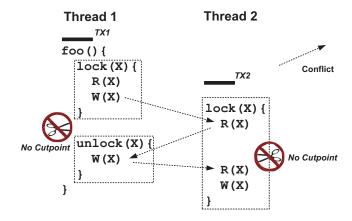

|            | 6.2.2 Checking Conflict Serializability for LifeTxes                                                       |

|            | 6.2.3 Splitting LifeTxes On a Conflict                                                                     |

|            | 6.2.4 Practical Issues                                                                                     |

|            | 6.2.5 Discussion and Limitations                                                                           |

| 6.3        | Runtime Support for LifeTxes                                                                               |

|            | 6.3.1 LifeTx-Stall Design                                                                                  |

|            | 6.3.2 LifeTx-CS Design                                                                                     |

|            | -                                                                                                          |

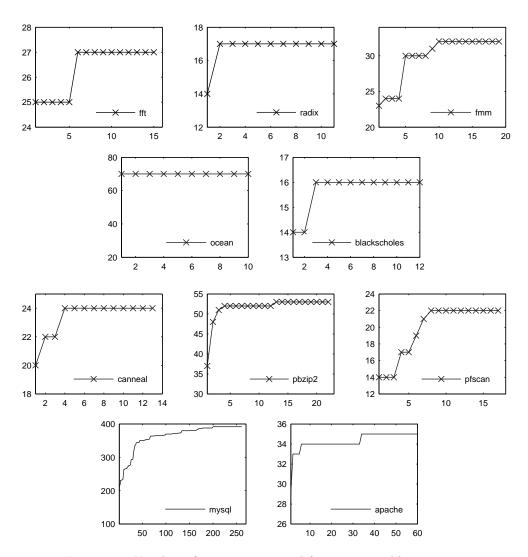

| $6.4 E^{-1}$  | valuatio  | n             |           |         |    | <br> |     | <br> |     | <br> | 113 |

|---------------|-----------|---------------|-----------|---------|----|------|-----|------|-----|------|-----|

|               | 6.4.1     | Experimer     | ital Setu | ιр      |    | <br> |     | <br> |     | <br> | 113 |

|               | 6.4.2     | Learning I    | lifeTxes  |         |    | <br> |     | <br> |     | <br> | 116 |

|               | 6.4.3     | Character     | stics of  | LifeTx  | æs | <br> |     | <br> |     | <br> | 116 |

|               | 6.4.4     | Bug Avoid     | lance Ca  | apabili | ty | <br> |     | <br> |     | <br> | 119 |

|               | 6.4.5     | Performan     | ce Stud   | у       |    | <br> |     | <br> |     | <br> | 121 |

| 6.5 Sı        | ummary    | • • • • • • • |           |         |    | <br> |     | <br> |     | <br> | 124 |

| VII. Future V | Work .    |               |           |         |    | <br> | ••• | <br> |     | <br> | 126 |

| VIII. Conclus | ion       |               |           |         |    | <br> | ••• | <br> | ••• | <br> | 131 |

| BIBLIOGRAPH   | <b>ΙΥ</b> |               |           |         |    | <br> |     | <br> |     |      | 134 |

# LIST OF FIGURES

# Figure

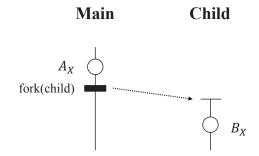

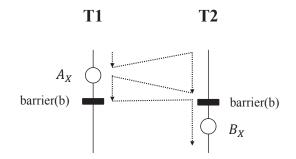

| 3.1  | The canonical idioms for two inter-thread dependencies and two threads                                                                                                                          | 25 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

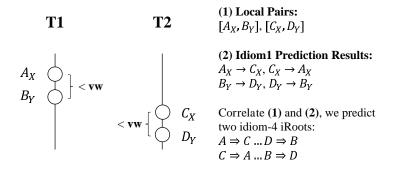

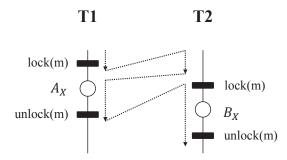

| 3.2  | An idiom1 concurrency bug                                                                                                                                                                       | 26 |

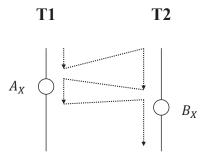

| 3.3  | A real idiom4 concurrency bug from MySQL                                                                                                                                                        | 27 |

| 4.1  | Overview of the framework.                                                                                                                                                                      | 32 |

| 4.2  | Infeasible iRoots due to non-mutex happens-before relations.                                                                                                                                    | 35 |

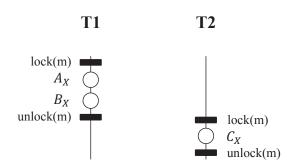

| 4.3  | Infeasible iRoots due to mutual exclusion.                                                                                                                                                      | 37 |

| 4.4  | Predicting iRoots for compound idioms.                                                                                                                                                          | 42 |

| 4.5  | The ideal situation for exposing an idiom 1 iRoot $A \Rightarrow B$                                                                                                                             | 44 |

| 4.6  | The naive approach could deadlock when exposing an idiom<br>1 iRoot $A \Rightarrow B.$                                                                                                          | 44 |

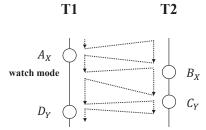

| 4.7  | The situation in which the watch mode is turned on for exposing an idiom1 iRoot $A \Rightarrow B$                                                                                               | 48 |

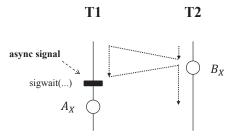

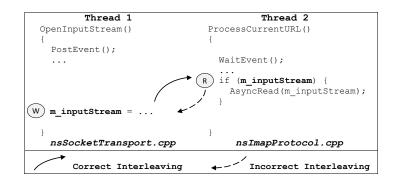

| 4.8  | Problem with asynchronous external events                                                                                                                                                       | 51 |

| 4.9  | Expose a compound idiom iRoot $A \Rightarrow BC \Rightarrow D.$                                                                                                                                 | 51 |

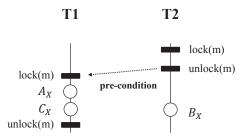

| 4.10 | A pre-condition exists when trying to expose iRoot $A \Rightarrow B$                                                                                                                            | 51 |

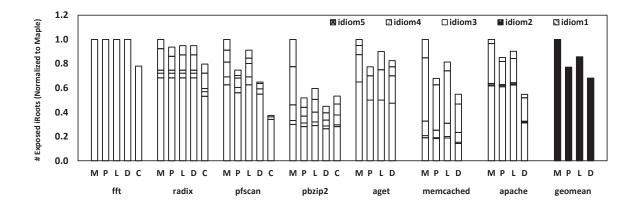

| 4.11 | Comparison with different testing methods using the same amount of time. $M$ stands for Maple, $P$ stands for PCT, $L$ stands for PCTLarge, $D$ stands for RandDelay, and $C$ stands for CHESS. | 63 |

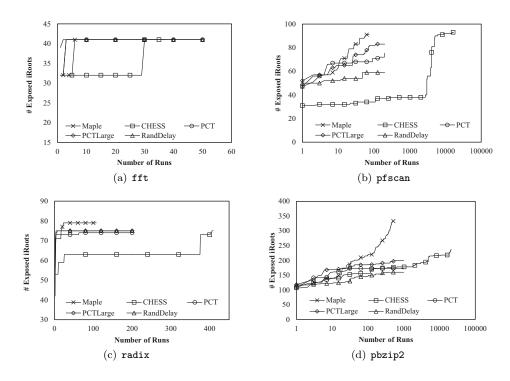

| 4.12 | Comparison with different testing methods. X-axis is the number of test runs, and Y-axis is the total number of iRoots exposed.                                                                 | 65 |

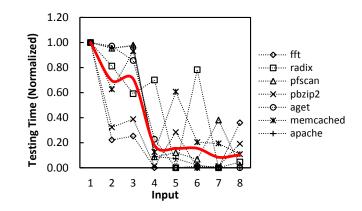

| 4.13 | Memoization saves testing time. Y axis is normalized to the execution time without memoization.                                                                                                 | 66 |

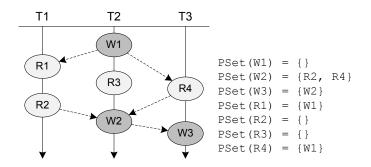

| 5.1  | PSet constraints for an interleaving.                                                                                                                                                           | 74 |

| 5.2  | A data race bug in Mozilla (Mozilla-7 in Table 3.5).                                                                                                                                            | 75 |

| 5.3  | An atomicity violation bug in Mozilla [43] (Mozilla-1 in Table 3.5)                                                                                                                             | 76 |

| 5.4 | An atomicity violation bug in Mozilla, which will not raise an AVIO [43] invariant violation. (Mozilla-4 in in Table 3.5)                                                                                               |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.5 | Order violation bug in Mozilla, which is neither a data race nor an atomicity vio-<br>lation. (Mozilla-9 in Table 3.5)                                                                                                  |

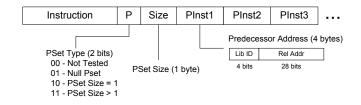

| 5.6 | Format for encoding an instruction's PSet                                                                                                                                                                               |

| 5.7 | Number of test runs required for learning PSets and AVIO invariants                                                                                                                                                     |

| 5.8 | Proportion of static memory instructions with a particular PSet size (normalized to the total number of static memory instructions in the application binary and libraries that were executed in at least one test run) |

| 6.1 | A conflict serializability violation                                                                                                                                                                                    |

| 6.2 | A conflict-serializability violation detected across multiple semantic-segments $104$                                                                                                                                   |

| 6.3 | Conflicts due to memory operations executed in synchronization functions 105                                                                                                                                            |

| 6.4 | Number of test runs required for getting stable cutpoints                                                                                                                                                               |

| 6.5 | Footprint distribution (dynamic)                                                                                                                                                                                        |

| 6.6 | Length distribution (dynamic)                                                                                                                                                                                           |

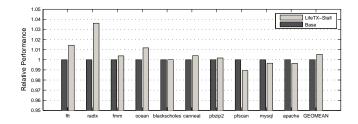

| 6.7 | LifeTx-Stall performance overhead                                                                                                                                                                                       |

# LIST OF TABLES

# <u>Table</u>

| 3.1 | Brief descriptions about concurrency bugs that we used in our studies                                                                                                                                                                                                                                                                                                                                                                                                                              | 28  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.2 | Empirical study on 34 documented bugs                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 29  |

| 4.1 | Bug exposing capability given bug triggering inputs. All the time reported in the table are in seconds. <b>TO</b> stands for timeout (24 hours). In the <b>type</b> column, <b>S</b> stands for synthetic bugs, <b>E</b> stands for extracted bugs, <b>R-K</b> stands for real bugs which are known, and <b>R-U</b> stands for real bugs which are unknown. * The root cause of <b>Bug #12</b> and bug <b>Bug #13</b> have not been confirmed yet. They are exposed when attempting idiom1 iRoots. | 59  |

| 4.2 | Memoization help expose bugs more quickly. All the time reported in the table are in seconds                                                                                                                                                                                                                                                                                                                                                                                                       | 61  |

| 4.3 | Runtime overhead of Maple comparing to native execution time                                                                                                                                                                                                                                                                                                                                                                                                                                       | 66  |

| 4.4 | The success rate of the active scheduler (# successfully exposed iRoots / # total predicted iRoots). For apache and mysql, we experimented with 100 randomly selected candidate iRoots.                                                                                                                                                                                                                                                                                                            | 67  |

| 5.1 | Bug detection capability. Comparing PSet with a happens-before data race detector and AVIO [43].                                                                                                                                                                                                                                                                                                                                                                                                   | 85  |

| 5.2 | Avoiding bugs using PSet constraints. True constraint violations are related to the bug.                                                                                                                                                                                                                                                                                                                                                                                                           | 86  |

| 5.3 | PSet constraint violations in bug-free executions                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 88  |

| 5.4 | Binary Size Increase.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 92  |

| 6.1 | Baseline configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 116 |

| 6.2 | Bug avoidance capability.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 120 |

| 6.3 | Characteristics of critical LifeTxes.                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 121 |

| 6.4 | Runtime statistics for (a) LifeTx-Stall, (b) LifeTx-CS.                                                                                                                                                                                                                                                                                                                                                                                                                                            | 123 |

| 6.5 | Granularity of conflict detection: Block vs Word.                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 124 |

#### ABSTRACT

Finding and Tolerating Concurrency Bugs

by Jie Yu

Chair: Satish Narayanasamy

Shared-memory multi-threaded programming is inherently more difficult than single-threaded programming. The main source of complexity is that, the threads of an application can interleave in so many different ways. To ensure correctness, a programmer has to test all possible thread interleavings, which, however, is impractical. Many rare thread interleavings remain untested in production systems, and they are the major cause for a majority of concurrency bugs.

Given that untested interleavings are the major cause of a majority of the concurrency bugs, this dissertation explores two possible ways to tackle concurrency bugs in this dissertation. One is to expose untested interleavings during testing to find concurrency bugs. The other is to avoid untested interleavings during production runs to tolerate concurrency bugs. The key is an efficient and effective way to encode and remember tested interleavings.

This dissertation first discusses two hypotheses about concurrency bugs: the small scope hypothesis and the value independent hypothesis. Based on these two hypotheses, this dissertation defines a set of interleaving patterns, called interleaving idioms, which are used to encode tested interleavings. The empirical analysis shows that the idiom based interleaving encoding scheme is able to represent most of the concurrency bugs that are used in the study.

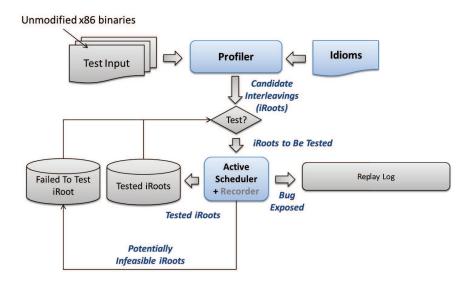

Then, this dissertation discusses an open source testing tool called Maple. It memoizes tested interleavings and actively seeks to expose untested interleavings. The results show that Maple is able to expose concurrency bugs and expose interleavings faster than other conventional testing techniques.

Finally, this dissertation discusses two parallel runtime system designs which seek to avoid untested interleavings during production runs to tolerate concurrency bugs. Avoiding untested interleavings significantly improve correctness because most of the concurrency bugs are caused by untested interleavings. Also, the performance overhead for disallowing untested interleavings is low as commonly occuring interleavings should have been tested in a well-tested program.

## CHAPTER I

# Introduction

Multi-threaded programming is inherently harder than von Neumann style singlethreaded programming. The number of possible states at a program statement exponentially increases with the number of threads executed, as the memory operations in a thread could interleave with the memory operations in the other threads in many different orders. Understanding, testing and verifying the correctness of all possible thread interleavings is impractical. Programmers tend to test only a small fraction of all possible legal thread interleavings in an application before shipping it to customers. The remaining untested interleavings are the major cause of a majority of concurrency bugs.

Given that concurrency bugs are typically caused by untested interleavings, we explore two possible research directions to tackle them. First, we propose a tool, called Maple, that tries to expose as many untested interleavings as possible during testing. This increases the chance of exposing any latent concurrency bug before the program is shipped. Even so, the interleaving space for a given program is so huge that Maple cannot practically expose all untested interleavings. For the remaining untested interleavings, we propose another approach which seeks to avoid them during production runs. This approach has the potential to tolerate most of the concurrency bugs as untested interleavings are the major cause of a majority of concurrency bugs. The key to both techniques is a way to encode and remember tested interleavings, based on which we can either seek to expose untested interleavings during testing, or try to avoid untested interleavings during production runs.

A thread interleaving is typically defined to be the order in which the memory operations are executed by all the threads in an execution. One natural way to encode a tested interleaving is to record the partial order of the memory operations executed by all the threads in an execution. However, this encoding scheme is not suitable for our purpose. Under such an encoding scheme, an encoded tested interleaving is only meaningful for a particular test run and becomes hardly useful when a different program input is used. Therefore, for a given program, there might exist an infinite number of untested thread interleavings. If one randomly picks an untested interleaving to test, the probability of exposing a concurrency bug is low. Avoiding untested interleavings at runtime using such an encoding scheme is also not practical as it is likely that many of the interleavings the system encounters at runtime are not tested. Finally, checking if an interleaving has been tested or not requires checking every memory operations involved in the interleaving, which is very expensive.

Hence, the challenge is to derive a way to encode tested interleavings such that it is generic enough for different program inputs. At the same time, it should be able to capture the set of all tested interleavings so that by exposing or avoiding untested interleavings, we can find and tolerate most of the concurrency bugs. Finally, checking if an interleaving has been tested or not can be carried out efficiently.

To address the above challenges, our high level idea is to define a *finite* set of *interleaving fragments* that can possibly be exposed for a given program. The set of interleaving fragments should be able to represent an infinite number of legal thread

2

interleavings of that program. At the same time, if one manages to expose the set of interleaving fragments, it is sufficient to expose a majority of concurrency bugs in this program. Tested interleavings are encoded using the set of interleaving fragments that are exposed during testing. We want the set of interleaving fragments to be as small as possible such that by exposing an untested interleaving fragment, the probability of finding a concurrency bug is much higher than randomly picking an untested thread interleaving from the infinite legal thread interleaving space.

#### 1.1 Two Hypotheses and Interleaving Idioms

In order to define interleaving fragments, we first discuss two hypotheses we make about concurrency bugs. These two hypotheses are the foundation of this dissertation. The way we encode and remember tested interleavings as well as the tools for exposing and avoiding untested interleavings are all based on these two hypotheses.

The first hypothesis is called *small scope hypothesis*. It is originally proposed by Jackson and Damon [34]. A recent adoption of this hypothesis on concurrency bugs [49] states that most concurrency bugs can be exposed using a small number of preemptions. CHESS [52] exploits this observation to bound the number of preemptions to reduce the search space. Our adoption of this hypothesis is that we focus on those simple concurrency bugs that involve no more than two threads, two variables and two inter-thread dependencies.

Surely there exist concurrency bugs that are more complex, and our technique is not able to handle them. However, previous study has shown that complex concurrency bugs are less likely to be exposed than simple ones [12]. Given the fact that we cannot practically expose all concurrency bugs in a program within a constant time budget, we prefer to spending more time on those concurrency bugs that are more likely to occur in production environment, which are, in order words, the less complex ones.

We propose a second hypothesis about concurrency bugs called *value independent hypothesis*. It states that a majority of concurrency bugs gets triggered if the erroneous inter-thread memory dependencies are exposed, irrespective of the program input and the data values of the shared variables involved in the dependencies. This hypothesis is based on our observation of several concurrency bugs in real-world applications. In fact, this hypothesis is implicitly assumed by many of the previous work on detecting, exposing and tolerating concurrency bugs [43, 44]. Given the value independent hypothesis, it is safe to choose an interleaving encoding scheme that is input and value oblivious.

Based on these two hypotheses, we introduce a set of *interleaving idioms* which we use as a foundation to define interleaving fragments and encode tested interleavings. Each interleaving idiom is a pattern of inter-thread dependencies through shared-memory accesses, which defines a type of interleaving fragments that we are interested in. In this dissertation, we focus on a set of canonical idioms that involve no more than two threads, two variables and two inter-thread dependencies, according to the small scope hypothesis.

An instance of an interleaving idiom is called an *iRoot*, which is represented using a set of static memory instructions. We say an iRoot is exposed in an execution if any part of the thread interleaving in that execution satisfies the interleaving pattern specified by the interleaving idiom and the involving static memory instructions match that specified in the iRoot. We use iRoots to represent interleaving fragments.

The tested interleavings can therefore be encoded using a set of iRoots exposed during test runs. Our empirical analysis shows that such an encoding scheme is able to capture 97% (33 out of 34) of the concurrency bugs <sup>1</sup> we have analyzed.

### 1.2 Finding Concurrency Bugs by Exposing Untested Interleavings

There have been significant work on detecting various kinds of concurrency bugs such as data races [21, 19], atomicity violations [43, 22], order violations [71] and deadlocks [53]. They can be divided into two major categories: static tools and dynamic tools. Static tools detect concurrency bugs by analyzing program code statically. These tools usually produce a large volume of false positives, thus preventing them from being widely adopted by programmers. Dynamic tools, however, can be very precise. They analyze an execution of a program and report potential concurrency issues. However, these dynamic tools can find a concurrency bug only if an appropriate execution is exposed. Exposing thread interleavings that exhibit concurrency bugs is therefore another challenge that we face.

Exposing concurrency bugs is much more difficult than exposing sequential bugs because it demands exploring not only the input space but also the huge thread interleaving space. In fact, almost all the existing testing techniques for multithreaded programs focus on exploring different thread interleavings and assume a fixed program input. One common practice for exposing concurrency bugs is stress testing [18, 12], where a multi-threaded program is subjected to extreme scenarios during a test run. This method is not adequate because executing a program again and again over an input tends to unnecessarily test similar thread interleavings and has less likelihood of exposing a rare buggy interleaving. An alternative to stress testing is systematic testing [26, 52], where the thread scheduler systematically explores all legal thread interleavings for a given test input. However, this approach does not scale well for large programs because of the huge interleaving space for those

<sup>&</sup>lt;sup>1</sup>When we say a concurrency bug, we mean a *static* concurrency bug.

programs. Active testing [59, 73, 69] is another recent development. A typical active testing tool focuses on a specific type of concurrency bugs. It only tests a small set of representative interleavings that are more likely to expose that type of concurrency bugs. As a result, a programmer may not be able to determine whether she should continue testing or not after the active testing tool finishes.

To address the above issues, we propose a coverage driven testing tool, called Maple, for exposing concurrency bugs. Maple memoizes past tested interleavings using the idiom based encoding scheme discussed above, and guides each future test run to explore new untested interleavings. It leverages the value independent hypothesis to test for an interleaving only once, and avoids testing the same thread interleaving again and again across different test inputs. Thus, the number of thread interleavings to test would progressively reduce as we test for more inputs. Our experiences in using Maple to test real-world applications shows that Maple is able to expose interleavings and exposing concurrency bugs faster than other existing testing techniques for multi-threaded programs. We also find 3 previously unknown bugs, which further demonstrates the bug exposing capability of Maple.

#### 1.3 Tolerating Concurrency Bugs by Avoiding Untested Interleavings

Even with a state-of-the-art testing tool like Maple, we cannot practically test all thread interleavings of a given program because of its huge interleaving space. For the remaining untested interleavings, one promising approach is to avoid them during production runs. This improves correctness because untested interleavings are the major cause of a majority of concurrency bugs. At the same time, avoiding untested interleavings at runtime should have little performance impact as the commonly occuring interleavings should already be tested for a well-tested program. Concurrency bug avoidance technique [64, 62, 45] has gained increasing attentions recently. It serves as the last safety net for the production system to prevent the concurrency bugs from manifesting in production runs. Some techniques integrate dynamic bug detection tools with checkpoint and re-execution systems [62, 64]. In these tools, once a bug is detected, the program will be rolled back to a previous checkpoint and re-execute so as to bypass the buggy interleavings. Other techniques [45] limit the freedom that threads can interleave in production systems such that some types of concurrency bugs will less likely to be exposed in production runs. For example, Atom-Aid [45] dynamically groups instructions into chunks and enforces a serial order between them. However, none of the previous technique takes tested interleavings into account and actively seeks to avoid untested interleavings. As a result, they are very sensitive to false positives, thus limiting their capabilities on avoiding variety of concurrency bugs.

In this dissertation, we propose two runtime system designs for tolerating concurrency bugs. Both systems remember tested interleavings and actively seek to avoid untested interleavings in production runs. Though possible, a software solution would incur significant performance overhead to the runtime system. Therefore, a hardware solution is a must. We first discuss a customized shared memory multiprocessor design for tolerating concurrency bugs. Like Maple, it encodes tested interleavings based on interleaving idioms. However, to ensure a complexity-effective hardware design, we only consider the simplest interleaving idiom which involves only one inter-thread dependency. Even though, we are still able to avoid at least 60% of the concurrency bugs according to our empirical analysis. We encode the tested interleavings in a program's binary executable using *Predecessor Set* (PSet) constraints. These constraints are efficiently enforced at runtime using processor support, which ensures that the runtime follows a tested interleaving. We analyze 17 bugs in open source applications and show that, by enforcing PSet constraints, we can avoid variety of concurrency bugs.

Though the PSet based runtime system is effective in tolerating many types of concurrency bugs, it has two major drawbacks. First, since we only consider the simplest interleaving idiom that involves only one inter-thread dependency due to hardware complexity concern, the system cannot avoid those concurrency bugs that involve multiple variables and inter-thread dependencies. For example, it cannot avoid multi-variable atomicity violations [41]. Second, the technique requires nontrivial changes to the commodity hardware, preventing it from being widely adopted.

As Hardware Transactional Memory (HTM) becoming a reality [2], we propose another runtime system design, called LifeTx, to tolerate concurrency bugs. It is based on a new type of interleaving constraints called *lifeguard transaction* (LifeTx), which is designed to be enforcible by HTM. Lifeguard transactions are similar to the programmer specified transactions [30, 32] in that it instructs the runtime to execute them in a serializable order. The difference is that LifeTxes are automatically derived based on interleavings observed during testing. LifeTx constraints can be efficiently enforced by a new hardware design similar to the eager conflict detection capability that exist in a conventional hardware transactional memory (TM) systems [32, 48], but without the need for versioning, rollback and unbounded TM support [8]. This greatly simplify the hardware design. Our experiments show that LifeTx is able to avoid 11 out of 12 atomicity violation bugs, including multi-variable atomicity violations, with only 0.6% performance overhead on average.

It is not unusual that the production environments (e.g. program inputs, hardware platforms, OS workloads) are substantially different from the testing environments

and the frequencies with which particular interleavings occur might be different from what we observed during testing. To understand the degree to which such heterogeneity between testing and production environments can affect the effectiveness and efficiency of our interleaving constrained systems, we make sure that the program inputs used in production runs are different from those used in testing in all of our experiments. Moreover, we try to use different hardware platforms and operating systems for testing and production runs. For instance, in LifeTx, we simulate the production environment in a simulator which is configured to be very different from the real machine in which testing is conducted. In spite of that, our interleaving constrained systems are still effective in avoiding concurrency bugs with little performance overhead as indicated by our results, which provides some evidences about the ability of our technique in tolerating the heterogeneity between testing and production environments. Nevertheless, if other factors which we have not studied cause performance problems in productions runs, we always have a choice to turn off the protection to recover performance if we find the performance overhead is too high and outweighs the extra reliability we get.

#### 1.4 Contributions

In summary, this dissertation makes the following contributions:

• We discuss two hypotheses about concurrency bugs: the small scope hypothesis that we adopt and the value independent hypothesis that we propose. Based on these two hypotheses, we define a set of interleaving idioms which we use to encode tested interleavings. Being able to encode tested interleavings enables us to build better tools for finding and tolerating concurrency bugs as we can concentrate on exposing and avoiding untested interleavings.

- We build a coverage driven testing tool called Maple. It memoizes tested interleavings based on interleaving idioms and actively seeks to expose untested thread interleavings as much as possible. We discuss our experiences in using the tool to expose 13 known and unknown bugs in real-world applications such as Apache and MySQL. Our results show that Maple is able to expose interleavings and expose concurrency bugs faster than other conventional testing techniques.

- We propose a customized shared memory multi-processor design for tolerating concurrency bugs. It is optimized for the simplest interleaving idiom which only involves one inter-thread dependency. We encode the tested interleavings in a program's binary executable using Predecessor Set (PSet) constraints. These constraints are efficiently enforced at runtime using processor support, which ensures that the runtime follows a tested interleaving. We analyze 17 concurrency bugs in open source applications such as MySQL, Apache, Mozilla, etc., and show that, by enforcing PSet constraints, we can avoid not only data races and atomicity violations, but also other forms of concurrency bugs.

- Following the PSet work, we discuss another hardware design for tolerating atomicity violation bugs. It is based on a new interleaving constraints called lifeguard transaction (LifeTx). LifeTx constraints can be efficiently enforced by a new hardware design similar to the eager conflict detection capability that exist in a conventional Hardware Transactional Memory (HTM) systems, but without the need for versioning, rollback and unbounded TM support. We show that 11 out of 12 atomicity violation bugs in programs like Apache, MySQL and Mozilla could be avoided using the proposed approach for only 0.6% performance overhead on average.

We have made several contributions to open source community. We released a set of concurrency bugs that we collected from a few open source applications [1]. This online bug database has already been used and cited by dozens of research papers. We also made Maple, along with a dynamic analysis framework for concurrency programs, available to the public under the Apache 2.0 license [4]. It has already been adopted by a few researchers.

#### 1.5 Structure

This dissertation is organized as follows. Chapter II discusses the background and the related work on finding and tolerating concurrency bugs. Chapter III defines the interleavings idioms and discuss two hypotheses about concurrency bugs which we use as a foundation of this dissertation. Chapter IV presents Maple, a coverage driven testing tool for exposing concurrency bugs. Chapter V and Chapter VI discuss two approaches for tolerating concurrency bugs. Chapter V describes the PSet based interleaving constrained shared memory multi-processor. Chapter VI discusses LifeTx, a transaction based approach for tolerating atomicity violation bugs. We discuss our future work in Chapter VII and conclude the dissertation in Chapter VIII.

## CHAPTER II

### **Background and Related Work**

In this chapter, we discuss previous work on finding and tolerating concurrency bugs. We first discuss existing approaches on detecting concurrency bugs (Section 2.1). Then, we discuss current testing techniques for exposing concurrency bugs (Section 2.2). Finally, we discuss existing runtime system solutions for tolerating concurrency bugs (Section 2.3).

#### 2.1 Detecting Concurrency Bugs

Concurrency bug detection is among one of the most widely studied techniques for finding concurrency bugs. Numerous tools have been made to find data races [19, 77, 21], atomicity violations [24, 43, 22], deadlocks [53] and other forms of concurrency bugs [71]. These tools report potential concurrency errors in a program either by analyzing the program statically (static tools), or by analyzing its dynamic executions (dynamic tools).

Static bug detection tools [19, 77, 53, 24, 41] predict concurrency bugs in a program by analyzing the program statically. They usually do not produce false negatives. However, one of the common problems with many static bug detection tools is that they produce a large volume of false positives. The reason is, without knowing the actual program states at runtime, these tools usually make conservative assumptions about program executions, many of which are not feasible. Because of the high false positive rate, static bug detection tools are not widely adopted by programmers.

Dynamic bug detection tools [21, 43, 22, 85, 80], however, can be very precise and produce no false positive [21, 22]. They monitor dynamic program executions and report concurrency errors that manifest in those executions, or predict errors that will potentially manifest in alternate executions. Since dynamic bug detection tools rely on dynamic program executions, they might produce false negatives because some bugs can only be detected under specific interleavings. Typically, they do not actively seek to perturb program executions to reduce false negatives. Another disadvantage of dynamic bug detection tools is that the runtime overhead is usually high because of the program monitoring cost.

#### 2.1.1 Data Race Detection

A data race can be defined as a pair of memory accesses to the same memory location, where at least one of the accesses is a write, and neither one happens-before the other. Dynamic data race detectors can be classified into two major categories: happens-before based and lockset based. A happens-before data race detector [55] finds only the data races that manifest in a given program execution. Lockset based techniques [68] can predict data races that have not manifested in a given program execution, but can report false positives.

Not all data races are harmful data races [54]. Many of the data races in production systems are benign, as programmers intentionally allow data races to optimize performance. Programmer constructed synchronizations could also result in benign data races. Benign data races also tends to be frequent, as opposed to harmful data races [54]. Therefore, a data race is really a heuristic, which is used to detect a particular interleaving pattern (concurrent memory accesses with no happens-before relation between them) that strongly correlates with the concurrency bugs that programmers tend to make.

#### 2.1.2 Atomicity Violation Detection

Atomicity violations is another major source of concurrency errors [82, 43, 58, 20, 7, 22]. An atomicity violation occurs when a programmer assume a code region to be atomic, but fails to enforce its atomicity. Most of the atomicity violation detectors rely on programmers to specify the atomic regions through annotations. Some tools [82, 43, 41] use heuristics to automatically infer atomic regions. Detecting atomicity violations becomes straightforward once the atomic regions are determined.

#### 2.2 Exposing Concurrency Bugs

Concurrency bug detection is one way to find concurrency bugs. Another way to find concurrency bug is to actually expose them in real executions. In this section, we discuss previous work on concurrent software testing.

#### 2.2.1 Coverage Driven Testing

Coverage metrics for single-threaded programs are well studied in the literature. However, defining an effective coverage metric for multi-threaded programs is much more difficult and remains an open problem. There have been a few studies on coverage metrics for concurrent programs [74, 83, 11, 40, 70, 38]. Taylor et al. [74] presented a family of coverage criteria for concurrent Ada programs. All-du-path [83] is a coverage metric for concurrent programs which is based on definition-use pairs. Sherman et al. [70] discussed a few coverage metrics based on synchronizations and inter-thread dependencies. However, none of these work discusses a synergistic set of testing tools that can help programmers achieve high coverage for the proposed coverage metric and analyzes its effectiveness in exposing concurrency bugs.

#### 2.2.2 Stress Testing and Random Testing

Stress testing is still widely used in software industry today. A parallel program is subjected to extreme scenarios during testing with the hope of increasing the likelihood of exposing buggy interleavings. This method is clearly inadequate since naively executing a program again and again over an input tends to unnecessarily test similar thread interleavings. A few techniques have been proposed to improve stress testing. The main idea is to randomize the thread interleavings so that different thread interleavings will be exercised in different test runs. These techniques mainly differ in the way in which they randomize thread interleavings. For example, Con-Test [18] injects random delays at synchronization points. PCT [12] assigns a random priority to each thread and changes priorities at random points during an execution. However, all of these random testing techniques still suffer a common problem: the probability of exposing a rare interleaving that can trigger a concurrency bug is very low given that the interleaving space is so huge.

#### 2.2.3 Systematic Testing

An alternative to stress testing is systematic testing [31, 26, 52, 78], which tries to explore all possible thread interleavings for each test input. Even with partial order reduction techniques [25, 23], the number of thread interleavings to test for a given input is still huge. Therefore, a few heuristics have been proposed to further reduce the testing time at the cost of missing potential concurrency errors. CHESS [52] bounds the number of preemptions in each test run. HaPSet [78] records PSet (discussed in Chapter V) during testing and guides the systematic search towards those interleavings that can produce new PSet dependencies. Even though, these tools still suffer from scalability problem, especially for long-running programs. Furthermore, these tools do not have a way to remember tested interleavings across different inputs. Finally, systematic testing tools usually require a closed unit testing environment which is not easy to setup in practice. However, systematic testing tools do have one distinct advantage in that they can provide certain guarantees to find a concurrency bug in a program for a given input.

#### 2.2.4 Active Testing

Active testing has recently emerged as a new way to test concurrent software [69, 59, 58, 73, 39, 33, 36]. A typical active testing tool has two phases: a prediction phase and a validation phase. In the prediction phase, active testing tools use approximate bug detectors to predict potentially buggy thread interleavings in a program. Then, in the validation phase, an active scheduler will try to exercise each of the suspicious buggy interleavings in a real execution to verify whether it is really a bug or just a false positive.

In the prediction phase, active testing tools use either static or dynamic analysis techniques to predict certain types of concurrency bugs in a program such as data races [69], atomicity violations [59, 58, 73], atomic-set serializability violations [39, 33], and deadlocks [36]. The interleaving patterns of these tools represent erroneous interleaving patterns and target certain types of concurrency bugs. Therefore, they are not generic. For a given test input, after actively testing for all the predicted buggy thread interleavings, a programmer may not be able to determine whether she should continue testing other thread interleavings for the same input or proceed to test a different input.

There are two common ways in which validation can be performed. One way is to precisely compute an alternate schedule from the observed schedule such that the computed alternate schedule is guaranteed to expose a buggy thread interleaving. The computed alternate schedule will then be enforced during an execution [73, 33, 37]. However, computing an alternate schedule precisely is usually very expensive. It typically involves changing the relative order of independent events in an observed trace and making sure that the transformed trace is feasible. Therefore, this solution not suitable if the goal is to achieve high interleaving coverage.

The other approach is to use heuristics, usually best effort, to expose predicted interleavings [69, 59, 58, 39, 36]. For example, CTrigger [59] injects time delays at certain points to increase the chance of exposing buggy interleavings.

#### 2.2.5 Test Input Generation

Test input generation is a testing technique that can be used to achieve high code coverage [27, 13, 28, 57]. For a given program, their goal is to generate test inputs so that testing the program with the generated test inputs can cover most of the code in the program. This technique is typically for single-threaded programs and is orthogonal to what we are doing in this dissertation.

#### 2.3 Tolerating Concurrency Bugs

Bug avoidance and tolerating techniques have gained increasing interests recently. They serve as the last safety net to prevent concurrency bugs from manifesting in production systems. The main idea is to limit the freedom that threads can interleave so that some concurrency bugs can be avoided. Some techniques integrate dynamic bug detection tools with checkpoint and re-execution systems [62, 64]. In these tools, once a bug is detected, the program will be rolled back to a previous checkpoint and re-execute so as to bypass the buggy interleavings. Such systems have two major drawbacks. First, the bug detection tools used are optimized for reducing false positives, which could limit their capabilities on avoiding variety of concurrency bugs. Second, supporting checkpoint and re-execution is usually heavyweight and complex.

Atom-Aid [45] is a seminal work on tolerating concurrency bugs. It leverages the chunk-based execution model described in [14] in which the processor dynamically constructs chunks and enforces a serial order between them. The authors show that many concurrency bugs can be probabilistically avoided using such an execution model. However, it is optimized for avoiding single-variable atomicity violations. For other concurrency bugs, though it can still avoid them sometimes, it is purely by chance.

ISOLATOR [65] and ToleRace [67] detect and avoid one specific type of concurrency errors: asymmetric data races. An asymmetric data race occurs when one thread obeys the locking discipline correctly while some other threads do not. Both systems can efficiently detect and avoid asymmetric data races by maintaining a shadow memory copy for each critical section and updating it speculatively.

Deterministic execution [17, 56] constrains the thread interleavings to provide a guarantee that any execution of a multi-threaded program would yield the same output as long as the input remains the same. In other words, they guarantee a deterministic order of all memory accesses for a given program input. This technique also reduces the freedom that threads can interleave at runtime, thereby can tolerate concurrency bugs at some degree. It could also help programmers in reproducing bugs. However, for a given input, the system chooses the deterministic order based on arbitrary program events (for example, number of retired stores). As a result, the chosen deterministic order is not going to be more correct than a random order chosen by the current systems. Therefore, a programmer would still have to test all legal interleavings to ensure concurrency bug free. This is a fundamental problem with the shared-memory multi-threaded programming model, which we seek to address in this dissertation.

### CHAPTER III

# Encoding Tested Interleavings Using Interleaving Idioms

As we mentioned in Chapter I, the key of this dissertation is an efficient and effective way to encode tested interleavings. Based on that, we can either expose untested interleavings during testing (Chapter IV), or avoid untested interleavings at runtime (Chapter V and Chapter VI).

A thread interleaving is typically defined to be the order in which the memory operations are executed by all the threads in an execution. One natural way to encode a tested interleaving is to record the partial order of the memory operations executed by all the threads in an execution. However, this encoding scheme is not suitable for our purpose. Under such an encoding scheme, an encoded tested interleaving is only meaningful for a particular test run and becomes hardly useful when a different program input is used. Therefore, for a given program, there might exist an infinite number of untested thread interleavings. If one randomly picks an untested interleaving to test, the probability of exposing a concurrency bug is low. Avoiding untested interleavings at runtime using such an encoding scheme is also not practical as it is likely that many of the interleavings the system encounters at runtime are not tested. Finally, checking if an interleaving has been tested or not requires checking every memory operations involved in the interleaving, which is very expensive. In this chapter, we discuss our approach for encoding tested interleavings. Our idea is to define a *finite* set of *interleaving fragments* that can possibly be exposed for a given program. The set of interleaving fragments should be able to represent an infinite number of legal thread interleavings of that program. At the same time, if one manages to expose the set of interleaving fragments, it is sufficient to expose a majority of concurrency bugs in this program. Tested interleavings are encoded using the set of interleaving fragments that are exposed during testing. We want the set of interleaving fragments to be as small as possible such that by exposing an untested interleaving fragment, the probability of finding a concurrency bug is much higher than randomly picking an untested thread interleaving fragment is tested or not can be carried out quite efficiently.

In order to define interleaving fragments, we first discuss two hypotheses we make about concurrency bugs (Section 3.1). Based on these two hypotheses, we introduce interleaving idioms and iRoots which we use to represent interleaving fragments (Section 3.2). Then, we introduce a set of canonical interleaving idioms that we focus on (Section 3.3), and discuss the relation between interleaving idioms and concurrency bugs (Section 3.4). Finally, we present our empirical analysis on 34 documented bugs to show the effectiveness of our idiom based interleaving encoding scheme (Section 3.5).

#### 3.1 Two Hypotheses about Concurrency Bugs

We first discuss two hypotheses we make about concurrency bugs. As we mentioned in Chapter I, these two hypotheses are the foundation of this dissertation.

The first hypothesis is called *small scope hypothesis*. It is originally proposed

by Jackson and Damon [34]. A recent adoption of this hypothesis on concurrency bugs [49] states that most concurrency bugs can be exposed using a small number of preemptions. CHESS [52] exploits this observation to bound the number of preemptions to reduce the search space. Our adoption of this hypothesis is that we focus on those simple concurrency bugs that involve no more than two threads, two variables and two inter-thread dependencies.

Surely there exist concurrency bugs that are more complex, and our technique is not able to handle them. However, previous study has shown that complex concurrency bugs are less likely to be exposed than simple ones [12]. Given the fact that we cannot practically expose all concurrency bugs in a program within a constant time budget, we prefer to spending more time on those concurrency bugs that are more likely to occur in production environment, which are, in order words, the less complex ones.

The second hypothesis is called *value independent hypothesis*. This hypothesis is proposed by us. It states that a majority of concurrency bugs gets triggered if the erroneous inter-thread memory dependencies are exposed, irrespective of the data values of the shared variables involved in the dependencies. This hypothesis is based on our observation of several concurrency bugs in real-world applications, which is shown in Section 3.5. In fact, this hypothesis is implicitly assumed by many of the previous work on detecting, exposing and tolerating concurrency bugs [43, 44].

#### 3.2 Interleaving Idiom

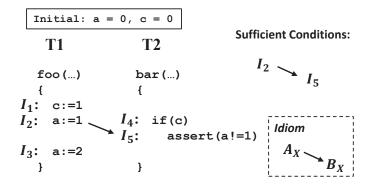

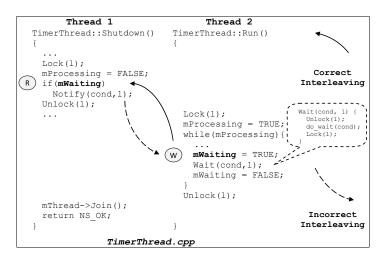

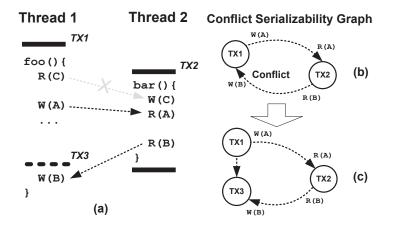

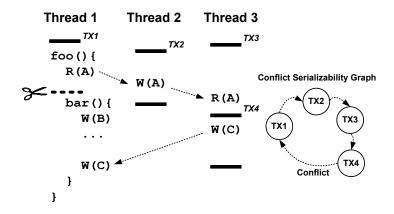

Based on these two hypotheses, we introduce interleaving idioms and iRoots which we use to represent interleaving fragments. An *interleaving idiom* is a pattern of inter-thread dependencies and the associated memory operations. An inter-thread memory dependency (denoted using  $\Rightarrow$ ) is an immediate (read-write or write-write) dependency between two memory accesses in two threads. A memory access could be either to a data or a synchronization variable. For example, the simplest interleaving idiom is shown in the dotted box in Figure 3.2. The arrow in the idiom represents an inter-thread memory dependency.  $A_X$  and  $B_X$  represent two conflicting memory accesses where A and B are static instruction addresses.

A dynamic instance of an idiom in a program's execution is called as an *interleaving root* (iRoot). A memory access in an iRoot is represented using the static address of the memory instruction. We say that an iRoot is exposed in an execution if any part of the thread interleaving in that execution satisfies the interleaving pattern specified by the interleaving idiom and the involving static memory instructions match that specified in the iRoot. For example, consider the execution shown in Figure 3.2. For the given idiom shown in the dotted box, three iRoots of that idiom are exposed in this execution:  $I_1 \Rightarrow I_4$ ,  $I_2 \Rightarrow I_5$  and  $I_5 \Rightarrow I_3$ . We propose to use iRoots to represent interleaving fragments. Tested interleavings can therefore be encoded using the set of iRoots that are exposed during test runs.

Notice that the definitions of interleaving idiom and iRoot are oblivious to the data values of the shared variables involved in the inter-thread dependencies. In order words, if an iRoot has been already exposed during an earlier execution for some test input, we say this iRoot is exposed and we will not seek to expose the same iRoot again even for a different test input. This is driven by the value independence hypothesis we just discussed. Moreover, for a given set of interleaving idioms, the set of possible iRoots of those idioms in a given program is finite, which satisfies our needs for interleaving fragments.

#### 3.3 Canonical Idioms

As we discussed above, interleaving idioms should be generic enough such that, by exposing their iRoots, most concurrency bugs could be triggered. At the same time, the set of iRoots that needs to be tested, called coverage domain, should be small enough that, the probability of exposing an unknown concurrency bug is high when an untested iRoot is exposed. To meet these competing demands, we make an assumption that most concurrency bugs can be exposed using simple thread interleaving patterns. This assumption is inspired by the small scope hypothesis just discussed.

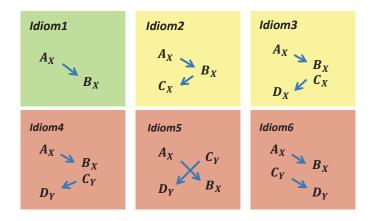

We study a set of canonical idioms that can be constructed for one or two interthread dependencies (which implies there can be only one or two shared-variables) involving no more than two threads. Figure 3.1 enumerates the canonical set of idioms for two inter-thread dependencies and two threads. There are six idioms in total. We refer to idiom1 as a simple idiom, and the rest as compound idioms. For compound idioms, to reduce the coverage domain without significantly compromising the ability to expose a concurrency bug, we include two additional constraints. First, the number of instructions executed between two events in the same thread should be less than a threshold. We refer to this threshold as the vulnerability window (vw). Second, in an idiom, if atomicity of two memory accesses in a thread T to a variable V is violated by accesses in another thread, we disallow accesses to V between those two accesses in the thread T. For example, in idiom3 we do not allow any access to the variable X between the two memory accesses  $A_X$  and  $D_X$ , but there could be accesses to X between  $B_X$  and  $C_X$ .

Six idioms in Figure 3.1 can represent interleavings required to expose a majority

Figure 3.1: The canonical idioms for two inter-thread dependencies and two threads.

of concurrency bugs: atomicity violations, including both single variable (idiom1, idiom2, idiom3) and multi-variable (idiom4, idiom5); typical deadlock bugs (idiom5), and generic order related concurrency bugs (idiom1, idiom6). These interleaving patterns are more general than the anomalous patterns used in prior studies to find specific classes of concurrency bugs [69, 59, 73].

# 3.4 Relation with Concurrency Bugs

The iRoot of a concurrency bug specifies the minimum set of inter-thread dependencies and the associated memory or synchronization accesses, which if satisfied, are sufficient to trigger that bug in an execution. Therefore, for a given concurrency bug, we can either seek to expose its iRoot during testing to find it, or try to avoid its iRoot at runtime to tolerate it. Of course, higher order iRoots may also expose the same concurrency bug, but for the purpose of classifying concurrency bugs, we consider the iRoot that provides the minimum set of sufficient interleaving conditions.

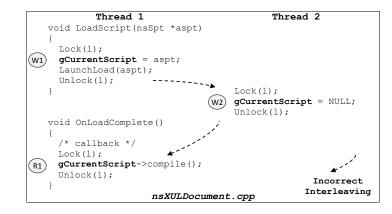

Figure 3.2 shows an example of a concurrency bug. The idiom of the bug is shown in the dotted box. A and B represent static instructions in the program and X represents a memory location. The arrows denote inter-thread dependencies. The

Figure 3.2: An idiom1 concurrency bug.

bug is triggered whenever the inter-thread dependency  $I_2 \Rightarrow I_5$  is satisfied in an execution. Therefore, this is an idiom1 bug and its iRoot is  $I_2 \Rightarrow I_5$  which we refer to as *idiom-conditions*.

Note that there exists an inter-thread dependency  $I_1 \Rightarrow I_4$  that must also be satisfied before the iRoot  $I_2 \Rightarrow I_5$  can be exposed. This dependency affects the control flow of the thread T2 and determines whether I5 is executed or not. We refer to such necessary conditions which must be satisfied in order to satisfy the idiom-conditions as *pre-conditions*. We choose not to include pre-conditions into the iRoot of a concurrency bug because these conditions might be irrelevant to the root cause of the bug and can typically be derived automatically based on the idiomconditions [37].

Also notice that  $I_5 \Rightarrow I_3$  will be exposed if the bug is triggered. However, this condition need not be part of the bug's iRoot  $(I_2 \Rightarrow I_5)$ , because it is always implied by the bug's iRoot interleaving conditions.

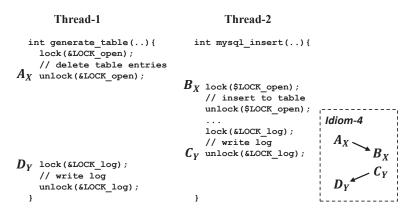

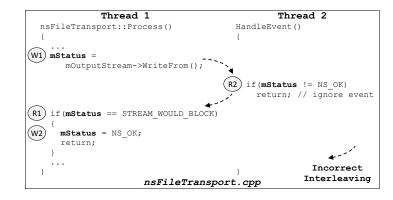

Figure 3.3 shows a real concurrency bug in MySQL and its idiom. In this example, two critical sections in Thread-1 are expected to execute atomically, but the programmer did not enforce that constraint explicitly. The bug will be exposed when the critical sections in Thread-1 are intercepted with the critical section in Thread-2.

Figure 3.3: A real idiom4 concurrency bug from MySQL.

The iRoot for this bug is of type idiom4 consisting of the two inter-thread dependencies between the lock and unlock operations. This example conveys an important observation that even if a concurrency bug is fairly complex involving many different variables and inter-thread dependencies, the iRoot of that bug (minimum set of interleaving conditions that need to be satisfied to trigger that bug) could be quite simple. Thus, by testing iRoots for a small set of idioms, we can hope to expose a significant fraction of concurrency bugs.

# 3.5 Empirical Analysis

To verify our hypothesis that exposing untested iRoots for our simple set of interleaving idioms could expose a significant fraction of concurrency bugs, we conducted an empirical study using 34 documented concurrency bugs from various programs including Apache, MySQL, and Memcached [1]. Here, when we say a concurrency bug, we mean a *static* concurrency bug.

Table 3.5 lists all the bugs we have analyzed. Each bug in the table has a unique name (Column-1) which is referred to throughout this dissertation. Column-2 provides a reference for each bug, which either specifies the issue number in the corresponding bug database if exists, or the paper in which the bug is studied. Among

| Bug Name     | Ref.   | Category  | Idiom   | Description                                                                                                                                                                                                                                                       |

|--------------|--------|-----------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Apache-1     | 25520  | Real      | Idiom-1 | A data race in ap_buffered_log_writer. The function can be invoked by multiple threads and<br>no synchronization is used to protect the shared memory accesses. This will cause garbage<br>data in the access log.                                                |

| Apache-2     | 21285  | Real      | Idiom-3 | An atomicity violation in mod_mem_cache.c. A temporary object is added to a cache and will<br>later be removed from the cache. The object is expected, but not guaranteed, to be in the<br>cache when the removal happens, which can lead to a possible crash.    |

| Apache-3     | 21287  | Real      | Idiom-1 | An atomicity violation in mod_mem_cache.c. apr_atomic_dec is not atomic when it is complied<br>on some platforms, which might cause an object to be cleared twice.                                                                                                |