# Thermoelectric Properties of Nanostructured Silicon Films

by

#### Xiao Guo

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Materials Science and Engineering) in the University of Michigan 2014

#### **Doctoral Committee:**

Assistant Professor Akram I. Boukai, Chair Assistant Professor Pramod S. Reddy Professor Dennis Sylvester Assistant Professor Anish Tuteja

Xiao Guo

All Rights Reserved

#### Acknowledgements

I would like to express my deeply felt gratitude to my thesis advisor, Prof. Akram Boukai, for his unreserved support, encouragement, motivation and enthusiasm. His generous guidance during my PhD helps pave the way of this research and the writing of this dissertation. I am also greatly indebted to Prof. Pramod Reddy, Prof. Anish Tuteja and Dr. Arun Kota for many insightful discussions and suggestions. They have in some way contributed to my research progress by giving valuable ideas and sharing their experience. I also like to thank Prof. Dennis Sylvester for serving on my PhD committee and for his helpful suggestions on this dissertation.

I am grateful to my co-author Bingyuan Huang for his help and contribution. I thank my colleagues Dr. Duck Hyun Lee, Jae Young Kwon, Xianhe Wei and Craig Shaner for providing their opinions and advice on experimental issues. I am glad to acknowledge my thanks to Prof. Ctirad Uher in physics department for his generosity, kindness and friendship. I also appreciate the help from the staff of Lurie Nanofabrication Facility for working with me closely from day one. The success of my research would not be possible without their helpful advice and technical support.

Finally, I thank the Department of Energy and Air Force for their generous support.

# **Table of Contents**

| Acknowledgements                                          | ii  |

|-----------------------------------------------------------|-----|

| List of Figures                                           | ix  |

| List of Tables                                            | xix |

| Abstract                                                  | xxi |

| Chapter                                                   |     |

| 1 Introduction                                            | 1   |

| 1.1 Thermoelectric energy conversion                      | 1   |

| 1.2 Thermal transport in silicon                          | 3   |

| 1.2.1 Phonons: classical lattice vibration                | 4   |

| 1.2.2 Debye approximation                                 | 7   |

| 1.2.3 Thermal conductivity                                | 9   |

| 1.2.3.1 Phonon-phonon scattering                          | 10  |

| 1.2.3.2 Phonon-imperfection scattering                    | 12  |

| 1.2.3.3 Phonon-boundary scattering                        | 13  |

| 1.2.3.4 Thermal conductivity from lattice dynamics        | 15  |

| 1.3 Thermal conductivity reduction through alloying       | 16  |

| 1.4 Thermal conductivity reduction through nanostructures | 17  |

| 1.5 Power factor enhancement through strained silicon with nanomesh    | 21 |

|------------------------------------------------------------------------|----|

| 1.5.1 Tensile strained silicon fabrication                             | 22 |

| 1.5.2 Effects of tensile strain on silicon bandstructure               | 25 |

| 1.6 Thermoelectric cooling study with silicon nanomesh thin film       | 28 |

| 1.6.1 Introduction to thermoelectric cooling (TEC)                     | 29 |

| 1.6.2 Thermoelectric cooling devices                                   | 33 |

| 1.6.3 Thermoelectric cooling measurements in a silicon nanomesh device | 35 |

| 1.7 Summary and organization of this thesis                            | 36 |

| 1.8 Reference                                                          | 38 |

| 2 Fabrication of $S^2\sigma$ and ZT device sets                        | 42 |

| 2.1 Block copolymer lithography (BCP)                                  | 42 |

| 2.1.1 Block copolymer self-assembly                                    | 43 |

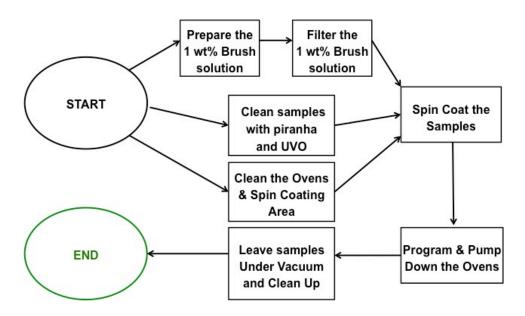

| 2.1.2 Pre-BCP brush treatment                                          | 45 |

| 2.1.2.1 Preparation of the 1 wt% brush solution                        | 46 |

| 2.1.2.2 Filtering of the 1 wt% brush solution                          | 46 |

| 2.1.2.3 Sample cleaning                                                | 47 |

| 2.1.2.4 Spin coating of the brush layer                                | 48 |

| 2.1.2.5 Brush layer annealing in a vacuum oven                         | 48 |

| 2.1.2.6 Sample cleaning after annealing                                | 49 |

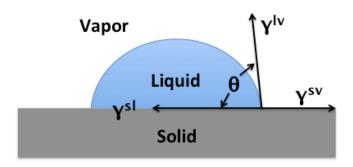

| 2.1.2.7 Contact angle measurement on the brush layer                   | 49 |

| 2.1.3 Block copolymer self-assembly (BCSA)                             | 52 |

| 2.1.3.1 Preparation of the block copolymer solutions                   | 53 |

| 2.1.3.2 Filtering of the block copolymer solutions                     | 54 |

| 2.1.3.3 Spin coating block copolymer solutions                                                                             | 54             |

|----------------------------------------------------------------------------------------------------------------------------|----------------|

| 2.1.3.4 Block copolymer thermal annealing in a vacuum oven                                                                 | 54             |

| 2.1.3.5 Block copolymer developing after thermal annealing                                                                 | 54             |

| 2.1.3.6 SEM image of nanomesh structure                                                                                    | 55             |

| 2.1.4 Nanomesh transfer from block copolymer to silicon                                                                    | 56             |

| 2.1.4.1 First nanomesh template transfer by RIE                                                                            | 56             |

| 2.1.4.2 Second nanomesh template transfer by DRIE                                                                          | 57             |

| 2.2 S <sup>2</sup> σ device set fabrication                                                                                | 60             |

| 2.2.1 Solid-state diffusion with phosphorus dopants                                                                        | 61             |

| 2.2.1.1 Pre-doping clean                                                                                                   | 61             |

| 2.2.1.2 Solid-state diffusion doping                                                                                       | 61             |

| 2.2.2 Metallic contacts                                                                                                    | 64             |

| 2.3 ZT device set fabrication                                                                                              | 65             |

| 2.3.1 Silicon nanomesh doped by ion implantation                                                                           | 67             |

| 2.3.1.1 Pre-implant cleaning                                                                                               | 68             |

| 2.3.1.2 Ion implantation                                                                                                   | 68             |

| 2.3.1.3 After-implant thermal annealing.                                                                                   | 69             |

| 2.3.1.4 Electrical resistivity result from four-point probe station                                                        | 69             |

| 2.5.1.4 Electrical resistivity result from four-point probe station                                                        |                |

| 2.3.2 Device fabrication after doping                                                                                      | 70             |

|                                                                                                                            |                |

| 2.3.2 Device fabrication after doping                                                                                      | 70             |

| 2.3.2 Device fabrication after doping                                                                                      | 70<br>71       |

| 2.3.2 Device fabrication after doping  2.3.2.1 First step-silicon nanomesh patterning  2.3.2.2 Second step - metallization | 70<br>71<br>73 |

| 2.4 Summary                                                                  | 75  |

|------------------------------------------------------------------------------|-----|

| 2.4.1 Summary of fabrication of $S^2\sigma$ device set                       | 75  |

| 2.4.2 Summary of fabrication of <i>ZT</i> device set                         | 76  |

| 2.5 Reference                                                                | 76  |

| 3 Characterization Techniques and Metrology for S2σ and ZT Device Sets       | 78  |

| $3.1 \text{ S}^2\sigma$ device set characterization techniques and metrology | 79  |

| $3.1.1 \text{ S}^2 \sigma$ device set characterization techniques            | 79  |

| 3.1.1.1 Scanning electron microscopy                                         | 79  |

| 3.1.1.2 Confocal Raman spectroscopy                                          | 80  |

| $3.1.2 \text{ S}^2 \sigma$ device set metrology                              | 82  |

| 3.1.2.1 Cryostat system                                                      | 82  |

| 3.1.2.2 Electrical conductivity measurement                                  | 84  |

| 3.1.2.3 Thermopower measurement                                              | 90  |

| 3.2 ZT device set characterization techniques and metrology                  | 94  |

| 3.2.1 ZT device set characterization techniques                              | 94  |

| 3.2.1.1 Scanning electron microscopy                                         | 94  |

| 3.2.1.2 Ellipsometry result                                                  | 95  |

| 3.2.1.3 Secondary ion mass spectroscopy result                               | 96  |

| 3.2.2 ZT device set metrology                                                | 96  |

| 3.2.2.1 The thermopower measurement                                          | 97  |

| 3.2.2.2 Electrical resistivity measurement                                   | 104 |

| 3.2.2.3 Thermal conductivity measurement                                     | 107 |

| 3.3 Summary                                                                  | 122 |

| 3.3.1 Summary of characterizations and metrology of the $S^2\sigma$ device set | 122 |

|--------------------------------------------------------------------------------|-----|

| 3.3.2 Summary of characterizations and metrology of <i>ZT</i> device set       | 123 |

| 3.4 Reference                                                                  | 124 |

| 4 Strained Silicon Power Factor Results and Discussion                         | 125 |

| 4.1 Electrical conductivity measurement results                                | 126 |

| 4.2 Thermopower measurement results                                            | 129 |

| 4.3 Power factor results                                                       | 133 |

| 4.4 Summary                                                                    | 136 |

| 4.5 References                                                                 | 137 |

| 5 ZT Measurement Results and Discussion                                        | 138 |

| 5.1 Thermopower measurement result                                             | 138 |

| 5.2 Electrical resistivity measurement result and discussion                   | 140 |

| 5.2.1 Metal-semiconductor junction.                                            | 141 |

| 5.2.2 High resistivity due to Schottky contact                                 | 142 |

| 5.2.3 High resistivity due to surface states                                   | 143 |

| 5.2.4 Thermal treatments to repair damaged silicon nanomesh                    | 144 |

| 5.2.4.1 RTA approach to improve resistivity                                    | 144 |

| 5.2.4.2 RTO approach to improve resistivity                                    | 148 |

| 5.3 Thermal conductivity measurement result                                    | 149 |

| 5.3.1 Measurement results of the stack layers                                  | 150 |

| 5.3.2 Measurement results of the double layers                                 | 153 |

| 5.3.3 Thermal conductivity of silicon nanomesh                                 | 154 |

| 5.4.7T of silicon nanomesh                                                     | 156 |

| 5.5 The thermoelectric cooling device and the cooling effect prediction | 156 |

|-------------------------------------------------------------------------|-----|

| 5.5.1 The thermoelectric cooling device                                 | 156 |

| 5.5.2 The thermoelectric cooling predictions                            | 159 |

| 5.6 Summary                                                             | 159 |

| 5.7 References                                                          | 160 |

| 6 Conclusion and outlook                                                | 161 |

| 6.1 Contributions                                                       | 161 |

| 6.2 Future work                                                         | 164 |

# **List of Figures**

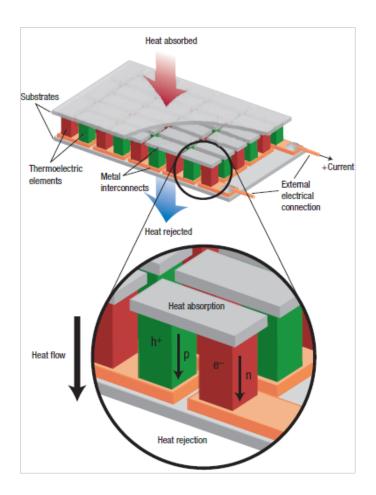

| Figure 1.1 Thermoelectric module functions as power generator or cooler. [5] P and n legs           |

|-----------------------------------------------------------------------------------------------------|

| are connected electrically in series and thermally in parallel                                      |

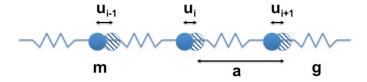

| Figure 1.2 Linear lattice of atoms: cross-hatched spheres represent the silicon atoms at            |

| their mean positions. 4                                                                             |

| Figure 1.3 Linear dispersion relation of phonons in silicon. The region $-\pi/a < k < \pi/a$ is the |

| first Brillouin zone. [8]                                                                           |

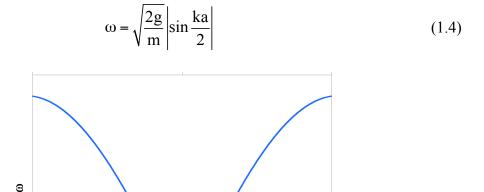

| Figure 1.4 The volumetric heat capacity of crystalline silicon. At low temperatures (T<50           |

| K) heat capacity varies as T <sup>3</sup> ; and at high temperatures (T~500 K), it approaches the   |

| Dulong-Petit limit. [11] 9                                                                          |

| Figure 1.5 Phonon-phonon interactions in a 2-D lattice plane. (a) Normal process; (b)               |

| Umklapp process                                                                                     |

| Figure 1.6 Differential and cumulative contributions of phonons to the thermal                      |

| conductivity at 277 K. The left plot shows the dependence on wavelength; the right plot             |

| shows the dependence on MFP. The differential and cumulative thermal conductivities                 |

| are shown in blue and red, respectively. [21]                                                       |

| Figure 1.7 Temperature dependence of figure of merit ZT for several bulk thermoelectric                            |

|--------------------------------------------------------------------------------------------------------------------|

| material systems. [25]                                                                                             |

| Figure 1.8 Temperature dependence of figure of merit ZT for superlattice systems. [28]. 19                         |

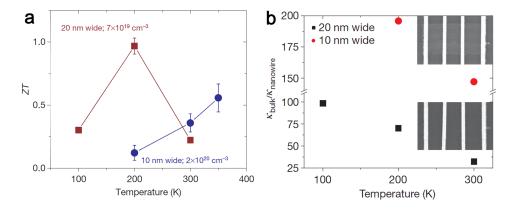

| Figure 1.9 10 nm and 20 nm wide silicon nanowire fabricated by SNAP method. (a) ZT                                 |

| of heavily doped nanowires as a function of temperature; (b) The ratio of thermal                                  |

| conductivity in bulk silicon to thermal conductivity in silicon nanowires as a function of                         |

| temperature. [4]                                                                                                   |

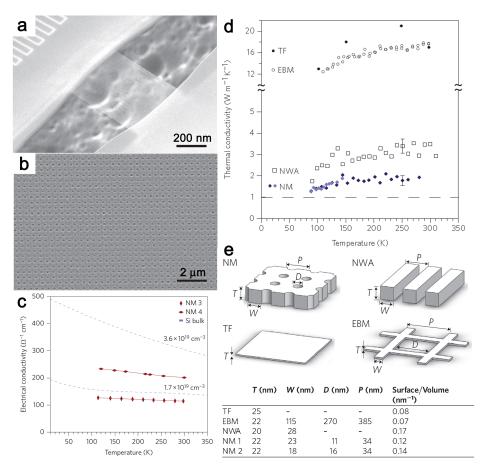

| Figure 1.10 Characterization and thermal conductivity results of different nanomesh                                |

| structures. (a) SEM image of fully suspended thermal microdevice; (b) SEM image of                                 |

| long-range ordered nanomesh film; (c) Electrical conductivity of two boron doped                                   |

| nanomesh films compared with boron doped bulk silicon film with similar doping level                               |

| (2x10 <sup>19</sup> atoms/cm <sup>3</sup> ); (d) Thermal conductivity of different nanostructures as a function of |

| temperature. TF (thin film) and EBM (large mesh fabricated by e-beam lithography)                                  |

| show similar high conductivity; NWA (nanowire arrays) show smaller thermal                                         |

| conductivity due to the size effect in two dimensions and a large surface to volume ratio;                         |

| NM1 and NM2 (nanomeshes) have the lowest thermal conductivity resulting from their                                 |

| three dimensional heat impedance. [23]                                                                             |

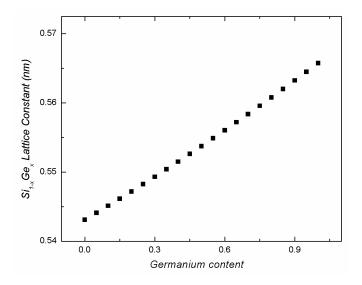

| Figure 1.11 Lattice constant of Si <sub>1-x</sub> Ge <sub>x</sub> as a function of germanium content               |

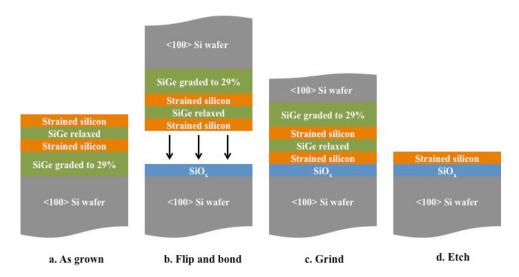

| Figure 1.12 Bond and etch back technology to obtain ultra-thin strained silicon thin film.                         |

| The plot is modified from reference [35].                                                                          |

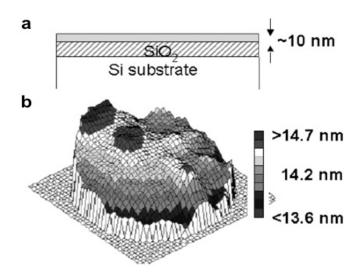

| Figure 1.13 Strained silicon on insulator. (a) The final structure after etch stop at the                          |

| strained silicon thin film; (b) Surface roughness of the top strained silicon thin film. [35] 25                   |

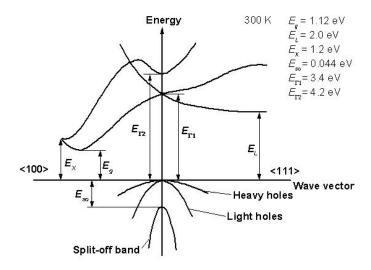

| Figure 1.14 Silicon bandstructure. [39]                                                                            |

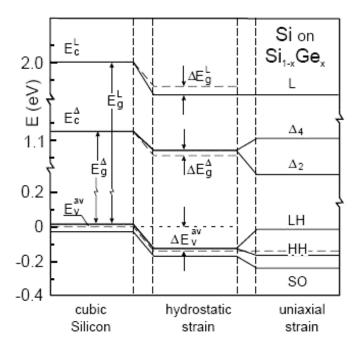

| Figure 1.15 Effect of hydrostatic and uniaxial strain on silicon conduction band and              |

|---------------------------------------------------------------------------------------------------|

| valence band by pseudomorphicly growing Si on Si <sub>0.7</sub> Ge <sub>0.3</sub> substrate. [40] |

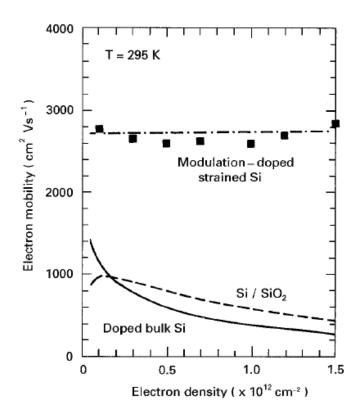

| Figure 1.16 The electron mobility dependence on electron density of modulation-doped              |

| strained silicon, doped bulk silicon and Si / SiO <sub>2</sub> inversion layer. [41]              |

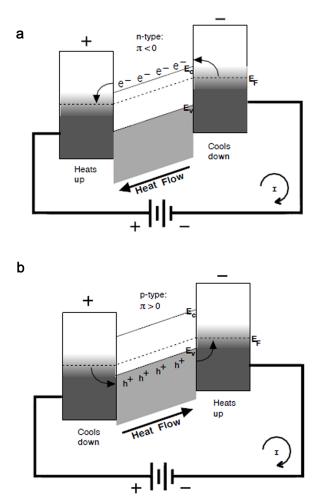

| Figure 1.17 Illustrations of Peltier effect on a metal-semiconductor-metal component. (a)         |

| Electrons with the highest energy overcome the energy barrier at the right end, and               |

| deplete the region while removing the heat from the left end to the right end; (b) Holes          |

| with the highest energy flow in the opposite direction, carrying heat from the left end to        |

| the right end. [42] 30                                                                            |

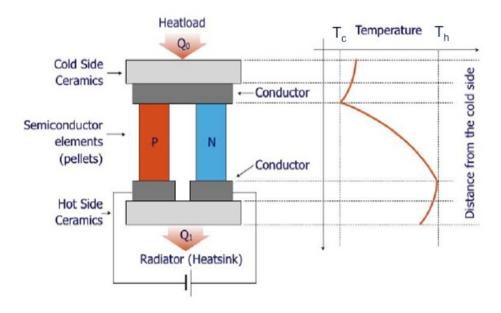

| Figure 1.18 Thermoelectric cooling module and temperature profile. [43]                           |

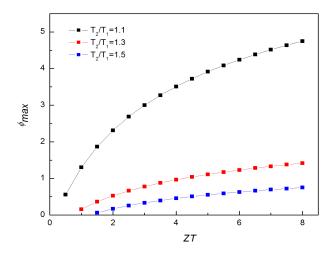

| Figure 1.19 The dependence of the thermoelectric cooling efficiency $\phi_{max}$ on the figure of |

| merit ZT for different values of the hot $(T_2)$ /cold $(T_1)$ temperature ratio in the device 33 |

| Figure 1.20 A commercial thermoelectric cooler. (a) Perspective view of an assembled              |

| single-stage thermoelectric cooler; (b) Partially cut-away view showing the arrangement           |

| of the n- and p- type semiconductor legs sandwiched between two thermally conductive              |

| plates; (c) Close-up view of the legs that are electrically connected by copper thin films.       |

| [43]                                                                                              |

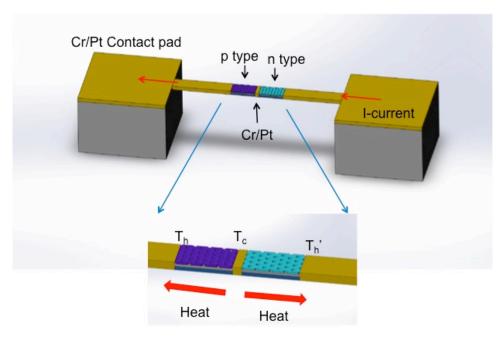

| Figure 1.21 Sketch of thermoelectric cooling of a suspended device with silicon                   |

| nanomesh thin films. 34                                                                           |

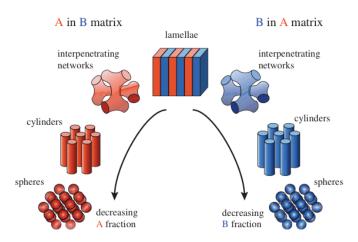

| Figure 2.1 Morphologies after linear diblock copolymer self-assembly. The motifs                  |

| gradually change based on block A and B's volume fraction. [1]                                    |

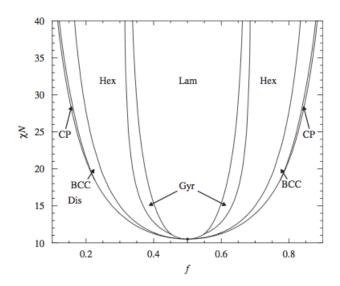

| Figure 2.2 Phase diagram of linear diblock copolymer. Ordered phases are labeled as        |

|--------------------------------------------------------------------------------------------|

| close-packed (CP) and body-centered cubic (BCC) spherical micelles; hexagonal              |

| cylindrical micelles (Hex); lamellae (Lam); gyroid (Gyr). [1,3-4]                          |

| Figure 2.3 Brush treatment process flow. 46                                                |

| Figure 2.4 UV-ozone machine used for the organic cleaning of the pre-brush samples 48      |

| Figure 2.6 Contact angle goniometer. 51                                                    |

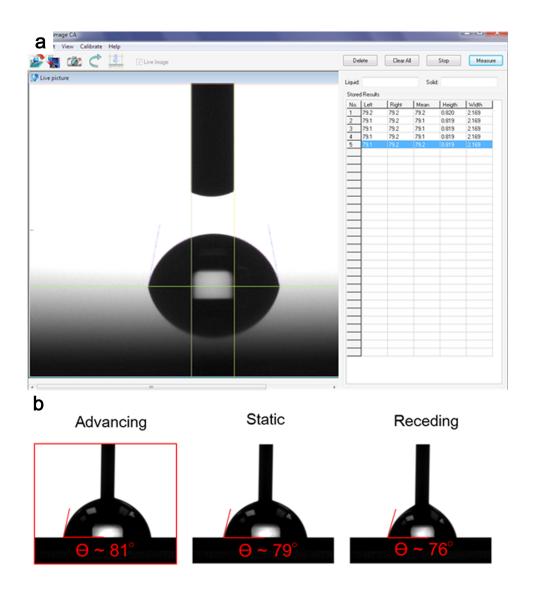

| Figure 2.7 Contact angle measurements. (a) Static measurement of brush layer with a        |

| contact angle goniometer; (b) Comparison of advancing, static, and receding contact        |

| angles on brush layer. 52                                                                  |

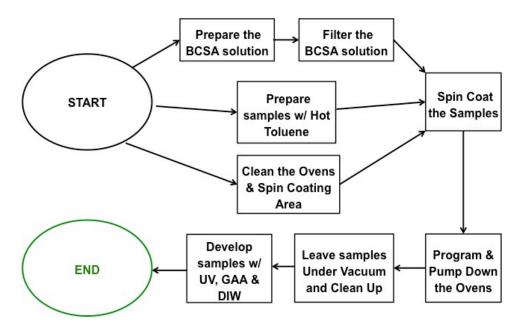

| Figure 2.8 Block copolymer self-assembly process flow. 53                                  |

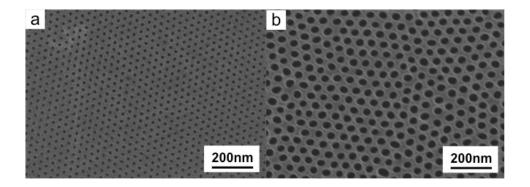

| Figure 2.9 SEM images of nanomesh structures after developing thermally annealed           |

| block copolymer. (a) The first nanomesh template for the $S^2\sigma$ device set where the  |

| nanomesh had 18 nm diameter and an 36 nm pitch; (b) The second nanomesh template           |

| for the ZT device set where the nanomesh had 40 nm diameter and an 80 nm pitch 56          |

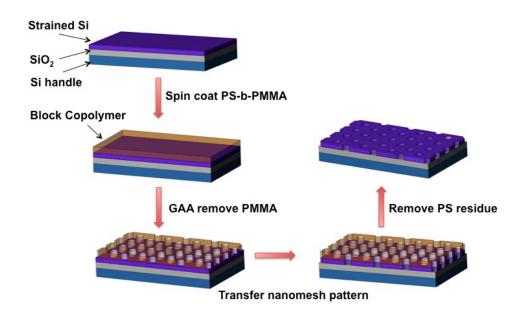

| Figure 2.10 Fabrication procedure for strained silicon nanomesh. (a) Starting sample is an |

| ~5 nm thick SSOI substrate; (b) Apply PS-b-PMMA coating and thermallly treat PS-b-         |

| PMMA block copolymer; (c) Remove PMMA by UV exposure and acetic acid; (d) RIE              |

| etch strained silicon thin film with PS as etch mask; (e) Remove PS residue by oxygen      |

| plasma descum. 57                                                                          |

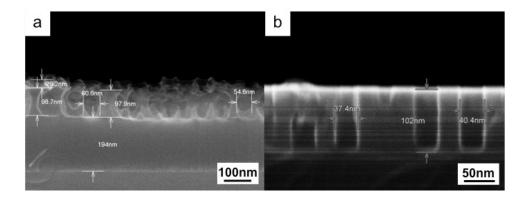

| Figure 2.11 Cross-sectional SEM images for SOI with ~100 nm thick silicon and 200 nm       |

| thick silicon oxide after DRIE. (a) Poor DRIE with excess lateral etching; (b) Good DRIE   |

| with vertical etching.                                                                     |

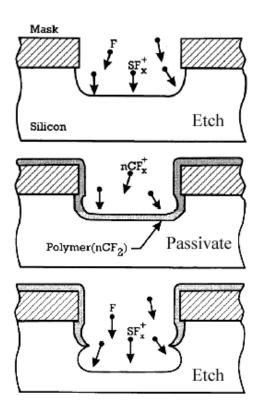

| Figure 2.12 Bosch etching with SF <sub>6</sub> and C <sub>4</sub> F <sub>8</sub> plasma alternatively switched to etch |

|------------------------------------------------------------------------------------------------------------------------|

| vertically into the trench. 59                                                                                         |

| Figure 2.13 Phosphorus dopants embedded solid diffusion wafer on a 4 in wafer carrier.62                               |

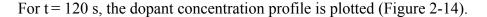

| Figure 2.14 Diffusion dopant concentration profile for phosphorus with arbitrary surface                               |

| dopant concentration, $N_0 = 10^{21} \text{cm}^{-3}$                                                                   |

| Figure 2.15 Mask design (using L-edit) of metallic contact pads for electrical                                         |

| conductivity measurement on SSOI and SOI samples                                                                       |

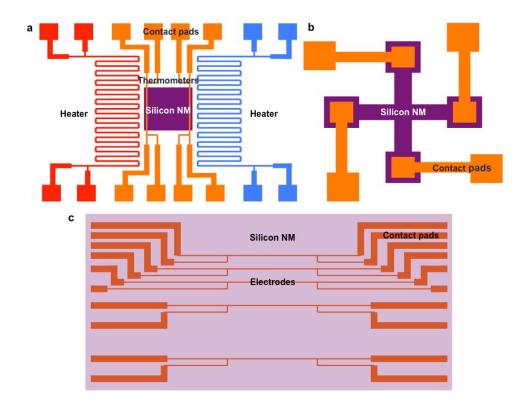

| Figure 2.16 Illustrations of three devices fabricated on the same chip. (a) The first device                           |

| is used to measure thermopower (S) with a 2-thermometer method; (b) The second device                                  |

| is used to measure electrical resistivity $(\rho)$ with a Van der Pauw method; $(c)$ The third                         |

| (suspended) device is used to measure thermal conductivity ( $\kappa$ ) with the $2\omega$ method 67                   |

| Figure 2.17 Optical microscopy image of LOR5A and SPR3612 double line feature after                                    |

| UV exposure and photoresist developing. 72                                                                             |

| Figure 2.18 The SOI sample was etched from the backside until the membrane looked                                      |

| semi-transparent. 74                                                                                                   |

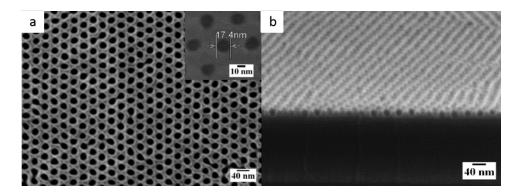

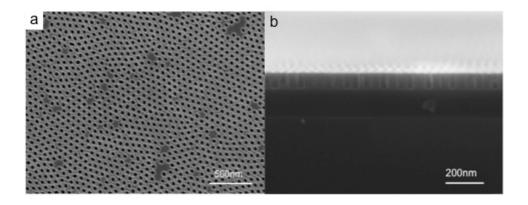

| Figure 3.1 SEM image of a nanomesh patterned strained silicon layer. (a) Top view                                      |

| (inset, hexagonally arranged nanomesh pattern with diameter of 17.4 nm); (b) Cross-                                    |

| sectional view                                                                                                         |

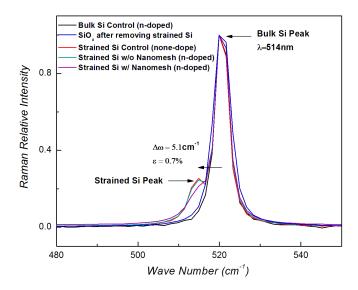

| Figure 3.2 Confocal Raman microscopy spectra with relaxed and strained silicon peaks at                                |

| 521 cm <sup>-1</sup> and 515.91 cm <sup>-1</sup> , respectively, with 514 nm laser excitation. A set of samples        |

| were measured to verify the source of the redshift: black curve - a relaxed silicon control                            |

| sample, slightly n-type doped; purple curve - SiO <sub>x</sub> layer from SSOI after removing the                      |

| strained silicon film with XeF <sub>2</sub> etching; blue curve - undoped strained silicon film on                     |

| SSOI; orange curve - heavily n-doped strained silicon film on SSOI without nanomesh;                           |

|----------------------------------------------------------------------------------------------------------------|

| green curve- heavily doped strained silicon film on SSOI with 18 nm-diameter                                   |

| nanomesh. 82                                                                                                   |

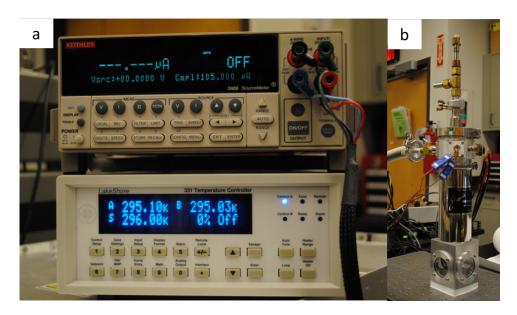

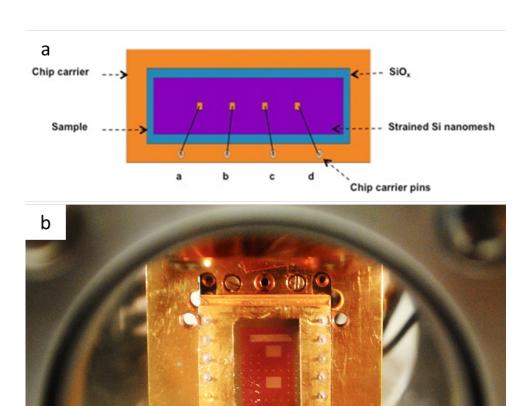

| Figure 3.3 Cryostat measurement setup. (a) Measurement instruments: sourcemeter and                            |

| temperature controller; (b) Cryostat                                                                           |

| Figure 3.4 Electrical conductivity and thermopower measurements conducted in cryostat                          |

| with temperature and vacuum controls. (a) SSOI mounted on a chip carrier sitting in a                          |

| cryostat sample stage. Pins on the chip carrier were connected to an electrical                                |

| feedthrough; (b) Electrical and thermocouple feedthroughs on the cryostat shell 84                             |

| Figure 3.5 Electrical conductivity devices. (a) SSOI sample with four contact pads                             |

| wirebonded to the chip carrier; (b) Chip carrier mounted to cryostat's sample stage with                       |

| four contact pads wirebonded to chip carrier pins.                                                             |

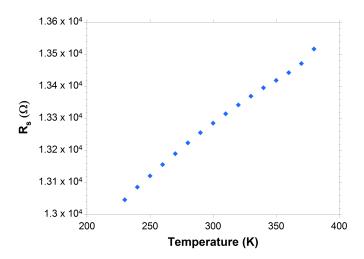

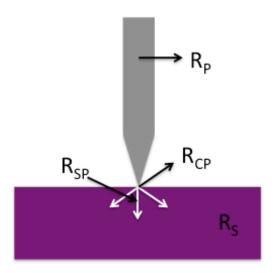

| Figure 3.7 Four-point probe measurement of silicon thin film sheet resistance (R <sub>P</sub> : probe          |

| resistance; $R_{CP}$ : probe contact resistance; $R_{SP}$ : probe spreading resistance; $R_{S}$ : silicon thin |

| film sheet resistance)                                                                                         |

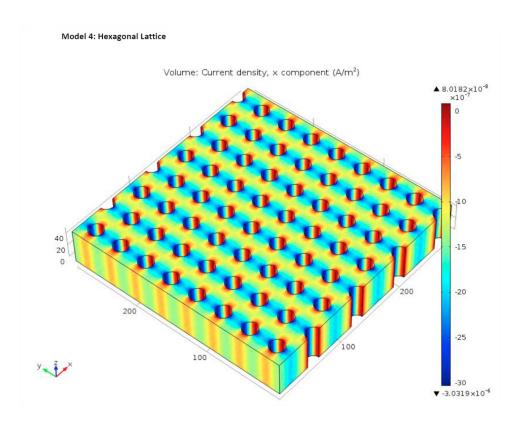

| Figure 3.8 COMSOL simulation of thin film current density in model 4, nanomesh with                            |

| hexagonal lattice and 18nm diameter. 90                                                                        |

| Figure 3.9 Thermopower measurement setup in cryostat simultaneously collecting                                 |

| voltage and temperature data. 91                                                                               |

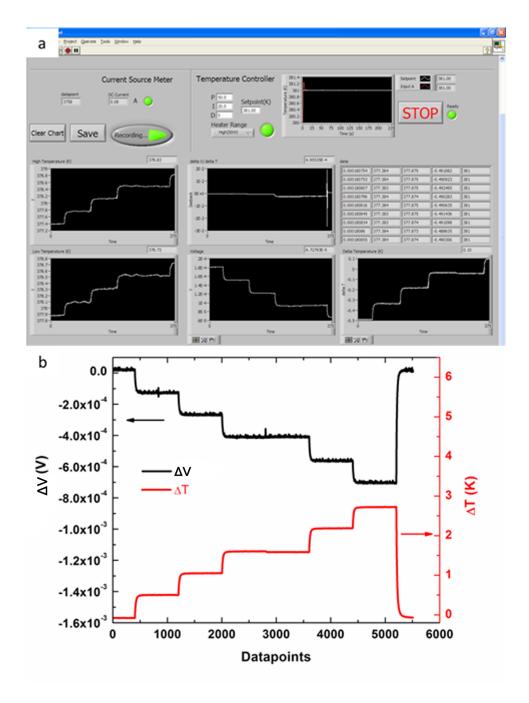

| Figure 3.10 Labview program used to activate and record voltage and temperature drops                          |

| from a SSOI sample. (a) The program interface showing the Kapton heater current,                               |

| voltage and temperature drops from SSOI sample, and sample stage temperature; (b) The                          |

| recorded data for $\Delta V$ and $\Delta T$ , with five plateaus triggered by the increase in Kapton    |

|---------------------------------------------------------------------------------------------------------|

| heater current. 93                                                                                      |

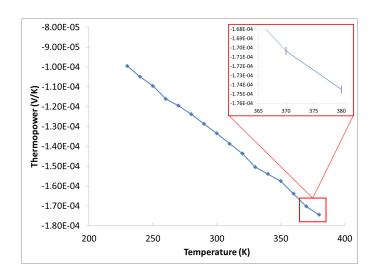

| Figure 3.11 Temperature dependence of the thermopower of strained silicon without                       |

| nanomesh. 94                                                                                            |

| Figure 3.12 SEM images of nanomesh patterned silicon thin film. (a) Top view of                         |

| nanomesh pattern; (b) Cross-sectional view of thoroughly etched silicon thin film 95                    |

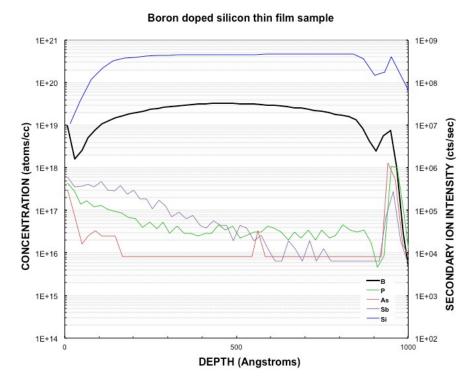

| Figure 3.13 Secondary ion mass spectroscopy (SIMS) result on monitor SOI after boron                    |

| implantation and activation                                                                             |

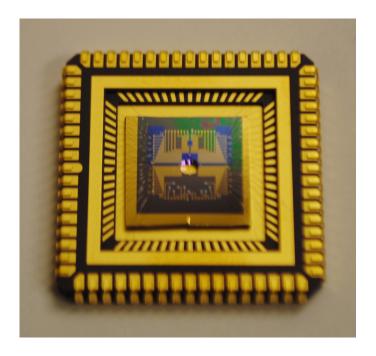

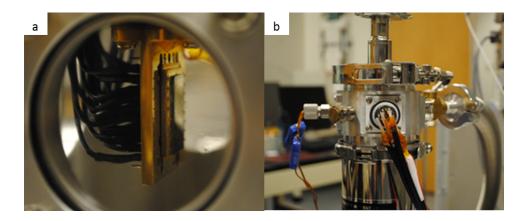

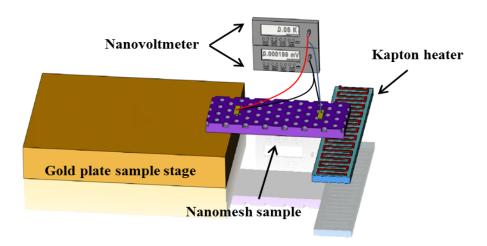

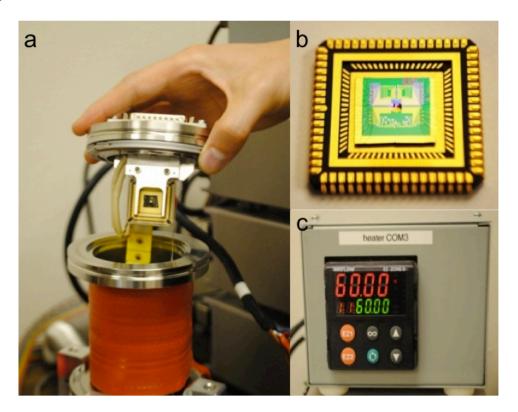

| Figure 3.14 ZT device set measurement setup pictures. (a) A custom-designed apparatus                   |

| sealed by vacuum; (b) ZT measurement sample wirebonded to a chip carrier. The chip                      |

| carrier was fixed on the cryostat stage in (a); (c) A PID global temperature controller 97              |

| Figure 3.15 Illustration of thermopower measurement by using one heater and two                         |

| thermometers. Both voltage and temperature difference between two thermometers under                    |

| a temperature gradient generated by the left heater were measured, and the linear fit of                |

| $\Delta V$ and $\Delta T$ gives the thermopower.                                                        |

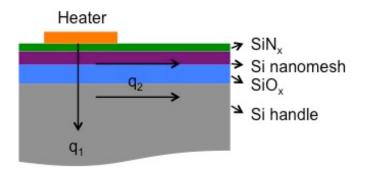

| Figure 3.16 The stack structure of silicon nitride (SiN <sub>x</sub> ), silicon nanomesh, silicon oxide |

| $(SiO_x)$ and bulk silicon handle with two directions of heat conduction: heat conduction               |

| downwards through the stack of layers (q1), and heat conduction in the sample from the                  |

| left to right (q <sub>2</sub> )                                                                         |

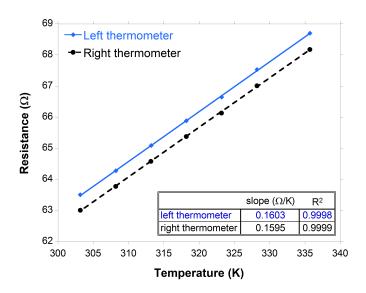

| Figure 3.17 The plot of the resistance of both thermometers as a function of sample                     |

| temperature. 101                                                                                        |

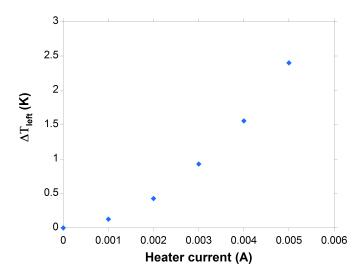

| Figure 3.18 The parabolic relationship between the temperature change of the left                       |

| thermometer and the left heater current as a result of thermal conduction                               |

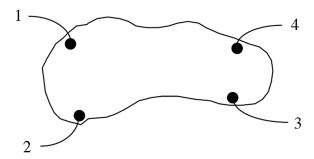

| Figure 3.19 Arbitrary shaped sample measured by the Van der Pauw method with four                             |

|---------------------------------------------------------------------------------------------------------------|

| contacts. [3]                                                                                                 |

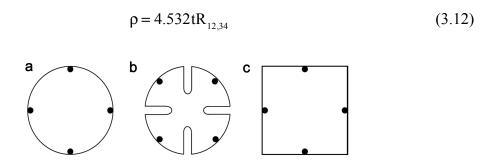

| Figure 3.20 Symmetrical sample shapes for Van der Pauw method. (a) Circular; (b)                              |

| Cloverleaf; and (c) Square sample configurations. [3]                                                         |

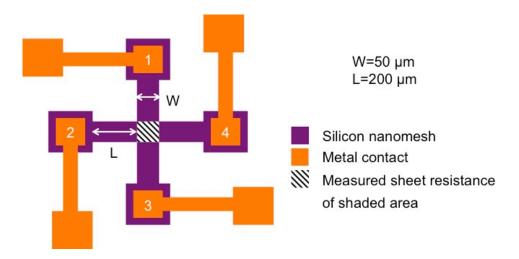

| Figure 3.21 Greek cross structure used in Van der Pauw method for silicon nanomesh                            |

| resistivity measurement. 107                                                                                  |

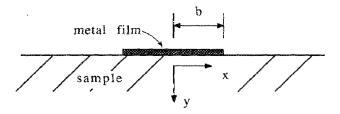

| Figure 3.22 Side view of the heater and sample geometry for the $3\omega$ method. [4] 108                     |

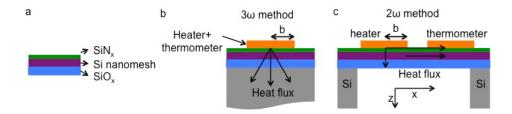

| Figure 3.23 The illustrations of sample structures in the $3\omega$ and the $2\omega$ methods. (a) The        |

| stack of layers for thermal conductivity measurement; (b) The sample structure in the $3\omega$               |

| method where the heater also acts as the thermometer, and the thermal conductivity is an                      |

| averaged result from $\kappa_X$ and $\kappa_Z;$ (c) The sample structure in the $2\omega$ method where the    |

| heater and the thermometer are separate, and the thermal conductivity is $\kappa_{\boldsymbol{X}}$ due to the |

| suspension of the film. 109                                                                                   |

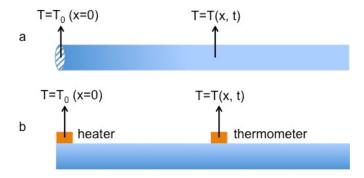

| Figure 3.24 Illustrations of one-dimensional heat flow. (a) The heat flow and boundary                        |

| conditions in a semi-infinite thin rod; (b) The heat flow and boundary conditions in                          |

| silicon nanomesh thin film using a metal heater as a heat source                                              |

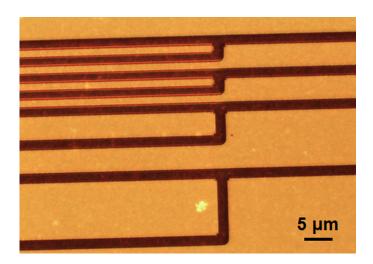

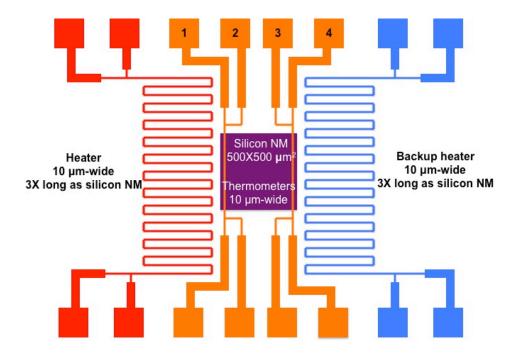

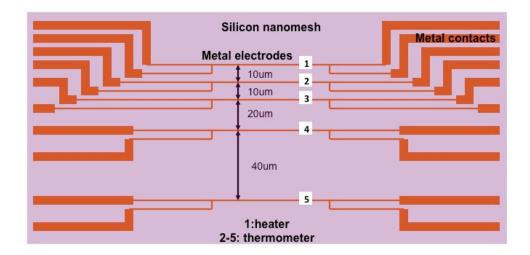

| Figure 3.25 The thermal conductivity device layout for the $2\omega$ measurement. The                         |

| electrode 1 is the heater, and electrodes 2-5 are thermometers                                                |

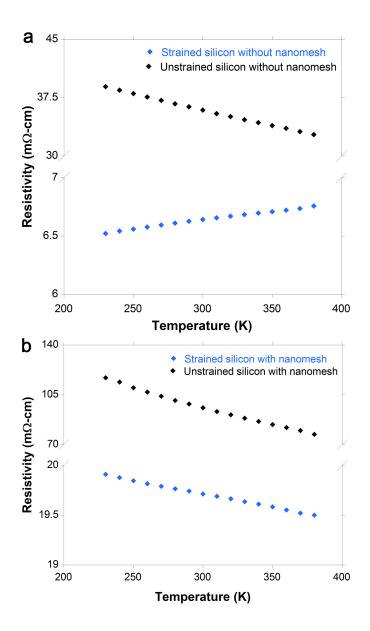

| Figure 4.1 Electrical resistivity from strained silicon and unstrained silicon thin films. (a)                |

| Before nanomesh, strained silicon showed metallic behavior while unstrained silicon                           |

| showed semiconductor behavior; (b) After nanomesh, both strained and unstrained                               |

| silicon showed semiconductor behavior.                                                                        |

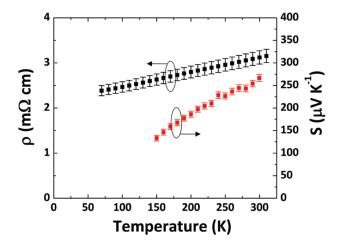

| Figure 4.2 Temperature-dependent electrical resistivity ( $\rho$ ) and thermopower (S) of boron                                      |

|--------------------------------------------------------------------------------------------------------------------------------------|

| doped 55 nm pitch holey silicon ribbon. 128                                                                                          |

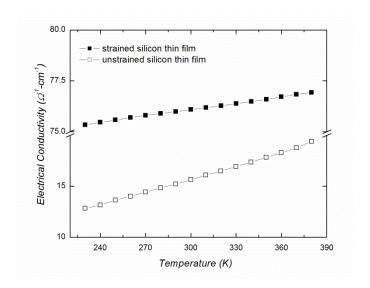

| Figure 4.3 Corrected electrical conductivity of strained and unstrained silicon thin films                                           |

| with nanomesh. 129                                                                                                                   |

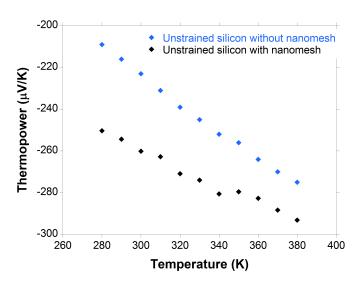

| Figure 4.4 Dependence of thermopower on temperature for unstrained silicon with and                                                  |

| without nanomesh. 131                                                                                                                |

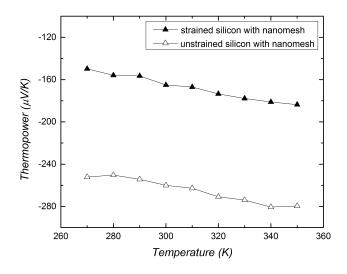

| Figure 4.5 Dependence of thermopower on temperature of strained and unstrained silicon                                               |

| thin films with nanomesh. 133                                                                                                        |

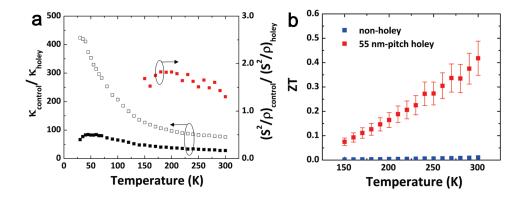

| Figure 4.6 Thermoelectric properties and ZT comparisons for 55 nm-pitch nanomesh                                                     |

| (holey) and non-nanomesh (non-holey) 100 nm thick silicon ribbons. (a) Thermal                                                       |

| conductivity comparison of nanomesh ribbon (red squares, 5X10 <sup>19</sup> atoms/cm <sup>3</sup> , boron                            |

| doped) with non-nanomesh ribbon (black squares, 5X1019 atom/cm3, boron doped) and                                                    |

| bulk silicon (open squares, 1.7X10 <sup>19</sup> atoms/cm <sup>3</sup> As-doped); power factor comparison of                         |

| nanomesh ribbon and non-nanomesh ribbon; (b) ZT comparison of nanomesh ribbon (red                                                   |

| squares) and non-nanomesh ribbon (blue squares). ZT is increased by $\sim$ 40 times with                                             |

| nanomesh at room temperature. [6] 134                                                                                                |

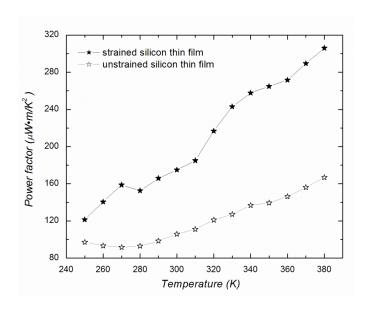

| Figure 4.7 Power factor of strained and unstrained silicon thin film with nanomesh 135                                               |

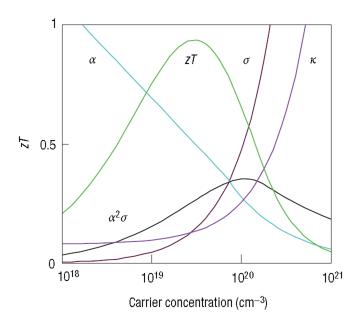

| Figure 4.8 Maximizing the efficiency (ZT) of a thermoelectric involves a compromise of                                               |

| thermal conductivity (κ; plotted on the y axis from 0 to 10 W/m•K) and Seebeck                                                       |

| coefficient ( $\alpha$ ; 0 to 500 $\mu V/K$ ) with electrical conductivity ( $\sigma$ ; 0 to 5000 $\Omega^{-1} cm^{-1}$ ). [7] . 136 |

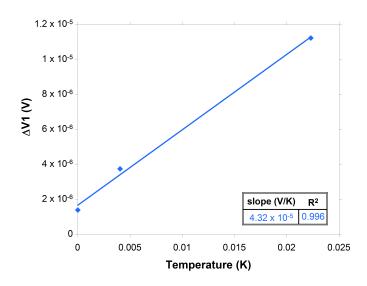

| Figure 5.1 The linear fit on $\Delta V1$ - $\Delta T$ plot with the goodness of fit of 0.996 for the first                           |

| thermopower result                                                                                                                   |

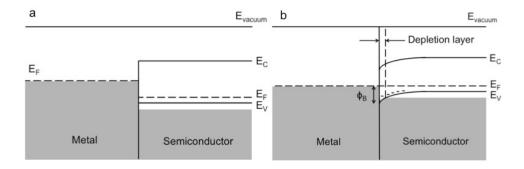

| Figure 5.2 Illustrations of the band diagrams of a metal and a p type semiconductor in                  |

|---------------------------------------------------------------------------------------------------------|

| contact. (a) Before Fermi levels have been equallized on both sides; (b) After Fermi                    |

| levels have been equalized on both sides. 142                                                           |

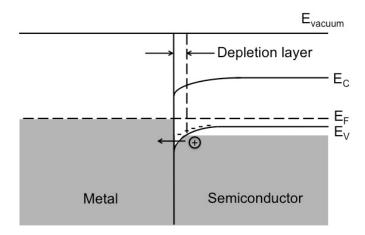

| Figure 5.3 Holes from the semiconductor transport through the Schottky barrier by                       |

| tunneling if the metal-semiconductor junction is an ohmic contact                                       |

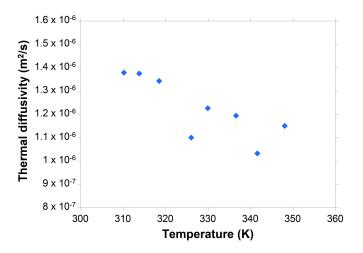

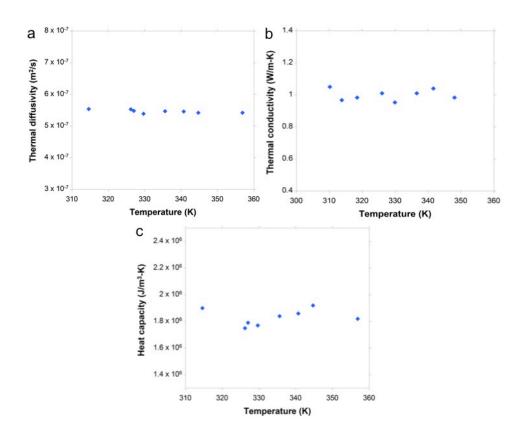

| Figure 5.4 The thermal diffusivity of the stack layers measured by the $2\omega$ method over            |

| the temperature range of 310-350 K. 151                                                                 |

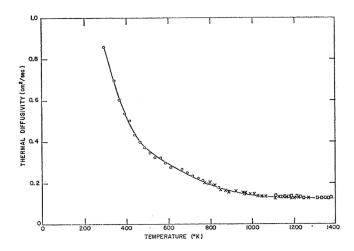

| Figure 5.5 Thermal diffusivity of silicon from 300 to 1400 K. [6]                                       |

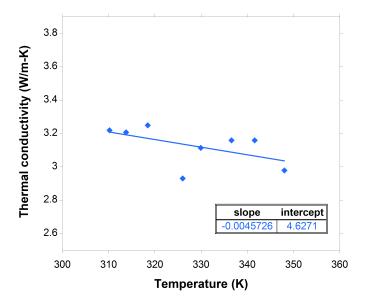

| Figure 5.6 The thermal conductivity of the stack layers measured by the $2\omega$ method over           |

| the temperature range of 310-350 K. 152                                                                 |

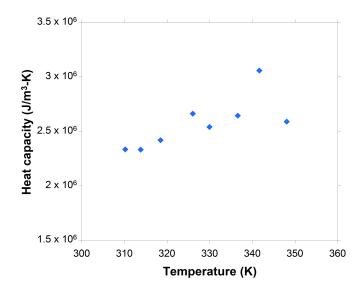

| Figure 5.7 The volume-specific heat capacity of the stack layers measured by the $2\boldsymbol{\omega}$ |

| method over the temperature range of 310-350 K. 153                                                     |

| Figure 5.8 The thermal properties measured from the $SiN_x$ and $SiO_x$ double layers by the            |

| $2\omega$ method over the temperature range of 310-350 K. (a) Thermal diffusivity; (b)                  |

| Thermal conductivity; (c) Volume specific heat capacity                                                 |

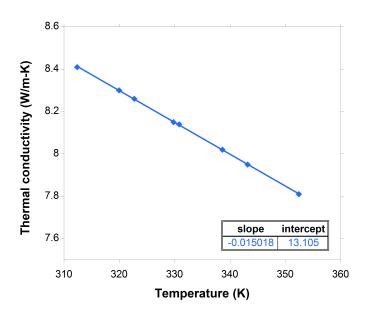

| Figure 5.9 The thermal conductivity of the silicon nanomesh thin film measured by the                   |

| $2\omega$ method over the temperature range of 310-350 K                                                |

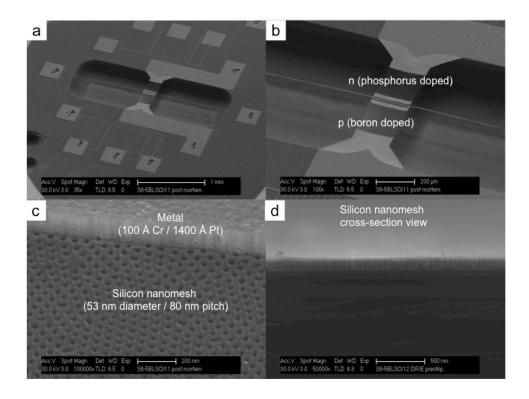

| Figure 5.10 SEM images of the suspended thermoelectric cooling device. (a) A                            |

| perspective view of the device; (b) A close-up view of the p type and n type nanomesh                   |

| islands and the resistive thermometer at the p-n junction; (c) The inferface of a metallic              |

| contact and the silicon nanomesh; (d) A tilted cross-sectional view of ~100 nm thick                    |

| silicon nanomesh                                                                                        |

## **List of Tables**

| Table 2.1 Sheet resistance of SSOI and SOI samples without and with nanomesh after                    |

|-------------------------------------------------------------------------------------------------------|

| diffusion doping at 900°C, measured with four-point probe station at room temperature in              |

| air                                                                                                   |

| Table 3.1 COMSOL simulation results of thin film resistance. 89                                       |

| Table 3.2 The thermoelectric voltage and temperature difference measured from                         |

| thermometer electrodes as the heater current was increased in 1 mA increments 104                     |

| Table 3.3 Table of comparison between the $3\omega$ and the $2\omega$ methods                         |

| Table 4.1 Electrical resistivity comparison of strained silicon thin film from SSOI and               |

| unstrained silicon thin film from SOI before and after fabrication of a nanomesh 129                  |

| Table 5.1 The thermopower fitting results from four plots of $\Delta V$ - $\Delta T$ with the average |

| thermopower and its error at 303 K. 139                                                               |

| Table 5.2 A comparison between the holey silicon study and this study regarding                       |

| nanohole (nanomesh) pitch, silicon film thickness (t), and electrical resistivity before and          |

| after making nanoholes; measurements were taken around room temperature 141                           |

| Table 5.3 Test A for resistivity comparison from ~100 nm thick pre-boron doped silicon                |

| nanomesh samples with various porosities and a RTA treatment                                          |

| Table 5.4 Test B for resistivity comparison from ~145 nm thick pre-boron dop | ed silicor  |

|------------------------------------------------------------------------------|-------------|

| nanomesh samples with different oxide passivation procedures and a RTA treat | ment. 147   |

| Table 5.5 Test C for resistivity comparison from ~100 nm thick pre-boron dop | ped silicon |

| nanomesh samples before and after RTO process.                               | 148         |

**Abstract**

Thermoelectric Properties of Nanostructured Silicon Films

by

Xiao Guo

Chair: Professor Akram I. Boukai

Based on the Seebeck effect, thermoelectric materials can convert temperature

heat into electrical energy. Alternatively, based on the Peltier effect, thermoelectric

cooling can be achieved by supplying current through thermoelectric materials. Since the

best thermoelectric materials are heavily doped semiconductors, and silicon is the most

abundant semiconductor on earth, investigation of the thermoelectric properties of

strained silicon and ~100 nm thick silicon thin films, and the thermoelectric cooling

application of the  $\sim$ 100 nm thick silicon thin film become the focus of this dissertation.

In the Seebeck effect, charge carriers thermally diffuse from a high temperature to

low temperature, creating an open circuit voltage potential across the thermoelectric

material. However, the application of such technology is mainly limited due to its poor

efficiency when competing with the traditional engines; the efficiency depends on the

temperature difference and a dimensionless figure of merit, ZT. It has been determined

xxi

that  $ZT=S^2\sigma T/\kappa$ , in which  $S^2\sigma$  is the power factor, S is the Seebeck coefficient,  $\sigma$  is the electrical conductivity,  $\kappa$  is the thermal conductivity, and T is the average temperature. The interdependence of S,  $\sigma$  and  $\kappa$  makes it difficult to improve ZT because optimizing one parameter adversely affects another. ZT is the key parameter to determine the thermoelectric performance not only in thermoelectric power generation application based on Seebeck effect, but also in thermoelectric cooling application based on Peltier effect. A higher ZT results in better thermoelectric performance. It has been proved that silicon nanomesh materials result in a reduced thermal conductivity due to the increased phonon-boundary scattering. This work focuses on using novel nanostructured silicon thin films fabricated by block copolymer lithography to study thermoelectric properties of silicon, and to use these results to estimate the thermoelectric performance of two types of silicon thin films with nanomesh structures.

In the past, improvements of ZT in silicon and other semiconductors were made by alloying or nanostructure engineering to reduce the thermal conductivity, while maintaining the power factor ( $S^2\sigma$ ). To improve ZT further, we propose to use n-type tensile strained silicon to *enhance the power factor* and to maintain a low thermal conductivity by using a nanomesh structure. It is known that tensile strained silicon exhibits splitting of the six-fold degenerate conduction bands, which leads to decreased inter-valley scattering and increased electron mobility. Thus, its electrical conductivity could be potentially increased. The first part of this dissertation investigates the electrical conductivity and thermopower of 5 nm thick strained silicon and 10 nm thick unstrained silicon thin films with a nanomesh structure over the temperature range of 230-380 K from the  $S^2\sigma$  device set. At 300 K, the electrical conductivity of strained silicon with nanomesh and its power factor were increased by ~400% and ~100%, respectively, compared with those measured in unstrained silicon with nanomesh. The measurements were conducted on a  $S^2\sigma$  (power factor) device set consisting of two bulk devices to measure  $\sigma$  and S, respectively.

The second part of the dissertation investigates the ZT of ~100 nm thick borondoped silicon nanomesh thin film from a ZT device set to study the thermoelectric cooling application of this material. Higher ZT results in higher cooling efficiency based on the Peltier effect. Three micro-sized devices were fabricated on the same sample chip to measure the thermopower (S), electrical resistivity ( $\rho = 1/\sigma$ ), and thermal conductivity (κ), respectively. The thermopower was measured from a 2-thermometer device over a 500 X 500 µm<sup>2</sup> size nanomesh thin film; the electrical resistivity was measured using the Van der Pauw method with a Greek cross structure; and the thermal conductivity was measured by a 2ω method from a suspended micro-device. The measurement results of the three parameters at 303 K were 435.99  $\mu$ V/K, 23.2 m $\Omega$ •cm, and 8.51 W/m•K, respectively. Thus, ZT was determined to be approximately 0.03 at 303 K. Due to the high resistivity of this silicon nanomesh sample, thermal treatments were investigated to reduce the damage-induced degradation of the electrical conductivity, possibly caused by the Schottky barrier at the metal-silicon nanomesh interface or the surface states of the silicon nanomesh. Furthermore, a thermoelectric cooling device composed of equally doped phosphorus and boron nanomesh legs was fabricated using the same material conditions as the one used in the ZT device set. It is predicted that the maximum temperature difference this device can generate under vacuum is 3.4 K when the hot side

temperature is kept at 303 K, and that the electrical current required to obtain such cooling effect is  $51.3 \,\mu\text{A}$ , flowing from the n-type leg towards the p-type leg.

The efforts in the studies of  $S^2\sigma$  device set and ZT device set both use block copolymer lithography to fabricate nanomesh structures in 5 nm thick strained silicon and ~100 nm thick silicon thin films. The thermoelectric properties of S,  $\sigma$  or  $\rho$  ( $\rho = 1/\sigma$ ) are measured in both studies from bulk samples and micro-devices, respectively. Both studies also benefit from the reduction of thermal conductivity due to nanomesh structure in each material, so that the ZT is increased. Therefore, better thermoelectric performance in thermoelectric power generation or thermoelectric cooling applications are expected from strained silicon and ~100 nm thick silicon thin films with nanomesh compared with bulk silicon.

### **Chapter 1**

#### Introduction

#### 1.1 Thermoelectric energy conversion

Thermoelectric effects can convert heat to electricity and vice versa. The sources of heat can be solar radiation or waste heat from a running automobile engine. In automobile engines, such thermal loss is up to 60-70% of the output energy in the vehicle and it is almost always wasted. Among all the thermoelectric effects, the Seebeck effect associates the power generation from a temperzature gradient on a conductor to an electrical field. [1-2] Classically, in a conductor, charge carriers (electrons or holes) diffuse from the high temperature side to low temperature side, creating an internal electrical field to counteract further charge carrier diffusion until a steady state is reached. A new temperature gradient is required to break the balance and resume the diffusion. This conversion process is environmental friendly without any secondary waste but its applications are mainly limited by low efficiency, which is determined by a dimensionless figure of merit *ZT* (Equation 1.1).

$$ZT = \frac{S^2 \sigma}{\kappa} T \tag{1.1}$$

ZT is a function of Seebeck coefficient or thermopower (S), electrical conductivity ( $\sigma$ ), thermal conductivity ( $\kappa$ ), and temperature (T). [3] For a given temperature T, the major challenge to maximize ZT is that the three parameters S,  $\sigma$ , and  $\kappa$  are interdependent and adversely affect each other. [4] For example, increasing electrical conductivity reduces thermopower due to the negative impact on charge carrier concentration and effective mass; but it increases the electronic part of the thermal conductivity due to the Wiedemann-Franz law. [5-6]

Taking the above three parameters into consideration, the most efficient thermoelectric materials have been heavily doped semiconductors. <sup>[4]</sup> A thermoelectric module for power generation typically consists of both n-type and p-type semiconductors. They are connected electrically in series and thermally in parallel (Figure 1.1). When a temperature gradient is applied across the module from top down, electrons and holes diffuse in the same direction and generate a current. The ratio of output electrical energy to input thermal energy gives the power generation efficiency. It has been shown that when *ZT*>3 the thermoelectric efficiency is competitive with the ones from traditional heat engines. <sup>[7]</sup> Numerous studies to improve the efficiency have been performed in the past 50 years. Most endeavors were devoted to reducing thermal conductivity in various semiconductor materials via two major approaches: alloying (section 1.3) and nanostructures (section 1.4). In order to understand how thermal conductivity can be reduced by both methods, detailed background on thermal transport in semiconductors is provided, with an emphasis on silicon (section 1.2).

Later on, with this understanding, two studies were conducted using a nanomesh structure to investigate thermoelectric properties of two types of thin films. The first study was the power factor enhancement in  $\sim$ 5 nm thick strained silicon thin film with nanomesh (section 1.5), and the second study was the ZT result of  $\sim$ 100 nm thick boron doped silicon nanomesh thin film, followed by an extended discussion of its potential in thermoelectric cooling application (section 1.6).

Figure 1.1 Thermoelectric module functions as power generator or cooler. <sup>[5]</sup> P and n legs are connected electrically in series and thermally in parallel.

#### 1.2 Thermal transport in silicon

Reduction in thermal conductivity has been the most convenient approach to increase thermoelectric efficiency. Comprehensive understanding of thermal conductivity has been developed through extensive studies of heat transfer in various materials. Two carriers are considered responsible for the thermal transport in electrical conductors: charge carriers and phonons (crystalline lattice vibration modes), while only phonons dominate the thermal transport in semiconductors such as silicon.

#### 1.2.1 Phonons: classical lattice vibration

Silicon atoms, which are bonded by covalent bonding, vibrate about their mean positions due to thermal fluctuations. Simple vibrations along a one-dimensional atomic lattice have been studied to understand the dispersion relation between phonon wavevectors and frequency (Figure 1.2). [8]

Figure 1.2 Linear lattice of atoms: cross-hatched spheres represent the silicon atoms at their mean positions.

The force equation for the  $i_{th}$  atom during vibration can be expressed based on the motions of the adjacent  $(i+1)_{th}$  and  $(i-1)_{th}$  atoms (Equation 1.2).

$$m\frac{d^2u_i}{dt^2} = g(u_{i+1} + u_{i-1} - 2u_i)$$

(1.2)

(m is the mass of the atom; g is the spring constant between atoms; and a is the lattice constant)

A solution to Equation 1.2 can take a general form (Equation 1.3) where k is the wavevector,  $k=2\pi/\lambda$ , n is an integer,  $\omega$  is the angular frequency of lattice wave, and t is the time.

$$u_{i} = ue^{i(nka - \omega t)}$$

(1.3)

π/a

Using this ansatz in Equation 1.2, the dispersion relation between wavevector and angular frequency can be derived with a sine function (Equation 1.4, Figure 1.3)

Figure 1.3 Linear dispersion relation of phonons in silicon. The region  $-\pi/a < k < \pi/a$  is the first Brillouin zone. [8]

k

-π/a

In this dispersion relation, the region  $-\pi/a < k < \pi/a$  is the first Brillouin zone of silicon in reciprocal space;  $-\pi/a$  and  $\pi/a$  are the boundaries of the first Brillouin zone. Due to the classical limit of  $\lambda_{min}=2a$ , the maximum wavevector is  $k_{max}=\pi/a$ . Any wavevector outside of the first Brillouin zone, however, can be transformed to a wavevector within the first Brillouin zone by subtracting a reciprocal lattice vector G, resulting in the same solution to the elastic wave equation.

This analysis can be extended to a 3-D crystal structure. Each silicon atom can be considered as a harmonic oscillator participating in different lattice vibrational modes or phonons in three dimensions. The discrete energies of phonons are given from quantum mechanics (Equation 1.5). [9]

$$E_{n} = (n + \frac{1}{2})\hbar\omega \tag{1.5}$$

(n is an integer and ħ is Planck's constant)

At each quantized energy level there are a certain number of phonon modes available. The total vibrational energy is thus a sum of phonons of all wavevectors and branches in a crystal system. Phonons have acoustic and optical branches based on frequency; for simplicity, Figure 1.3 shows only the acoustic branch. The total energy can be expressed using the number of phonon modes (Equation 1.6) per unit frequency range, i.e. the phonon density of states  $(D(\omega), Equation 1.7)$ .

$$N = \frac{\frac{4}{3}\pi k^3}{\left(\frac{2\pi}{L}\right)^3} = \frac{k^3 V}{6\pi^2}$$

(1.6)

(L is the 3-D cubic crystal side length; V=L<sup>3</sup> is the volume of the crystal)

$$D(\omega) = \frac{dN}{d\omega} = \frac{dN}{dk} \frac{dk}{d\omega} = \frac{Vk^2}{2\pi^2} \frac{dk}{d\omega}$$

(1.7)

The number of modes (N) is defined as the volume of reciprocal space  $\frac{4}{3}\pi k^3$

divided by the volume occupied by each phonon mode  $\left(\frac{2\pi}{L}\right)^3$ .  $D(\omega)$  is directly related to

the phonon dispersion relation,  $\frac{dk}{d\omega}$ . A linear Debye approximation (explained in next

section) sufficiently simplifies the dispersion relation for lower energy modes at lower temperature with the exception of some acoustic modes at the first Brillouin zone edge. For a large crystal, the discretization in the wave-vector space is very dense, so the sum of total vibrational energy,  $E = \sum_{k,p} (n + \frac{1}{2})\hbar \omega_{k,p}$ , can be converted to an integral over  $\omega$  using  $D(\omega)$  (eq 1.8).

$$E = \sum_{p} \int (n + \frac{1}{2}) \hbar \omega_{k,p} D(\omega) d\omega$$

(1.8)

The total energy is the key to understanding the heat capacity  $(C_v)$  and the thermal conductivity  $(\kappa)$ , and it can be simplified by using the Debye approximation for the dispersion relation,  $\frac{dk}{d\omega}$ .

#### 1.2.2 Debye approximation

Two classic models are widely accepted for estimating the heat capacity (or specific heat) in solids: the Einstein model and the Debye model. Unlike the Einstein model that assumes that all the atoms vibrate at the same frequency independently, the Debye model treats thermal vibrations as collective modes of all the atoms confined in a box. The Debye model matches well with experimental results at low temperatures (4-50 K), in which the dependence of heat capacity on temperature T is proportional to  $T^3$ . The Debye model starts with a linear dispersion relation assumption (Equation 1.9), in which the phonon modes propagate at the group velocity ( $v_g$ ) closely estimated by the speed of sound ( $v_s$ ) in silicon. [10] It also provides a cut-off frequency ( $\omega_D$ , Equation 1.10) based on

Equations 1.6 and 1.9. <sup>[8]</sup> The heat capacity  $(C_v)$  can be derived from the total thermal energy with a simplified density of states  $D(\omega)$  (Equations 1.11-1.12).

$$\omega = v_{o}k \tag{1.9}$$

$$\omega_{\rm D} = v_{\rm s}^3 \sqrt[3]{\frac{6\pi N}{V}} \tag{1.10}$$

$$D(\omega) = \frac{V\omega^2}{2\pi^2 v_s^3}$$

(1.11)

$$C_{v} = \frac{\partial E}{\partial T} = \frac{9Nk_{B}}{V} \left(\frac{T}{\theta_{D}}\right)^{3} \int_{0}^{\frac{\theta_{D}}{T}} \frac{x^{4}}{\left(e^{x} - 1\right)^{2}} dx$$

(1.12)

$(\theta_D = \frac{\hbar v_s}{k_B} \sqrt[3]{\frac{6\pi^2 N}{V}} \text{ is the Debye temperature derived from } \theta_D k_B = \hbar \omega_D, \ k_B \text{ is Boltzmann}$  constant and  $\hbar$  is Planck's constant)

The Debye temperature can be interpreted as the temperature at which all the phonon modes are activated. The Debye temperature of silicon is reported to be 645 K. <sup>[4]</sup> When  $T << \theta_D$ ,  $C_v \approx 233 \text{Nk}_B (T/\theta_D)^3$  for 3-D crystals; when  $T >> \theta_D$ ,  $C_v = 3 \text{Nk}_B / V$  is the Dulong-Petit limit (Figure 1.4). <sup>[11]</sup> The volumetric heat capacity ( $C_v$ ) is an essential parameter in calculating thermal conductivity based on the kinetic theory of gases.

Figure 1.4 The volumetric heat capacity of crystalline silicon. At low temperatures (T<50 K) heat capacity varies as T<sup>3</sup>; and at high temperatures (T~500 K), it approaches the Dulong-Petit limit. [11]

#### 1.2.3 Thermal conductivity

Phonons are essentially wave-like lattice vibrations but they can also be treated as particles in order to approximate how heat is transferred in solids. The same kinetic theory used to model a large number of small gas particles traveling in random fashion is applied to heat-carrying phonons moving in a solid under a temperature gradient. Phonons interact with boundaries, imperfections (defects, impurities, etc), and other phonons, to transfer energy. The theory assumes that all the interactions among phonons are in the form of collisions (i.e. phonon-phonon scattering) and that all collisions are elastic and conserve energy. The phonons can also interact with other defects or imperfections in the crystal, as well as the crystal's boundaries (i.e. phonon-imperfection scattering and phonon-boundary scattering). The average time that phonons travel between interactions is defined as the mean free time  $(\tau)$ , and the average distance that phonons travel between interactions is defined as the mean free path (MFP,  $\ell$ ). The

thermal conductivity can be estimated based on heat capacity, the speed of sound, and the phonon mean free path (Equation 1.13).

$$\kappa = \frac{1}{3} C_{v} v_{s} \ell \tag{1.13}$$

Essentially, the thermal conductivity is determined by energy-dependent parameters such as the dispersion relation  $\frac{dk}{d\omega}$ , which defines density of states  $D(\omega)$ ; the average group velocity of all phonons  $v_g \approx v_s$ , and the average phonon mean free time  $\tau = \ell/v_g$ . Here, the group velocity is considered to be the same for all phonons; in reality, short wavelength phonons (with higher energy) travel slower than long wavelength ones (with lower energy). The phonon mean free time depends on the scattering mechanisms as expressed by Matthiessen's rule (Equation 1.14). The strongest scattering determines the limit for thermal conductivity. The phonon scatterings are highly dependent on material, phonon frequency, and temperature. They will be discussed in detail below with a focus on silicon; however, the same mechanisms apply in general to all semiconductors.

$$\frac{1}{\tau} = \frac{1}{\tau_{\text{phonon-phonon}}} + \frac{1}{\tau_{\text{phonon-imperfection}}} + \frac{1}{\tau_{\text{phonon-boundary}}}$$

(1.14)

#### 1.2.3.1 Phonon-phonon scattering

To simplify the discussion only the scenario of two phonons interacting to form a third phonon is considered. This interaction leads to two results: a normal process and an Umklapp process (Figure 1.5). [8]

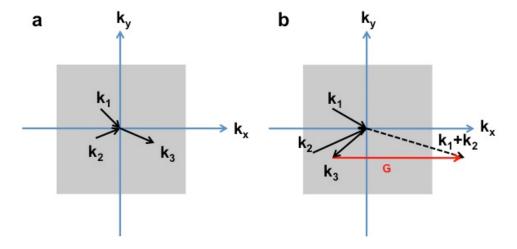

Figure 1.5 Phonon-phonon interactions in a 2-D lattice plane. (a) Normal process; (b) Umklapp process.

In a normal process, the wavevector of the third phonon is within the first Brillouin zone so that both energy and phonon momentum (hk) are conserved. The interactions following a normal process do not create thermal resistance in silicon; therefore, they do not contribute to heat transfer. In an Umklapp process, the interaction results in a third phonon with a wavevector ( $k_1+k_2$ ) that would extend beyond the first Brillouin zone. But that is physically impossible because the minimum wavelength of a phonon is 2a so the maximum wavevector is limited by  $\pi/a$ . The third phonon with  $|k_1+k_2|>\pi/a$  is brought back to the first Brillouin zone by subtracting a reciprocal vector G. The phonon interaction in an Umklapp process creates thermal resistance due to the lack of momentum conservation and is mainly responsible for the phonon-phonon scattering that affects lattice thermal conductivity at high temperatures where more phonons with larger wavevectors and higher frequencies are activated. The phonon-phonon scattering mean free time is found to relate to phonon angular frequency as

#### 1.2.3.2 Phonon-imperfection scattering

Imperfections in a crystal such as silicon can be the absence of atoms or the presence of foreign atoms; such imperfections create changes in mass and local strain field that alter the vibrational characteristics of the crystal. Phonons are treated as lattice vibrational waves here. A travelling lattice wave is scattered by imperfections resulting in thermal resistance to heat transfer.

Based on the kinetic theory from Vincenti, the phonon-imperfection scattering mean free time is related to the scattering cross section and velocity of phonons (Equation 1.15). [12]

$$\frac{1}{\tau_{\text{phonon-imperfection}}} = \alpha \phi \eta v_{g}$$

(1.15)

( $\alpha$  is a constant on the order of unity;  $\phi$  is the scattering cross section;  $\eta$  is the number of scattering sites per unit volume or the imperfection density; and  $v_g$  is the phonon group velocity,  $v_g \approx v_s$ )

The scattering cross section  $\phi$  is related to the incident phonon frequency and the imperfection size. If the phonon wavelength ( $\lambda$ ) is larger than imperfection size ( $\pi R^2$ , R is imperfection radius), the relation approaches the Rayleigh limit, [13]  $\phi \propto \lambda^{-4}$ ; if  $\lambda << \pi R^2$ , the scattering cross section is  $\phi = \pi R^2$ , independent of  $\lambda$ . [14] Majumdar proposed a relation between  $\phi$  and  $\lambda$  to link these two limits (Equation 1.16). [15]

$$\varphi = \pi R^2 \left( \frac{\chi^4}{\chi^4 + 1} \right) \tag{1.16}$$

( $\chi$  is the size parameter,  $\chi = \frac{2\pi R}{\lambda}$ )

At very low temperatures, most of the excited phonons have low frequency and long wavelength. The phonon-imperfection scattering cross section  $\phi$  appears very small to the incident phonons, according to the Rayleigh limit; consequently, the mean free time of this type of scattering ( $\tau_{phonon-imperfection}$ ) is long. Therefore, phonon-imperfection scatterings do not dominate at very low temperatures. However, with large amount of imperfections such as dopants or alloying atoms, the imperfection density  $\eta$  can increase and lead to a smaller scattering mean free time to reduce thermal conductivity over a wide temperature range according to Equations 1.13 and 1.15. Otherwise the phonon-impurity scattering starts to dominate thermal conductivity when the temperature increases and more short-wavelength phonons are activated with  $\lambda$  comparable to the imperfection size  $\pi R^2$ .

## 1.2.3.3 Phonon-boundary scattering

Casimir proved that during phonon-boundary scattering, a boundary wall is not a perfect mirror surface that simply reflects phonons without energy loss; in fact, a boundary wall is a rough surface where phonons are first absorbed then re-radiated based on the local temperature in a diffusive fashion. <sup>[16]</sup> Diffusive scattering introduces thermal resistance into the crystal and affects the phonon mean free path (MFP). The phonon mean free path (MFP) in this scattering mechanism has a fixed value in an infinite crystal such as bulk silicon. <sup>[17]</sup> For most of the finite structures such as thin films, the MFP ( $\ell$ ) is determined by the film thickness (L) according to Sondheimer's work (Equations 1.17-1.18). <sup>[18]</sup>

$$\frac{\ell}{L} = \frac{3}{4} \left( \frac{2 - d}{d} \right) \ln \left( \frac{\ell_b}{L} \right) \text{ for } \ell_b \gg L$$

(1.17)

$$\frac{\ell}{L} = \frac{1}{L/\ell_b + 3d/8} \text{ for } \ell_b \ll L$$

(1.18)

(d is the probability of diffuse phonon scattering at boundaries, in perfect diffusive scattering d=1;  $\ell_b$  is the MFP in a bulk medium. It is reported that in bulk silicon,  $\ell_b$  ~300 nm. <sup>[19]</sup>)

When the film thickness is much smaller than the mean free path of the bulk material,  $L \ll \ell_b$ , the MFP is on the order of film thickness,  $\ell \sim L$ . <sup>[15]</sup> Thermal conductivity is mainly limited by phonon-boundary scattering at low temperature (T<20 K in bulk silicon) since most short wavelength phonons are still not activated and phonon-imperfection scattering is not dominant.

The above described three major scattering mechanisms that explain how the thermal resistance in bulk silicon is produced and how the thermal conductivity is determined. At very low temperatures (T<20 K), phonon-boundary scattering dominates. Thermal conductivity has a T³ temperature dependence based on the Debye approximation. As temperature increases, phonons with wavelengths close to the imperfection size determine the mean free path (MFP). At high temperatures, more phonons with larger wavevectors and shorter wavelengths scatter to increase thermal resistance and thus reduce thermal conductivity.

Unlike the situation in bulk silicon, nanostructures can further tailor the thermal conductivity based on phonon-boundary scattering over a wide temperature range. This behavior can also be explained from the dependence of the cumulative thermal conductivity on the MFP distribution. Boundary roughness can also be important.

## 1.2.3.4 Thermal conductivity from lattice dynamics

Dames and Chen [20-21] treated phonons as lattice waves and derived the contribution from each phonon mean free path (MFP) to the total thermal conductivity in bulk silicon (Equations 1.19-1.20). The MFP is a function of wavelength,  $\lambda$ .

$$d\kappa(\ell_{k\lambda}) = \frac{1}{3} C_{V,k\lambda} \nu_{g,k\lambda} \ell_{k\lambda}$$

(1.19)

$$\kappa(\ell) = \frac{1}{N} \sum_{k\lambda}^{\ell_{k\lambda} < \ell} d\kappa(\ell_{k\lambda})$$

(1.20)

$(C_{v,k\lambda}, v_{g,k\lambda})$  and  $\iota_{k\lambda}$  are the heat capacity, group velocity, and MFP associated with the phonon mode  $k\lambda$ )

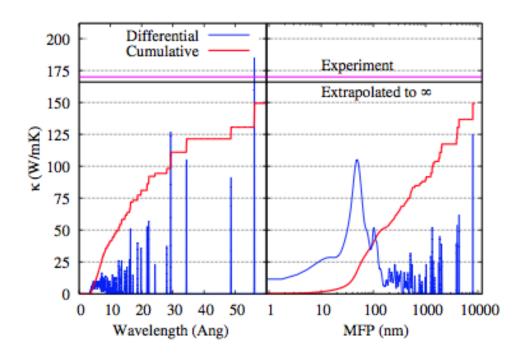

From the above differential and cumulative thermal conductivity analysis, phonons with thermal wavelength  $\lambda$  < 6 nm carry all the heat at 277 K in bulk silicon, and its thermal conductivity is ~150 W/m•K. The MFPs in silicon range from 1 nm to 10 µm, with more than 67% of MFPs above 100 nm. It has significant meaning for nanostructures in silicon; as the critical dimension ( $\ell_c$ , the smallest in-plane size in silicon) is lowered, more MFPs are reduced by phonon-boundary scattering since the MFPs approaches  $\ell_c$ ; in turn, phonon-boundary scattering limits the thermal conductivity over the temperature range 100-500 K, in agreement with experimental results. [21]

Figure 1.6 Differential and cumulative contributions of phonons to the thermal conductivity at 277 K. The left plot shows the dependence on wavelength; the right plot shows the dependence on MFP. The differential and cumulative thermal conductivities are shown in blue and red, respectively. [21]

Thermal conductivity in silicon has been reduced in the past decades based on engineering principles to increase phonon-imperfection scattering and phonon-boundary scattering. Different approaches employed to reduce thermal conductivity in order to increase the figure of merit ZT are discussed below.

## 1.3 Thermal conductivity reduction through alloying

Before the 1990s, the major focus in thermoelectric research was to search for bulk material systems that exhibited high *ZT* within a wide temperature regime. Such systems as Bi<sub>2</sub>Te<sub>3</sub>, PbTe, Si<sub>1-y</sub>Ge<sub>y</sub> and Zn<sub>4</sub>Sb<sub>3</sub> were widely investigated, especially in the high temperature range (>600 °C). Alloying was the first attempt to tailor the thermal conductivity in those materials to increase *ZT*. By adding atoms with heavier atomic

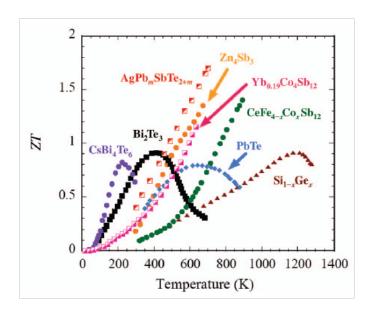

mass, the lattice thermal conductivity (phonon contribution) was lowered due to anharmonic phonon scattering. Specifically, the imperfection density  $\eta$  (alloying atom density) can increase and lead to a smaller phonon-imperfection scattering mean free time to reduce thermal conductivity (see section 1.2.3.2). Studies have shown Bi<sub>2</sub>Te<sub>3</sub> based alloys  $((Bi_{1-x}Sb_x)_2(Te_{1-x}Se_x)_3)$  with ZT near 1 at room temperature <sup>[22-23]</sup> (Figure 1.7). Historically,  $ZT\sim1$  was referred to as the 'alloy limit' <sup>[24]</sup> for the past 30 years, though there was no theoretical prediction that it should be the upper limit of thermoelectric performance. <sup>[25]</sup> Later on, nanostructure engineering has been found to be a promising approach to improve ZT.

Figure 1.7 Temperature dependence of figure of merit ZT for several bulk thermoelectric material systems. [25]

#### 1.4 Thermal conductivity reduction through nanostructures

Experiments starting in the 1990s using 'phonon-glass electron-crystal' engineering on traditional thermoelectric materials have improved thermoelectric performance. The idea is to suppress thermal conductivity by reducing the dimensions of

materials in structures such as superlattices, thin films, or quantum wires, while retaining bulk-like electrical conductivity. The minimum limit of thermal conductivity in bulk semiconductors was considered to be  $\sim 1~\text{W/m} \cdot \text{K}$  found in amorphous  $\text{SiO}_x$  since its heat transfer was considered as a random walk. [5] Nanostructures have made it possible to reach such a limit in single crystal materials without the need to make an amorphous material.

This nanostructure-engineering was proposed to describe the ideal thermoelectric material, one that scatters phonons but not charge carriers. One method to accomplish this is to exploit the difference between the electron and phonon mean free paths (MFPs). For example, the electron mean free path (MFP) in highly doped bulk silicon at room temperature is 5-10 nm, <sup>[3, 26]</sup> but 67% of its phonon MFPs are above 100 nm (see section 1.2.3.4). <sup>[21]</sup> Therefore, silicon with nanostructures approaching a critical dimension of ~10nm should reduce thermal conductivity by increasing phonon-boundary scattering without significantly affecting electrical conductivity, leading to an increase in *ZT*. This idea was first examined on the earliest and most investigated materials.

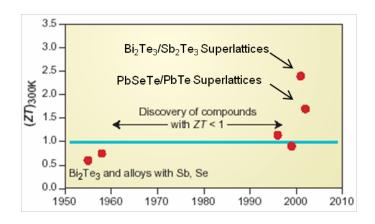

L.D. Hicks <sup>[6, 27]</sup> showed theoretically that *ZT* of Bi<sub>2</sub>Te<sub>3</sub> could be increased dramatically from bulk material by using quantum well or quantum wires. Experimentally, it was shown that *ZT* was increased from 0.5 in bulk Bi<sub>2</sub>Te<sub>3</sub> with Sb, Se alloys to approximately 2.4 in a Bi<sub>2</sub>Te<sub>3</sub>/Se<sub>2</sub>Te<sub>3</sub> superlattice at room temperature. <sup>[28]</sup> T.C. Harman <sup>[29]</sup> also discovered that by growing a PbTe/Te superlattice, *ZT* of PbTe was improved by approximately 40.5% (Figure 1.8). Past efforts in nanostructure-engineering have been focused on rare semiconductors. Few investigations on earth abundant elements such as silicon have been performed.

Figure 1.8 Temperature dependence of figure of merit ZT for superlattice systems. [28]

Recent research has shown that nanostructure-engineering in both silicon nanowires and nanomesh structures exhibited extremely low thermal conductivities, about two orders of magnitude lower than that of bulk silicon. Such drastic reduction in thermal conductivity made a positive impact on silicon's ZT value. Bulk silicon has  $ZT\sim0.01$  at 300 K due to a high thermal conductivity ( $\sim150$  W/m·K). A. I. Boukai showed  $ZT\sim1$  at 200 K in 20 nm wide silicon nanowires made by the superlattice nanowire pattern transfer (SNAP) method; [4] SNAP reduced the thermal conductivity by a factor of 75 (Figure 1.9).

Figure 1.9 10 nm and 20 nm wide silicon nanowire fabricated by SNAP method. (a) ZT of heavily doped nanowires as a function of temperature; (b) The ratio of thermal conductivity in bulk silicon to thermal conductivity in silicon nanowires as a function of temperature. [4]

J.Y. Tang et al <sup>[22]</sup> studied holey silicon nanostructures fabricated by nanosphere lithography (NSL) or block copolymer lithography (BCP) in 100nm thick silicon films. Reduction in hole pitch to 55 nm further reduced the thermal conductivity to ~2 W/m·K. The *ZT* measured in this holey structure was 0.4 at 300 K. J.K. Yu et al <sup>[23]</sup> demonstrated similar nanomesh structures (Figure 1.10, a, b, e) fabricated by e-beam lithography (EBM) and superlattice nanowire pattern transfer (SNAP). The nanomesh silicon and holey silicon are essentially two terminologies for the same structure. The lowest thermal conductivity obtained was 1.9 W/m·K (Figure 1.10, d) for nanomesh structures by SNAP, while the electrical conductivity was preserved close to that of bulk silicon at a similar doping level (Figure 1.10, c).

Figure 1.10 Characterization and thermal conductivity results of different nanomesh structures. (a) SEM image of fully suspended thermal microdevice; (b) SEM image of long-

range ordered nanomesh film; (c) Electrical conductivity of two boron doped nanomesh films compared with boron doped bulk silicon film with similar doping level (2x10<sup>19</sup> atoms/cm³); (d) Thermal conductivity of different nanostructures as a function of temperature. TF (thin film) and EBM (large mesh fabricated by e-beam lithography) show similar high conductivity; NWA (nanowire arrays) show smaller thermal conductivity due to the size effect in two dimensions and a large surface to volume ratio; NM1 and NM2 (nanomeshes) have the lowest thermal conductivity resulting from their three dimensional heat impedance. [23]

These results indicated that phonon propagation was significantly reduced in nanostructure-engineered materials, while the electrical conductivity ( $\sigma$ ) or even the power factor ( $S^2\sigma$ ) was comparable to that of the bulk silicon. The impedance in heat transfer was found to be the main reason for enhancement of ZT. The next step is to further enhance ZT by increasing the power factor, while retaining low thermal conductivity by using nanostructures such as nanomesh. The work in this thesis describes efforts to enhance the power factor of tensile strained silicon to uncover its potential in improving ZT and to perform a cooling measurement on silicon nanomesh devices for the first time.

## 1.5 Power factor enhancement through strained silicon with nanomesh

Tensile strained silicon has been used in n-channel MOSFETs (NMOS) to increase electron mobility through the channel. This idea was first used in Intel's 90 nm process to increase device performance by more than 10% in 2000. [30-32] This improvement in electron mobility also leads to increased electrical conductivity. Therefore strain-engineered silicon can be a solution to increase the power factor. One of the objectives in this dissertation is to employ tensile strained silicon with nanomesh to maximize ZT both by enhancing the power factor and reducing the thermal conductivity. This is also the first time that tensile strained silicon is studied for its thermoelectric

properties. In the following, the method of tensile strained silicon thin film fabrication is introduced then the strain effects on silicon's bandstructure are studied in detail.

#### 1.5.1 Tensile strained silicon fabrication