Article type: Full Paper

# Exploiting in situ Redox and Diffusion of Molybdenum to Enable Thin-Film Circuitry for Low-Cost Wireless Energy Harvesting

Youngbae Son and Rebecca L. Peterson\*

Department of Electrical Engineering and Computer Science, University of Michigan, Ann Arbor, Michigan, 48109-2122, USA

E-mail: blpeters@umich.edu

Keywords: amorphous oxide semiconductors, thin-film circuitry, additive fabrication, large-area electronics, solution process

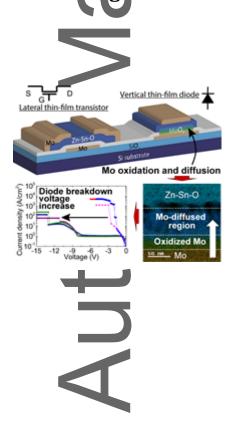

Direct additive fabrication of thin-film electronics using high-mobility, wide-bandgap amorphous oxide semiconductor (AOS) can pave the way for integration of efficient power circuits with digital electronics. For power rectifiers, vertical thin-film diodes (V-TFDs) offer superior efficiency and higher frequency operation compared to lateral thin-film transistors (TFTs). However, the AOS V-TFDs reported so far require additional fabrication steps and generally suffer from low voltage handling capability. Here, we overcome these challenges by exploiting in situ reactions of molybdenum (Mo) during the solution-process deposition of amorphous zinc tin oxide film. The oxidation of Mo forms the rectifying contact of the V-TFD while the simultaneous diffusion of Mo increases the diode's voltage range of operation. The resulting V-TFDs are demonstrated in a full-wave rectifier for wireless energy harvesting from a commercial radio-frequency identification (RFID) reader. Finally, by using the same Mo film for V-TFD rectifying contacts and TFT gate electrodes, our process allows simultaneous fabrication of both devices without any additional steps. The integration of TFTs alongside V-TFDs opens a new fabrication route for future low-cost and large-area thin-film circuitry with embedded power management.

This is the aut or manuscript accepted for publication and has undergone full peer review but has not been the soft the copyediting, typesetting, pagination and proofreading process, which may lead to differences between this version and the <u>Version of Record</u>. Please cite this article as <u>doi:</u> 10.1002/adfm.201806002.

#### 1. Introduction

Additive fabrication of thin-film electronics offers critical solutions for the "More than Moore" era Thanks to compatibility with flexible substrates and large-area uniformity, additive fabrication of large-area electronics (LAE) has achieved commercial success in the display market. The use of LAE is now expanding to provide enhanced functionality to medical, wireless, sensing, and flexible systems. [1,2] To enable autonomous operation, wireless energy harvesting by thin-film components is often desired, for example in RFID tags. In parallel to these LAE efforts, the ongoing drive toward miniaturization of electronics demands functionality diversification via heterogeneous integration. Although silicon (Si) complementary metal oxide semiconductor (CMOS) integrated circuits (IC) offers better electrical performance than thin-film circuits, the maximum operation voltage of sub-22nm node Si CMOS is typically less than 1 V(3) Therefore integration with electrical components that require higher input voltages requires board-level solutions or use of high voltage (HV) Si CMOS processes with larger gate lengths. To bridge this gap, higher-voltage thin-film electronics can be directly and additively labricated on sub-22nm node CMOS.[4,5]

In both of these sectors, thin-film circuits are needed to provide power harvesting and management. For example, wireless powering of either LAE or miniaturized CMOS ICs requires alternating current-to-direct current (AC-DC) conversion, while assembly of sub-blocks for diverse functionality requires DC-DC power conversion to provide various operating voltages. Such power management circuitry requires power rectifiers and switches that operate at high efficiency over a wide range of voltages. To meet this need, numerous thin-film materials have been investigated for use in power devices. Some work has been done on thin film transistors for input/output bridging or high voltage, low-current switching, [4,6-8] but most efforts have focused on rectifiers for energy harvesters in RFID tag applications. The materials investigated

so far for power rectifiers include amorphous oxide semiconductors (AOS),<sup>[9,10]</sup> organic semiconductors,<sup>[11,12]</sup> or combined material architectures.<sup>[13]</sup> Although research on organics<sup>[14,15]</sup> is ongoing, AOS have a higher charge carrier mobility,<sup>[16]</sup> which is crucial to operate power devices at high frequency and efficiency.<sup>[17]</sup> Due to the advantageous material properties of AOS, both lateral thin-film transistors (TFTs)<sup>[9]</sup> and vertical thin-film diodes (V-TFDs)<sup>[10]</sup> have been demonstrated for use in RFID energy harvesters. V-TFDs show superior performance<sup>[10,18]</sup> because their lower turn-on voltage, larger conduction area, and shorter device length enable a lower voltage drop and higher operating frequency.

However the AOS V-TFDs demonstrated to date face two major challenges. First, the devices cannot withstand high operating voltages, limiting their use as power devices. Applying a moderate voltage vertically across a thin-film leads to high electric field within the film that can create ion migration and cause premature breakdown. [19,20] Although the dynamics of ion migration can be utilized in resistive memory (RRAM) applications, [21,22] this mechanism should be avoided in diodes that are intended to handle high voltages with long-term stability. However, the effect of ion migration within AOS on V-TFD performance has not been characterized yet. Moreover, a way to prevent this mechanism is needed to enable wider application of V-TFDs. A second challenge for AOS V-TFDs is fabrication complexity. Previously reported methods to form rectifying contacts to AOS require deposition and patterning of a new, high work function Schottky metal, often followed by sophisticated oxidation steps in order to reduce oxygen vacancy defects near Schottky interfaces. [23-25] These additional process steps make V-TFD incompatible with TFT fabrication. This has led to the frequent use of diodeconnected TFTs in rectifiers (by shorting the TFT gate and drain to form a two-terminal device). However the large on-resistance of these devices causes poor rectifier performance. [9,26]

In this study, we demonstrate a novel method to overcome these challenges by using a dualpurpose solution process. We harness the chemical evolution of our ink, which can be controlled by the material underneath, to simultaneously enable the growth of rectifying junctions as well as of high quality AOS channel layers. Our solution process not only solves the fabrication complexity issue of V-TFDs and TFTs, but it also forms a distinct layer at the Schottky barrier that prevents ion migration and enhances the voltage handling capability of V-TFDs. As a result, using a single fabrication process we are able to integrate high-voltage diode rectifiers - which can operate at a much higher frequency than TFT rectifiers - alongside TFTs, which can be used for future digital circuitry. Solution processing is an attractive, low-cost, and large-area deposition method, as its in-air deposition capability eliminates the need for expensive vacuumdeposition tools.[1] It also offers inexpensive patterning via printing techniques for future additive fabrication.[27-29] Among various AOS candidates, we use amorphous zinc tin oxide (a-Zn-Sn-O) due to its earth-abundant and non-toxic elemental composition. We have previously demonstrated a solution process for environmental-friendly, in-air deposition of a-Zn-Sn-O film with consistently high quality obtained across a wide humidity range for future large scale manufacturing.[30] Our process temperature, 520 °C, allows non-destructive, additive fabrication on standard CMOS and low-cost substrates like glass, [31,32] When our ink is deposited on a gate dielectric, it creates a high quality a-Zn-Sn-O film that can be used as a TFT channel layer. [30] When deposited on top of a Mo metallic layer, reduction-oxidation (redox) reactions and atomic diffusion of Mo occur in situ during *a*-Zn-Sn-O film coating and annealing. The redox mechanism enables formation of different interfacial layers with distinct properties in areas with different underlying patterns. This allows simultaneous fabrication of V-TFDs and TFTs by selective patterning of the underlying materials. In addition, atomic diffusion at the bottom Schottky interface greatly enhances the voltage handling capability of V-TFD. The resulting high voltage

and high frequency operation of V-TFDs enables wireless energy harvesting from a commercial high frequency (HF) RFID reader. Here we specifically choose Mo as it is one of the most commonly used metal electrodes for AOS TFTs due to its high-quality ohmic contact properties with various AOS.<sup>[33–37]</sup> Thus, our exploitation of Mo interaction with *a*-Zn-Sn-O may be widely adapted to other AOS.

#### 2. in situ Mo oxidation to form rectifying contact

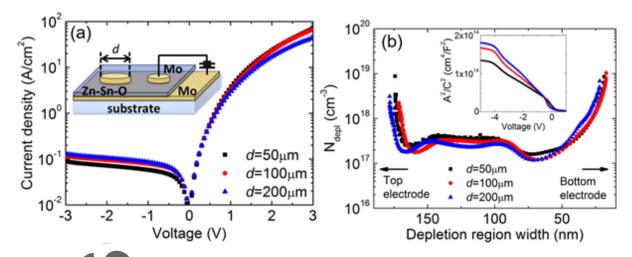

**Figure 1.** (a) Typical J-V characteristics obtained from Mo:a-Zn-Sn-O diodes with various sizes. The inset shows a schematic of the V-TFDs, where d is the diameter of the top electrode. (b) Depletion concentration ( $N_{depl}$ ) profile for various size diodes. The corresponding C-V measurements are shown in the inset. C-V characteristics were measured at 1 MHz, across a DC sweep from +1 V to -5 V, with 50 mV of AC voltage, in parallel RC model. Full depletion is achieved at -5 V, which corresponds to a film thickness of 180 nm.

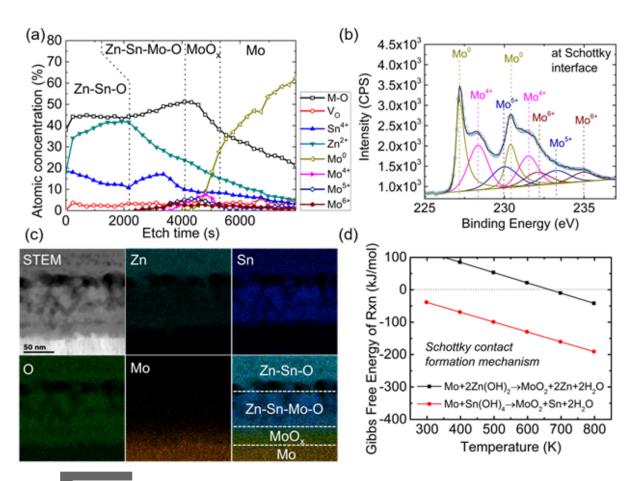

In order to explain the formation of a rectifying junction at the bottom Mo, extensive material characterization was performed as shown in **Figure 2**. X-ray photoelectron spectroscopy (XPS) depth profile was taken at the bottom Mo/a-Zn-Sn-O junction. Figure 2a reveals that two additional layers are formed as a result of *a*-Zn-Sn-O deposition on Mo. First, on top of the metallic Mo layer lies a Mo suboxide layer. In this region, Mo 3d core level analysis shows that Mo co-exists in the Mo<sup>6+</sup>, Mo<sup>5+</sup>, Mo<sup>4+</sup>, and Mo<sup>6</sup> oxidation states (Figure 2b). The Mo oxidation states transition from Mo<sup>0</sup> to Mo<sup>4+</sup> to Mo<sup>6+</sup> as we move from bottom Mo metal to top Zn-Sn-O. A similar transition of Mo oxidation state has been reported for thermally oxidized Mo and for MoO<sub>3</sub> grown on Mo substrates, where Mo<sup>6+</sup> was interpreted as fully oxidized MoO<sub>3</sub>, Mo<sup>5+</sup> as MoO<sub>3</sub> with oxygen vacancies, and Mo<sup>4+</sup> as metallic MoO<sub>2</sub> <sup>1-9</sup> Second, on top of this suboxide layer is a Zn-Sn-O layer with a noticeable amount of Mo incorporated into it (~4 at.%) and with Sn-rich composition (Zn:Sn ratio of ~5:3 compared to a ratio of ~3:1 in the upper *a*-Zn-Sn-O layer). We hereafter refer to these layers as MoO<sub>x</sub>

and Zn-Sn-Mo-O, respectively. The spatial distribution of the Mo<sup>6+</sup>, Mo<sup>5+</sup>, and Mo<sup>4+</sup> oxidation states indicates that the MoO<sub>x</sub> and Zn-Sn-Mo-O layers are formed due to oxidation and diffusion of bottom Mo during the *a*-Zn-Sn-O deposition and annealing process.

In order to confirm the formation of these distinctive layers, scanning transmission electron microscopy (STEM) and energy-dispersive X-ray spectroscopy (EDS) studies were carried out. Figure 2c shows two distinctive regions between Mo and a-Zn-Sn-O, with a  $\sim$ 50 nm thick MoO<sub>x</sub> layer and a  $\sim$ 80 nm thick Sn-rich, Mo-doped Zn-Sn-Mo-O layer. While Mo itself is low work function metal,  $\Phi_{\text{Mo}}$ -4/4-5.0 eV, [40] and is often used to form ohmic contacts to AOS, [34] its oxidized counterpart has a high work function,  $\Phi_{\text{MoOx}}$ =4.7-6.8 eV, the value of which depends on oxygen composition [39,41]. Therefore we conclude that the thick, high-work-function MoO<sub>x</sub> layer, which is generated at the bottom electrode as a result of our solution process, functions as a rectifying junction. The rectifying nature of the bottom contact is furthermore confirmed by the C-V measurements shown in Figure 1b, which show a deposition thickness of 180 nm. Cross-sectional STEM and scanning electron microscope (SEM) images likewise show that the thickness of the Zn-Sn-Mo-O layer and Zn-Sn-O layer combined is 180 nm (Figure S1 in Supporting Information). Thus, the MoO<sub>x</sub> layer functions as a rectifying contact and enables complete depletion of the Zn-Sn-Mo-O and Zn-Sn-O layers in reverse bias. This is in contrast to the ohmic top electrode that consists of metallic Mo deposited by sputtering.

The underlying mechanism of  $MoO_x$  layer formation can be explained by calculating the standard Gibbs free energy of reactions ( $\Delta G_{rxn}^{o}$ ) that occur during our solution process. When the ink is deposited on glass or alumina, the zinc and tin acetates in the solution first thermally decompose into hydroxides ( $Zn(OH)_2$  and  $Sn(OH)_4$ ), and later go through a dehydroxylation process to form a uniform a-Zn-Sn-O film:<sup>[30]</sup>

$$x\operatorname{Zn}(OH)_2 + (1-x)\operatorname{Sn}(OH)_4 \to \operatorname{Zn}_x\operatorname{Sn}_{1-x}O_{2-x} + (2-x)H_2O.$$

(1)

**Figure 2.** (a) XPS depth profile of bottom Mo/a-Zn-Sn-O deposited on Si substrate. In between the Mo and a-Zn-Sn-O, layers of MoO<sub>x</sub> and Zn-Sn-Mo-O appear. (b) XPS Mo 3d core level analysis of the MoO<sub>x</sub> layer, which corresponds to an etch time of 4800 s in (a). Hollow circles indicate the summation of the de-convoluted peaks, which overlaps with the measured curve. Details of XPS corelevel analysis methods are described in Section S1 in Supporting Information. (c) Cross-sectional STEM dark field image and EDS elemental mapping of Zn (cyan), Sn (blue), O (green), and Mo (orange) elements obtained near Mo/a-Zn-Sn-O junction. A STEM image of the entire film stack is shown in Figure S1 in Supporting Information. Two additional interfacial layers (i.e., MoO<sub>x</sub> and Zn-Sn-Mo-O) appear between metallic Mo and Zn-Sn-O, which accords with the XPS depth profile shown in (a). (d) Standard Gibbs free energy of Mo oxidation during solution process of Zn-Sn-O, showing negative values at the film anneal temperature (793 K).

However, during this process the intermediate  $Zn(OH)_2$  and  $Sn(OH)_4$  species can interact with the bottom Mo layer to form  $MoO_2$ :

$$2Zn(OH)_2 + Sn(OH)_4 + 2Mo \rightarrow 2MoO_2 + 2Zn + Sn + 4H_2O.$$

(2)

#### 3. in situ Mo diffusion to enhance voltage handling capability

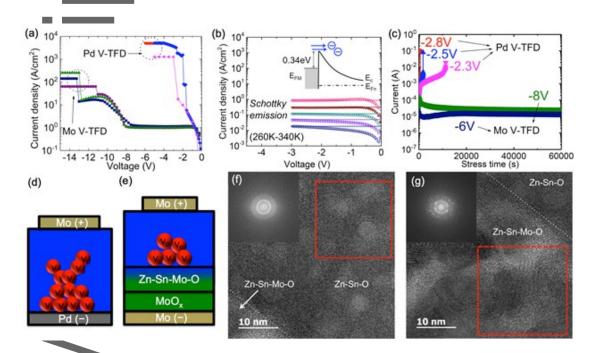

After material characterization, we evaluated the V-TFD device performance for power rectifiers (**Figure 3**). When a diode rectifies an AC voltage, most of the input voltage is applied as reverse bias across the diode, since the diode has higher impedance when it is in the off-state compared to the onstate. Therefore the diode breakdown voltage (BV) and reverse-bias-stress endurance are important parameters for rectifier applications, which determine its voltage handling capability and lifetime. The previously-reported AOS V-TFDs have faced challenges in this regard, due to low BV and severe degradation when in reverse bias. The physical origin of these weaknesses have been attributed to field-induced oxygen vacancy (V<sub>0</sub>) migration within AOS, as set-and-reset behavior was observed after breakdown in AOS V-TFDs. These weaknesses, which we also previously observed in solution-processed Pd:*a*-Zn-Sn-O diodes, significantly limit their use in rectifier applications: the rectifier degrades within short period of time (tens of minutes) and breaks down at low input AC voltage (peak-to-peak voltage of 5 V), as illustrated in Figure S3 in Supporting Information. These challenges must be overcome for power rectifiers.

The Mo:a-Zn-Sn-O diodes presented here (which will be referred as Mo V-TFD for simplicity) offer a new way to address these challenges. For oxygen vacancy migration to degrade and cause breakdown of AOS V-TFD, Vo defects must first accumulate adjacent to the Schottky interface and then form a conductive filament in order to short the bottom and top electrodes, as has often been observed in memristors. [43,44] In our Mo/a-Zn-Sn-O junctions, the layer adjacent to the MoO<sub>x</sub> Schottky contact is the Zn-Sn-Mo-O film that was formed via in situ diffusion as shown in Figure 2. Therefore, the reverse bias behavior of Mo V-TFD is determined by the dynamics of V<sub>O</sub> migration within the Zn-Sn-Mo-O layer As shown in Figure 3a, the Mo V-TFD has a high BV of over 10 V, and exhibits a constant leakage current prior to breakdown. The leakage current of Mo V-TFD was analyzed with temperature-varying J-V measurements (Figure 3b). The temperature variance and bias independence indicates that current flow is via Schottky emission without image force lowering, obeying  $J_r =$  $A^*T^2 \exp\left(\frac{\Phi_b}{kT}\right)$ , with  $A^*$  as 0.74 Acm<sup>-2</sup>K<sup>-2</sup> and  $\Phi_b$  of 0.34 eV. Thermionic emission leads to a constant leakage current, independent of reverse bias.  $\Phi_b$  is the potential barrier formed at the  $MoO_x/Zn$ -Sn-Mo-O interface; the larger the value of  $\Phi_b$ , the lower the leakage current,  $J_r$ . In the future, it may be possible to minimize leakage by increasing  $\Phi_b$  through additional oxidation of Mo via O<sub>2</sub> plasma or O<sub>2</sub> annealing.<sup>[41,45]</sup> In addition to a constant leakage current, Mo:a-Zn-Sn-O diodes show negligible degradation during reverse bias, even when relatively high voltages of 6 V or 8 V were applied for up to 60,000 s (Figure 3c).

The high BV and excellent bias-stress endurance of Mo V-TFD distinguish it from our previously-reported Pd V-TFD, as shown in Figure 3a and 3c. We note that the same *a*-Zn-Sn-O and top Mo deposition methods were used for both the Pd and Mo V-TFDs, and the resulting *a*-Zn-Sn-O thicknesses are identical (~110 nm) in these devices. As shown in Figure 3d, the poor stress endurance and low BV of the Pd V-TFD is due to oxygen vacancy (V<sub>O</sub>) migration within *a*-Zn-Sn-O, causing trap-assisted tunneling near the Schottky contact and conductive filament (CF) formation through the

bulk. In contrast with the Pd case where a-Zn-Sn-O layer forms a junction with a Pd Schottky contact (confirmed with XPS depth profile<sup>[24]</sup>), for Mo V-TFD, a Zn-Sn-Mo-O layer forms in between the Schottky junction and Zn-Sn-O. Thus, the voltage handling capability of Mo V-TFDs is dominated by Vo dynamics within Zn-Sn-Mo-O. As both BV and bias stress endurance are better for Mo V-TFD, we conclude that V<sub>0</sub> cannot easily migrate and accumulate within the Zn-Sn-Mo-O layer (Figure 3e). Our experimental data suggest a physical origin for the different oxygen vacancy behavior observed within Zn-Sn-Mo-Q. First, the Zn-Sn-Mo-O layer has a Sn-rich composition with Mo incorporated by diffusion, as shown in Figure 2a and 2c. The different metal cation stoichiometry of Zn-Sn-Mo-O compared to a-Zn-Sn-O may lead to high activation energies for V<sub>O</sub> formation and migration, caused by the change in oxygen ion hopping distance or in potential barriers within the ionically-bonded structure. This approach – modifying activation energies for V<sub>O</sub> formation and its migration with the help of impurity doping – is often used to tune forming behavior in memristive devices. [46] Second, in addition to the effect of chemical composition, the different crystallinity of the film may affect V<sub>O</sub> migration and CF forming behavior. It has been previously reported that annealing a-IGZO with diffused copper can generate crystalline clusters which results in prevention of CF forming behavior. [22] In order to characterize the crystallinity of the films, high resolution transmission electron microscopy (HRTEM) imaging was performed with the microscope operated in conventional TEM mode on the same sample shown in Figure 2. The HRTEM images and fast Fourier transform (FFT) diffraction patterns obtained for the Zn-Sn-O and Zn-Sn-Mo-O layers are shown in Figure 3f and 3g, respectively. While the Zn-Sn-O layer possesses an amorphous structure as expected, the Zn-Sn-Mo-O layer possesses a polycrystalline structure. Third, as indicated by analysis of forward J-V curves in Section S2 in Supporting Information, the Zn-Sn-Mo-O layer functions as a low-doped region, reducing the maximum electric field at the Schottky interface under reverse bias. All of these mechanisms prevent or reduce field-induced accumulation of Vo defects at the Schottky interface, as illustrated in Figure 3e. As a result, in the Mo V-TFDs, we obtain a reduced leakage current,

compared to the Pd V-TFDs, and avoid premature breakdown by CF formation. To further optimize Mo V-TFD diode performance, in the future work can be done to quantify the diffusion kinetics occurring in situ during solution-processed film deposition and annealing, in order to more precisely control the thickness and stoichiometry of the MoO<sub>x</sub> and Zn-Sn-Mo-O layers.

Figure 3. (a) Breakdown voltage (BV) > 10 V measured on Mo V-TFDs with various electrode sizes (diameter of 30 μm, 50 μm, and 100 μm). BV measured on Pd V-TFDs with the same sizes are also shown for comparison. (b) Temperature-varying reverse *J-V* measurements (symbols) of Mo V-TEDs. The bias-independent reverse current obeys Schottky emission over a potential barrier of 9.34 eV without image force lowering (solid lines). The charge transport analysis on forward current is shown in Figure S4 in Supporting Information. (c) Reverse bias stress in Mo V-TFD and Pd V-TFD. Unlike the Pd V-TFD, which was tested at < 3 V magnitude, the Mo V-TFD were tested at a higher reverse voltages, 6 V and 8 V, and still did not show any increase in leakage current. After the stress test, the Mo V-TFD still maintained its rectifying behavior as shown in the Figure S5 in Supporting Information. (b) and (c) are from 100 μm-diameter diodes. (d) In Pd V-TFD, oxygen vacancy defects (V<sub>0</sub> in red circles) accumulate near the Pd layer, which causes an increase in leakage current and premature breakdown, as shown in (c). (e) In the Mo V-TFD, the Zn-Sn-Mo-O layer prevents V<sub>0</sub> defects from accumulating near the MoO<sub>x</sub> Schottky layer, preventing an increase in leakage current and resulting in a higher BV, as shown in (c). (f) and (g) show HRTEM images near Zn-Sn-O/Zn-Sn-Mo-O interface. The interface is marked with a white dotted line. The regions for FFT analysis are marked with red dashed lines and the corresponding FFT patterns are shown in the insets. Zn-Sn-O shows an amorphous morphology in (f) while Zn-Sn-Mo-O is polycrystalline (g).

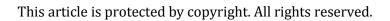

For AC rectifiers, the BV of the diode should be larger than twice the desired DC output voltage. As the DC voltage required to drive logic circuits can be as high as 5 V, a BV of > 10 V is desired. Commercial proximity HF RFID readers, which often generate output power of 200 mW with a 50  $\Omega$ source, can deliver AC peak-to-peak voltages up to ~8.9 V to the diode  $(P_{source} = \frac{1}{8} \times \frac{V_{pp}^2}{50 \,\Omega})$ . Thanks to the strong reverse bias characteristics of our Mo V-TFD, shown in Figure 3, our diode can stably rectify AC voltages within this range. To confirm the rectifier behavior of the fabricated V-TFD at high frequency and voltage ranges, we characterized the diode in a half-wave rectifier circuit, shown in Figure 4. Figure 4a inset shows the measurement setup for observing AC-to-DC conversion. In order to obtain a stable DC output voltage, the load capacitance,  $C_L$ , should minimally discharge through the load resistor,  $R_L$ , during one AC cycle (period T = 1/f), i.e.  $R_LC_L \gg 1/f$ . In addition, the ratio between  $C_L$  and the diode capacitance,  $C_D$ , defines the amplitude of the small-signal AC voltage:  $C_L$  needs to be very large compared to  $C_D$ ,  $C_L \gg C_D$ . [14,47] Therefore, a 1  $\mu F$  load capacitor and 1 M $\Omega$ load resistor were used, which gives  $R_LC_L=1$  s and satisfies  $C_L\gg C_D$ , where  $C_D$  for the  $d=100~\mu m$ diode measured here is approximately 25 pF when measured at 1 MHz at zero bias. In this configuration, the V-TFD rectifies the supplied AC voltage to DC (Figure 4a). AC peak-to-peak voltages as high as 10 V could be rectified to a DC output as high as 3 V (Figure 4b). As shown in Figure 4b, the diode does not show any cutoff behavior up to 15 MHz, indicating its usefulness for HF RFID tags operating at 13.56 MHz.

**Aut**

**Figure 4.** (a) The measurement configuration of the diode in a half-wave rectifier circuit is shown in the inset. An AC input voltage ( $V_{AC}$ ) was generated by a function generator, operated in 50 Ω mode and used in parallel with a 62 Ω input resistor. In (a),  $V_{in}$  (in black) indicates the 1 MHz, 5 V sinusoidal peak-to-peak voltage across the 62 Ω input resistor, measured using an oscilloscope.  $V_{out}$  (in red) shows the DC output voltage measured across the load. (b) The frequency response of the output voltage measured up to 15 MHz, which is the maximum frequency of the function generator, is shown for different  $V_{in}$  peak-to-peak values. Because the diode has BV > 10 V, the rectifier can rectify up to peak-to-peak voltage of 10 V. The devices tested here have diameter of 100 μm.

#### 4. Co-fabrication of wireless energy harvesters alongside TFT switches

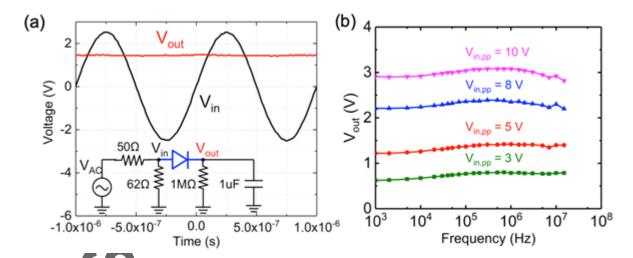

The commercialization of AOS TFTs in display backplane applications has been enabled by their superior switching performance in metal-insulator-semiconductor field-effect transistors (MISFETs). MISFETs can be diode-connected to perform rectifying functions, but their performance is significantly worse than that of a V-TFD made using the same active semiconductor layer. To confirm that Mo V-TFDs can be used to enhance rectifier performance of thin-film electronics, we next demonstrated the simultaneous fabrication of Mo V-TFDs and MISFETs on the same substrate (Figure 5). In future thin film circuits, TFTs can be used for digital logic and analog amplification, while V-TFDs integrated on the same die can be used for efficient and high-frequency AC-DC rectification. The fabrication process flow is illustrated in Figure 5a. A key feature of our process is

that the Zn-Sn-O ink goes through different chemical evolution during annealing based on the material underneath. On top of Al<sub>2</sub>O<sub>3</sub> gate dielectric, it forms a high quality AOS channel layer for TFTs, while on top of exposed bottom Mo layers, it forms MoO<sub>x</sub> and Zn-Sn-Mo-O layers for high-voltage V-TFDs. The former reaction involves dehydroxylation processes (Equation (1)), while the latter involves Mo diffusion and oxidation (Equation (2)). For this sample, we deposited five spin-coated layers of Zn-Sn-O instead of seven, as were shown in Figure 1 - 4. We chose five spin-coated layers for Zn-Sn-O because we previously reported high quality TFT performances with five-layer Zn-Sn-O,<sup>[30]</sup> and V-TFDs made with five layers shows higher on-current while maintaining good BV for use in energy harvesters for our 200 mW RFID reader, as shown in Figure S6 in Supporting Information. Figure 5b shows transfer curves of fabricated TFTs, with enhancement-mode operation. For simple logic circuits, enhancement-mode is more desirable than depletion-mode, as it does not require level shifting.<sup>[48]</sup>

To justify the need for V-TFDs in rectifier applications, we compare the performance of V-TFDs with TlTs used in diode configuration, i.e. with gate and drain shorted. When enhancement-mode TFTs are used in the diode configuration, the positive turn-on voltage significantly limits the oncurrent. In addition, diode-connected TFTs have a fundamental geometric weakness compared to V-TFDs, due to the long transit length (the channel length) and narrow conduction area (the cross-sectional area of the thin film). These limits have been previously reported for vacuum-deposited AOS.<sup>[9,10,17,10,26,48]</sup> Despite attempts to minimize lateral resistance by increasing channel width,<sup>[49]</sup> and decreasing channel length<sup>[50,51]</sup> or overlap length,<sup>[52]</sup> the on-current of diode-connected TFTs is still low, compared to V-TFDs. In addition, to obtain short TFT lengths, high-resolution photolithography is required, which can be prohibitive.

To illustrate these points, a V-TFD and a TFT in a diode configuration were measured and compared. Both devices were located on the same sample and co-fabricated, and both had a size of

$100 \ \mu m \times 100 \ \mu m$ . For the TFT, the top contact area is included in the area calculation. Microscope images of these devices are shown in Figure S7 in Supporting Information. Due to the V-TFD's lower turn-on voltage, larger conduction area (size of electrode), and shorter carrier transit length (film thickness) compared to the lateral TFT, the on-current of the V-TFD was more than five orders of magnitude higher than the diode-connected TFT, as shown in Figure 5c. A high on-current is important, as it not only reduces the voltage drop and increases the overall efficiency of a rectifier, but also increases rectifier operating frequency.

The theoretical operating frequency limits of the V-TFD and TFT were calculated for comparison. These were estimated using two approaches: the transit time of carriers  $(f_t)$  and the on-current of the rectifier  $(f_c)$ .  $f_t$  considers the time that it takes for the fastest electron (with velocity v) to transit from one electrode to the other, i.e. to travel the distance L. This frequency can be expressed as:

$$f_t = \frac{v}{2\pi L} = \mu \frac{V_{in} - V_{out}}{2\pi L^2},\tag{3}$$

where  $V_{out}$  is the maximum forward voltage applied across the rectifier and  $\mu$  is the effective carrier mobility.  $f_c$  is the frequency at which the charge dissipated through the load  $(R_L)$  becomes comparable to the charge stored on the load capacitance  $(C_L)$  by the diode on-current. The maximum operating frequency for V-TFD  $(f_{c,TFD})$  and diode-connected TFT  $(f_{c,TFT})$  are expressed as: [47]

$$f_{c,TFD} = \frac{9\mu_{TFD}}{16\pi L_{TFD}^2 V_{out}} \left\{ \left(V_{in}^2 + 2V_{out}^2\right) \cos^{-1}\left(\frac{V_{out}}{V_{in}}\right) - 3V_{out}\sqrt{V_{in}^2 - V_{out}^2} \right\} (4)$$

$$f_{c,TFT} = \frac{\mu_{TFT}}{4\pi L_{TFT}^2 V_{out}} \left\{ \left( V_{in}^2 + 2V_{out}^2 \right) \cos^{-1} \left( \frac{V_{out}}{V_{in}} \right) - 3V_{out} \sqrt{V_{in}^2 - V_{out}^2} \right\}$$

(5)

**Figure 5.** (a) Simplified schematic of simultaneous fabrication of V-TFD and TFT on a single substrate. Thin films with different chemical composition are grown via different chemical evolution during solution deposition of Zn-Sn-O. Specifically, Zn-Sn-O is grown via dehydroxylation on top of Al<sub>2</sub>O<sub>3</sub>, while Mo oxidation and diffusion occur on top of bottom Mo, creating MoO<sub>x</sub> and Zn-Sn-Mo-O layers in specific regions. A two-dimensional cross-sectional view (A  $\leftrightarrow$  Á) of completed devices is shown in step 5. (b) Transfer curves obtained from a TFT with device dimensions of 100 μm in width, 3 μm in channel length, and 6 μm in overlap length, which leads to 100 μm × 100 μm in overall size, including source and drain contacts. Output curves are shown in Figure S7c in Supporting Information. (c) Comparison of *I-V* curves obtained from TFT in (b) with its gate and drain connected, and from V-TFD with 100 μm × 100 μm size. Hollow circles and squares are measured data and dotted lines are from the on-current model used to calculate  $f_{c,TFT}$  and  $f_{c,TFD}$  in (d). (d) Maximum operating frequencies, calculated based on transit time ( $f_t$ ) and measured on-current ( $f_c$ ).

As seen in Equation (3) - (5), a shorter transit length, L, and a higher effective mobility,  $\mu$ , lead to a higher rectifier operating frequency. Using a fixed  $V_{in}$  of 5 V,  $f_{CTFD}$ ,  $f_{CTFD}$ ,  $f_{CTFD}$ , and  $f_{CTFT}$  were calculated and are shown in Figure 5d. For calculation of Equation (3), a Hall mobility of 5 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, extracted from an identical five-layer a-Zn-Sn-O film was used. [30] For calculation of Equation (4) and (5),  $\mu_{TFT}$  and  $\mu_{TFD}$  were extracted from the experimental I-V curves shown Figure 5c, following the well-established method for  $f_c$  calculations. [14,15,17,47] An extended discussion of the frequency calculations can be found in Section S3 in Supporting Information. It is clear that V-TFDs have a higher operating frequency than TFTs connected in the diode configuration. The maximum frequency of the V-TFD under  $V_{in}$  of 5 V and  $V_{out}$  of 3 V (i.e., the magenta line in Figure 4b) may be as high as 1.6 GHz. This estimate agrees with the previous demonstration of gigahertz-range operation of AOS V-TFDs made with a-IGZO. [10,18] The high operating frequency of the V-TFD is primarily due to the higher effective  $\mu$  due to the lack of a turn-on voltage and the shorter L due to the vertical structure. For the TFT, L corresponds to the channel length ( $L_{ITT}$  = 3  $\mu$ m) while for V-TFD, it is the film thickness ( $L_{TFD}$  = 150 nm).

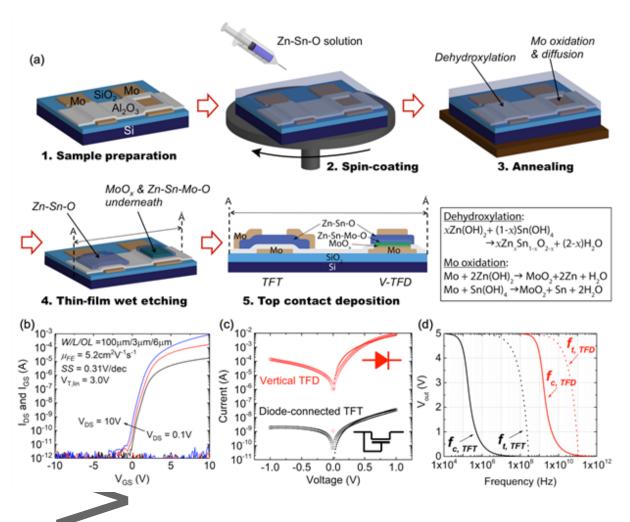

Lastly, the wireless energy harvesting capability of solution-processed V-TFDs was tested, using a full-wave rectifier with four  $100~\mu m \times 100~\mu m$  V-TFDs fabricated on the same sample (**Figure 6**). To validate its applicability for wireless energy harvesting, a commercial 13.56 MHz RFID tag reader (DLP-RFID1, DLP Design) and antenna (DLP-RFID-ANT, DLP Design) were used. The reader has an output power of 200~mW and a read range of 10~cm (Protocol: ISO 15693~and ISO 18000-3). The full-wave rectifiers were wire-bonded to a printed circuit board (PCB) on which the load components and SubMiniature version A (SMA) connectors were soldered. As shown in Figure 6a, the PCB was connected to the antenna to assess the energy harvested via inductive coupling from a commercial RFID reader.

The circuit diagrams of the wireless test setup for both input and output voltages are shown in Figure 6b. The AC voltage ( $V_{in}$ ) delivered to the antenna via inductive coupling was measured using 1 M $\Omega$  load resistor (Figure 6b (bottom)). As shown in Figure 6c, the maximum peak-to-peak  $V_{in}$  coupled from the reader to the antenna at 0 mm of distance was  $\sim$ 8.7 V, which gives the output power of the reader to be  $V_{rms}^2/50~\Omega \approx 190~\text{mW}$ . For DC output voltage ( $V_{out}$ ) measurement, a 1  $\mu$ F load capacitor and 1 M $\Omega$  load resistor attached to PCB via surface mount were connected to full-wave rectifier, as shown in Figure 6b (top). The result, shown in Figure 6c inset, measured with an oscilloscope, is excellent AC-DC conversion using the V-TFD FWR for wireless energy harvesting. As shown in Figure 6c, reasonable output voltages are measured across the load as a function of distance, with  $V_{out}/V_{in}$  exceeding 80% at < 40 mm of distance. At 0 mm,  $V_{out}$  as high as  $\sim$ 5 V is obtained, which demonstrates that V-TFDs rectifiers can be used to power thin-film logic circuitry. [53] In order to obtain a higher  $V_{out}$  at larger distance, a voltage multiplier configuration can be implemented. [11] A comprehensive assessment of the FWR behavior at various input voltage and frequencies, obtained by additional measurements  $V_{out}$  and  $V_{in}$  in a wired configuration, is shown in Figure S8 in Supporting Information.

# Author

Figure 6. (a) Wireless energy harvesting experimental setup. A commercial HF (13.56 MHz) RFID antenna and reader with 200 mW output power were placed in parallel. The power from the reader was wirelessly harvested using the antenna while the distance between them was varied. The antenna was attached via SMA connection to an FWR wire-bonded onto a PCB with surface-mount loads. The DC output voltage of the FWR was measured with an oscilloscope. The inset shows a microscope image of a FWR with four 100 μm × 100 μm V-TFDs. (b) Circuit diagrams showing the wireless energy harvesting measurement setup (top). To compare the measured  $V_{out}$  with  $V_{in}$ ,  $V_{in}$  was measured as the voltage across a 1 MΩ resistor attached to the antenna, without the rectifier included (bottom). The maximum peak-to-peak  $V_{in}$  obtained at a distance of 0 mm was ~8.7 V, which gives  $P_{out} = V_{rms}^2/50 \,\Omega \approx 190$  mW, close to the maximum output power of the reader. (c) The magnitude of  $V_{in}$  and  $V_{out}$  as a function of separation distance.  $V_{out}$  exceeds over  $V_{in}$  when the distance is < 10 mm, which is attributed to resonance due to mutual inductance. The inset shows  $V_{in}$  and  $V_{out}$  measured over time with the antenna and reader separated by a distance of 21 mm.

#### 5. Conclusion

In conclusion, we have developed a facile solution process that enables integration of high-voltage V-TFDs during the fabrication of Zn-Sn-O TFTs. We achieve this by exploiting in situ redox and diffusion of bottom Mo electrodes that occurs during ink-based deposition and annealing of Zn-Sn-O. The chemical interaction of the bottom Mo during AOS deposition not only forms a rectifying junction for V-TFDs, but also increases its voltage handling capability for rectifier applications by forming a low-doped Zn-Sn-Mo-O intermediate layer. After characterizing the effect of Mo oxidation and diffusion, which leads to formation of a rectifying junction and improvement in bias-stress endurance. V-TFDs were co-fabricated with TFTs on the same sample, without any additional

fabrication steps. Both of the devices were characterized and compared for power rectifying applications. The performance of V-TFD diodes is far superior to that of diode-connected TFTs of the same size when operated at the same voltage, due to the larger on-current and shorter device length of V-TFDs: V-TFDs fabricated here show on-current at least four orders of magnitude higher than TFT, with the estimated maximum operating frequency being three orders of magnitude higher. To experimentally confirm the usefulness of the Mo-V-TFD as a power rectifier thanks to its enhanced voltage handling capability, wireless energy harvesting using a full-wave rectifier was demonstrated with a commercial RFID reader. Despite the advantages of V-TFDs over diode-connected TFTs for rectifiers, three-terminal TFTs have unique functionality that cannot be replaced by V-TFDs. For example, TFTs are required for digital logic circuits, analog amplification, and pulse-width modulation in DC-DC conversion. TFTs fabricated in this work show enhancement-mode operation, and can be fabricated alongside V-TFD rectifiers to enhance the performance of thin-film electronics.

To our knowledge, this is the first report of simultaneous formation of different materials via chemical evolution of ink in order to fabricate different active circuit elements with a single solution-process. Previously, Schottky diodes with AOS, including vacuum-deposited AOS, have only been reported using noble, high-work function metals for rectifying contacts. [18,23-25] Such metals are disadvantageous as they are often incompatible with TFTs due to poor ohmic contact formation, they may require additional surface treatments to reduce oxygen vacancies near the Schottky interface, [23-25] and AOS V-TLDs fabricated with such metals often show vulnerability to bias stress. [19,20] In this work, we report for the first time a novel way to make a rectifying contact starting with low-work function Mo, a metal widely used for AOS TFTs, by utilizing in situ formation of the Schottky contact during Mo interaction with our Zn-Sn-O solution ink. The Mo oxidation and diffusion that occur during solution process, demonstrated here, can be widely exploited not only to enhance bias stress endurance of the films, but also to create novel fabrication routes for thin-film circuitry for future

LAE or heterogeneous integration. For wider implementation of thin-film circuitry, the development of fully solution-processed electronics is highly desirable. To realize our MoO<sub>x</sub>-based V-TFD with a fully solution-processed approach, solution-processed MoO<sub>x</sub> can be used for the bottom Schottky contact, while the top ohmic contact could be replaced with solution-processed ITO or IZO. In this scenario, because solution-processed Mo has not been developed, a low-work-function bottom gate metal for TFTs can be achieved by developing an area-selective, in situ reduction process, in which a solution-processed MoO<sub>x</sub> layer could be converted into a metallic Mo gate metal during subsequent gate insulator deposition and annealing.

#### 6. Experimental Section

Preparation of precursor solutions and film formation: The α-Zn-Sn-O layer was deposited by spin-coating a 0.5 or metal acetate precursor solution. Zinc acetate dihydrate (99.999%, Zn(CH<sub>3</sub>COO)<sub>2</sub>·2H<sub>2</sub>O, CAS number 5970-45-6, Sigma-Aldrich), and tin (II) acetate (Sn(CH<sub>3</sub>COO)<sub>2</sub>, CAS number 638-39-1, Sigma-Adrich) were dissolved in 2-methoxyethanol (99.8%, CH<sub>3</sub>OCH<sub>2</sub>CH<sub>2</sub>OH, CAS number 109-86-4, Sigma-Aldrich) and ethanolamine (≥ 99.5%, NH<sub>2</sub>CH<sub>2</sub>CH<sub>3</sub>OH, CAS number 141-43-5, Sigma-Aldrich), with a Zn:Sn ratio of 7:3. The solution was stirred for 12 hours and filtered through a 0.22-μm syringe filter during dispensing, followed by spin-coating at 3000 rpm for 30 seconds. Each spun layer was pre-annealed at 520 °C for one minute at controlled numidity and temperature. After spin-coating the final layer, the samples were post-annealed at 520 °C for one hour. We have previously used this process to deposit smooth, amorphous zinc tin oxide semiconductor layers and fabricate thin film transistors<sup>[30,54]</sup> and Schottky diodes.<sup>[24,55]</sup>

Vertical thin-film diode fabrication: First, heavily-doped n-type Si (n<sup>++</sup>-Si (Sb), 0.01-0.02 Ω·cm, <100>) was used as a substrate, which was solvent-cleaned and dried. 100-nm Mo was sputtered to

form the bottom electrode (Kurt J. Lesker Lab 18). After solvent cleaning, seven layers of Zn-Sn-O were deposited using the solution process described above. To expose the bottom Mo electrode, the deposited Zn-Sn-O layer at the edge of the sample was wet etched using dilute HCl and HNO<sub>3</sub> solution. After another solvent cleaning, a top electrode of 100-nm Mo was sputtered to form an ohmic contact to a-Zn-Sn-O,<sup>[34]</sup> and patterned with lift-off. Electrical characterization was done using an HP4156A semiconductor parameter analyzer and an HP 4284A Precision LCR meter. Temperature-dependent current-voltage measurements were taken using an HP4156A semiconductor parameter analyzer with a Lakeshore Cryotronics TTPX cryogenic probe station. For AC-DC measurements on a half-wave rectifier, an HP 33120A function generator was used with a Tektronix MSO2024b oscilloscope.

Co-fabrication of thin-film diode and transistor: Bottom-Schottky-contact V-TFDs were co-fabricated with bottom-gate, top-contact TFTs. Heavily-doped n-type Si with 100-nm thermally grown SiO<sub>2</sub> was used as the substrate. On top of a cleaned substrate, 60-nm Mo was sputtered to form the gate electrode for TFT and bottom electrode for V-TFD (Kurt J. Lesker Lab 18). Then, bottom Mo was patterned using a reactive ion etching (LAM 9400). Next, a 55-nm Al<sub>2</sub>O<sub>3</sub> gate dielectric was deposited using atomic layer deposition at 250 °C (Oxford OpAL ALD). The Al<sub>2</sub>O<sub>3</sub> thickness was confirmed using spectroscopic reflectometry. To make an opening for bottom gate metal for TFT and to grow V-TFD, the Al<sub>2</sub>O<sub>3</sub> layer was patterned by wet etch, using dilute NH<sub>4</sub>OH. After solvent cleaning, five layers of Zn-Sn-O solution were deposited using the process described above. Next, the solution-processed Zn-Sn-O layer was patterned by wet etch, using dilute HCl and HNO<sub>3</sub> solution. This etch process enables device isolation and exposes the bottom gate electrode for TFT measurements. Top electrodes of 100-nm Mo were then sputtered to form ohmic contact for both TFTs and TFDs (Kurt J. Lesker Lab 18), and were patterned via lift-off. The fabrication steps are identical to those required for bottom-gate top-contact TFTs.

Material characterization: XPS was measured using Kratos Axis Ultra XPS. A monochromatic Al x-ray source (8 mA and 14 kV) was used with a 110 μm aperture, pass energy of 20 eV, and step size of 0.1 eV. The Kratos charge neutralizer system was used. For depth profiling, argon ion sputtering was used with energy of 5 kV and ion source extractor current of approximately 90 μA, which resulted in a sputtering rate of 2-3 nm·min<sup>-1</sup>. XPS measurements were performed between 240-s sputtering intervals. For TEM measurements, an in-situ FIB lift-out cross-sectional specimen was studied by using a IEOL JEM-3100R05 analytical electron microscope (AEM) attached with double Cs-correctors operated at 300 keV. Element mapping was conducted using X-ray signals with the microscope performed in scanning transmission electron microscopy (STEM) mode. High-angle annular dark-field (HAADF) images were taken for defining mapping regions.

#### **Supporting Information**

Supporting Information is available from the Wiley Online Library or from the author.

#### Acknowledgements

This work was supported by SPAWAR through DARPA Young Faculty Award N66001-14-1-4046 under program managers Dr. Daniel Green and Dr. Young-Kai Chen. Any opinions, findings, conclusions or recommendations expressed in this publication are those of the authors and do not necessarily reflect the views of DARPA or SPAWAR. Y.S. was supported in part by the Kwanjeong Educational Foundation. Portions of the work reported here were performed in the Lurie Nanofabrication Facility and Michigan Center for Materials Characterization, which are supported by the University of Michigan's College of Engineering. The authors thank Ming-Hsun Lee for the help with TEM sample preparation.

Received: ((will be filled in by the editorial staff))

Revised: ((will be filled in by the editorial staff))

Published online: ((will be filled in by the editorial staff))

#### References

- [1] A. C. Arias, J. D. MacKenzie, I. McCulloch, J. Rivnay, A. Salleo, *Chem. Rev.* **2010**, *110*, 3.

- [2] K. Myny, Nat. Electron. **2018**, 1, 30.

- [3] T. van Breussegem, M. Steyaert, *CMOS integrated capacitive DC-DC converters*; Analog circuits and signal processing; Springer: New York, **2013**.

- [4] A. Marette, A. Poulin, N. Besse, S. Rosset, D. Briand, H. Shea, *Adv. Mater.* **2017**, *29*, 1700880.

- [5] K. Kaneko, N. Inoue, S. Saito, N. Furutake, H. Sunamura, J. Kawahara, M. Hane, Y. Hayashi, in *IEDM Tech. Dig.* IEEE, **2011**, 7.4.1.

- [6] C. Allemang, R. L. Peterson, in 2017 75th Annual Device Research Conference (DRC), IEEE, South Bend, IN, 2017, 1.

- [7] M. L. Schuette, A. J. Green, K. D. Leedy, J. P. McCandless, G. H. Jessen, in *Proc. of SPIE, Oxide-based Materials and Devices VIII* (Eds: F. H. Teherani, D. C. Look, D. J. Rogers), **2017**, 10105, 1010512.

- [8] H. Sunamura, K. Kaneko, N. Furutake, S. Saito, M. Narihiro, M. Hane, Y. Hayashi, in *VLSI Technology (VLSIT), 2013 Symposium on*, IEEE, **2013**, T250.

- [9] T. Kawamura, H. Wakana, K. Fujii, H. Ozaki, K. Watanabe, T. Yamazoe, H. Uchiyama, K. Torii, *IEEE Trans. Electron Devices* **2012**, *59*, 3002.

- [10] A. Chasin, V. Volskiy, M. Libois, K. Myny, M. Nag, M. Rockele, G. A. E. Vandenbosch, J. Genoe, G. Gielen, P. Heremans, *IEEE Trans. Electron Devices* **2014**, *61*, 3289.

- [11] M. Jung, J. Kim, J. Noh, N. Lim, C. Lim, G. Lee, J. Kim, H. Kang, K. Jung, A. D. Leonard, J. M. Tour, G. Cho, *IEEE Trans. Electron Devices* **2010**, *57*, 571.

- [12] V. Fiore, P. Battiato, S. Abdinia, S. Jacobs, I. Chartier, R. Coppard, G. Klink, E. Cantatore, E. Ragonese, G. Palmisano, *IEEE Trans. Circuits Syst. Regul. Pap.* **2015**, *62*, 1668.

- [13] K. Myny, M. Rockelé, A. Chasin, D.-V. Pham, J. Steiger, S. Botnaras, D. Weber, B. Herold, J. Ficker, B. van der Putten, G. H. Gelinck, J. Genoe, W. Dehaene, P. Heremans, *IEEE Trans. Electron Devices* **2014**, *61*, 2387.

- [14] C. Kang, J. Wade, S. Yun, J. Lim, H. Cho, J. Roh, H. Lee, S. Nam, D. D. C. Bradley, J.-S. Kim, C. Lee, *Adv. Electron. Mater.* **2016**, *2*, 1500282.

- [15] T. M. Kraft, P. R. Berger, D. Lupo, Flex. Print. Electron. 2017, 2, 033001.

- [16] K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, H. Hosono, *Nature* **2004**, *432*, 488.

- [17] J. Semple, D. G. Georgiadou, G. Wyatt-Moon, G. Gelinck, T. D. Anthopoulos, *Semicond. Sci. Technol.* **2017**, *32*, 123002.

- [18] J. Zhang, Y. Li, B. Zhang, H. Wang, Q. Xin, A. Song, *Nat. Commun.* **2015**, *6*, 7561.

- [19] Y. Son, R. L. Peterson, in 2017 75th Annual Device Research Conference (DRC), IEEE, South Bend, IN, 2017, 1.

- [20] Y.-S. Fan, P.-T. Liu, *IEEE Trans. Electron Devices* **2014**, *61*, 1071.

- [21] Z. Q. Wang, H. Y. Xu, X. H. Li, H. Yu, Y. C. Liu, X. J. Zhu, Adv. Funct. Mater. 2012, 22, 2759.

- [22] H.-W. Yeon, J. Jo, H. Song, Y. Kang, S. Na, H. Yoo, S.-Y. Lee, H. Cho, H.-Y. Kang, J.-K. Jung, S. Han, M. Kim, Y.-C. Joo, Adv. Funct. Mater. 2017, 27, 1700336.

- [23] A. Chasin, S. Steudel, K. Myny, M. Nag, T.-H. Ke, S. Schols, J. Genoe, G. Gielen, P. Heremans, *Appl. Phys. Lett.* **2012**, *101*, 113505.

- [24] Y. Son, J. Li, R. L. Peterson, ACS Appl. Mater. Interfaces **2016**, 8, 23801.

- [25] T. Schultz, S. Vogt, P. Schlupp, H. von Wenckstern, N. Koch, M. Grundmann, *Phys. Rev. Appl.* **2018**, 9.

- [26] B. R. McFarlane, P. Kurahashi, D. P. Heineck, R. E. Presley, E. Sundholm, J. F. Wager, *IEEE Electron Device Lett.* **2010**, *31*, 314.

- [27] W.-J. Lee, W.-T. Park, S. Park, S. Sung, Y.-Y. Noh, M.-H. Yoon, *Adv. Mater.* **2015**, *27*, 5043.

- [28] W. J. Scheideler, R. Kumar, A. R. Zeumault, V. Subramanian, *Adv. Funct. Mater.* 2017, 27, 1606062.

- [29] S. K. Garlapati, M. Divya, B. Breitung, R. Kruk, H. Hahn, S. Dasgupta, *Adv. Mater.* **2018**, 1707600.

- [30] Y. Son, A. Liao, R. L. Peterson, J. Mater. Chem. C 2017, 5, 8071.

- [31] G. Liu, S. J. Fonash, Appl. Phys. Lett. 1993, 62, 2554.

- [32] S. Sedky, *IEEE Trans. Electron Devices* **2001**, 48, 9.

- [33] K. Park, C.-H. An, B.-I. Hwang, H.-J. Lee, H. Kim, K. Son, J.-Y. Kwon, S. Lee, *J. Mater. Res.* **2010**, *25*, 266.

- [34] W. Hu, R. L. Peterson, Appl. Phys. Lett. 2014, 104, 192105.

- [35] Y. Ueoka, Y. Ishikawa, J. P. Bermundo, H. Yamazaki, S. Urakawa, Y. Osada, M. Horita, Y. Uraoka, *Jpn. J. Appl. Phys.* **2014**, *53*, 03CC04.

- [36] "Q. Wu, L. Xu, J. Xu, H. Xie, C. Dong, Mater. Sci. Semicond. Process. 2016, 48, 23.

- [37] X. Liu, H. Xu, H. Ning, K. Lu, H. Zhang, X. Zhang, R. Yao, Z. Fang, X. Lu, J. Peng, Sci. Rep. 2018, 8.

- [38] R. F. Pierret, *Semiconductor Device Fundamentals*; Addison-Wesley Publishing Company: Reading, Massachussets, **1996**.

- [39] M. T. Greiner, L. Chai, M. G. Helander, W.-M. Tang, Z.-H. Lu, *Adv. Funct. Mater.* **2013**, *23*, 215.

- [40] *CRC Handbook of Chemistry and Physics* (Ed: W. M. Haynes), CRC Press/Taylor & Francis, Boca Raton, FL, **2017**.

- [41] M. T. Greiner, M. G. Helander, Z. B. Wang, W. M. Tang, J. Qiu, Z. H. Lu, *Appl. Phys. Lett.* **2010**, *96*, 213302.

- [42] C. R. Valenta, G. D. Durgin, *IEEE Microw. Mag.* **2014**, *15*, 108.

- [43] J.-Y. Chen, C.-W. Huang, C.-H. Chiu, Y.-T. Huang, W.-W. Wu, Adv. Mater. 2015, 27, 5028.

- [44] Y. Yang, W. Lu, Nanoscale **2013**, *5*, 10076.

- [45] L. D. López-Carreño, G. Benítez, L. Viscido, J. M. Heras, F. Yubero, J. P. Espinós, A. R. González-Elipe, *Surf. Interface Anal.* **1998**, *26*, 235.

- [46] S. Kim, S. Choi, J. Lee, W. D. Lu, ACS Nano **2014**, 8, 10262.

- [47] S. Steudel, S. De Vusser, K. Myny, M. Lenes, J. Genoe, P. Heremans, *J. Appl. Phys.* **2006**, 99, 114519.

- [48] Y.-H. Kim, J.-S. Heo, T.-H. Kim, S. Park, M.-H. Yoon, J. Kim, M. S. Oh, G.-R. Yi, Y.-Y. Noh, S. K. Park, *Nature* **2012**, *489*, 128.

- [49] C.-S. Chuang, T.-C. Fung, B. G. Mullins, K. Nomura, T. Kamiya, H.-P. D. Shieh, H. Hosono, J. Kanicki, in *SID Symposium Digest of Technical Papers*, Wiley Online Library, **2008**, *39*, 1215.

- [50] S. F. Nelson, D. H. Levy, L. W. Tutt, Appl. Phys. Lett. 2012, 101, 183503.

- [51] Y. Wang, J. Yang, H. Wang, J. Zhang, H. Li, G. Zhu, Y. Shi, Y. Li, Q. Wang, Q. Xin, Z. Fan, F. Yang, A. Song, *IEEE Trans. Electron Devices* **2018**, 1.

- [52] N. Munzenrieder, L. Petti, C. Zysset, T. Kinkeldei, G. A. Salvatore, G. Troster, *IEEE Trans. Electron Devices* **2013**, *60*, 2815.

- [53] H. Chen, Y. Cao, J. Zhang, C. Zhou, *Nat. Commun.* **2014**, *5*.

- [54] W. Hu, R. L. Peterson, J. Mater. Res. 2012, 27, 2286.

- [55] Y. Son, R. L. Peterson, Semicond. Sci. Technol. 2017, 32, 12LT02.

- [56] K. Song, D. Kim, X.-S. Li, T. Jun, Y. Jeong, J. Moon, J. Mater. Chem. 2009, 19, 8881.

- [57] K. Song, W. Yang, Y. Jung, S. Jeong, J. Moon, J. Mater. Chem. 2012, 22, 21265.

- [58] X. Li, W. G. H. Choy, F. Xie, S. Zhang, J. Hou, J. Mater. Chem. A 2013, 1, 6614.

- [59] S. R. Hammond, J. Meyer, N. E. Widjonarko, P. F. Ndione, A. K. Sigdel, A. Garcia, A. Miedaner, M. T. Lloyd, A. Kahn, D. S. Ginley, J. J. Berry, D. C. Olson, *J. Mater. Chem.* **2012**, *22*, 3249.

We develop a facile solution processing method that can fabricate vertical thin-film diodes and lateral thin-film transistors in a single process. By exploiting in situ redox and diffusion of a bottom molybdenum electrode occurring during semiconductor deposition, the thin-film diodes achieve high voltage and high frequency operation. Furthermore, we demonstrate their use in full wave rectifiers for wireless energy harvesting.

**Keyword** Thin Films

Youngbae Son and Rebecca L. Peterson\*

Exploiting in situ Redox and Diffusion of Molybdenum to Enable Thin-Film Circuitry for Low-Cost Wireless Energy Harvesting