# Exploiting Sparsity, Compression and In-Memory Compute in Designing Data-Intensive Accelerators

by

Thomas Chih Chen

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in the University of Michigan 2019

Doctoral Committee:

Associate Professor Zhengya Zhang, Chair Assistant Professor Ronald G. Dreslinski Professor Michael P. Flynn Professor Wei Lu Thomas Chih Chen tcchen@umich.edu ORCID iD: 0000-0003-3168-9122

© Thomas Chih Chen 2019 All Rights Reserved

### ACKNOWLEDGEMENTS

First, I sincerely thank my advisor Prof. Zhengya Zhang, for his guidance, help, and support over the years. His advice and encouragement have inspired me to overcome greater challenges and deeply influenced my research. Prof. Zhangs consideration and good insights have developed many students professionally, with broader views and maturity. All of us appreciate his dedication to the group. I would like to thank Prof. Wei Lu, Prof. Michael Flynn, Prof. Ronald Dreslinski for being part of my committee. They gave many constructive suggestions on my research projects and provided valuable advice for my dissertation. I would also like to thank Prof. Mark Kushner and Prof. Olshausen for sharing insightful ideas and extending my research toward a wider range of applications.

My research could not be completed without the help and support from the sponsors: DARPA (HR0011-17-2-0018), the SONIC Center, Intel, and NSF (GRFP DGE 1256260), and the University of Michigan. I would like to thank them for sponsoring my works.

I am thankful for the discussions and collaborative efforts with my lab mates Phil Knag, Jung Kuk Kim, Chia-Hsiang Chen, Yun Sung Park, Shuanghong Sun, Yaoyu Tao, Ching-En Lee, Jacob Botimer, Shiming Song, Chester Liu, Sung-Gun Cho, Teyuh Chou, and Reid Pinkham. Working with them has been an invaluable part of my years at the University of Michigan. Their insights and support have helped me grow as a researcher. I appreciate those whom I know in SI program, MICL, EECS, and other engineering departments for their support. I value the interactions and friendships I have made here.

Finally, I would like to thank my parents for their continuous support. I would also like to thank my siblings and relatives who have been around and cheering me up over the years. Again, I appreciate the great individuals at the University of Michigan, sponsors, friends, colleagues, and family who have influenced me to complete this dissertation.

# TABLE OF CONTENTS

| ACKNOWLE    | EDGEMENTS                                                 | ii                                     |

|-------------|-----------------------------------------------------------|----------------------------------------|

| LIST OF FIG | GURES                                                     | vi                                     |

| LIST OF TAL | BLES                                                      | ix                                     |

| ABSTRACT    |                                                           | х                                      |

| CHAPTER     |                                                           |                                        |

| I. Intro    | duction                                                   | 1                                      |

| 1.1<br>1.2  | Related Work and Challenges                               | $     4 \\     7 \\     8 \\     9   $ |

| II. Desig   | gn of Video Sequence Inference Processor                  | 12                                     |

| 2.1         | Introduction                                              | 12                                     |

| 2.2         | Video Inference Algorithm Formulation                     | 14                                     |

| 2.3         | Sparse and All-Spiking Inference Formulation              | 19                                     |

|             | 2.3.1 Rectification and Sparsification                    | 19                                     |

|             | 2.3.2 Design Specification and Parameter Settings         | 21                                     |

| 2.4         | Design of Video Inference Processor                       | 26                                     |

|             | 2.4.1 Dictionary Compression and Non-Uniform Quantiza-    |                                        |

|             | tion                                                      | 27                                     |

|             | 2.4.2 Residual Layer $\ldots$                             | 28                                     |

|             | 2.4.3 Charge Layer                                        | 30                                     |

|             | 2.4.4 Activate Layer                                      | 32                                     |

|             | 2.4.5 Summary of Design Optimizations                     | 33                                     |

| 2.5         | Prototype Implementation, Measured Results and Comparison | 36                                     |

| 2.6         | Conclusion                                                | 40                                     |

| 3.1   | Introduction                                                            |

|-------|-------------------------------------------------------------------------|

| 3.2   | Numerical PDE Solver by Finite Difference Method and Jacob<br>Iteration |

| 3.3   | Algorithm Formulation For Faster Convergence and Lower Pre-             |

|       | cision                                                                  |

|       | 3.3.1 Hybrid Layer Update Method                                        |

|       | 3.3.2 Multigrid and Low-Precision Complete Residual Ap-                 |

|       | proach                                                                  |

|       | 3.3.3 Evaluation of Algorithm Improvement                               |

| 3.4   | Mapping of PDE Solver on MAC SRAM                                       |

|       | 3.4.1 Direct Mapping                                                    |

|       | 3.4.2 Rotation Mapping                                                  |

| 3.5   | Prototype Architecture                                                  |

| 3.6   | Group Read and Word Line Pulse Generation                               |

| 3.7   | Bit Line Readout                                                        |

| 3.8   | Results and Comparison                                                  |

| 3.9   | Conclusion                                                              |

|       |                                                                         |

| Concl | lusion                                                                  |

# LIST OF FIGURES

# Figure

| 1.1 | Von Neumann architecture for computer processors. $[1]$                                                                                                                                                | 2  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Top-1 accuracy vs operations, parameters for state-of-the-art DNN architectures. The size of each blob is proportional to number of parameters, as indicated in the legend at bottom right corner. [2] | 2  |

| 1.3 | Roofline performance model for CPU, GPU, and TPU. [3] $\ldots$ .                                                                                                                                       | 5  |

| 1.4 | Neurocube architecture. [4]                                                                                                                                                                            | 6  |

| 1.5 | Deep in-memory computing architecture. $[5]$                                                                                                                                                           | 7  |

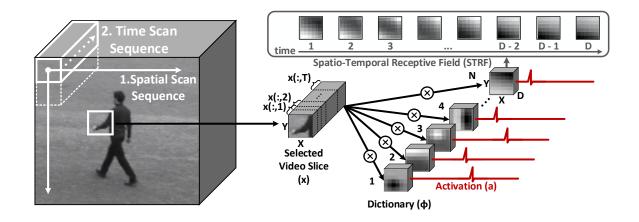

| 2.1 | Illustration of video inference processing                                                                                                                                                             | 15 |

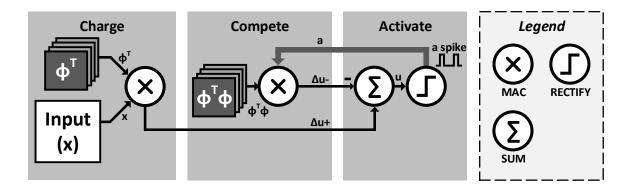

| 2.2 | Baseline implementation of video inference                                                                                                                                                             | 17 |

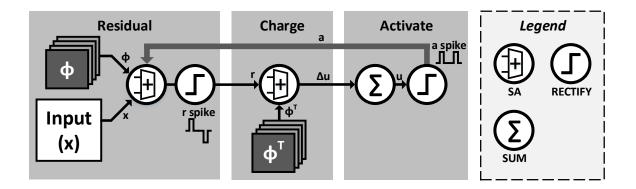

| 2.3 | Sparse, all-spiking implementation of video inference                                                                                                                                                  | 17 |

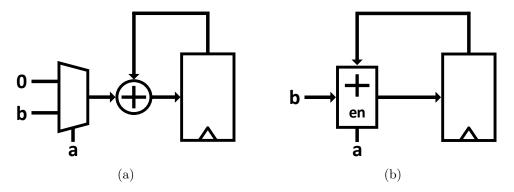

| 2.4 | SA implementations: (a) select-add, (b) skip-add. $\ldots$                                                                                                                                             | 17 |

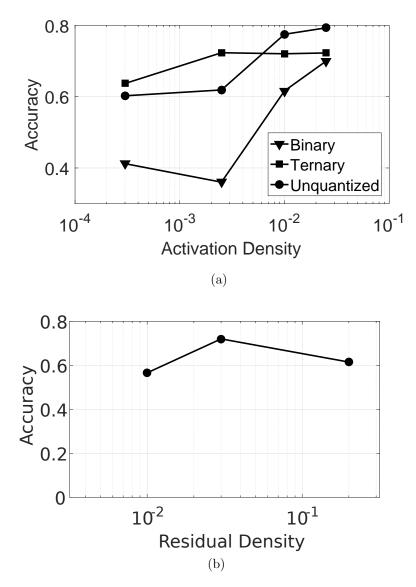

| 2.5 | Effect of a) activation density and b) residual density on classification accuracy.                                                                                                                    | 22 |

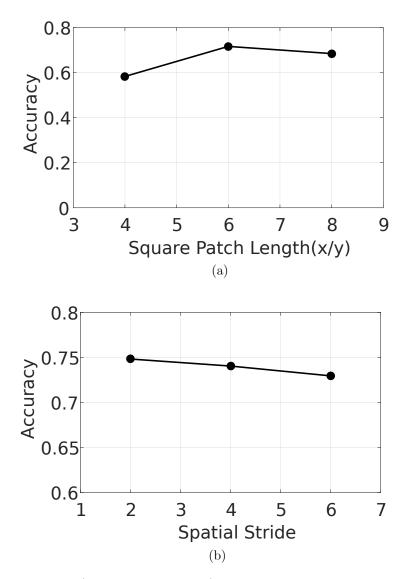

| 2.6 | Effect of a) patch size and b) $6 \times 6$ patch spatial stride on classification accuracy.                                                                                                           | 23 |

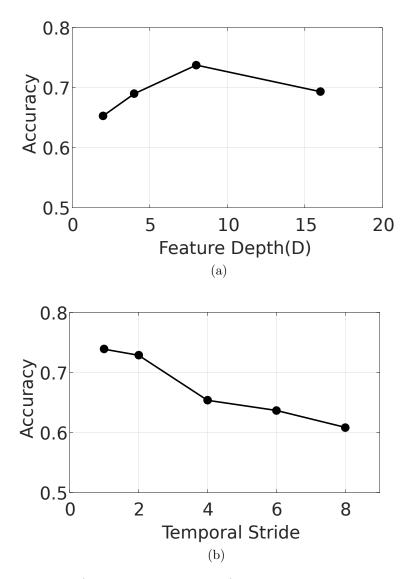

| 2.7 | Effect of a) feature depth and b) time overlap on classification accuracy.                                                                                                                             | 24 |

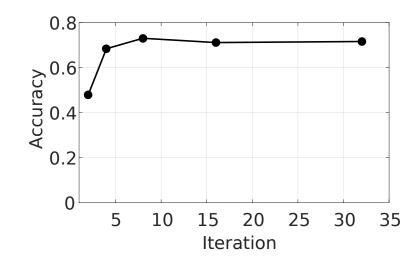

| 2.8 | Effect of number of iterations on classification accuracy                                                                                                                                              | 25 |

| 2.9 | Effect of number of neurons on classification accuracy                                                                                                                                                 | 25 |

| 2.10 | Architectural sketch of 3-layer implementation of video inference pro-<br>cessor                                                                                                                                                                        | 26 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.11 | (a) Distribution of deltas between frames of STRFs; (b) non-uniform quantization of deltas.                                                                                                                                                             | 27 |

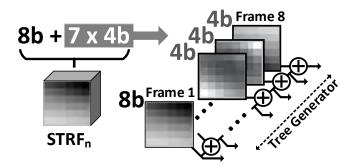

| 2.12 | a tree generator for decompressing delta-encoded STRF. $\ldots$ .                                                                                                                                                                                       | 28 |

| 2.13 | Visualization of residual compute                                                                                                                                                                                                                       | 29 |

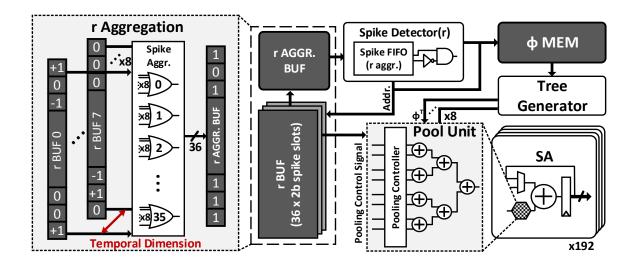

| 2.14 | Residual layer design                                                                                                                                                                                                                                   | 30 |

| 2.15 | Visualization of charge compute                                                                                                                                                                                                                         | 30 |

| 2.16 | Charge layer design                                                                                                                                                                                                                                     | 31 |

| 2.17 | Activate layer design                                                                                                                                                                                                                                   | 32 |

| 2.18 | Effect of nonzero activation limit on classification accuracy                                                                                                                                                                                           | 33 |

| 2.19 | Timing illustration.                                                                                                                                                                                                                                    | 34 |

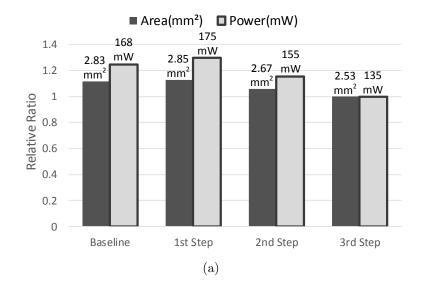

| 2.20 | (a) Area and power and (b) latency and energy after three design optimization steps: 1) sparse activation, 2) residual rectification, and 3) compressed activations.                                                                                    | 35 |

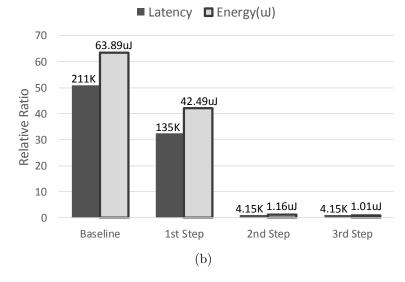

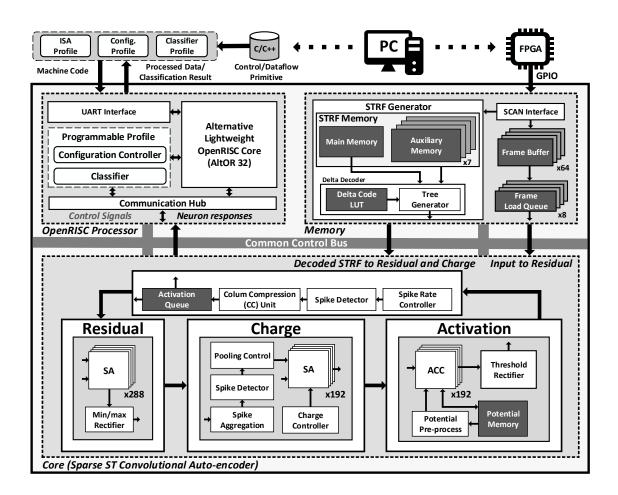

| 2.21 | System-level design of video inference processor.                                                                                                                                                                                                       | 37 |

| 2.22 | Microphotograph of the video inference SoC chip in 40nm CMOS. $% \mathcal{M}^{(1)}$ .                                                                                                                                                                   | 38 |

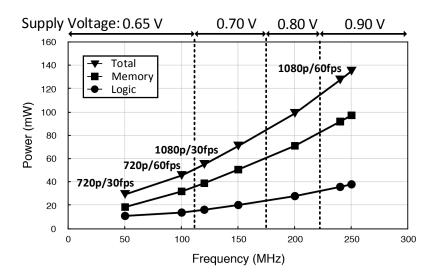

| 2.23 | Measured power and performance of the video inference SoC chip                                                                                                                                                                                          | 39 |

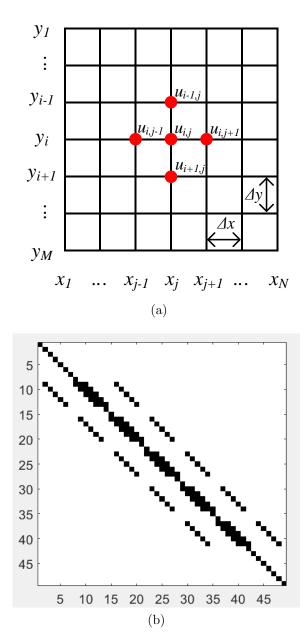

| 3.1  | (a) Illustration of a 2D finite difference grid; and (b) rendition of matrix $\mathbf{A}$ for a 7×7 grid                                                                                                                                                | 45 |

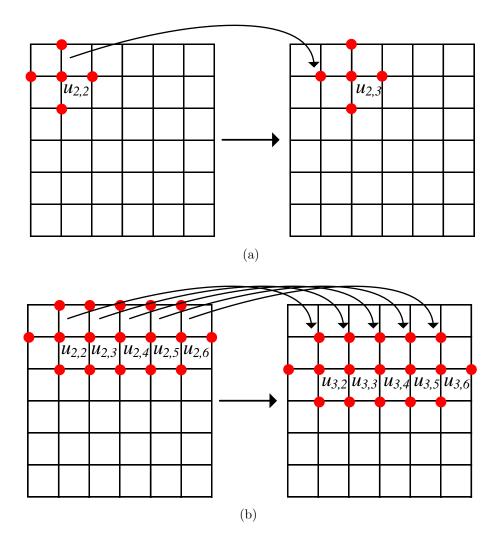

| 3.2  | PDE iterative methods with sequential updates: (a) Gauss-Seidel update; (b) hybrid layer update                                                                                                                                                         | 49 |

| 3.3  | Residual approaches: (a) standard residual approach applied to fine<br>grid only; (b) complete residual approach applied to both fine grid<br>and coarse grid; and (c) reformulated complete residual approach<br>without high-precision multiplication | 51 |

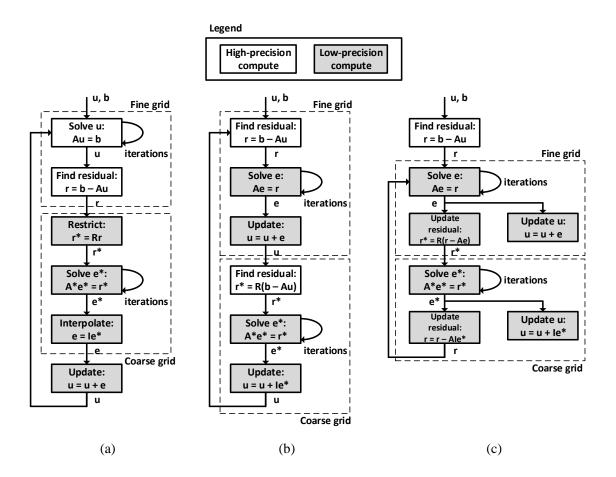

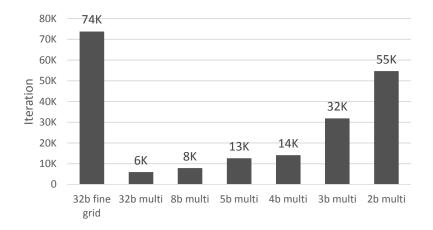

| 3.4  | Latency of solving 2D Poisson's equation to reach an error tolerance of $10^{-7}$ using a $127 \times 127$ single-grid and 32b, 8b, 5b, 4b, 3b, and 2b quantized multigrids (a $127 \times 127$ fine grid combined with a $64 \times 64$ coarse grid).                                 | 52 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

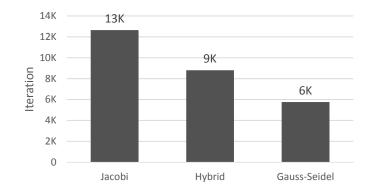

| 3.5  | Latency of solving 2D Poisson's equation with 5b quantization to reach an error tolerance of $10^{-7}$ using 5b multigrid and Jacobi, hybrid layer update, and Gauss-Seidel methods.                                                                                                   | 53 |

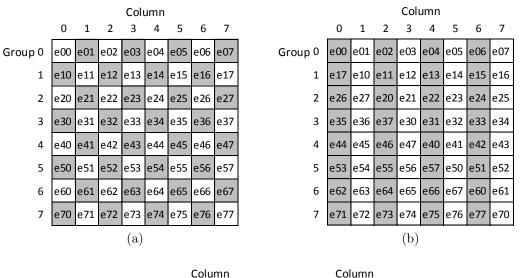

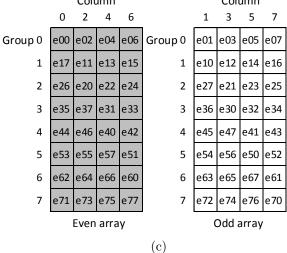

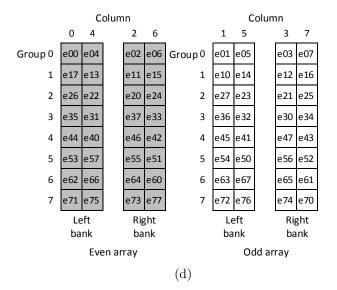

| 3.6  | PDE mapping on MAC SRAM: (a) direct mapping; (b) rotation mapping; (c) array splitting, and (d) bank splitting.                                                                                                                                                                        | 55 |

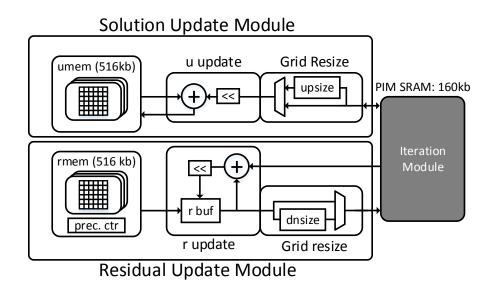

| 3.7  | Top-level architecture of PDE solver                                                                                                                                                                                                                                                   | 58 |

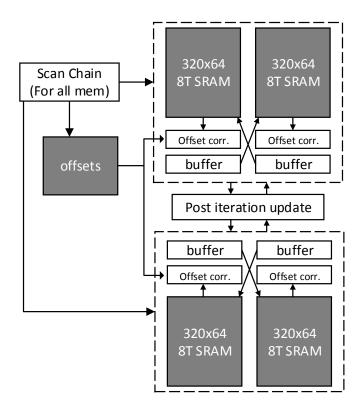

| 3.8  | Architectural sketch of PDE iteration module.                                                                                                                                                                                                                                          | 59 |

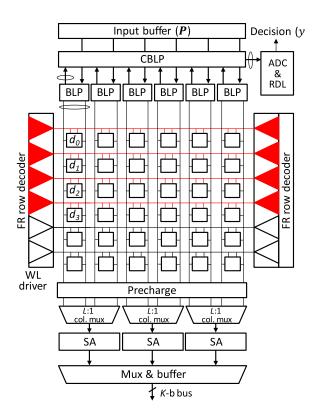

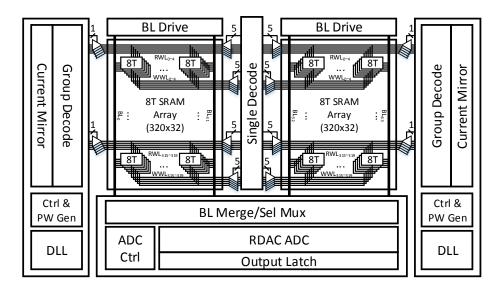

| 3.9  | Block diagram of MAC SRAM.                                                                                                                                                                                                                                                             | 59 |

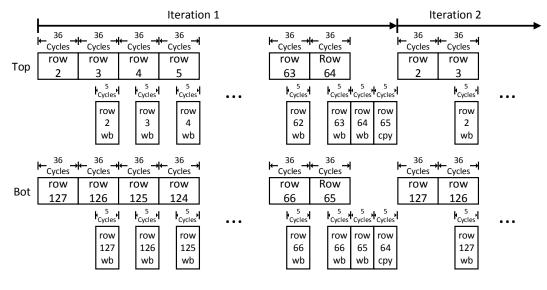

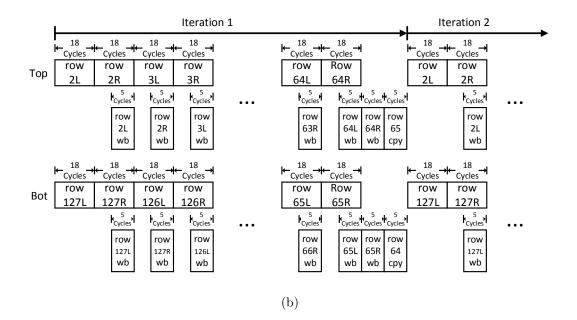

| 3.10 | Timing diagram of PDE iteration module in (a) the Jacobi method and (b) the hybrid method.                                                                                                                                                                                             | 61 |

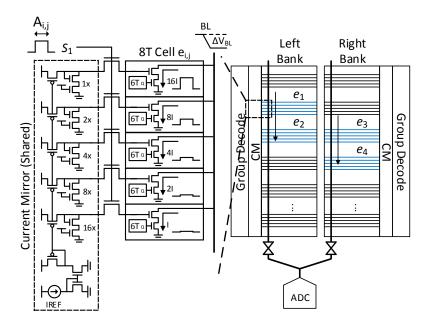

| 3.11 | Illustration of group read for MAC operations                                                                                                                                                                                                                                          | 62 |

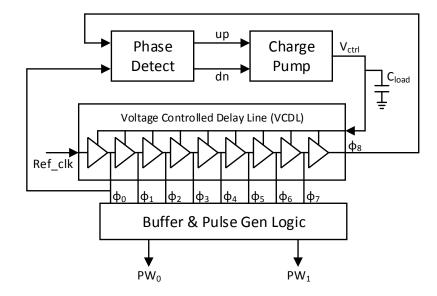

| 3.12 | DLL design for WL pulse generation.                                                                                                                                                                                                                                                    | 62 |

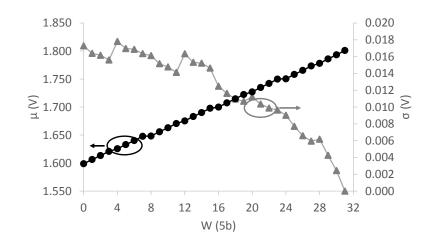

| 3.13 | BL voltage variation.                                                                                                                                                                                                                                                                  | 63 |

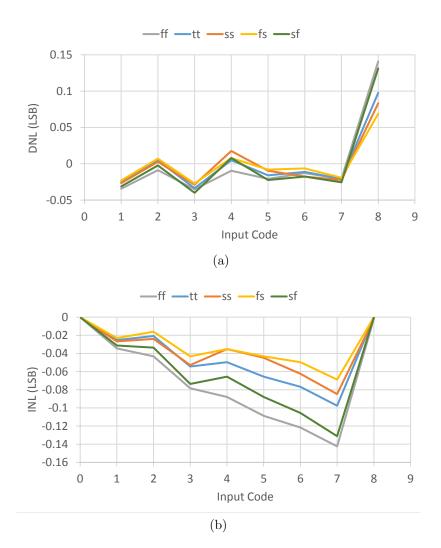

| 3.14 | Differential nonlinearity (DNL) and integral nonlinearity (INL) of WL pulses generated by DLL                                                                                                                                                                                          | 64 |

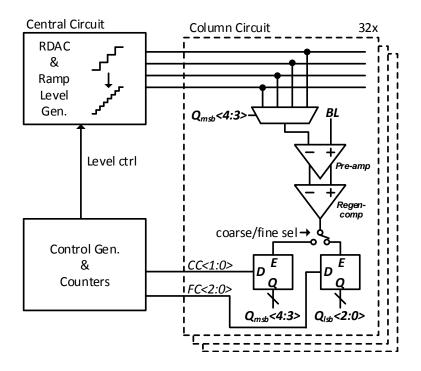

| 3.15 | 5-bit dual-ramp single-slope ADC design for BL readout                                                                                                                                                                                                                                 | 65 |

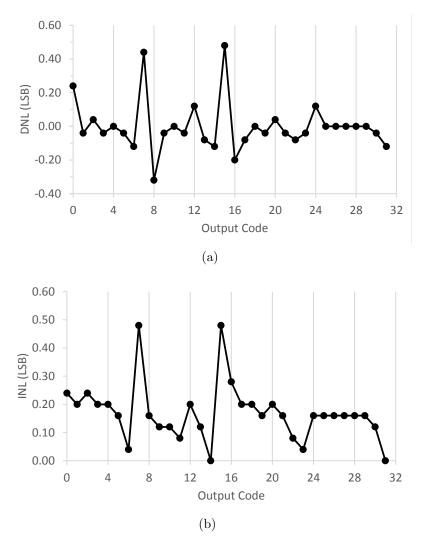

| 3.16 | ADC differential nonlinearity (DNL) and integral nonlinearity (INL).                                                                                                                                                                                                                   | 66 |

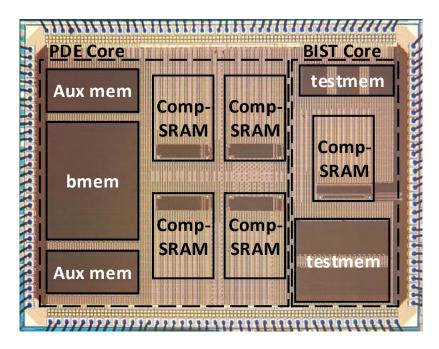

| 3.17 | Microphotograph of PDE solver test chip                                                                                                                                                                                                                                                | 67 |

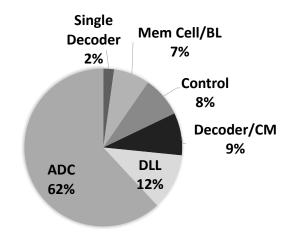

| 3.18 | Breakdown of MAC SRAM power                                                                                                                                                                                                                                                            | 68 |

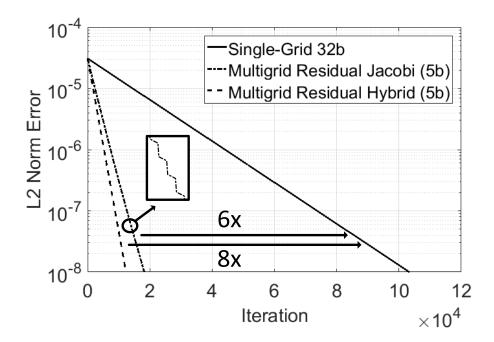

| 3.19 | Convergence of 5b multigrid (5b fine-grid: $127 \times 127$ , 5b coarse-grid: $64 \times 64$ ) using Jacobi and hybrid layer update iterations compared to single-grid baseline implementation (32b fine-grid: $127 \times 127$ ). Results are based on solving 2D Poisson's equation. | 68 |

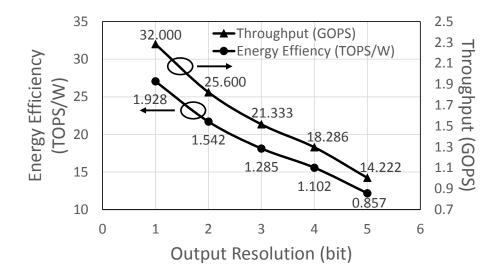

| 3.20 | Measured performance and energy.                                                                                                                                                                                                                                                       | 69 |

|      |                                                                                                                                                                                                                                                                                        |    |

# LIST OF TABLES

## <u>Table</u>

| 1.1 | Estimated energy cost for data access and floating-point computation<br>on 45nm technology. [6]      | 3  |

|-----|------------------------------------------------------------------------------------------------------|----|

| 2.1 | Baseline Implementation Complexity of One Iteration of Inference .                                   | 18 |

| 2.2 | Implementation Complexity of One Iteration of Inference Using Residual Approach         ual Approach | 18 |

| 2.3 | Implementation Complexity of One Iteration of Inference Using Sparse<br>and All-Spiking Approach     | 18 |

| 2.4 | Action Classification Results of KTH Human Action Database $\ . \ .$                                 | 38 |

| 2.5 | Comparison with Prior Work                                                                           | 40 |

| 3.1 | Comparison with State-of-the-Art SRAM-Based PIM (Unnormalized)                                       | 70 |

| 3.2 | Comparison with Prior PDE Accelerators (Unnormalized)                                                | 70 |

### ABSTRACT

Enabled by technology scaling, processing parallelism has been continuously increased to meet the demand of large-scale and data-intensive computations. However, the effort to increase processing parallelism is largely hindered by the von Neumann bottleneck. To achieve a higher performance, domain-specific computing has become the most promising direction. Domain-specific computing employs highly optimized datapaths, simplified control and efficient dataflow to enable the dense integration of processing elements with optimized memory access. Many domain-specific designs have demonstrated significantly better figure of merit than a general-purpose CPU or GPU, but the von Neumann bottleneck still limits the maximum achievable performance.

To reduce the data transfer cost, a closer integration between memory and computation is needed, which ultimately leads to the so-called in-memory computing approach. In-memory computing re-purposes memory cell array for multiply-accumulate operations and apply both bit-line and word-line parallelism to realize large matrix computation before memory readout, eliminating the von Neumann bottleneck entirely. However, in-memory computing is inherently analog compute, where limited precision and high sensitivity to noise pose major challenges.

This thesis work presents two approaches to address the von Neumann bottleneck: 1) reducing the amount of data that needs to be moved by sparsity and data compression; and 2) robust multi-bit in-memory compute design to extend the applicability of in-memory compute to a wider range of applications. With video input and 3D features, a video processor requires many times larger memory size and computation than a 2D image processor. In this work, I chose a video sequence inference processor to demonstrate sparsity-oriented optimizations using a quantized all-spiking network, where the sparsity can reach a high 90% level. By kernel compression and activation compression, memory size can be reduced further by 43% and 64%, respectively. High data sparsity and memory compression lead to two orders of magnitude of improvement in performance and energy. The design was demonstrated in a 2.53mm<sup>2</sup> 40nm CMOS chip for video sequence inference that achieved 1.70TOPS with a power dissipation of 135mW at 0.9V and 250MHz. The results show the effective use of sparsity and data compression to loosen the von Neumann bottleneck.

It is well known that in-memory computing is limited in operand and output precision, which restricts its applications to binary or low-precision applications. Through an algorithmic transformation using a residual approach, I demonstrate that it is possible to map a high-precision partial differential equation (PDE) solver to a lowprecision 5-bit in-memory computing. To support multi-bit computation, I adopt both width and level modulation of word-line pulses. To reduce the cost and improve the speed of analog-to-digital conversion, I employ a compact array of dual-ramp single-slope (DRSS) ADCs for bit-line readout. These ideas were demonstrated in a 1.87mm<sup>2</sup> 180nm test chip made of four  $320 \times 64$  multiply-accumulate (MAC) SRAMs, each supporting  $128 \times$  parallel  $5b \times 5b$  MACs with 32 5-bit output ADCs and consuming 16.6mW at 200MHz. The prototype was able to solve a  $127 \times 127$  PDE grid at 56.9 GOPS. This SRAM based in-memory compute provides over  $40 \times$  compute density than an equivalent ASIC, demonstrating that the von Neumann bottleneck can be removed for applications that require higher precisions.

This work shows the importance of algorithm-architecture-circuit co-design for uncovering opportunities to mitigate and remove the von Neumann bottleneck. The design techniques and approaches can be applicable to a wide array of applications for improving performance and efficiency.

### CHAPTER I

## Introduction

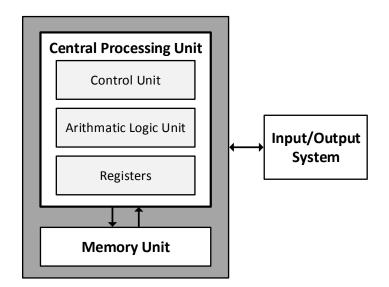

The vast majority of modern computer processors are designed based on the von Neumann architecture [7] as shown in Fig. 1.1 that roughly consists of four parts: a processing unit for arithmetic and logic operations, a control unit that steps through instructions, a memory that stores data and instructions, and input and output devices. The architecture has served us well in the era when semiconductor devices are relatively large, expensive and slow, and the datasets are small.

With the rapid scaling down of CMOS devices following Moore's law [8], CMOS devices have become exponentially smaller, cheaper, and faster. Processors can afford to have multiple or many processing cores [9]. Graphics processing units (GPU) and application-specific integrated circuits (ASIC) can provide hundreds or thousands of processing units on chip to boost performance [10,11]. Enabled by the rapid growth of processing capabilities, new classes of applications, such as computer vision [12], natural language processing [13], autonomous navigation [14], virtual reality [15] and augmented reality [16], crypto currency [17] and blockchain [18], have emerged. A commonality among all these emerging applications is that the datasets can be massive and the compute models are large and complex.

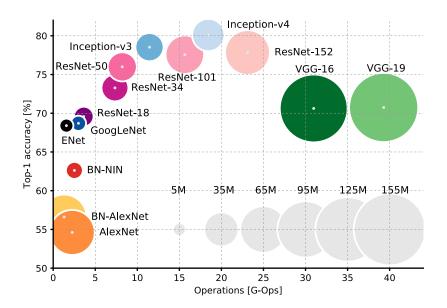

An example is shown in Fig. 1.2 for the state-of-the-art deep neural network (DNN) models [2] compiled by Canziani, et al. A state-of-the-art DNN model contains over

Figure 1.1: Von Neumann architecture for computer processors. [1]

Figure 1.2: Top-1 accuracy vs operations, parameters for state-of-the-art DNN architectures. The size of each blob is proportional to number of parameters, as indicated in the legend at bottom right corner. [2]

| FP Add  |                    | SRAM Cache (64 bit) |            |

|---------|--------------------|---------------------|------------|

| 16  bit | 0.4 pJ             | 8 KB                | 10 pJ      |

| 32 bit  | $0.9 \mathrm{ pJ}$ | 32 KB               | 20 pJ      |

| FP Mult |                    | 1 MB                | 100 pJ     |

| 16  bit | 1 pJ               |                     |            |

| 32 bit  | 4 pJ               | DRAM                | 1.3-2.6 nJ |

Table 1.1: Estimated energy cost for data access and floating-point computation on 45nm technology. [6]

100 million parameters, and requires 40 GOPs to process a relatively low-resolution image of  $224 \times 224 \times 3$  (3 channels).

One can argue that the current CMOS device technology can comfortably provide the level of parallelism needed for the growing list of emerging applications. For example, Nvidia's V100 GPU accelerator already boasts a 15 TFLOPS performance [19]. However, as Horowitz famously pointed out, the compute problem we are facing is no longer how parallel we can make the processing units, but how much it costs to supply the input data and take away the output data from the processing units [6].

Indeed, as Table 1.1 shows, in a 45nm CMOS technology, moving data from a relatively small-sized 8KB SRAM cache memory costs  $10 \times$  more in energy than a 16-bit floating-point multiplication. The energy cost escalates by another  $10 \times$  when moving data from a larger 1MB SRAM. If data have be moved from off-chip DRAM, we can expect to pay yet another  $10 \times$  energy cost. The lopsided energy breakdown shows that data movement, rather than parallel processing, is the determining factor in high-performance and efficient processor designs. This is known as the von Neumann bottleneck [20]. It is not surprising that the vast majority of the Nvidia V100 GPU's 300 W thermal design power is attributed to the memory interface [19].

#### **1.1** Related Work and Challenges

Architecture specialization for a domain of applications has been named as one promising way forward [21]. Domain-specific architectures are designed for special classes of applications. Compared to general-purpose processors that incur a high control overhead, a less efficient processing pipeline, and frequent load and store accesses, domain-specific architectures can be made much more efficient by simplifying the control, optimizing the data flow, and maximizing local data reuse.

Google's tensor processing unit (TPU) [3] is a prime example of a domain-specific processor that is tailored to DNN workloads. The core of the TPU is a  $256 \times 256$  8-bit vector-matrix product engine. The 64k multiply-accumulate (MAC) units are wired up in a systolic array. The partial results are passed between one MAC unit to its nearest neighbor, allowing the final results to be accumulated along the compute path and avoiding expensive SRAM access. The massive parallelism, together with an optimized data flow, contribute to the TPU's record performance and efficiency: using only half the silicon area of the Intel Haswell CPU or Nvidia Kepler K80 GPU, and half the power, TPU provides  $25 \times$  more MAC operations [22] than both.

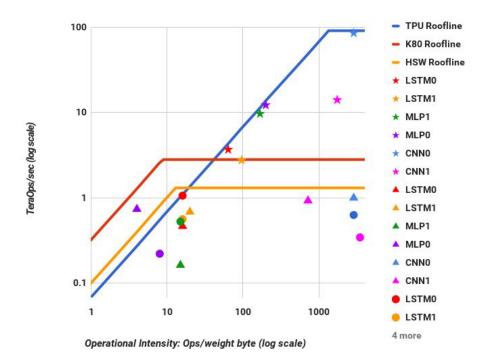

Domain specialization allows the TPU to score a much better figure of merit than a general-purpose CPU and GPU. However, TPU is still hurt by the von Neumann bottleneck as evidenced in the roofline plot shown in Fig. 1.3. A roofline curve shows the performance of a processor as the data reuse is increased. A roofline curve has two distinct parts, a slanted part and a flat part. The flat part defines the maximum achievable performance of the processor (the performance roof); and in the slanted part, the performance of the processor is capped by memory bandwidth. As data reuse is increased, the same memory bandwidth can support a higher performance. Fig. 1.3 clearly shows that the TPU raised the performance roof compared to a CPU and a GPU, but it also features a long slanted region. Many workloads, such as long short-term memory (LSTM) and multilayer perceptron (MLP), are still limited by

#### Log-Log Scale

Figure 1.3: Roofline performance model for CPU, GPU, and TPU. [3]

memory bandwidth.

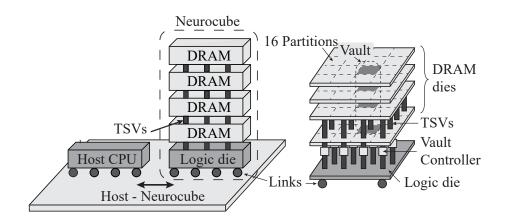

To alleviate or resolve the von Neumann bottleneck, near-memory compute and in-memory compute have been proposed. In near-memory compute, processing is moved very close to memory to reduce the data movement cost [23]. 3D integration technology is a key enabler of near-memory compute. High bandwidth memory (HBM) [24] and hybrid memory cube (HMC) [25] are schemes that stack layers of DRAM on top of a logic layer. The layers are interconnected by a large number of through-silicon vias (TSVs). Making use of the third dimension increases the memory capacity, and TSVs provide short-distance and dense connectivity to memory.

Based on HMC, two near-memory designs, Neurocube [4], shown in Fig. 1.4, and TETRIS [26], have been demonstrated. Both designs place processing units on the bottom logic layer, which access layers of DRAMs directly on top. Benefiting from 3D integration and the substantially reduced wiring distance and increased bandwidth,

Figure 1.4: Neurocube architecture. [4]

Neurocube demonstrated  $4 \times$  improvement in power efficiency compared to a GPU [4].

Note that near-memory compute still follows the von Neumann architecture with a much relaxed memory access bottleneck. In comparison, in-memory compute, illustrated in Fig. 1.5, relies on memory for both storage and compute. Compute is performed inside memory cells, without moving data out of memory. As a result, in-memory compute can offer a higher efficiency than near-memory compute. Inmemory compute also activates multiple or all the word lines of a memory array in parallel to unleash the array's intrinsic high parallelism.

In-memory compute has been demonstrated in a number of silicon prototypes. Early work used SRAM for in-memory compute [27]. Lately, prototypes have been designed based on resistive RAM (RRAM) [28]. Comparing RRAM to SRAM, RRAM offers denser and nonvolatile storage, and it is the more attractive option for inmemory compute. However, SRAM is made of CMOS devices, which are more mature and can be readily demonstrated. SRAM-based in-memory compute accelerators, such as Conv-RAM [29], demonstrated more than  $16 \times$  improvement in energy efficiency compared to a conventional digital accelerator.

In-memory compute is no longer limited by the von Neumann bottleneck. However, in-memory compute is fundamentally a form of analog compute that relies on

Figure 1.5: Deep in-memory computing architecture. [5]

modulating analog voltages and summing analog currents. As such, in-memory compute is less reliable than conventional digital compute, and it can be easily affected by noise, variations and offsets. Although in-memory compute can be made highly parallel, it is difficult to obtain high-precision results. Early efforts have relied on converting the results to 1 bit [30]. With proper circuit techniques, up to 7 bits can be obtained [29], but it requires costly analog-to-digital conversion. To sum up, limited precision and high sensitivity to noise and variation are the key challenges of in-memory compute.

### **1.2** Thesis Contribution

This thesis work provides new solutions targeting high-performance and energyefficient accelerator design for data-intensive applications. As the datasets are large, the von Neumann bottleneck presents a major challenge. The proposed solutions are based on two primary approaches: 1) reducing the amount of data that need to be moved by exploiting sparsity and data compression; and 2) robust multi-bit in-memory compute design to extend the applicability of in-memory compute to a wider range of applications.

#### 1.2.1 Data Sparsity

Sparsity is often inherent in large datasets. For example, sensory data can be highly sparse in the sense that the amount of meaningful information is low relative to the large number of raw data points. Even if the raw data appear dense, through a signal processing technique called compressed sensing [31], the raw data can be projected to a new space to make the data appear sparse. Popular compression techniques make use of this principle. For example, audio and image compression often employs discrete cosine transform (DCT) that expresses a finite sequence of data points in terms of a sum of cosine functions at different frequencies [32]. After applying DCT, audio and image data become sparse and can be efficiently compressed.

The brain does an amazing job in compressing input sensory data. The sensory inputs, e.g., images, videos, audio, speech, are coded in highly sparse neuron spikes for cognitive processing [33]. It is hypothesized that the brain employs an efficient coding scheme that maximizes both coding accuracy and sparsity [34], akin to compressed sensing. The high sparsity could be a key factor behind the ultra-high efficiency of the brain.

The data sparsity inspires the design of better accelerators. Sparsity implies that most of the data are zeros, leading to reduced workload and higher performance. More importantly, sparsity results in a lower memory traffic, which alleviates the von Neumann bottleneck.

In this work, a video sequence inference processor design is chosen to demonstrate data-sparsity-optimized design techniques. A video sequence inference processor takes 2D + time video inputs and extracts spatio-temporal features [35]. The extracted spatio-temporal features are used to infer the activities, or actions that are present in the input video. The video sequence inference task is highly challenging because the data size is significantly larger than 2D image processing that is commonly used in benchmarking machine learning hardware. However, video inputs are highly sparse, possibly more sparse than 2D images. By applying a neuro-inspired compressed sensing algorithm, the video inputs are efficiently coded in the feature domain. The data sparsity can reach a high 90% level, offering an opportunity to obtain both high performance and high efficiency.

Chapter 2 will discuss the design of a sparse, all-spiking accelerator for the implementation of a video sequence inference accelerator. This work was a joint effort with my group member Ching-En Lee. Sparsity is inherently high in videos; and sparsity can be further increased using a residual approach and a rectification technique. A residual approach operates on the incremental changes in each iteration, rather than the raw data directly. It is reasonable to expect that the residuals are sparser than the raw data. Rectification is an approximate compute technique that quantizes intermediate data to a few finite levels, allowing the intermediate data to be sparsified.

Backed by the high data sparsity and simple data compression techniques, the performance and energy of the accelerator can be improved by nearly two orders of magnitude. The substantial improvements are attributed to the effective use of data sparsity that loosens the von Neumann bottleneck.

#### 1.2.2 Multi-Bit In-Memory Compute Accelerator

A key limitation of in-memory compute is the limited precision. Many prior designs resorted to storing 1-bit operands in memory or converting outputs to 1 bit, so as to match a digital memory with binary sense amplifiers and avoid costly ADCs. The low precision of in-memory compute limits its applicability to simple or toy examples, e.g., binary neural networks [36], true or false classifications [37].

A partial differential equation (PDE) solver is chosen to demonstrate the multi-bit in-memory compute technique. A PDE solver is widely used in scientific applications. A PDE solver is commonly implemented using Jacobi method [38]. The equation and the solution space are first discretized to a grid, and the solutions are found through iterations of matrix-vector products.

PDE solver is a big-data workload: discretization results in a large number of data points. If an accurate solution is required, which is often the case, a fine grid of fine step size and a floating-point quantization are used, producing even more data. It can take tens of thousands of iterations to converge, requiring a large amount of data to be passed back and forth between memory and processing units. The von Neumann bottleneck becomes the limiter. Although in-memory compute can cut the data movement cost, it appears to be a mismatch for a PDE solver application due to the PDE's high precision requirement.

Chapter 3 will discuss how a residual approach is applied to reduce the precision requirement of a PDE solver, allowing a high-precision PDE solver can be mapped to a low-precision in-memory compute. The key is a residual technique that operates on the incremental differences of data between iterations rather than the raw data. Although the raw data can be in high precision, the incremental differences of the data between iterations are much smaller in magnitude and can be represented using a low precision. A drawback of the approach is that the convergence speed worsens with reduced precision. However, there exists an optimal point in the trade-off between ]hlprecision and convergence speed. The optimal point for the PDE solver is near 4 to 5 bits, where the increase in convergence latency is still manageable.

Even after the PDE solver computation is quantized to 5 bits, it is still not feasible to map the computation to an existing in-memory compute accelerator. Some in-memory compute accelerators support only 1-bit multiplicands [27, 29, 30], 1-bit multipliers [30, 39], or 1-bit outputs [27, 30, 39], which are not sufficient for a PDE solver. None of the existing in-memory compute accelerators provides enough number of multi-bit ADCs to support the bandwidth needed for iterative solution updates in a PDE solver.

This work presents a number of new circuit approaches to enable a practical multibit in-memory compute. First, both width and level modulation are used in word line modulation to allow the multiplication of multi-bit operands. A delayed-locked loop (DLL) is used to generate well-control word line pulses, while offering tolerance against process voltage temperature (PVT) variations. Second, a dual-ramp singleslope (DRSS) ADC is used to perform the analog-to-digital conversion of bit line outputs. A DRSS ADC shortens the conversion time and it can be constructed using a shared centralized reference generation and compact comparator circuitry per column. The circuit techniques are demonstrated in an SRAM-based prototype. Over  $40 \times$  compute density can be achieved compared to a conventional digital ASIC design.

A part of this work is contributed by my group member, Jacob Botimer. He has contributed to the design of the MAC SRAM module, and the implementation of the PDE solver chip.

This thesis work demonstrates that by exploiting sparsity, compression and multibit in-memory computing, it is possible to drastically reduce and eliminate data movement and overcome the von Neumann bottleneck. This work also points out the need to perform extensive analyses of the algorithms and models to uncover algorithmarchitecture-circuits co-design opportunities. The results of this work have been demonstrated through silicon prototypes and verified by experimental measurements. The approaches and techniques can be applicable to a wide array of high-performance and efficient designs of future data-intensive accelerators.

### CHAPTER II

## Design of Video Sequence Inference Processor

### 2.1 Introduction

Object detection in videos is employed in a wide range of applications from smart user interface to surveillance and autonomous navigation. Due to the demanding resolution and frame rate of videos, real-time object detection has been a challenge. Designing real-time object detection on embedded platforms is especially difficult due to the limited energy source available on embedded platforms.

State-of-the-art object detection accelerators [40–44] have been designed based on SIFT [45], SURF [46] and DPM [47] algorithms. These popular algorithms extract 2D features from images, and compare them with features stored in a database [45,46] or perform classifications [47] on the features to recognize objects. The accelerators target real-time videos, but the base operations are on 2D images.

Video sequence classification, or action classification, operates on sequences of video frames to extract activity or action information from videos. Video sequence classification relies on extracting spatio-temporal features and performing classification on the spatio-temporal features, thus it is expected to demand more computation than the 2D processing of videos.

Classic video sequence classification relies on engineered features, such as cuboid [48], space-time Harris [49], and Hessian [50]. Each feature selection is tailored to a

specific task, but may not deliver the best performance for every task. It is desirable to use automatically learned features that are most suitable for the data. An auto-encoder is one such approach that automatically learns sparse, shift-invariant spatio-temporal features [51]. Sparse coding is a similar approach that adapts an overcomplete dictionary of space-time functions (features) to represent time-varying natural images with high sparsity [35]. The space-time features resemble the motion-selective receptive fields (RF) of simple cells in the mammalian visual cortex, suggesting that the approach may be at work in the visual cortex [35].

In this work, we adopt a sparse coding approach called locally competitive algorithm (LCA) [52]. LCA is formulated as a compressed sensing method. When applied to videos, LCA learns the spatio-temporal RFs (STRFs) and encodes inputs using a sparse set of STRFs. As such, LCA is highly effective in reducing the input size, allowing the most salient STRFs to be extracted for classification.

LCA can be mapped to a spiking recurrent neural network (RNN) [53, 54]. Implemented using iterative forward projection and backward reconstruction, a video sequence inference processor based on spiking RNN can extract spatio-temporal RFs (STRFs), i.e., spatio-temporal features, from videos. The extracted STRFs can in turn enable action classification [55] and motion tracking [56] tasks.

Due to the large video data size, spatio-temporal, and iterative processing, the computational requirement of the video sequence inference RNN is high. Even for a relatively small-scale processing of a  $6 \times 6 \times 64$  video slice using 192 STRFs costs 200M multiply-accumulates (MACs). To enable a practical implementation, we adopt a residual formulation of the RNN [57] and apply an algorithm transformation by rectifying the residuals after each inference iteration to ternary spikes without costing classification accuracy. After the transformation, the intermediate data through the compute stages, i.e., activations and residuals, become spikes with a sparsity level well above 90%. The transformed algorithm leads to a sparse, all-spiking video inference

processor design that reduces the computational complexity from 200M MACs to 4M select-accumulates per iteration, making it possible to support video processing in real-time at a reasonable power consumption. To reduce the large on-chip storage, we apply non-uniform delta encoding on the highly redundant STRFs and compressed column storage (CCS) on the highly sparse activations to reduce their memory size by 43% and 64%, respectively.

The design is demonstrated in a 2.53mm<sup>2</sup> 40nm inference SoC that integrates a video sequence inference core and an OpenRISC core. The chip is measured to achieve 1.70TOPS at 0.9V and 250MHz, dissipating 135mW at room temperature. With the video sequence inference core extracting the activation response of STRFs, a soft-max classifier programmed on the OpenRISC core achieves a 76.7% classification accuracy on the 6-class KTH Human Action Dataset [58].

This work was a joint effort with my group member Ching-En Lee. My key contributions to this work were the algorithm analysis, architectural sparsity evaluation and the back-end layout and integration of the SoC.

The rest of the paper is organized as follows. Section II provides an overview of the baseline inference algorithm, and Section III shows how the algorithm is transformed to a sparse, all-spiking formulation to reduce its implementation cost. Section IV presents the design details of each compute layer and memory, and quantifies the performance and energy gain. Section V shows the chip implementation and measured results, and Section VI concludes the work.

### 2.2 Video Inference Algorithm Formulation

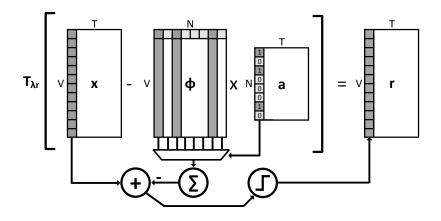

In this work, we adopt the LCA algorithm [52] to perform compressed sensing of videos. LCA can be mapped to a recurrent network of spiking leaky integrateand-fire neurons, where a neuron's potential increases due to input excitation, and decreases due to inhibition by neighboring neurons. The LCA algorithm is described

Figure 2.1: Illustration of video inference processing.

by equation (2.1).

$$\Delta \mathbf{u} = \eta \left[ \mathbf{\Phi}^T \mathbf{x} - \left( \mathbf{\Phi}^T \mathbf{\Phi} - \mathbf{I} \right) \mathbf{a} - \mathbf{u} \right]$$

(2.1)

$$\mathbf{a} = T_{\lambda}(\mathbf{u}),$$

where **u** is the neuron potential,  $\Delta \mathbf{u}$  is the potential update;  $\eta$  is the update step size;  $\boldsymbol{\Phi}$  is the receptive fields (RF) of neurons, also known as the dictionary; **x** is the input; **a** is the neuron activation; and **I** is the identity matrix.  $T_{\lambda}()$  is a binary threshold function and it outputs 1 if its input exceeds  $\lambda$ , or 0 otherwise. Dictionary  $\boldsymbol{\Phi}$  and threshold  $\lambda$  are trained by stochastic gradient descent, which aims to maximize encoding accuracy and the sparsity of neuron activations.

In performing inference on video inputs, an input is divided to 3D segments for processing. In (2.1),  $\mathbf{x}$  is a time series of T number of  $X \times Y \times D$  consecutive and overlapping video segments, as shown in Fig. 2.1. The dictionary  $\mathbf{\Phi}$  is a collection of N RFs, and each RF is a  $X \times Y \times D$  spatio-temporal feature, known as STRF.  $\mathbf{u}$ ,  $\Delta \mathbf{u}$ , and  $\mathbf{a}$  are collections of N neurons' potentials, potential updates, and activations, respectively, over T time steps. Mathematically,  $\mathbf{x}$  is a  $V \times T$  matrix, where V = *XYD*;  $\Phi$  is a  $V \times N$  matrix;  $\mathbf{u}$ ,  $\Delta \mathbf{u}$  and  $\mathbf{a}$  are  $N \times T$  matrices.

The inference described by equation (2.1) consists of four functional steps:

- 1. Charge: Input  $\mathbf{x}$  is projected to the feature space as described by  $\mathbf{\Phi}^T \mathbf{x}$ . The projection can be understood as encoding the input  $\mathbf{x}$  in STRFs, i.e., extracting STRFs from the input. The projection increases, or charges, the neuron potential.

- 2. Compete: To maintain sparse activation, active neurons suppress other neurons. The inhibition weight between a pair of neurons is computed by correlating their STRFs, i.e.,  $\Phi^T \Phi$ . Self-inhibition is removed by subtracting **I**. The closer the two neurons' STRFs, the stronger the inhibition between the two neurons. Neuron activations trigger inhibitions as described by  $(\Phi^T \Phi - \mathbf{I}) \mathbf{a}$ .

- 3. *Leak*: Neuron potential decreases over time, and the leakage is proportional to the potential.

- 4. Activate: Neuron potential is thresholded to generate binary spikes.

The four steps above constitute one iteration of inference. Given an input  $\mathbf{x}$ , the inference is done by iterating the four steps until convergence. It is common to use a fixed number of iteration I. The baseline implementation is outlined in Fig. 2.2, where the leak step is omitted for simplicity.

The implementation complexity of one iteration of inference is analyzed and the results are listed in Table 2.1. The dictionary storage requires VN entries. The inhibitory weights are computed by  $\mathbf{\Phi}^T \mathbf{\Phi} - \mathbf{I}$ , requiring  $N^2 V$  MACs. The  $N^2$  inhibitory weights can be computed once and stored in memory.

In every iteration of inference, the charge step requires NVT MACs. Because the two inputs  $\mathbf{\Phi}^T$  and  $\mathbf{x}$  to the charge step do not change between iterations, the charge is computed only once per inference regardless of the number of iterations.

Figure 2.2: Baseline implementation of video inference.

Figure 2.3: Sparse, all-spiking implementation of video inference.

Figure 2.4: SA implementations: (a) select-add, (b) skip-add.

| Function                  | Storage ( $\#$ weights) | Compute (# MACs) |  |

|---------------------------|-------------------------|------------------|--|

| Dictionary storage        | VN                      | -                |  |

| Inhibitory weight storage | $N^2$                   | -                |  |

| Charge step               | -                       | NVT              |  |

| Compete step              | -                       | $N^2TI$          |  |

| Total                     | $VN + N^2$              | $NVT + N^2TI$    |  |

Table 2.1: Baseline Implementation Complexity of One Iteration of Inference

Table 2.2: Implementation Complexity of One Iteration of Inference Using Residual Approach

| Function           | Storage ( $\#$ weights) | Compute (# MACs) |

|--------------------|-------------------------|------------------|

| Dictionary storage | VN                      | -                |

| Residual step      | -                       | NVTI             |

| Charge step        | -                       | NVTI             |

| Total              | VN                      | 2NVTI            |

Table 2.3: Implementation Complexity of One Iteration of Inference Using Sparse and All-Spiking Approach

| Function           | Storage ( $\#$ weights) | Compute ( $\#$ SAs) |

|--------------------|-------------------------|---------------------|

| Dictionary storage | VN                      | -                   |

| Residual step      | -                       | $NVTS_aI$           |

| Charge step        | -                       | $NVTS_rI$           |

| Total              | VN                      | $NVT(S_a + S_r)I$   |

The compete step is driven by neuron activations, requiring  $N^2T$  MACs per iteration for I iterations.

Typically the number of neurons (N) ranges from hundreds and more for practical applications, and video inference can be particularly challenging due to its large dimensionality and real-time processing requirement. A silicon implementation requires a large area and power.

## 2.3 Sparse and All-Spiking Inference Formulation

Video data is large, but it also contains high redundancy, especially from frame to frame. The redundancy offers opportunities for significant complexity reduction in storage and compute. The sparse coding algorithm also lends itself to an efficient implementation by exploiting its inherent sparsity.

We formulate the algorithm such that all steps operate on spiking inputs. As a result, expensive MACs are replaced by efficient select-accumulates (SAs); and operations are skipped if no spikes are present.

#### 2.3.1 Rectification and Sparsification

The LCA equation can be reformulated by factoring the term  $\Phi^T$  in (2.1):

$$\Delta \mathbf{u} = \eta \left[ \mathbf{\Phi}^T \left( \mathbf{x} - \mathbf{\Phi} \mathbf{a} \right) + \mathbf{a} - \mathbf{u} \right]$$

(2.2)

$$\mathbf{a} = T_{\lambda}(\mathbf{u}).$$

The reformulated inference, first proposed by [57], can be interpreted as having four steps: residual, charge, leak and activate. The leak and activate steps are identical to the original formulation. The residual and charge steps are described below.

- 1. Residual: The input  $\mathbf{x}$  is reconstructed,  $\hat{\mathbf{x}} = \mathbf{\Phi} \mathbf{a}$ . The reconstruction is subtracted from the input to obtain the residual  $\mathbf{r} = \mathbf{x} - \hat{\mathbf{x}}$ .

- 2. Charge: The residual is projected to the feature space,  $\mathbf{c} = \mathbf{\Phi}^T \mathbf{r}$ .

The residual form removes the storage of inhibitory weights and replaces it by computing the weights on the fly. As a result, the storage required is smaller, but the compute complexity poses a challenge, as shown in Table 2.2. To reduce the complexity, we propose to quantize the residuals. If the residuals can be quantized to binary spikes (1, -1), the computational complexity of the charge layer can be significantly simplified. However, as Fig. 2.5(a) shows, the binary quantization has a large impact on the classification accuracy when the activation density is low. With 0 being the binary threshold, small noise values near 0 are amplified, preventing convergence and degrading accuracy.

To fix this problem, we propose a min/max rectification to the residuals to quantize the residuals to ternary spikes. The residual rectification is done by applying thresholds of  $\lambda_r$  and  $-\lambda_r$  to quantize the residuals to 1 (above  $\lambda_r$ ), 0 (between  $-\lambda_r$ and  $\lambda_r$ ), and -1 (below  $-\lambda_r$ ). With appropriate threshold choices, the ternary quantization outperforms binary quantization by a large margin and can even match the unquantized accuracy, as shown in Fig. 2.5(a). The updated equation is given in (2.3), where  $T_{\lambda_r}$  is the min/max rectification function.

$$\Delta \mathbf{u} = \eta \left[ \mathbf{\Phi}^T T_{\lambda_r} \left( \mathbf{x} - \mathbf{\Phi} \mathbf{a} \right) + \mathbf{a} - \mathbf{u} \right]$$

(2.3)

$$\mathbf{a} = T_{\lambda}(\mathbf{u}).$$

A key advantage of quantizing the residuals to binary or ternary spikes is that the multiplication by these quantized values and accumulating the partial sums no longer requires a MAC. Instead, a simpler SA can be used. Suppose a is binary (0 or 1), multiplying a by b followed by accumulation can be done using an SA that is implemented as in Fig. 2.4(a), where a is used as the select input in the multiplexer to choose whether 0 (if a is 0) or b (if a is 1) is accumulated by the adder. The accumulated sum is saved in a register. Alternatively, SA can be implemented using a skip-add shown in Fig. 2.4(b), where a is used as the enable input to the adder to decide whether to accumulate b (if a is 1) or not (if a is 0). Although the example was shown for the binary spike case, the implementation can be easily modified to support ternary spikes.

Similar to the residual rectification, neuron activation is obtained by rectifying neuron potentials to produce sparse, binary spikes. Binary spikes allow the reconstruction in the residual step to be implemented using SAs, presenting another opportunity for significant complexity and power reduction.

Taking advantage of both residual rectification and neuron activation, the sparse, all-spiking approach can be implemented as shown in Fig. 2.3. It features a lower complexity compared to the conventional residual approach as summarized in Table 2.3, where  $S_a$  and  $S_r$  refer to the density, or fraction of nonzero entries, in neuron activations and the residuals, respectively. The sparser the inputs (i.e., the lower density), the less the amount of effectual workload. However, sparsifying the inputs (activations or residuals) can degrade the classification accuracy. The effects are illustrated in Fig. 2.5. The activation density  $S_a = 1\%$  and residual density  $S_r = 3\%$ are nearly optimal for the KTH Human Action Dataset [58]. Below or above the optimal density results in under- or over-representation of the input, and degradation in classification accuracy.

#### 2.3.2 Design Specification and Parameter Settings

We present a prototype video inference processor to demonstrate the sparse, allspiking LCA approach. The prototype design, including the model and parameters, is based on the KTH dataset [58]. The inference processor takes video inputs in  $6 \times 6 \times 64$  slices, and divides into 57  $6 \times 6 \times 8$  (T = 57,  $V = 6 \times 6 \times 8 = 288$ ) consecutive and overlapping segments for processing.

The optimal X-Y patch size is determined by the size of features for a dataset. For KTH dataset,  $6 \times 6$  patch size provides the best accuracy as shown in Fig. 2.6(a). More spatial overlap (smaller spatial stride) produces better results as shown in Fig. 2.6(b).

Figure 2.5: Effect of a) activation density and b) residual density on classification accuracy.

Figure 2.6: Effect of a) patch size and b)  $6{\times}6$  patch spatial stride on classification accuracy.

Figure 2.7: Effect of a) feature depth and b) time overlap on classification accuracy.

However, in the prototype design, we chose no overlap to reduce the processing complexity. It degrades accuracy by only 2%.

The optimal STRF depth is determined by the action sequence duration for a dataset. For the KTH dataset, a larger depth yields better accuracy as shown in Fig. 2.7(a). We used a depth of 8, below which the accuracy drops by about 2% per depth reduction of 1. Temporal overlap (small temporal stride) is essential for guaranteeing a good accuracy, e.g., increasing the temporal stride from 1 to 4 reduces the accuracy by more than 8% as shown in Fig. 2.7(b). In the prototype design, we

Figure 2.8: Effect of number of iterations on classification accuracy.

Figure 2.9: Effect of number of neurons on classification accuracy.

chose a stride of 1.

The number of neurons, i.e., the number of STRFs, is dependent on the input size and it affects the classification accuracy as shown in Fig. 2.9. In testing the prototype design, we employ 192 neurons (N = 192). Each neuron's STRF is sized  $6 \times 6 \times 8$ . The STRF weights are quantized to 8 bits. Simulations show that 6 to 8 iterations are sufficient in Fig. 2.8, beyond which the accuracy saturates. We used 8 iterations (I = 8) for measurement in this work. Based on the STRFs extracted from the video, action classification can be performed.

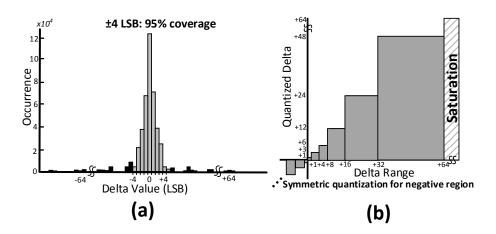

Figure 2.10: Architectural sketch of 3-layer implementation of video inference processor.

To realize this prototype chip, 54KB memory is needed to store the dictionary. The density of neuron activations and residuals are optimally set to  $S_a = 1\%$  and  $S_r = 3\%$ , respectively. The sparse, all-spiking approach reduces the number of operations per inference from 200M MACs to 4M SAs, which translates to a significant reduction in complexity and power consumption.

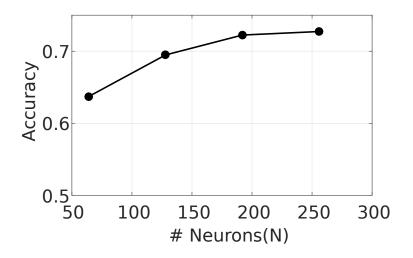

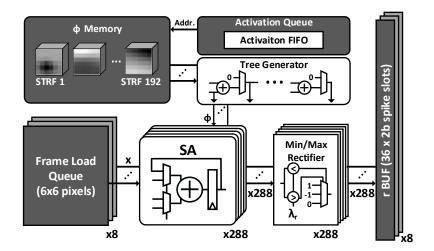

## 2.4 Design of Video Inference Processor

The video inference processor is made of three compute layers: residual layer, charge layer, and activate layer as illustrated in Fig. 2.10. Each layer corresponds to one step outlined in the previous section (the leak step is absorbed as part of the charge layer). The residual and charge layers are the workhorse of the inference processor. The inputs to the residual layer are sparse binary neuron spikes. The inputs to the charge layer are sparse residuals in the form of ternary spikes. Inputs are streamed through the three layers and back to the residual layer for the next iteration.

Figure 2.11: (a) Distribution of deltas between frames of STRFs; (b) non-uniform quantization of deltas.

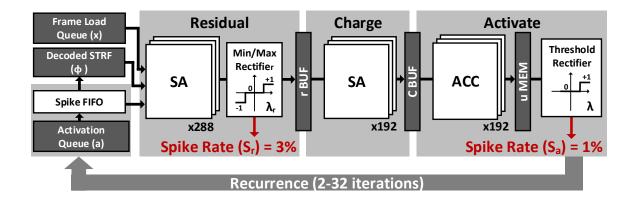

#### 2.4.1 Dictionary Compression and Non-Uniform Quantization

The dictionary  $\Phi$  and its transpose  $\Phi^T$  are accessed by the residual layer and the charge layer, respectively. Since the two layers operate concurrently in a streaming pipeline and the dictionary elements' access orders are different, both  $\Phi$  and  $\Phi^T$  are stored on chip, requiring 108KB of memory for the prototype design. Due to the high access bandwidth needed for highly parallel processing, the dictionary memory is divided into banks, sacrificing the storage efficiency. The dictionary memory alone is estimated to take 2mm<sup>2</sup> chip area in a 40nm CMOS technology.

In the prototype design, each dictionary element is a  $6 \times 6 \times 8$  8-bit STRF that is essentially a sequence of 8  $6 \times 6$  frames. Redundancy exists between consecutive frames, making it possible to compress each STRF to save memory, chip size and power. In Fig. 2.11(a), we plot the distribution of the pixel-by-pixel differences between consecutive frames of STRFs that are learned by training on the KTH dataset. The results show that 95% of the pixel-by-pixel differences cover a narrow range of only 4 LSBs.

The similarity between consecutive frames motivates the delta encoding of STRFs by storing the first  $6 \times 6$  8-bit frame as the anchor frame, and subsequent frames as

Figure 2.12: a tree generator for decompressing delta-encoded STRF.

4-bit deltas to the previous frame. The delta encoding reduces the dictionary storage by 43%.

Although 4 bits are sufficient to cover 95% of the deltas, a better result requires a larger coverage. To keep deltas to 4 bits while increasing the range of coverage, we propose the non-uniform quantization of deltas as shown in Fig. 2.11(b). The non-uniform quantization is specifically tailored to the delta distribution: smaller quantization step sizes are used at the lower end, and increasingly larger quantization step sizes are used towards the higher end to keep the number of quantization steps to 15.

The delta-encoded dictionary elements need to be decompressed before being used in compute. We employ a tree generator, shown in Fig. 2.12 to take the anchor frame as the base, and sequentially add the deltas to recover the remaining frames. With delta encoding and taking into account the overhead of tree generator, the dictionary memory storage in our prototype design, including compression and decompression, occupies 27% less area compared to the baseline.

#### 2.4.2 Residual Layer

The residual layer computes the reconstruction  $\hat{\mathbf{x}}$   $(V \times T)$  by multiplying  $\Phi$   $(V \times N)$  by  $\mathbf{a}$   $(N \times T)$ . Recall that since  $\mathbf{a}$  consists of binary activations, the matrix multiplication is done by SAs. The input  $\mathbf{a}$  is provided to the residual layer one

Figure 2.13: Visualization of residual compute.

column at a time, as the time-series output of N neurons from the activate layer. Since activations are sparse, we use a spike detector to skip 0 activations and provide the addresses of the activated neurons.

The residual layer computation is illustrated in Fig. 2.13. For each column of  $\mathbf{a}$ , the spike detector looks at a block of entries at a time and finds the address of the first entry that is 1. Suppose in processing column i of  $\mathbf{a}$ , the spike detector outputs j as the first entry in column i that is 1, then column j of  $\mathbf{\Phi}$  is read from memory, decompressed by the tree generator, and accumulated by the SA array as the temporary output of column i of  $\hat{\mathbf{x}}$ . We employ an array of V SAs to compute one vector accumulation at a time. The process continues with the spike detector providing the next nonzero entry. Upon completion, the reconstruction is subtracted from the input  $\mathbf{x}$ ; and the results are rectified to obtain the residuals. Since the reconstruction is computed column by column, the residuals are obtained column by column and provided to the charge layer in this order.

An implementation of the residual layer is shown in Fig. 2.14. The number of actual accumulations done by the SA array is  $NVTS_a$ , with  $S_a$  being the density of 1's in **a**. Since V SAs operate in parallel, the residual layer takes on average  $NTS_a = 192 \times 57 \times 1\% = 109$  cycles.

Figure 2.14: Residual layer design.

Figure 2.15: Visualization of charge compute.

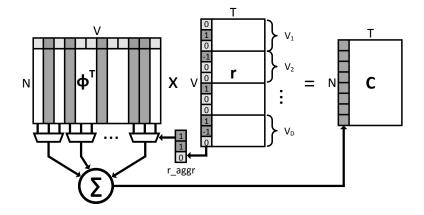

### 2.4.3 Charge Layer

The charge layer computes the charge **c** by multiplying  $\mathbf{\Phi}^T (N \times V)$  by **r**  $(V \times T)$ . Since **r** is a collection of ternary spikes  $\{0, -1, 1\}$ , the matrix multiplication is also done by SAs.

A similar architecture as the residual layer can be designed to implement the charge layer. The input **r** is provided one column at a time, as shown in Fig. 2.15. In processing a column of **r**, a nonzero entry triggers the accumulation of a column of  $\Phi^T$  to compute **c**. An array of N SAs is employed. The number of actual accumulations done by the SA array is  $NVTS_r$ . Since N SAs operate in parallel, the charge layer takes  $VTS_r$  to complete. Given the prototype specification, the charge layer takes

Figure 2.16: Charge layer design.

492 cycles.

To balance the layers, we apply temporal aggregation to shorten the latency of the charge layer. Each column of  $\mathbf{r}$  represents a  $X \times Y \times D$  frame. We compress  $\mathbf{r}$ to  $\mathbf{r}_a$  by pooling pixels at the same (x, y) location across D frames in a time series. If at least one of the D pixels is nonzero, pooling will output 1 for the pixel. After pooling, each entry of  $\mathbf{r}_a$  represents an "aggregated" pixel i (in the XY-plane) across D frames. Note that temporal aggregation does not make use of any approximation. It essentially collects a vector of inputs and applies parallel processing. The technique has no impact on the encoding fidelity or classification accuracy.

Temporal aggregation enables shorter latency. As shown in Fig. 2.16,  $\mathbf{r}_a$  is passed to a spike detector to output the first nonzero entry. As illustrated in Fig. 2.15, suppose the spike detector outputs address i (in the XY-plane), the address is used to read the D columns of  $\mathbf{\Phi}^T$  that correspond to pixel i, and the D  $\mathbf{r}$  values that are associated with pixel i. The D columns of  $\mathbf{\Phi}^T$  are vector summed by the pool units located inside the SA array, as shown in Fig. 2.16, with the D  $\mathbf{r}$  values as the control bits that determine whether the respective columns are zeroed, added or subtracted.

The aggregate processing increases the parallelism by a factor of D. The tem-

Figure 2.17: Activate layer design.

poral aggregation the D frames to one aggregate frame increases the density of 1's in the aggregate frame. If the D frames are completely independent, the density  $S'_r$ increases by D. However, the D frames belong to a time series and are highly correlated. In the prototype design, the density increases from 3% to 5%. With temporal aggregation and aggregate processing, the charge layer latency is reduced to  $XYTS'_r$  $= 6 \times 6 \times 57 \times 5\% = 103$  cycles on average for the prototype design.

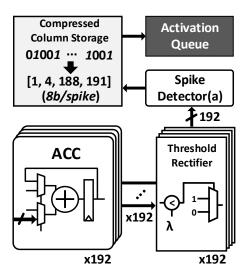

#### 2.4.4 Activate Layer

The activate layer accumulates potential updates  $\Delta \mathbf{u}$   $(N \times T)$  to compute new neuron potentials.  $\Delta \mathbf{u}$  is received column by column from the charge layer. The activate layer uses an array of N accumulators to update one column of potentials at a time. The potentials are thresholded to obtain binary activations  $\mathbf{a}$ .

The activations  $\mathbf{a}$  ( $N \times T$ ) are binary and sparse. As described in Section 2.4.2,  $\mathbf{a}$  is fed to a spike detector to locate the nonzero entries for processing in the residual layer. The spike detector can be used to encode  $\mathbf{a}$  in a CCS format, referring to storing only the addresses of nonzero entries in every column. as illustrated in Fig. 2.17.

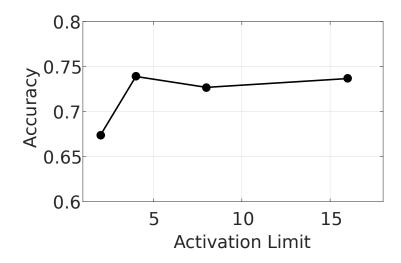

Due to high sparsity, we can limit the number of nonzero entries in a column to

Figure 2.18: Effect of nonzero activation limit on classification accuracy.

a small fixed number. Simulations show that at least 4 nonzero activations need to be stored to ensure a high accuracy. If only 2 nonzero activations are stored, the accuracy is reduced by 10% as shown in Fig. 2.18. In the prototype design, we allow up to 8 nonzero activations to be stored. Additional nonzero entries are dropped with negligible impact on the accuracy due to the extremely low likelihood of occurrence. CCS effectively reduces the storage by 64%.

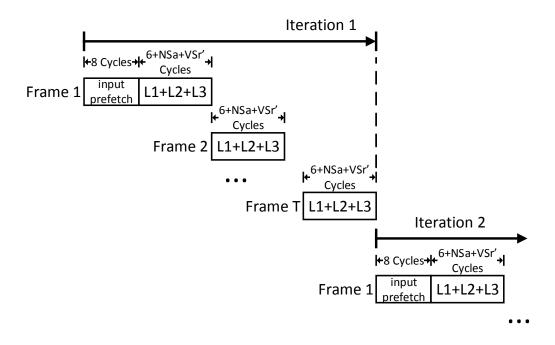

Putting the three layers together, the timing diagram for processing one  $6 \times 6 \times 64$ input is illustrated in Fig. 2.19. The input is divided into T = 57 temporally overlapped frames to be dispatched to the 3-layer processing in series. The processing is repeated for I = 8 iterations. Input data stream through the layers in sequence.

### 2.4.5 Summary of Design Optimizations

In the above subsections, we present the design techniques based on the prototype specification. The techniques are generally applicable and not limited to the given specification.

To quantify the benefits of the design techniques, we synthesized a baseline design in 40nm CMOS, along with design points after every step of the optimization. The

Figure 2.19: Timing illustration.

results are shown in Fig. 2.20. The baseline design employs a V-parallel MAC array in the residual layer, an N-parallel MAC array in the charge layer, and an N-parallel accumulator array in the activate layer. The design uses dense processing without spike detectors; and the residuals are not rectified. The baseline design reflects a standard parallel implementation without any sparsity or spiking optimizations. The latency of one iteration of processing is 211k cycles. The design is estimated to occupy 2.83mm<sup>2</sup> and consume 168mW.

The residual and charge layers account for the majority of the workload. Introducing sparsity optimizations has a major impact on the performance and the energy efficiency. In the first step of the optimization, we take advantage of sparse binary neuron activations to change the MAC array in the residual layer to an SA array, and use a spike detector to skip computations when activation is 0. The area and power increase by 1% and 4%, respectively, to support the net increase of the spike detection overhead minus the savings of the SA array, and the processing latency decreases by 36%. The latency is now entirely dominated by the charge layer.

Figure 2.20: (a) Area and power and (b) latency and energy after three design optimization steps: 1) sparse activation, 2) residual rectification, and 3) compressed activations.

In the second step, we apply ternary rectification to the residuals to change the MAC array to an SA array, and apply temporal aggregation to the charge layer. The area and power are reduced by 7% and 11%, respectively, and the latency is reduced by  $32\times$ .

In the third step, we compress the activations stored in the activate layer. The compression results in 5% area reduction and 13% power reduction.

In total, the three optimization steps increase the throughput by  $51\times$ , reduce the energy by  $63\times$ , and the area is reduced by 11%. Assume the KTH dataset with  $6\times6\times64$  inputs and the following parameter settings: N = 192,  $X \times Y \times D = 6\times6\times8$ , temporal stride of 1, spatial stride of 6, I = 8,  $S_a = 1\%$  and  $S_r = 3\%$ . At a clock frequency of 240MHz, the real-time processing of 1080p HD video at 60 frames per second (FPS) requires the processing of a  $6\times6\times64$  input to be completed in 4.16k cycles. The optimizations proposed in this work are crucial for meeting this latency requirement.

Lastly, note that activation sparsity and ternary rectification of residuals caused most of the accuracy loss as shown in Fig. 2.5. However, these two techniques also contributed most of the performance and energy efficiency gain, as shown in Fig.2.20.

## 2.5 Prototype Implementation, Measured Results and Comparison

We design a prototype SoC for video inference applications. The system block diagram is shown in Fig. 2.21. The core of the SoC chip is the video inference processor that is made of three compute layers and memory to store dictionary, neuron potentials and input video frames for testing. The SoC also consists of an Open-RISC processor for programming, control, configuration and classification. Through the OpenRISC processor, the video inference processor is configurable with several

Figure 2.21: System-level design of video inference processor.

|                 | ф<br>Main MEM |                 |

|-----------------|---------------|-----------------|

|                 |               |                 |

| Frame<br>Buffer | r+C+a         | Potentia<br>MEM |

| ф<br>Aux. MEM   | RISC          | ф<br>Aux. MEM   |

Figure 2.22: Microphotograph of the video inference SoC chip in 40nm CMOS.

| <u>Table 2.4: Action Classification Results of KTH Human Action Database</u> |        |          |        |         |         |         |         |  |  |

|------------------------------------------------------------------------------|--------|----------|--------|---------|---------|---------|---------|--|--|

|                                                                              | Boxing | Clapping | Waving | Jogging | Running | Walking | Average |  |  |

| On-chip softmax classifier                                                   | 70.0%  | 68.4%    | 85.0%  | 73.7%   | 94.4%   | 70.0%   | 76.7%   |  |  |

| Off-chip SVM classifier                                                      | 85.0%  | 78.9%    | 85.0%  | 73.7%   | 94.4%   | 80.0%   | 82.8%   |  |  |

Table 2.4: Action Classification Results of KTH Human Action Database

settings: 64, 128 or 192 neurons (N), frame size  $(X \times Y)$  from 1 to 36 and depth (D) from 1 to 8.

The video inference SoC chip is implemented in 40nm CMOS, occupying 3.98mm<sup>2</sup>. The core area measures 1.77mm × 1.43mm. The chip photo is shown in Fig. 2.22. The chip is tested for the KTH dataset with  $6 \times 6 \times 64$  inputs and the following parameter settings: N = 192,  $X \times Y \times D = 6 \times 6 \times 8$ , temporal stride of 1, spatial stride of 6, I= 8,  $S_a = 1\%$  and  $S_r = 3\%$ . At room temperature, the chip is measured to achieve an effective performance of 1.70TOPS (including skipped OPs) at 0.9V and 240MHz. The performance meets the 60FPS 1920×1080 HD video data rate, while dissipating 135mW. The measured power and performance at room temperature are shown in Fig. 2.23.

The 6-class KTH Human Action Dataset [58] is used for action classification testing, with 600 samples and a training/testing split ratio of 5:1. Using the core extract-

Figure 2.23: Measured power and performance of the video inference SoC chip.

ing the activation response of STRFs and a soft-max classifier programmed on the OpenRISC processor, the SoC achieves a 76.7% classification accuracy.