# **Comprehensive Review of Non-isolated** geless Power Factor Converter Topologies

ISSN 1751-8644 doi: 000000000 www.ietdl.org

Ankit Kumar Singh<sup>1</sup>, Anjanee Kumar Mishra<sup>2</sup>, Krishna Kumar Gupta<sup>1</sup> and Taehyung Kim,<sup>2</sup>

partment of Electrical and Instrumentation Engineering Engineering TIET, Patiala, India-147004

- University of Michigan Dearborn, Electrical and Computer Engineering 4901 Evergreen Rd Dearborn, MI, USA 48128

\* E-.mail: ankitee04@gmail.com

aract: The intention of this paper is to provide a critical review of single-phase non-isolated bridgeless power factor converter topologies, which will be useful for novice researchers in the power electronics field. The bridgeless nature of the converter reduces en umber of switching devices in the current path and achieves higher efficiency. Non-isolated topologies are considered in this evir w due to the inherent advantages they offer such as lower cost, weight and size and higher efficiency, which are desirable for systems such as on-board electric vehicle battery chargers, DC-power supplies and variable speed drives. These topologies erived from conventional boost, buck and buck/boost converters. Moreover, the topologies can be operated in continuous or

disc ntinuous conduction modes subject to their applications. Each topology is described in terms of its advantages and limitations. dition, a comparative study is conducted for each group (boost, buck and buck/boost).

#### Introduction 1

Single-phase AC-DC converters with a power factor correction stage are most commonly used for power conversion systems 1 and can be applied in many residential and industrial applications such as power supplies for consumer electronics, electric vehiarging, and variable speed drives. To maintain rigorous grid regulation, e.g., IEC-61000-3-2 harmonic limits, sinusoidal current v rulation and a high power factor (PF) converter are required for ... aforementioned applications. Single-phase PFC converters are very prevalent components for achieving the IEC harmonic reguand current regulation limits [1]. Therefore, in the existing literature, various types of single-phase PFC converters have been presented that are essentially derived from conventional boost and buck/boost converters, although boost PFC converters are the most widely used in many applications due to their simplicity, cost effec-

ss, and high performance in terms of efficiency and high power tactor. With the boost PFC converters, the inherent limitation is that rut voltage is always higher than the peak AC supply voltage [2-o] On other hand, in buck derivative PFC converters, the output

voltege is always lower than peak of AC input voltage. When a wide ...ge of output voltage is desired, e.g., for plug-in electric vehicles (PEV s) battery charging, where the battery sets at variable voltage in the range between 50-700 V in order to satisfy the different vehicles and battery types [9], conventional buck/boost converters

heir derived forms are employed [10–14] for such applications. However, the above-mentioned topologies whether boost, buck, or h k/boost based, have a bridge rectifier at the input stage, which is responsible for a considerable portion of the conduction losses in the converter. To mitigate the conduction loss in the bridge-rectifier, bridgeless variants of boost, buck, and buck/boost converters have been given in [15-29]. The bridgeless approach decreases the er of devices in the current path, which results in a reduction

of the losses and achieves higher efficiency at lower line voltages [15]. To further improve the efficiency in bridgeless converters, they perated in discontinuous mode (DCM) of operation. The DCM

tion provides zero-current turn-on of the switches and zerourrent turn-off of the diodes, which reduce the switching losses uring the turn-on and turn-off times of the switches and diodes, resp. ctively . Moreover, some bridgeless topologies utilize resonant components to achieve soft switching in the continuous conduction

mode (CCM) of operation and those topologies are used in high power applications with high efficiency.

As has been discussed in the literature, , there is a consistent demand for high-efficiency, high-PF small-sized and lightweight single-phase PFC converters for various power applications. Some of these demands are met by conventional diode bridge-based singlephase PFC converters using buck, boost, or buck-boost converters. Isolated PFC converters using bridge rectifiers pose serious concerns for efficiency. The bridgeless nature of the converter reduces the number of switching devices in the current path and achieves higher efficiency. Moreover, the non-isolated nature of the converter further assists in raising the efficiency and lowering the weight of the converter system, which are desirable for systems such as on-board electric vehicle battery chargers, DC-power supplies, and variable speed drives. The goal of this paper is to provide a critical review, based on various parameters, of single-phase non-isolated bridgeless PFC topologies, which will be useful for novice researchers in the power electronics field.

The remaining sections of the paper are organized as follows: section 2 gives a review of bridgeless boost PFC topologies and a comparative analysis among them. Section 3 is a review of bridgeless variants of buck PFC topologies and a comparison among them. In section 4, buck/boost-based bridgeless topologies are reviewed. Finally, conclusions drawn from this review study are given in section 5.

#### Bridgeless boost and its derived topologies 2

In this section, boost and its derived version of bridge less PFC topologies are reviewed and a comparison among the topologies is tabulated in Tables I and II.

#### Classical bridgeless boost PFC converter 21

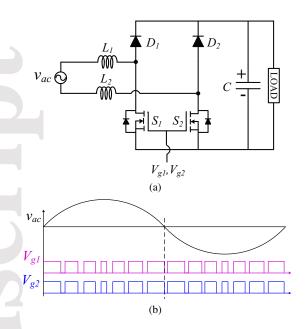

The bridgeless boost PFC converter shown in Fig. 1 is an attractive solution for power levels greater than 1 kW where power density and efficiency (reduction in gate driver loss) are especially critical parameters. In this topology, both switches are turned-ON using a single driver circuit; thus, the gating signal of the switches is iden-

This is the author manuscript accepted for publication and has undergone full peer review but has not been through the copyediting, typesetting, pagination and proofreading process, which may lead to IET Research Journals, pp. 1-9 © The Institution of Engineering and Technology 2015

This article is protected by copyright. All rights reserved.

**Fig. 1**. (a) Classical bridgeless boost PFC converter. (b) Gating signals of switches.

of an additional gate driver circuit) and efficiency of the converter improves in comparison with those bridgeless boost PFC converters where separate driver circuits are used. Also, this topology avoids the heat management problem of diode bridge rectifiers while it does introduce electromagnetic interference (EMI) problems [30]. Moreover, in this topology, the input line is floating with respect to the PFC ground; therefore, it is not possible to sense the input voltage without a low frequency transformer or an optical-coupler. Because of current does not share the same path during each half cycle of input voltage, complex circuity is needed to sense the input current.

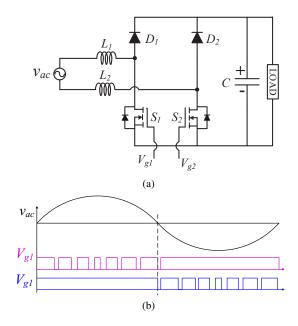

For further improvement in the bridgeless converter shown in Fig. 1(a), a phase shifted bridgeless PFC converter, which is also known as a dual-boost PFC converter [26] was introduced, as shown in Fig. 2(a). In this topology, the gates of the MOSFET switches are decoupled and one of the switches remains ON during each half cycle of the input supply. Fig. 2(b) shows the gating scheme of the switches. This topology reduces the gate conduction loss and at light load conditions, the conduction loss can be reduced until the voltage drop across the MOSFET body diode becomes equal to the voltage drop across the MOSFET channel  $r_{ds}(on)$ , since beyond this point, additional current flows through the body diode. The light load efficiency improvement is achieved at the expense of additional driver circuits.

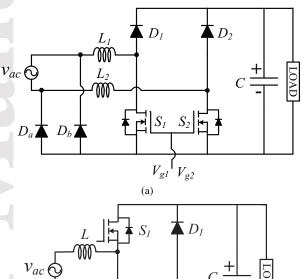

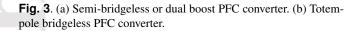

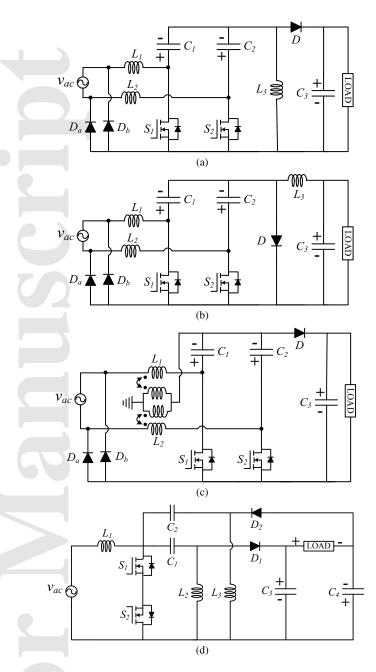

### 2.2 Semi-bridgeless converter

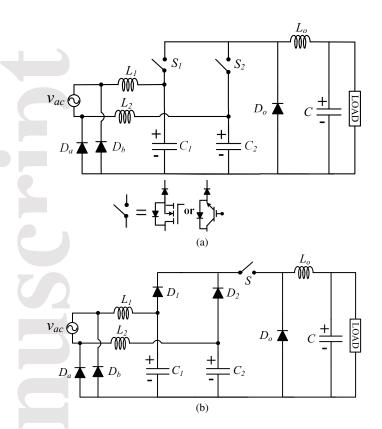

The semi-bridgeless configuration is derived from conventional bridgeless topology (Fig.1(a)) by adding two additional slow diodes, namely:  $D_a$  and  $D_b$ , as shown in Fig. 3 (a). These additional slow diodes connect the input to the ground of the PFC and solve the EMI related problems. The associated conduction loss in these two diodes is low because current does not always return through them. This is due to low inductor impedance at line frequency; therefore, a large portion of the current flows through the body diodes of the MOSFET. With this topology, it is possible to sense the input voltage through a string of voltage dividers. In this topology, the two boost converters will work alternatively during the positive and negative half cycles of the input supply. The low utilization of the inductors and devices reduces the power density and increases the cost of the converter compared to the conventional boost PFC.

The totem-pole bridgeless PFC, as shown in Fig. 3(b), has only one switch and one low frequency diode conducting at any time.

**Fig. 2**. (a) Phase shifted bridgeless boost PFC converter. (b) Gating signals of switches.

Thus, it has the lowest conduction loss compared with the conventional boost PFC and the semi-bridgeless dual-Boost PFC. Therefore, the totem-pole bridgeless converter achieves higher efficiency and power density compared to aforementioned converters. In the totem-pole PFC topology, the body-diode of  $S_1$  or  $S_2$  provides the freewheeling path for the inductor current. The recovery speed of body diode in the MOSFET is so slow that it makes  $S_1$  and  $S_2$  conduct at the same time leading to the destruction of the circuits. Therefore, a MOSFET with fast recovery speed should be used in the totem-pole topology.

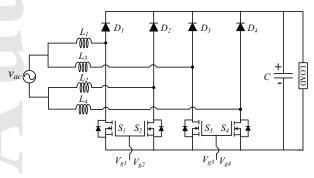

### 2.3 Bridgeless interleaved converter

The bridgeless interleaved (BLIL) converter has the same number of semiconductor devices as in a conventional interleaved boost (ILB) PFC converter [5]. In comparison to the ILB converter, the BLIL converter has two additional MOSFETs and two fast diodes in place of four slow diodes. From the operational point of view of the converter, the gating signal of switches  $S_1$  and  $S_2$  is 180 ° out of phase with switches  $S_3$  and  $S_4$ ; similar to the conventional ILB converter.

The peak efficiency of the BLIL is reported as 98.5% at 1.2 kW load and 70 kHz switch frequency [16]. The efficiency improvement at high power load (above 3 KW) is the major contribution of this topology. Moreover, due to the interleaving structure, current stress in switches is low and hence the reliability and fault tolerance of the converter are improved compared to other bridgeless converters. However, the significant drawback of this topology is its higher cost due to the increased number of magnetic components.

# 2.4 Bridgeless converter with low conduction losses and reduced diode reverse-recovery problems

The output diodes in the converters shown in Fig. 1(a), Fig. 2(a) and Fig. 3 have the severe problem of high reverse recovery losses due to high diode forward current and high voltage. As the switching frequency increases, the large reverse-recovery currents of the output diodes affect the switches in the form of additional turnon losses and also produce electromagnetic interference (EMI) noises. To overcome these issues, various active and passive snubber approaches have been proposed for the bridgeless boost rectifier [31–35]. These topologies either have higher conduction losses due to a large amount of circulating current flowing through the auxiliary

## Table 1 Comparison of bridgeless boost PFC converters

| Topology    | Input current ripple | EMI/Noise | Magnetic size | Efficiency | Cost   |

|-------------|----------------------|-----------|---------------|------------|--------|

| Figure 1(a) | High                 | High      | Large         | Poor       | Low    |

| Figure 2(a) | High                 | Fair      | Large         | Fair       | Low    |

| Figure 3(a) | High                 | Fair      | Large         | Poor       | Medium |

| Figure 3(b) | High                 | High      | Large         | High       | Low    |

| Figure 4    | Low                  | Low       | Small         | High       | High   |

| Figure 5    | Low                  | Fair      | Medium        | Fair       | Medium |

| Figure 6(a) | High                 | High      | Large         | High       | Medium |

| Figure 6(b) | High                 | High      | Large         | High       | Medium |

Table 2

comparison of component count in bridgeless boost PFC converters

| Topology    | Switches | Diodes | Capacitors | Inductors   | On-path devices | Off-path switches |

|-------------|----------|--------|------------|-------------|-----------------|-------------------|

| Figure 1(a) | 2        | 2      | 1          | 2           | 1S+1D           | 2D                |

| Figure 2(a) | 2        | 2      | 1          | 2           | 1S+1D           | 2D                |

| Figure 3(a) | 2        | 4      | 1          | 2           | 1S+1D           | 2D                |

| Figure 3(b) | 2        | 2      | 1          | 1           | 1S+1D           | 2D                |

| Figure 4    | 4        | 4      | 1          | 4           | 2S+2D or 1S+1D  | 2D                |

| Figure 5    | 2        | 4      | 1          | 3 (Coupled) | 1S+1D           | 2D                |

| Figure 6(a) | 3        | 4      | 3          | 2           | 1S+1D           | 2D                |

| Figure 6(b) | 2        | 6      | 3          | 3           | 1S+1D           | 2D                |

Fig. 4. Bridgeless interleaved boost PFC converter.

Fig. 5. Ripple free bridgeless boost PFC converter.

**Fig. 6**. (a) Hybrid resonant PWM bridgeless boost PFC converter. (b) Soft switching based bridgeless boost PFC converter.

circuit and high stress on switching devices or require an isolated transformer to sense the AC input voltage and a Hall effect sensor to detect the input current, which limits the use of this topology in practical designs. The bridgeless boost PFC converter proposed in [15] reduces the conduction and diode reverse-recovery losses without sensing the input voltage, as shown in Fig.5. With this topology, zero-current turn-off of the output diodes is achieved, and the

**Fig. 7**. (a) Bridgeless buck PFC converter with discontinuous capacitor Voltage mode (DCVM) using two switches. (b) Bridgeless buck PFC converter with discontinuous capacitor Voltage mode (DCVM) using single switch.

reverse-recovery currents of the additional diodes are slowed down to reduce the diode reverse-recovery losses. The inductive components are wound on a single core by using the leakage inductance of the coupled inductor. This converter has an efficiency improvement at low line input voltage, e.g., at 90 V, 300 W load, and 100 kHz switching frequency it achieves a measured efficiency of 95.5%.

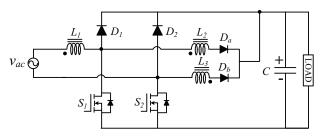

#### 2.5 Soft-switching based bridgeless boost PFC converter

In [19], a soft switching based bridgeless boost PFC converter has been proposed for power supply and battery charging applications, as shown in Fig. 6(a), which operates in CCM and achieves zerovoltage switching (ZVS) for all switches. The converter operates in both PWM and resonant modes in each switching cycle. When switches  $S_1$  and  $S_2$  are turned-on converter operates in resonant mode, utilizing capacitor  $C_r$  and inductor  $L_r$  and PWM mode when switches  $S_1$  and  $S_2$  are turned-off and axillary switch  $S_a$  is in ON mode. Thus, its switching operation is known as the hybrid resonant PWM. Moreover, the converter also reduces the turn-off losses of the PWM operating switches. The PWM switches of the converter are gated with the same PWM signal which simplifies the control design. Furthermore, the converter exhibits an approximately 1% efficiency improvement as well as lower device temperature rise at full load compared to a conventional hard switched boost PFC converter. The PWM switching frequency is selected as 150 kHz for experimentation.

In [20], a new bridgeless boost PFC based on a passive soft switching method was proposed for high power applications as shown in Fig. 6(b). In this method, an extra auxiliary switch or additional control circuitry to realize soft switching has been eliminated. In fact a few passive components are employed in the converter. The driving signals of the two switches are in phase hence only one drive signal is needed. Therefore, the configuration is simple and easy to

4

**Fig. 8**. Bridgeless buck PFC converter with voltage doubler output using two inductors.

implement which yields a low cost solution for high power applications. All the power switches and diodes  $(S_1, S_2, D_4, D_5 \text{ and } D_6)$ operate under a soft switching condition. The  $S_1$  and  $S_2$  switches operate with zero-current and zero-voltage turn-on and zero-voltage turn-off, and  $D_4$ ,  $D_5$  and  $D_6$  operate with zero-voltage turn-on and turn-off.

#### 2.6 Comparative study of bridgeless boost PFC topologies

A comparative study of the bridgeless boost PFC topologies is conducted in terms of input current ripple, EMI/noise, magnetic size, efficiency and cost as presented in Table 1 using [16]. A qualitative comparison among the topologies has been done for the aforementioned parameters. The terms "high", "low", "small", etc. are used to only describe comparisons among the topologies and not in an absolute sense. Table 2 using [36] shows the number of active and passive components as well as the on-path and off-path devices for each topology.

## 3 Bridgeless buck PFC converters

In this section, buck type derivative bridgeless converters for PFC applications are reviewed. A comparative study among the topologies in terms of voltage conversion ratios and component counts is presented in Tables 4 and 5, respectively.

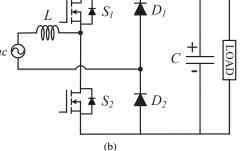

### 3.1 A discontinuous capacitor voltage mode (DCVM) operated bridgeless buck PFC converter

In [22], a bridgeless buck PFC converter operating in DCVM was presented. Compared to conventional full bridge buck DCVM PFC converters, the bridgeless buck PFC converter decreases the number of semiconductor devices in the current path. Therefore, the conduction losses and thermal stress on the semiconductor devices are reduced and converter efficiency gets improved as a result. Unlike the boost PFC converter, the proposed converter has the same advantages as the conventional full bridge buck DCVM converters such as: inherent inrush current protection during start-up conditions, lower input current ripple, fewer reverse recovery problems and low EMI noise. The major limitation of DCVM operation is high switch voltage stress which increases in accordance with the load current; therefore, the converter is suitable for low power applications (< 300 W).

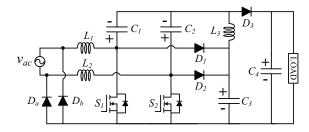

Figs. 7(a) and (b) show two bridgeless DCVM buck PFC converters. The first topology in Fig. 7(a), which uses two switches,  $S_1$  and

**Fig. 9**. (a) Bridgeless buck PFC converter with voltage doubler output using two inductors. (b) Bridgeless buck PFC converter with voltage doubler output using coupled inductors. (c) Bridgeless buck PFC converter with voltage doubler output using two inductors and two bidirectional switches. (d) Bridgeless buck PFC converter with nonlinear output using two inductors.

$S_2$ , driven by the same pulse width modulation (PWM) signal, simplifies the control circuit. It is noted that the two switches  $S_1$  and  $S_2$  are unidirectional switches (current flows in only one direction) and hence a diode is added in series with the switch. On the other hand, the second topology uses a single switch, as shown in Fig. 7(b). Compared to the conventional full bridge DCVM PFC converters [37, 38] the proposed bridgeless converter utilizes one additional capacitor and inductor, which is a disadvantage in terms of cost and size. However, two inductors have better thermal performance compared to a single inductor.

#### 3.2 Bridgeless converter with Voltage doubler output and nonlinear output

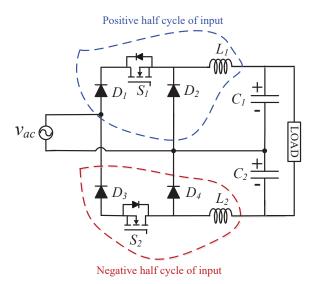

In [23], voltage doubler and nonlinear output based bridgeless buck topologies were proposed. The first version of these configurations, which utilizes two back-to-back buck converters, is shown in Fig. 8; one unit of it operates in the positive half cycle of input and second unit operates in the negative half cycle of the input as indicated by the dotted lines in Fig. 8. During converter's operation, the voltage across capacitors  $C_1$  and  $C_2$ , i.e.,  $V_1$  and  $V_2$  must be selected lower than the peak of input voltage,  $v_{acpeak}$ . The voltage output across load is  $V_0$  which is sum of the voltages  $V_1$  and  $V_2$ , and is given by

$$V_0 = 2D|v_{ac}| \tag{1}$$

where D is the duty cycle and  $|v_{ac}|$  is the instantaneous rectified AC input voltage. The relationship shown in (1) is valid for input voltage  $v_{ac} > V_0/2$ . When  $v_{ac}$  falls below  $V_0/2$ , the energy can not be delivered to the load and hence the load current is maintained by capacitors  $C_1$  and  $C_2$ . The major advantage of this converter is, low-line efficiency of the converter can be improved for 0-300 V output voltage range. Another important feature of this topology is the low common mode noise problem. With reference to Fig. 8, the return path of the input source and the mid-point of  $C_1$  and  $C_2$  are connected to each other. Therefore, there is no high dv/dt problem between the input and output terminals and as result the converter can operate with low common-mode noise.

Furthermore, four topologies are derived from Fig. 8 as shown in Fig. 9. The inductors  $L_1$  and  $L_2$  in the Fig. 8 are replaced by single inductor L shown in Fig. 9(a). Since this topology uses only one inductor, magnetic component utilization is better compared to the two inductor topologies. However, this topology has a high common mode noise problem because voltage developed across the inductor, L induces the high dV/dt between the input and output terminals.

Another topology presented in Fig. 9(b) has the same commonmode noise as the topology shown in Fig. 8. Moreover, the topology shown in Fig. 9(b) reduces the number of magnetic components by coupling the inductor  $L_1$  and  $L_2$  of the Fig. 8. Because windings of  $L_1$  and  $L_2$  utilize the same core as a result the utilization of core increases. However, to accommodate both windings on single core, it may require a customized core with a large window area since commercially available toroidal-type cores are typically designed to accommodate only a single winding.

A topology shown in Fig. 9(c), is obtained by moving switches  $S_1$  and  $S_2$  in the Fig. 8 to the AC side. For implementation of this topology, two bidirectional current carrying switch are employed in series with an AC source. The driving circuit of these two switches is simple because the source terminals of  $S_1$  and  $S_2$  are connected together. Another variation of the bridgeless converter (Fig. 8) is shown in Fig. 9(d). In this configuration (Fig. 9(d)), the circuit exhibits a non-linear gain which is given as

$$V_0 = \frac{2D}{1 + (1 - D)^2} |v_{ac}| \tag{2}$$

According to (2), if a duty cycle D is near unity, then expression (2) is converted into (1). However, if a duty cycle D is near zero, i.e., a case when output voltage  $V_0$  is much lower than input voltage  $v_{ac}$ ,

#### Table 3 comparison of component count in bridgeless buck PFC converters

| Topology    | Switches                                                                            | Diodes                                                                                                                                                                             | Capacitors                                                                                                                                                                                                                                     | Inductors                                                                                                                                                                                                                                                                                                                                                      | On-path switches                                                                                                                                                                                                                                                                                                                                                 | Off-path switches                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 7(a) | 2                                                                                   | 3                                                                                                                                                                                  | 3                                                                                                                                                                                                                                              | 2                                                                                                                                                                                                                                                                                                                                                              | 1S+1D                                                                                                                                                                                                                                                                                                                                                            | 1D                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 7(b) | 1                                                                                   | 3                                                                                                                                                                                  | 3                                                                                                                                                                                                                                              | 2                                                                                                                                                                                                                                                                                                                                                              | 1S+1D                                                                                                                                                                                                                                                                                                                                                            | 1D                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 8    | 2                                                                                   | 4                                                                                                                                                                                  | 2                                                                                                                                                                                                                                              | 2                                                                                                                                                                                                                                                                                                                                                              | 1S+1D                                                                                                                                                                                                                                                                                                                                                            | 1D                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 9(a) | 2                                                                                   | 4                                                                                                                                                                                  | 2                                                                                                                                                                                                                                              | 1                                                                                                                                                                                                                                                                                                                                                              | 1S+1D                                                                                                                                                                                                                                                                                                                                                            | 1D                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 9(b) | 2                                                                                   | 4                                                                                                                                                                                  | 2                                                                                                                                                                                                                                              | 2 (Coupled)                                                                                                                                                                                                                                                                                                                                                    | 1S+1D                                                                                                                                                                                                                                                                                                                                                            | 1D                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 9(c) | 2                                                                                   | 4                                                                                                                                                                                  | 2                                                                                                                                                                                                                                              | 2                                                                                                                                                                                                                                                                                                                                                              | 1S+2D                                                                                                                                                                                                                                                                                                                                                            | 1D                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 9(d) | 2                                                                                   | 4                                                                                                                                                                                  | 2                                                                                                                                                                                                                                              | 2                                                                                                                                                                                                                                                                                                                                                              | 1S+1D                                                                                                                                                                                                                                                                                                                                                            | 1D                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|             | Figure 7(a)<br>Figure 7(b)<br>Figure 8<br>Figure 9(a)<br>Figure 9(b)<br>Figure 9(c) | Figure 7(a)         2           Figure 7(b)         1           Figure 8         2           Figure 9(a)         2           Figure 9(b)         2           Figure 9(c)         2 | Figure 7(a)         2         3           Figure 7(b)         1         3           Figure 8         2         4           Figure 9(a)         2         4           Figure 9(b)         2         4           Figure 9(c)         2         4 | Figure 7(a)         2         3         3           Figure 7(b)         1         3         3           Figure 8         2         4         2           Figure 9(a)         2         4         2           Figure 9(b)         2         4         2           Figure 9(b)         2         4         2           Figure 9(c)         2         4         2 | Figure 7(a)       2       3       3       2         Figure 7(b)       1       3       3       2         Figure 8       2       4       2       2         Figure 9(a)       2       4       2       1         Figure 9(b)       2       4       2       2         Figure 9(b)       2       4       2       2         Figure 9(c)       2       4       2       2 | Figure 7(a)       2       3       3       2       1S+1D         Figure 7(b)       1       3       3       2       1S+1D         Figure 8       2       4       2       2       1S+1D         Figure 9(a)       2       4       2       1       1S+1D         Figure 9(b)       2       4       2       2       1S+1D         Figure 9(b)       2       4       2       2       (Coupled)       1S+1D         Figure 9(c)       2       4       2       2       1S+1D |

Table 4

Voltage conversion ratio of bridgeless buck converter in CCM

| Topology                           | $M = V_0 / v_{ac}$     |

|------------------------------------|------------------------|

| Figure 7(a) and (b)                | D                      |

| Figure 8, Figure 9(a), (b) and (c) | 2D                     |

| Figure 9(d)                        | $\frac{2D}{1+(1-D)^2}$ |

then input-output gain becomes as (3)

$$V_0 = D|v_{ac}| \tag{3}$$

, which is similar to the conventional buck converter.

Table 3 summarizes the part counts and the number of semiconductor devices in the current path for switch-on and off conditions. Table 4 shows the voltage conversion ratio for each topology.

## 4 Bridgeless buck/boost PFC converters

In this section, bridgeless buck/boost PFC topologies are reviewed. These topologies are derived using non-inverting buck/boost, SEPIC, CuK and inverting buck/boost converters.

# 4.1 Cascaded buck/boost derivative bridgeless PFC converter

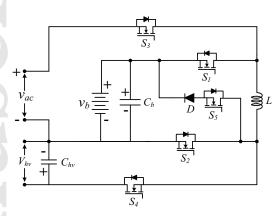

The bridgeless buck/boost PFC converter shown in Fig. 10 has been derived from the conventional cascaded buck/boost converter [17]. The important features of this converter is the low voltage and current stresses on the components. Therefore, this bridgeless converter can be used for higher power applications compared to other buck/boost derivative bridgeless converters (SEPIC, ZETA, CuK, etc.). During the positive half cycle of input voltage when the AC input voltage  $(v_{ac})$  is lower than the output load voltage  $(V_0)$ , the converter operates in the boost mode. The switch  $S_1$  is continuously turned-on and  $S_3$  is gated through the PWM and then operation of the converter is exactly the same as the operation of a conventional boost converter. When the AC input voltage is higher than the output voltage, the converter operates in the buck mode and when the switch  $S_1$  is turned-on, the capacitor  $C_1$  discharges and the input voltage supplies power to the inductor and load. Moreover, when the switch  $S_1$  is turned-off, the diode  $D_3$  conducts and the inductor releases its stored energy to the load. The capacitor  $C_1$  is charged through the input voltage. The operation of the converter in the negative half cycle of the input supply is described similarly to the operation in the positive half cycle.

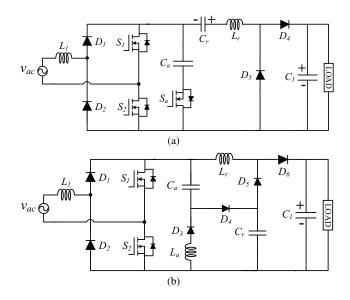

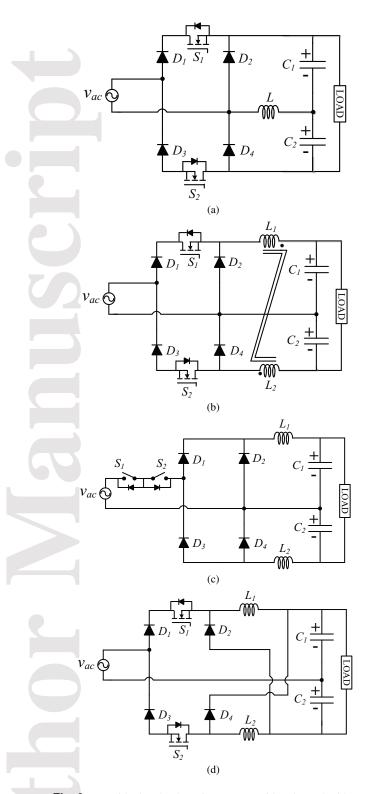

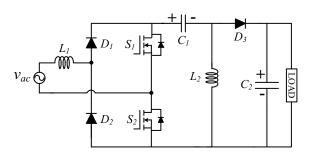

# 4.2 Bridgeless SEPIC and CuK PFC rectifiers with low conduction loss

In [18], the authors have presented SEPIC and CuK based bridgeless converters as shown in Fig. 11(a) and (b), respectively, which are operated in DCM. During a switching cycle only two semiconductor devices are in the current path, which results in lower conduction losses and improves the thermal management problem. DCM operation brings the additional advantages of zero-current turn-on of the switches and zero-current turn-off of the output diode *D*. In addition, DCM operation reduces the complexity of control design. However,

**Fig. 10**. Bridgeless buck/boost PFC derived from the cascaded buck/boost converter.

when a converter operates in DCM, the current stress on the components becomes relatively higher compared to CCM operation and hence DCM operating converter is suitable to low-power applications (< 300 W). With this topology, the problem of common-mode EMI noise is reduced because of the two additional slow diodes ( $D_a$ and  $D_b$ ) and the connection of the output ground to the AC main.

The voltage waveforms of the inductors in the converter shown in Figs. 11(a) and (b) are identical, and hence they can magnetically be coupled on a single core which significantly reduces the overall size of the converter because the inductor is the heaviest component over any other components in a converter [6]. Fig. 11(c) depicts the circuit arrangement of bridgeless SEPIC with coupled inductors. The voltage conversion ratio M, i.e.,  $V_0/v_{ac}$  of the circuit shown in Fig.11 in the DCM operation is expressed as

$$M = \sqrt{\frac{R_L}{2R_e}} \tag{4}$$

where  $R_L$  is the load resistance and  $R_e$  is given as

$$R_e = \frac{2L_e}{D_1^2 T_s} \tag{5}$$

where

$$L_e = \frac{L_2 L_3 + L_1 L_3 + L_1 L_2}{L_1 L_2 L_3} \tag{6}$$

and  $D_1$  is duty cycle of the switches.

Another version of the bridgeless SEPIC PFC converter, which has advantages of reduced switch voltage stress and low EMI noise compared to the conventional SEPIC converter, is shown in Fig. 11(d).

#### 4.3 A modified bridgeless SEPIC PFC converter with extended gain

In [24], the authors proposed a bridgeless SEPIC rectifier (Fig. 12) with a voltage multiplier cell which is derived from the modified SEPIC converter in [39]. The bridgeless structure reduces the conduction losses, and multiplier cells  $(D_1,C_3)$  and  $(D_2,C_3)$  increases the gain and reduce the stress on the switches. However, the increase of voltage gain leads to efficiency improvement at the lower side of grid voltage; therefore, requirements for thermal management are drastically reduced compared to their conventional counterparts [18]. However, the common mode EMI generation of this topology is similar to the converter in [18]. Furthermore, to achieve low

**Fig. 11**. (a) Bridgeless SEPIC PFC converter. (b) Bridgeless CuK PFC converter. (c) Coupled inductors based bridgeless SEPIC PFC converter. (d) A modified bridgeless SEPIC PFC converter.

input current ripples all three inductors can be coupled on a single magnetic core. Therefore, the requirement for input filtering is minimized.

The voltage conversion ratio M in CCM operation is defined as

$$M = \frac{V_0}{v_{ac}} = \frac{1 - D}{1 + D}$$

(7)

where D is the duty cycle.

The voltage conversion ratio in DCM operation is given as

$$M = \frac{V_0}{v_{ac}} = \frac{D_1^2 \alpha}{K} \tag{8}$$

where  $D_1$  is duty cycle of the switches, and  $\alpha$  and K are expressed as

$$\alpha = -\frac{2}{\pi} - M + \frac{2M^2}{\pi\sqrt{M^2 - 1}} \left[\frac{\pi}{2} + \tan^{-1}\left(\frac{1}{\sqrt{M^2 - 1}}\right)\right]$$

(9)

Fig. 12. Bridgeless SEPIC PFC converter with extended gain.

Fig. 13. Bridgeless SEPIC PFC converter with reduced components.

**Fig. 14.** (a) Bridgeless SEPIC converter with a ripple-free input current (b) Conventional gating signals for switches in bridgeless SEPIC converter. (c) The gating signals used for bridgeless SEPIC converter of Figure 14(a).

$$K = \frac{2L_e}{T_s R_L} \tag{10}$$

where  $L_e$  is given the same as (6).

*IET Researchis Loutinele, ip. pro* tected by copyright. All rights reserved. © The Institution of Engineering and Technology 2015

Table 5 comparison of component count in bridgeless buck/boost PFC converters

| Topology     | Switches | Diodes | Capacitors | Inductors   | On-path switches | Off-path switches |

|--------------|----------|--------|------------|-------------|------------------|-------------------|

| Figure 10    | 3        | 4      | 3          | 1           | 2S+1D            | 2D                |

| Figure 11(a) | 2        | 3      | 3          | 3           | 1S+1D            | 2D                |

| Figure 11(b) | 2        | 3      | 3          | 3           | 1S+1D            | 2D                |

| Figure 11(c) | 2        | 2      | 3          | 3 (Coupled) | 1S+1D            | 2D                |

| Figure 11(d) | 2        | 2      | 4          | 3           | 1S+1D            | 1D                |

| Figure 12    | 2        | 5      | 4          | 3           | 1S+1D            | 2D                |

| Figure 13    | 2        | 3      | 2          | 2           | 1S+1D            | 2D                |

| Figure 14(a) | 2        | 3      | 2          | 3           | 1S+1D            | 2D                |

| Figure 15    | 5        | 1      | 2          | 1           | 2S               | 1S+1D             |

Fig. 15. A bridgeless based integrated converter for PEVs.

## 4.4 Bridgeless SEPIC PFC converter with reduced components and conduction losses

A bridgeless SEPIC PFC converter (Fig. 13) in [25] has lower conduction losses and a reduced number of components compared to the other existing bridgeless SEPIC converters. This topology is designed to operate in DCM, where the switches operate as zero-current turn-on and the output diode operates as zero-current turn-off. In addition, in DCM operation the control circuit requires only a voltage loop for PFC; hence the controller design becomes simpler and easy to implement in the processor. Furthermore, the measured efficiency of this topology has a 1% improvement over a conventional SEPIC PFC converter. Moreover, this topology can be operated in CCM for higher power applications such as on-board EV charging systems. In an on-board charging system, a compact size converter is desirable due to space and weight constraint. In addition to this, a wide variation of battery voltage is reached during charging; therefore; buck-boost capability of the PFC converter is mandatory, which is easily met by the SEPIC converter.

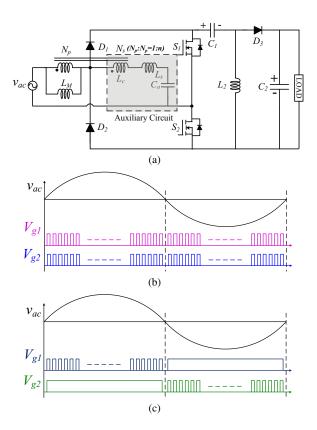

# 4.5 Bridgeless SEPIC converter with a ripple-free input current

The bridgeless SEPIC PFC converter shown in Fig. 13 has a reduced number of components and gains higher efficiency due to the absence of the diode bridge-rectifier. However, a large input inductance is used in order to reduce the input current ripples. In addition, conduction loss occurs in the body diode of the switches due to the use of a single PWM gate signal for both switches ( $S_1$  and  $S_2$ ).

In order to overcome above mentioned problems, a new bridgeless SEPIC PFC converter with a ripple free input current has been proposed in [26], as shown in Figure 14(a). An auxiliary circuit (shaded area in Figure 14(a)) consisting of a small inductor, a capacitor and an additional winding of input inductor is used to reduce the input current ripple. Usually, coupled inductors techniques are used to mitigate the current ripple [40–42]. Fig. 14(c) shows PWM gating of switches  $S_1$  and  $S_2$ . For a half cycle of the input supply, one switch is continuously turned-on and current is forced to flow through the channel of the switch rather than through the intrinsic

8

Table 6 Voltage conversion ratio of bridgeless buck/boost converter in CCM

| Topology                                 | $M = V_0 / v_{ac}$                   |

|------------------------------------------|--------------------------------------|

| Figure 10, 11(a), (c), (d), 13 and 14(a) | $\frac{D}{1-D}$                      |

| Figure 11(b)                             | $-\frac{\overline{D}}{1-D}$          |

| Figure 12                                | $\frac{1+D}{1-D}$                    |

| Figure 15                                | $\frac{1}{1-D}$ and $-\frac{D}{1-D}$ |

body diode. As a result, conduction loss of switch is reduced and efficiency improves.

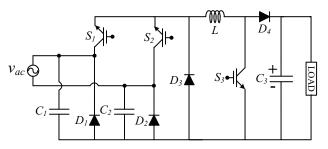

# 4.6 A bridgeless integrated PFC converter for automotive applications

The authors in [29] proposed a bridgeless integrated PFC converter for plug-in electric vehicles (PEVs) application as shown in Fig.15. In plug-in charging mode, the converter operates in boost as well as buck/boost mode. During the postive half cycle of the input voltage, the converter operates in the boost mode and in the negative half cycle of the input voltage, it operates as an inverting buck/boost converter. Moreover, in either boost or buck/boost mode, two semiconductor devices are in the current path similar to other bridgeless converters. Therefore, efficiency of the converter will be similar to that of the other existing bridgeless converters. Apart from plug-in charging mode, this converter works in other modes of vehicles, i.e., propulsion and regenerative braking.

The comparative study of bridgeless buck/boost converters has been conducted based on the number of components and the number of semiconductor devices that come in current path during switch-on and switch-off conditions shown in Table 5. The voltage conversion ratio of each topology has been shown in Table 6.

## 5 Conclusions

In this study, a family of single-phase non-isolated bridgeless boost, buck and buck/boost PFC converters has been reviewed along with their relative merits and drawbacks. These topologies are operated in either continuous conduction mode (CCM) or discontinuous conduction mode (DCM). CCM operation of the converter is used for high power applications, e.g., electric vehicle charging, DC drive systems, etc. CCM operation with soft switching methods can be used for high power applications with higher efficiency. On other hand, DCM operation is used for low power applications and high efficiency requirements. In some bridgeless topologies, coupled inductors are utilized to reduce the input current ripple as well as the magnetic size. Moreover, reduction in input current ripple leads to a lower size EMI filter, which results in a reduced overall converter size.

### 6 References

- 'Electromagnetic compatibility (EMC)-part 3-2: Limits- limits for harmonic current emissions (equipment input current 16 A per phase).

- 2 Singh, A.K., Pathak, M.K., Rao, Y.S. 'A multi-device front-end power factor converter for EV battery charger'. In 3rd International Conference on Computational Intelligence Communication Technology (CICT)., 2017. pp. 1–6

- Marxgut, C., Krismer, F., Bortis, D., Kolar, J.W.: 'Ultraflat interleaved triangu-3 lar current mode (TCM) single-phase PFC rectifier', IEEE Transactions on Power *Electronics*, 2014, **29**, (2), pp. 873–882 Musavi, F., Edington, M., Eberle, W., Dunford, W.G.: 'Evaluation and effi-

- 4 ciency comparison of front end ac-dc plug-in hybrid charger topologies', IEEE Transactions on Smart Grid, 2012, 3, (1), pp. 413-421

- Jang, Y., Jovanovic, M.M.: 'Interleaved boost converter with intrinsic voltagedoubler characteristic for universal-line PFC front end', IEEE Transactions on Power Electronics, 2007, 22, (4), pp. 1394-1401

- Singh, A.K., Pathak, M.K.: 'Single-phase bidirectional ac/dc converter for plug-in electric vehicles with reduced conduction losses', IET Power Electronics, 2018, 11, (1), pp. 140-148

- Pahlevaninezhad, M., Das, P., Drobnik, J., Jain, P.K., Bakhshai, A.: 'A ZVS interleaved boost ac/dc converter used in plug-in electric vehicles', IEEE Transactions on Power Electronics, 2012, 27, (8), pp. 3513-3529

- Suzdalenko, A., Zakis, J.: 'Single-loop current sensorless control for half-bridge based ac/dc converter', IETE Technical Review, 2016, 33, (6), pp. 662-673

- Aggeler, D., Canales, F., Zelaya, H., Parra, D.L., Coccia, A., Butcher, N., et al. 'Ultra-fast dc-charge infrastructures for ev-mobility and future smart grids'. In IEEE PES Innovative Smart Grid Technologies Conference Europe (ISGT Europe)., 2010. pp. 1-8

- Chen, J., Maksimovic, D., Erickson, R.W.: 'Analysis and design of a low-stress buck-boost converter in universal-input PFC applications', IEEE Transactions on Power Electronics, 2006, 21, (2), pp. 320-329

- Zane, R., Maksimovic, D.: 'Nonlinear-carrier control for high-power-factor rec-11 tifiers based on up-down switching converters', IEEE Transactions on Power Electronics, 1998, 13, (2), pp. 213–221

- Singh, B., Singh, S., Chandra, A., Al.Haddad, K.: 'Comprehensive study of single-12 phase ac-dc power factor corrected converters with high-frequency isolation', IEEE Transactions on Industrial Informatics, 2011, 7, (4), pp. 540-556

- Tang, Y., Zhu, D., Jin, C., Wang, P., Blaabjerg, F.: 'A three-level quasi-two-stage 13 single-phase PFC converter with flexible output voltage and improved conversion efficiency', IEEE Transactions on Power Electronics, 2015, 30, (2), pp. 717–726

- Huber, L., Jang, Y., Jovanovic, M.M. 'Performance evaluation of bridgeless PFC 14 In APEC 07 - Twenty-Second Annual IEEE Applied Power boost rectifiers'. Electronics Conference and Exposition., 2007. pp. 165-171

- Choi, W.Y., Kwon, J.M., Kim, E.H., Lee, J.J., Kwon, B.H.: 'Bridgeless boost rectifier with low conduction losses and reduced diode reverse-recovery problems', IEEE Transactions on Industrial Electronics, 2007, 54, (2), pp. 769–780

- Musavi, F., Eberle, W., Dunford, W.G.: 'A high-performance single-phase bridgeless interleaved PFC converter for plug-in hybrid electric vehicle battery chargers', IEEE Transactions on Industry Applications, 2011, 47, (4), pp. 1833–1843

- 17 Wei, W., Hongpeng, L., Shigong, J., Dianguo, X. 'A novel bridgeless buckboost pfc converter'. In IEEE Power Electronics Specialists Conference., 2008. pp. 1304–1308 Sabzali, A.J., Ismail, E.H., Al.Saffar, M.A., Fardoun, A.A.: 'New bridgeless DCM

- 18 sepic and Cuk PFC rectifiers with low conduction and switching losses', IEEE Transactions on Industry Applications, 2011, 47, (2), pp. 873-881

- Alam, M., Eberle, W., Gautam, D.S., Botting, C.: 'A soft-switching bridgeless ac -dc power factor correction converter', IEEE Transactions on Power Electronics, 2017, **32**, (10), pp. 7716–7726

- Liu, Y., Smedley, K. 'A new passive soft-switching dual-boost topology for power 20 factor correction'. In Power Electronics Specialist Conference, 2003. PESC '03. 2003 IEEE 34th Annual. vol. 2., 2003. pp. 669–676 vol.2

- Ismail, E.H.: 'Bridgeless SEPIC rectifier with unity power factor and reduced 21 conduction losses', IEEE Transactions on Industrial Electronics, 2009, 56, (4), pp. 1147–1157

- Fardoun, A.A., Ismail, E.H., Khraim, N.M., Sabzali, A.J., Al.Saffar, M.A.: 22 Bridgeless high-power-factor buck-converter operating in discontinuous capacitor voltage mode', IEEE Transactions on Industry Applications, 2014, 50, (5), pp. 3457-3467

- Jang, Y., JovanoviÄĞ, M.M.: 'Bridgeless high-power-factor buck converter', IEEE 23 Transactions on Power Electronics, 2011, 26, (2), pp. 602-611

- Gabri, A.M.A., Fardoun, A.A., Ismail, E.H.: 'Bridgeless PFC-modified SEPIC rectifier with extended gain for universal input voltage applications', IEEE Transactions on Power Electronics, 2015, 30, (8), pp. 4272-4282

- Mahdavi, M., Farzanehfard, H.: 'Bridgeless SEPIC PFC rectifier with reduced components and conduction losses', IEEE Transactions on Industrial Electronics, 2011, **58**, (9), pp. 4153–4160 Yang, J.W., Do, H.L.: 'Bridgeless sepic converter with a ripple-free input current',

- 26 IEEE Transactions on Power Electronics, 2013, 28, (7), pp. 3388–3394

- Bist, V., Singh, B.: 'An adjustable-speed PFC bridgeless buck-boost converter-fed BLDC motor drive', IEEE Transactions on Industrial Electronics, 2014, 61, (6), pp. 2665–2677

- Kong, P.Y., Aziz, J.A., Sahid, M.R., Yao, L.W. 'A bridgeless PFC converter for on-28 board battery charger'. In IEEE Conference on Energy Conversion (CENCON)., 2014. pp. 383-388

- 29 Dusmez, S., Khaligh, A.: 'A charge-nonlinear-carrier-controlled reduced-part single-stage integrated power electronics interface for automotive applications', IEEE Transactions on Vehicular Technology, 2014, 63, (3), pp. 1091-1103

- 30 Kong, P., Wang, S., Lee, F.C.: 'Common mode emi noise suppression for bridgeless pfc converters', IEEE Transactions on Power Electronics, 2008, 23, (1), pp. 291-297

- de Souza, A.F., Barbi, I. 'A new zcs quasi-resonant unity power factor rectifier with reduced conduction losses'. In Proceedings of PESC '95- Power Electronics 31 Specialist Conference. vol. 2., 1995. pp. 1171-1177 vol.2

- de Souza, A.F., Barbi, I.: 'A new ZVS-PWM unity power factor rectifier with 32 reduced conduction losses', IEEE Transactions on Power Electronics, 1995, 10, (6), pp. 746-752

- 33 Chien-Ming Wang: 'A novel zero-voltage-switching pwm boost rectifier with high power factor and low conduction losses', IEEE Transactions on Industrial Electronics, 2005, 52, (2), pp. 427-435

- Chien-Ming Wang: 'A novel ZCS-PWM power-factor preregulator with reduced conduction losses', IEEE Transactions on Industrial Electronics, 2005, 52, (3), pp. 689–700

- Kim, I., Bose, B.K.: 'New ZCS turn-on and ZVS turn-off unity power factor pwm 35 rectifier with reduced conduction loss and no auxiliary switches', IEE Proceedings Electric Power Applications, 2000, 147, (2), pp. 146-152

- Zhao, B., Abramovitz, A., Smedley, K.: 'Family of bridgeless buck-boost PFC rectifiers', IEEE Transactions on Power Electronics, 2015, 30, (12), pp. 6524-6527

- Tse, C.K., Chow, M.H.L. 'New single-stage power-factor-corrected regulators operating in discontinuous capacitor voltage mode'. In 28th Annual IEEE Power 37 Electronics Specialists Conference. Formerly Power Conditioning Specialists Conference 1970-71. Power Processing and Electronic Specialists Conference 1972. vol. 1., 1997. pp. 371-377 vol.1

- Grigore, V., Kyyra, J.: 'High power factor rectifier based on buck converter oper-38 ating in discontinuous capacitor voltage mode', IEEE Transactions on Power Electronics, 2000, 15, (6), pp. 1241-1249

- de Melo, P.F., Gules, R., Romaneli, E.F.R., Annunziato, R.C.: 'A modified SEPIC converter for high-power-factor rectifier and universal input voltage applications', IEEE Transactions on Power Electronics, 2010, 25, (2), pp. 310-321

- 40 Do, H.L.: 'Soft-switching SEPIC converter with ripple-free input current', IEEE Transactions on Power Electronics, 2012, 27, (6), pp. 2879–2887

- Zhao, Y., Li, W., Deng, Y., He, X.: 'Analysis, design, and experimentation of an iso-41 lated ZVT boost converter with coupled inductors', IEEE Transactions on Power Electronics, 2011, 26, (2), pp. 541-550

- Kotny, J.L., Margueron, X., Idir, N.: 'High-frequency model of the coupled inductors used in EMI filters', IEEE Transactions on Power Electronics, 2012, 27, (6), pp. 2805-2812