### Advanced Noise-Shaping Data Conversion Techniques

by

Lu Jie

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical and Computer Engineering) in the University of Michigan 2021

Doctoral Committee:

Professor Michael Flynn, Chair Assistant Professor Hun-Seok Kim Professor Scott Mahlke Associate Professor Zhengya Zhang Lu Jie

jielu@umich.edu

ORCID: 0000-0001-5046-3917

© Lu Jie 2021

## **Table of Contents**

| List of Tables                                         | iv |

|--------------------------------------------------------|----|

| List of Figures                                        | v  |

| List of Appendices                                     | ix |

| Abstract                                               | x  |

| Chapter 1 Fundamentals of Noise-Shaping Data Converter | 1  |

| 1.1 Concept and Needs of Data Conversion               | 1  |

| 1.2 Main Specifications and Figure of Merit            | 2  |

| 1.3 Basic Concept of Noise-Shaping                     | 4  |

| 1.4 Common Noise-Shaping Converter Architectures       | 7  |

| 1.5 Fundamental Limitations and Trade-offs             | 10 |

| Chapter 2 Nested Noise-Shaping Converter               | 13 |

| 2.1 Different Forms of Noise Transfer Function         | 13 |

| 2.2 Realizing Cascaded NTF by Nested Noise-Shaping     | 15 |

| A. Cascading Loop Filter                               | 15 |

| B. Nested Structure                                    | 16 |

| 2.3 A Design Example of Nested Noise-Shaping SAR ADC   | 19 |

| A. Architecture                                        | 19 |

| B. Implementation                                      | 20 |

| C. Silicon Results                                     | 26 |

| Chapter 3 Time-Interleaved Noise-Shaping Converter     | 31 |

| 3.1 Basic Concept of Time-Interleaving                 | 31 |

| 3.2 Interleaving of Noise-Shaping System                          | 32 |

|-------------------------------------------------------------------|----|

| A. Direct Interleaving                                            | 32 |

| B. Inter-channel Feedback and Causality Restrictions              | 33 |

| C. Midway Feedback and Multi-Phase Conversion                     | 34 |

| D. Non-Idealities of Interleaving                                 | 36 |

| 3.3 A Design Example of Interleaved Noise-Shaping SAR ADC         | 37 |

| A. Architecture                                                   | 37 |

| B. Implementation                                                 | 42 |

| C. Addressing Non-Idealities                                      | 45 |

| D. Silicon Results                                                | 50 |

| Chapter 4 CT-DT Hybrid Noise-Shaping Converter                    | 54 |

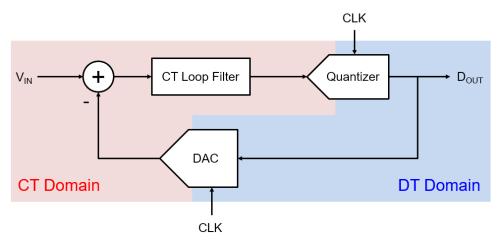

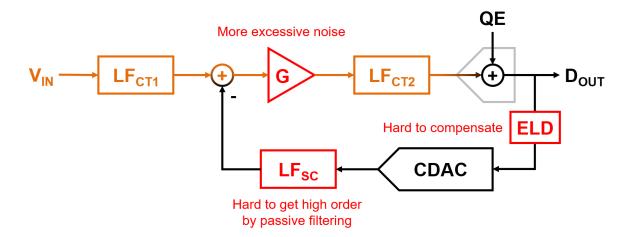

| 4.1 Continuous-Time Noise-Shaping System: Advantages and Problems | 54 |

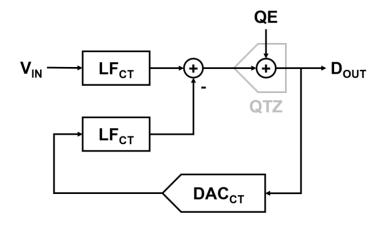

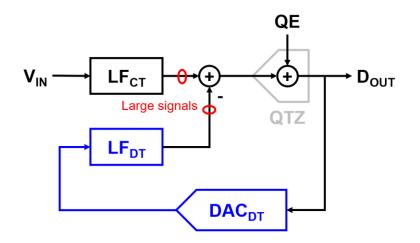

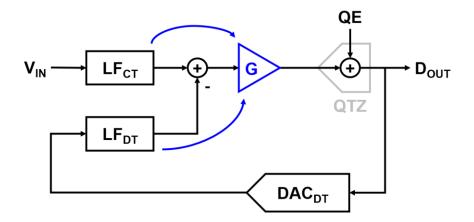

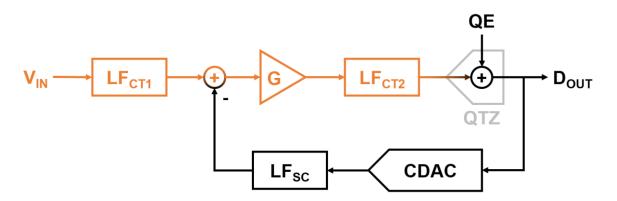

| 4.2 CT-DT Hybrid Noise-Shaping System                             | 57 |

| A. Basic Concepts                                                 | 57 |

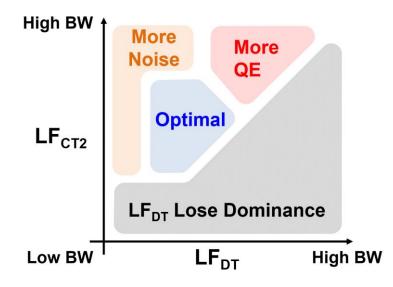

| B. System Trade-offs                                              | 60 |

| C. Concerns for High Order Noise-Shaping                          | 61 |

| 4.3 A Design Example of Hybrid Noise-Shaping Converter            | 63 |

| A. Improved TINS SAR Quantizer                                    | 63 |

| B. Architecture                                                   | 69 |

| C. Implementation                                                 | 70 |

| D. Silicon Results                                                | 74 |

| Chapter 5 Advanced Circuit-Level Techniques for Data Converters   | 79 |

| 5.1 Parasitic Pre-Charging                                        | 79 |

| 5.2 Dynamic Bandwidth Amplification                               | 82 |

| 5.3 Ring Buffer                                                   | 87 |

| Chapter 6 Conclusions                                             | 91 |

| Appendices                                                        | 93 |

| Bibliography                                                      | 98 |

### List of Tables

| Table 1 Noise Performance of RA2 |    |

|----------------------------------|----|

| Table 2 Comparison Table         |    |

| Table 3 Comparison Table         | 53 |

| Table 4 Main Design Parameters   | 71 |

| Table 5 Comparison Table         |    |

# List of Figures

| Fig. 1 A general model of an ADC                                                     | 2         |

|--------------------------------------------------------------------------------------|-----------|

| Fig. 2 Spectrum effects of Oversampling and Noise-Shaping                            | 5         |

| Fig. 3 Signa block diagram of a common NS system                                     | 6         |

| Fig. 4 Sigma-Delta ADC of conventional architecture                                  | 7         |

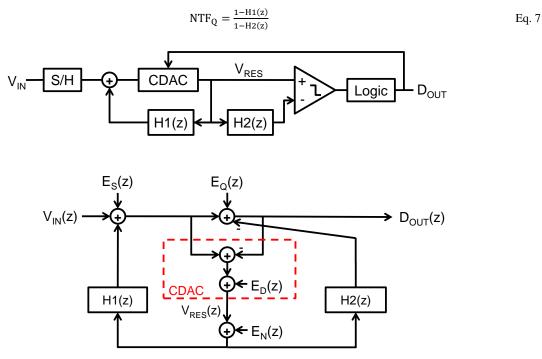

| Fig. 5 Generalized behavioral (top) and signal (bottom) model of NS SAR              |           |

| Fig. 6 Power efficiency and area comparison between conventional SD ADC and I        | NS SAR.   |

|                                                                                      | 9         |

| Fig. 7 Trade-offs between in-band SNR, OSR and NTF's order                           | 11        |

| Fig. 8 Different DT filter implementation forms                                      | 13        |

| Fig. 9 Maximum FoM versus NTF order for different NTF form (yield = $95\%$ )         | 14        |

| Fig. 10 EF NS system with loop filter in cascaded FIR form                           | 15        |

| Fig. 11 SD ADC with noise-shaped quantizer                                           | 16        |

| Fig. 12 SD ADC with Noise Coupling (EF based NS quantizer)                           | 17        |

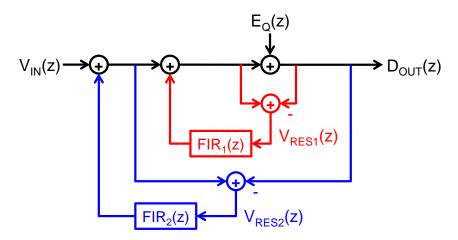

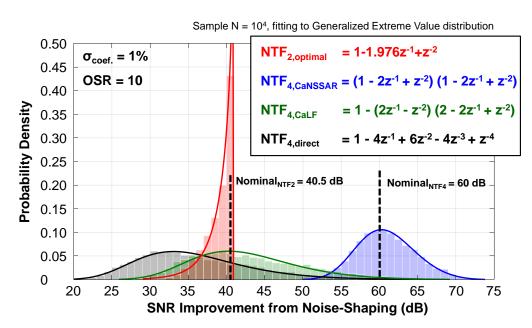

| Fig. 13 Nested Error-Feedback Noise-Shaping System.                                  | 17        |

| Fig. 14 Performance distributions for four different NTFs for a 1% 1-sigma co        | efficient |

| variation                                                                            |           |

| Fig. 15 A straightforward architecture of the Nested NS SAR                          | 19        |

| Fig. 16 Realizing passive summation by a serial capacitor.                           | 20        |

| Fig. 17 Schematic of the example Nested NS SAR ADC.                                  |           |

| Fig. 18 Cross-differential sampling of FIR capacitors                                | 22        |

| Fig. 19 FIR <sub>1</sub> switches timing. FIR <sub>2</sub> operates with same timing | 22        |

| Fig. 20 Operation timing                                                             |           |

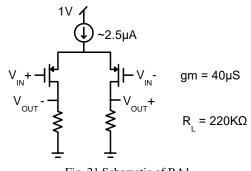

| Fig. 21 Schematic of RA1                                                             |           |

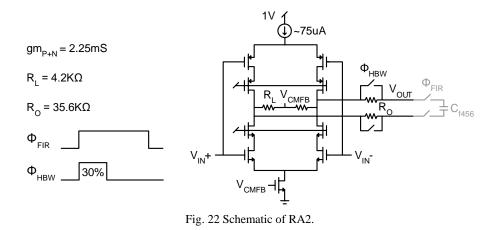

| Fig. 22 Schematic of RA2                                                             | 25        |

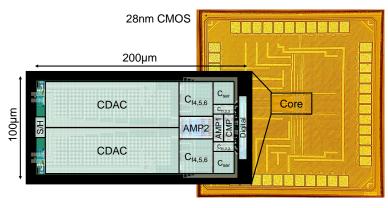

| Fig. 23 Die photo                                                                    |           |

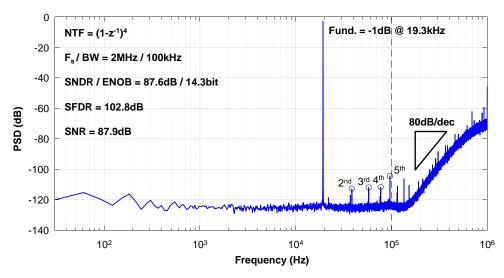

| Fig. 24 FFT for single-tone test (64K samples Hann window, 16x averaging)            |           |

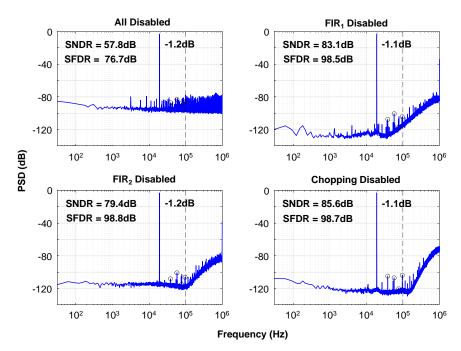

| Fig. 25 Single-tone tests for different configurations.                              | 27       |

|--------------------------------------------------------------------------------------|----------|

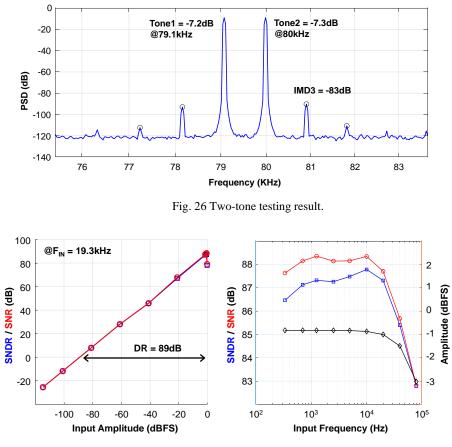

| Fig. 26 Two-tone testing result.                                                     | 28       |

| Fig. 27 Measured performance versus input amplitude and frequency                    | 28       |

| Fig. 28 Measured performance versus input amplitude and frequency                    | 28       |

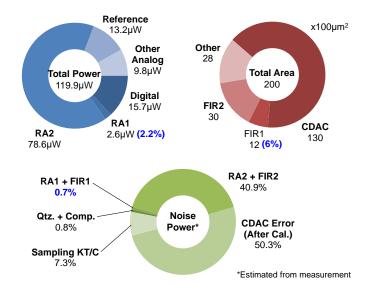

| Fig. 29 Power, area and noise (estimated) breakdown.                                 | 29       |

| Fig. 30 Time-interleaved ADC (top) and timing diagram (bottom).                      | 31       |

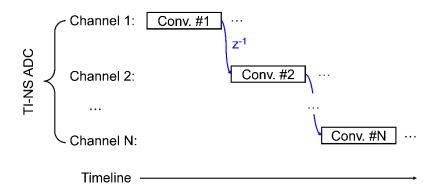

| Fig. 31 Direct interleaving of NS ADCs                                               | 32       |

| Fig. 32 Comparison of the original NTF for single NS SAR ADC (top) and the re        | peating  |

| pattern of the interleaved NTF (bottom).                                             | 33       |

| Fig. 33 Inter-channel feedback and the possible non-causal paths                     | 34       |

| Fig. 34 This causal inter-channel feedback loses the throughput advantages of interl | eaving.  |

|                                                                                      | 34       |

| Fig. 35 Timing diagram for a time-interleaved noise-shaping ADC with no              | single   |

| interleaving period $(z - 1)$ delay                                                  | 35       |

| Fig. 36 Midway Feedback with Multi-Phase Conversion.                                 | 36       |

| Fig. 37 Output spectrum due to channel mismatch (4x TI as example)                   | 36       |

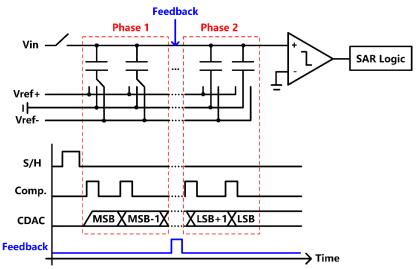

| Fig. 38 Multi-phase division of SAR ADC (2-phase example)                            | 38       |

| Fig. 39 Channel signal model with injected midway feedback signal                    | 38       |

| Fig. 40 Midway Error Feedback and its signal model (2nd order case as example).      | 39       |

| Fig. 41 Potential overload caused by feedback injection                              | 40       |

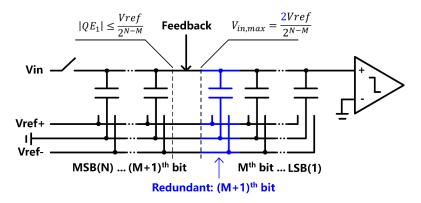

| Fig. 42 A redundant bit enlarges the quantization range.                             | 41       |

| Fig. 43 Comparison of an aggressive NTF and a mild NTF                               | 41       |

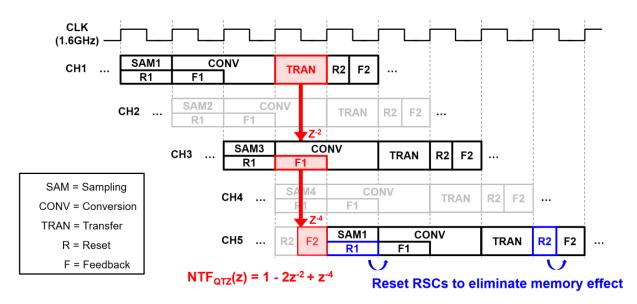

| Fig. 44 The example design's timing diagram (top) and signal model (bottom)          | 42       |

| Fig. 45 Summing pre-amplifier implementation of EF.                                  | 43       |

| Fig. 46 The pre-amplifier and CDAC form a Virtual CDAC that realizes an equ          | iivalent |

| feedback injection.                                                                  | 43       |

| Fig. 47 Summing pre-amplifier schematic                                              | 44       |

| Fig. 48 Actual ADC timing sequence.                                                  | 45       |

| Fig. 49 Signal model considering noise and gain variation.                           | 46       |

| Fig. 50 Signal model considering noise and gain variation.                           | 48       |

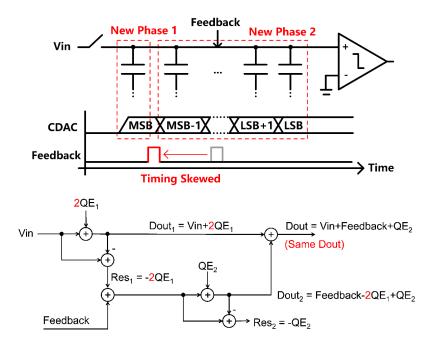

| Fig. 51 Feedback timing skew has no effect on the system behavior                    | 49       |

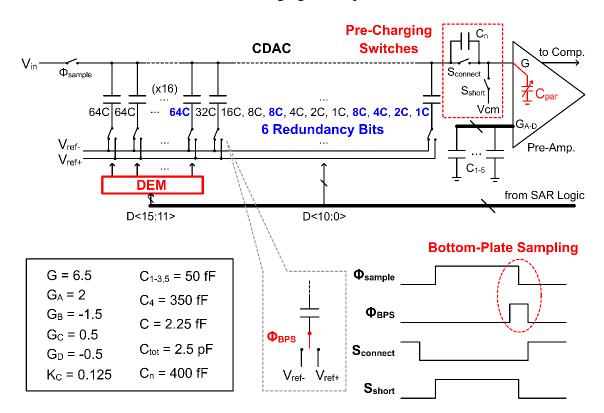

| Fig. 52 DEM, BPS and Parasitic Pre-Charging technique enhance linearity 50              |

|-----------------------------------------------------------------------------------------|

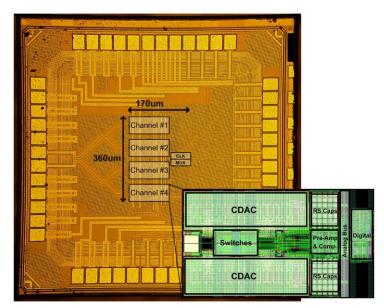

| Fig. 53 Die photo and layout zoomed in51                                                |

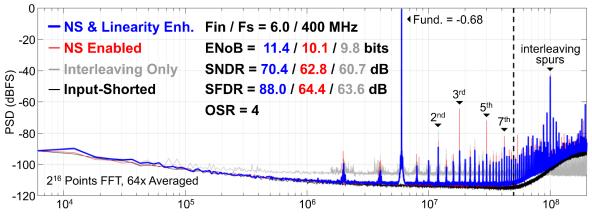

| Fig. 54 Measured output spectrum for different configurations                           |

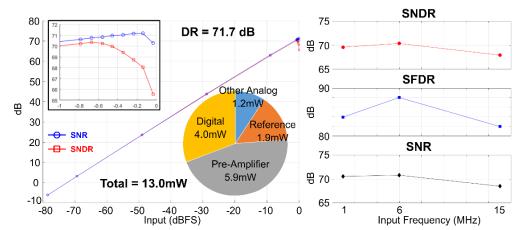

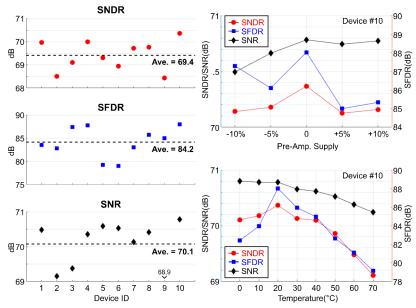

| Fig. 55 Measured SNR/SNDR versus input power, power breakdown (left), and               |

| performance versus input frequency (right)                                              |

| Fig. 56 Measured performance of 10 devices (left), and measured performance under       |

| supply voltage, and temperature variation (right)                                       |

| Fig. 57 Signal model of a common CT NS ADC55                                            |

| Fig. 58 CT Loop and its equivalent DT Loop55                                            |

| Fig. 59 A transformed signal model of CT NS converter                                   |

| Fig. 60 Replacing the CT loop filter with a DT counterpart                              |

| Fig. 61 Relocate the gain of the filters59                                              |

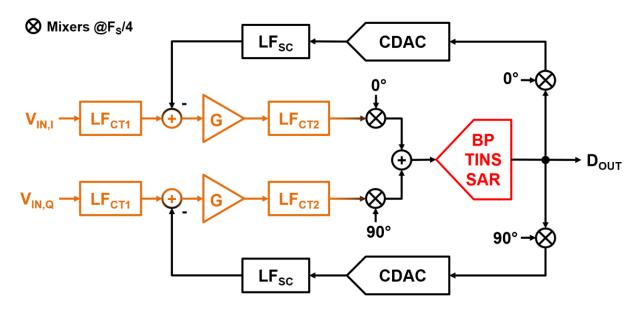

| Fig. 62 Proposed CT-DT hybrid NS converter                                              |

| Fig. 63 Effects on the CT and DT loop filter's bandwidth60                              |

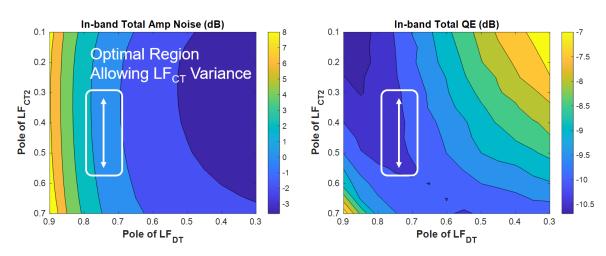

| Fig. 64 An example of loop design trade-off61                                           |

| Fig. 65 Potential problems in high order hybrid NS system                               |

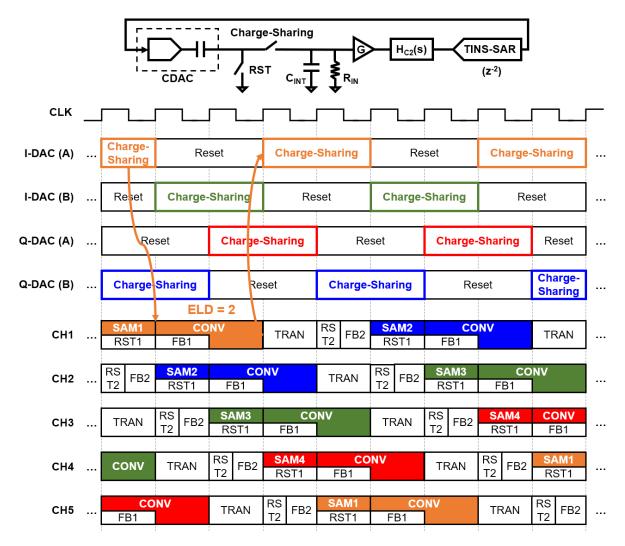

| Fig. 66 Timing diagram of the TINS SAR in section 3.3                                   |

| Fig. 67 The critical path in TINS SAR 64                                                |

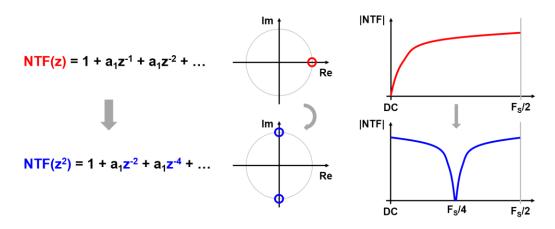

| Fig. 68 z to z <sup>2</sup> transformation                                              |

| Fig. 69 Modified TINS SAR with bandpass NTF.                                            |

| Fig. 70 Interleaving artifacts under bandpass input with different TI configurations 66 |

| Fig. 71 The large gm requirement for the summing pre-amp in TINS SAR                    |

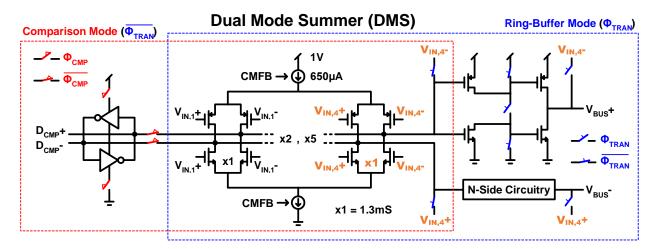

| Fig. 72 Schematic of the Dual Mode Summer67                                             |

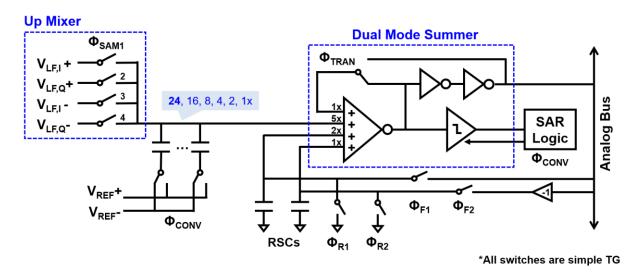

| Fig. 73 Schematic of the improved TINS SAR design                                       |

| Fig. 74 Timing diagram of the TINS SAR 69                                               |

| Fig. 75 Architecture of the example CT-DT Hybrid NS converter                           |

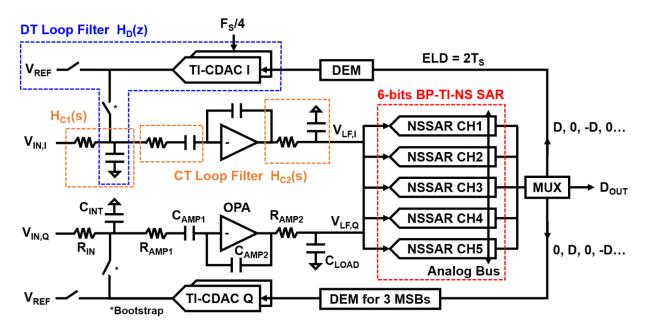

| Fig. 76 Schematic of the example CT-DT Hybrid NS ADC.                                   |

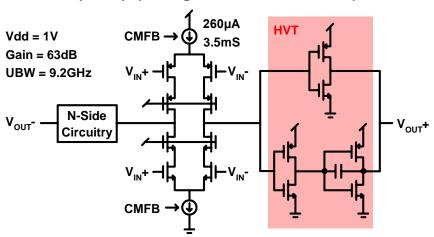

| Fig. 77 Schematic of the op-amp in this design72                                        |

| Fig. 78 Operation timing details72                                                      |

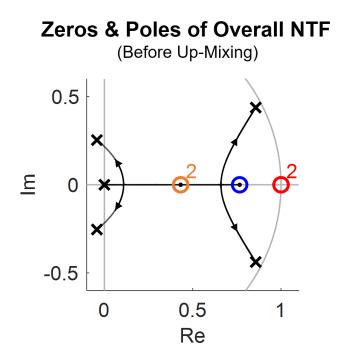

| Fig. 79 Zeros and poles location of the NTF (before up mixing)73                        |

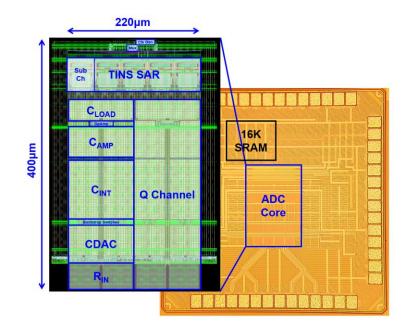

| Fig. 80 Die photo and layout zoomed in74                                                |

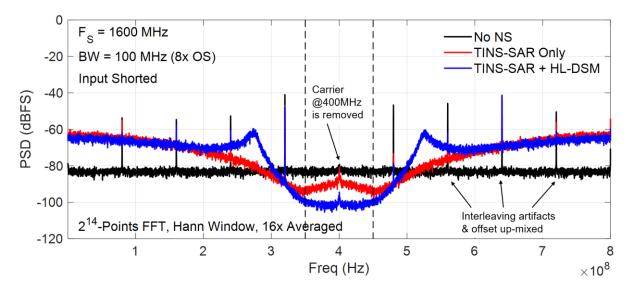

| Fig. 81 Input shorted noise floor under with NS configuration75                           |

|-------------------------------------------------------------------------------------------|

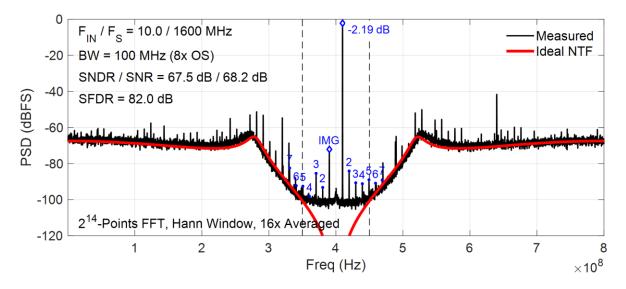

| Fig. 82 Single-tone testing result75                                                      |

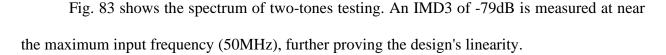

| Fig. 83 Two-tone testing result76                                                         |

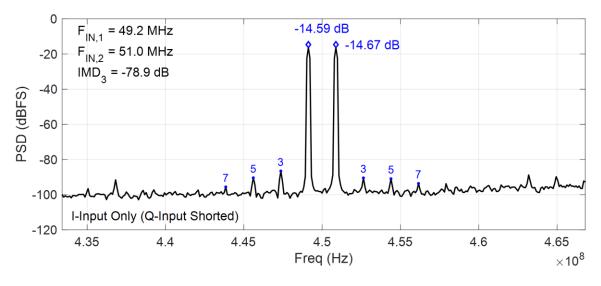

| Fig. 84 Measured performance over input magnitudes (left) and frequencies (right) 76      |

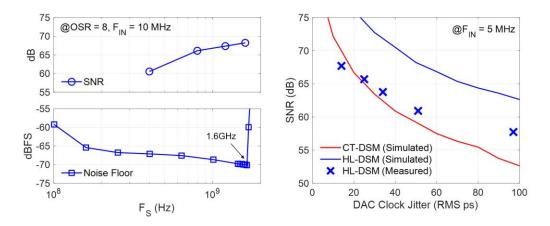

| Fig. 85 Measured performance over sampling rate (left) and with DAC jitter (right) 77     |

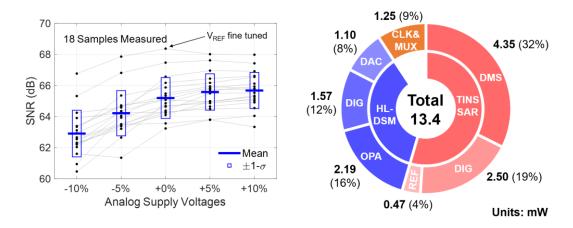

| Fig. 86 Multi-device measurement over analog supply voltage variation (left), and power   |

| breakdown (right)                                                                         |

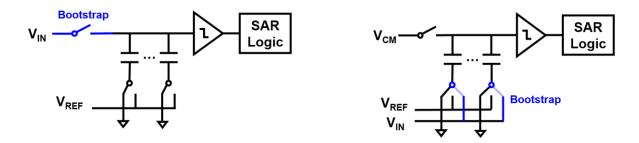

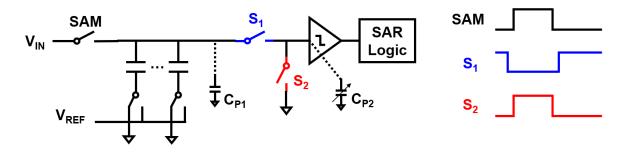

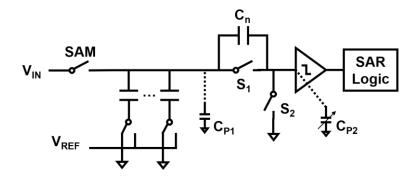

| Fig. 87 SAR converter with top-plate sampling (left) and bottom-plate sampling (right) 80 |

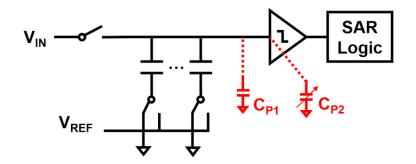

| Fig. 88 The two kinds of parasitic caps in top-plate sampling SAR converter               |

| Fig. 89 Basic concept of Parasitic Pre-Charging technique                                 |

| Fig. 90 Adding a noise limiting capacitor                                                 |

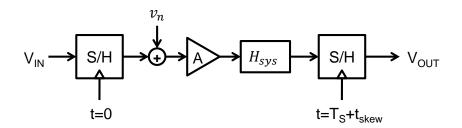

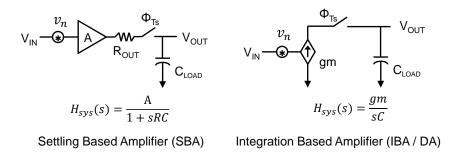

| Fig. 91 Generalized signal model of DT amplifier                                          |

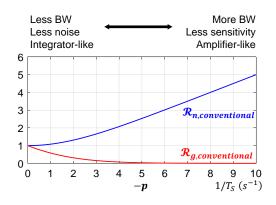

| Fig. 92 Conventional DT amplifiers                                                        |

| Fig. 93 Noise-robustness tradeoff for a conventional DT amplifier                         |

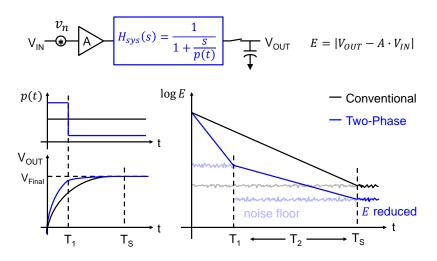

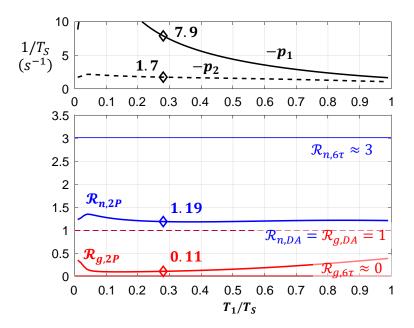

| Fig. 94 Amplification progress (step response) of two-phase settling amplifier            |

| Fig. 95 Optimal pole locations (top) and metrics (bottom) of two-phase settling amplifier |

| versus phase-division ratio                                                               |

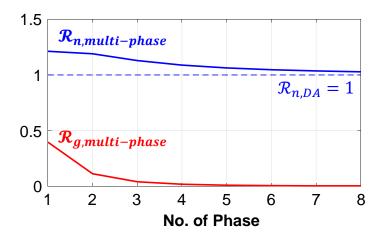

| Fig. 96 Theoretical (optimal) performance versus number of settling phases                |

| Fig. 97 Basic schematic of Ring Amplifier                                                 |

| Fig. 98 Classic SC gain block by Ring Amplifier                                           |

| Fig. 99 Schematic of Ring Buffer                                                          |

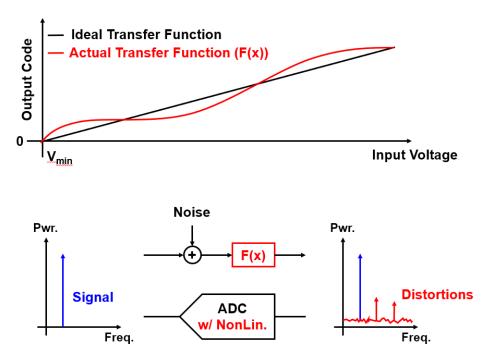

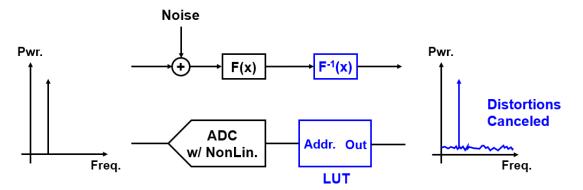

| Fig. 100 The nonlinearity of ADC's characteristic curve (top) and the distortions induced |

| (bottom)                                                                                  |

| Fig. 101 LUT based post-calibration cancels out the distortions caused by ADC's           |

| nonlinearity                                                                              |

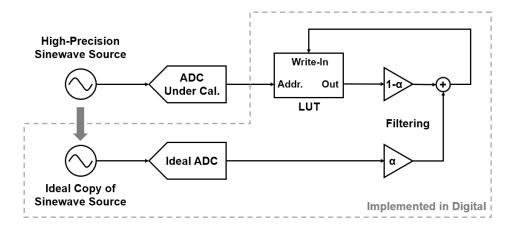

| Fig. 102 A practical LUT generation method based on sinewave input testing                |

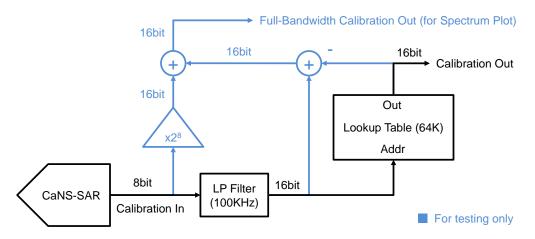

| Fig. 103 LUT based calibration system (applied on the NS SAR in section 2.3 as example)   |

|                                                                                           |

# List of Appendices

| A. Assumptions for the Noise-Shaping SAR Model Used in Section 2.1  | . 93 |

|---------------------------------------------------------------------|------|

| B. LUT Based Linearity Post-Calibration for Noise-Shaping Converter | . 95 |

#### Abstract

The rapidly increasing digital device market is creating a huge demand for Data Conversion. In high-resolution data conversion applications, noise-shaping techniques are essential. This thesis first goes through the fundamentals of data conversion and noise-shaping techniques, and then discusses the latest advanced noise-shaping techniques that further boost data converter performance.

Three new noise-shaping techniques (architectures) are introduced. The first technique boosts the order of the noise-shaping system. A system-level approach is used to achieve high-order noise-shaping with enhanced robustness. A prototype noise-shaping SAR ADC is designed and measured. This design is the first 4th-order noise-shaping SAR ADC published.

The second technique effectively increases the bandwidth of noise-shaping data converters using a time-interleaving framework. A prototype time-interleaved noise-shaping SAR ADC is designed and measured to illustrate the technique. This prototype has the highest bandwidth among noise-shaping SAR ADCs to date.

The final technique aims to solve some inherent problems in continuous-time noiseshaping systems. A Continuous Time - Discrete Time (CT-DT) hybrid noise-shaping architecture is introduced, which adopts the advantages of both conventional CT and DT structures. A prototype ADC, showing benefits of tuning-free operation and high tolerance to non-idealities.

#### **Chapter 1 Fundamentals of Noise-Shaping Data Converter**

#### **1.1** Concept and Needs of Data Conversion

In electrical signal processing, *Data Conversion* generally refers to the conversion between analog signals and digital signals. Analog signals can be loosely defined as signals continuous in both time-domain and value-domain. Most physical signals, such as voltage, current, temperature, and pressure, are analog signals. Digital signals, on the other hand, are eventually logical signals, which are discrete in time-domain and quantized in value-domain. In most electrical systems, digital signals are represented in two-states, known as binary digits (bits).

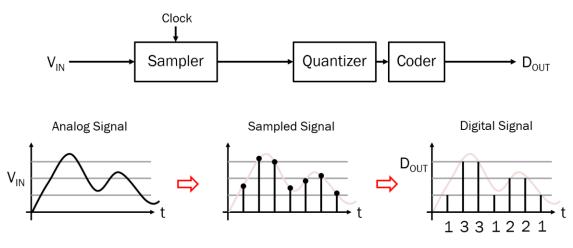

The conversion between analog and digital has two possible directions: from analog to digital, known as Analog to Digital (A/D) conversion; and from digital to analog, which is known as Digital to Analog (D/A) conversion. Hence, the system that realizes A/D conversion is called an Analog to Digital Converter (ADC), and one that does the opposite is called a Digital to Analog Converter (DAC). In this thesis, the discussions mainly focus on ADCs, but some techniques and conclusions are also applicable to DACs. To convert an analog signal to a digital one, an ADC generally consists of three functional parts (Fig. 1): 1) A sampler samples the analog signal at given moments, i.e., turns it into a discrete-time signal series; 2) A quantizer then quantizes the sampled signal and describe it with certain levels; The output signal is finally processed by 3) a coder, and is converted into a digital signal with the required coding format.

Fig. 1 A general model of an ADC

In recent decades, the requirements for data converters have been growing rapidly, as digitalization has become mainstream for almost all modern electrical systems. Digital systems have many advantages over conventional analog circuits, including high fidelity, high flexibility, and the capability to run sophisticated algorithms. Moreover, modern CMOS integration techniques have enabled low-cost but large-scale digital systems to be built, which are essential for sophisticalted electronic products. However, since real physical world signals are always analog, data converters are the necessary bridges so that digital systems can serve the analog world. Taking modern smartphones as an example, there are usually tens of data converters embedded in these devices, processing signals for audio, radio, video, and all kinds of sensing.

#### **1.2** Main Specifications and Figure of Merit

There are many specifications of data converters, but usually, the most important ones are the speed, accuracy, power, and cost.

There are a few specifications to measure the speed of an ADC. The most commonly used ones are the sampling rate and the analog bandwidth. The sampling rate is the number of samples that an ADC can take and digitize per second, in units of S/s. In most cases, the sampling rate will also be the output digital data rate. According to the Nyquist Sampling Theory, the sampling rate should be at least twice the signal bandwidth to prevent aliasing. The analog bandwidth is the input frequency range where the ADC gain loss is within 3dB. An ideal ADC should have an infinite analog bandwidth, meaning that signals at any frequency should be converted at a constant gain (even after aliasing). But in general, we consider an ADC as being good enough if the analog bandwidth is half the sampling rate. However, in some sub-sampling ADCs, the analog bandwidth can be much higher than that.

There are two sets of accuracy specifications for ADCs: Static Characteristics and Dynamic Characteristics. Static Characteristics focus on ADC's accuracy for DC inputs, such as offset, gain error, Differential-Non-Linearity (DNL), and Integral-Non-Linearity (INL). Dynamic Characteristics care more about the performance under AC inputs, including Signal-to-Noise Ratio (SNR), Signal-to-Noise-and-Distortion Ratio (SNDR), Spur-Free Dynamic Range (SFDR), and Effective Number of Bits (ENoB). For different applications, different metrics of accuracy are used. But in general, the AC performance is more conservative, as some dynamic effects can degrade the ADC with high-frequency inputs.

Power and cost are two important factors in many on-chip systems. For ADCs, the power is often quantified a energy per sample, because in many cases, the ADC power is proportional to the sampling rate. Cost is generally considered to be related to die area.

To compare two ADCs in overall performance, some Figure of Merits (FoM) are defined to characterize the specifications mentioned above with a single value. Two most commonly used FoMs are defined as:

$$FoM_{,Walden} = \frac{P}{2^{ENoB} BW \times 2}$$

Eq. 1

$$FoM_{Schreier} = SNR + 10 \log_{10} \left(\frac{BW}{P}\right)$$

Eq. 2

which are given by R. H. Walden [1] and R. Schreier [2], respectively. Here, P is the ADC power consumption in Watts; SNR is in dB; ENoB is in bits, and BW is the effective bandwidth in Hz.

Walden's definition assumes that the ADC's power per sample is proportional to the number of quantization levels, while Schreier's definition assumes that it is proportional to the SNR. In general, Walden's FoM is more reasonable for low-resolution ADCs (ENoB < 10), while Schreier FoM is more reasonable at a higher resolution (ENoB > 10) where the SNR is thermal noise limited (rather than quantization error limited). Under the topic of noise-shaping, this thesis focuses on high-resolution converters, thus FoMs is used in the following discussions.

A limitation of  $FoM_S$  is that it does not consider area (cost). Further, it ignores the robustness of the performance. To cover these, this thesis modifies Schreier and Sauerbrey's FoM [3] to consider both area and robustness:

$$FoM_{MS} = SNR_{worst} + 10\log_{10}\sqrt{\frac{BW}{P \times A \times OSR}}$$

Eq. 3

Here, SNR<sub>worst</sub> is the worst-case SNR in dB under PVT variation for a certain yield, BW is the effective bandwidth in Hz, P is the total power consumption in Watts, A is the area in mm<sup>2</sup>, and OSR is the over-sampling rate (will be explained later). This FoM definition assumes that the error is dominated by thermal noise ( $\propto P^{-1}BW$ ) and kT/C noise ( $\propto A^{-1}OSR^{-1}$ ). Assuming that both types of noise are comparable in a reasonable design, then both ( $P^{-1}BW$ ) and ( $A^{-1}OSR^{-1}$ ) should decrease by 3dB to increase SNR by 3dB.

#### **1.3 Basic Concept of Noise-Shaping**

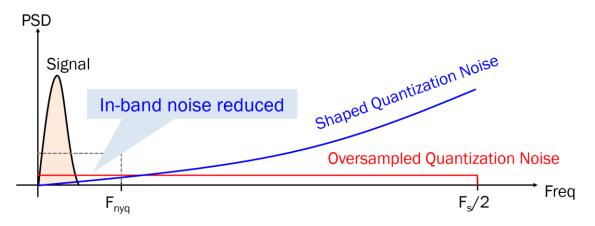

Noise-shaping (NS) is a system-level method aiming at increasing the Signal-to-Noise Ratio (SNR) of data converters. Here, "noise" mainly refers to the quantization errors from the quantization behavior of the converters; And "shaping" means changing the power spectrum distribution of the noise, by some mechanisms discussed later, such that the noise power in the desired frequency band is suppressed. NS is usually associated with another technique: Over-Sampling (OS). An OS data converter runs at a much higher sampling rate than the necessary rate

(i.e., the Nyquist rate, or twice of the maximum signal frequency [4]), where the ratio between is called the Over-Sampling Rate (OSR). OS brings two benefits: 1) it spreads out the quantization noise in the broader frequency range. Therefore, the noise spectrum density is reduced as the total quantization noise power is constant; 2) More importantly, it leaves many "blanks" on the spectrum as the input signal is at relatively low frequencies. And the in-band noise can be moved to the blanks using the NS technique, which further reduces the in-band noise power. Fig. 2 shows the spectrum effects of OS and NS techniques, respectively.

Fig. 2 Spectrum effects of Oversampling and Noise-Shaping

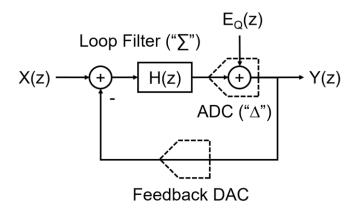

The realization of NS is often by some kind of feedback system. To better understand how these work, Fig. 3 shows an example of a simple NS system with feedback. Here, the quantizer is approximately modeled as an additive white noise source ( $E_Q$ ). This is a reasonable assumption in most real cases. Two extra blocks, including a loop filter (H) and a feedback DAC, are added to the system and form a simple feedback loop, which essentially shapes the noise.

Fig. 3 Signa block diagram of a common NS system.

For simplicity, we consider the case that the input X is already sampled and is discrete in time (i.e., DT signal). Applying feedback theory, we can derive the transfer functions of this system, from the input and the noise source to the final output respectively, given as:

$$Y(z) = X(z)STF(z) + E_Q(z)NTF(z)$$

Eq. 4

$$STF(z) = \frac{H(z)}{1+H(z)}$$

Eq. 5

$$NTF(z) = \frac{1}{1+H(z)}$$

Eq. 6

where the transfer function from input to output is called the Signal Transfer Function (STF), and the transfer function from noise to output is called the Noise Transfer Function (NTF). The results above indicate that the system will pass the input signal while suppressing the noise at the frequency where the loop gain (H) is large. Therefore, we can harness this by making the loop filter high-gain in the wanted band, thereby the in-band noise is effectively reduced, and the SNR is boosted.

The earliest NS data converters have first-order loop filters (i.e., an integrator) and 1-bit quantizers [5]. Therefore, people also name those converters as "Delta-Sigma" (or "Sigma-Delta") converters. In the later developments, higher-order loop filters and multi-bit quantizers are used. But the term Delta-Sigma is still used and can be regarded as an alternative name for NS techniques.

#### **1.4 Common Noise-Shaping Converter Architectures**

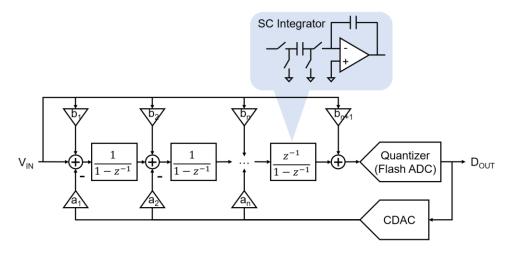

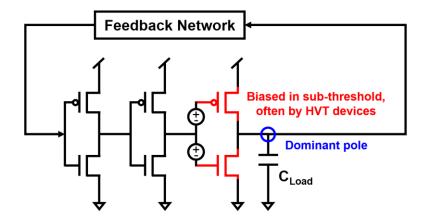

Although the signal models behind them may be quite similar, NS architectures vary greatly. For NS ADCs, the most conventional architecture is a block-to-block implementation of the signal model, where the loop filter is built with op-amps. Fig. 4 shows a generalized block diagram of the conventional Sigma-Delta (SD) ADC.

Fig. 4 Sigma-Delta ADC of conventional architecture.

Based on the loop filter's topology, there are a few sub-classes of this architecture (e.g., CIFF, CIFB, and something in between [6]). The loop filter can also work in either discrete-time (DT) mode or continuous-time (CT) mode. However, all of these can be essentially counted as variants of the same architecture. This kind of architecture is good for robustness and accuracy, mainly thanks to the high gain of op-amps which suppress most non-idealities. Nevertheless, as CMOS processes scale down, building high gain op-amps is getting harder. Moreover, in a sense, the op-amp's high gain is highly redundant, which means the design does not fully use the power and area.

On the other hand, recently some alternative architectures exhibit various advantages over the conventional ones. One of the most promising is the Noise-Shaping SAR architecture [7]. As a variant architecture of SAR, NS SAR adopts the advantages of SAR architecture, including lowpower, area-compact, and scaling-friendly circuits. And nearly a decade of development, NS-SAR can now achieve comparable SNR performance to conventional NS architectures. Fig. 5 shows a generalized block diagram of the NS SAR architecture. The main difference between it and a plain SAR ADC is the two extra loop filters inserted (H1 and H2), which process the residue (i.e., quantization errors,  $E_Q$ ) of the SAR conversion. The two feedback paths form a similar signal model to Fig. 3, and therefore realize NS effects. The NTF of this model can be derived as:

Fig. 5 Generalized behavioral (top) and signal (bottom) model of NS SAR.

Here, the feedback configuration with H1 is also named as Error-Feedback (EF) structure [8], while the configuration with H2 is called Cascaded-Integrator-Feed-Forward (CIFF). Eq. 7 implies that an FIR filter in H1 can place the zeros of NTF, while an FIR filter in H2 can place the poles instead. Generally, the zeros of the NTF is much more critical, so a pure EF based NS SAR is very attractive as it only requires an FIR filter with no integrator.

Note that the Error-Feedback structure can also be applied in the conventional Sigma-Delta architecture. However, it is much harder to extract the residue in conventional architecture. Thus

EF structure is not very practical for them [9]. On contract, a key advantage of the SAR ADC is that the residue can be precisely extracted, as it is naturally presented on the CDAC after each conversion. The availability of the residue enables NS SAR to be more flexible in realizing NS.

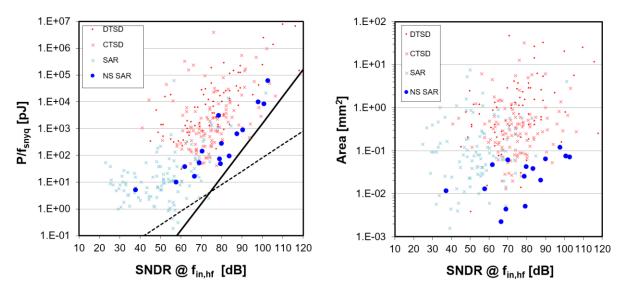

Fig. 6 gives an intuitive illustration of NS SAR architecture's advantages by comparing NS-SARs to the conventional Sigma-Delta ADCs (data from the ADC survey [10]). Obviously, NS SAR is much more power-efficient than the Sigma-Delta architecture, and is notably lower in cost (i.e., smaller in the area).

Fig. 6 Power efficiency and area comparison between conventional SD ADC and NS SAR.

Due to the notable advantages of NS SAR, the proposed techniques in this thesis are based (or partially based) on the NS SAR architecture. But some of the techniques are independent of the implementation and are also applicable to the other architectures.

Lastly, there is an interesting thing to mention: Although most NS systems are based on feedback, there are still some exceptional cases where NS can be achieved is open-loop. One of the examples is the Voltage Controlled Oscillator (VCO) based converter [11]. This kind of converter provides an inherent 1st-order NS. The open-loop nature leads to its simplicity in

circuitry and avoids any feedback stability concern. Therefore, it is usually used as a building block (e.g., the quantizer) in some advanced NS converter.

#### **1.5 Fundamental Limitations and Trade-offs**

The Noise-Shaping technique has some fundamental limitations. Some of these limitations are due to the nature of feedback systems. A general NS system shown is Fig. 3 is essentially a Single-Input-Single-Output (SISO) feedback system with a single loop, where the noise is recognized as a "disturbance" in classic control theory. By definition, NTF is equivalent to the sensitivity function (S) in this theory. Bode gives a well-known Sensitivity Integral for this kind of feedback system, and B. Wu extends it to the DT case [12]:

$$\int_{-\pi}^{\pi} \ln |S(e^{j\omega})| \, d\omega = \int_{-\pi}^{\pi} \ln |NTF(e^{j\omega})| \, d\omega = 2\pi \left( \sum \ln |p_k| - \ln \left| \lim_{z \to \infty} L(z) + 1 \right| \right)$$

Eq. 8

where L(z) is the loop filter, and  $p_k$  are the unstable poles. In most NS system, the loop filter is designed to be stable and has at least one more pole than zero. Besides, the NTF is even in general. Thus Eq. 8 can be further simplified as:

$$\int_{0}^{\pi} \ln|NTF(e^{j\omega})| \, d\omega = 0 \qquad \qquad \text{Eq. 9}$$

The integral above implies the first limitation: the area under the NTF curve, in log scale, is always a constant. Therefore, lowering the NTF at some frequencies inevitably raises the NTF in some other frequencies by the same amount in dB.

The second limitation is related to the maximum slope of the NTF. From filter theory, the roll-off rate of an N-th filter is approximately 20N dB per decade. This rule is also applicable to the slope of an NTF, which means that at least N-th order NTF is required to achieve a slope of 20N dB per decade.

Lastly, the maximum response amplitude of the NTF is also limited. This is because the quantizer in NS system is highly non-linear, and our additive noise model will fail if the input to

the quantizer is too large (which is also known as *quantizer overload*). Once that happens, the behavior of the whole NS system changes, increasing the in-band noise, and in some cases, becoming even unstable. A practical way to prevent this is to limit the NTF response to be lower than a specific threshold. But unfortunately, there isn't a precise (i.e., analytical) conclusion on this threshold. Usually, people use some rules of thumb for a rough design, and then optimize with simulation. One well-known rule of thumb is the (modified) Lee's rule [13]: A NS system (in the form of Fig. 3) with a 1-bit quantizer is likely to be stable if max(|NTF(z)|) < 1.5. And generally, increasing the number of quantizer levels can raise the threshold of the NTF.

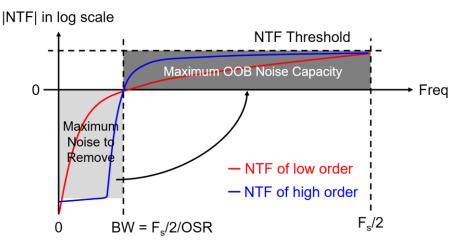

The three limitations above directly lead to some design trade-offs in a NS system. More specifically, the in-band SNR improvement, OSR, the NTF order, and the quantizer's resolution are tightly linked in an optimal NS system design. Fig. 7 illustrates such trade-offs intuitively.

Fig. 7 Trade-offs between in-band SNR, OSR and NTF's order

Due to the NTF threshold and given OSR, there is a limited area in the out-of-band region. And due to the Sensitivity Integral (Eq. 9), this area is equal to the noise area that we can remove in-band. So in an ideal case, where we can implement an infinite order of NTF, the maximum SNR improvement in-band can be calculated as:

$$\Delta SNR_{ideal} = 10 \log_{10}(NTF_{thres}) \times (OSR - 1)$$

Eq. 10

In practice, the order of NTF is finite. In such cases, it is hard to derive a simple expression for the SNR improvement, and usually, this can only be examined by numerical methods. Although some recent work [14] already derives some analytical conclusions about the optimal NTF under given constraints (i.e., NTF threshold, NTF order, and OSR), these optimal NTFs are often heavily rely on the coefficient precision, and thus are not very useful. In a practical design, the NTF is usually chosen to be sub-optimal so that it is less sensitive to the coefficients.

In the following chapters, we will go through three techniques extending the Noise-Shaping. The first technique (Chapter 2) intends to increase the system order, and reduces the cost and sensitivity. The second technique (Chapter 3) aims to improve the bandwidth of noise-shaping converters. The third technique (Chapter 4) further enhances the converter's robustness and practicability, while keeping the speed advantages. Finally in Chapter 5, we introduce some circuit-level techniques to enable better implementations.

#### **Chapter 2 Nested Noise-Shaping Converter**

#### **2.1 Different Forms of Noise Transfer Function**

We have learned from Section 1.5 that the SNR improvement by NS is related to the NTF and OSR. But it is less obvious that the form of NTF also matters a lot. In this chapter, different forms of NTF are compared, and then the Nested structure is naturally introduced. Later, an implementation of the Nested structure in a NS SAR is given, showing how this technique can be applied in practice. The following discussion is based on DT NS systems, but many conclusions apply to CT NS systems as well.

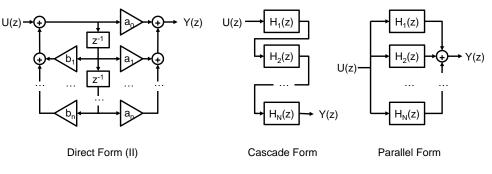

The NTF of a NS system essentially describes a filter applied to the quantization noise. In the field of filter implementation, there are three common structures for DT filters: Direct Form (type II), Cascade Form, and Parallel Form, as shown in Fig. 8. Similarly, the NTF can also be implemented with one of these three forms. Although all the forms are equivalent in sense of algebra, they are quite different in some practical concerns.

Fig. 8 Different DT filter implementation forms.

The direct form is the most straightforward one, and it can be easily constructed from the filter coefficients. However, the direct form has several inherent disadvantages. It needs the

greatest number of summing blocks and requires relatively large coefficient magnitudes, which increase the cost in terms of power and area. Also, the direct form suffers from high sensitivity to variation in coefficients, which means poor PVT robustness.

The cascade form is the most robust against coefficient variation and requires the smallest coefficients. Unlike the parallel form, the cascade form enables direct, independent control of each zero (pairs), and thus has even lower coefficient sensitivity than the parallel form [15]. Another advantage of the cascade form is that the later stages filter the preceding stages' noise, which reduces the overall in-band noise.

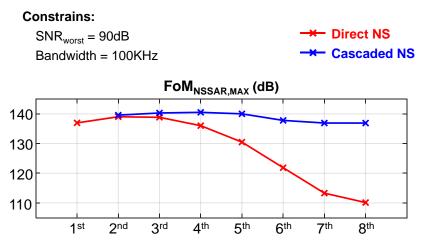

To show the difference between the direct and cascaded forms, a mathematical model of a NS SAR converter is built in this thesis to investigate the theoretical performance. This model considers the variation of NTF coefficients, and evaluates the performance using the modified FoM (see Section 1.2) by a Statistical method. Therefore we can exam the worst-case performance of a NS SAR converter with different orders and different forms of NTF. Fig. 9 shows the result of this modeling with given constraints. The details of the model can be found in Appendix A.

Fig. 9 Maximum FoM versus NTF order for different NTF form (yield = 95%).

We notice that for a certain SNR and BW (90dB and 100kHz in this example), the optimal FoM for the ADC with a direct-form NTF occurs for 2<sup>nd</sup>-order, while the peak for the cascade

form is with a 4<sup>th</sup>-order NTF. We also notice that a better FoM is possible with higher-order noiseshaping for the cascade form NTF, while direct form cannot provide as good a performance.

#### 2.2 Realizing Cascaded NTF by Nested Noise-Shaping

#### A. Cascading Loop Filter

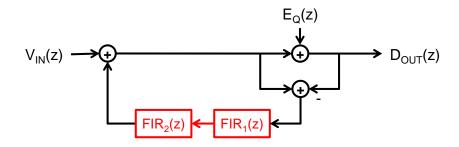

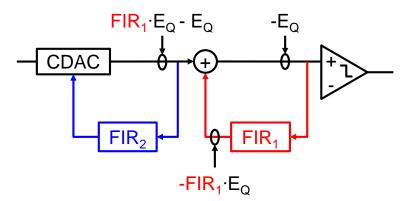

A straightforward "cascading" of an NS system might directly cascade the loop filter. Fig. 10 shows an example of cascading the loop filter in an Error-Feedback NS system. The cascade of FIR<sub>1</sub> and FIR<sub>2</sub> implements the loop filter.

Fig. 10 EF NS system with loop filter in cascaded FIR form.

Although such an implementation can reduce the magnitude of the filter coefficients, it does not preserve the ability to independently place the zeros of the NTF, which is an essential advantage of cascade form. The NTF for  $E_Q$  is:

$$NTF_Q(z) = 1 - FIR_1(z) \cdot FIR_2(z)$$

Eq. 11

We notice that the zeros of the NTF in Eq. 11 are not directly related to  $FIR_1$  or  $FIR_2$ . In other words, cascading the loop filter does not provide a cascade form of the NTF. This problem not only increases design complexity, but also worsens the robustness of the NTF. For a 4<sup>th</sup> order NTF in the form of Eq. 11, the SNR degradation with coefficient variation can be 20dB larger than an NTF with a true cascade form. We provide a more detailed numerical comparison in the next section.

#### **B.** Nested Structure

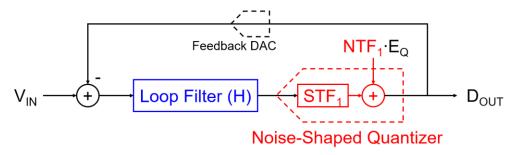

Some existing work on CT SD ADCs with noise-shaped quantizers [16][17] suggests a practical alternatives to using a cascaded loop filter. Fig. 11 illustrates the signal model of this kind of SD ADC.

Fig. 11 SD ADC with noise-shaped quantizer.

In these SD ADCs, an outer modulator loop is built around an inner NS system (i.e., the Noise-Shaped Quantizer). In classic control theory, this configuration is also recognized as the Nested Structure. Notice that the overall NTF of this system is in the cascade form of the two individual NTFs:

$$NTF(z) = NTF_1(z) \cdot NTF_2(z) = \frac{NTF_1(z)}{1 + H(z)STF_1(z)}$$

Eq. 12

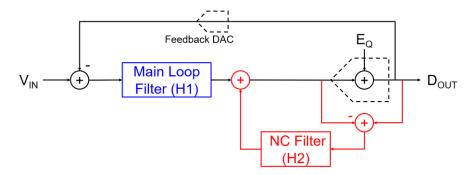

Although most of these SD works use the nested structure for higher NTF order, this configuration can provide other benefits of cascade form, especially improvement of robustness. Theoretically, any NS converter can be used as the noise-shaped quantizer. But in practice, we would like to make the signal transfer function of the quantizer (i.e., STF<sub>1</sub>) to be all pass, so that the design of the outer NS loop is more straightforward. Conventionally, the most commonly used noise-shaped quantizer is an error-feedback-based NS converter, also known as the Noise Coupling technique [18]. Fig. 12 shows the signal model of a Noise Coupled SD ADC.

Fig. 12 SD ADC with Noise Coupling (EF based NS quantizer).

As mentioned in Chapter 1, EF based NS system is much simpler in its loop filter design. Still, due to the difficulty of residue extraction, EF structure is never used to form the outer NS loop in conventional designs. However, with the help of SAR architecture, residue extraction is much easier. Besides, the tolerance to residue extraction error can be greatly relaxed if the nested structure is induced. Thus, we find that a pure EF based nested NS system is practical, and can be even simpler than conventional designs. Fig. 13 gives the model of the EF NS system in the nested structure.

Fig. 13 Nested Error-Feedback Noise-Shaping System.

In this NS system, the overall NTF is in cascade form, and the sub-loop-filters independently control the zeros:

$$NTF(z) = (1 - FIR_1(z))(1 - FIR_2(z))$$

Eq. 13

As mentioned, it enables a high-order NTF with small coefficients. But more importantly, this independent control dramatically reduces the sensitivity of the NTF to coefficient variation. To better illustrate this, Fig. 14 shows the calculated performance distributions for four different NTFs for a 1% 1-sigma coefficient variation. The horizontal axis represents the SNR improvement from noise-shaping, assuming an OSR of 10. The NTF of the proposed nested structure provides a much better overall SNR, even accounting for manufacturing variation. Notice that, the direct-form loop filter and cascaded-form loop filter (i.e., Fig. 10) of 4th-order NTF perform even worse than 2nd order one. Therefore, the proposed cascaded architecture is crucial for reliable high SNR operation.

Fig. 14 Performance distributions for four different NTFs for a 1% 1-sigma coefficient variation.

The nested structure extends the advantages of EF at the circuit-level, as well. The outer loop shapes the noise from the inner loop and the noise from the FIR1 filter. This shaping greatly relaxes the noise requirements for FIR1, and thus reduces power and die area.

#### 2.3 A Design Example of Nested Noise-Shaping SAR ADC

In this example, we apply the Nested Structure to a NS SAR ADC and observe the advantages. The prototype was taped-out and measured, and the result was published in [19].

#### A. Architecture

For simplicity, the NS SAR in this example is based on pure EF structure, which means there is no CIFF path (see section 1.4). The goal is to implement the signal model shown in Fig. 13.

As we know, the SAR conversion naturally converges the comparator's input to near zero. In other words, after each round of conversion, we will get the residue ( $E_Q$ ) at the comparator's input. At the same time, notice that in Fig. 13, the input to FIR2 ( $V_{RES2}$ ) is derived as:

$$V_{RES2}(z) = V_{RES1}(z) - FIR_1(z) \cdot V_{RES1}(z) = FIR_1(z) \cdot E_Q(z) - E_Q(z)$$

Eq. 14

This suggests a straightforward architecture of a Nested NS SAR, where we can use an adder to synthesis the  $V_{RES2}$  from Eq. Fig. 15 shows the block diagram of this method.

Fig. 15 A straightforward architecture of the Nested NS SAR.

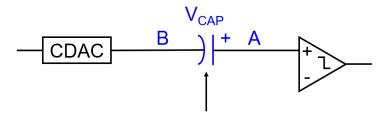

Certainly, we can use an active adder to implement Fig. 15, but an active adder consumes extra power, brings in extra noise, and may even worsen linearity. Passive adder is thus attractive. In this example, we introduce a serial capacitor [20] to realize the summation, as shown in Fig. 16.

Summation signal loaded on C

Fig. 16 Realizing passive summation by a serial capacitor.

It is evident that the voltage at node B is the voltage at node A subtracted by the voltage across the capacitor. Such summation needs only a single capacitor, and the summation gain is independent of the capacitance. This makes it insensitive to any possible variation. The FIR filters should be active to charge the capacitor, but this is acceptable as it only processes a sampled signal (i.e., DT signal). We will cover the FIR filter in the later section.

The design aims to provide 90dB SNR over a 100kHz bandwidth. For simplicity, we choose a classic 4th order NTF  $((1-z^{-1})^4)$  such that it can be easily decomposed into the product of two sub-NTF for cascading. OSR is set to 10x, which corresponding to a 2MHz sampling rate. Such a NS configuration leave plenty margin for circuit variations.

#### **B.** Implementation

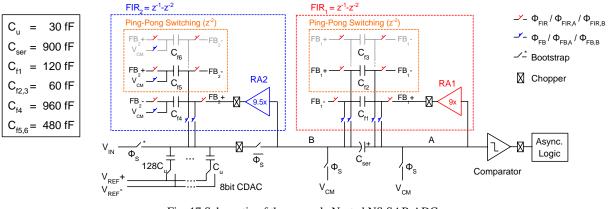

Fig. 17 shows the complete schematic of the prototype Nested NS SAR ADC. Besides the nested EF structure, the remainder of the implementation is relatively straightforward. The SAR core uses an 8-bit CDAC, a Strong-ARM dynamic comparator, and asynchronous SAR logic [21]. The input sampling switch is boot-strapped, while the other switches are simple transmission gates. Chopping in the main signal path suppresses flicker noise.

Fig. 17 Schematic of the example Nested NS SAR ADC.

A serial capacitor ( $C_{ser}$  in Fig. 17) cascades the noise-shaping stages and implements the inner loop feedback.  $C_{ser}$  is reset before each round of feedback to clear any residual charge from the previous cycle. Feedback for the inner stage is through simple change-sharing of the output of FIR<sub>1</sub> with  $C_{ser}$ . In the subsequent conversion, the voltage on the top plate of  $C_{ser}$  ( $V_A$ ) is naturally equal to the voltage on the bottom plate of  $C_{ser}$  ( $V_B$ ), plus the voltage across  $C_{ser}$  ( $V_{ser}$ ):

$$V_A = V_B + V_{ser} = V_B + \alpha V_{FIR1}$$

Eq. 15

where,  $V_{FIR1}$  is the output of FIR<sub>1</sub> and  $\alpha$  represents the loss due to charge-sharing. As mentioned, this summation requires only one single capacitor and is entirely passive. And because the outer stage relaxes the noise requirements for the inner stage,  $C_{ser}$  can be a relatively small capacitance. The power and area overheads are therefore low. On the other hand, the large capacitance of CDAC suppresses the noise from FIR<sub>2</sub>, which is the dominant noise of the system. In effect, this reuse of the CDAC capacitance for FIR<sub>2</sub> noise reduction reduces the area further.

A residue amplifier (RA) driving the input of each FIR filter compensates for the chargesharing loss ( $\alpha$ ) and maintains the FIR coefficients. Cross-differential sampling, as in [20], provides an extra gain of 2, which relaxes residue amplifiers' gain requirement and provides common-mode suppression (Fig. 18). Charge-injection from the switches is negligible because of the fully differential operation, and also because of the relatively large capacitance of FIR filters.

Fig. 18 Cross-differential sampling of FIR capacitors.

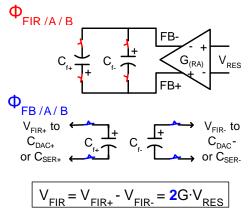

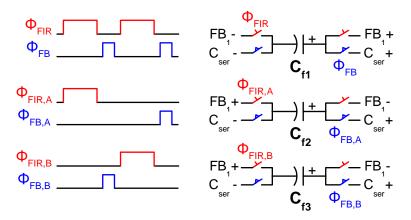

The FIR filters in this design use ping-pong switching to realize two cycles of delay.  $C_{f2}$  and  $C_{f3}$  alternatively sample the output of RA1 (i.e., FB<sub>1</sub>) and transfer their sampled charges to  $C_{ser}$  two cycles later, as Fig. 19 shows. Such an implementation simplifies the switching logic as there is only a single charge-sharing step in each conversion cycle.

Fig. 19 FIR1 switches timing. FIR2 operates with same timing.

FIR<sub>2</sub> operates similarly to FIR<sub>1</sub> and injects its output to the CDAC by charge-sharing [8]. This charge-sharing inevitably attenuates the sampled input voltage on CDAC and thus reduces the overall SNR. A high RA gain is required to mitigate the attenuation entirely, but this increases the design complexity and sensitivity. Therefore, we choose an RA with around 10x gain, leading to a tolerable SNR degradation of 1.5dB (16%).

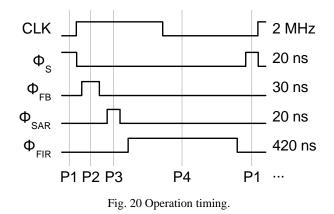

Conversion occurs in four steps, as described in Fig. 20. The overall timing is simple and little more complex than in a conventional SAR ADC.

In the first step (P1), CDAC samples the input signal. At the same time, the series capacitor  $C_{ser}$  discharges (reset). Feedback occurs in the second step (P2). The FIR filters inject their outputs onto  $C_{ser}$  and CDAC by charge-sharing. The third step (P3) proceeds in the same way as conversion in a conventional SAR ADC. The fourth and final step (P4) is residue sampling. In this step, the two RAs amplify the residues on CDAC and the top plate of Cser. After that, the two FIR filters sample the amplified outputs using the cross-differential connection for an additional gain of 2.

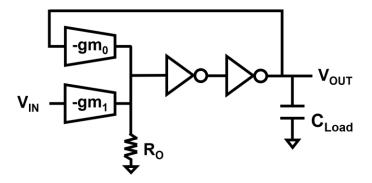

This operation tolerates linear parasitic capacitance at the plates of  $C_{ser}$  and  $C_{fl-6}$  because these capacitances only cause a linear gain error, and Nested NS SAR is insensitive to gain error. However, any nonlinear parasitic capacitance on nodes A and B, such as from the input transistors of the RAs, causes distortion and degrades SNDR. To reduce this distortion, we induce the Parasitic Pre-Charging method that reset nodes A and B to  $V_{CM}$  during P1. After P1, the parasitic capacitances at A and B share some of the charge from CDAC and C<sub>ser</sub>. However, since V<sub>A</sub> and V<sub>B</sub> converge to virtual ground during SAR conversion, the charge shared by these two parasitic capacitors eventually returns, mostly eliminating the nonlinear error. More details on the Parasitic Pre-Charging technique are discussed in section 5.1. As mentioned, an advantage of the cascaded architecture is that it suppresses the noise of the inner loop. This greatly relaxes the noise requirements for RA1, allowing it to be a simple low-power gm-R amplifier (Fig. 21). However, the noise of RA2 remains critical, because its noise is not shaped and dominates the overall ADC noise. To solve this problem, we design a gm-R amplifier with the Two-Phase Settling technique to suppress noise and improve efficiency. The details on the Two-Phase Settling technique will be discussed in section 5.2.

Fig. 21 Schematic of RA1

As shown in Fig. 22, RA2 is a gm-R structure with a push-pull structure to double the transconductance and improve efficiency. The CMFB resistors ( $R_L$ ) are the dominant resistive load. Cascoding reduces the influence of channel-modulation on gain and linearity. The output resistance is configured by shorting the output series resistors ( $R_0$ ). And thus, the main pole location can be changed during settling. The noise of  $R_0$  is suppressed by the gain of RA2 and is thus negligible.

Table 1 compares the simulated noise performance of RA2 for different settling configurations. The simulations are for the same RA2 design and differ only in  $R_0$  and the switch operation. In the conventional settling case, an external  $R_0$  is added to satisfy 6- $\tau$  settling. The simulations show that 2-phase settling reduces noise by 33%.

|                |                                      | Conventional           | Two-                     | Phase     |

|----------------|--------------------------------------|------------------------|--------------------------|-----------|

|                |                                      |                        | P1                       | P2        |

|                | gm                                   |                        | 2.25 mS                  |           |

|                | RL                                   |                        | 4.2 ΚΩ                   |           |

|                | CL                                   |                        | 2.88 pF                  |           |

|                | Ro                                   | $7~{ m K}\Omega$ $^+$  | shorted                  | 35.6 ΚΩ   |

|                | Ts                                   | 420 ns                 | 120 ns                   | 300 ns    |

| 1              | main pole (p) ++                     | 2.2 MHz                | 6.6 MHz 0.7 MHz          |           |

| tiı            | me constant ( $\tau$ ) <sup>++</sup> | 71 ns                  | 28 ns                    | 230 ns    |

| $v_{n,in}^{2}$ | gm noise only                        | (15.0 μV) <sup>2</sup> | $(10.2 \ \mu V)^2$       |           |

|                | gin noise only                       | $(13.0 \mu \text{V})$  | [54% re                  | eduction] |

|                | all noise enabled                    | (17.6 µV) <sup>2</sup> | $(14.4 \ \mu V)^2$       |           |

|                | an noise enabled                     |                        | [ <b>33% reduction</b> ] |           |

| Table 1 Noise Performance of R | A2 | 2 |

|--------------------------------|----|---|

|--------------------------------|----|---|

$^+$   $\rm R_{\rm O}$  is added to satisfy 6- $\tau$  settling

++ from post-layout AC simulation

+++ statistical result from post-layout transient simulation with noise (1000 cases)

## C. Silicon Results

Fig. 23 Die photo.

The prototype design is fabricated in 28nm CMOS and measures 100µm by 200µm (Fig. 23). The majority of the chip area is occupied by the CDAC, while the noise-shaping FIR filters account for only 21% of the total area.

In single tone testing with 19.3kHz full-scale input signal (1.05Vp differential), the measured peak SNDR over a 100kHz bandwidth is 87.6dB. A 4th-order-shaped noise floor with an 80dB per decade slope is evident in the output spectrum, as shown in Fig. 24. Here, CDAC mismatch is canceled with an off-chip calibration method. Details about this calibration are described in Appendix B.

Fig. 24 FFT for single-tone test (64K samples Hann window, 16x averaging).

For comparison, we perform the same test with different configurations (Fig. 25). SNDR is improved by 25.3dB when the outer loop (FIR<sub>2</sub>) is enabled. The inner loop (FIR<sub>1</sub>) provides an additional 4.5 dB SNDR improvement. The mild SNDR improvement from the inner loop is due to a conservative design strategy that makes the shaped quantization error much smaller than the thermal noise. Therefore, there is a large margin for NTF variation so that quantization error does not overwhelm thermal noise. However, a more aggressive design strategy with a lower OSR and quantizer resolution can achieve the same SNR but with less NTF margin. The low-cost increased noise-shaping order provided by Nested NS SAR architecture gives the designer extra freedom and can either improve performance or robustness.

Fig. 25 Single-tone tests for different configurations.

Fig. 26 shows the measured spectrum for a two-tone test. The measured IMD3 is -83dB for a near-maximum input frequency. Fig. 27 shows the measured performance for different input amplitudes and frequencies. These measurements indicate consistent performance over the entire input frequency range. The measured dynamic range is 89dB.

Fig. 27 Measured performance versus input amplitude and frequency.

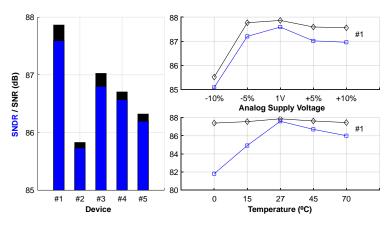

Five different devices are measured to demonstrate the PVT robustness of the design. Without any PVT calibration, the measured SNR variation across the devices is only 2dB. As shown in Fig. 28, the measured variation in SNR is within 3dB over  $\pm 10\%$  change in analog supply voltage and a 0-70°C temperature range.

Fig. 28 Measured performance versus input amplitude and frequency.

Fig. 29 shows a breakdown of the measured power and area. The ADC consumes  $120\mu$ W at 2MS/s. Only 2.2% of power and 6% of area is taken by the inner NS loop, which contributes <1% of the total noise. Therefore, the cost of the increased order is negligible.

Fig. 29 Power, area and noise (estimated) breakdown.

Finally, Table 2 compares this design with some other state-of-the-art sub-MHz ADCs. The prototype exhibits higher order noise-shaping than conventional noise-shaping SAR ADCs. The overall efficiency, as measured with the Schreier FoM, is comparable to that of the most efficient conventional noise-shaping SAR ADCs, but our implementation is free of dynamic amplifiers and is PVT stable on system-level. Compared to Sigma-Delta ADCs, the prototype is more than 7x smaller in area, and thus far lower in cost. The prototype Nested NS SAR ADC demonstrates the highest NTF order and highest SNDR among NS SAR ADCs over 100kHz bandwidth to date (Feb. 2020), and provides a low-cost solution for high-resolution sub-MHz analog-to-digital conversion.

|                           | This design      | ISSCC 2020           | ISSCC 2020  | ISSCC 2018 | VLSI 2017   | ISSCC 2018        | VLSI 2018   |

|---------------------------|------------------|----------------------|-------------|------------|-------------|-------------------|-------------|

|                           | This design      | X. Tang [22]         | J. Liu [23] | S. Li [8]  | W. Guo [24] | P. Vogelmann [25] | C. Lee [26] |

| Architecture              | CaNS-SAR         | NS-SAR               | NS-SAR      | NS-SAR     | NS-SAR      | DT-SD             | CT-SD       |

| NTF Order                 | 4                | 2                    | 2           | 2          | 2           | 3                 | 3           |

| Amplifier                 | 2-Phase Settling | Dynamic, Closed-Loop | Passive     | Dynamic    | Passive     | Op-Amp            | Op-Amp      |

| Process (nm)              | 28               | 40                   | 40          | 40         | 40          | 180               | 65          |

| Area (mm <sup>2</sup> ) + | 0.02             | 0.037                | 0.06        | 0.024      | 0.04        | 0.363             | 0.14        |

| Supply (V)                | 1                | 1.1                  | 1.1         | 1.1        | 1.1         | 3                 | 1.2         |

| Power (µW) +              | 120              | 107                  | 67          | 84         | 143         | 1100              | 68          |

| Fs (MHz)                  | 2                | 10                   | 2           | 10         | 8.4         | 30                | 6.14        |

| OSR                       | 10               | 8                    | 25          | 8          | 16          | 150               | 128         |

| BW (KHz)                  | 100              | 625                  | 40          | 625        | 263         | 100               | 24          |

| SNDR (dB)                 | 87.6++           | 83.8++               | 90.5        | 79++       | 80          | 86.6              | 94.1        |

| SFDR (dB)                 | 102.8++          | 94.3++               | 102.2       | 89++       | -           | 101.3             | 107         |

| DR (dB)                   | 89               | 85.5                 | 94.3        | 80.5       | -           | 91.5              | 98.2        |

| FoM <sub>S</sub> (dB)     | 176.8            | 181.5                | 178.2       | 177.7      | 172.6       | 166.2             | 179.6       |

Table 2 Comparison Table

\*Excludes power and area of CDAC calibration

++With CDAC mismatch calibration

## **Chapter 3 Time-Interleaved Noise-Shaping Converter**

## **3.1 Basic Concept of Time-Interleaving**

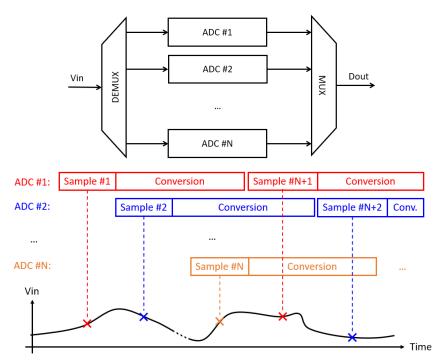

Time-Interleaving (TI) is a commonly used technique to speed-up the system. The key idea of TI is to have multiply identical copies of a system and run them in parallel. With proper input and output multiplexing, the overall interleaved system can achieve higher throughput. Fig. 30 shows a generalized block diagram of time-interleaved ADCs.

Fig. 30 Time-interleaved ADC (top) and timing diagram (bottom).

The overall sampling rate (i.e., throughput) of a time-interleaved ADC is given by:

$$F_{S,tot} = N \times F_{S,ch}$$

Eq. 16

where  $F_{s,tot}$  is the overall sampling rate of the interleaved ADC, *N* is the number of channels and  $F_{s,ch}$  is the sampling rate of each sub-channel ADC. Therefore, TI is a direct trade-off between speed and hardware resources (power and cost, etc.). But it cannot improve the system's efficiency alone, that is, the throughput per channel keeps the same. Another thing to mention is that the multiplexer is the bottleneck in a TI system. As for TI ADC, the sampler has to run at full rate, and its performance determines the upper bound of the overall system's performance.

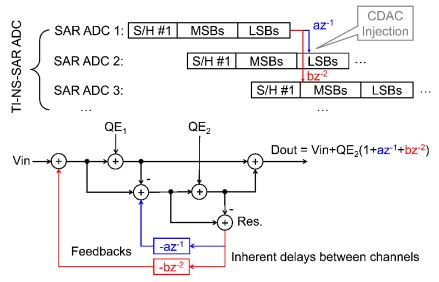

## **3.2 Interleaving of Noise-Shaping System**

#### A. Direct Interleaving

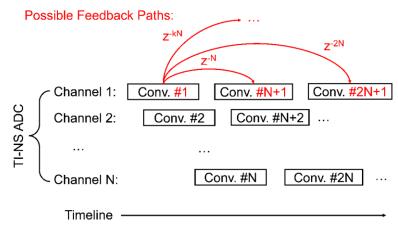

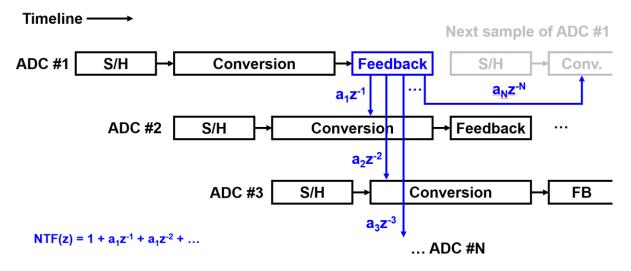

Although TI is a possible way of mitigating the reduced bandwidth of NS ADCs, the combination of TI and NS is challenging in practice. The difficulty is not only in the circuit-level implementation, but is also fundamental at the system level. This system-level difficulty is related to the extra feedback delay in a TI system: When we attempt to interleave multiple ADCs containing feedback, the effective feedback delay changes. Thus, the overall system does not preserve the noise-shaping transfer function of the individual NS system. To better explain this, Fig. 31 shows a direct attempt at interleaving multiple conventional NS ADCs.

Fig. 31 Direct interleaving of NS ADCs

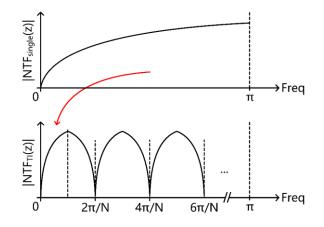

Feedback is within each NS ADC, however due to the interleaving, the actual feedback delay is a *N* times the interleaved-ADC sampling period. This means all unit delays,  $z^{-1}$ , in the individual NTF are replaced with  $z^{-N}$ . Therefore the equivalent NTF of this TI-NS ADC becomes:

$$NTF_{TI}(z) = NTF_{single}(z^N)$$

Eq. 17

Fig. 32 shows the resulting NTF. Since the overall NTF is now in a repeating pattern, we can hardly synthesize the desired single-notch noise-shaping characteristic.

Fig. 32 Comparison of the original NTF for single NS SAR ADC (top) and the repeating pattern of the interleaved NTF (bottom).

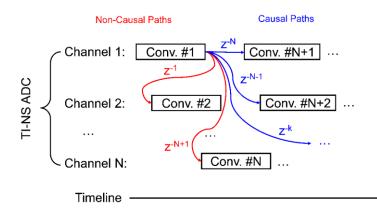

## **B.** Inter-channel Feedback and Causality Restrictions

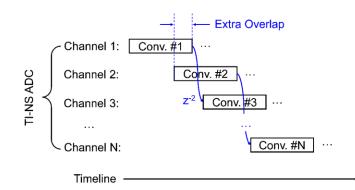

Knowing the root cause of the problem, one may wonder if we can re-arrange the feedback path to have the correct delay. One obvious way is to feed the signal from one channel to the others, i.e., Inter-Channel Feedback, which seems to be a promising solution (Fig. 33). With inter-channel feedback, the effective feedback signal delay can be as small as a single sampling delay, so that the NTF can be similar to a classical noise-shaping ADC.

Fig. 33 Inter-channel feedback and the possible non-causal paths.

Nevertheless, the TI-NS ADC shown in Fig. 33 is not physically realizable, as some of the feedback signal paths are non-causal. Inter-channel feedback paths traveling earlier in time can never be implemented. If we attempt to make these inter-channel feedbacks causal, then each channel must finish conversion before the next channel starts, as shown in Fig. 34. However, imposing this requirement eliminates the benefit of interleaving as there is no longer an overlap between channels to improve conversion throughput.

Fig. 34 This causal inter-channel feedback loses the throughput advantages of interleaving.

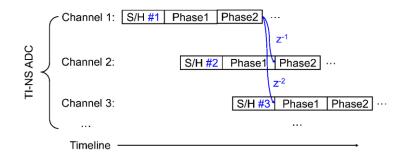

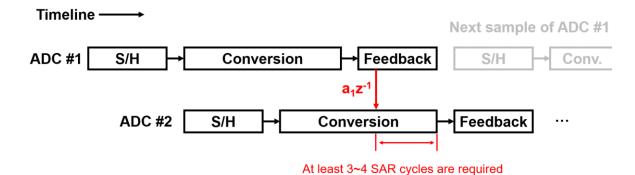

#### C. Midway Feedback and Multi-Phase Conversion

As discussed above, it is difficult to retain the benefits of interleaving and maintain flexibility in the transfer function. Although this may seem discouraging, we can still draw two useful conclusions from Fig. 33 and Fig. 34. First, for a feedback path with a longer delay, that is, traveling from a channel to another channel further separated in the interleaving sequence, the

causality restriction is relaxed. For example, if a TI-NS system does not have any feedback from a channel to an adjacent channel (i.e., there is no  $z^{-1}$  term in the transfer function), then there can still be some overlap in the conversions, as shown in Fig. 35. Therefore, if we can decompose the system into subsystems each with different delay, each subsystem can retain some benefits of interleaving (except for the subsystem with a delay of  $z^{-1}$ ).

Fig. 35 Timing diagram for a time-interleaved noise-shaping ADC with no single interleaving period  $(z^{-1})$  delay.

Second, the discussion above is based on the analysis of the feedback system. However, in a practical ADC system, many other actions introduce delay, including sampling, signal settling, and logic delay, etc. All these events are not restricted by the causality considerations that we mention, and therefore can be overlapped (i.e., interleaved) for higher ADC throughput.

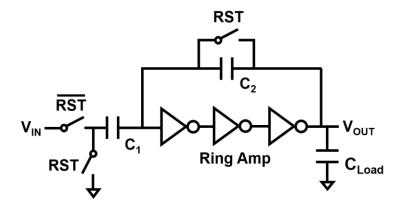

Inspired by these observations, we introduce Midway Feedback and Multi-Phase Conversion to implement a realizable TI-NS system. Fig. 36 shows the concept of Midway Feedback with a timing diagram. In this configuration, the feedbacks get into the channels at the midway of their running. And to make this work, the conversion process for each channel is decomposed into multiple phases, so each phase performs only part of the conversion (i.e., Multi-Phase Conversion). Besides, the feedback path is also decomposed into multiple feedback paths with different delays, so that each sub-path feeds between different phases of different channels, enabling the maximum overlap.

Fig. 36 Midway Feedback with Multi-Phase Conversion.

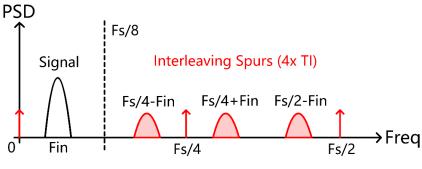

#### D. Non-Idealities of Interleaving

A significant drawback of time-interleaving is the degradation in accuracy due to the mismatch between channels. Typically, three kinds of mismatch dominate: offset mismatch, gain mismatch, and sampling skew. Offset mismatch causes input-independent tones at  $\frac{F_S}{N}$  and its multiples, where  $F_S$  is the overall sampling rate and N is the number of channels. Gain mismatch and sampling skew cause modulation around  $\frac{F_S}{N}$  and its multiples [27], as shown in Fig. 37.

Fig. 37 Output spectrum due to channel mismatch (4x TI as example).

For interleaved Nyquist-rate ADCs, these artifacts fall in the band of interest, and therefore the performance of traditional TI ADCs is susceptible to mismatch. However, for a TI-NS ADC, the band of interest is reduced by the OSR. We notice in Fig. 37 that, as the artifacts are only located at frequencies around  $\frac{F_S}{N}$ , it is possible to limit the bandwidth of interest so that the interleaving artifacts all fall out-of-band. More specifically, assuming the signal band is from DC to *BW*, the lowest possible artifact is located at  $\frac{F_S}{N} - BW$ . Thus, if we limit  $BW < \frac{F_S}{N} - BW$  or  $OSR = \frac{F_S}{2BW} > N$ , then, the artifacts fall out-of-band. In this way, TI-NS ADC can suppress the mismatch problem naturally. This is a significant advantage because, generally, TI ADCs need complicated and power-hungry calibration to mitigate channel mismatch impacts. Although out-of-band blockers can still be mixed-down into the signal band, in this case, a pre-filter can be used to suppress the out-of-band blockers. An advantage is that this filter can be simpler than the anti-aliasing filter in a Nyquist rate ADC, as the modulation by channel mismatch is relatively weak.

## 3.3 A Design Example of Interleaved Noise-Shaping SAR ADC

In this example, we apply the Midway Feedback and Multi-Phase Conversion techniques in a TI-NS SAR ADC and demonstrate the advantages. The prototype was taped-out and measured, and the result is published in [28].

## A. Architecture

As mentioned in section 3.2, a prerequisite for Midway Feedback is the decomposition of the original conversion into Multi-Phase Conversion. This might not be simple for some ADC architectures (e.g., Flash), but fortunately, it is easy for a SAR ADC. As we know, the SAR conversion naturally contains multiple cycles. Therefore, we can simply group these cycles into phases, as shown in Fig. 38.

Fig. 38 Multi-phase division of SAR ADC (2-phase example).

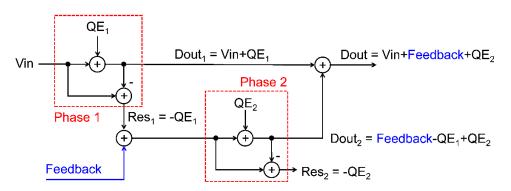

Such a division is only in a logical sense, as each phase of the conversion is still performed with the same physical circuitry. Similar to a pipeline ADC with an inter-stage residue gain of 1, each phase partially digitizes the signal and passes a residue to the next phase. Although each conversion phase generates its independent quantization noise, this noise is digitized in subsequent phases and passed to the digital output. Eventually, the quantization noise from all phases, except the last, cancels at the output. Furthermore, as long as the ADC is not overloaded, any signal injected onto the CDAC, irrespective of the conversion phase, is all digitized and passed to the digital output, as shown in Fig. 39.

Fig. 39 Channel signal model with injected midway feedback signal.

The feedback summation position in this configuration naturally supports the Error-Feedback structure, which is promising as we already discussed the advantage of EF structure in section 1.4. Therefore, we implement the TI-NS SAR with Midway Error-Feedback in this design, as shown in Fig. 40.

Fig. 40 Midway Error Feedback and its signal model (2nd order case as example).

The combination of CDAC injection and TI indicates an interesting implementation of the FIR filter. Recall that for Midway Feedback, we decompose the feedback path into multiple different feedbacks with different delays. Thus, we can simply sum different delayed paths with appropriate weights to form any desired FIR filter. In other words, we can make use of the inherent delay between different channels in a TI ADC to significantly simplify the overall architecture.

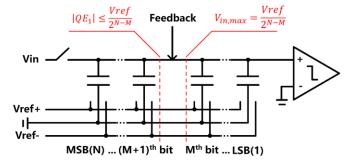

Although midway feedback in a TINS-SAR is elegant and straightforward, it is susceptible to overload, especially during the later quantization phases. We simply model each quantization phase as an ideal quantizer with purely additive quantization noise. However, this model fails when the input signal is larger than the quantizer's maximum quantization range. In a multi-phase SAR, since there is no gain between phases, the quantization range shrinks along with the successiveapproximation steps, as Fig. 41 shows. Therefore the overloading condition, QE + Feedback >  $V_{in,max}$ , can easily occur. In particular, for the final phase, the conversion range is as small as a few LSBs, so even a small injected feedback signal can cause overload.

Fig. 41 Potential overload caused by feedback injection.

Once overload occurs, the quantizer's digital output can no longer be regarded as the summation of the input and noise, and the assumption of quantization noise cancellation no longer holds. As a result, the overall noise-shaping performance badly degrades, and the system can even become unstable. Worse, for a high-order FIR filter, the coefficients are large, which means the injected feedback signal is amplified, making overload even more likely.

We introduce two modifications to solve the overload problem. Firstly, we add redundant bits [29] to each quantization phase. The extra redundant decision bits provide an extended input range to tolerate errors made by previous decisions. This extended signal range also helps with the overload problem, as shown in Fig. 42. Although additional redundancy bits can further prevent overload, the tradeoff is reduced overall sampling rate. In practice, we add redundant bits mainly to the last phase as it has a more limited conversion range and is easier to overload.

Fig. 42 A redundant bit enlarges the quantization range.

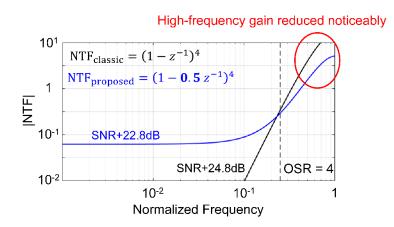

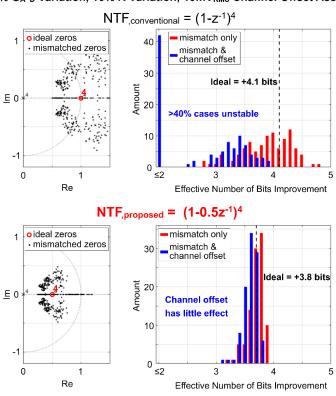

Secondly, we reduce the coefficients of the FIR filter to limit the amplitude of the feedback signals. As mentioned, the coefficients of a high-order FIR filter are generally large, especially for an aggressive NTF such as  $(1 - z^{-1})^N$ . However, for NS ADCs with low OSR as 4x, a mild NTF with relatively small coefficients still delivers near-optimum SNR. Fig. 43 compares the performance for a conventional NTF and for a mild NTF to illustrate this idea. In this prototype, we use  $(1 - 0.5z^{-1})^4$  since the 0.5 coefficient is easily implemented in layout with a ratio of 2. Another advantage is that a mild NTF is much more tolerant to coefficient variation. This is an important advantage as the poles' and zeros' positions always vary in real circuits due to mismatch and gain variations. An aggressive NTF degrades rapidly in the presence of small variation even without considering overload. A quantitative comparison of the NTFs is given in the next section.

Fig. 43 Comparison of an aggressive NTF and a mild NTF.

Finally, the prototype TINS-SAR ADC targets a 400M/s sampling rate with four-way interleaving. It employs 4<sup>th</sup> order EF-based noise-shaping, as shown in Fig. 44. Each channel of the TINS-SAR performs 16 conversion cycles grouped in 4 phases. 6 bits of redundancy are added to the 10-bit binary digitization to eliminate overload based on model simulation results. As mentioned, the NTF is relaxed to  $(1 - 0.5z^{-1})^4$  to help further prevent overload. With 4x OSR, this is enough to provide 70dB SNR over 50MHz bandwidth.

Fig. 44 The example design's timing diagram (top) and signal model (bottom).

## **B.** Implementation

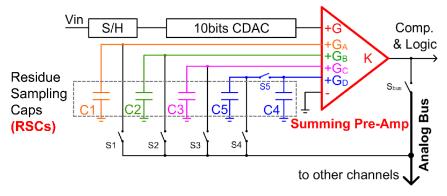

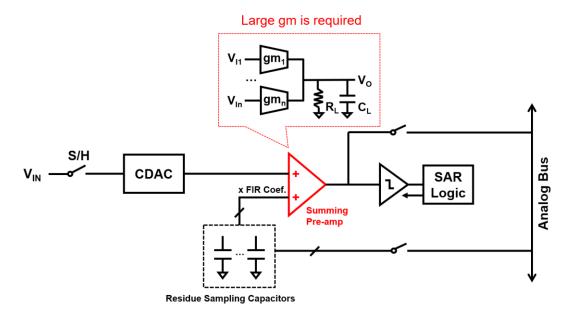

In this design example, we introduce a summing pre-amplifier to accomplish CDAC injection, as shown in Fig. 45.

Fig. 45 Summing pre-amplifier implementation of EF.

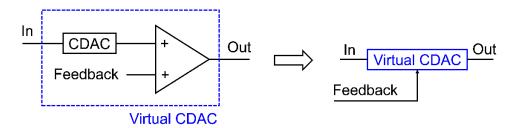

In each channel, a summing pre-amplifier drives the comparator. The pre-amplifier output also provides feedback to all the interleaved channels through a single shared analog bus. The pre-amplifier is a multi-input low-gain differential amplifier, with its inputs connected to the CDAC and to four Residue Sampling Capacitors (RSCs, C1-C4 in Fig. 45), which hold the feedback signals from each channel. The pre-amplifier sums and weights the CDAC voltage as well as the stored feedback values. Thus, the output of the pre-amplifier is equivalent to CDAC output voltage after feedback injection. From another perspective, the pre-amplifier and the CDAC form a *Virtual CDAC* that realizes feedback injection (Fig. 46).

Fig. 46 The pre-amplifier and CDAC form a Virtual CDAC that realizes an equivalent feedback injection.

There are significant benefits to using a pre-amplifier. First, the charge on the CDAC is not contaminated during the feedback operation, and the cancelation of quantization error is therefore preserved. Second, the pre-amplifier provides good isolation between the comparator and both the CDAC and the RSCs (which hold the feedback voltages), thereby reducing comparator kickback

concerns. Third, the pre-amplifier can be realized as a simple single-stage open-loop amplifier due to the low required gain. A single-stage open-loop amplifier is smaller and more power-efficient than a high-gain amplifier, and is also easier to be implemented in modern CMOS processes. Furthermore, unlike a dynamic amplifier, such an amplifier does not require accurate timing.

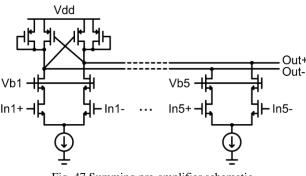

In the pre-amplifier, multiple differential pairs with ratioed sizes drive a cross-coupled diode load, as shown in Fig. 47. The different input pair sizes implement the various feedback-gain coefficients (i.e., G,  $G_A - G_D$ ), shown in Fig. 45. The amplifier provides the required gain (~10x considering all inputs) and a stable common-mode output voltage. Since the input of the amplifier (i.e., the residue) is only a few mV, such an open-loop design's linearity is sufficient for the target SNDR.

Fig. 47 Summing pre-amplifier schematic.

At any time, only one channel is completing a conversion and generating a residue to feedback. A shared bus (i.e., Analog Bus in Fig. 45) passes feedback between channels, keeping the wiring implementation simple. In addition to the inter-channel sampling capacitors (C1-C3), an auxiliary capacitor (C5) samples the residue of the channel itself. After C5 samples the pre-amplifier output, this sampled value is passed to the corresponding residue storage capacitor (C4) by simple charge-sharing. The attenuation due to charge-sharing is simply considered to be part of the feedback coefficient.

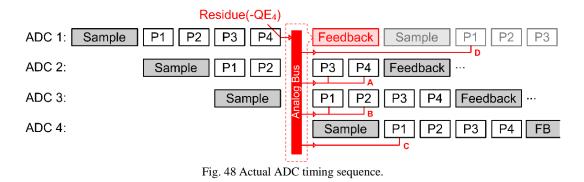

Fig. 48 shows the prototype's actual timing sequence, where phases 1 and 2 are approximately aligned to phases 3 and 4, respectively. Thus, some of the feedbacks are actually injected in earlier phases than is shown in Fig. 44. Note that Fig. 48 only illustrates the timing in the nominal case and is subject to possible skew, which will be addressed in the next section. The advantage of such a design is that more time can be assigned to the feedback phase, so that the bandwidth of the pre-amplifier can be smaller and the noise minimized. Similarly, the sampling phases are also lengthened to improve the linearity of the bootstrap switch.

#### C. Addressing Non-Idealities

In this section, we cover a few possible non-idealities in this design, and suggest solutions. Some of the problems are also further discussed in section 4.3A, and corresponding solutions are provided.

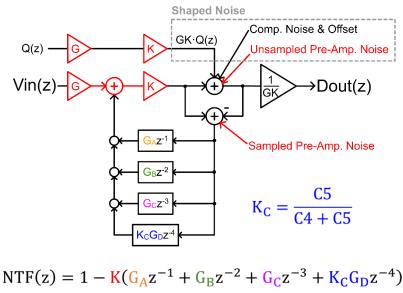

#### *i-* Noise