#### **Accelerated Systems for Pattern Matching**

by

Arun Subramaniyan

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in the University of Michigan 2021

#### **Doctoral Committee:**

Associate Professor Reetuparna Das, Chair Professor David Blaauw Professor Satish Narayanasamy Professor Westley Weimer Arun Subramaniyan arunsub@umich.edu

ORCID iD: 0000-0001-6119-3182 •

© Arun Subramaniyan 2021

To my parents and grandparents

#### **ACKNOWLEDGMENTS**

Firstly, I feel deeply honored to have been advised by Professor Reetuparna Das. I am constantly amazed by Professor Das' enthusiasm and passion for research. Even before starting graduate school, Professor Das gave me a head start to my PhD by involving me in her compute cache research project. Since then, I have greatly enjoyed and benefitted from each of my interactions with her. Over the last 5 years, she has helped me think systematically and spent countless hours providing structure and clarity to several of my hazy ideas. This thesis would never have been possible without her constant support, encouragement and guidance.

I would also like to thank Professor Satish Narayanasamy, Professor David Blaauw and Professor Westley Weimer for agreeing to serve on my dissertation committee and providing many useful suggestions to improve this thesis. Professor Narayanasamy was always available to discuss different ideas and their merits. Professor Blaauw helped me navigate several research challenges and is a constant source of new ideas. Professor Weimer has provided valuable feedback to improve both my oral and written presentation. He also encouraged me to open source our genomics benchmark suite and provided helpful suggestions to improve its reach.

My sincere thanks to Dr. Bill Bolosky who hosted me for two summer internships at Microsoft Research. I will greatly miss my interactions with him. He always encouraged me to strive for high-quality work with long-term impact and provided many helpful suggestions on job search. I would also like to thank Dr. Ramarathnam Venkatesan for making my stay at Redmond memorable and providing me with many valuable life lessons.

I am also deeply grateful to my undergraduate research mentors at Karlsruhe Institute of Technology: Muhammad Shafique, Semeen Rehman, Florian Kriebel and BITS-Pilani: Nitin Chaturvedi. They were the first to introduce me to research and motivated me to pursue a PhD.

Much of the work in this thesis would not have been possible without inputs from my amazing collaborators. Jack Wadden and Kush Goliya contributed a lot to this thesis. I greatly enjoyed brainstorming with them and appreciate their critical feedback on different ideas. Daichi Fujiki and Tianjun Zhang are joint first authors with me on our GenAx, genome accelerator work. I thank them for allowing me to present the results of our collaboration in my dissertation. Sanchit Misra, Md. Vasimuddin and Somnath Paul from Intel Labs provided many useful inputs on the Genomics-Bench project. Kevin Skadron, Elaheh Sadredini and Reza Rahimi from the University of Virginia provided valuable feedback on Cache Automaton and helped in the design of our in-cache DPDA accelerator, ASPEN. I also appreciate Ezhil Balasubramanian for his help in designing Cache Automaton and Jingcheng Wang for discussions on SRAM-based switches. Many thanks to Kevin Angstadt for patiently answering my questions on parsing pipelines, grammars and automata.

I also greatly appreciate the generous support from my sponsors. Parts of this thesis were supported by Precision Health at the University of Michigan (Precision Health Scholar Award), by the Kahn foundation, by Rackham's International Student Fellowship, by the NSF under the CAREER-1652294 award and the Applications Driving Architectures (ADA) Research Center, a JUMP Center co-sponsored by SRC and DARPA. Many thanks to Colin Hercus from Novocraft Technologies for providing an academic evaluation license.

A special thanks to all the members of the MBits and Precision Health Research Groups: Daichi Fujiki, Vidushi Goyal, Charles Eckert, Xiaowei Wang, Nathan Ozog, Xiao Wu, Tianjun Zhang, Zhehong Wang, Yu Zeng, Timothy Dunn, Harisankar Sadasivan, Yufeng Gu, Yichen Gu and Alireza Khadem for all the fun times, attending numerous practice talks, discussions, dinners and more. I would also like to thank all the members of the CSE department and staff for patiently answering my questions, booking rooms for practice talks, helping with group lunch orders and purchasing.

At the University of Michigan, I feel incredibly fortunate to spend time with an incredible group of friends and seniors. Thank you Subarno, Aman, Ankush, Aditya, Mani, Jana, Vivek, Vidushi, Harini, Mitali, Sandipp, Suresh, Sanjay, Subramaniam, Salar, Hossein, Amir, Subhankar

and Aporva for making my time at Ann Arbor enjoyable. I also thank my seniors – Shaizeen, Supreet, Ram for guiding me in the initial years of my PhD. Finally, I am deeply indebted to my parents – Subramaniyan and Bharathi, late grandfathers – Gopalakrishnan and Raman, grandmothers – Radha and Ananthalakshmi for their unconditional love and support throughout the thesis, especially during the difficult times. I dedicate this thesis to them. I also thank my sister – Subhasri, brother-in-law – Afsar and my extended family of uncles and aunts for their continuous encouragement.

# TABLE OF CONTENTS

| DEDIC   | ATIONii                                                                         |

|---------|---------------------------------------------------------------------------------|

| ACKNO   | DWLEDGMENTS                                                                     |

| LIST O  | F FIGURES                                                                       |

| LIST O  | F TABLES xii                                                                    |

| ABSTR   | ACT                                                                             |

| СНАРТ   | TER                                                                             |

| 1 Intro | duction                                                                         |

| 1       | 1 Parallel Pattern Matching: Parallelizing Input Stream Processing on In-Memory |

|         | Hardware Accelerators                                                           |

| 1       | 2 Cache Automaton for Pattern Matching                                          |

| 1       | 3 Accelerating Pattern Matching in Genomics                                     |

|         | String Matching                                                                 |

|         | 1.3.2 SillaX : Approximate String Matching Acceleration                         |

| 1       | 4 GenomicsBench: Characterizing the Genomics Computing Landscape 9              |

| 2 Back  | ground and Related Work                                                         |

| 2       | 1 Finite State Automata for Pattern Matching                                    |

|         | 2 Automata Processing Acceleration                                              |

|         | 2.2.1 Software Approaches                                                       |

|         | 2.2.2 Hardware Approaches                                                       |

| 2       | 3 Pattern Matching in Genomics                                                  |

|         | 2.3.1 Common Genomics Pipelines                                                 |

|         | 2.3.2 Read Alignment                                                            |

|         | 2.3.2.A Seeding       20         2.3.2.B Seed-Extension       22                |

| 3 Para  | llel Pattern Matching on In-Memory Hardware Accelerators                        |

| 3       | 1 Finite State Machine Parallelization                                          |

| 3       | 2 Parallel Automata Processor                                                   |

|         | 3.2.1 Range Guided Input Partitioning        | 28        |

|---------|----------------------------------------------|-----------|

|         | 3.2.2 Enumeration using Flows                | 29        |

|         | 3.2.3 Merging Flows                          | 31        |

|         | 3.2.3.A Leveraging Connected Components      | 31        |

|         | 3.2.3.B Active State Group and Common Parent | 33        |

|         | 3.2.3.C Dynamic Convergence Checks           | 34        |

|         | 3.2.3.D Deactivation Checks                  | 34        |

|         | 3.2.4 Composition of Input Partitions        | 35        |

|         |                                              | 37        |

| 3.3     | Evaluation Methodology                       | 37        |

|         | 3.3.1 Workloads                              | 38        |

|         | 3.3.2 Experimental Setup                     | 40        |

| 3.4     | Results                                      | 41        |

|         | 3.4.1 Overall Speedup                        | 41        |

|         |                                              | 43        |

|         |                                              | 44        |

| 3.5     | Summary                                      | 46        |

| 4 Cache | as a Pattern Matching Engine                 | 48        |

|         |                                              | 48        |

| 4.1     |                                              | +0<br>50  |

| 4.2     | C I                                          | 50<br>51  |

| 4.2     |                                              | 51<br>51  |

|         | $\epsilon$                                   | 51<br>53  |

|         | 1                                            | 54        |

|         |                                              | 54<br>55  |

|         | $\varepsilon$                                | 55<br>56  |

|         |                                              | 50<br>57  |

|         | 4.2.7 Configuration and ISA Interface        |           |

| 13      | Cache Automaton Compiler                     |           |

| 4.3     | 4.3.1 Connectivity Constraints               |           |

|         | 4.3.2 Mapping Algorithm                      |           |

|         |                                              | 51<br>52  |

| 4.4     |                                              | 52<br>53  |

| 4.5     | <i>5</i> ,                                   | 65        |

| 4.5     |                                              | 65        |

|         |                                              | 53<br>57  |

|         |                                              | o 1<br>68 |

|         |                                              | 59        |

|         | •                                            | ง9<br>71  |

|         |                                              | 71<br>71  |

| 4.6     |                                              | 71<br>73  |

|         |                                              |           |

|         |                                              | 74<br>    |

| 5.1     | Exact String Matching Acceleration (Seeding) | 75        |

|     | 5.1.1 Exact Matching Using the FMD-Index                              | . 75  |

|-----|-----------------------------------------------------------------------|-------|

|     | 5.1.2 Seeding Algorithm and Super-Maximal Exact Matches               | . 76  |

|     | 5.1.3 Memory-Bandwidth Limitations of Seeding                         | . 78  |

|     | 5.1.4 Set Intersection Approach for Seeding                           | . 80  |

|     | 5.1.5 Enumerated Radix Trees for Seeding                              | . 80  |

|     | 5.1.5.A K-mer Enumerated Index                                        |       |

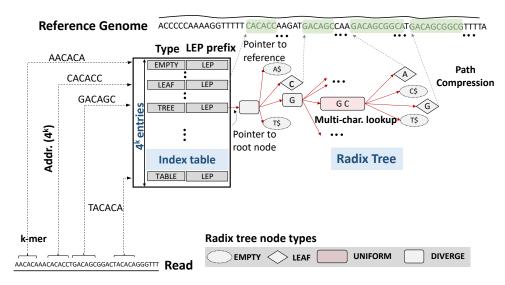

|     | 5.1.5.B Customized Radix Tree                                         | . 82  |

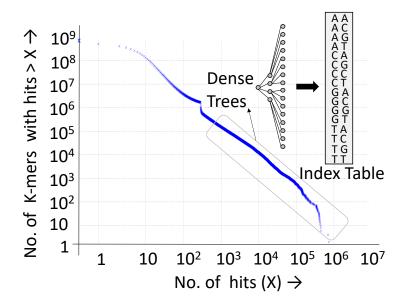

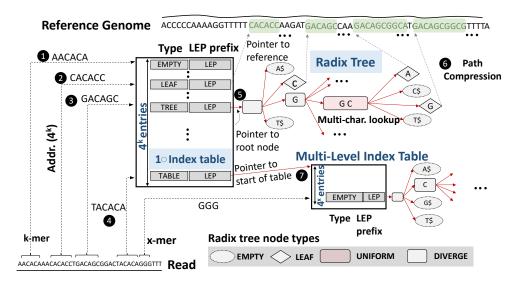

|     | 5.1.5.C Supporting large K at low space overhead                      | . 83  |

|     | 5.1.5.D ERT index table entries and radix tree nodes                  | . 84  |

|     | 5.1.5.E ERT Construction                                              | . 85  |

|     | 5.1.5.F Finding longest exact matches in forward direction with ERT . | . 86  |

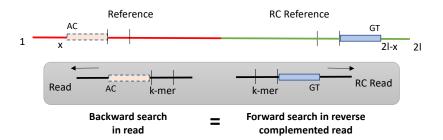

|     | 5.1.5.G Supporting Backward Search with ERT                           | . 87  |

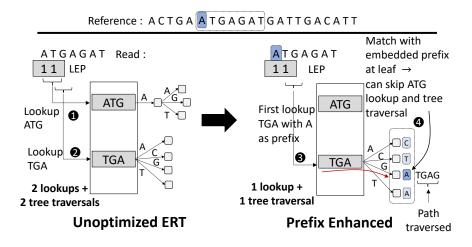

|     | 5.1.5.H Re-using MEM Searches with Prefix-Merged Radix Trees          | . 88  |

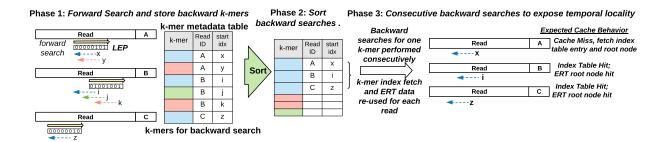

|     | 5.1.5.I Locality with K-mer Reuse                                     | . 90  |

|     | 5.1.5.J Tiled Layout for Spatial Locality                             | . 92  |

|     | 5.1.5.K Pruning Backward Searches: Zigzag Seeding                     | . 93  |

|     | 5.1.5.L Pruning Backward Searches: Ordering Backward Searches         | . 94  |

|     | 5.1.6 Hardware Accelerators for Seeding                               | . 95  |

|     | 5.1.6.A Set Intersection Accelerator                                  | . 95  |

|     | 5.1.6.B Enumerated Radix Tree Traversal Accelerator                   | . 97  |

|     | 5.1.6.B.1 Overview                                                    | . 97  |

|     | 5.1.6.B.2 Processing Elements                                         | . 98  |

|     | 5.1.6.B.3 Control Processor                                           | . 99  |

|     | 5.1.6.B.4 K-mer Reuse Metadata Storage and Sorting                    |       |

|     | 5.1.6.B.5 System Integration and Programming API                      |       |

|     | 5.1.6.B.6 Evaluation Methodology                                      |       |

|     | 5.1.6.B.7 Results                                                     |       |

| 5.2 |                                                                       |       |

|     | 5.2.1 Silla for Indel                                                 |       |

|     | 5.2.2 3D Silla for Substitutions                                      |       |

|     | 5.2.3 Collapsed 3D Silla for Indels and Substitutions                 |       |

|     | 5.2.4 Merging Confluence Paths is Sound                               |       |

|     | 5.2.5 Silla Accelerator for Genome Sequencing                         |       |

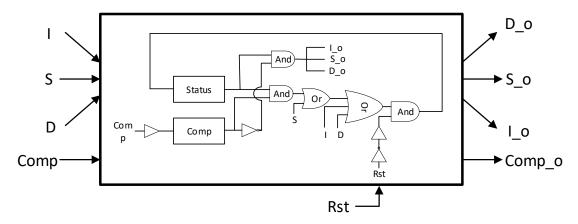

|     | 5.2.5.A SillaX Edit Machine                                           |       |

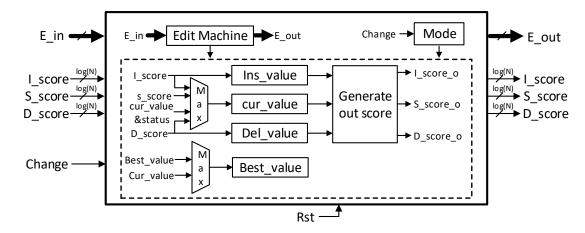

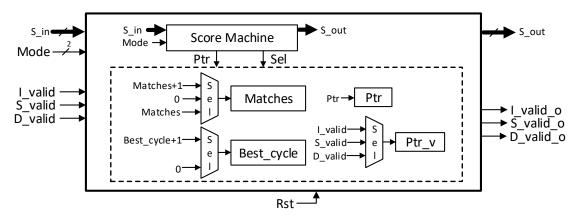

|     | 5.2.5.B Scoring Machine                                               |       |

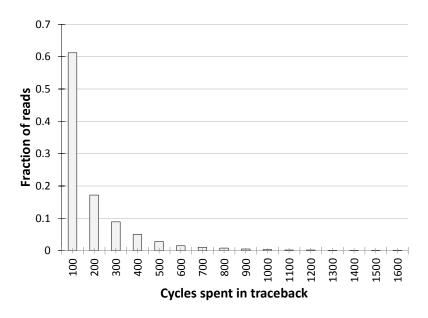

|     | 5.2.5.C Traceback Machine                                             |       |

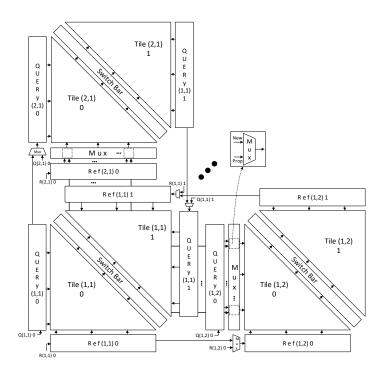

|     | 5.2.5.D Composable SillaX                                             |       |

|     | 5.2.6 Comparison with Banded Smith-Waterman                           |       |

|     | 5.2.7 Evaluation Methodology                                          |       |

|     | 5.2.8 Results                                                         |       |

| 5.3 | $\mathcal{E}$                                                         |       |

|     | 5.3.1 GenAx                                                           |       |

|     | 5.3.2 ERT + SeedEx [74]                                               |       |

| 5.4 | Summary                                                               | . 129 |

| 6 GenomicsBench: Characterizing the Genomics Computing Landscape | 131 |

|------------------------------------------------------------------|-----|

| 6.1 Need For A Genomics Benchmark Suite                          | 131 |

| 6.2 GenomicsBench Benchmark Suite                                | 132 |

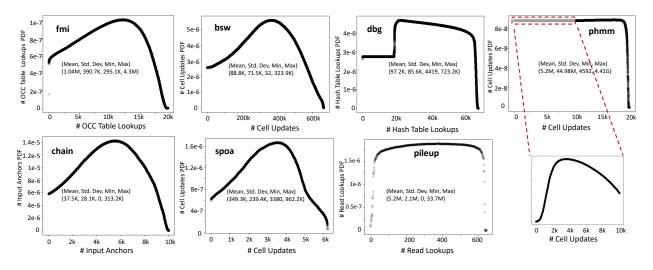

| 6.3 Performance Characterization of Benchmarks                   | 142 |

| 6.3.1 Characterization Methodology                               | 142 |

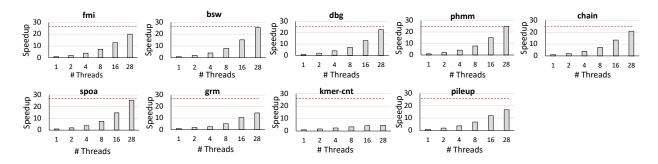

| 6.3.2 Parallelism                                                | 143 |

| 6.3.2.A CPU benchmarks                                           | 143 |

| 6.3.2.B GPU benchmarks                                           | 146 |

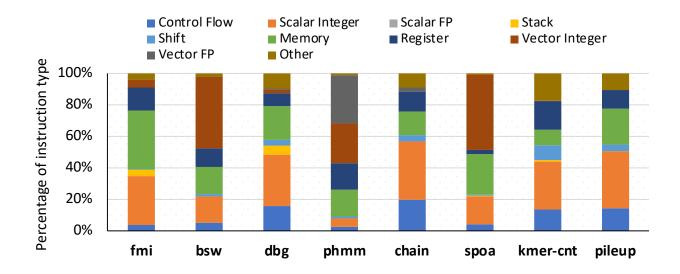

| 6.3.3 Instruction Diversity                                      | 147 |

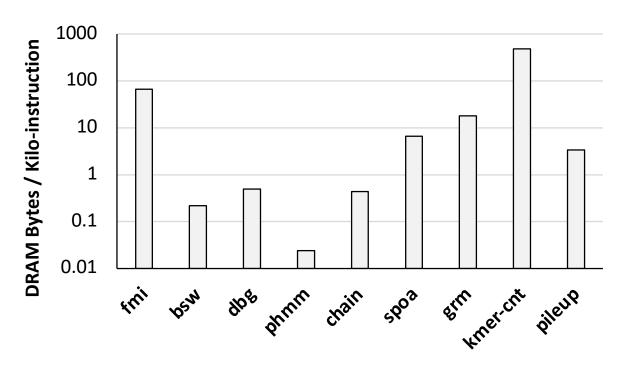

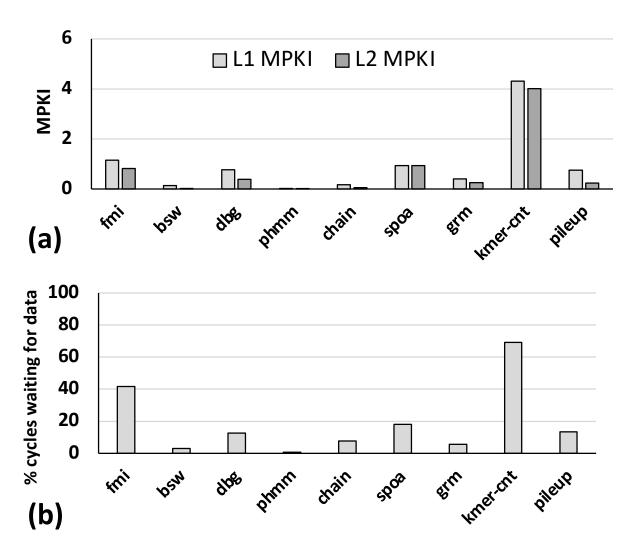

| 6.3.4 Memory Access Characteristics                              | 148 |

| 6.3.4.A CPU benchmarks                                           | 148 |

| 6.3.4.B GPU benchmarks                                           | 150 |

| 6.3.5 Thread Scaling                                             | 151 |

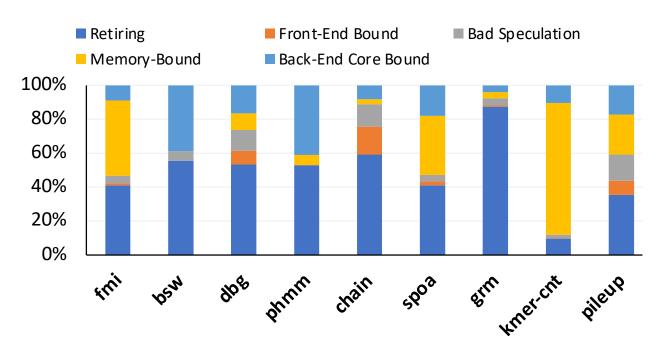

| 6.3.6 Microarchitectural Bottleneck Analysis                     | 152 |

| 6.4 Summary                                                      | 153 |

| 7 Conclusion                                                     | 154 |

| BIBLIOGRAPHY                                                     | 156 |

# LIST OF FIGURES

#### **FIGURE**

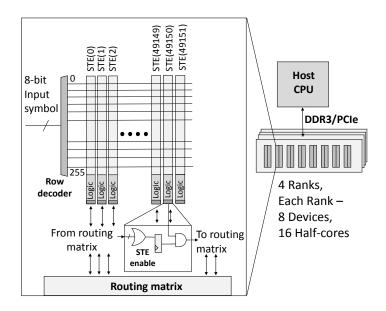

| 2.1  | Automata Processor interfaced with the host CPU                             | 15 |

|------|-----------------------------------------------------------------------------|----|

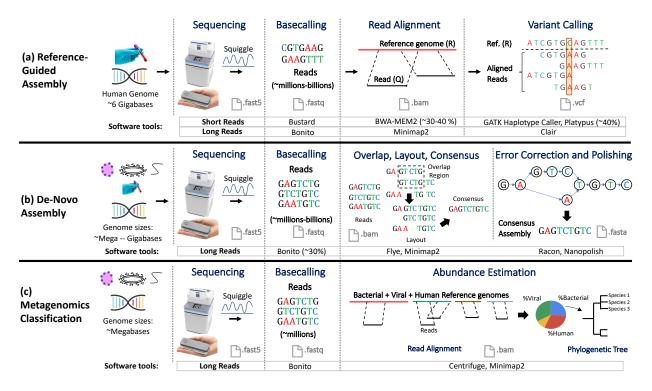

| 2.2  | Common workflows in genomics                                                | 18 |

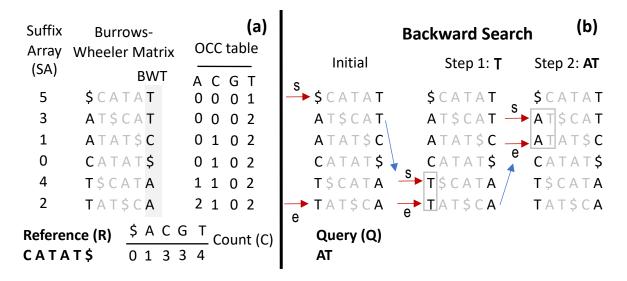

| 2.3  | FM-index example                                                            | 21 |

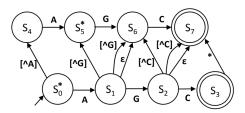

| 2.4  | Levenshtein Automata for edit distance K = 1 and reference string AGC       | 23 |

| 3.1  | An FSM example with enumeration                                             | 26 |

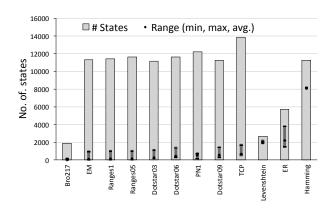

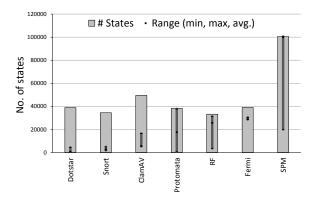

| 3.2  | Range of symbols for different benchmarks                                   | 28 |

| 3.3  | Merging paths belonging to separate connected components                    | 32 |

| 3.4  | Merging states in the range with common parent                              | 33 |

| 3.5  | Overlapping $T_{cpu}$ with symbol processing                                | 36 |

| 3.6  | Overall framework for low-cost enumeration on the Automata Processor        | 36 |

| 3.7  | Speedup for different inputs                                                | 41 |

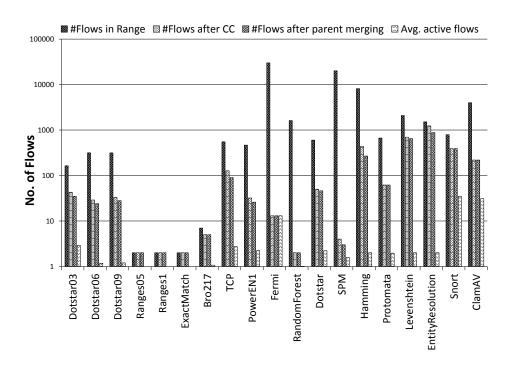

| 3.8  | Average number of flows across benchmarks                                   | 43 |

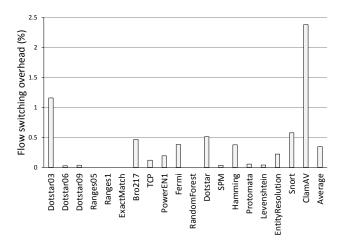

| 3.9  | Costs of flow switching                                                     | 44 |

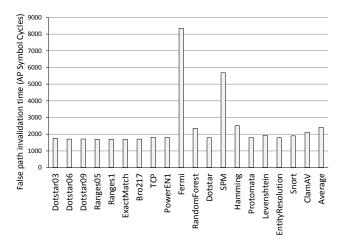

| 3.10 | False path decoding costs                                                   | 45 |

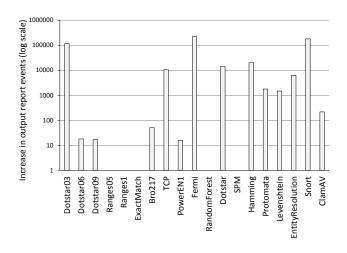

| 3.11 | Increase in output reports due to false paths                               | 46 |

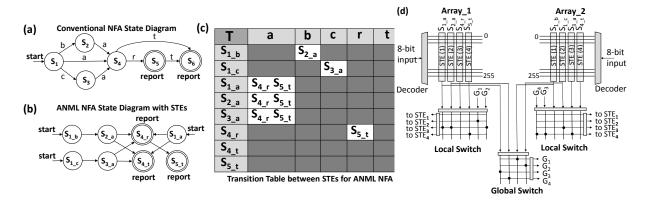

| 4.1  | Example NFA mapping to SRAM arrays and switches                             | 49 |

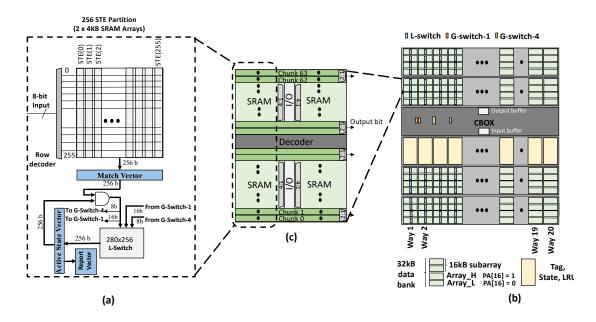

| 4.2  | Cache Automaton Architecture                                                |    |

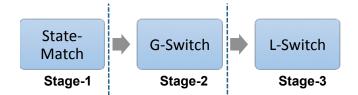

| 4.3  | Three-stage pipeline design for Cache Automaton                             | 53 |

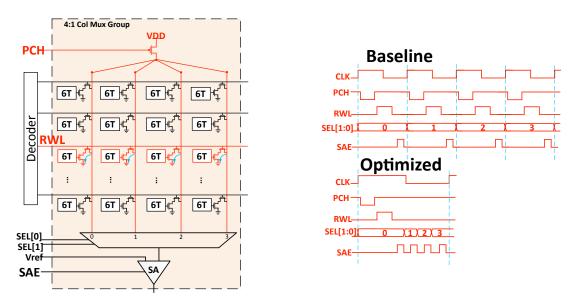

| 4.4  | Design and timing diagram for a 4-way multiplexed SRAM column               | 55 |

| 4.5  | The 8T cross-point design for switches                                      | 56 |

| 4.6  | Mapping <i>Entity Resolution</i> to cache arrays                            | 62 |

| 4.7  | Performance - Cache Automaton and Micron's Automata Processor               | 66 |

| 4.8  | Cache utilization of benchmarks                                             | 67 |

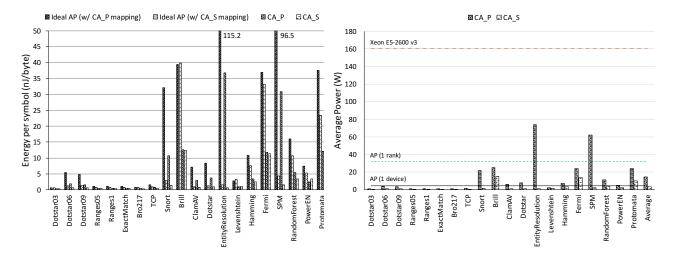

| 4.9  | Energy and power Consumption of Cache Automaton                             |    |

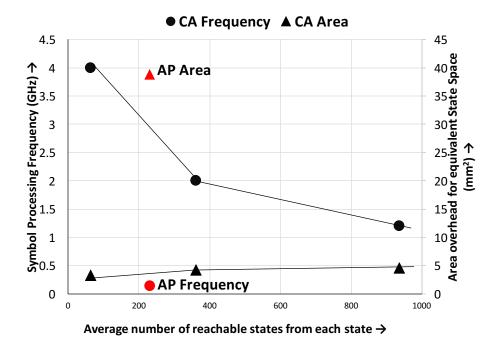

| 4.10 | Performance, reachability and area tradeoffs for automata processing        | 70 |

| 5.1  | FM-Index example                                                            | 77 |

| 5.2  | Forward and backward search to identify super-maximal exact matches         | 78 |

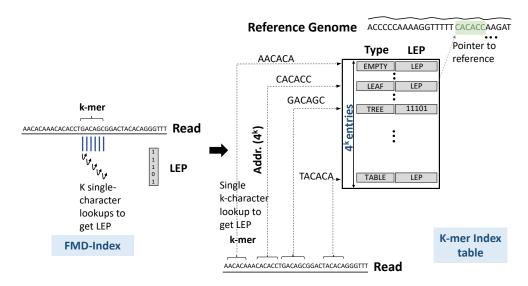

| 5.3  | K-mer index table compared to FMD-index                                     | 81 |

| 5.4  | Enumerated Radix Tree (ERT) with index table and space-optimized radix tree | 82 |

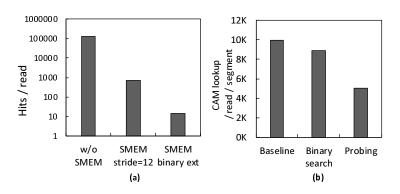

| 5.5  | Figure showing the skewed hit distribution for k-mers                       | 84 |

| 5.6  | Multi-level index table in ERT to support large K at low space overhead     |    |

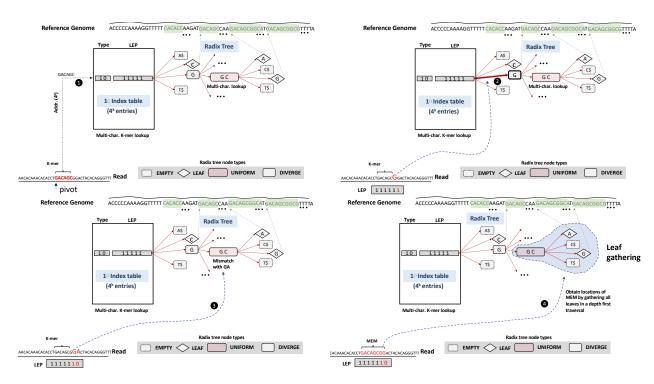

| 5.7  | Forward search for maximal exact match (MEM) with ERT                       | 87 |

| 5.8  | Bidirectional search                                                       | 88 |

|------|----------------------------------------------------------------------------|----|

| 5.9  | Reusing MEM searches with prefix-merged radix trees                        | 89 |

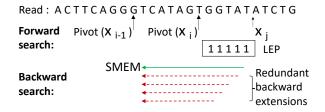

| 5.10 | K-mer reuse algorithm for leveraging temporal locality across MEM searches | 91 |

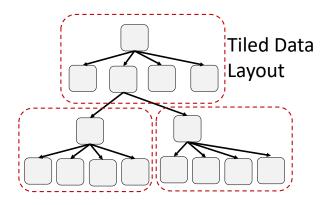

| 5.11 | Cache-friendly tiled data layout for ERT                                   | 93 |

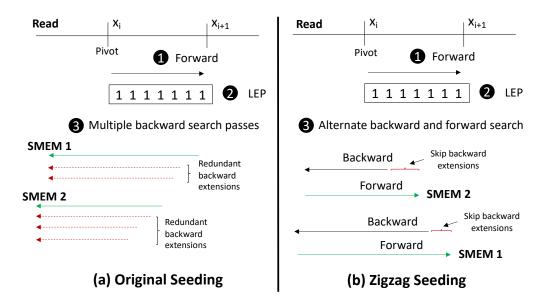

| 5.12 | Zigzag seeding to reduce backward searches                                 | 94 |

| 5.13 | Right-to-left backward search algorithm                                    | 94 |

| 5.14 | GenAx seeding accelerator optimizations                                    | 96 |

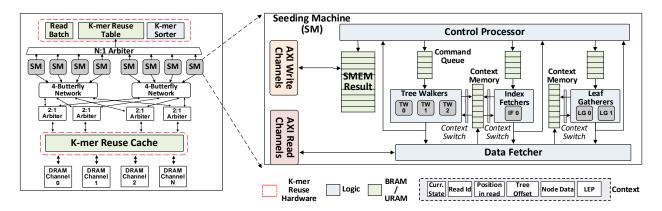

| 5.15 | ERT seeding accelerator architecture                                       | 97 |

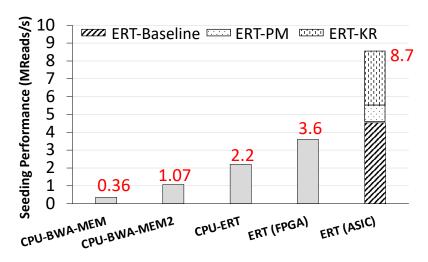

| 5.16 | Seeding performance in million reads/s                                     |    |

| 5.17 | Memory access characteristics of different designs                         |    |

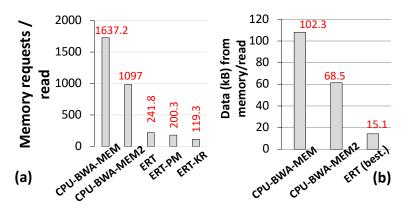

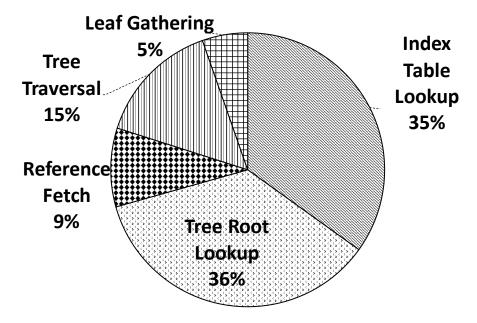

| 5.18 | DRAM page open breakdown for ERT-KR                                        |    |

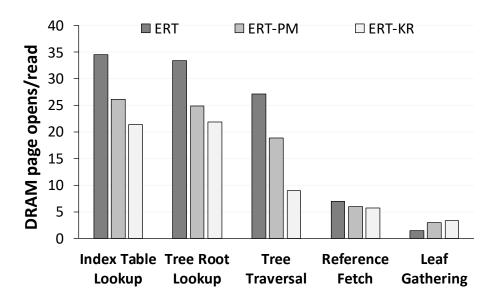

| 5.19 | DRAM page opens per read across optimizations                              | 07 |

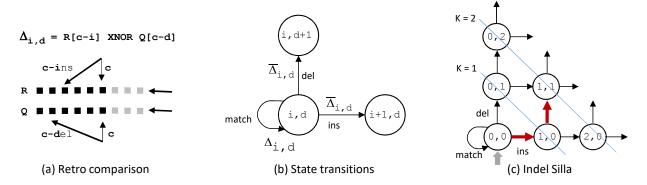

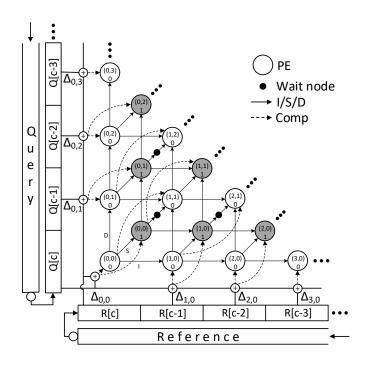

| 5.20 | Silla design                                                               | 08 |

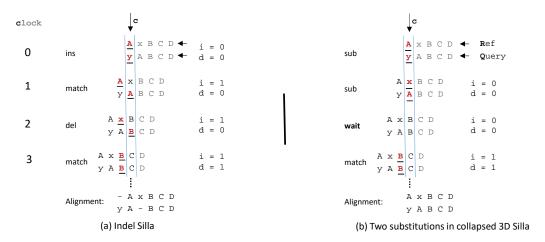

| 5.21 | Silla illustration                                                         |    |

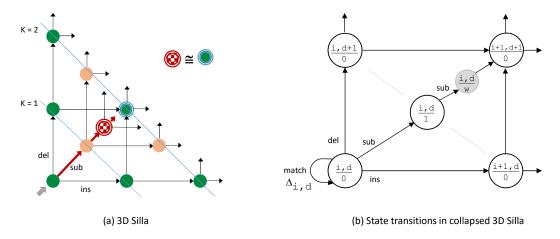

| 5.22 | Collapsing 3D Silla to two dimensions                                      | 10 |

| 5.23 | SillaX accelerator                                                         |    |

| 5.24 |                                                                            |    |

| 5.25 |                                                                            |    |

| 5.26 |                                                                            |    |

| 5.27 | PE for SillaX affine gap machine with traceback                            |    |

| 5.28 | Illustration of composable SillaX                                          |    |

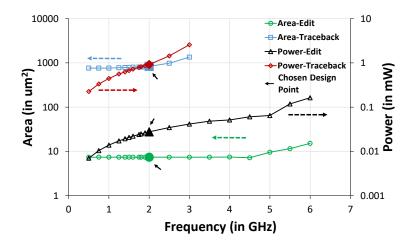

| 5.29 | SillaX area and power for a single PE                                      |    |

| 5.30 |                                                                            |    |

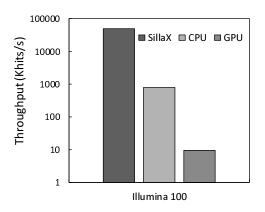

| 5.31 | SillaX throughput (in Khits/s)                                             |    |

| 5.32 | GenAx architecture overview                                                |    |

| 5.33 | Comparing throughput and power of SillaX                                   | 28 |

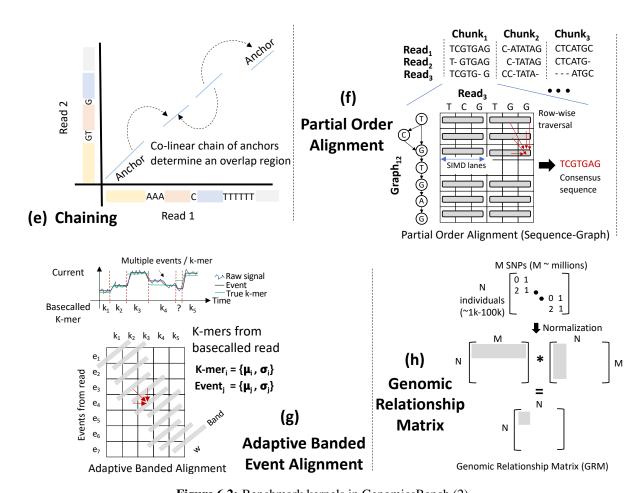

| 6.1  | Benchmark kernels in GenomicsBench (1)                                     | 33 |

| 6.2  | Benchmark kernels in GenomicsBench (2)                                     | 37 |

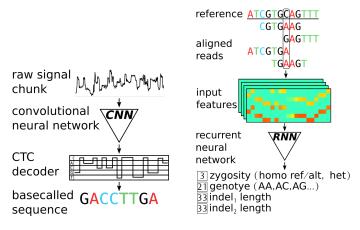

| 6.3  | Neural Network-based algorithms in Bonito and Clair                        | 41 |

| 6.4  | Variation in the amount of computation performed for each task             |    |

| 6.5  | Dynamic instruction breakdown for different benchmarks                     |    |

| 6.6  | Off-chip data requirements for different benchmarks                        |    |

| 6.7  | Cache misses and stalls for different benchmarks                           | 50 |

| 6.8  | Thread scaling for different kernels in GenomicsBench                      |    |

| 6.9  | Microarchitectural bottleneck analysis                                     | 52 |

# LIST OF TABLES

#### **TABLE**

| 3.1 | Regex and ANMLZoo benchmark characteristics and AP resources needed      |

|-----|--------------------------------------------------------------------------|

| 4.1 | Regex and ANMLZoo benchmarks – with and without common prefix merging 64 |

| 4.2 | Switch parameters for memory-based state transition interconnect 64      |

| 4.3 | Pipeline stage delays and operating frequency                            |

| 4.4 | Impact of optimizations and parameters                                   |

| 4.5 | Comparison with related ASIC designs                                     |

| 5.1 | Baseline system configuration                                            |

| 5.2 | Seeding – comparison candidates for evaluation                           |

| 5.3 | ASIC Configuration and Synthesis Results                                 |

| 5.4 | ERT accelerator – Per-FPGA configuration and synthesis results           |

| 5.5 | Baseline system configuration                                            |

| 5.6 | Area breakdown: GenAx                                                    |

| 5.7 | Overall read alignment performance on AWS EC2                            |

| 5.8 | FPGA-ERT + SeedEx: estimated resource utilization                        |

| 5.9 | Seeding – area and energy efficiency comparison                          |

| 6.1 | Baseline system configuration used for characterization                  |

| 6.2 | GenomicsBench: Benchmark characteristics                                 |

| 6.3 | Sources of parallelism for different benchmarks                          |

| 6.4 | GPU kernel control flow and compute regularity                           |

| 6.5 | Proportion of GPU global memory bandwidth used                           |

|     |                                                                          |

#### **ABSTRACT**

Pattern matching forms the core of many applications and contributes to a significant fraction of their execution time. For instance, scanning the human reference genome for motifs and identifying variations between individuals requires processing of 100s of gigabytes of unstructured data and can take several days on a multi-core processor. Parsing activities in the frontend of browsers can account for up to 40% of web page loading time. Datacenter log processing involves the analysis of data generated at the rate of several terabytes every few minutes.

While general-purpose processors have been optimized for regular, data-parallel workloads, the class of pattern matching workloads identified above typically employ computational models and data-structures that are not well suited for general-purpose processing. In particular, these workloads perform irregular memory accesses and spend disproportionately more time and energy in moving data from storage to compute units when compared to the actual computation and are often bottlenecked by memory bandwidth. To address these inefficiencies, this dissertation proposes to repurpose existing memories for efficient in-memory pattern matching computation and presents new hardware-software co-design techniques to significantly improve the performance of these pattern matching workloads.

First, a new hardware design is proposed that allows embarrassingly sequential finite state automata, a common computation model used for pattern matching, to be executed in parallel in a DRAM-based in-memory accelerator. Next, this dissertation presents the Cache Automaton architecture, which repurposes CPU last-level caches for massively parallel automata processing. This dissertation also takes a deep dive into accelerating genomics analysis, an emerging application domain which heavily relies on pattern matching. In particular, we design custom hardware and present new hardware-friendly data-structures and algorithms to accelerate read alignment, a time-consuming string matching workload in genomics analysis, which matches each of the billions of short fragments of DNA emitted by the sequencer (called reads) against a reference genome. Finally, this dissertation presents a detailed characterization of the pattern matching landscape in genomics and highlights opportunities for the development of new domain-specific architectures customized for genomics analysis.

#### **CHAPTER 1**

# Introduction

By 2025, the International Data Corporation (IDC) estimates that the total amount of data produced by individuals and corporations would be  $165 \text{ ZB} (10^{23} \text{ bytes})$  [11]. A major contributor to this data is unstructured data, which is being generated in large volumes in forms such as system logs, social media posts, emails, and news articles. Unstructured data is also expected to grow at an annual rate of 61%. With growing volumes of unstructured data, it becomes increasingly important to develop fast and efficient pattern matching techniques that can parse this data and extract insights.

Pattern matching on unstructured data poses unique challenges to general-purpose processing. While CPUs have been optimized for data-parallel processing of regular structured data, many applications dealing with unstructured data often employ computational models that are not amenable to efficient general-purpose processing. For instance, finite state automata (FSAs) are widely used as the computational model in many end-to-end applications that utilize pattern matching such as deep packet inspection [181], web-browser frontend [93] and motif-search [148]. FSA computation is inherently sequential and hard to parallelize. Modern multi-core processors cannot efficiently process FSA (in particular non-deterministic finite state automata or NFA), since they are limited by the number of state transitions they can perform per thread in a given cycle and suffer from branch mispredictions. This limits the number of patterns they can identify. Furthermore, their processing capability is also limited by the available memory bandwidth. GPGPUs (General-Purpose Graphics Processing Units) on the other hand have had limited success with automata processing because FSA processing is inherently dominated by irregular memory accesses.

Therefore, there is a need for efficient computing architectures to accelerate FSA computation.

Pattern matching using FSA is dominated by data movement and involves very little computation per state transition. To address this inefficiency, Micron introduced the Automata Processor (AP) which facilitates in-situ FSA computation in DRAM in a highly parallel and energy-efficient manner. AP has been successful in accelerating FSA computation because of three factors: massive bit-level parallelism inherent in memory technologies such as DRAM, eliminating data movement overheads (between memory and CPU), and reducing instruction processing overheads compared to a CPU. While AP significantly improves the state-of-the-art, it still processes the input stream sequentially. To break the sequential execution bottleneck and enable parallel processing of a single input stream, we propose the Parallel Automata Processor (PAP) architecture that demonstrates the feasibility of enumerative parallelization on the AP with low-cost hardware extensions.

DRAM is an attractive substrate for automata processing because of its density. However, we notice that a significant fraction of the die area in the AP is devoted to custom logic for efficient state transition. As a result, the AP can sacrifice the density of DRAM storage by up to  $16.6 \times 10^{-5}$  to support automata processing. This is because DRAM technology has not been shrinking at the same rate as processor logic and implementing additional logic to support state transition on lower technology DRAM nodes is inefficient. To overcome this limitation, we explore the feasibility of repurposing the last-level cache in general-purpose processors for automata processing. This has several advantages: (1) SRAM is faster and more energy-efficient than DRAM, (2) SRAM is integrated on-chip and can benefit from being implemented in cutting-edge technology nodes, similar to the rest of the performance-optimized logic.

Having seen the benefits of in-memory pattern matching, we looked at application domains that can benefit from such acceleration. One application domain that heavily relies on fast and efficient pattern matching is genome sequence analysis. A genome is essentially a long string of characters or bases from the DNA alphabet i.e., A, G, C, and T. A single strand of the human genome has  $\sim$ 3 billion characters. Current sequencing technologies cannot read the entire genome at once, and typically split the DNA into billions of small substrings called *reads*. A major computational

problem in sequence analysis is the problem of mapping each of the sequenced reads to their original position in the genome prior to splitting, referred to as *read alignment* in literature. This is typically performed in two steps: (1) an exact string matching step called seeding, which involves performing exact matches of short substrings in the read against a previously sequenced reference genome, and (2) an approximate string matching step, called seed-extension which matches the rest of the read at the candidate reference locations identified by seeding, while allowing for edits. Approximate string matching is needed to account for sequencing errors and true variations between individual genomes.

The most widely used software for read alignment, BWA-MEM [118] and the recently released faster version, BWA-MEM2 [128], perform seeding using a compressed index data structure called the FMD-index, that supports only single character queries on the index. Furthermore, each of the index accesses tends to touch a different part of the index data structure and exhibits little spatial or temporal locality. This leads to high memory-bandwidth requirements and poor performance on conventional CPUs. To overcome this limitation, we propose a memory-bandwidth aware data structure for seeding called Enumerated Radix Trees (ERT) that is designed from the ground up to support multi-character lookup. We further redesign the seeding algorithm in BWA-MEM2 to exploit reuse opportunities inherent in the seeding algorithm.

On the other hand, approximate string matching on CPUs is commonly performed using the Smith-Waterman algorithm [154]. This algorithm has time and space-complexity  $\mathcal{O}(MN)$ , where M is the length of the read string and N is the length of the reference string. Often, the read and reference strings are similar and only alignments with less than K edits are interesting. In those cases, the runtime and memory space can be improved to  $\mathcal{O}(KN)$  [160]. We propose a non-deterministic finite automata called Silla for approximate string matching. The space requirements of Silla scale quadratically with edit distance and not string length and its time complexity is  $\mathcal{O}(N)$ . Furthermore, when compared to the Levenshtein automata commonly used for approximate string matching, Silla is string-independent and hardware-friendly since all state transitions are local. It is also composable, lending itself well to a hardware implementation that can scale to larger edit

distances. To leverage these properties of Silla, we design a hardware accelerator called SillaX. SillaX also supports other features required for read alignment such as affine gap scoring, and traceback of alignment path.

# 1.1 Parallel Pattern Matching: Parallelizing Input Stream Processing on In-Memory Hardware Accelerators

While the Automata Processor can perform several thousand state-transitions in parallel, it still processes the input stream sequentially by looking at one input symbol every cycle. Parallelizing across a single input stream can significantly improve throughput. Parallelization of finite state automata is known to be a hard problem due to its inherent sequential nature and high computational complexity. To break this sequential dependency and allow for parallel processing, enumeration may be employed [136]. In enumeration, the input is divided into segments and computations are done on individual segments in parallel. This computation is carried out for every possible state of the FSA. Once all input segments have been processed, their results can be composed to identify the true paths (i.e., sequence of states visited in the sequential execution of the complete input).

While the enumerative approach is promising, there are several challenges to realize it on the AP. First is the difficulty of tracking enumeration paths in a non-von Neumann architecture like the AP which has no notion of threads or local variables. Enumeration paths need to be tracked to discard false paths and retain true paths when combining the results from different input segments. The second challenge is the sheer computational complexity of enumeration. Enumerations can be highly inefficient because in the worst case each state has to be enumerated. Real-world NFA can have tens of thousands of states. In general, enumeration of an FSA with n states, over k input segments can lead to an ideal speedup of k provided we have  $n \times k$  independent computing resources. For typical NFA, these resources far exceed what is available on the AP.

To solve the above problems, we leverage some unique properties of real-world NFA as well as unique features of the AP. For instance, some enumeration paths can be pruned by partitioning

the input stream at symbols that have a small set of state transitions defined for them in the NFA. To solve the enumeration path tracking problem, we utilize the notion of AP "flows" which allows different users to time-share the same NFA execution on different input streams. A "flow" is defined as the set of active states for each user. We notice that the AP flow can be repurposed to track each enumeration path. Similar to prior work [136], we observe enumeration paths converge at runtime and implement lightweight dynamic convergence checks in AP using the flow abstraction. The proposed parallelization scheme demonstrates significant speedup (25.5× on average) using a 4-rank AP (with 32 DRAM dies) compared to sequential execution averaged across several benchmarks spanning network intrusion detection, malware detection, text processing, protein motif searching, DNA sequencing, and data analytics.

# 1.2 Cache Automaton for Pattern Matching

Given the benefits of memory-centric automata processing as demonstrated by the DRAM-based Automata Processor, this dissertation seeks to answer the question: Are SRAM-based last-level caches (LLCs) a suitable substrate for automata processing?

Caches typically have lower capacity compared to DRAM and one may wonder if it can store large real-word state machines. Interestingly, we observe that DRAM-based AP sacrifices a huge fraction of die area (up to 16.6×) to support state transition logic on lower technology DRAM. Thus, while DRAM's packing density is high, DRAM-based AP's packing density is comparable to LLCs (20-40 MB) which are located on-chip and can benefit from performance-optimized logic.

The memory technology benefits of moving to SRAM are apparent, but repurposing the 40-60% passive on-chip LLC area for massively parallel automata computation comes with several challenges. A naive approach that processes an input symbol every LLC access (~20-30 cycles @ 4GHz), would lead to an operating frequency comparable to DRAM-based AP (~200 MHz), negating the memory technology benefits. Increasing the operating frequency further can be made possible only by two insights. First, architecting an in-situ computation model that is cognizant

of the internal geometry of LLC slices. We observe that the LLC access latency is dominated by wire-delays inside a cache slice, accessing upper-level cache control structures, and network-on-chip. Fortunately, in-situ architectures require only SRAM array accesses and do not incur the overheads of a traditional cache access. We use sense-amplifier cycling techniques to further accelerate SRAM array access. We also leverage the internal geometry of LLC slices to build a hierarchical state-transition interconnect. All these optimizations lead to a speedup of 12×-15× over AP on average across a wide variety of automata benchmarks from the ANMLZoo [166] and Regex [43] benchmark suites using a 40 MB LLC.

# **1.3** Accelerating Pattern Matching in Genomics

Exact and approximate string matching find extensive utility in genomic data analysis. During primary analysis, a sequencing instrument splits the DNA molecule into *billions* of short ( $\sim$ 101 bp) strings called *reads*. Secondary analysis aligns each of the reads to a reference genome and determines genetic variants in the analyzed genome compared to the reference.

Short read alignment is one of the major compute bottlenecks in secondary analysis [30], contributing 30% to the overall runtime. In read alignment, these reads are aligned by matching them to a previously sequenced genome. This task is complicated by the fact that the new individual's genome may not exactly match that of the reference genome. In fact, the end goal is to determine the variants in the new genome. Naively aligning by matching a string to every possible position in the reference genome is computationally intractable. Popular read aligners such as BWA-MEM [118] and Bowtie [112] solve this using seeding. Seeding finds a set of candidate locations (hits) in the reference genome where a read can potentially align. Hits for a read are determined by finding exact matches for its sub-strings (seeds) in the reference. The seed-extension phase then uses approximate string matching to select the hit with the best score as the alignment position for the read.

Both the seeding and the seed-extension steps of read alignment are important candidates for

acceleration. Seeding contributes  $\sim$ 40% to the overall execution time of BWA-MEM2 [128] and seed-extension contributes 35%.

# 1.3.1 Enumerated Radix Trees: Enabling Memory Bandwidth-Aware Exact String Matching

We focus on seeding in BWA-MEM2, as it is the fastest available implementation of BWA-MEM, which is recommended as industry standard in the Broad Institute's best practices pipeline. The primary performance bottleneck in seeding is memory bandwidth. This is because both BWA-MEM and BWA-MEM2 use a compressed index structure (FMD-Index) that only allows iterative processing of each base in a read, leading to high bandwidth requirements.

BWA-MEM trades off high memory bandwidth for small memory space by using a highly compressed FMD-index (4.3 GB for human genome). In contrast, we propose a data structure for seeding that makes the opposite trade-off: it trades off increased memory space for reducing bandwidth, while still fitting within a modern server's main memory (64 GB). BWA-MEM2 also makes a similar tradeoff but our solution further improves bandwidth efficiency (4.3×) by virtue of supporting multi-character lookup and exploiting reuse opportunities present in the seeding algorithm.

We refer to our bandwidth-efficient data structure as Enumerated Radix Trees (ERT). Like FMD-index, ERT enables variable length exact match search functionality. But, unlike FMD-index, it avoids iterative lookup for every base on a large structure. It achieves this by coalescing all substrings in a reference genome that start with the same k-mer (string of length k, where k is less than the minimum length for a seed) together, and representing them using a variant of a radix tree. As we discuss later, ERT allows *multiple consecutive bases to be matched with one lookup*, and exhibits better spatial locality than FMD-index. ERT also helps *reduce computation when substrings* within a read that need to be matched with the reference *overlap* using a prefix-encoded radix tree.

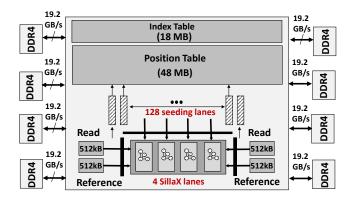

ERT's increase in bandwidth efficiency unlocks significant acceleration potential. To exploit

this acceleration potential, we design a custom seeding accelerator. The seeding accelerator leverages a butterfly network to efficiently feed data to parallel specialized seeding processors. Each seeding processor leverages light-weight context switching to provide high compute density and hide the long latency of DRAM accesses. *The FPGA ERT seeding accelerator can achieve up to* 2.8 million reads/s on AWS F1 FPGA resulting in a speedup of 2.6× over BWA-MEM2 seeding.

We open source the ERT software implementation for the benefit of the research community. ERT-based seeding is also integrated into BWA-MEM2 (ert branch: https://github.com/bwa-mem2/bwa-mem2/tree/ert)

#### 1.3.2 SillaX : Approximate String Matching Acceleration

Using the hits obtained from seeding, the seed-extension step performs pairwise approximate string matching between the read and reference substrings at each of the hit locations to determine the hit with the best score as the read's alignment position. Approximate string matches are scored using an *affine gap function* [134, 77], which is based on the Levenshtein edit distance, but weighs different edit types (insertion, substitution and deletion) differently. Apart from the alignment score, it is also required to output the trace of edits needed to align the read at the chosen reference position. This final step is referred to as *traceback*.

We propose a non-deterministic finite state automata for approximate string matching called Silla (String Independent Local Levenshtein Automata) and a corresponding hardware implementation based on Silla called SillaX. Silla has been designed from the ground up to support an efficient hardware implementation. Unlike the Levenshtein automata, Silla is string-independent and hardware-friendly since all state transitions are only to neighbouring states reducing communication complexity.

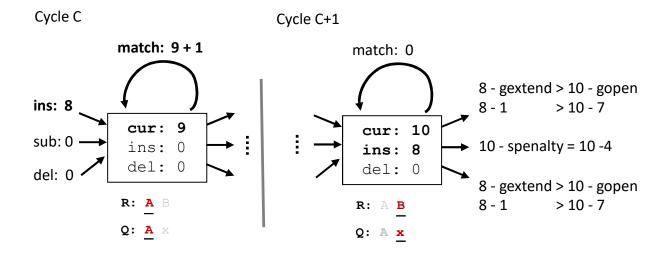

SillaX processing elements (PEs) are organized in the form of a systolic architecture. Each SillaX PE is customized to support affine gap scoring and traceback necessary to be used for seed-extension. SillaX also compresses traceback paths by keeping a count of matches in each PE. The proposed SillaX accelerator is also organized as composable sub-grids for flexibility. Compared

to alternate Smith-Waterman implementations for string matching [84], the processing elements in the SillaX edit-distance machine are  $30 \times$  smaller. Furthermore, SillaX supports in-place traceback. Prior approaches either require external traceback memory or increase the time complexity of traceback to  $\mathcal{O}(NlogN)$ . SillaX provides  $62.9 \times$  speedup over optimized banded Smith-Waterman running on a 56-thread CPU.

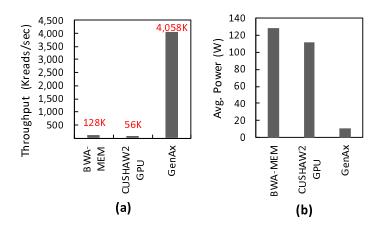

# 1.4 GenomicsBench: Characterizing the Genomics Computing Landscape

Genomics is at the forefront of the precision medicine revolution. Genome sequencing can help in early cancer detection [161], developing targeted therapies to different tumor mutations [95], identifying the causes of complex genetic diseases [186], assessing risk factors, and developing new drugs. For example, 42% of the drugs approved by FDA in 2018 were based on precision medicine data obtained from genome sequencing [29]. With the advent of portable and cheap sequencers, it is now feasible to test and monitor the emergence of novel infectious diseases such as COVID-19 [3] among our population and take timely action to prevent their spread.

Over the last decade, advances in high-throughput sequencing and the availability of portable sequencers have enabled fast and cheap access to genetic data. Of particular note, is the advent of third generation sequencing, which enables reading out longer sections of sample DNA, but with higher per-character error rates. For example, a single modern sequencer can produce several terabytes of data per day at the low cost of \$100 per human genome. As a result, sequencing data is now being produced at a rate that far outpaces Moore's law and poses significant computational challenges on commodity hardware. For a given sample, sequencers typically output fragments of the DNA in the sample. Depending on the sequencing technology, the fragments range from a length of 150-250 at high accuracy to lengths in few tens of thousands but at much lower accuracy. To meet this demand, software tools have been extensively redesigned and new algorithms and custom hardware have been developed to deal with the diversity in sequencing data. However,

a standard set of benchmarks that captures the diverse behaviors of these recent algorithms is lacking. We believe that the availability of such a benchmark suite will be crucial in facilitating future architectural exploration, specific to this rapidly growing important domain. Towards that end, we present the GenomicsBench benchmark suite which contains 12 computationally intensive data-parallel kernels drawn from popular bioinformatics software tools. It covers the major steps in short and long-read genome sequence analysis pipelines such as basecalling, sequence mapping, de-novo assembly, variant calling and polishing. We observe that while these genomics kernels have abundant data-level parallelism, it is often hard to exploit on commodity processors because of input-dependent irregularities. We also perform a detailed microarchitectural characterization of these kernels and identify their bottlenecks. GenomicsBench includes parallel versions of the source code with CPU and GPU implementations as applicable along with representative input datasets of two sizes - small and large.

#### **CHAPTER 2**

# **Background and Related Work**

In this chapter, we first provide background on how finite state automata can be used for pattern matching. We then describe prior compute-centric and memory-centric approaches to accelerate finite state automata computation. Later, we present some applications of pattern matching to genomics and describe prior hardware and software approaches to accelerate read alignment, a computationally intensive step in analyzing genomic data.

# 2.1 Finite State Automata for Pattern Matching

Non-Deterministic Finite State Automata (NFAs) form the core of many end-to-end applications that utilize pattern matching such as data analytics and data mining [169, 45], network security [181, 72, 110, 131], bioinformatics [148, 62, 172], tokenization of web pages [136], computational finance [18, 36] and software engineering [142, 58, 38]. In web browser frontends, finite state automata computations can contribute to about 40% of the loading time for many web pages [93]. The *oligo\_scan* routine used in Weeder 2.0, an open-source tool for motif discovery in DNA sequences contributes 30-62% of the total runtime [170]. In the *Apriori* algorithm for frequent itemset mining, NFA processing accounts for 33-95% of the execution time, based on the frequency threshold [168]. Prior work [190] has shown that without accelerating finite state automata operations, it is infeasible for these applications to achieve sustained performance improvement, no matter how well other parts of these applications are parallelized (Amdahl's law).

A Non-deterministic Finite Automata (NFA) is formally described by a quintuple  $\langle Q, \Sigma, \delta, q_0, F \rangle$ , where Q is a set of states,  $\Sigma$  is the input symbol alphabet,  $q_0$  is the set of start states and F is the set of reporting or accepting states. The transition function  $\delta\left(Q,\alpha\right)$  defines the set of states reached by Q on input symbol  $\alpha$ . The non-determinism is due to the fact that an NFA can have multiple states active at the same time and have multiple transitions on the same input symbol.

NFA computation entails processing a stream of input symbols one at a time, determining which of the current active states match an incoming input symbol (*state match*) and looking up the transition function to determine the next set of active states (*state transition*). Conventional compute-centric architectures store the complete transition function as a lookup table in the cache/memory. Since a lookup is required for every active state on every input symbol, symbol processing is bottlenecked by the available memory bandwidth. This leads to performance degradation especially for large NFAs with many active states. With limited memory bandwidth, the number of state transitions that can be processed in parallel is also limited. Converting these NFAs to equivalent deterministic finite state automata (DFAs) also cannot help improve performance since it leads to an exponential growth in the number of states.

## 2.2 Automata Processing Acceleration

# 2.2.1 Software Approaches

Conventional compute-centric architectures like CPUs and GPUs typically store NFAs as a state-transition matrix in cache/memory. These architectures have two main limitations: (1) need for high memory bandwidth or memory capacity especially for large NFA with many active states and (2) high instruction processing overheads per state transition (as many as 24 *x86* instructions for a single DFA state transition [44]). As a result, several CPU/GPU-based automata processing engines have either limited themselves to DFAs [44, 182, 41, 184] or have proposed optimizations that aim at reducing memory footprint and minimizing the memory bandwidth [183]. Several works have also explored automata-friendly cache or memory layouts [86, 173, 103].

To deal with the high cache miss rates and branch misprediction rates associated with the random access patterns of finite state automata, SIMD operations have been explored [136, 121]. Several speculative and enumerative parallelization approaches have also been proposed to speedup FSM processing [136, 190, 189, 145, 92]. Ladner and Fischer [111] parallelize deterministic FSMs (DFA) using parallel prefix-sums. Hillis and Steele [87] present an improved parallel prefix algorithm that reduces the execution time from  $O(log(m) \times n^3)$  to  $O(log(m) \times n)$  when executing on m processors. More recently, Todd and others [136] leverage classic parallel prefix sums to do enumeration of FSMs on modern hardware. The key contribution of their work is three fold: improving enumeration efficiency by reducing the dependence on n (number of states in the FSM) by cleverly leveraging convergence, demonstrating a scalable implementation on modern multicore processors with vector SIMD units and careful data mapping of the transition table based on the range of input symbols to improve the spatial locality of cache accesses. However, their work is limited to small DFAs, primarily due to the large computational complexity of enumerating NFAs.

To reduce the computational complexity and space footprint of conventional NFAs in multicore architectures, modular NFA architectures have also been proposed [178]. To improve locality of access, several small regular expressions and regular expressions with *common prefixes* are merged into larger segments. Parallelism is achieved by mapping these segments to separate threads, with each thread processing either the same or different inputs in parallel.

An alternative to enumerating all states is *speculation*, i.e. guessing the start states of input segments [190, 189, 145]. Speculation for parallelizing FSMs has been applied to specific application domains such as browser's frontend [94], JPEG decoder that uses parallel Huffman decoding [104], intrusion detection using hot state prediction [123], and speculative parsing [96]. Notably, Zhao and others [190, 189] introduce the concept of principled speculation, which is the first rigorous approach to speculative parallelization.

#### 2.2.2 Hardware Approaches

Compute-centric architectures: While several regular expression matching and DFA processing accelerators designs have been proposed in literature [162, 159], we discuss the two most relevant and recent designs. In general prior compute-centric hardware accelerators are limited by the number of parallel matches and transitions they can support. HARE [76] is a regular expression accelerator that is designed to match the DRAM memory bandwidth. However, the maximum number of simultaneous components that can be matched is limited to 64 even in the design with width = 32. This comes at an area cost of  $80mm^2$ . This limits its applicability for packet inspection which requires simultaneously matching against a large number of regular expressions (>3000). Also, its power grows quadratically with the number of patterns to be matched. On the other hand, the Unified Automata Processor [68] processes multiple input streams in parallel using vector lanes. However each lane is provided with only a 16 kB local bank, limiting the largest connected component in the NFA it can support. Furthermore, only 8 concurrent activations per lane are allowed and NFAs with many active states overflow the combining queue used in their design. This is a limiting factor for benchmarks that have hundreds to thousands of active states every cycle.

Memory-centric architectures: Micron's Automata Processor (AP) is an in-situ memory-based computational architecture targeted at accelerating automata processing and can facilitate highly parallel and energy efficient processing of finite state automata in hardware. Memory-centric architectures like the Micron Automata Processor (AP) [64, 167] are attractive for automata processing because the inherent bit-level parallelism of DRAM enables it to support multiple parallel state matches at bandwidths that far exceed the available off-chip pin bandwidth. Since the same input symbol can be matched against multiple states in parallel, instruction processing overheads are also reduced.

AP accelerates finite state automata processing by implementing NFA states and state transitions in memory. Each automata board fits in a DIMM slot and can be interfaced to a host CPU/F-PGA using the DDR/PCIe interface. Figure 2.1 illustrates the automata processor architecture.

Figure 2.1: Automata Processor interfaced with the host CPU.

The architecture uses DRAM columns to encode automata states and custom logic to encode state transitions in a routing matrix. The address bus is repurposed to stream input symbols.

Before processing in the AP, the classical representation of NFAs needs to be transformed to a compact ANML NFA representation [64] where *each state has valid outgoing transitions for only one input symbol*. Thus, each state in an ANML NFA can be *labeled* by one unique input symbol. ANML NFA computation entails processing a stream of input symbols one at a time. Initially, all the start states are active states. Each step has two phases. In the *state match* phase, we identify which of the active states have the same label as the current input symbol. In the *state transition* phase, we look up the transition table to determine the destination states for these matched states. These destination states would become the active states for the next step.

In the AP, the FSM states (called State Transition Elements or STEs) are stored as columns in DRAM arrays (256 bits). Each STE is programmed to the one-hot encoding of the 8-bit input symbol (same as it is *label*) that it is required to match against. For example, for an STE to match the input symbol a, the bit position corresponding to the  $97^{th}$  row must be set to 1. Each cycle, the input symbol (ASCII alphabet) is broadcast to all DRAM arrays and serves as the *row address*. If an STE has a '1' bit set in the row, it means that the label of the state it has stored matches the

input symbol. *State match* is then simply a DRAM row read operation, with the input symbol as the *row address* and the contents of the row determining the STEs that match against the input symbol. Thus, by broadcasting the input symbol to all DRAM arrays, it is possible to determine all the states that match the current input symbol in parallel. *State transitions* between currently active states to next states are accomplished by a proprietary interconnect (*routing matrix*) which encodes the transition function. Reconfiguring this interconnect requires a costly recompilation step. Only the states that match the current input symbol and are active, undergo state transition. The bits of a register (*active state mask*) at the bottom of the STE columns determine the set of STEs that are *active* in a particular symbol cycle. These bits are initially set for only *start states*. All active bits for all STEs can be independently set in a given cycle, as they are all mapped to different columns of the DRAM arrays. Thus, the AP allows any number of transitions to be triggered in a given cycle, enabling massive parallelism and efficient NFA processing.

Due to physical routing constraints, each logical AP device (D480) is organized hierarchically as half-cores, blocks, rows and STEs with no state transitions across half-cores. Therefore, each half-core can be considered as the smallest unit of parallellization for partitioning into input segments. STEs configured as *reporting* have no outgoing transitions and their results are communicated to the CPU by writing to an *output event buffer*. Each entry in this buffer contains a report code and a byte offset (in the input stream) of the symbol causing the report. These entries are parsed in the host and communicated to the user. The current generation AP contains 4 ranks of 8 D480 devices each. Each device consists of 2 half-cores encompassing 49152 STEs, organized into 192 blocks. Each block further contains 256 rows and each row stores 16 STEs. The Micron AP also includes block-level power gating circuitry that disables a block with no active states. In terms of the reporting hierarchy, each AP device is also partitioned into 6 output regions, with each output region storing a maximum of 1024 reporting elements. Also present are 768 counters and 2304 programmable boolean elements to augment pattern matching functionality.

Recent efforts at the University of Virginia's Center for Automata Processing have demonstrated that AP can outperform x86 CPUs by 256×, GPGPUs by 32×, and accelerators such as

# 2.3 Pattern Matching in Genomics

Genomics analysis is one application domain that extensively employs pattern matching. Genomics refers to the study of the structure, function and development of genes and gene expression in an individual. There are several computationally intensive problems in genomics that involve extensive string matching. Some examples include identifying a sequence of base pairs and matching those to a database of known strings (e.g., motif search) or aligning a fragment of a query genome against a reference genome to identify potential similarity (e.g., genotyping). Whole genome sequencing (WGS) which determines the complete DNA sequence of an organism's genome is of particular interest in the near term because of its relevance to precision medicine [83], wherein strategies for disease prevention and drug selection are developed and customized to meet the needs of an individual. Since human genomes across individuals are more than 99.9% similar, sequencing the genome of a new person can be made faster by mapping it to an already sequenced genome (also known as the reference genome).

### 2.3.1 Common Genomics Pipelines

In this subsection, we provide a brief summary of some of the common genomics pipelines used to analyze reads from different sequencing technologies (both short and long read sequencing data) (illustration in Figure 2.2). Section 6 provides a detailed description of the different computational steps involved in these pipelines. All three pipelines start with the raw sequencer output. Given a biological sample, typically, multiple copies of the contained genome sequence are extracted and then decomposed into smaller nucleotide fragments. A sequencer reads the sequence of nucleotides in the fragments and generates raw signals based on what it reads. The first step in all the three pipelines prior to downstream analyses is the interpretation of these signals to derive reads, which are sequences of bases over the nucleotide alphabet {A,C,G,T}. This step is called **basecalling**.

**Figure 2.2:** Common workflows in genomics.

(a) Reference-Guided Assembly. (b) De-Novo Assembly. (c) Metagenomics Classification

For Illumina sequencing machines, the signal data are fluorescence images which are converted into bases using a proprietary basecaller, Bustard [47]. For Oxford Nanopore (ONT) sequencers, raw signals are the current perturbations in the nanopore (e.g., in the FAST5 format). Guppy [175] is ONT's proprietary basecaller software. We characterize the open-source research basecaller from ONT, Bonito [4] as part of the nn-base kernel in GenomicsBench (Section 6.2), which demonstrates higher basecalling accuracy than Guppy [22].

**Reference Guided Assembly:** This pipeline reconstructs the sample genome by aligning reads from it to a reference genome and identifies differences in the sample (also called *variants*) compared to the reference genome. Typically, small differences, i.e., substitutions, short insertions and deletions (< 50 bases) are identified. Sufficient number of copies of the sample genome need to be sequenced to ensure random sequencing errors can be distinguished from true variations (each genome position is covered  $30 - 50 \times$  on average). This is especially needed for long reads from PacBio and ONT which have 5 - 15% error rate per base [175, 174], resulting in input datasets of

several hundreds of gigabytes. Subsequent analysis of this data can take several days on a modern multi-core processor [153].

Figure 2.2 (a) shows the two main time-consuming steps: (1) **Read Alignment**, which determines the best location for each read in the reference genome. (2) **Variant Calling**, which uses machine learning or statistics-based models to gather support for variants from aligned reads. BWA-MEM [118, 128] and GATK Haplotype Caller [8] are the most popular short-read software tools for these two steps recommended as part of GATK Best Practices [9]. These account for  $\sim$ 30-40% and  $\sim$ 40% time of the reference guided assembly pipeline respectively [128, 165].

De Novo Assembly: This pipeline attempts to assemble the reads into a genome  $de\ novo$  based on read overlaps in the absence of a suitable reference. The availability of long reads for de novo assembly has greatly improved the quality of draft reference genomes. This is mainly because they can span large structural variations (e.g, > 50 bases insertions/deletions, large rearrangements between the sample and reference genomes) [126] and can help resolve mutations from maternal and paternal chromosomes [151]. Long read de novo assembly is typically done using the *overlap-layout-consensus* method as shown in Figure 2.2 (b). In the overlap identification step, common seeds shared between read pairs are used to identify potential overlapping regions. In the layout step, these overlapping regions are extended into larger contiguous regions. Finally the consensus step corrects small errors in assembly. Large assembly errors are corrected in a later graph-based polishing step. For long-read assembly and polishing, Flye [105] and Racon [163] are popular software tools. Assembly of the human genome using Flye [105] and Racon [163] takes  $\sim$ 4.5 days on a 64-thread server, each contributing  $\sim$ 30% to the overall time [153]. Basecalling is performed using Guppy [175], ONT's proprietary basecaller, and also accounts for  $\sim$ 30% of overall time [153].

**Metagenomics Classification:** The advent of portable sequencers like ONT MinION [27] has enabled several applications like real-time pathogen detection [146] and microbial abundance estimation [115] in the field. Abundance estimation involves aligning input microbial reads to a reference pan-genome (consisting of reference genomes of all bacteria, virus, fungi and humans)

and later estimating the proportion of different microbes in the sample as shown in Figure 2.2 (c). It is typically performed using software tools like Minimap2 [119] and Centrifuge [100].

#### 2.3.2 Read Alignment

In this dissertation, we focus on accelerating the read alignment step, which is one of the computationally intensive parts of the reference guided assembly pipeline ( $\sim$ 30% of overall analysis time in GATK's best practices workflow [9]). Read alignment essentially maps a large number of sequenced reads to a reference genome using a combination of exact and approximate string matching algorithms. Read alignment is hard and time consuming because of the need to account for true variations between individuals (i.e., substitution, insertion, deletions of bases) [156], to detect and tolerate sequencing errors, the presence of a large number of repeated sequences ( $\sim$ 50% of human genome [152]) and structural variants usually associated with abnormalities.

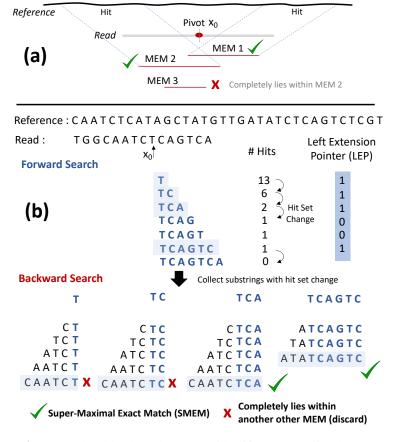

Since scanning the reference genome to identify the location for each read is computationally infeasible, state-of-the-art software tools for read alignment [118, 112, 125] use the seed-and-extend heuristic. Seeding identifies a set of candidate locations (hits) in the reference genome where the read can potentially align, by querying an index of the reference genome for the locations of short exact matches (seeds) from the read. The hits are then verified by an approximate string matching step called seed-extension, that extends these 'seeds' in both directions while allowing for gaps (i.e., insertions or deletions) and mismatches.

#### 2.3.2.A Seeding

FMD-index [116], suffix-trees, suffix arrays [63] and hash-tables [130] are the most commonly used data structures for seeding. We focus on FMD-index based seeding in this dissertation since it is used in BWA-MEM/BWA-MEM2, which is recommended as part of GATK's Best Practices pipeline. While this work focuses on FMD-index based seeding, there exists a rich body of work that also uses hash-tables for seeding [35, 98, 177, 185] and have optimized its cache behavior [81, 82].

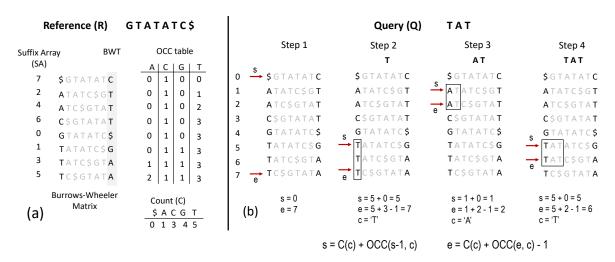

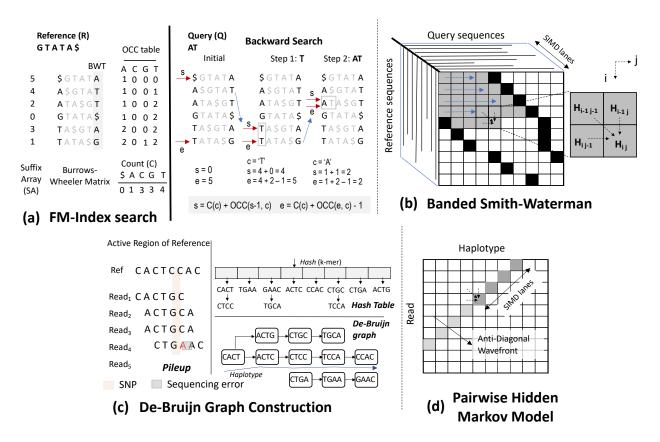

**FMD-Index:** To identify seeds and their locations in the reference genome, popular read alignment tools like BWA-MEM/BWA-MEM2 use a highly compressed data structure called the FMD-index [117, 71] which is built using both strands of DNA. As shown in Figure 2.3 (a), the FMD-index consists of: (1) the *suffix array* (SA), which contains the locations of lexicographically sorted suffixes of the reference genome R, (2) the *Burrows Wheeler Transform* (BWT), computed as the last column of the cyclically sorted suffix array of the reference, (3) the *count table* (C) which stores the number of characters in R lexicographically smaller than a given character c and (4) the *occurrence table* (C) which stores the number of occurrences of a character up to a certain index in the suffix array. Using the count and occurrence tables, one can identify intervals (c) and c) in

**Figure 2.3:** FM-index example. (a) FM-index for reference R (b) Backward search using the FM-index.

the Burrows-Wheeler matrix where a particular query string exists in the reference by performing iterative lookups for each successive character in the query as shown in Figure 2.3 (b).

**CPU-/GPU-based Seeding:** FMD-index based seeding [117, 71] involves many irregular memory accesses and has been found to be bottlenecked by LLC and TLB misses on CPUs [49, 187]. Prior work has explored reordering memory accesses [187] and performing *n*-character lookup on an *n*-step FMD-index [49] to improve the locality and data requirements of FMD-index based seeding. Data-parallel architectures such as GPUs have also been leveraged to accelerate FMD-

index search [48] by virtue of their high memory bandwidth and memory level parallelism.

Seeding Accelerators: Seeding accelerators based on the FMD-index use custom bit-wise operations to traverse the index and improve memory parallelism [171, 52, 60]. However, these implementations soon hit the memory-bandwidth roofline. Several other read alignment accelerators have also been proposed in literature [1, 127] that use hash-tables (with fixed-length keys) in novel ways to perform variable-length seeding. However, hash-based seeding algorithms produce a large number of seeds and hits that need to be verified by seed-extension and often need to be coupled with filtration algorithms [101, 176] to achieve comparable accuracy to variable-length seeds produced by FMD-index seeding.

#### 2.3.2.B Seed-Extension

The fundamental operation in seed-extension is approximate string matching [155, 185]. Dynamic-programming and automata-based approaches are commonly used for approximate string matching.

**Dynamic Programming:** The most widely used algorithm in sequencing software is a dynamic programming algorithm called Smith-Waterman [154]. It computes optimal local alignments between two sequences by comparing segments of all possible lengths. It operates in two phases. *Score-computation* builds the dynamic programming matrix  $(N^2)$  based on a general scoring scheme. Then *traceback* constructs the optimal alignment by tracing back pointers starting from the highest scoring cell. It fundamentally has  $\mathcal{O}(N^2)$  time and space complexity. While there have been several optimizations [70, 135], and approximation heuristics [188] developed to reduce their time, it does not scale well as string length increases.

Several FPGA-based hardware accelerators have been proposed for the Smith-Waterman algorithm [56, 127]. These leverage wavefront parallelism in systolic arrays to accelerate the *score-computation* phase of the Smith-Waterman algorithm. There has also been work on banded implementations of the Smith-Waterman algorithm [84], where only cells within a 2K + 1 band around the principal diagonal of the Smith-Waterman matrix are computed. Most of these accelerators

Figure 2.4: Levenshtein Automata for edit distance K = 1 and reference string AGC.

also either offload the *traceback* phase to software or have traceback support only for short string lengths for an additional  $\mathcal{O}(N)$  space overhead [139, 140, 127, 54].

**Automata-based:** The Levenshtein Automata (LA) for approximate string matching accepts all strings that lie within K edit distance of its stored pattern. Figure 2.4 shows an example LA. Each state essentially represents the position in the reference string up to which a match has been found, and the number of edits seen so far. As a result, it has a total of K \* N states. Its time complexity is  $\mathcal{O}(N^2)$ , as in the worst case all of its states may be active. Sequencing software systems rarely use LA based implementations as they struggle to outperform Smith-Waterman.

In-memory [65, 157] and ASIC automata accelerators [76, 69] can be used to implement LA. However, LA is poorly suited for hardware acceleration due to several reasons. One, since it is string dependent, the hardware needs to be reprogrammed every time the string changes, which can be prohibitive especially for seed-extension in sequencing. It requires processing billions of different reads, where each read needs to be compared to several seeds in the reference. Two, its space requirement is proportional to string length. When read lengths increase to millions of bases, LA based hardware solutions would be impractical. Third, none of the existing hardware automata accelerators support unique features required in sequence aligners: scoring, clipping, and traceback. It is challenging to include these features. For example, adding logic to compute affine gap scores for state transitions in Micron's Automata Processor (AP) is likely to be expensive.

A recent advancement in automata theory called Universal Levenshtein Automata (ULA) addressed some of the limitations of LA [133]. While ULA is string independent, it does not efficiently map to a hardware accelerator as communication between states are not local. Also, each state has a high-degree of fan-out  $(\mathcal{O}(K))$ , as every state in ULA is connected to a state in every

higher level of edit distance to support deletions. To date, there is no hardware realization of the Universal Levenshtein Automata (ULA), nor has it been used in sequencing software.

# **CHAPTER 3**

# Parallel Pattern Matching on In-Memory Hardware Accelerators

Spatial in-memory hardware accelerators like Micron's Automata Processor can accelerate automata processing by performing massively bit-parallel state-match and state-transition. However, they can still be bottlenecked by sequential processing of the input stream. To break this sequential execution bottleneck, enumerative parallelization is an attractive option. However, realizing enumerative parallelization in a non-von Neumann hardware accelerator substrate like the Micron Automata Processor comes with several challenges. In this chapter, we present these challenges and discuss architectural extensions to enable low-cost enumerative parallelization on the Automata Processor.

# 3.1 Finite State Machine Parallelization

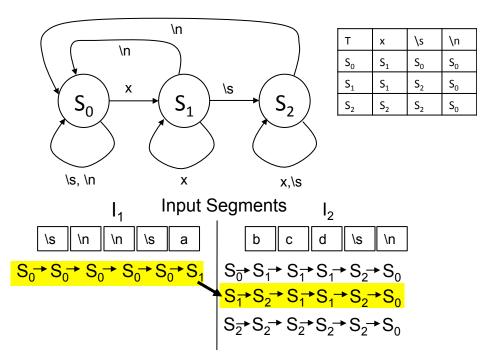

Parallelizing finite state machine (FSM) traversal is known to be extremely difficult due to the inherent sequential nature of computation arising because of dependencies between consecutive state transitions. One way to parallelize FSM traversal is by partitioning the input string into segments, and processing these segments concurrently. This is feasible because FSM computation can be expressed as a *composition of transition functions* [87]. Parallelization is possible because transition function composition is *associative*. Figure 3.1 shows an example of FSM parallelization with two input segments ( $I_1$  and  $I_2$ ) each with five symbols. The FSM shown detects the first word

in every line. The transition table is shown on right. Both these segments can be executed in parallel to provide a speedup of  $2\times$  over the sequential baseline.

**Figure 3.1:** An FSM example with enumeration. The FSM detects the first word in every line.

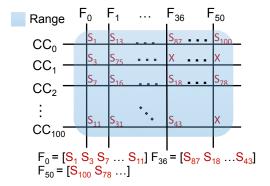

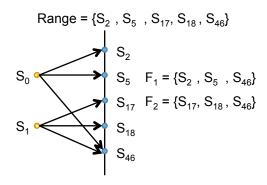

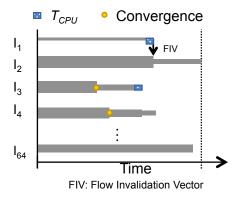

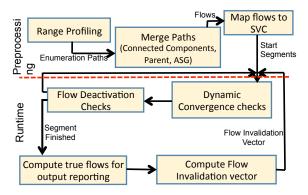

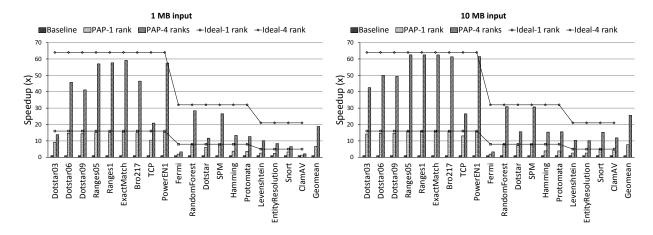

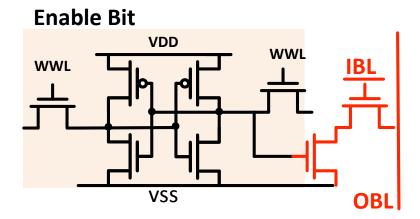

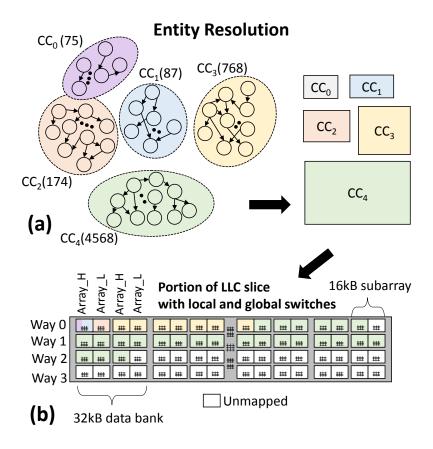

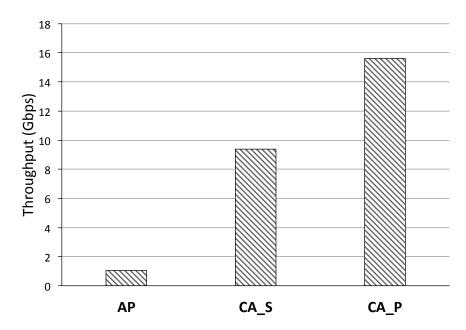

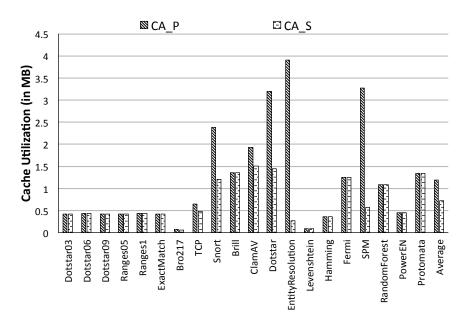

However, the starting states for each input segment, except the first segment are unknown. The starting states for the first input segment are the initial start states. The starting states for other segments are essentially the ending states of the corresponding previous segment. These dependencies prevent concurrent execution among threads. This problem can be solved by leveraging the classic parallel prefix-sum [111] algorithm. The basic idea is to execute the second segment for *every state* of the FSM. This method is referred to as an enumerative computation, since it involves processing each input symbol for all possible start states [136].