# Efficient Deep Learning Accelerator Architectures by Model Compression and Data Orchestration

by

Jie-Fang Zhang

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical and Computer Engineering) in The University of Michigan 2022

Doctoral Committee:

Professor Zhengya Zhang, Chair Associate Professor Ronald G. Dreslinski Assistant Professor Hun-Seok Kim Professor Dennis Sylvester Jie-Fang Zhang jfzhang@umich.edu © ORCID iD 0000-0002-6609-4383

© Jie-Fang Zhang 2022 All Rights Reserved To my family and Yu-Hsien for always being there for me. And to all the moments of frustration in life.

### ACKNOWLEDGEMENTS

I would like to thank my advisor, Professor Zhengya Zhang, who has given me guidance and advice on both research and life. Thank you for being patient and believing in me whenever I struggle to find a more interesting research topic or try to make a research direction more interesting. I would also like to thank Professor Dennis Sylvester, Professor Hun-Seok Kim, and Professor Ronald Dreslinski for being on my dissertation committee and providing valuable feedback.

I have had the pleasure working with many talented people in the VLSISP group. Thanks to Shuanghong, Shiming, Thomas, Wei, Chester, Sung-Gun, Alex, Teyuh, Yaoyu, Reid, Jacob, Junkang, Cheng-Hsun, Jack, and Justin, for the valuable help and discussions about research and life struggles.

Thanks to all the research collaborators. Especially, thanks to Chester Liu, Thomas Chen, Wei Tang, Tim Wesley, and Cheng Fu for their help on the SNAP chip tapeout. And thanks to Ching-En (Alex) Lee, Sophia Shao, Steve Keckler for their helpful advice on the Stitch-X/SNAP project. Thanks to Yi-Chung Wu, Reid Pinkham, Chester Liu, Shang-En Huang, and Wei Tang for their help and discussion on the Point-X project. Thanks to Shang-En Huang, Miao Yin, and Salar Latifi for the insightful advice about the TetriX project.

Thanks to my family, Yu-Hsien, and my friends for always supporting and encouraging me throughout the journey.

# TABLE OF CONTENTS

| DEDICATION                                                                      | ii                           |

|---------------------------------------------------------------------------------|------------------------------|

| ACKNOWLEDGEMENTS                                                                | iii                          |

| LIST OF FIGURES                                                                 | vii                          |

| LIST OF TABLES                                                                  | х                            |

| LIST OF ABBREVIATIONS                                                           | xi                           |

| ABSTRACT                                                                        | xiv                          |

| CHAPTER                                                                         |                              |

| I. Introduction                                                                 | 1                            |

| 1.1       DNN Computation                                                       | $2 \\ 3 \\ 4 \\ 6 \\ 7 \\ 8$ |

| II. SNAP: Accelerator Architecture for Unstructured Sparse Neu-<br>ral Networks | 10                           |

| 2.1.1 Channel-Last Dataflow for Sparse DNN Processing .                         | 14<br>15<br>17               |

| 2.2 Channel-First Processing Dataflow                                           | 17<br>17<br>17<br>19         |

| 2.3 Channel Index Matching                                                      | 19<br>21<br>22<br>22         |

|             |              | 2.3.3 Design Tradeoff Exploration                         | 24              |

|-------------|--------------|-----------------------------------------------------------|-----------------|

|             | 2.4          | Two-Level Partial Sum Reduction                           | 25              |

|             |              | 2.4.1 PE-level Channel-Dimension Reduction                | 25              |

|             |              | 2.4.2 Core-Level Pixel-Dimension Reduction                | 27              |

|             |              | 2.4.3 Support for Pointwise CONV and FC                   | 28              |

|             | 2.5          | Implementation and Evaluation Results                     | $\frac{-0}{29}$ |

|             | 2.0          | 2.5.1 SNAP Architecture Overview                          | 29              |

|             |              | 2.5.2 Performance Analysis                                | 31              |

|             |              | 2.5.3 Comparison Against State-of-the-art Works           | 34              |

|             | 2.6          | Summary                                                   | 38              |

| ттт         | <b>D</b> • 4 |                                                           |                 |

| 111.        |              | -X: Spatial-Locality-Aware Accelerator Architecture for   | 20              |

|             | Grapi        | h-Based Point-Cloud Neural Networks                       | 39              |

|             | 3.1          | Background                                                | 44              |

|             |              | 3.1.1 Edge Convolution Computation                        | 44              |

|             |              | 3.1.2 Computation Models and Bottlenecks                  | 45              |

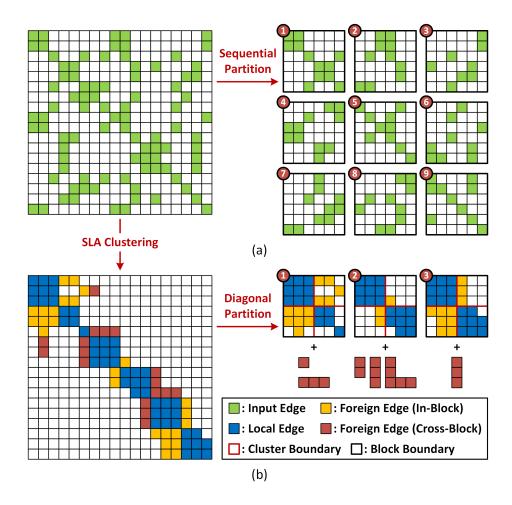

|             | 3.2          | Spatial-Locality-Aware Clustering                         | 48              |

|             | 0.2          | 3.2.1 Graph Traversal for Spatial Locality                | 48              |

|             |              | 3.2.2 Speculative Breadth-First Search (SBFS) Traversal . | 52              |

|             |              | 3.2.3 SLA Clustering Module Implementation                | 53              |

|             | 3.3          | Locality-Aware NoC                                        | 55              |

|             | 0.0          | 3.3.1 Chain NoC Architecture                              | 55              |

|             |              | 3.3.2 Routing Algorithm                                   | 56              |

|             | 3.4          | CTile Architecture                                        | 58              |

|             | 3.5          | Point-X System Architecture                               | 61              |

|             |              | 3.5.1 Multi-Mode Dataflow                                 | 62              |

|             |              | 3.5.2 Workload Partitioning                               | 64              |

|             | 3.6          | Benchmarking and Evaluation                               | 65              |

|             |              | 3.6.1 Evaluation Methodology                              | 66              |

|             |              | 3.6.2 Area, Performance, Efficiency Analysis              | 67              |

|             |              | 3.6.3 Workload Scalability Analysis                       | 68              |

|             |              | 3.6.4 Performance Comparison                              | 69              |

|             | 3.7          | Related Work                                              | 72              |

|             | 3.8          | Summary                                                   | 73              |

| <b>TX</b> 7 | Totai        | X: Efficient Accelerator Architecture for Flexible Ten-   |                 |

| 1 V .       |              | ed Neural Network Processing                              | 75              |

|             |              | 0                                                         |                 |

|             | 4.1          | Background                                                | 78              |

|             |              | 4.1.1 Tensor Decomposition Methods                        | 79              |

|             |              | 4.1.2 TNN Inference with Tensor Contraction               | 83              |

|             |              | 4.1.3 Computation Challenges                              | 84              |

|             | 4.2          | Optimal Contraction Sequence Search                       | 85              |

|             |              | 4.2.1 Tensor Network Representation                       | 86              |

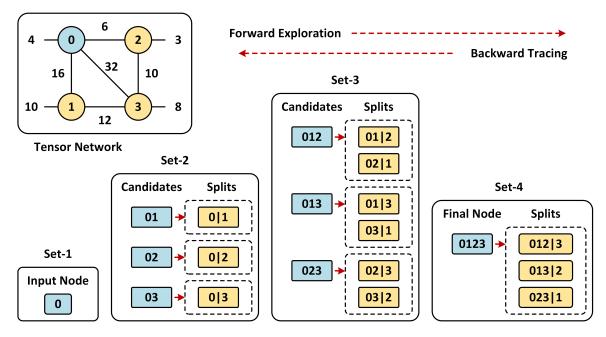

|           | 4.2.2      | Breadth-First Contraction Search           | 87  |

|-----------|------------|--------------------------------------------|-----|

|           | 4.2.3      | Contraction Sequence Analysis              | 88  |

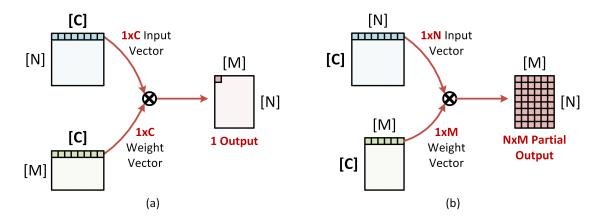

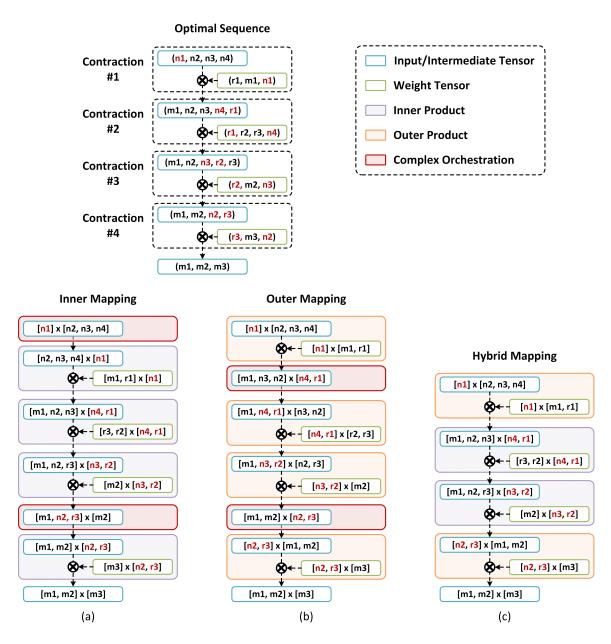

| 4.3       | Hybrid (   | Contraction Sequence Mapping               | 90  |

|           | 4.3.1      | Limitation of Baseline Mapping             | 90  |

|           | 4.3.2      | Hybrid Inner-Outer Product Mapping         | 93  |

| 4.4       | TetriX S   | System Architecture                        | 95  |

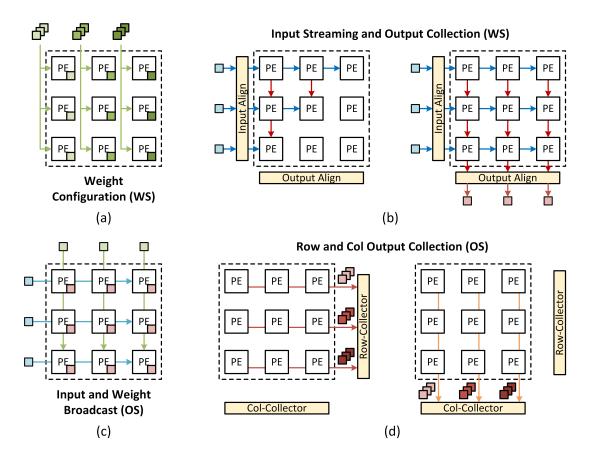

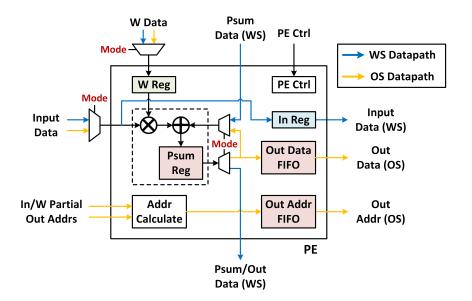

|           | 4.4.1      | Configurable Stationary Dataflow           | 97  |

|           | 4.4.2      | Index Translation                          | 99  |

|           | 4.4.3      | Output Gathering                           | 101 |

| 4.5       | Benchm     | arking and Evaluation                      | 103 |

|           | 4.5.1      | Evaluation Methodology                     | 103 |

|           | 4.5.2      | Performance, and Mapping Efficacy Analysis | 103 |

|           | 4.5.3      | Performance Comparison                     | 106 |

| 4.6       | Summar     | · · · · · · · · · · · · · · · · · · ·      | 108 |

|           |            |                                            |     |

| V. Conc   | lusion an  | d Outlook                                  | 109 |

|           |            |                                            |     |

|           |            |                                            |     |

| BIBLIOGRA | <b>PHY</b> |                                            | 112 |

# LIST OF FIGURES

# Figure

| 1.1          | Top-1 accuracy, size, and complexity of modern DNN models. Adapted from [1].                                                              | 1               |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 1.2          | Core computations of DNNs: (a) vector-matrix multiplication in MLP and RNN, and (b) 2D convolution in CNN.                                | 2               |

| 1.3          | Evolution of model size in the fields of (a) CV and (b) NLP. Adapted from [2].                                                            | 4               |

| 1.4          | Common model compression techniques: (a) data quantization, (b) network sparsification, and (c) tensor decomposition.                     | 5               |

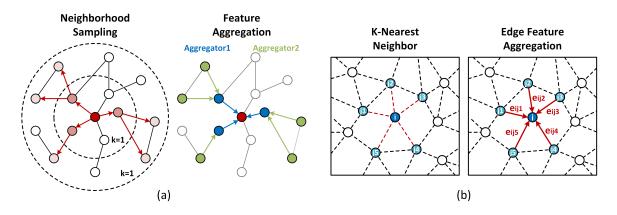

| 1.5          | Examples of novel operations: (a) GraphSAGE in GNNs and (b) EdgeCONV in point-cloud networks. Adapted from [3, 4]                         | 6               |

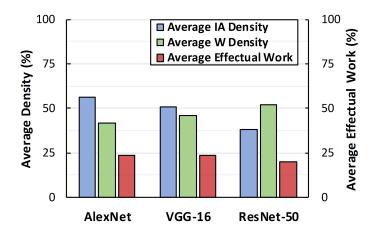

| 2.1          | Average density of IA, W data and average effectual work of common DNNs after network pruning                                             | 11              |

| 2.2          | Convolution computation between unstructured sparse IA and W in<br>a sparse DNN. The colored cells indicate nonzero entries, and the      | 10              |

|              | white cells indicate zero entries.                                                                                                        | 12              |

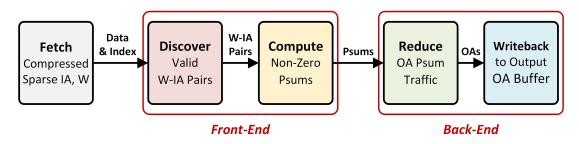

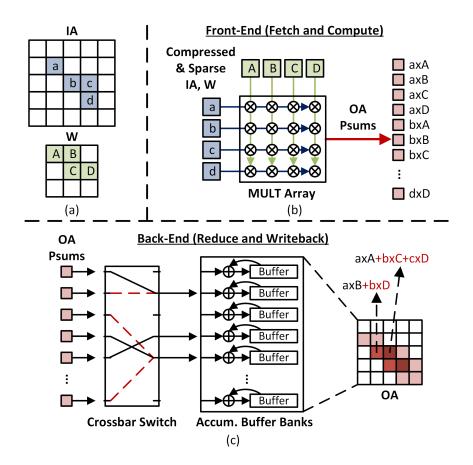

| 2.3          | Processing pipeline of a sparse DNN processor                                                                                             | 12              |

| 2.4          | Illustration of channel-last data<br>flow for sparse DNN processing                                                                       | 15              |

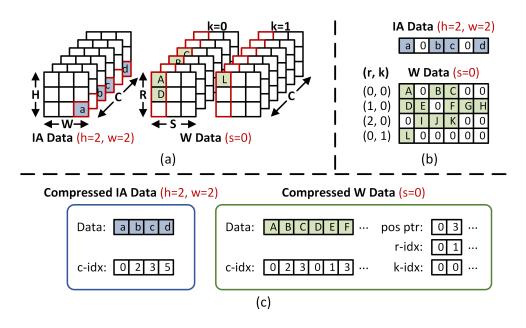

| 2.5          | Channel-first compression in SNAP                                                                                                         | 18              |

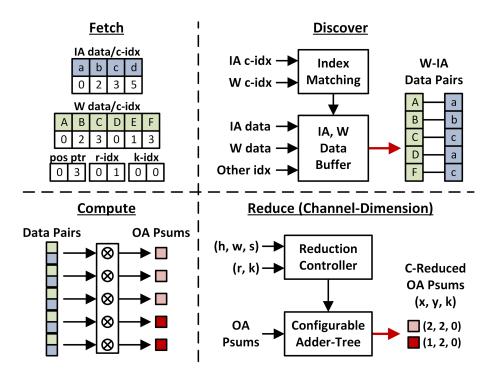

| 2.6          | SNAP's channel-first dataflow with channel index matching and psum                                                                        |                 |

|              | reduction along the channel dimension                                                                                                     | 20              |

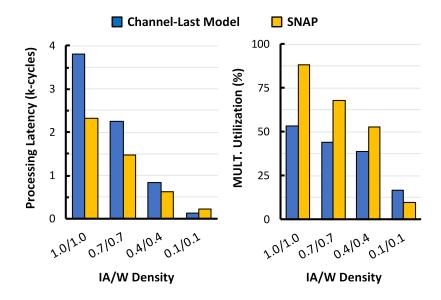

| 2.7          | Comparison between channel-last dataflow and SNAP (channel-first                                                                          |                 |

|              | dataflow) for dense, medium and sparse workloads                                                                                          | 21              |

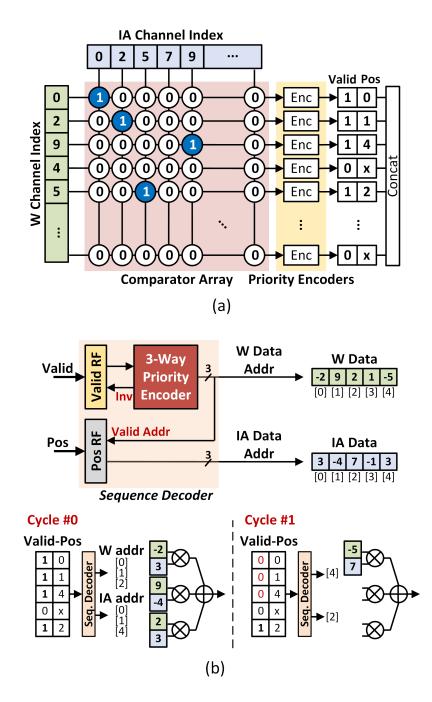

| 2.8          | (a) Microarchitecture of associative index matching (AIM), and (b)                                                                        |                 |

|              | microarchitecture of sequence decoder and step-by-step example of                                                                         |                 |

|              | W-IA data pair dispatch in a PE                                                                                                           | 23              |

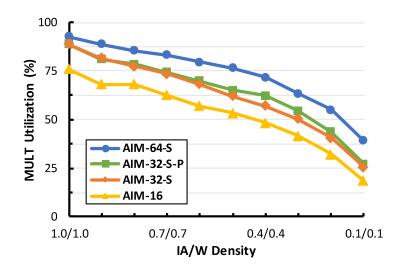

| 2.9          | Multiplier utilization of AIM designs at different data density levels.                                                                   | 24              |

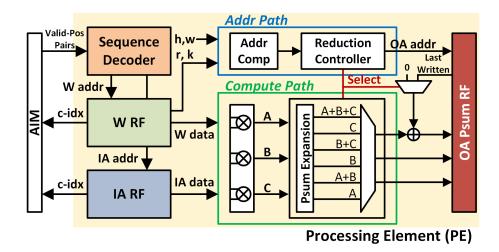

| 2.10         | PE microarchitecture and psum reduction along the channel dimension.                                                                      | 25              |

| 2.11         | Psum reduction configuration across an array of PEs (a) $3 \times 3$ CONV in diagonal mode, (b) pointwise CONV in row mode, and (c) FC in |                 |

|              | row mode.                                                                                                                                 | 27              |

| 2.12         | SNAP system architecture.                                                                                                                 | $\frac{21}{30}$ |

| 2.12<br>2.13 | Microphoto of the 16nm SNAP test chip.                                                                                                    | 31              |

| 2.10         | merophoto of the form STAL test clipt                                                                                                     | υı              |

| 2.14 | (a) Measured power consumption at different operating frequencies<br>and the optimal supply voltages, and (b) measured effectual energy              |     |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 0.15 | efficiency for synthetic sparse workloads at different data density levels.                                                                          | 32  |

| 2.15 | Processing speedup by SNAP (a channel-first dataflow) and a channel-                                                                                 |     |

|      | last dataflow over a dense accelerator baseline running the residual                                                                                 | იე  |

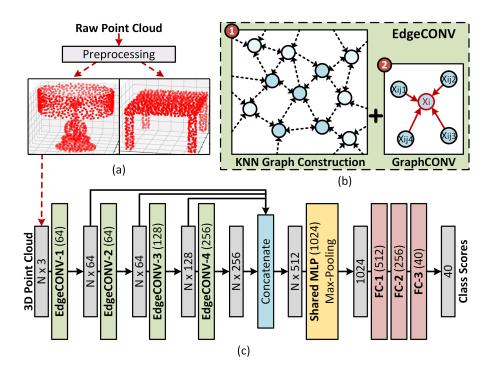

| 3.1  | blocks of a sparse ResNet-50 model                                                                                                                   | 33  |

| 0.1  | Illustration of (a) point cloud recognition pipeline, (b) EdgeCONV layer divided into KNN graph construction and GraphCONV on ver-                   |     |

|      | tex point $i$ , and (c) DGCNN's network architecture for 3D object                                                                                   |     |

|      | classification $[4]$ .                                                                                                                               | 40  |

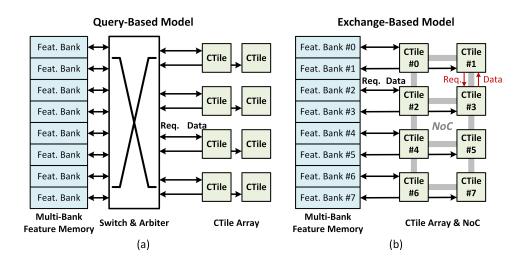

| 3.2  | EdgeCONV computation models: (a) query-based model, and (b)                                                                                          | 40  |

| 5.2  | exchange-based model.                                                                                                                                | 46  |

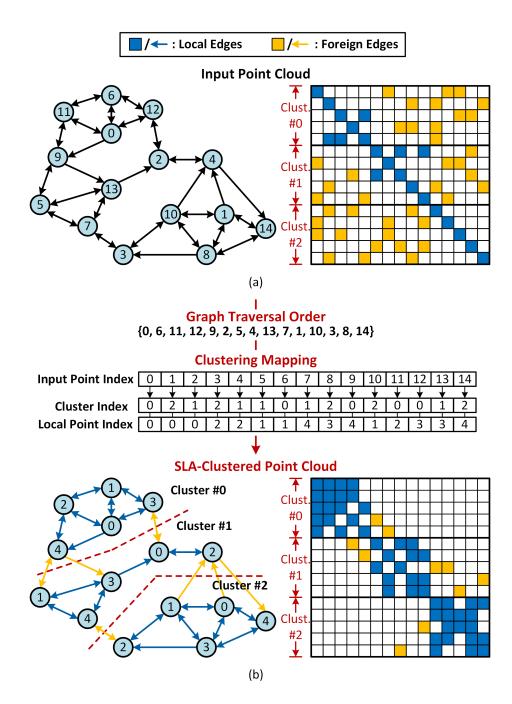

| 3.3  | (a) KNN graph of input point cloud and its adjacency matrix repre-                                                                                   | 10  |

| 0.0  | sentation; (b) the KNN graph is traversed and the points clustered                                                                                   |     |

|      | following traversal order; the clustered KNN graph and its adjacency                                                                                 |     |

|      | matrix are shown.                                                                                                                                    | 49  |

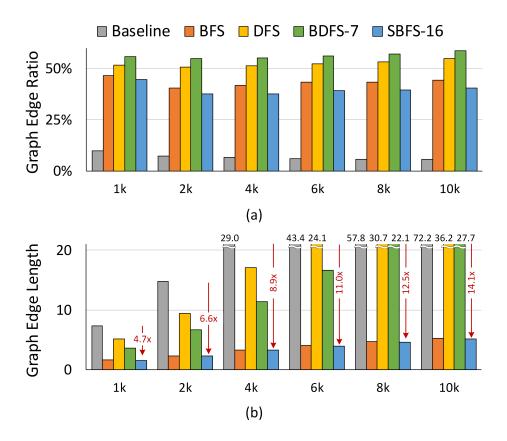

| 3.4  | Clustering performance on KNN graphs: (a) graph edge ratio, and                                                                                      | 10  |

| 0.1  | (b) graph edge length, using different graph traversal methods on 1k                                                                                 |     |

|      | to 10k point clouds                                                                                                                                  | 51  |

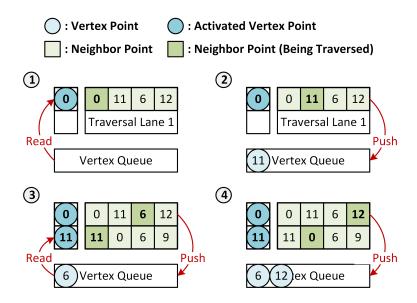

| 3.5  | Illustration of the SBFS algorithm with 2 traversal lanes                                                                                            | 52  |

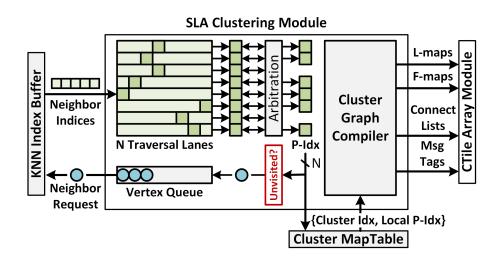

| 3.6  | Architecture and dataflow of SLA clustering module.                                                                                                  | 54  |

| 3.7  | Speedup of the SLA clustering module using SBFS with different                                                                                       |     |

|      | traversal lane numbers over a BFS implementation baseline                                                                                            | 54  |

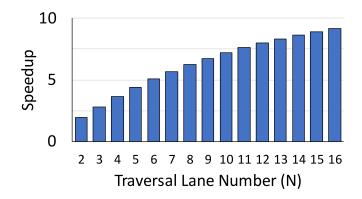

| 3.8  | Architecture of (a) a chain NoC, and (b) a router for chain NoC                                                                                      | 56  |

| 3.9  | Microarchitecture of (a) a compute tile (CTile), (b) a compute engine,                                                                               |     |

|      | and (c) a sort engine.                                                                                                                               | 58  |

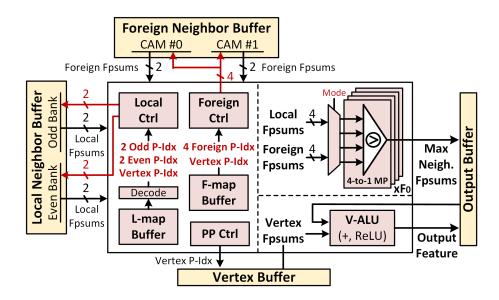

| 3.10 | Microarchitecture of a group engine                                                                                                                  | 60  |

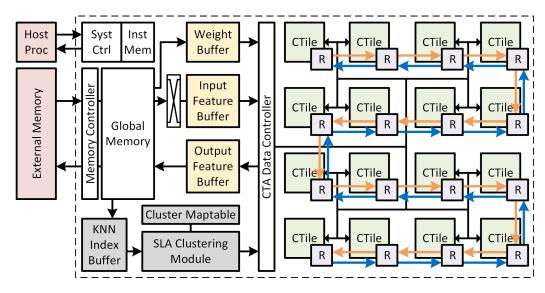

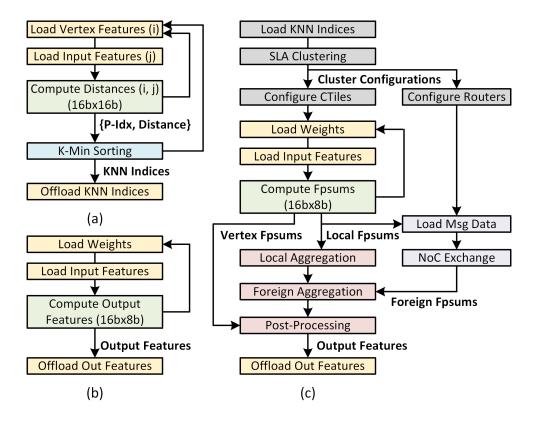

| 3.11 | Point-X system architecture                                                                                                                          | 61  |

| 3.12 | Multi-mode dataflow for (a) KNN graph construction, (b) shared                                                                                       |     |

|      | MLP and FC, and (c) GraphCONV operations. $\ldots$ $\ldots$ $\ldots$                                                                                 | 63  |

| 3.13 | Workload partition schemes: (a) sequential partition and (b) diagonal                                                                                |     |

|      | partition                                                                                                                                            | 64  |

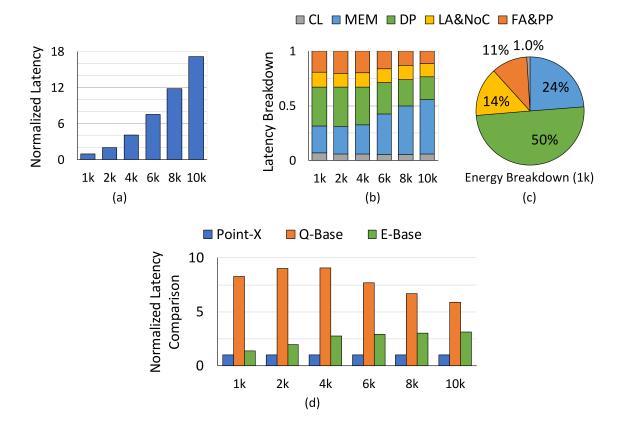

| 3.14 | (a) Normalized latency, (b) latency breakdown, and (c) energy break-                                                                                 |     |

|      | down of Point-X for GraphCONV workloads in DGCNN; (d) nor-                                                                                           |     |

|      | malized latency comparison of Point-X to query-based (Q-Base) and                                                                                    |     |

|      | the exchange-based (E-Base) baselines for GraphCONV workloads of                                                                                     |     |

|      | each point size.                                                                                                                                     | 69  |

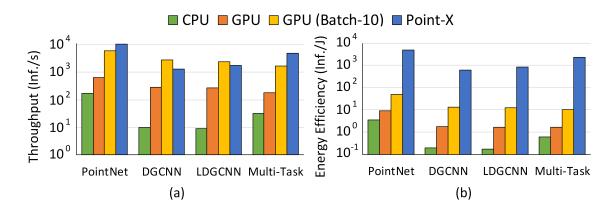

| 3.15 | Comparison of (a) throughput and (b) energy efficiency of Point-X                                                                                    |     |

|      | to the CPU and GPU baselines.                                                                                                                        | 71  |

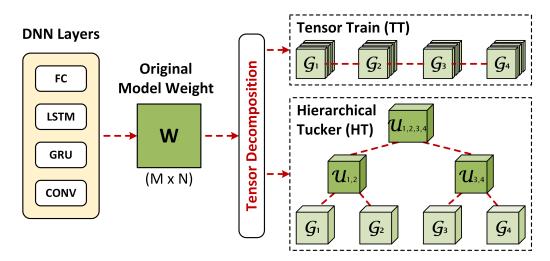

| 4.1  | Illustration of model weight and tensor decomposition for TNNs                                                                                       | 76  |

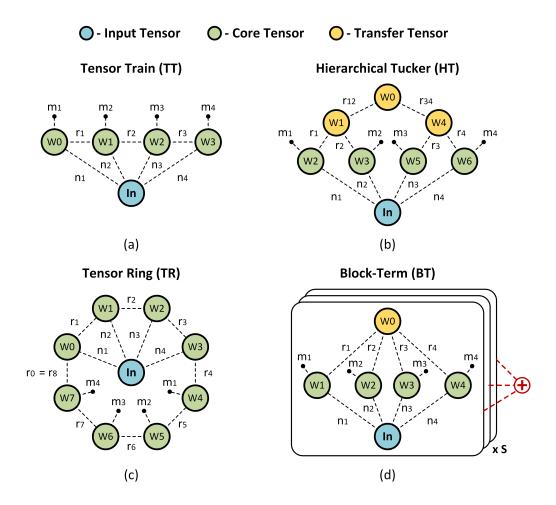

| 4.2  | Tensor network graph representation of TNN layer with (a) TT, (b)                                                                                    |     |

|      | HT, (c) TR, and (d) BT tensor decomposition methods, where the $T_{n}$                                                                               | 0.0 |

| 4.9  | input tensor $\in \mathbb{R}^{n_1 \times n_2 \times n_3 \times n_4}$ and the output tensor $\in \mathbb{R}^{m_1 \times m_2 \times m_3 \times m_4}$ . | 86  |

| 4.3  | Illustration of breadth-first approach for optimal contraction sequence                                                                              | 00  |

|      | search                                                                                                                                               | 88  |

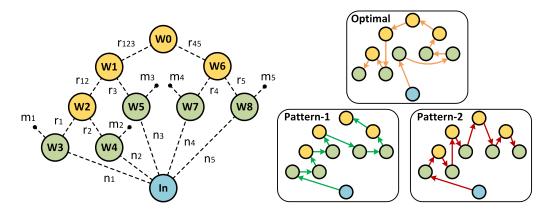

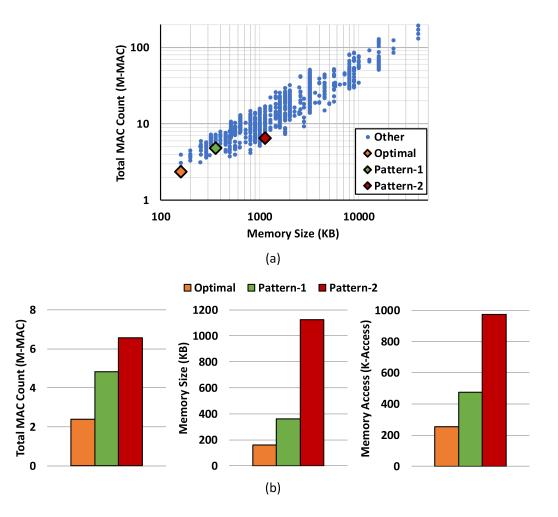

| 4.4  | Illustration of contraction sequences for an HT-TNN layer inference<br>example: optimal sequence (Optimal) and fixed contraction patterns     | 00  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4 5  | used in previous works (Pattern-1, Pattern-2).                                                                                                | 89  |

| 4.5  | (a) Contraction sequence space in terms of total MAC operations                                                                               |     |

|      | and required memory size; (b) comparison of contraction sequences in                                                                          |     |

|      | total MAC operations, required memory size, and number of memory                                                                              | ~ ~ |

|      | accesses.                                                                                                                                     | 89  |

| 4.6  | Illustration of (a) inner product and (b) outer product operation and memory layout.                                                          | 91  |

| 4.7  | Example of the mapping options for an optimal contraction sequence:                                                                           |     |

|      | (a) inner-only mapping, (b) outer-only mapping, and (c) hybrid inner-<br>outer mapping, where the dimensions for contraction are indicated in |     |

|      | red                                                                                                                                           | 92  |

| 4.8  | TetriX system architecture                                                                                                                    | 96  |

| 4.9  | Illustration of WS and OS dataflows in TetriX architecture                                                                                    | 97  |

| 4.10 | Illustration of integrated PE microarchitecture for WS/OS dataflows.                                                                          | 98  |

| 4.11 | Illustration of (a) arbitrary permute and reshape operations on tensor                                                                        |     |

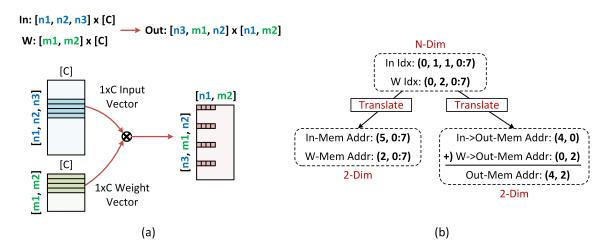

|      | data in memory, and (b) proposed index translation mechanism                                                                                  | 99  |

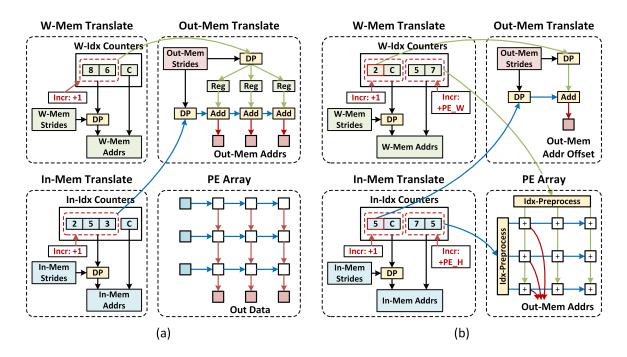

| 4.12 | Microarchitecture of index translation for (a) WS dataflow and (b)                                                                            |     |

|      | OS dataflow                                                                                                                                   | 100 |

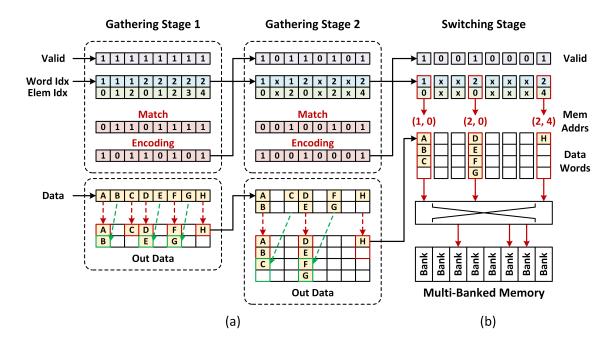

| 4.13 | Illustration of the hierarchical output gathering mechanism using (a)                                                                         |     |

|      | two gathering stages followed by (b) a switching stage.                                                                                       | 102 |

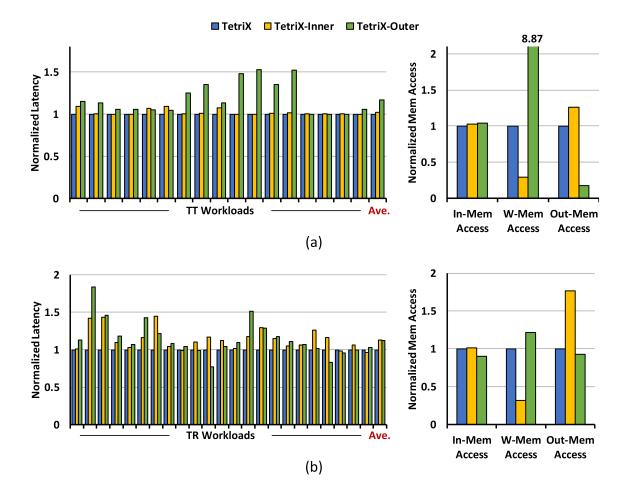

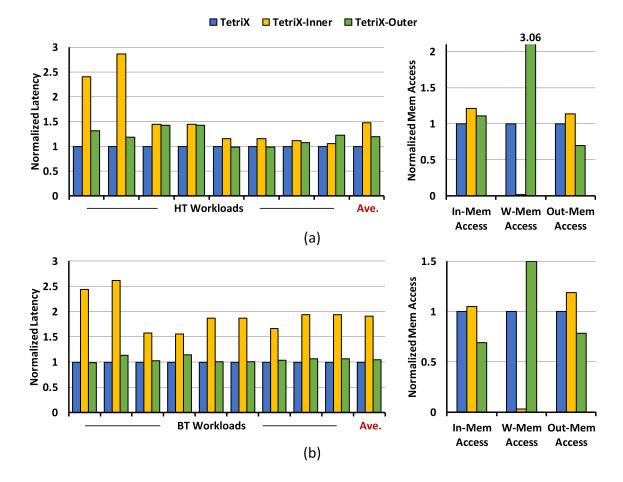

| 4.14 | Performance comparison of hybrid mapping (TetriX), inner-only map-                                                                            |     |

|      | ping (TetriX-Inner), and outer-only mapping (TetriX-Outer) for (a)                                                                            |     |

|      | TT and (b) TR workloads.                                                                                                                      | 104 |

| 4.15 | Performance comparison of hybrid mapping (TetriX), inner-only map-                                                                            |     |

|      | ping (TetriX-Inner), and outer-only mapping (TetriX-Outer) for (a)                                                                            |     |

|      | HT and (b) BT workloads                                                                                                                       | 105 |

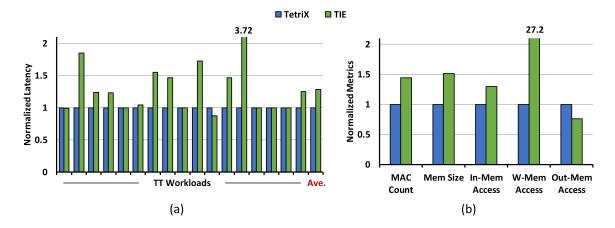

| 4.16 | Comparison of the TetriX to TIE [5] in (a) normalized latency, and                                                                            |     |

|      | (b) total MAC count, maximum memory size, and number of memory                                                                                |     |

|      | accesses                                                                                                                                      | 106 |

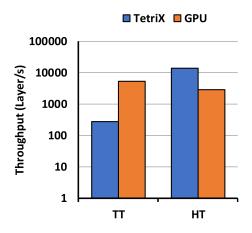

| 4.17 | End-to-end throughput comparison for TT and HT workloads                                                                                      | 107 |

# LIST OF TABLES

# <u>Table</u>

| 35 |

|----|

| 00 |

|    |

| 47 |

| 67 |

| 67 |

| 70 |

| 82 |

|    |

# LIST OF ABBREVIATIONS

- **AI** Artificial Intelligence

- **AIM** Associative Index Matching

- ASIC Application-Specific Integrated Circuit

- **BDFS** Bounded Depth-First Search

- **BFS** Breadth-First Search

- $\mathbf{BT} \ \mathrm{Block} \ \mathrm{Term}$

- **CAM** Content-Addressable Memory

- **CNN** Convolution Neural Network

- ${\bf CONV}$  Convolution

- **CP** Canonical Polyadic

- **CPU** Central Processing Unit

- **CSC** Compressed Sparse Column

- **CSR** Compressed Sparse Row

- **CTA** Compute Tile Array

- **CTile** Compute Tile

- **CV** Computer Vision

- **DFS** Depth-First Search

- **DNN** Deep Neural Network

- **DP** Dot-Product

**DRAM** Dynamic Random-Access Memory

EdgeCONV Edge Convolution

FC Fully-Connected

F-Map Foreign Map

**FPGA** Field-Programmable Gate Array

${\bf fps}\,$  Frames per Second

**Fpsum** Feature Partial Sum

GCN Graph Convolutional Network

**GNN** Graph Neural Network

GPU Graphics Processing Unit

GraphCONV Graph Convolution

**GRU** Gated Recurrent Unit

${\bf HT}$  Hierarchical Tucker

**IA** Input Activation

Inf. Inference

KNN K-Nearest Neighbor

L-Map Local Map

**LSTM** Long Short Term Memory

MAC Multiply-and-Add

ML Machine Learning

MLP Multi-Layer Perceptron

**MMM** Matrix-Matrix Multiplication

$\mathbf{MP}$  Max-Pool

**NLP** Natural Language Processing

${\bf NN}\,$  Neural Network

- NoC Network-on-Chip

- **OA** Output Activation

- **OS** Output Stationary

- OP Operation

- **PE** Processing Element

- **PP** Post-Processing

- Psum Partial Sum

- ${\bf ReLU}$  Rectifier Linear Unit

- ${\bf RNN}\,$  Recurrent Neural Network

- **ROI** Region of Interest

- **SBFS** Speculative Breadth-First Search

- SE Sorting Element

- **SIMD** Single Instruction Multiple Data

- **SLA** Spatial-Locality-Aware

- **SNAP** Sparse Neural Acceleration Processor

- **SRAM** Static Random-Access Memory

- **SVD** Singular-Value Decomposition

- ${\bf TNN}\,$  Tensorized Neural Network

- TR Tensor Ring

- ${\bf TT}\,$  Tensor Train

- V-ALU Vector Arithmetic Logic Unit

- VMM Vector-Matrix Multiplication

- W Weight

- **WS** Weight Stationary

### ABSTRACT

Deep neural networks (DNNs) have become the primary methods to solve machine learning and artificial intelligence problems in the fields of computer vision, natural language processing, and robotics. The advancements in DNN model development are to a large degree attributed to the increase of model size, complexity, and versatility. The continuous growth of model size, complexity, and versatility causes intense memory storage and compute requirements, and complicates the hardware design, especially for the more resource-constrained mobile and smart sensor platforms.

To resolve the resource bottlenecks, model compression techniques, i.e., data quantization, network sparsification, and tensor decomposition, have been used to reduce the model size while preserving the accuracy of the original model. However, they introduce several computation challenges including 1) irregular computation in an unstructured sparse neural network (NN) from network sparsification, and 2) complex and arbitrary tensor orchestration for tensor contraction in a tensorized NN.

Meanwhile, DNN's capability has been transferred to new domains and applications to handle drastically different modalities and non-Euclidean data, e.g., point clouds and graphs. New computation challenges continue to emerge, for example, irregular memory access for graph-structured data in a graph-based point-cloud NN.

These challenges lead to a low processing efficiency for existing hardware architectures and motivate the exploration of specialized hardware mechanisms and accelerator architectures. This dissertation consists of three works that explore the design of efficient accelerator architectures to overcome the computation challenges by exploiting model compression characteristics and data orchestration techniques. The first work presents the sparse neural acceleration processor (SNAP) to process sparse NNs resulted from unstructured network pruning. SNAP uses parallel associative search to discover valid weight and input activation pairs for parallel computation. A two-level partial sum (psum) reduction dataflow is used to eliminate access contention at the output buffer and cut the psum writeback traffic. The SNAP chip is implemented and achieves a peak effectual efficiency of 21.55 TOPS/W for sparse workloads and 3.61 TOPS/W for pruned ResNet-50.

The second work presents Point-X, a spatial-locality-aware architecture that exploits the spatial locality in point clouds for efficient graph-based point-cloud NN processing. A clustering method extracts fine-grained and coarse-grained spatial locality from the input point cloud to maximize intra-tile computational parallelism and minimize inter-tile data movement. A chain network-on-chip (NoC) further reduces the data traffic and achieves up to  $3.2 \times$  speedup over a traditional mesh NoC. The Point-X prototype achieves a throughput of 1307.1 inference/s and an energy efficiency of 604.5 inference/J on the DGCNN workload.

The third work presents TetriX, an architecture-mapping co-design for efficient and flexible tensorized NN inference. An optimal contraction sequence with minimized computation and memory size requirements is identified for inference. A hybrid mapping scheme is used to eliminate complex orchestration operations by alternating between inner and outer product operations. TetriX uses index translation and output gathering to support flexible orchestration operations efficiently. TetriX is the first work to support all existing tensor decomposition methods for tensorized NNs and demonstrates up to  $3.9 \times$  performance improvement compared to the prior work for tensor-train workloads.

Overall, these three works explore the computation of different network optimization techniques. They exploit the full potentials of model compression and novel operations, and convert them into hardware performance and efficiency. The architectures can also be used to further enhance and support the development of more effective network models.

# CHAPTER I

# Introduction

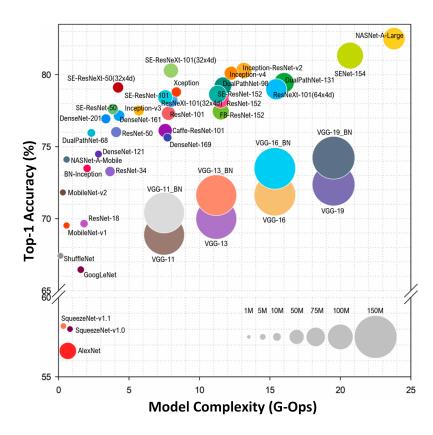

Figure 1.1: Top-1 accuracy, size, and complexity of modern DNN models. Adapted from [1].

Deep learning [6], or more specifically, deep neural networks (DNNs) have become the dominant methods to solve machine learning (ML) and artificial intelligence (AI) problems in the fields of computer vision (CV), natural langurage processing (NLP),

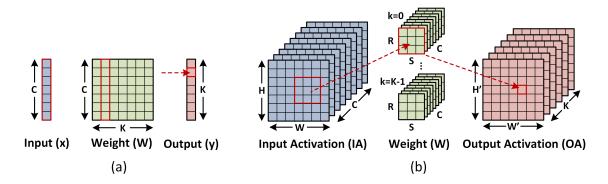

Figure 1.2: Core computations of DNNs: (a) vector-matrix multiplication in MLP and RNN, and (b) 2D convolution in CNN.

autonomous driving, and robotics [1, 2, 7–17]. To achieve an even better accuracy, there is an constant effort to design larger and more powerful models, resulting in increasing number of parameters and computation complexity. Figure 1.1 presents the accuracy of modern network models with their model size and complexity in terms of number of parameters and operation counts.

#### 1.1 DNN Computation

In general, there are three different network structures for DNN models: 1) multilayer perceptron (MLP), 2) convolutional neural network (CNN), and 3) recurrent neural network (RNN). We present the three network structures along with its core computation.

An MLP consists of multiple feedforward fully-connected (FC) layers cascaded one after another. The computation of an FC layer can be formulated into a vectormatrix multiplication (VMM) between the input vector  $\boldsymbol{x} \in \mathbb{R}^{C}$  and the weight matrix  $\boldsymbol{W} \in \mathbb{R}^{C \times K}$  to obtain the output vector  $\boldsymbol{y} \in \mathbb{R}^{K}$ , as described in Figure 1.2(a).

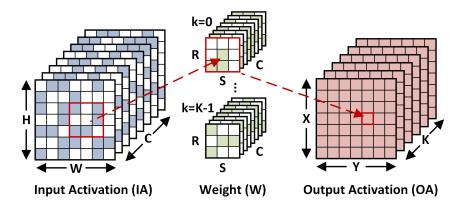

A CNN is specialized to 2D image processing and uses convolution (CONV) layers for spatial feature extraction and FC layers for classification. The input and output are often referred as input activation (IA) and output activation (OA). A CONV layer has a weight (W) of size  $R \times S \times C \times K$  and receives an IA of size  $H \times W \times C$  to obtain an OA of size  $H' \times W' \times K$ , as shown in Figure 1.2(b). In terms of computation, a CONV layer performs 2D convolution with a kernel size of  $R \times S$  on the IA. The partial sums (Psums) are accumulated across input channel C to obtain an OA. The same operation is repeated for K kernels. The model hyperparameters C and Kare the input and output channel sizes, respectively. The output channel size is also known as the (weight) kernel number.

An RNN uses recurrent connections to process the input sequence of the current timestep t and the output sequence from the previous timestep t - 1. Two popular forms of the recurrent unit are widely adopted: gated recurrent unit (GRU) and long short term memory (LSTM). An LSTM uses input, output, forget gates, and a cell, i.e., i, o, f, c, to keep track of features that are relevant in long term and improves accuracy over traditional recurrent units. The computation of an LSTM can also be formulated into a VMM (Figure 1.2(a)), where the input vectors are the input sequence  $\mathbf{x}_t$  and the hidden sequence  $\mathbf{h}_{t-1}$ , the matrix is the concatenation of i, f, o, cmatrices with respect to the input or hidden sequences, and the output vector is the hidden sequence  $\mathbf{h}_t$ .

### **1.2** Network Model Optimization

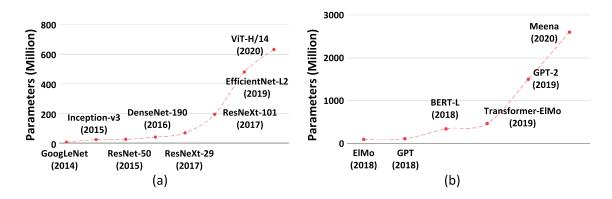

The continuing growth of model size and computation complexity poses a significant challenge to the deployment to real-time applications or on resource-constrained devices. As shown in Figure 1.3, state-of-the-art CV and NLP models requires millions or billions of parameters to obtain the best accuracy [9, 12]. Model compression techniques are proposed to reduce the model size and computation complexity.

On the other hand, there is an increasing effort to apply deep learning into new fields with new modalities or non-Euclidean data beyond the heavily-focused CV and NLP fields [14, 15, 18, 19]. To obtain better accuracy, new operations are proposed from scratch or adapted from traditional operations.

Figure 1.3: Evolution of model size in the fields of (a) CV and (b) NLP. Adapted from [2].

At the algorithm-level, model compression techniques and novel operation types successfully achieve smaller model size and better accuracy, respectively. However, most techniques also introduce sources of inefficiency at the hardware-level, resulting in lower compute utilization and larger computation overhead. Therefore, hardware accelerator and specialized architecture are necessary to bridge network optimization algorithms to hardware performance and computation efficiency.

#### 1.2.1 Model Compression

The rapid growth of the model size and computation complexity leads to a huge cost for model training and inference that only server-scale graphics processing units (GPUs) and central processing units (CPUs) equipped with large compute parallelism, memory storage, and memory bandwidth can support. For example, GPT-3 model contains 175 billion parameters and requires trillions of multiply-and-add (MAC) operations for a single inference [12]. While these heavy models perform extremely well at server-scale, they are impractical and cannot be deployed to resource-constrained platforms, i.e., mobile, drone, and smart sensor, where compute, memory, bandwidth, and battery are largely limited. This has motivated researches on model compression techniques that aim to reduce the model size and the complexity of a DNN model while preserving the accuracy [2, 20–22]. Several model compression techniques, i.e.,

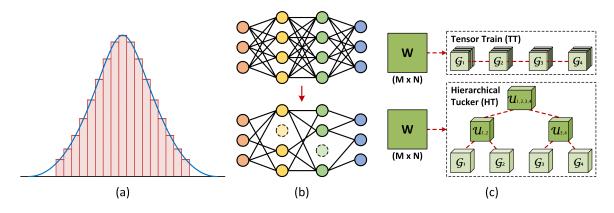

Figure 1.4: Common model compression techniques: (a) data quantization, (b) network sparsification, and (c) tensor decomposition.

data quantization, network sparsification, and tensor decomposition, have been proposed and are widely applied to DNNs.

Data quantization (Figure 1.4(a)) reduces the data bit precision of model parameters by truncating or rounding high-precision values into lower-precision values [23, 24]. A quantized network requires the same amount of computation (at reduced precision), but needs much less bits for memory storage.

Network sparsification (Figure 1.4(b)) is performed via network pruning that removes unimportant connections in the network, generating a sparse model [25–28]. A sparse network can be stored in a sparse format, i.e., compressed sparse row (CSR), to reduce the amount of memory space needed. In addition, a sparse network reduces the amount of computation since most multiplications are unnecessary and can be avoided.

Tensor decomposition (Figure 1.4(c)) aims to find a simpler, low-rank approximation of the original weight matrix or tensor [29–34]. Traditional low-rank approximation methods, i.e., singular-value decomposition (SVD) [29], are used for 2D weight model, whereas, recent tensor decomposition methods, i.e., tensor-train (TT) [33, 34], decomposes the original model into a series of smaller tensors, largely reducing the memory space.

Note that both data quantization and sparsification can be applied to the input

Figure 1.5: Examples of novel operations: (a) GraphSAGE in GNNs and (b) Edge-CONV in point-cloud networks. Adapted from [3, 4].

vector or activation. These compression methods can also be combined when applying on a network, which may generate an even larger compression of the model [21].

#### 1.2.2 Novel Operation Types

After the wide success of CNNs and RNNs in the CV and NLP fields, researchers have worked on converting the insights obtained from traditional network models to new applications and new modalities. For example, a graph is a natural representation of the relationship between the data points in a network and is used for graph mining applications, i.e., community detection, social network analysis [18, 19]; a point cloud is an accurate representation of 3D space and has become a popular modality for 3D vision tasks, i.e., object classification and scene segmentation [14, 16, 17]. These new modalities and non-Euclidean data may have completely different data structures and characteristics compared to the traditional 2D images and 1D text sequences. Therefore, the traditional operations, i.e., CONV, may not be sufficient, leading to the development of novel operations and network models. For example, graph convolution (GraphCONV) [35] with different frameworks i.e., GraphSAGE [3], DeepWalk [36], are used in graph neural networks (GNNs) to obtain better graph embeddings. Similarly, for point-cloud recognition, novel operations, like edge convolution (EdgeCONV) [4], were proposed to extract more meaningful features from point clouds.

The novel operations proposed enable the application of DNN into new fields of applications and successfully outperform the accuracy of traditional models [14, 15, 19].

**GraphSAGE (Figure 1.5(a))**: In GraphSAGE [3], the neighborhoods for each node are first sampled from the graph. Then, each node in the graph aggregates the representations of the nodes in its k-hop neighborhood. The aggregated neighborhood vector is concatenated with the node's current representation, then processed with an FC layer to obtain the new representation of the node. This process is repeated for every hop count k = 1, ..., K.

EdgeCONV (Figure 1.5(b)): For each point in the point cloud, the Edge-CONV operation forms an edge between the point and its K-nearest neighbors, then computes the edge features based on the point feature difference for every edge. Then, the edge features are aggregated to obtain the output feature of the point [4].

#### 1.2.3 Computation Challenges

At the algorithm-level, model compression techniques succeed in achieving better balance between reasonable accuracy and affordable model size. Similarly, novel operation design can achieve higher accuracy than a traditional model. However, most techniques also introduce sources of inefficiency at the hardware-level. For instance, the sparse formats from network sparsification are highly unstructured and irregular, causing an inefficient parallel computation for a single instruction, multiple data (SIMD) architecture. Similar irregular computation and memory access can be observed for EdgeCONV computation in point-cloud networks. A SIMD architecture must gather and reorganize the data obtained from scattered memory accesses before performing parallel computation, causing a low compute utilization. In addition, the set of tensors from tensor decomposition require complex and arbitrary data orchestration to map a tensor contraction into matrix multiplication, resulting in additional memory access and control overheads if the mapping is not optimized. These motivate us to design specialized architectures and hardware accelerators to unlock the full potentials of network optimizations and achieve higher processing performance and efficiency.

### **1.3** Dissertation Outline

To fully benefit from model compression techniques and to support novel operation types, specialized hardware mechanisms and signal processing techniques must be incorporated into the accelerator architecture and design. This dissertation focuses on the design of efficient AI and ML accelerator architecture using optimizations at algorithm, architecture, and microarchitecture levels.

The organization of this dissertation is summarized as follows. Chapter II presents SNAP [37, 38], a sparse neural acceleration processor for unstructured sparse neural network (NN) processing. Specialized associative index matching (AIM) units were designed to pair IA and W operands and provide a sufficient number of them to maintain compute utilization. A two-level reduction dataflow was proposed to eliminate unnecessary memory accesses in the psum reduction process. Chapter III presents Point-X [39, 40], a spatial-locality-aware (SLA) architecture for efficient graph-based point-cloud NN processing. An SLA clustering extracts the spatial locality in the input point cloud to maximize the computational parallelism at each compute tile (CTile) and minimize the inter-CTile data movement. By exploiting the locality, a low-cost chain NoC is designed to reduce the data exchange latency during processing. Chapter IV presents TetriX, an architecture and mapping co-design for efficient and flexible tensorized neural network (TNN) processing. An optimal search is used to identify the contraction sequence with minimized computation for TNN inference. A hybrid mapping scheme is proposed to eliminate complex tensor orchestration operations by alternating between inner and output product operations. An index translation and an output gathering mechanisms are designed to support arbitrary and scalable tensor permute and reshape operations. Chapter V concludes this dissertation and provides outlooks for future research in ML and AI accelerator design.

## CHAPTER II

# SNAP: Accelerator Architecture for Unstructured Sparse Neural Networks

Deep learning or more specifically, deep neural network (DNN), has emerged to be a key approach to solving complex cognition and learning problems [6, 41]. State-ofthe-art DNNs [7, 8, 42–47] require billions of operations and hundreds of megabytes to store activations and weights. Given the trend towards even larger and deeper networks, the compute and storage requirements will prohibit real-time, low-power deployment on platforms that are resource and energy constrained. The compute and storage challenges motivated efforts in network pruning to zero out a large number of weights (W) in a DNN model with only little inference accuracy degradation [25, 26, 28]. In addition to sparsity in weights, the commonly-used rectifier linear unit (ReLU) clamps all negative activations to zeros, resulting in sparsity in output activations (OAs), which become input activations (IAs) of the next layer.

Figure 2.1 shows that the typical density of nonzero W (after network pruning [26]) and IA (due to ReLU) in well-known network models: AlexNet, VGG-16 and ResNet-50. An average of 50% density is common. Because the nonzero W and IA are nearly randomly distributed, the amount of effectual computation, i.e., computation that does not involve a zero, is only 25%. If a small sacrifice in inference accuracy can be tolerated, the density of operands and the effectual computation can be further

Figure 2.1: Average density of IA, W data and average effectual work of common DNNs after network pruning.

reduced.

Data sparsity can be exploited to save power. Many DNN accelerators, i.e., Eyeriss [48], gates the computation by turning off the clock, whenever a zero in the IA is detected in runtime. Most dense DNN accelerators can incorporate this technique to reduce power, but it does not shorten the latency or improve the throughput.

Cnvlutin [49] and Cambricon-X [50] are well-known early architectures that exploit sparsity in compressed IA for latency reduction and throughput improvement. However, they were designed to work with the sparsity in one of the two operands, W or IA, but not both. A dense processing architecture can be easily adapted to support one-operand sparsity by indirect data access.

To fully exploit sparsity in both operands, W and IA are stored in a compressed form where nonzero elements are represented by value-index pairs. Storage in a compressed form can reduce the memory size and bandwidth. However, unlike the common dense array and matrix storage, a compressed storage is not amenable to regular and efficient vector processing. One approach is to decompress the compressed form before processing, but decompression costs performance, memory, and power. Instead, state-of-the-art sparse DNN accelerators [51–55] process data directly in the compressed form, offering both low memory bandwidth and high degree of accelera-

Figure 2.2: Convolution computation between unstructured sparse IA and W in a sparse DNN. The colored cells indicate nonzero entries, and the white cells indicate zero entries.

Figure 2.3: Processing pipeline of a sparse DNN processor.

tion.

Figure 2.2 illustrates sparse convolutions, and Figure 2.3 shows the high-level computation pipeline of DNN processing in the compressed format (which will be referred to as sparse DNN processing for simplicity). A sparse DNN processor loads Ws and IAs in a compressed form consisting of a data array (zeros removed) and an index array. Compressed W and IA arrays are paired by matching indices, dispatched to a multiplier array, and the resulting partial sums (Psums) are accumulated to their respective OAs in output buffers.

Data sparsity leads to better performance and efficiency, but major challenges remain:

1. *Front-end challenge*: Multiplier under-utilization due to an insufficient number of W-IA pairs that can be extracted and dispatched to the multiplier array.

- 2. **Back-end challenge**: Data traffic and access contention to support accumulation of psums whose destination addresses are seemingly random.

- 3. *Flexibility challenge*: Limited support for different kernel sizes and layer types.

State-of-the-art sparse DNN accelerators including EIE [51], SCNN [52], Sticker [53, 54], and Eyeriss v2 [55] addressed some of the challenges in sparse DNN processing, but did not solve all of them. EIE [51] exploits both W and IA sparsity but is restricted to fully-connected (FC) layers. SCNN [52] is the first attempt at exploiting both W and IA sparsity for convolution (CONV) layers. It maximizes multiplier utilization at the cost of massive psum writeback traffic and access contention, and it supports only CONV layers. Sticker [53, 54] follows SCNN's dataflow and uses 2-way set-associative processing elements (PEs) to alleviate the access contention but requires offline preprocessing to re-arrange IA data. Without the data re-arrangement, the access contention remains as significant as in SCNN. Eyeriss-v2 [55] employs a two-step search front-end to find effectual W-IA pairs by first fetching nonzero IAs, and then using the channel index of the IA to look for nonzero Ws. Eyeriss-v2 adopts an Eyeriss-like row stationary dataflow [56] to avoid memory access contention.

We present Sparse Neural Acceleration Processor (SNAP) that adopts a channelfirst dataflow and is optimized for the efficient processing of unstructured sparse DNNs. To solve the front-end challenge, SNAP uses parallel associative index matching (AIM) units and sequence decoders to extract a sufficient number of W-IA pairs to maintain a high multiplier array utilization of 75%. To solve the back-end challenge, SNAP adopts a two-level psum reduction that consists of PE level and core-level reduction to eliminate memory access contention and reduce psum writeback traffic to an average of 2.79 OA reductions/cycle for a core of 63 multipliers. The core-level reduction is configurable to support common layers in vision-based DNN models, including general  $R \times S$  CONV (R, S > 1), pointwise CONV, and FC. The rest of the chapter is organized as follows. Section 2.1 introduces the channellast dataflow, an approach adopted by state-of-the-art sparse accelerators, and analyzes its advantages and inefficiencies in processing sparse DNNs. Section 2.2 presents our channel-first dataflow and quantitatively compares it against the channel-last dataflow to demonstrate its advantages. In Section 2.3, we describe our solution to the front-end challenge using parallel index matching, and in Section 2.4, we describe our solution to the back-end challenge using two-level psum reduction. The configurable core-level reduction makes the SNAP architecture flexible to support different kernel sizes and layer types. Section 2.5 presents the overall SNAP architecture, followed by measurement and evaluation results using both synthetic sparse workloads and commonly-used pruned networks. Finally, Section 2.6 summarizes the contributions of this work.

#### 2.1 Background

A dense CONV operation can be described by Eq. (2.1), where f represents the activation function. For simplicity, the bias is ignored and IA padding is assumed to be zero. FC can be viewed as a special case of CONV. In this work, we will use the following indexing convention: a W index of (r, s, c, k) corresponds to (row, column, channel, kernel), an IA index of (h, w, c) corresponds to (row, column, channel), and an OA index of (x, y, k) corresponds to (row, column, output channel (kernel)).

$$OA_{(x,y,k)} = f\left(\sum_{i=0}^{R-1} \sum_{j=0}^{S-1} \sum_{c=0}^{C-1} IA_{(x+i,y+j,c)} \times W_{(i,j,c,k)}\right).$$

(2.1)

As Eq. (2.1) shows, there are two main steps in computing CONV (besides the activation function): 1) IAs and Ws are multiplied to produce psums; and 2) the psums are accumulated (or reduced) along the channel dimension (C) and along the pixel dimension (R, S). The channel-dimension reduction and pixel-dimension

Figure 2.4: Illustration of channel-last dataflow for sparse DNN processing.

reduction are commutative. The channel indices of a W and an IA need to match for the two to be multiplied together.

In ordering inputs for storage and processing, we can choose either the pixel dimension first ((r, s) for W and (h, w) for IA) followed by the channel dimension (c), termed channel-last dataflow, or vice versa, termed channel-first dataflow. Both SCNN [52] and Sticker [54] adopt the channel-last dataflow.

#### 2.1.1 Channel-Last Dataflow for Sparse DNN Processing

The channel-last dataflow is illustrated in Figure 2.4. In the channel-last dataflow, the nonzero W and IA data are ordered in the pixel dimension first for storage and processing. Because data are ordered pixel dimension first, as W and IA data are streamed in, their channel indices are aligned. Since any nonzero W can be multiplied with any nonzero IA of the same channel in a CONV operation, the W and IA can be freely paired to produce a large number of W-IA pairs for a multiplier array.

The simple W-IA pairing results in a simple front-end for the channel-last dataflow. Shown in Figure 2.4(a) and (b), the compressed W and IA data of size n can be broadcast over a  $n \times n$  2D multiplier array vertically and horizontally, respectively, so that each W is multiplied to every IA. The drawback of the channel-last dataflow is that the address of the OA that a psum needs to be accumulated to (will be referred to as the psum address) does not follow a deterministic ordering. According to Eq. (2.1), if a nonzero W and a nonzero IA have matching channel index c, they can be multiplied to produce a psum with an index of (x, y, k) = (h - r, w - s, k). The 3D index is then translated to a 1D physical address. Hence, the  $n \times n$  2D multiplier array produces  $n^2$  psums whose (x, y) indices are  $\{(h - r, w - s)\}$  with random drawings of  $h \in [0, H - 1], r \in [0, R - 1], w \in [0, W - 1]$ , and  $s \in [0, S - 1]$ . It is highly likely to have two or more psums that share the same address, and in theory they should be accumulated, or reduced, before writeback. However, it is challenging to organize psums and reduce them before writeback. Without any psum reduction, the writeback traffic becomes congested, and frequent contentions are possible at the OA buffer. It requires complex hardware or wiring, e.g., a crossbar switch, to resolve the contention, and results in pipeline stalls and a low multiplier array utilization.

This back-end challenge is illustrated in Figure 2.4(c). The psums need to be distributed by a switch to the corresponding buffer bank. The red lines indicate the psum writebacks that lead to buffer contentions. To avoid contentions, conflicting psums need to be held. In the example, one output requires the accumulation of 3 psums, resulting in a 3-cycle writeback where the multiplier array stalls for 2 cycles.

#### 2.1.2 Other Related Work

Numerous DNN accelerators have been proposed to exploit the parallelism in DNN inference operations [38, 48–62]. To leverage the sparsity in Ws and IAs, some work implemented power-saving techniques by clock-gating a PE when a zero IA is detected [48, 59] to increase energy efficiency. Some work exploited sparsity at the bit level [60] by skipping the computation for the zero-valued bits in the bit-serial multiplication. Compared to earlier methods, exploiting sparsity in bit-level reduces the overall computation cycles, and increases both efficiency and throughput. However, the dataflows are still similar to traditional dense accelerators, where zero elements are fetched on-chip, incurring unnecessary data transfers.

In this work, we focus on the DNN inference accelerator design that exploits sparsity at data level and operates in the compressed form. Only nonzero elements are fetched on-chip for computation, like in [51, 52, 54, 55]. This type of accelerator skips all unnecessary data transfers and computation to optimize for energy efficiency and computation throughput. We will refer to this type of accelerator as a sparse accelerator for discussion and comparison.

### 2.2 Channel-First Processing Dataflow

Compared to the channel-last dataflow, the channel-first dataflow orders W and IA data across the channel dimension first for storage and processing. The channelfirst dataflow allows the psums computed by the multiplier array to be locally reduced before writeback.

#### 2.2.1 Compression Format

In the channel-first dataflow, nonzero W and IA data are ordered and processed in the channel dimension first, and then in the pixel dimension. An example of a  $3 \times 3$

Figure 2.5: Channel-first compression in SNAP.

CONV is shown in Figure 2.5. The channel-first dataflow supports arbitrary IA data size and a  $3\times3$  IA data is chosen for the ease of illustration.

In Figure 2.5(a), the W and IA data are illustrated in the dense form. In our channel-last dataflow, a bundle of nonzero W data and a bundle of nonzero IA data are provided to a PE at a time. An IA bundle contains data in  $(h, w, \underline{c})$ , where  $\underline{c}$  represents all nonzero elements along the channel dimension; and a W bundle is larger and it contains data in  $(\underline{r}, s, \underline{c}, \underline{k})$ , where  $\underline{r}, \underline{c}, \underline{k}$  represent all nonzero elements along the row, channel and kernel dimension, respectively. In general, a larger data bundle leads to a higher utilization and processing efficiency, but we limit the IA bundle not to span more than one pixel location to simplify channel index matching.

Figure 2.5(b) illustrates the IA bundle of  $(h, w, \underline{c}) = (2, 2, \underline{c})$  and the W bundle of  $(\underline{r}, \underline{s}, \underline{c}, \underline{k}) = (\underline{r}, 0, \underline{c}, \underline{k})$ . The bundles are stored in the compressed form with all zeros squeezed out as shown in Figure 2.5(c). The IA data are stored channel first. The IA storage consists of a data array that stores nonzero IA data and a channel index (c-idx) array that stores the channel index of the corresponding IA data. The W data are also stored channel first, followed by row (r-idx) and kernel (k-idx). The W

storage consists of a data array, a c-idx array, a r-idx array and a k-idx array, as well as a position pointer (pos-ptr) array to track the starting points in the data array of the next r-idx and/or k-idx. For instance, the pos-ptr array stores 0 and 3, indicating that the first three data values A, B, and C have (r, k) = (0, 0), and the data values D, E, and F have (r, k) = (1, 0). An IA bundle and a W bundle are sent to one PE for processing.

#### 2.2.2 Channel-First Dataflow

In a channel-first dataflow, the nonzero W and IA data are streamed in channel first, the addresses of the psums computed are aligned and the psums can be immediately reduced along the channel dimension. Despite the appeal of the channel-first dataflow, a W and an IA can only be paired and multiplied if their channel index match. Hence, channel index matching must be performed at the front-end to extract the valid W-IA pairs. Compared to the channel-last dataflow, this additional channel index matching step introduces an overhead, but it provides immediately-reducible psums to cut the writeback traffic, leading to potential improvements in both power and performance.

The channel-first dataflow is illustrated in Figure 2.6. Each PE receives a W bundle  $(\underline{r}, \underline{s}, \underline{c}, \underline{k})$  and an IA bundle  $(h, w, \underline{c})$ , as illustrated in Figure 2.5(c). The W c-idx is matched with the IA c-idx to generate valid W-IA pairs. Valid W-IA data pairs are fetched and multiplied to produce psums. The psums are accumulated and saved to the OAs at (x, y, k) = (h - r, w - s, k). Due to the channel-first input ordering and bundled processing, the address of the psums computed by one PE will stay the same until the PE completes an IA bundle and switches to a new IA bundle (change of h, w), or until the r-idx or k-idx changes (change of r, k) for a W bundle. Due to the high locality of psum address, the majority of the psums are immediately reduced to one within a PE. To process a complete convolution, the IA and W data

Figure 2.6: SNAP's channel-first dataflow with channel index matching and psum reduction along the channel dimension.

are decomposed and compressed into IA and W bundles. The IA and W bundles are distributed to different PEs for processing as shown in Figure 2.6 until all bundles are fully processed.

In a channel-first dataflow, channel-dimension psum reduction is done first. A second-level pixel-dimension psum reduction can be done on-chip to further reduce the writeback bandwidth. To enable the second-level psum reduction, PEs can be arrayed and coordinated to facilitate the psum reduction across the PEs. The second-level psum reduction will be described in more detail in Section 2.4.2.

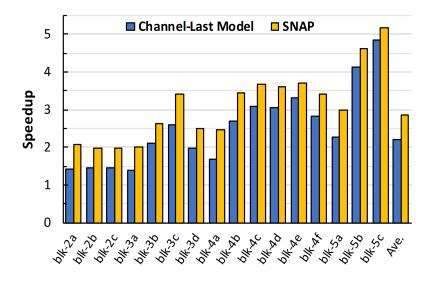

To evaluate the benefits of the channel-first dataflow, we prototyped a channellast dataflow that follows the processing pipeline described in Figure 2.4 and quantify the key differences between the two dataflows as shown in Figure 2.7. The channellast dataflow is limited by the large number of OA buffer accesses and the access contention, causing the compute to stall and worsening both utilization and processing latency; and in comparison, the channel-first dataflow employs a front-end

Figure 2.7: Comparison between channel-last dataflow and SNAP (channel-first dataflow) for dense, medium and sparse workloads.

channel index matching to reduce the number of OA buffer accesses and remove the access contention. The channel-first dataflow provides on average  $1.51 \times$  and  $1.45 \times$  improvement over the channel-last dataflow in processing latency and multiplier utilization, respectively. Only when the data density drops below a threshold, e.g., 10% W and IA data density, does the channel-first dataflow starts to underperform the channel-last dataflow due to two factors: 1) the lack of reduction opportunities due to highly sparse data, and 2) the imbalance of input bundle sizes causing PE workload imbalance.

The SNAP architecture follows the channel-first dataflow. The two key techniques, channel index matching and two-level psum reduction, will be presented in the next two sections.

# 2.3 Channel Index Matching

Channel index matching extracts pairs of nonzero W-IA pairs of matching channel index. We propose an associative index matching (AIM) unit to extract a sufficient number of W-IA pairs to sustain a high utilization of a parallel multiplier array. The AIM performs index matching, encodes the addresses of valid W-IA pairs, and a sequence decoder decodes the addresses and dispatches the pairs for parallel computation.

### 2.3.1 Associative Index Matching

Figure 2.8(a) shows the microarchitecture of the AIM and illustrates its mechanism. The AIM consists of a  $N \times N$  comparator array, where each row is connected to a priority encoder. During operation, an AIM receives the W and IA channel index arrays from a PE; and it compares each W channel index to each IA channel index. In Figure 2.8(a), for example, the W channel indices 0, 2, 9, 5 are matched to the IA channel index at position 0, 1, 4, 2, respectively, whereas the W channel index 4 does not have a match. A priority encoder encodes the match result in each row into a valid bit to indicate a match and the matched position in the IA channel index array. Upon completion, an AIM returns a list of valid-position pairs to a PE for processing.

### 2.3.2 Sequence Decoder

Within a PE, a sequence decoder converts a list of valid-position pairs to W-IA data pairs. Figure 2.8(b) shows the microarchitecture and illustrates the sequence detection mechanism with the valid-position list output from Figure 2.8(a): 1) a 3-way priority encoder converts 3 valid-position pairs (with valid bit = 1) at a time to W-IA data addresses; 2) the positions in the valid-position pairs are used as the addresses to fetch IA data, and the indices of the valid-position pairs are used as the addresses to fetch W data; and 3) the 3 valid-position pairs are invalidated by overwriting the valid bits to 0, and the W and IA data are sent to the multipliers to compute psums. After completing the list of valid-position pairs, the PE requests a new list from the AIM.

Figure 2.8: (a) Microarchitecture of associative index matching (AIM), and (b) microarchitecture of sequence decoder and step-by-step example of W-IA data pair dispatch in a PE.

Figure 2.9: Multiplier utilization of AIM designs at different data density levels.

### 2.3.3 Design Tradeoff Exploration

The size of the comparator array, N, determines AIM's throughput and effectiveness. N needs to be sufficiently large to even out the workload density imbalance and variations across W and IA bundles for extracting enough W-IA pairs to maintain a high multiplier utilization. However, the area and power consumption of AIM increase nearly quadratically with N. To balance these two competing factors, we avoid using a small AIM, e.g., one with a 4×4 or 8×8 comparator array, and instead use a larger AIM and time-multiplex it between multiple PEs to amortize the cost.

Figure 2.9 shows the multiplier utilization across a range of workload densities for N = 16, 32, or 64, where a suffix S indicates that a large AIM is timemultiplexed among an appropriate number of PEs, and a suffix P indicates that a simple prefetch mechanism is implemented to further reduce the workload imbalance by pre-requesting valid-position pairs from the AIM. A larger AIM provides a higher multiplier utilization across all workload densities: the utilization improves by 10% from N = 16 to 32, and again from 32 to 64. A large AIM with N = 64 incurs an area overhead of 50%. A moderate-sized AIM with N = 32 cuts the area overhead below 12.5%, and adding prefetching increases the utilization by up to 5%. Therefore, in

Figure 2.10: PE microarchitecture and psum reduction along the channel dimension.

designing SNAP, we adopt a time-multiplexing, prefetching AIM design with a N = 32 comparator array to balance the performance, area and power consumption. This design achieves an average multiplier utilization above 75% for our benchmarks.

# 2.4 Two-Level Partial Sum Reduction

To reduce the output bandwidth, after the psums are computed by the PEs, they should be maximally accumulated to reduce the number of writebacks to the output buffer. Following the channel-first dataflow, SNAP implements a two-level psum reduction to minimize the read-accumulate-writes to the output buffer. The psums are first reduced along the channel dimension inside the PEs, and then along the pixel dimension across PEs. The across-PE reduction is configurable to support not only CONV, but also pointwise CONV and FC.

## 2.4.1 PE-level Channel-Dimension Reduction

The PE microarchitecture is shown in Figure 2.10. Each PE contains a compute path consisting of 3 multipliers and psum accumulators, an address path that computes the addresses and then selects the psum reduction pattern, a sequence decoder,

| OA Addresses                       | Out[0] | Out[1] | Out[2] |

|------------------------------------|--------|--------|--------|

| $Addr_A = Addr_B = Addr_C$         | A+B+C  | -      | -      |

| $Addr_A = Addr_B < Addr_C$         | A+B    | С      | -      |

| $Addr_A < Addr_B = Addr_C$         | А      | B+C    | -      |

| $\boxed{Addr_A < Addr_B < Addr_C}$ | A      | В      | С      |

Table 2.1: Selection of Reduction Pattern

a W register file (RF) and an IA RF to provide the inputs, and an OA psum RF to store the outputs. In each cycle, the sequence decoder dispatches 3 W-IA data pairs and their indices ((h, w) for IA data and (r, s, k) for W data). The W-IA data pairs are directed to the compute path to produce the psums, A, B, and C; and the W and IA indices are sent to the address path to compute the addresses (recall psum index is (x, y, k) = (h - r, w - s, k), which is translated to a physical 1D address). Given the 3 psum addresses, the reduction controller selects one psum reduction pattern in the compute path.

The channel-first input processing order guarantees that the addresses for A, B, and C are ordered and non-decreasing, i.e.,  $Addr_A \leq Addr_B \leq Addr_C$ . Due to the deep channels seen in modern DNN layers, in most cases,  $Addr_A = Addr_B = Addr_C$ , and the 3 psums can be accumulated and reduced to one. If not, the reduction controller selects one of the reduction patterns according to Table 2.1. One, two or three psums are produced and sent to the OA psum RF every cycle, avoiding stalls in the computation pipeline. A PE retains a OA psum in the RF until all possible reductions along the channel dimension are complete, cutting the psum writeback traffic by up to the channel depth compared to the channel-last dataflow. Note that the number of multipliers in a PE is set to 3 to keep a reasonable overhead for the reduction pattern selection.

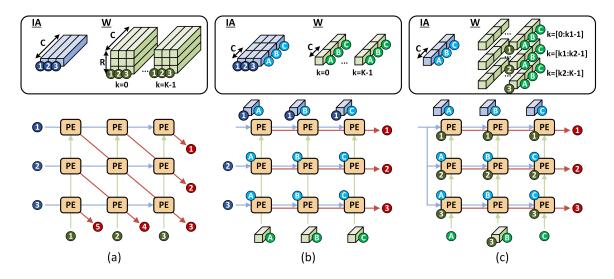

Figure 2.11: Psum reduction configuration across an array of PEs (a)  $3 \times 3$  CONV in diagonal mode, (b) pointwise CONV in row mode, and (c) FC in row mode.

### 2.4.2 Core-Level Pixel-Dimension Reduction

To reduce the writeback traffic, after the first-level psum reduction along the channel dimension, a second-level psum reduction across an array of PEs can be done. Figure 2.11(a) illustrates a  $3\times3$  PE array and the input data mapping for a  $3\times3$  CONV kernel. The three W bundles of s = 0, 1, 2 are broadcast to the three PE columns, and the three IA bundles of (h, w) = (2, 2), (2, 3), (2, 4) are broadcast to the three PE rows. This mapping allows W and IA reuse by a column and a row of PEs, respectively. Following this mapping, the PEs on the same diagonal lane produce psums of the same address. For example, assume (r, k) = (0, 0) for the W bundles, PE<sub>11</sub>, PE<sub>22</sub>, and PE<sub>33</sub> compute the psums going to the OA address of (x, y, k) = (h - r, w - s, k) = (2, 2, 0); and similarly, PE<sub>12</sub> and PE<sub>23</sub> compute the psums going to the OA address of (x, y, k) = (h - r, w - s, k) = (2, 1, 0). Therefore, the psums along the diagonal lanes are accumulated.

We name an array of PEs a core. To support the popular  $3 \times 3$  CONV seen in modern DNN models, the number of columns can be set to 3 (which also sets the number of PEs along a diagonal to 3) to achieve the full utilization. The number

of rows can be set based on the throughput requirement for an application. Going beyond the  $3\times3$  CONV, the diagonal mode reduction is used for general  $R\times S$  CONV (R, S > 1). If R, S > 3, the CONV kernel is divided into  $R\times3$  sub-kernels, and then distributed and processed independently on multiple compute cores. A global accumulator merges the psums from the multiple cores to compute the final OA for writeback.

The core-level psum reduction along the pixel dimension cuts the writeback traffic by 2.3 to  $3.0\times$ . The two-level reduction resolves the access contention seen in prior work [52–54]. It reduces the writeback traffic to only 2.79 OAs per cycle on average for a core of  $7\times3$  PEs that contain a total of 63 multipliers. The output bandwidth of a channel-first dataflow using the two-level reduction is  $22\times$  lower than the channel-last dataflow with an equal number of multipliers.

### 2.4.3 Support for Pointwise CONV and FC

In our work, we considered the pointwise CONV and FC as special cases of the CONV computation shown in Figure 2.2 with size constraints R = S = 1 and R = S = H = W = 1, respectively. The size constraints in pointwise CONV and FC eliminate the possibility of pixel-dimension reduction. The interconnection between the PEs and the core reducer is configurable to support not only the diagonal mode, but also provide a row mode to support DNN layers that do not have any pixel-dimension reduction opportunities.

To reuse the same architecture for a pointwise CONV including the same output bandwidth and to achieve a high utilization, the inputs are divided into groups in the channel dimension, and the core is reconfigured to perform reduction along the channel dimension. For example, in Figure 2.11(b), a W bundle is divided into three groups in the channel dimension, and each group is broadcast to a column of PEs; an IA bundle is divided into three groups in the channel dimension, and multicast to the three PEs in a row. This mapping allows W reuse by the PEs along a column. Following this mapping, the PEs on the same row produce the psums going to the same OA address. Therefore, the core reducer is configured to accumulate the psums from the PEs along the rows.

In processing an FC, W data cannot be reused in batch-1 processing. Similar to the pointwise CONV, the PE array is utilized in channel-dimension reduction. An IA bundle is divided into groups in the channel dimension; a W bundle is divided into groups in both the channel and kernel dimensions. For example, in Figure 2.11(c), a W bundle is divided into three groups in the channel and kernel dimension, and multicast to the three PEs in a column; and an IA bundle is divided into three groups in the channel dimension and broadcast to the three PEs in a column. This mapping allows IA reuse by the PEs along a column. Similar to the pointwise CONV, the PEs on the same row produce the psums going to the same OA address, and the core reducer is configured to accumulate the psums from the PEs along the rows.

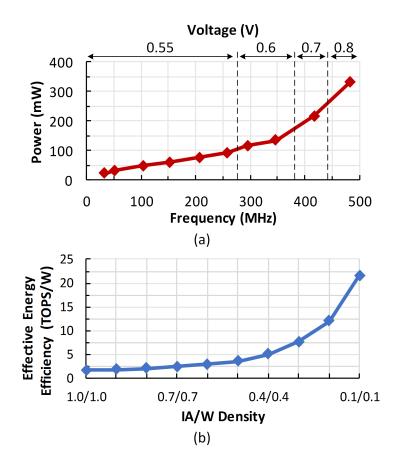

## 2.5 Implementation and Evaluation Results

We present the SNAP system architecture based on the techniques introduced above. The SNAP architecture is prototyped in a 16nm test chip. The chip is measured and evaluated using workloads of different sparsity levels and a pruned ResNet-50 model. The results are summarized and compared with state-of the-art dense and sparse DNN accelerators.

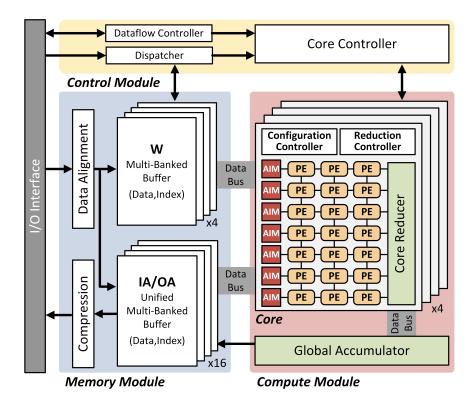

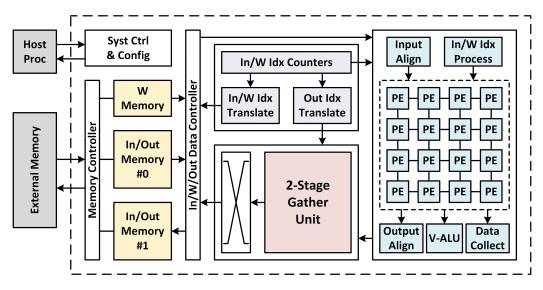

## 2.5.1 SNAP Architecture Overview

The SNAP high-level architecture is shown in Figure 2.12. It consists of multiple cores, a control module, and a memory module. The control module provides the configuration of the compute cores and coordinates the communication with the external interface. The memory module is composed of multi-banked IA and OA buffers

Figure 2.12: SNAP system architecture.

shared between the compute cores, and non-shared W buffers of each compute core. The compressed W and IA data are fetched from off-chip and aligned by bundles. W bundles are stored in each core's W buffers following the system configuration, and IA bundles are stored in the IA buffers. The output OAs are compressed before writeback to the external memory.

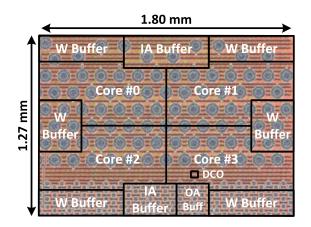

Following the high-level architecture, we designed a SNAP test chip that is made of 4 cores, and each core is implemented in a  $7\times3$  PE array. Within a core, 7 AIM units are shared in a time-multiplexed fashion between the 3 PEs in a row. Each PE is implemented with 3 multipliers and a sequence decoder. The PEs output psums, which are accumulated by the core reducer, and a global reducer is used to further accumulate psums before the final writeback.

The SNAP test chip provides a total of 252 multipliers of 16-bit fixed-point precision and a total of 280.6KB SRAM. Note that a 8-bit design would work equally

Figure 2.13: Microphoto of the 16nm SNAP test chip.

as well to demonstrate the architectural advantages and show an even better performance and energy efficiency. The only difference is that the overhead of index matching, measured as a fraction of the compute core, increases from 12.5% (in a 16-bit design) to 17% (in a 8-bit design). The test chip is implemented using a 16nm CMOS process technology with a core area of 2.3mm<sup>2</sup>. Figure 2.13 shows the chip microphoto.