# **In-SRAM Computing for Neural Network Acceleration**

by

Charles S. Eckert

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in the University of Michigan 2022

#### **Doctoral Committee:**

Associate Professor Reetuparna Das, Chair Professor Trevor N. Mudge Professor Dennis Sylvester Professor Lingjia Tang Charles S. Eckert

eckertch@umich.edu

ORCID iD: 0000-0002-8839-9890

© Charles S. Eckert 2022

#### **ACKNOWLEDGMENTS**

I would like to deeply thank my advisor Processor Reetuparna Das. Reetu has been instrumental during my PhD, always providing me with advice and support. This PhD wouldn't have been possible without her support.

I would like to thank Professor Trevor Mudge, Professor Lingjia Tang, and Professor Dennis Sylvester for agreeing to be a part of my committee and for the helpful feedback they provided throughout the process.

I am also thankful for my many collaborators during my Ph.D. In addition to being on my committee, Professor Sylvester along with Professor David Blaauw were very valuable contributors from the ECE department. I also frequently collaborated with Ravi Iyer and Charles Augustine from Intel who were able to provide an industry perspective to my research. Additionally, I worked with fellow Ph.D. students Arun Subramaniyan, Xiaowei Wang, and Jingcheng Wang who were all invaluable resources for questions and brainstorming with.

I would like to acknowledge my generous funding support from Applications Driving Architectures (ADA) Research Center and my NDSEG fellowship. NDSEG is a prestigious fellowship DoD National Defense Science and Engineering Graduate fellowship that provided me funding for the final three years of my Ph.D. In addition to funding, the fellowship gave me mentorship opportunities with two Air Force Research Labtoroies researchers, Stanley Wenndt and Andrew Noga as well as the opportunity to network at the NDSEG conference. I would like to thank Stanley and Andrew for their mentorship and support. I would like to thank Professor Blaauw, Ravi Iyer, and my advisor Professor Das for writing my recommendation letters for my fellowship.

My fellow labmates have all been wonderful people to work with, share an office with, and

hang out with outside of work; Daichi, Xiaowei, Vidushi, Arun, Tim, Hari, Yufeng, Ali, Yichen, Jack, Kush, and Yuwei.

I would also like to thank my family, my friends from undergrad, Daelin, Bar, Naz, Bryan, Zuzanna, and Hayley, and hometown friends; Ben, Bobby, Brandon, and Pat who all provided me with support. A shout out to Daelin in particular who demanded a shout-out in exchange for helping proofread my dissertation, Zuzanna and Julie instead simply helped out of the kindness of their hearts. I am also thankful for my climbing partners: Tim, Amrit, and Marisa. I was only injured twice while Tim was belaying me! I also made many wonderful friends at the university and in the area who I would like to thank; Reid, Tan, Alextia, Gabby, Tara, Andrew, Barrett, Will, Miles, Christian, and Julie.

# TABLE OF CONTENTS

| nowledgments                                                                                                                                                                                                                                                                                           | ii         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| of Figures                                                                                                                                                                                                                                                                                             | <b>vii</b> |

| of Tables                                                                                                                                                                                                                                                                                              | ix         |

| ract                                                                                                                                                                                                                                                                                                   | X          |

| pter                                                                                                                                                                                                                                                                                                   |            |

| troduction                                                                                                                                                                                                                                                                                             | 1          |

| ackground                                                                                                                                                                                                                                                                                              | 8          |

| 2.1 In-SRAM Computing          2.2 Deep Neural Networks          2.3 Accelerating Neural Networks                                                                                                                                                                                                      | 11         |

| ior Works                                                                                                                                                                                                                                                                                              | 20         |

| <ul><li>3.1 DNN Accelerators</li></ul>                                                                                                                                                                                                                                                                 |            |

| eural Cache                                                                                                                                                                                                                                                                                            | 32         |

| 4.1 Introduction 4.2 Neural Cache Organization 4.3 Neural Cache Arithmetic 4.3.1 Bit-Serial Arithmetic 4.3.2 Addition 4.3.3 Multiplication 4.3.4 Reduction 4.3.5 SRAM Array Peripherals 4.3.6 Transpose Gateway Units 4.4 Neural Cache Architecture 4.4.1 Data Layout 4.4.2 Data Parallel Convolutions |            |

| 4.4.3 Orchestrating Data Movement                                                                                                                                                                                                                                                                      | 50         |

|   |         | 4.4.6 ISA support and Execution Model                                                                          | 2  |

|---|---------|----------------------------------------------------------------------------------------------------------------|----|

|   | 4.5     | Evaluation Methodology                                                                                         | 3  |

|   | 4.6     | Results                                                                                                        | 5  |

|   |         | 4.6.1 Latency                                                                                                  | 5  |

|   |         | 4.6.2 Batching                                                                                                 | 7  |

|   |         | 4.6.3 Power and Energy                                                                                         | 8  |

|   |         | 4.6.4 Scaling with Cache Capacity                                                                              | 0  |

|   | 4.7     | Summary                                                                                                        | 0  |

| 5 | Eidetic |                                                                                                                | 1  |

|   | 5.1     | Introduction                                                                                                   | 1  |

|   | 5.2     |                                                                                                                | 3  |

|   |         |                                                                                                                | 3  |

|   |         |                                                                                                                | 5  |

|   |         |                                                                                                                | 5  |

|   |         | 1                                                                                                              | 6  |

|   | 5.3     |                                                                                                                | 8  |

|   |         |                                                                                                                | 8  |

|   |         |                                                                                                                | 0  |

|   |         | ,                                                                                                              | 1  |

|   |         |                                                                                                                | 3  |

|   | 5.4     |                                                                                                                | 5  |

|   | 5.1     | 11 6                                                                                                           | 5  |

|   |         | 11 6                                                                                                           | 8  |

|   |         |                                                                                                                | 0  |

|   | 5.5     |                                                                                                                | 1  |

|   |         |                                                                                                                | 2  |

|   | 5.7     | 6,7                                                                                                            | 4  |

|   | 3.7     | , and the second se | 4  |

|   |         |                                                                                                                | 6  |

|   |         | 6.7                                                                                                            | 7  |

|   |         | $\mathcal{C}$ 1                                                                                                | 88 |

|   | 5.8     |                                                                                                                | 9  |

|   |         |                                                                                                                |    |

| 6 | _       |                                                                                                                | 0  |

|   | 6.1     |                                                                                                                | 0  |

|   | 6.2     | 11 6                                                                                                           | 2  |

|   | 6.3     |                                                                                                                | 4  |

|   |         | r                                                                                                              | 4  |

|   |         |                                                                                                                | 5  |

|   |         |                                                                                                                | 6  |

|   |         |                                                                                                                | 7  |

|   |         |                                                                                                                | 8  |

|   | 6.4     | Summary                                                                                                        | 8  |

| 7 | Conclus | sion                                                                                                           | 0  |

| Bibliography   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 1( | 13 |

|----------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|----|----|

| Dibilogi apily | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 1  | ,  |

# LIST OF FIGURES

| Figu       | res                                                                                                                                                                                      |    |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1<br>2.2 | SRAM circuit for in-place operations. Two rows ( $WL_i$ and $WL_j$ ) are simultaneously activated. An <i>AND</i> operation is performed by sensing bit-line (BL). A <i>NOR</i> operation | 10 |

| 2.3        | Computation of a convolution layer.                                                                                                                                                      |    |

| 2.3        | •                                                                                                                                                                                        | 14 |

| 2.5        |                                                                                                                                                                                          | 15 |

| 3.1        | Google TPU with its 2D Systolic Array                                                                                                                                                    | 21 |

| 4.1        | V 11 1                                                                                                                                                                                   | 36 |

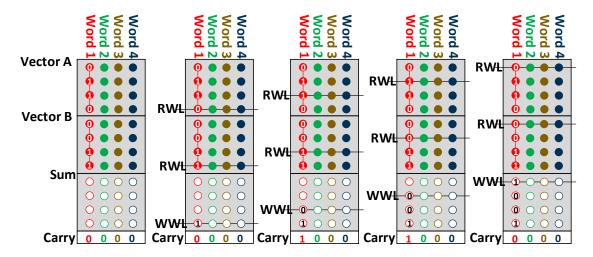

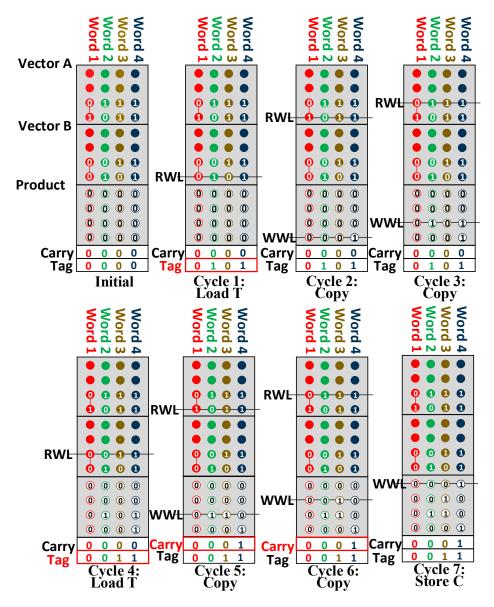

| 4.2        | Addition operation                                                                                                                                                                       | 37 |

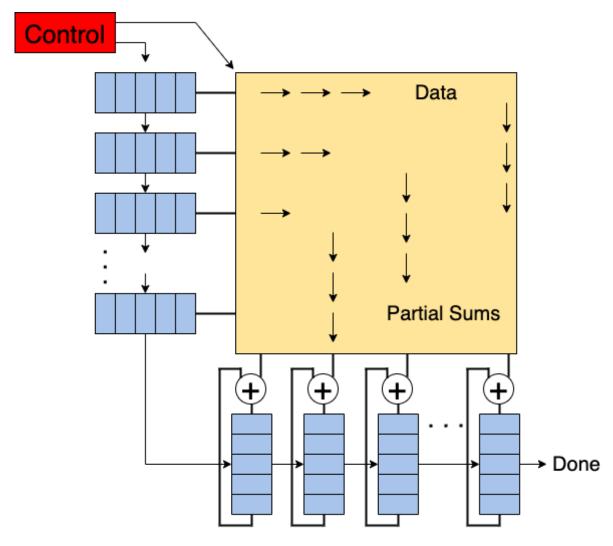

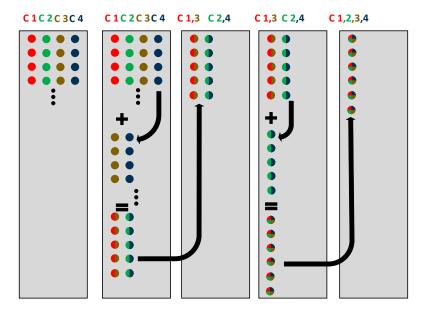

| 4.3        | Reduction Operation                                                                                                                                                                      | 38 |

| 4.4        |                                                                                                                                                                                          | 39 |

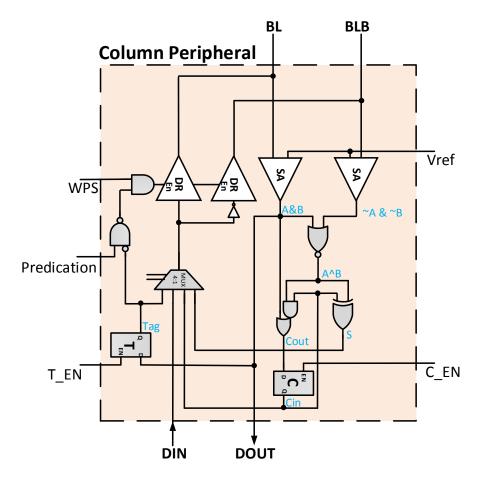

| 4.5        | Bitline peripheral design                                                                                                                                                                | 42 |

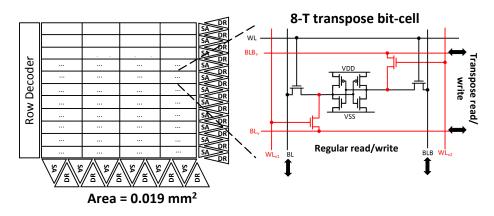

| 4.6        | Transpose Memory Unit (TMU)                                                                                                                                                              | 43 |

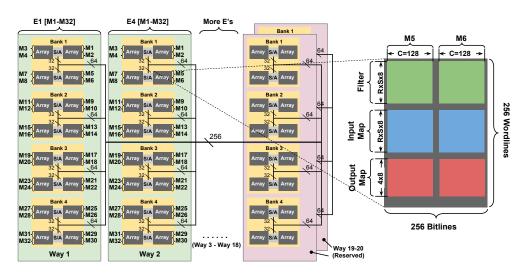

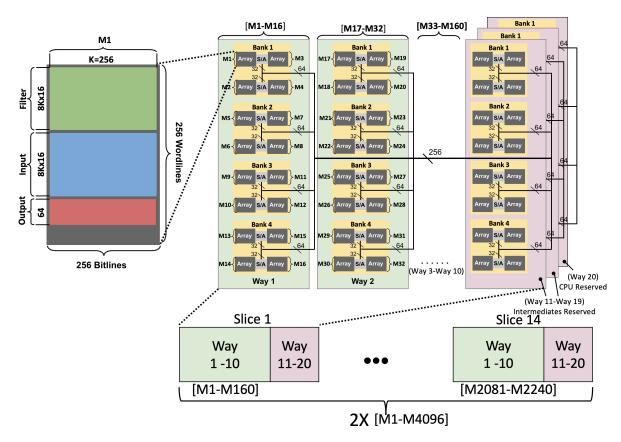

| 4.7        | Neural Cache Data Layout for one LLC Cache Slice                                                                                                                                         | 43 |

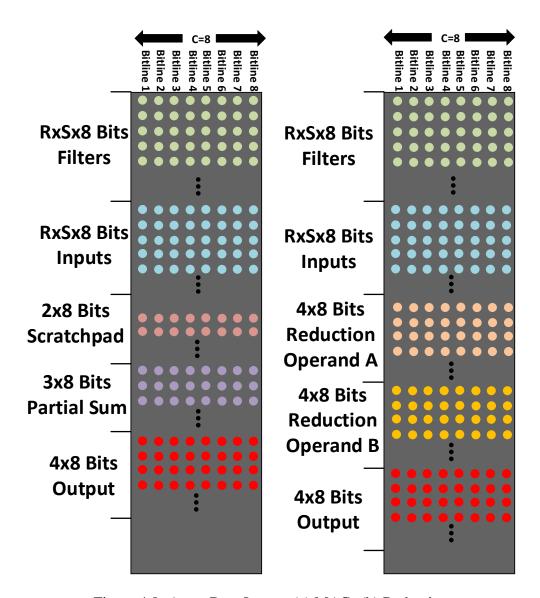

| 4.8        | Array Data Layout (a) MACs (b) Reduction                                                                                                                                                 | 46 |

| 4.9        | Partitioning of Convolutions between Slices                                                                                                                                              | 47 |

| 4.10       |                                                                                                                                                                                          | 53 |

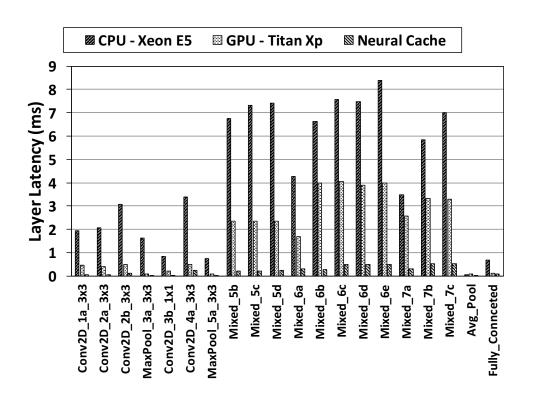

| 4.11       | Inference latency by Layer of Inception v3                                                                                                                                               | 56 |

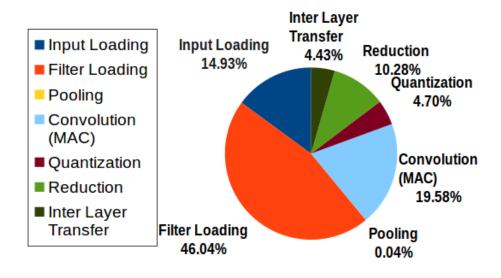

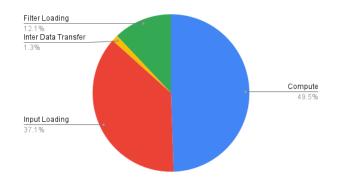

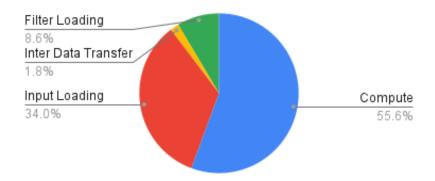

| 4.12       | Inference Latency Breakdown                                                                                                                                                              | 56 |

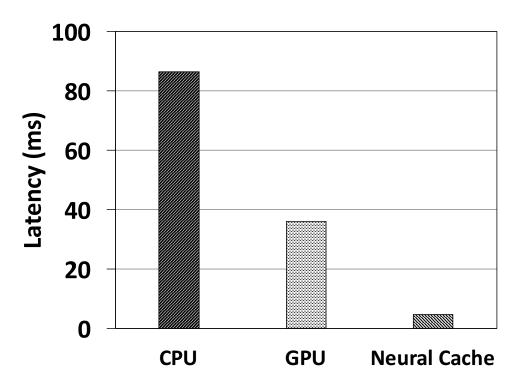

| 4.13       | Total Latency on Inception v3 Inference                                                                                                                                                  | 58 |

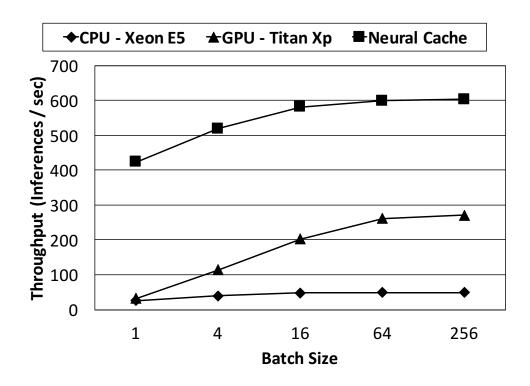

| 4.14       | Throughput with Varying Batching Sizes                                                                                                                                                   |    |

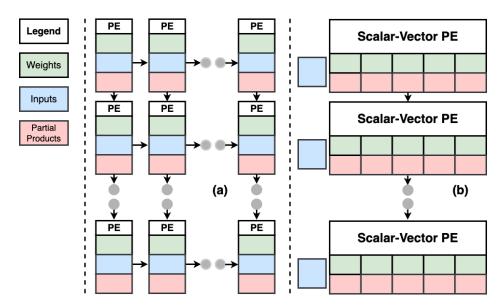

| 5.1        | (a) Systolic Array (b) Optimized Systolic Array                                                                                                                                          |    |

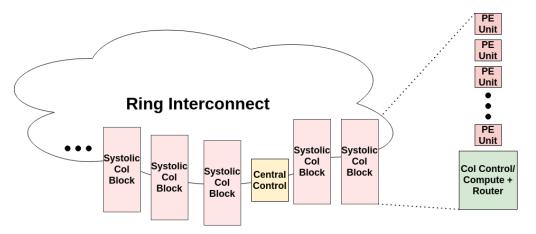

| 5.2        | Eidetic Overview                                                                                                                                                                         |    |

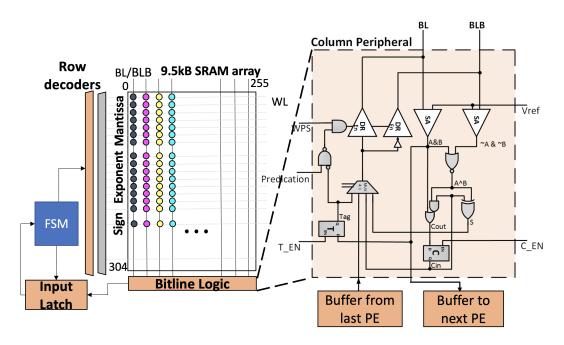

| 5.3        | SRAM-based <i>Eidetic</i> PE Unit                                                                                                                                                        |    |

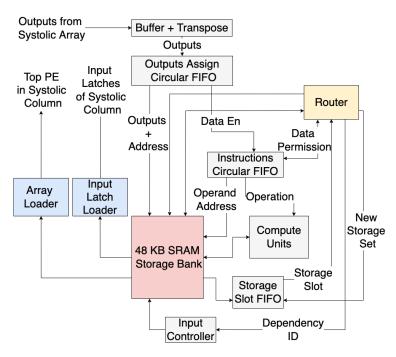

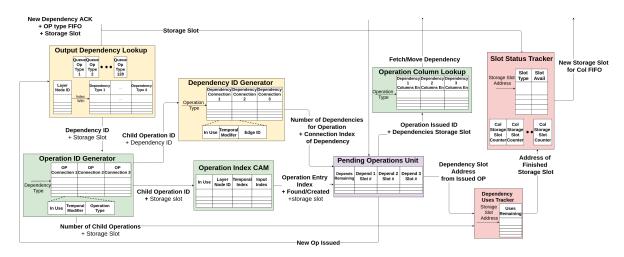

| 5.4        | Column Block Logic Overview                                                                                                                                                              | 72 |

| 5.5  | Control Flow of Central Control Unit. Bold text between units indicates the passed |    |

|------|------------------------------------------------------------------------------------|----|

|      | information was created in one of the units                                        | 74 |

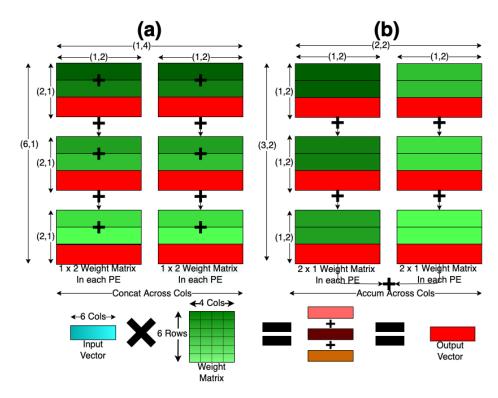

| 5.6  | Mapping of weights to a systolic array                                             | 76 |

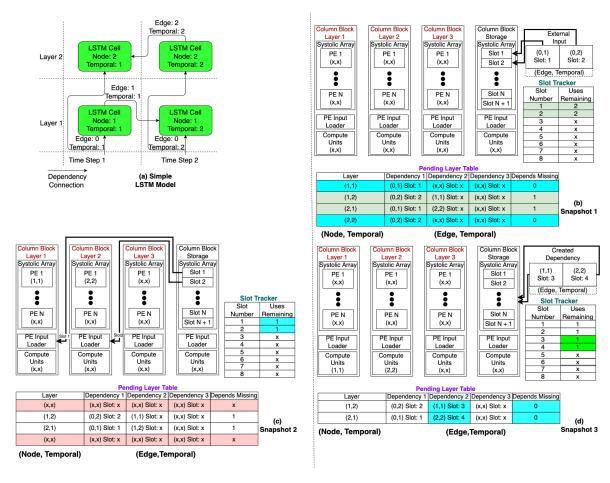

| 5.7  | Putting it together                                                                | 81 |

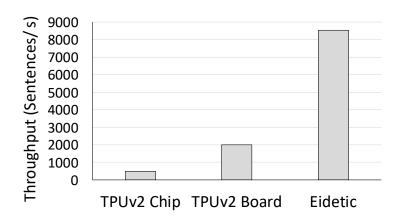

| 5.8  | Throughput of TPU Batch Size 1024 vs <i>Eidetic</i> Input Batch Size 16            | 85 |

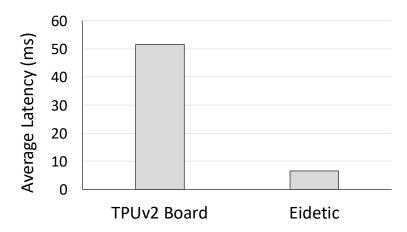

| 5.9  | Latency of TPU Batch Size: 8 vs <i>Eidetic</i> Input Batch Size: 16                | 85 |

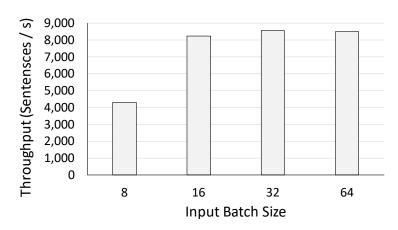

| 5.10 | <i>Eidetic</i> throughput by input batch size                                      | 86 |

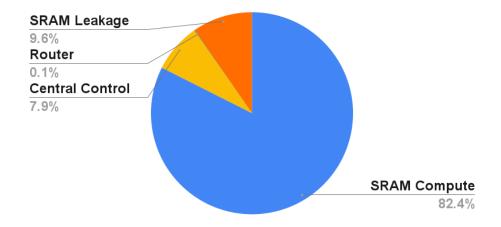

| 5.11 | Power Breakdown                                                                    | 87 |

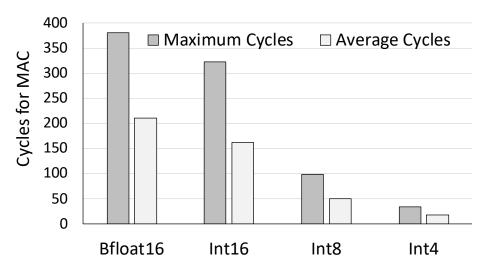

| 5.12 | Avg. and Max Cycles for MAC – different precision                                  | 89 |

| 6.1  | Mapping of Eidetic on Neural Cache                                                 | 92 |

| 6.2  | Breakdown of <i>Neural Cache</i> 's Throughput                                     | 96 |

| 6.3  | Breakdown of <i>Neural Cache</i> 's Energy                                         | 96 |

# LIST OF TABLES

| Tabl | les                                                                                                                                                                                                                                          |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.1  | Parameters of the Layers of Inception V3                                                                                                                                                                                                     | 53 |

| 4.2  | Baseline CPU & GPU Configuration                                                                                                                                                                                                             | 54 |

| 4.3  | Energy Consumption and Average Power                                                                                                                                                                                                         | 59 |

| 4.4  | Scaling with Cache Capacity (Batch Size=1)                                                                                                                                                                                                   | 59 |

| 5.1  | Area breakdown of <i>Eidetic</i> by component. There are 54 Systolic Column Blocks each with 2.375MB of compute SRAM                                                                                                                         | 86 |

| 5.2  | Area and power normalized throughput comparison for different accelerators. For comparison, the metrics in the last five rows are normalized to 22nm using Deep-ScaleTool [2]. For TPUv3 and Hanguang 800, we conservatively assume reported |    |

|      | numbers are in 14nm for normalization to 22nm                                                                                                                                                                                                | 87 |

| 5.3  | ML Microbenchmarks Eidetic Mapping and TPU V2 and Eidetic Performance                                                                                                                                                                        | 88 |

| 6.1  | Comparison of Eidetic and Neural Cache Latency and Throughput                                                                                                                                                                                | 95 |

| 6.2  | Comparison of Eidetic and <i>Neural Cache</i> Energy and Power                                                                                                                                                                               | 95 |

#### **ABSTRACT**

For decades, the computing paradigm has been composed of separate memory and compute units. Processing-in-Memory(PIM) has often been proposed as a solution to break past the memory wall. With PIM, compute logic is moved near the memory, which can reduce the data movement. In-memory computing expands on PIM by morphing the memory into hybrid memory compute units, where data can be stored and computed on in-place. Recent work has modified SRAM arrays to allow logical operations to be performed directly inside the arrays. Our work extends basic logical operations and additionally adds support for arithmetic operations.

Coinciding with the rise of increasing memory on-chip and more focus on near and in-memory computing is the ascendance of neural networks. Neural networks are highly data-parallel applications that are challenging to accelerate due to being data-bound, compute-bound, or both. In-memory computation reduces on-chip data movement and will increase the amount of compute available as well as the amount of storage in a custom chip. These factors can greatly alleviate compute and data bottlenecks.

First, this thesis observes that SRAM memory has increasingly dominated the on-chip area for general-purpose processors. This area comes at the cost of compute potential and can be repurposed to function as a dual storage and compute unit. The benefits of such repurposing are greatly expanding the parallel compute capability of the chip while also reducing the on-chip data movement, all with minimal area increase. When SRAM is repurposed, the storage area can be reclaimed with minimal overhead. Modifications to the SRAM arrays are presented that allow the SRAM to function as hybrid compute/storage units capable of arithmetic operations. Additionally,

this work presents a mapping strategy for supporting CNNs in the hybrid SRAM storage compute arrays.

Second, this thesis proposes a custom ASIC called Eidetic that utilizes hybrid compute/storage SRAM arrays as both its primary storage and compute units. Repurposing a processor's SRAM is hamstrung by maintaining the cache's original functions and area footprint. Too many modifications to the cache would render the solution undesirable to chip designers. By further customizing the SRAM we can create more efficient PE units. Additionally, the increased SRAM storage allows more weights to be stored on-chip. Finally, the custom ASIC allows for a control logic that supports a graph-based programming model that further reduces off-chip data movement. These customizations allow Eidetic to target data-bound applications such as RNNs and MLPs.

Third, we propose a detailed comparison between the in-cache and ASIC approaches to ML acceleration. Between repurposing the cache and creating an SRAM-based custom ASIC, in-SRAM computing offers multiple viable approaches. In-Cache computing is cheaper but comes with limitations, while an ASIC design is more expensive due to the total cost of ownership (TCO).

We compare the performance and energy efficiency of our repurposed cache with a serverclass GPU and the baseline CPU. We similarly evaluate our custom ASIC to other state-of-the-art ASIC DNN accelerators. For both the repurposed cache and the ASIC, we develop cycle-accurate simulators to determine the performance.

### **CHAPTER 1**

## Introduction

Over the last two decades compute architecture has been increasingly limited by the gap between memory and compute known as the memory wall. The performance of compute on-chip is increasing at a much faster rate than the improvements in off-chip (DRAM) memory technology. The difference in improvement rates is leading to an imbalance in the speedups of compute and memory. As Amdhals's law dictates, speedups for one component of execution (compute) will result in continually decreased performance gains as the other components (memory) dominate execution time. Thus, the current paradigm of computer architecture has led us to a memory wall where memory bandwidth and memory energy have increasingly dominated execution time and energy. Another trend in computer architecture is the increase in the number of cores on-chip. Previously, the frequency could be increased from one generation to another without vastly increasing the amount of power used. However, since the end of Dennard scaling, this is no longer true, thus motivating increasing the number of cores on-chip to increase compute performance.

Overcoming the memory wall problem is a complicated task with several suggested solutions. One option is to address this gap by adding/increasing the amount of intermediate storage between the DRAM and compute. Static random-access memory (SRAM) is on-chip memory that is commonly found on most chips, particularly as the cache. The cache is typically organized in a multi-level hierarchy of SRAM, where from level to level, the amount of SRAM in that group is increased, but so is the time and energy to fetch data. By increasing the amount of on-chip storage, more data can be reused without going off-chip. However, increasing the amount of SRAM

comes with costs. More on-chip SRAM creates the need for a deeper and wider hierarchy, thus increasing the time and energy of on-chip data access. This is still less than the cost of accessing data from off-chip. Additionally, any area dedicated to on-chip storage means a reduction in the number of compute units as well as an increase in static/leakage power from the SRAM. Since memory access is the larger bottleneck, sacrificing some compute for storage will yield speedups. However, sacrificing one component of the execution for another will limit the possible speedups compared to a solution where neither is sacrificed. Thus increasing the on-chip area for storage is an imperfect solution.

Another solution involves rethinking the memory/compute paradigm and how they are separated on-chip. It is possible to move the compute closer to the memory. Moving the compute closer has been referred to as processing-in-memory (PIM) or near-memory computing. PIM has long been suggested as a solution to the memory wall. PIM helps alleviate issues with on-chip data movement with the compute units close to the memory units. However, the compute can be moved even closer. Instead of using separate compute and storage units, the two can be morphed together as a single unit where data is both stored and computed on. This style of architecture termed *in-memory computing* can offer intrinsically more efficiency compared to the traditional computing paradigm or even near-memory computing. Additionally, hybrid compute memory units can offer a lower overhead than separate compute and memory units.

The industry has largely responded with the first solution, with on-chip SRAM increasingly growing over the last two decades. Chips today have SRAM exceeding 3/4 of the total die area. However, these two solutions do not necessarily have to be separate. SRAM can be modified to support in-memory computing with minimal cost. This is a very attractive solution as on-chip memory would no longer come at sacrificing compute area. Additionally, SRAM is an existing technology that can be found on almost any chip. SRAM has ongoing research efforts to scale and reduce power, as well as an established manufacturing protocol. Less established technologies would require significant investments to implement and manufacture. And since it is found everywhere, incorporating in-SRAM computing into existing architectures is a more viable solution.

Further exasperating the memory wall bottleneck is the rise of data-intensive applications, such as neural networks. These data-intensive applications have created a data bottleneck from general-purpose CPUs to accelerators. Neural networks in particular suffer from both computation and data bottlenecks, making it difficult to balance both the amount of compute and storage on-chip. In-memory computing with SRAMs offers a way to achieve this balance.

Previous work for in-SRAM computing has provided the basis for logical operations but lacks support for arithmetic operations. By increasing the capabilities of the SRAM compute arrays to perform arithmetic operations, neural networks can be supported.

This dissertation offers two solutions for accelerating DNNs using in-memory computing to push back against Moore's slowdown and the memory wall. By using in-SRAM computing, we can transform existing processors and build custom chips that will see significant performance improvements. By offering a solution for both general purpose and customs chips, we show the vast potential of in-SRAM computing.

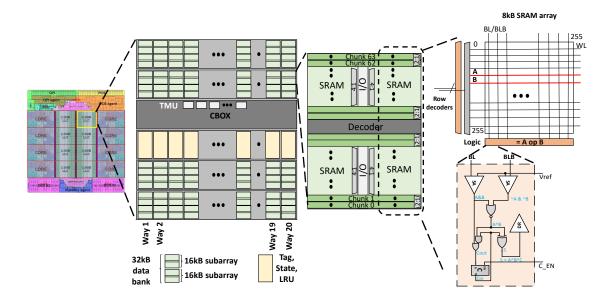

Firstly, our work in *Neural Cache* allows us to take an existing processor that is designed for general-purpose computing and expand its capabilities to parallel computing for neural network acceleration. The last level cache of the Xeon can be repurposed from a storage unit to a hybrid compute-storage unit capable of bit-serial arithmetic. This is accomplished primarily by augmenting logic to the peripherals of the SRAM array, resulting in a very small area penalty. The Intel Xeon E5-2697 v3 35MB cache can be transformed into 1,146,880 bit-serial ALUs. Additionally, *Neural Cache* provides a mapping for CNNs and data movement strategies that allow these bit-serial ALUs to take advantage of the inherent parallelism of DNNs for massive performance gains. All of this is accomplished without the need for a new chip or sacrificing the CPU's general-purpose computing capabilities. With the rise in demand for parallel processing, the ability to support both general-purpose and parallel processing is a huge advantage that cannot be overstated.

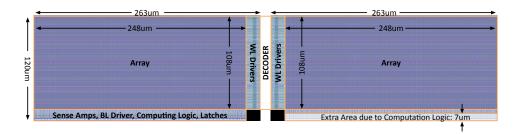

The work in *Neural Cache* presents bit-serial computing in SRAM arrays. With modifications to the bitline peripherals, we can perform addition, subtraction, multiplication, division, and

comparison on any two operands stored along a bitline, without moving them outside the array. Additionally, the computation inside the array is driven by an FSM rather than fixed logic. This allows us to support configurable precision without adding additional hardware to the SRAM arrays. Adding compute support to the SRAM arrays only incurs a 2% area overhead across the processor chip while adding 1,146,880 bit-serial ALUs.

In order to facilitate bit-serial computation, we first need to transpose our data. This can be done in software, but we instead developed hardware to transpose our data on the fly. Our transpose memory units (TMU) are a custom 8T SRAM array used solely to transpose data. The additional transistors are designed to add an extra set of bitlines and wordlines that are perpendicular to the originals. This allows data to be written horizontally into the array as usual, but then the perpendicular wordline can be activated to read data out vertically, as if along the bitline. As weights can be pre-transposed, only a few TMUs in the cbox for each slice are needed to transpose the input.

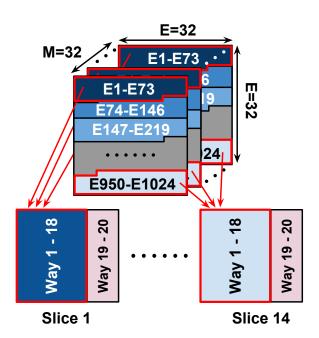

Additionally, this work provides a mapping for CNNs onto our newly compute-enabled cache. The filters and inputs can be unrolled into 2D matrices, with one dimension being the height and width of the filter, and the other the input and output channels. Along an SRAMs bitline, the unrolled filters and inputs can be stored. This allows us to perform multiple multiplications and accumulate the outputs along the bitline. Across the bitlines in the arrays, other channels of the output activation are computed. The reduction will be performed inside the SRAM arrays. The remaining input channels, followed by the output channels, will be mapped across the SRAM arrays in a bank, the banks in a way, the ways in a slice, and the slices on-chip. Small layers can be replicated to allow more output activations to be computed in parallel.

This data mapping is designed to exploit the parallelism in CNNs and reuse the weights as much as possible. Every multiply in the convolution is independent of each other; however, the multiplications within a filter window and across the filter channels will be accumulated. The next sliding window of inputs can be loaded into the array to reuse the weights that are stored in the SRAM arrays. This mapping allows accumulation to stay local while also reusing the weights.

Weight replication reduces the weight reuse, but will improve the parallelism that can be exploited, and therefore throughput.

Secondly in *Eidetic* we look to push the power of in-SRAM computing further by designing a custom architecture that uses in-SRAM computing as its fundamental building block. By creating a custom architecture instead of repurposing an existing cache, *Eidetic* is able to break past the limitations of *Neural Cache*. *Eidetic* can support many more compute units than *Neural Cache* without the CPU logic or cache overhead. *Eidetic* contains 3,538,944 bit-serial ALUs while remaining effectively area neutral with *Neural Cache*. Additionally, the architecture can be designed to more efficiently handle the data-bound problems in DNNs with a focus on pinning weights, facilitating data movements, and handling data dependencies. Finally, the SRAM PEs can be redesigned to improve their efficiency. These modifications give *Eidetic* significantly more compute power, but also ensure the availability of data to compute on.

By customizing the SRAM arrays and their organization, we can optimize our SRAM architecture to balance power, storage density, area, and compute throughput. The SRAM PEs can be organized into a systolic array allowing accumulation to be performed through more efficient data propagation rather than reduction across bitlines. A systolic array is a common dataflow architecture for neural networks that focuses on data reuse and data movement. Further, the compute operations themselves can be optimized with the addition of an input latch outside the SRAM arrays.

The vast increase in the number of SRAM arrays coupled with a custom array structure allows for new possibilities such as pinning weights, computing in place on the pinned weights, and executing multiple layers in parallel. *Eidetic* custom control logic allows on-demand processing of inputs for a network with complex dependencies and inputs of varying lengths. The custom control logic creates a second tier to the dataflow architecture, where the outputs of a layer are automatically routed to the input of the next layer. These optimizations are made to overcome potential data bottlenecks so that the vast number of compute units can be kept occupied.

Finally, in this dissertation, we discuss the usage of both approaches, including the cost and

benefits of each. Providing both of these solutions and an analysis of the two allows us to make a case for in-SRAM computing to take over the computing paradigm.

In summary, this dissertation offers the following contributions.

- Neural Cache, an architecture that repurposes the last level cache to support the inference

of DNNs. This repurposing maintains the original cache structure and results in minimal

increases in total area.

- SRAM modifications for Neural Cache that allow for arithmetic operations such as multiplication, division, subtraction, and addition. Each SRAM array is transformed into 256 vector bit-serial ALU.

- A data layout for Neural Cache to optimize the mapping of DNNs. The parallelism of DNNs is exploited across the cache structure of the SRAM arrays.

- Eidetic, an architecture that uses in-SRAM computing to accelerate neural networks. The ASIC design allows for more efficient neural network inference.

- Customization of the SRAM PEs to support scalar vector multiplication, resulting in simplified systolic arrays. The customized SRAM allows for reduced data movement and more efficient operations.

- A dataflow architecture capable of mapping neural networks based on high-level graphs. The graph-based programming reduces the amount of off-chip data movement.

- A comparison and a discussion between the two approaches. This discussion provides optimal use cases and makes the case for the range of in-SRAM computing.

Our experimental results show that the proposed architecture can improve inference latency by  $18.3 \times$  over state-of-art multi-core CPU (Xeon E5), and  $7.7 \times$  over server-class GPU (Titan Xp), for Inception v3 model. *Neural Cache* improves inference throughput by  $12.4 \times$  over CPU ( $2.2 \times$  over GPU), while reducing power consumption by 50% over CPU (53% over GPU). We evaluate *Eidetic*

on Google's Neural Machine Translation System (GNMT) encoder and demonstrate a  $17.20 \times$  increase in throughput and  $7.77 \times$  reduction in average latency over a single TPUv2 chip.

The remainder of this dissertation is as follows. We discuss the background and related research work in Chapter 2. Following that, we describe our proposed research in transforming a cache into a neural network accelerator in Chapter 4 and our SRAM-based ASIC for neural network acceleration in Chapter 5. In Chapter 6 we discuss the two approaches of using cache vs a custom SRAM-based architecture for neural network acceleration. Finally, we conclude the dissertation in Chapter 7.

### **CHAPTER 2**

# **Background**

In this chapter, we will first give a background on the design and usage of SRAM in modern architectures. Then we will discuss how SRAM can be modified to support computation. Finally, we will give an overview of the types of DNNs, discussing their usages, characteristics, and features.

## 2.1 In-SRAM Computing

Random-access memory (RAM) is a category of memory that is extremely common in on-chip caches and off-chip main memory. RAM is a type of volatile memory that requires constant power to retain the stored data. The two main types are static (SRAM) and dynamic (DRAM). DRAM's memory cells typically consist of a capacitor and transistor and require frequent refreshes to retain the data/charge. The memory cell for SRAM is generally composed of 6 transistors (6T) and does not require a refresh. SRAM is less dense than DRAM, but is more energy efficient and provides for faster memory reads and writes. For instance, SRAM arrays are capable of operating at high frequencies such as 4.0GHz in Intel's Xeons. Most modern processors utilize SRAM for both register files and on-chip caches. Two sets of two transistors store the bit and inverted bit value within the memory cell. The other two transistors are used for access control. The SRAM memory cells have a set of complement bitlines, BL and BLB, and a wordline that is used for reading and writing to the cells. During the read access, the set of bitlines is pre-charged, and the wordline is activated. This connects the stored bit and the inverted bit to the pair of bitlines and will cause the voltage on one of the bitlines to drop. A sense amp reads the difference between these bitlines to

determine if a one or zero is stored. To write a value, the charge and the inverted charge are applied to the corresponding bitline and inverted bitline. The target wordline is also activated during the write. These components are shown in Figure 2.2.

SRAM cells are typically organized in a 2D array, with cells along a column sharing a bitline and cells across a row sharing a wordline to share the needed peripherals, decreasing the area overhead. This structure allows reading and writing to the SRAM array in parallel across a single row only. An SRAM array has a row decoder used to select a wordline. Typically multiple sets of bitlines will share a single sense amp. This reduces the parallel access to a row by the amount of sense amp sharing or column muxing. Modern processors store and compute data in a bit parallel format. Processors have a fixed data width of a "word" that contains some multiple of 8 bits. Data is read and written in the SRAM arrays in this granularity, with multiple words occupying a cache line.

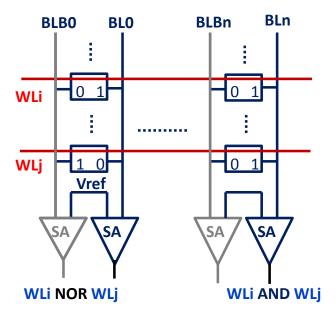

This dissertation builds on previous work on SRAM bitline circuit technology [1, 3, 4] shown in Figure 2.2. To enable computation on data stored along a bitline, a second row decoder is added so that two wordlines can be activated simultaneously. Additionally, the differential sense amp is replaced with two single-ended sense amps. When multiple wordlines are activated, these two single-ended sense amps can be configured to detect if the activated cells along the bitline contain all ones or zeros. This effectively allows in-place computation of (and and nor) along a SRAM bitlines.

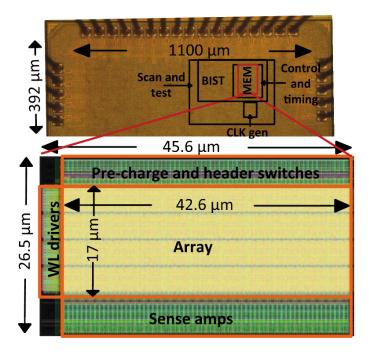

Data corruption due to multi-row access is prevented by lowering the wordline voltage to bias against the write of the SRAM array. Measurements across 20 fabricated 28 nm test chips (Figure 2.1) demonstrate that data corruption does not occur even when 64 wordlines are simultaneously activated during such an in-place computation, which is more than adequate as compute cache requires only two. Monte Carlo simulations also show a stability of more than six sigma robustness, which is considered the industry standard for robustness against process variations. The robustness comes at the cost of an increase in delay during compute operations. Conventional array read/write accesses remain unaffected. The increased delay is more than compensated by

Figure 2.1: Prototype test chip [1].

Figure 2.2: SRAM circuit for in-place operations. Two rows (WL<sub>i</sub> and WL<sub>j</sub>) are simultaneously activated. An *AND* operation is performed by sensing bit-line (BL). A *NOR* operation is performed by sensing bit-line complement (BLB).

massive parallelism exploited with in-SRAM computing.

Compute caches [5] further extends the in-SRAM bitline computing framework to support additional operations: copy, bulk zeroing, xor, equality comparison, and search. With this, they make a case for using a processor's cache for processing data-centric operations by addressing various architectural problems: operand locality, managing parallelism across various cache levels and banks, coherency, consistency, and reliability. Performing computation along the bitline with data stored in a bit-parallel format prevents more complicated operations, such as addition, because there is no way to move data across the bitlines without additional hardware. Addition would require a carry to be propagated across the bitlines.

Cache Automaton [6] introduced the concept of sense amp cycling. If an SRAM array has multiple columns that share a sense amplifier, sense amp cycling can be used to increase the throughput of in-SRAM compute. Most of the compute cycle is spent pre-charging the bitlines with a smaller amount of time devoted to sensing. Thus all bitlines can be precharged, and the sense amp can cycle through each shared bitline without the pre-charging overhead.

## 2.2 Deep Neural Networks

The field of Deep Neural Networks (DNNs) and Machine Learning (ML) was reinvigorated by Alexnet in 2012. Alexnet achieved significant improvements at ImageNet 2012. Alexnet showed the importance of using multiple layers in a network and GPUs' potential to make training these deep neural networks feasible. DNNs are a key component in the field of Machine learning with applications in bioinformatics, speech recognition, autonomous vehicles, economics, fraud detection speech translation, and more.

Artificial Neural Networks (ANNs) are attempts to mimic biological neural networks by creating a layer of nodes with a weight or learned value that interacts with inputs to produce an output. Deep neural networks are ANNs with multiple layers between the input and output layers. Neurons can be implemented in a variety of different ways, but typically invoke a matrix operation such

as matrix-matrix multiplication, vector-matrix multiplication, and convolution. Common types of DNNs are multi-layer perceptrons (MLPs), Recurrent Neural Networks (RNNs), Convolutional Neural Networks (CNNs), and Transformers. While CNNs utilize convolutions, the convolution is often converted into matrix-matrix multiplication. The nodes in RNN, MLP, and Transformer all heavily utilize matrix multiplication. RNNs introduce a recurrent data dependency and transformers invoke a self-attention mechanism. The two most important operations in a neural network are convolution and matrix multiplication. However, since a convolution can be converted to matrix multiplication, accelerators can be optimized strictly for matrix multiplication operations.

DNNs have two important stages; training and inference. Training uses a set of test data to determine optimal weight values for all the nodes or neurons in the network. The network will be trained for specific applications or tasks. Training data consists of input data and the desired output/classification for each input. Additionally, a separate set of test data is used to evaluate the accuracy of the output without the network being specifically trained on it. Most commonly an algorithm called gradient descent is used to update the weights based on the error from the expected outputs and the realized outputs. Inference is running the network with inputs after the network has been trained for the task.

MLPs are usually defined as a relatively generic feed-forward ANN. A basic MLPs layer consists of matrix multiplication usually followed by a nonlinear activation such as sigmoid or tanh.

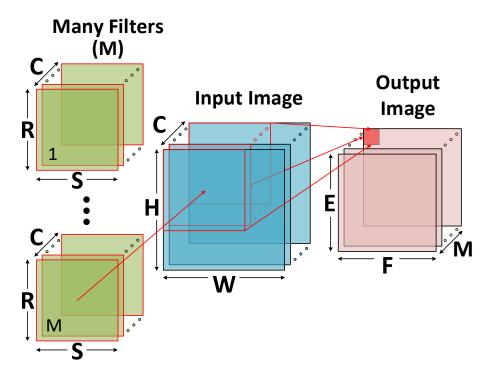

CNNs will typically have pooling and fully connected layers mixed in as well. Rectified Linear Unit (ReLU) is typically used as the activation function for each layer. Most CNNs spend the majority of the compute during the convolution cycles. A convolution layer uses the weights as a filter and applies the filter to the input image. Filters have four dimensions, height (R), width (S), channels (C), and batches of 3D filters (M). Inputs have three dimensions with a height (H), width (W), and channel (C). The filter is overlaid on the inputs, and each pixel of the input is multiplied by the corresponding filter pixel and repeated across the M dimension. The results across the  $R \times S$ , i.e. the height and width, are accumulated together. Further, the channels are also reduced

Figure 2.3: Computation of a convolution layer.

into a single element. Thus each window gives us an output of  $1 \times 1 \times M$ . The filter window is slid across the input to produce multiple output activations. The window is slid using a stride (U), increasing the stride will decrease the number of output elements computed. The output's channel size is equivalent to the M dimension of the filter. The output image, after an activation function that varies across networks and layers, is fed as the input to the next layer. CNNs vary greatly in size and number of layers. AlexNet, for instance, has 5 convolutional layers and 3 fully connected layers whereas Inception v3 has 94 convolutional 'sub layers'. The convolutional layers at the start of a network tend to have an input with a large height and width, whereas the channel size and depth of the filters are small. The layers at the end feature inputs with smaller heights and widths but have a much larger depth and number of channels. This results in the first layers having smaller weight matrices but a larger amount of compute, and the later layers having larger weight matrices but a smaller amount of compute.

RNNs introduce a recurrent element through a temporal dependency. The output of a node is not only passed to the next layer but is reused in the same node for a future input. This is extremely

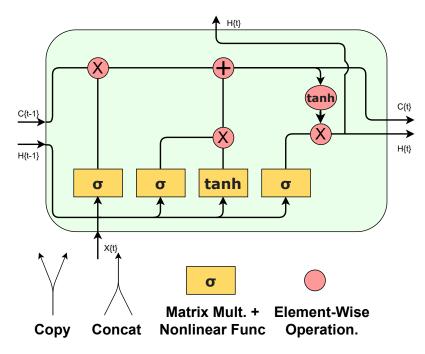

Figure 2.4: Typical LSTM Cell showing micro-operations performed

useful for speech translation, where words in a sentence are separate components of the inputs and the meaning depends on past and future words. Incorporating the previous word's output into the input of the node allows past information to be retained. Additionally, a network can have a bidirectional layer where the input is reversed allowing for translation to be based on the past and future words in the sentence.

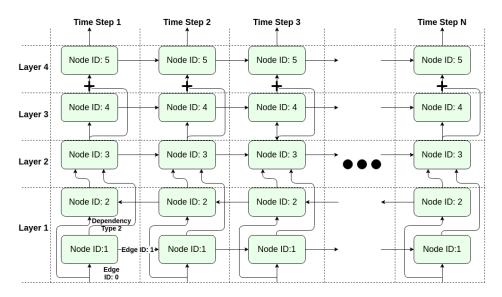

Long short-term memory (LSTM) is a popular subcategory of RNNs. An LSTM layer is typically referred to as an LSTM cell. Each cell takes in and concatenates an input from a previous layer and its own output from a past or future time step. Figure 2.4 shows an LSTM cell that consists of various micro-operations. The yellow box represents a matrix multiplication operation (matmul) with hidden weights, followed by a non-linear activation function. The outputs of these non-linear functions are then involved in a variety of element-wise operations. The outputs of the cell can become inputs to the next cells and the same cell at a different time step. GNMT is a widely used LSTM, a subclass of RNN, that features a bidirectional layer. Figure 2.5 shows how the different LSTM cells connect across layers and time steps in the GNMT encoder.

Matrix-Matrix multiplication can be described with an input matrix of [n x k] and a weight

Figure 2.5: GNMT Encoder Layout

matrix of [k x m]. Note that the number of columns in the input matrix and the number of rows in the weight matrix match. A convolution can be converted into a matrix multiplication by performing an Im2col transform on the input image. This creates an input matrix of dimensions [E\*F x R\*S\*C] with a weight matrix of dimensions [R\*S\*C x M]. A column of elements from the input matrix is multiplied by the corresponding elements of a row of the weight matrix with the products being accumulated together. This multiplication and accumulation happen for each input row and weight column pair. Thus the output matrix will be of dimension [n x m]. The number of multiply and accumulations needed will be n\*k\*m.

DNNs have a wide range of network and layer sizes based on their application, power, latency, and throughput budget. A larger network tends to have better accuracy but also increases the amount of compute and energy needed. For instance, EfficientNet is an image classification network designed for edge computing with 5.3M parameters. Bert Large, on the other hand, is used in data centers for Natural Language Processing (NLP) and contains 345M parameters.

## 2.3 Accelerating Neural Networks

Matrix multiplication is a highly parallelizable operation, as every multiplication is independent of each other and thus can be parallelized. However, the weight matrices in networks are generally too large to parallelize every multiplication. Additionally, since the products produced need to be accumulated with other products from the same row in the weight matrix, it is common for DNN accelerator architectures to design PEs capable of a single fused multiply and accumulate (MAC). Products that are accumulated together can be created sequentially in the MAC units, eliminating the need for a separate accumulation.

Matrix multiplication acceleration can suffer from being compute-bound or data-bound, and sometimes both across multiple layers. Compute-bound refers to when computation is limited by the number of compute units. If a bottleneck is created because there are more available operations to perform than compute units, the application is said to be compute-bound. Data-bound can refer to when there are available compute units, but not enough operations are available to execute due to lack of data. The lack of data can come from on-chip data movement and off-chip data movement as well as from data dependencies. TPUv1 detailed the breakdown of compute cycles and data stalls for a pair of each CNNs, MLPs, and LSTMs. The compute units in MLPs and LSTMs were only active 8.2% to 12.7% of the execution time. Instead loading weights from memory and moving weights on-chip resulted in stalls for between 57.6% and 79.2% of the cycles for the 4 MLPs and LSTMs. The two CNNs had the compute units active 78.2% and 46.2% of the cycles, with weight stalls and shifts between 0.0% to 35.1%. These number help show the extreme range that DNNs can have for being compute-bound or data-bound.

Critical factors for accelerating DNNs consist of supporting optimal precision(s), optimizing data reuse, facilitating optimal dataflow, and having a large amount of compute units available. Additionally, these factors affect throughput, latency, and power budgets which need to be balanced. The type of precision(s) supported affects not only the accuracy of the network but the ability to do training, the compute units' speed, the power of the compute units, the area of the compute units as well as the available software support. Data reuse is also a key factor, as every off-chip

memory access and on-chip storage access adds an energy and delay penalty. Efficient caching can prevent multiple off-chip memory access for the same data. Further data can be reused in registers. Both reducing off-chip and on-chip accesses are achieved by creating an architecture and data mapping designed for the parallel computation and data reuse of neural networks. Facilitating an efficient dataflow can be key to making reuse available without stalls. Accumulations, dependencies between layers, and replications of weights or inputs for parallelization all have dataflow considerations. Throughput and latency will often have an inverse relationship when inputs are batched together to increase the reuse of the weights.

DNNs are most commonly designed using single-precision floating-point format (FP32) data format. FP32 is used to represent a dynamic range of decimal numbers. IEEE FP32 contains a sign bit, 8 exponent bits, and 23 fraction or mantissa bits. With this dynamic range, FP32 can represent both  $1.4012984643 \times 10^{-45}$  and  $3.4028234664 \times 10^{38}$ . Floating point is used for training neural networks due to its increased flexibility in range and precision. Training with floating point results in significantly better accuracy than with integers.

Other reduced precision floating point formats can also be used. IEEE half-precision floating-point format (FP16) uses 5 exponent bits and 10 mantissa bits. Bfloat16 instead uses a truncated version of IEEE FP32, maintaining 8 bits for the exponent but reducing the mantissa bits to 7. Nvidia's TensorFloat uses a 19-bit format, 8 for the exponent and 10 for the mantissa. AMD's fp24 uses 7 exponent bits and 16 mantissa bits. Note that all of these formats have a single bit for the sign.

Additionally, networks can be quantized to an integer format for inference. Oftentimes the activations and weights are converted to int8 but extremely low precisions with binary quantization are also used. The range of values for activations and weights can be calculated. The range can be used to create a scale and offset value that is used to convert the floating point values to integers. After a layers computation, the output is converted back to floating point using the scale. Networks can be trained in floating point and run in either floating point or quantized integer. Networks can also specifically be trained for quantization, reducing the accuracy loss. Training in integer is

very uncommon, using floating-point during training is more common even when inference uses quantization.

Using reduced format precisions data format can reduce the amount of storage and memory bandwidth needed. Reducing the precisions can also result in significantly faster compute times. However, this requires ALU units and instructions capable of running reduced precisions operations efficiently.

Modern architectures provide support for both integer and floating point operations. But won't necessarily support the reduced precisions effectively as a custom architecture. For instance, quantized inference for matrix multiplication might want to support 8-bit inputs and weights with the result of the multiplication stored at 16 bits. Further accumulation can be supported with 16, 24, or 32-bits. Integer ALUs occupy significantly less area and are faster than floating point ALUs. However, designing an architecture that only uses integer ALUs results in some accuracy loss which can limit the networks and applications. Additionally, it prevents using the custom architecture for training.

A challenging aspect of accelerating DNNs is optimizing for data reuse. Given an input and weight matrix of [n x k] and [k x m] respectively, the reuse factor, or the number of times a weight element is accessed is n. If the value of n is 1, the input is a vector instead of a matrix. It is common for RNNs, MLPs, and fully connected layers in CNNs to have an input vector instead of an input matrix. In the case of RNNs, the input sequence is a matrix of inputs that are separated into vectors by time. Because of a temporal dependency, these vectors cannot be combined into a matrix for greater reuse. However, multiple independent inputs can be combined into a batch. Batching of inputs allows the input vectors to be combined into a matrix, as well as input matrices concatenated together. Batching is done to increase the reuse of the weights. Batching inputs can have huge gains for throughput as it amortizes costly weight loading, but comes at a direct cost to latency. Inputs will have to wait for the other inputs in the batch to finish before the next layer can start executing resulting in increased latency. Additionally, batching also requires that there are available inputs to be batched at the time of inference. Each input will further increase the amount

of on-chip memory needed as each input will create its own intermediates that need to be stored.

In addition to weight reuse, the networks also have reuse with the inputs. With an input and weight matrix of [n x k] and [k x m], each input matrix or vector is applied to each of the m rows of the weight matrix. If the m rows of the weight matrix are separated across multiple compute units, the input would have to be either replicated or passed from one compute unit to another.

Finally, products reuse exists during the accumulation of the matrix multiplication. The output of each MAC is a product that needs to be accumulated with other MACs from the same column in the weight matrix. The product can be reused in the compute unit if a new input and weight are loaded in. The products can also be passed to other compute units where they will be accumulated with another product in its column. Or, the products can all be collected and accumulated outside the matrix compute units.

There are multiple approaches to designing an architecture for accelerating DNNs. One approach is using many parallel compute units for single instruction multiple data (SIMD) processing. The computation is parallelized across the compute units with all compute units acting in lockstep. The outputs from these units would have to be collected and accumulated together. In chapter 4 we present *Neural Cache* which uses a SIMD approach.

Another approach involves using a dataflow architecture such as a systolic array. With a systolic array, one of the 3 operands is kept stationary, with the other two passed to neighboring PE units. This style of architecture is explored in chapter 5 where we present *Eidetic* which uses a dataflow architecture.

### **CHAPTER 3**

### **Prior Works**

In this chapter, we will cover both industry and academic work for designing DNN accelerators. Additionally, we will discuss the prior work on in-memory computing that has led to in-SRAM computing as well as other in-memory DNN accelerators.

### 3.1 DNN Accelerators

Many industry giants, promising startups, and academic researchers have proposed their own architecture for DNN/ML acceleration. A common approach is to have a small number of cores per chip, with each core having a large or several large matrix compute units. These architectures are often dataflow architectures, with emphasis on data movement between PEs, with a systolic array being a very common option. Another option for ML accelerator architecture is a many-cores solution. GPU for instance is a specific type of many-core architecture. A many-core architecture can improve the granularity compared to a dense matrix multiplication unit. The mapping of operations is not as rigid as these large matrix multiplications units and will have a smaller array of compute units. This can improve efficiency for mapping and leveraging sparsity. A core can be turned off or mapped with other operations. Utilizing unoccupied PEs in a large dense compute array is a harder task. Additionally, each core can have more control over how data is passed and shared. This finer granularity comes at a cost in efficiency. Each core will have added overhead with its control logic. Simple data movement from PE to PE is less expensive in the area, energy, and time compared to moving data from one core to another. Often times the dataflow architecture

Figure 3.1: Google TPU with its 2D Systolic Array

will have a few complex instructions for the matrix operations. These instructions and the matrices will need to be broken up into many parallel instructions increasing the instruction overhead and the amount of software support needed for a many-core architecture. The work in *Eidetic* supports many large matrix multiplication units due to the density of in-SRAM computing. The 54 systolic arrays on-chip may look similar to a many-core architecture, however, the dataflow and programming between the systolic arrays is more similar to the PE dataflow architecture. Instead of a many-core architecture *Eidetic* is two-level dataflow architecture, connecting PEs together to compute a layer, and systolic arrays together to compute the network.

TPUv1 [7] is a neural network accelerator that Google introduced in 2016 and published the

details of in 2017. The first version of TPU has a matrix multiplication unit that was a 256 x 256 systolic array of PEs. Figure 3.1 shows the TPU systolic array. Each PE supported both 8-bit and 16-bit integer for each input operand. An 8-bit and 16-bit operand would cause the PEs to operate at half speed. Two 16-bit operands would cause them to operate at a quarter speed. Like *Neural Cache* and *Eidetic*, TPU supports a weight stationary mapping. Weight tiles are loaded into the systolic array, inputs are propagated across the systolic array and products are passed downwards. At the bottom of each column in the systolic array is an accumulator to hold the products and accumulate them with the products from the next weight tile. An activation pipeline takes the accumulated output and performs the needed activation and passes its output to the local buffer. TPUv1 devotes a significant 24 MB and 29% of its chip area to its local unified buffer. This allows TPU to support a large batch size to increase the utilization of the systolic array. Additionally, training was not supported in this version.

TPUv2 [8] was first deployed in 2017 and no longer supported integer arithmetic. Instead, it supports its own custom Bfloat16 data format. Additionally, it supported FP32 but resulted in an 8× performance loss from Bfloat16. With a floating point data format, this TPU was able to support inference and training. TPUv2 additionally has two identical cores per chip, with each core featuring a 128 x 128 systolic array. Despite having half the matrix compute units and an improved technology node, the TPUv2 is almost twice the size of TPUv1. This can be explained by the floating point units occupying a significantly larger amount of area than their integer counterparts. TPUv3 introduced a second matrix multiplication unit per core while keeping the same systolic array structure. TPUv2 and v3 feature 32MB of on-chip SRAM.

Amazon Inferentia chips [9] is another example of industry utilizing systolic arrays as their matrix multiplication unit. Each chip consists of 4 Neuron Cores with a systolic array that supports BF16, INT8, and FP16 data types. Each chip has a large on-chip cache and a commodity DRAM.

Tesla's Full Self-Driving Chip features two Neural Processing Units, a light GPU for post-processing, and 12 Cortex-A72 cores for general-purpose processing. Each neural processing unit has a 96x96 multiply-accumulate array for performing MACs. Unlike some other accelerators,

these are not systolic arrays. Additionally, each neural processing unit has 32MB of SRAM for a total of 64 MB on-chip. The SRAM is used to store intermediates and reduce the main memory accesses.

Another prominent DNN accelerator is Project Brainwave [10] from Microsoft. Brainwave is a "soft processor" that is synthesized onto its cloud FPGAs. Like *Eidetic* brainwave seeks to process AI, specifically RNNs, in real-time. Brainwave processes a single input and pins the weights in the distributed on-chip SRAM. However, unlike *Eidetic*, Brainwave's weights are not computed on inplace, requiring the weights to be moved to the compute units for each input. Brainwave relies on RNNs having multiple elements in the input to achieve a high utilization. Additionally, Brainwave uses a block floating point format that shares 5-bit exponents across a group of numbers.

Nvidia introduced Tensor Cores [11] in its Volta GPU micro-architecture. Tensor Core performs matrix-multiply-and-accumulate on 4×4 matrix each cycle. The Tensor Core takes in half-precision input operands and performs the multiplication in half-precision but the accumulation in single precision. Each streaming multiprocessor is partitioned into four processing blocks, each with two Tensor Cores, 8 FP64 cores, 16 FP32 cores, 16 INT32 cores, and one Special Function Unit. The second generation [12] added support for Int8, Int4, and Int1. The third generation included Bfloat16, TF32, and FP64. The fourth generation adds support for FP8. The GPU architecture is designed to support many parallel threads. Each processing block has a large register file to support temporal and spatial locality. The Volta architecture contains 36MB of on-chip memory across the 80 streaming multiprocessors.

Tenstorrent Grayskull [13] architecture is another many-core example with their architecture containing 120 cores in a 12x10 grid. Each core features a small 1MB SRAM, a compute engine, and 5 scalar RISC CPUs. The compute engines are optimized for INT8 but can support FP16 and Bfloat16 as well as a custom FP8 with the same throughput of INT8. Additionally, the chip has 4 super-scalar CPUs to manage the data flow.

Grog's Think Fast TSP [14] presents another take on the many-core architecture. Each tile in the network is designed to implement a specific function. A slice is composed of 20 of these tiles

stacked vertically. All the tiles in a slice use the same instruction stream for SIMD and pipelined execution. Think Fast TSP presents results for ResNet50 with a batch size of one.

In addition to industry, many academic works have proposed various DNN accelerators. Many of these works [15, 16, 17, 18, 19, 20] focus solely on CNN acceleration. Using systolic arrays as the computing engine is also an extremely common theme [15, 21, 22]. Approximation can be used to improve the compute performance and reduce energy consumption while not significantly reducing accuracy. This is done through dynamic quantization and bit-widths [21, 23, 24] and using approximate memory [25]. Leveraging sparsity in DNNs can improve compute performance and save significant amounts of energy. Architectures and mappings to leverage sparsity have also been proposed [15, 19, 26].

Eyeriss [20] was a trend-setting DNN accelerator published and tapped out back in 2016. This accelerator focuses on CNN acceleration, processing a CNN layer-by-layer. The core computing unit employs a spatial array of 168 PEs organized as a 12 x 14 rectangle. The PEs are capable of doing 16-bit fixed-point arithmetic. The convolution is broken into multiple 2D convolutions for inference. They present a row-stationary dataflow to optimize energy efficiency for any convolutional layer. The row stationary dataflow involves passing all three operands to adjacent PEs. Filters are passed horizontally, inputs are passed diagonally, and partial products are passed vertically. *Neural Cache* also uses a layer-by-layer approach and employs a hybrid of weight stationary and output stationary reuse pattern. *Eidetic* uses a weight stationary design and does not follow a layer-by-layer approach.

Our work in *Neural Cache* and *Eidetic* leverage bit-serial computation to exploit parallelism at the level of numerical representation. Stripes [27] leverages bit-serial computation for inner product calculation to accelerate DNNs. Its execution time scales proportionally with the bit length, and thus enables a direct trade-off between precision and speed. Our work in *Neural Cache* differs from Stripe in that *Neural Cache* performs in-situ computation in the SRAM arrays, while Stripe requires arithmetic functional units and dedicated eDRAM. DaDianNao [28] is an architecture for DNNs which integrates filters into on-chip eDRAM. It relieves the limited memory

bandwidth problem by minimizing external communication and doing near-memory computation. Bitfusion [29] introduces bit-level fusion and decomposition among the PEs. The BitBricks PEs can be decomposed to support lower bit-level arithmetic for bit-level granularity for each layer.

# 3.2 Processing in Memory, In-Memory, and Near-Memory Computing

Processing-in-memory (PIM) [30, 31, 32, 33, 34] was a popular concept in the 90s that had fallen out of favor, but has seen a resurgence with in-memory and near-memory computing. These works moved the compute units *near* main memory (DRAM), thereby reducing the gap between memory and compute units. Today this method of computing is generally referred to as near-memory computing as the computation is performed outside of the actual memory units. This distinction is important because there has also been a rise in in-memory computing, where the compute units exist as part of the memory/storage units. These PIM architectures of the 90s were mainly DRAM and faced challenges integrating the logic inside the DRAM cells or even on the same die. Since then the memory wall problem has accelerated and exasperated the need to improve the memory bandwidth of the Von Neumann architecture. This increased need coupled with the newly available 3D stacked memory has led to a resurgence in moving compute closer to memory. The work presented in this dissertation is an example of in-memory computing as the computations are performed inside the SRAM arrays. This is an example of in-SRAM computing. Processing in/near memory can be done with a variety of storage/memory types. In addition to DRAM and SRAM, other memory technologies such as flash and ReRAM also exist.

Memristors/ReRAM-based architectures were some of the first in-memory computing that was proposed in this current iteration. ReRAM is an extremely dense non-volatile memory that has been looked at to replace Flash memory. ReRAM is often referred to as memristors. Memristors can be programmed with up to 32 different resistance values that remain even without access to power. Applying an input voltage to the memristor creates a resulting current that is the multipli-

cation of the programmed weight and input voltage. When two currents are joined, the resulting current is the sum of the two. This allows multiple rows of memristor cells to be activated with the results accumulated along the shared bitline. Built-in accumulation and ReRAM density make it an attractive option, however, ReRAM faces several challenges that limit ReRAM potential. ReRAM is highly susceptible to process variation. The multiply relies on a linear current-voltage curve for the resistance. Process variation can break this curve causing inaccuracies or forcing the memristor to store fewer bits per cell. Compared to volatile memories, ReRAM has a lower cell life, as well as a higher latency and energy cost to program due to a higher voltage needed. Finally, the representation is limited because negative values cannot be stored in the cells and also because of the limited range of programmed resistance and scalability of ADC and DAC logic. The area and energy overhead of an ADC increases exponentially with the resolution.

PRIME [35] presents a memristor design for accelerating MLPs and CNNs. PRIME handles the bit-precision challenge by using 8-bit weights and 6-bit inputs. The weight and inputs are further split in half across four cells. The four outputs are decoded by a smaller ADC and are pierced together with peripheral adders and shifters. ISAAC [36] is another CNNs memristor accelerator. ISAAC presents a different approach to precision. Weights are still split across the cells in a row, but the input is fed sequentially, one bit at a time. This reduces the DAC and ADC precision needed. ADC peripheral logic is needed to collect each output over the 16 cycles. This allows ISAAC to use 16-bit operands. Additionally, ISAAC creates a pipeline for the CNN layers. The density of the memristors allows it to pin multiple layers in the network and separate the layers into different tiles. The output of one tile is sent to the input of the next, creating the pipeline. ISAAC can replicate the weights of a slow layer to spare tiles to improve the compute performance. FPSA [37] is a full stack solution that proposes reconfigurable routing architecture to break the communication bottleneck. Additionally, they support a spiking schema to improve PE density and efficiency. FloatPIM [38] introduces support for floating point and supports all operations using a NOR operation. The NOR operation is performed only on single-bit operands eliminating the overhead of the costly ADC and DAC. The cycles for FP multiplication are based on the number of mantissa and exponent bits. Single-bit memristors also increase the feasibility from a manufacturing standpoint. Like the work in *Eidetic* and *Neural Cache*, floatPIM operates on only one bit of the operands per cycle. PipeLayer [39] creates a pipelined ReRam architecture for training CNNs. Training for CNNs increases the complexity of dependencies but does not include support for temporal dependencies and on-demand processing.

In-SRAM/Near-SRAM computing has been well explored in the last several years. A majority of the works listed are designed for neural network acceleration. There are many ways that these works differentiate themselves from each other. Some of the novelties in these in-SRAM computing works involve using analog/mixed sensing, using alternative in-SRAM computing methods, and modifying the SRAM bit cells and peripherals. Additionally, the cells or the hardware and software can be designed to support weight sparsity and processing can be done near-SRAM instead of in-SRAM.

Our work proposes bit-serial arithmetic in the digital domain. From our differential senseamps, we can calculate if the activated cells are all ones (AND) or all zeros (NOR). Another