# Investigation of p-type Oxide Semiconductor Thin Film Transistors for Complementary Metal Oxide Semiconductor Technologies

by

Jaesung Jo

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical and Computer Engineering) in the University of Michigan 2023

Doctoral Committee:

Associate Professor Becky Peterson, Chair Assistant Professor Elaheh Ahmadi Associate Professor Neil Dasgupta Associate Professor Emmanouil Kioupakis Jaesung Jo

jsjo@umich.edu

ORCID iD: 0000-0003-0559-017X

© Jaesung Jo 2023

To my parents.

Thank you for everything.

## Acknowledgements

First and foremost, I would like to express my deepest gratitude to my research advisor, Professor Rebecca L. (Becky) Peterson, for her invaluable advice, continuous support, and patience during my PhD study in the University of Michigan. Without her guidance and support, I might have not been on the right track during this challenging journey. In addition, her precision in research gave me a chance to learn how to perform the research logically and systematically as well as how to think critically. She was not just an amazing advisor in research but also a great mentor in life for me. I again appreciate her willingness to help students in various aspects.

I would like to extend my sincere thanks to my doctoral committee, Prof. Neil Dasgupta, Prof. Emmanouil (Manos) Kioupakis, and Prof. Elaheh Ahmadi, for their willingness to serve on my committee and for their insightful feedback on research.

I also want to thank my master's research advisor at the University of Seoul, Prof. Changhwan Shin, for encouraging me to pursue graduate school and for the support.

I would like to thank all the PetersonLab group members, both current and former. It has been a pleasure working with them and discussing with my colleagues. In addition, I would like to thank all of my friends I met in University of Michigan for their emotional support.

I acknowledge the financial support from the Intel Corporation through a PMOS Intel Strategic Research Alliance (ISRA). I thank Intel Components Research for the fruitful discussion and their comments. I also thank the Department of Electrical Engineering and Computer Science (EECS) at the University of Michigan for their financial support. I am also thankful for all the technical assistance from the staff of Department of EECS, Lurie Nanofabrication, and Department of Materials Science and Engineering. Working with them has been a great experience and have enabled me to finish this thesis.

Last but not least, I many thank my parents, Hyunwook Jo and Myungja Ahn, and my brother, Jaedeok Jo, for their unconditional support and encouragement. I always appreciate it.

# **Table of Contents**

| Dedicationii                                                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Acknowledgementsiii                                                                                                                                |

| List of Tables                                                                                                                                     |

| List of Figures ix                                                                                                                                 |

| Abstractxv                                                                                                                                         |

| Chapter 1 Introduction 1                                                                                                                           |

| 1.1 Past, current, and future of computing technology1                                                                                             |

| 1.2 Motivation for oxide-semiconductor thin film electronics                                                                                       |

| 1.3 Opportunities in p-type oxide semiconductor thin film transistors7                                                                             |

| 1.4 Thesis Objectives 11                                                                                                                           |

| 1.5 Thesis Overview                                                                                                                                |

| Chapter 2 Causes of the Difference between Hall mobility and Field Effect Mobility for p-type RF Sputtered Cu <sub>2</sub> O Thin Film Transistors |

| 2.1 Introduction                                                                                                                                   |

| 2.2 Experimental Methods 16                                                                                                                        |

| 2.3 Results and Discussion                                                                                                                         |

| 2.3.1 Material properties of RF-sputtered CuO <sub>x</sub> thin films                                                                              |

| 2.3.2 Electrical properties of RF-sputtered CuO <sub>x</sub> thin films                                                                            |

| 2.3.3 Device level issues: non-idealities in thin film transistor                                                                                  |

| 2.3.4 TCAD simulation methods and results                                                                                                          |

| 2.4 Conclusion                                                                                                                                     |

| Chapter 3 Experimental and theoretical study of hole scattering in RF sputtered p-type Cu <sub>2</sub> O thin films |

|---------------------------------------------------------------------------------------------------------------------|

| 3.1 Introduction                                                                                                    |

| 3.2 Experimental Methods                                                                                            |

| 3.3 Results and Discussion                                                                                          |

| 3.3.1 Temperature-dependent Hall measurements                                                                       |

| 3.3.2 Thin film level issues: hole scattering mechanisms                                                            |

| 3.3.3 Theoretically-estimated hole mobility                                                                         |

| 3.4 Conclusion                                                                                                      |

| Chapter 4 Process Temperature Effect on p-type RF Sputtered Cu <sub>2</sub> O Thin Film Transistors 54              |

| 4.1 Introduction                                                                                                    |

| 4.2 Experimental Methods 55                                                                                         |

| 4.3 Results and Discussions                                                                                         |

| 4.3.1 Material properties as a function of process temperature                                                      |

| 4.3.2 Electrical properties as a function of process temperature                                                    |

| 4.3.3 Optical properties as a function of process temperature                                                       |

| 4.4 Conclusions                                                                                                     |

| Chapter 5 N:Cu <sub>2</sub> O S/D to reduce contact resistance of p-type Cu <sub>2</sub> O thin film transistor     |

| 5.1 Introduction                                                                                                    |

| 5.2 Experimental Methods                                                                                            |

| 5.3 Results and Discussion                                                                                          |

| 5.3.1 Development of N:Cu <sub>2</sub> O thin film                                                                  |

| 5.3.2 Cu <sub>2</sub> O thin film transistor with N:Cu <sub>2</sub> O S/D interlayer                                |

| 5.3.3 Contact resistance and transport mechanisms with N:Cu <sub>2</sub> O S/D interlayer78                         |

| 5.4 Conclusion                                                                                                      |

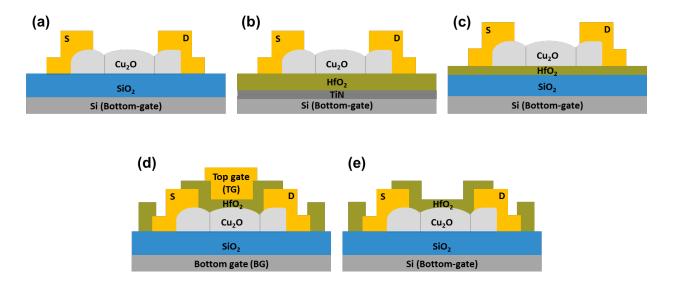

| Chapter 6 Dielectric engineering for Cu <sub>2</sub> O thin film transistor                                         |

| 6.1 Introduction                                   |

|----------------------------------------------------|

| 6.2 Experimental Methods                           |

| 6.3 Results and Discussions                        |

| 6.3.1 High-k dielectric with bottom gate structure |

| 6.3.2 High-k dielectric with top gate structure    |

| 6.3.3 Passivation                                  |

| 6.4 Conclusions                                    |

| Chapter 7 Conclusion and Future work               |

| 7.1 Conclusion                                     |

| 7.2 Future Work                                    |

| Bibliography                                       |

# List of Tables

| Table 1.1 Comparison of p-type oxides, from ref. [30], [33]    9                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 2.1 Material properties and electrical characteristics of p-type $CuO_x$ thin film transistor with different film thickness. © 2020 IEEE. Reprinted, with permission, from [71] 23                                                                                                                                                                                                                                                               |

| Table 2.2 Contact resistance measured by transmission line method (TLM). © 2020 IEEE.Reprinted, with permission, from [71]                                                                                                                                                                                                                                                                                                                             |

| Table 2.3 TCAD simulation parameters to express the sub-band gap density of state of $Cu_2O34$                                                                                                                                                                                                                                                                                                                                                         |

| Table 3.1 Calculated hole mobility as a function of phonon BZ sampling grid size, illustratingthe convergence of room-temperature hole mobility as the grid size increases. Reproduced from[95], with the permission of AIP Publishing.48                                                                                                                                                                                                              |

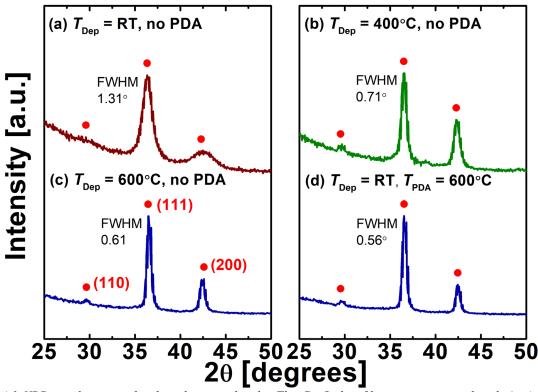

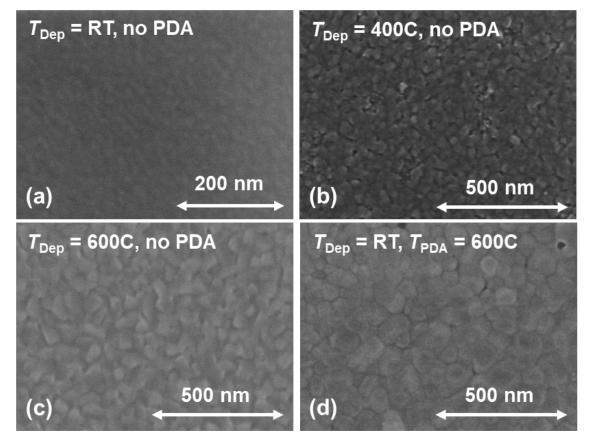

| Table 4.1 Copper oxide thin film deposition conditions described in this chapter along with the films' dominant crystal structures, as determined by XRD. Each column represents a unique set of process conditions. Here, T <sub>Dep</sub> is the deposition temperature, T <sub>PDA</sub> is the temperature of the post-deposition anneal (PDA), and PP is the deposition process pressure. RT indicates room temperature (no intentional heating.) |

| Table 5.1 Contact properties of three TFTs. The effective barrier height, $\varphi_{b,eff}$ , was obtained using the thermionic emission (TE) model                                                                                                                                                                                                                                                                                                    |

| Table 6.1 Effect of gate dielectric on Cu <sub>2</sub> O TFT performance                                                                                                                                                                                                                                                                                                                                                                               |

| Table 6.2 Electrical properties of Cu <sub>2</sub> O thin film transistors with different HfO <sub>2</sub> passivation layer thickness                                                                                                                                                                                                                                                                                                                 |

| Table 6.3 Electrical properties of Cu <sub>2</sub> O thin film transistors made with and without a 30 nm Al <sub>2</sub> O <sub>3</sub> passivation layer                                                                                                                                                                                                                                                                                              |

# List of Figures

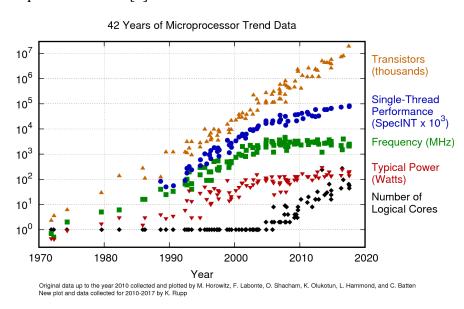

| Figure 1.1 Silicon microprocessor trend data. Adapted from [7]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

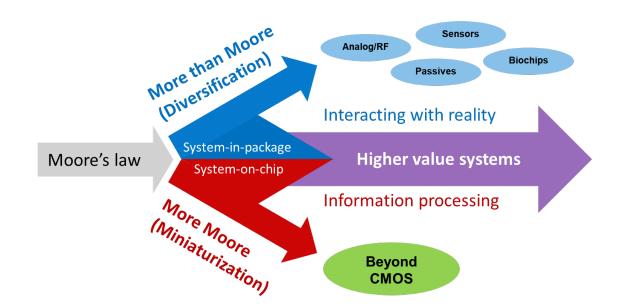

| Figure 1.2 International roadmap for devices and systems (IRDS): More Moore and More than Moore. Adapted from [10]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

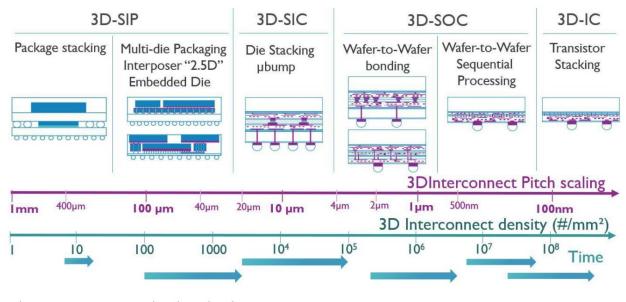

| Figure 1.3 The 3D integration technology landscape. Adapted from [16]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

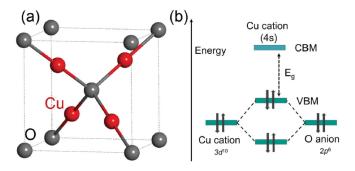

| Figure 1.4 (a) $Cu_2O$ crystal structure and (b) schematic illustration of valence band formation in $Cu_2O$ . © 2016 John Wiley & Sons, Inc. Reprinted, with permission, from [33]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

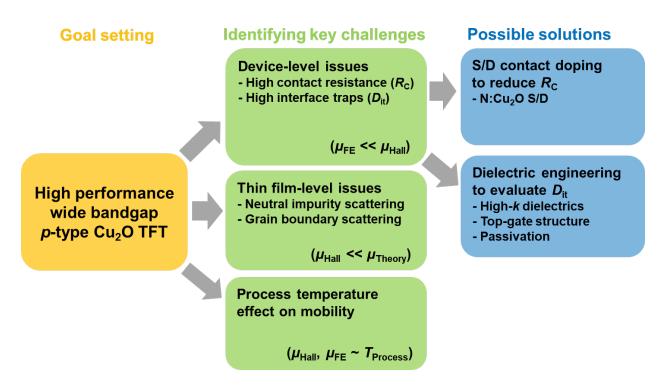

| Figure 1.5 Thesis objective and overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

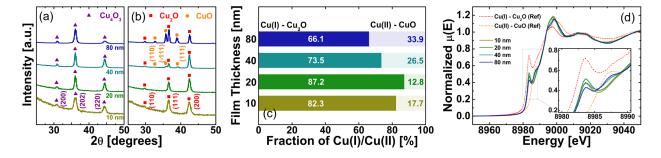

| Figure 2.1 GIXRD data for (a) as-deposited films and (b) films after post-deposition annealing (PDA), for films with different thickness: 10 nm, 20 nm, 40 nm, and 80 nm. (c) Fractions of Cu(I) and Cu(II) obtained from XANES data shown in (d), for films after PDA. The dotted lines in (d) show XANES data from Cu <sub>2</sub> O and CuO powder references with Cu(I) and Cu(II) oxidation states, respectively. © 2020 IEEE. Reprinted, with permission, from [71]                                                                                                                                                                                                                                                                   |

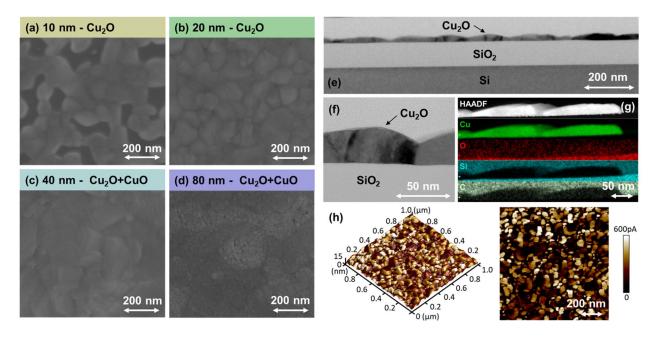

| Figure 2.2 SEM images of Cu <sub>2</sub> O films with different film thickness: (a) 10 nm, (b) 20 nm, (c) 40 nm, and (d) 80 nm films on SiO <sub>2</sub> /Si. (e), (f) TEM images of the 20 nm Cu <sub>2</sub> O film on SiO <sub>2</sub> /Si. (g) HAADF-STEM image and EDS mapping (Cu, O, Si, and C) of the 20 nm Cu <sub>2</sub> O film on SiO <sub>2</sub> /Si. (h) Surface topography (left) and vertical current (right) in a 20 nm Cu <sub>2</sub> O film deposited on Si, obtained by C-AFM. © 2020 IEEE. Reprinted, with permission, from [71]                                                                                                                                                                                     |

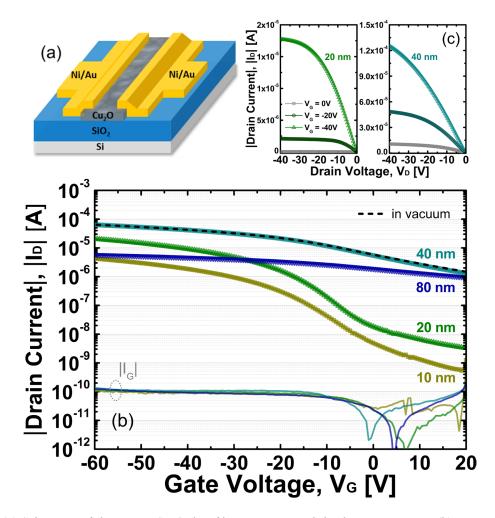

| Figure 2.3 (a) Schematic of the p-type Cu <sub>2</sub> O thin film transistor with back-gate structure. (b) Drain current, gate current versus gate voltage (I <sub>D</sub> , I <sub>G</sub> vs. V <sub>G</sub> ) with different film thickness: 10 nm, 20 nm, 40 nm, and 80 nm. The measured TFTs have W/L = $3000 \mu m/100 \mu m$ and 100 nm SiO <sub>2</sub> dielectric layer. The dashed line indicates behavior of a 40 nm thick TFT in vacuum. For this measurement, the roughing pump was run for approximately 24 hr before measurement. The drain voltage, V <sub>D</sub> , is $-10$ V for all TFTs. (c) I <sub>D</sub> vs. V <sub>D</sub> curves of the 20-nm and 40-nm TFTs. © 2020 IEEE. Reprinted, with permission, from [71] |

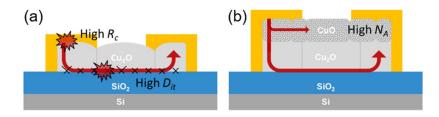

| Figure 2.4 (a) Illustration of the possible current flow paths in (a) thin (10 nm–20 nm) $CuO_x$<br>TFTs with high contact resistance and interface scattering and (b) thick (40 nm–80 nm) $CuO_x$<br>TFTs with vertically non-homogenous films. © 2020 IEEE. Reprinted, with permission, from<br>[71]25                                                                                                                                                                                                                                                                                                                                                                                                                                    |

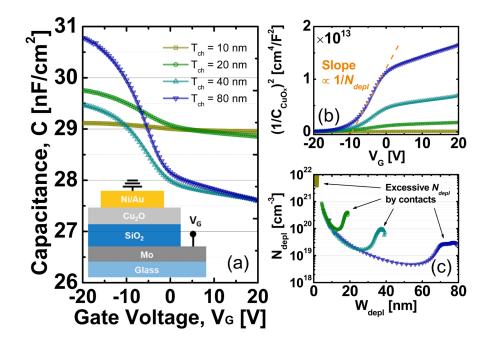

| Figure 2.5 (a) Capacitance versus gate voltage (C vs. $V_G$ ) of MOSCAPs with different CuO <sub>x</sub> film thickness: 10 nm, 20 nm, 40 nm, and 80 nm. (b) $(1/C_{CuOx})^2$ vs. $V_G$ plot. (c) Depletion carrier concentration (N <sub>depl</sub> ) vs. depletion width (W <sub>depl</sub> ) plot. © 2020 IEEE. Reprinted, with permission, from [71]                                                                                                                                                                                                                                                                                                                                                                                    |

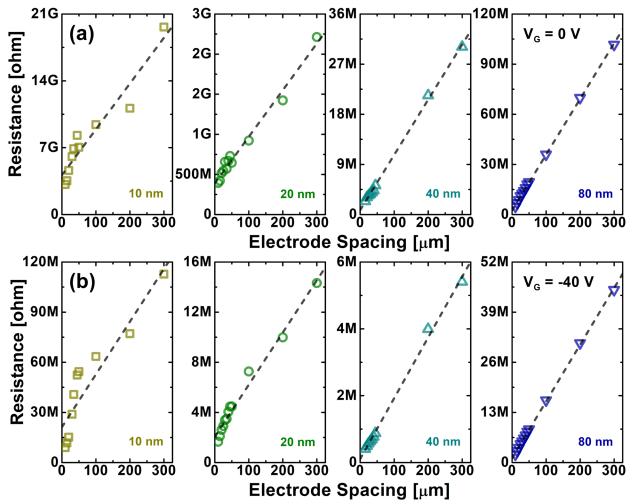

| Figure 2.6 Transmission line measurement results with different $CuO_x$ thin film thickness: 10 nm, 20 nm, 40nm, and 80 nm. Resistance versus electrode spacing plots when (a) gate voltage $(V_G) = 0 \text{ V}$ and (b) $V_G = -40 \text{ V}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

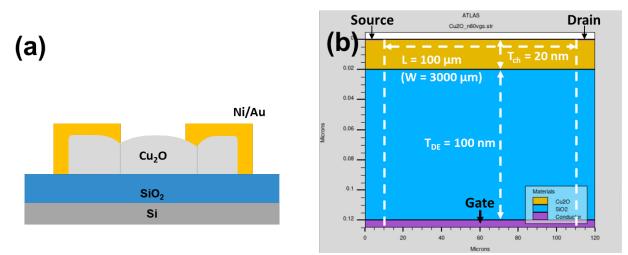

| Figure 2.7 (a) 2D schematic illustration of Cu <sub>2</sub> O thin film transistor used in experiment with back-gate structure. (b) 2D simulation structure in Silvaco ATLAS TCAD simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

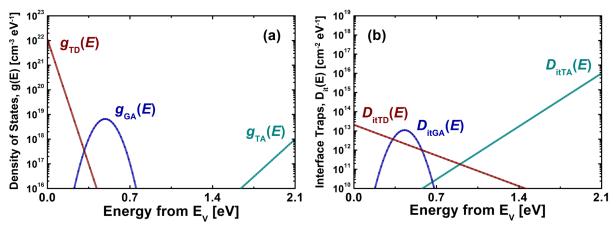

| Figure 2.8 Plots of the sub-band gap density of state profiles in Cu <sub>2</sub> O used to model: (a) bulk defect states and (b) interface trap states. For the bulk defects, $g(E)$ , the curves labelled $g_{TA}$ , $g_{GA}$ , $g_{TD}$ indicate the acceptor-like tail sates near $E_C$ , the acceptor-like Gaussian deep states, and the donor-like tail states near $E_V$ , respectively. For the interface traps, $D_{it}(E)$ , located at the channel-dielectric junction, the curves labelled $D_{itTA}$ , $D_{itGA}$ , $D_{itTD}$ refer to acceptor-like interface traps, acceptor-like Gaussian interface traps, and donor-like interface traps                                                                                       |

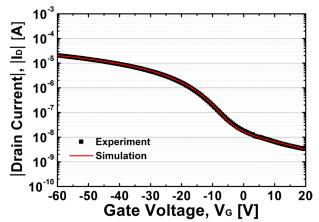

| Figure 2.9 Comparison between experimental data and TCAD simulation result for drain current versus gate voltage ( $I_D$ vs. $V_G$ ) for a Cu <sub>2</sub> O thin film transistor. The drain voltage ( $V_D$ ) value is $-10$ V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

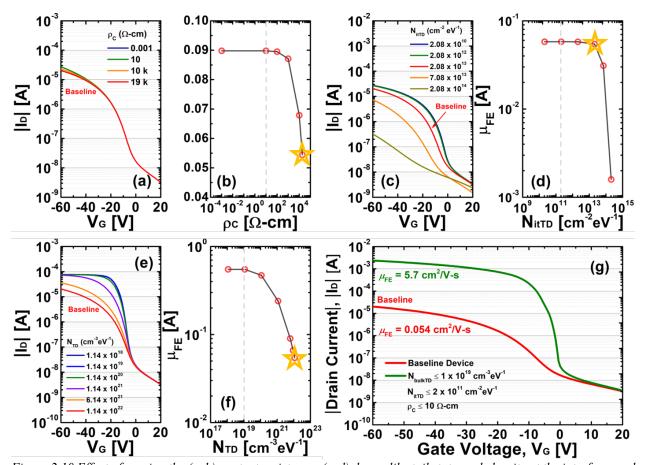

| Figure 2.10 Effect of varying the (a, b) contact resistance, (c, d) donor-like tail state peak density at the interface, and (e, f) donor-like tail state peak density in the bulk on drain current and field effect mobility. For (a, c, e), the red line indicates the baseline device. For (b, d, f), the star indicates the field effect mobility of the baseline device. (g) Comparison of simulation results for the baseline device and an optimized device with low contact resistance and low interface/bulk traps. The dashed lines in (b, d, f) indicate the maximum values of each parameter that can be present before the field effect mobility begins to decrease. For all plots, the drain voltage, $V_D$ , is $-10 \text{ V}$ . |

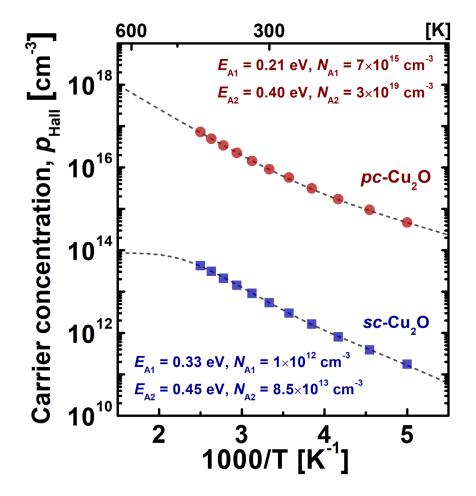

| Figure 3.1 Temperature-dependent carrier concentration ( $p_{Hall}$ vs. 1000/T) of a poly-crystalline (pc) Cu <sub>2</sub> O thin film (red circles) and a single-crystalline (sc) Cu <sub>2</sub> O bulk substrate (blue squares), which have thickness of 20 nm and 500 $\mu$ m, respectively. The dashed lines indicate fits to Eq. (1) using the parameters given in the figure. Reproduced from [95], with the permission of AIP Publishing. 40                                                                                                                                                                                                                                                                                             |

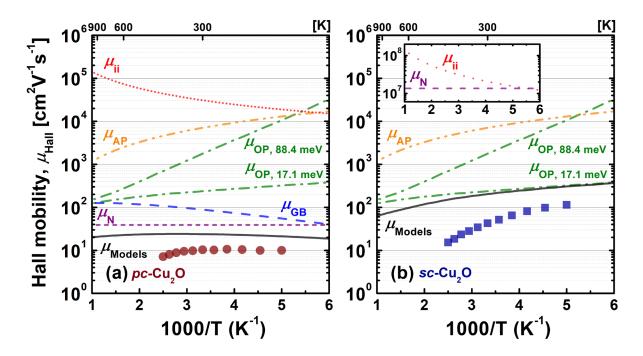

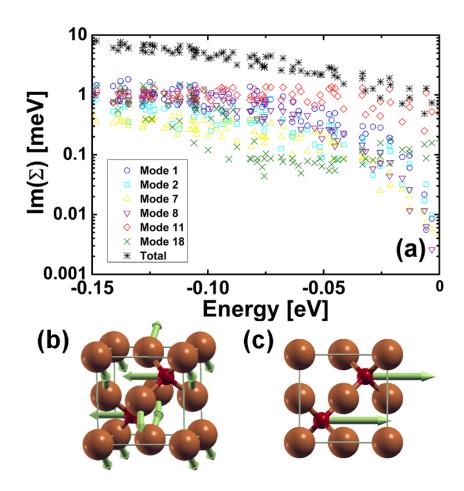

| Figure 3.2 Temperature-dependent Hall mobility ( $\mu_{Hall}$ vs. 1000/T) for (a) 20-nm thick poly-<br>crystalline (pc) Cu <sub>2</sub> O thin film (red circles) and (b) 500- $\mu$ m thick single-crystalline (sc) Cu <sub>2</sub> O<br>bulk substrate (blue squares). Symbols indicate the experimental data, while lines represent the<br>predicted mobility values due to ionized impurity scattering (ii), neutral impurity scattering (N),<br>grain boundary scattering (GB), and optical phonon (OP) and acoustical phonon (AP) scattering,<br>as well as the total predicted mobility (Models), as labelled. Reproduced from [95], with the                                                                                             |

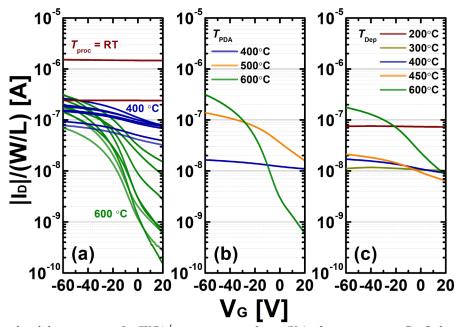

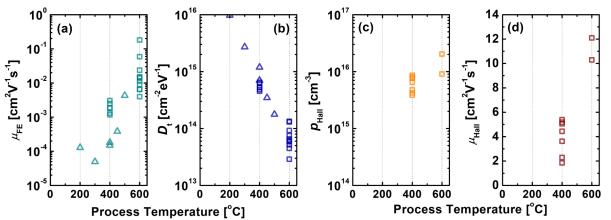

Figure 4.4 Normalized drain current,  $I_D \cdot (W/L)^{-1}$ , versus gate voltage (V<sub>G</sub>) of various p-type Cu<sub>2</sub>O thin film transistors: (a) compares films made with different processes (conditions A, C, F, and I–L from Table 4.1), where the labelled process temperature indicates the maximum of the film deposition temperature and PDA temperature; (b) compares films with different post-deposition temperature (T<sub>PDA</sub>) (conditions D–F); (c) compares films with different deposition temperature (T<sub>Dep</sub>) (conditions B and C). A drain voltage (V<sub>D</sub>) of –10 V was used for all measurements. Note that, for (a), the 400 °C Cu<sub>2</sub>O films were prepared using a Cu<sub>2</sub>O target and,

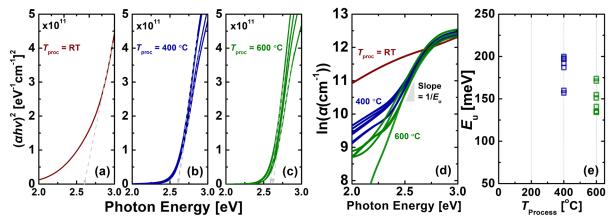

Figure 4.6 Optical properties of Cu<sub>2</sub>O thin films with different process temperatures. Here, the process temperature indicates the maximum temperature of the deposition temperature ( $T_{Dep}$ ) and post-deposition anneal temperature ( $T_{PDA}$ ). Tauc plots,  $(\alpha h \upsilon)^2$  versus photon energy, for (a) RT, (b) 400°C, and 600°C Cu<sub>2</sub>O thin films. (d) ln( $\alpha$ (cm<sup>-1</sup>)) versus photon energy plot and (e) Urbach energy for films made with different process temperatures. The film deposition conditions used for RT, 400°C, and 600°C samples correspond to columns A, I–L, and C, F, respectively, in Table 4.1.

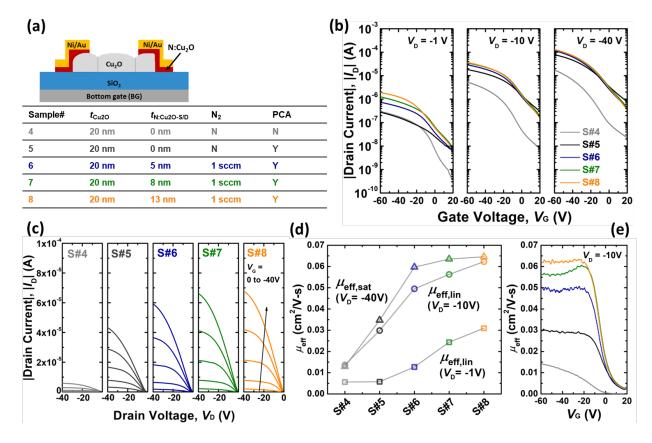

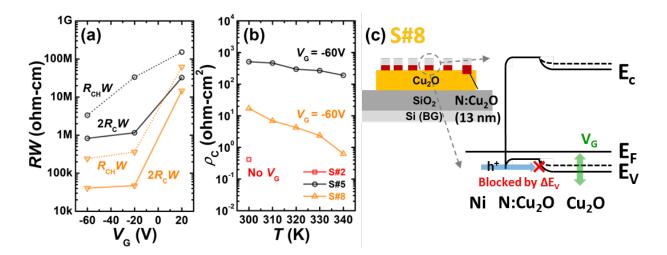

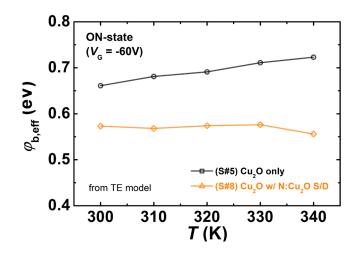

Figure 5.4 (a) Schematic of a Cu<sub>2</sub>O TFT with a N:Cu<sub>2</sub>O contact layer, coated with a probing layer of 20 nm Ni / 80 nm Au. (b) Drain current versus gate voltage (I<sub>D</sub> vs. V<sub>G</sub>) curves. (c) Drain current versus drain voltage (I<sub>D</sub> vs. V<sub>D</sub>) for different gate voltages (V<sub>G</sub> = 0 V, -10 V, -20 V, -30 V and -40 V). (d)  $\mu_{eff}$  of samples with different N:Cu<sub>2</sub>O contact layer thickness. (e) Effective mobility as a function of gate voltage ( $\mu_{eff}$  vs. V<sub>G</sub>) with V<sub>D</sub> = -10 V. The table shows key sample information: sample number, Cu<sub>2</sub>O thin film thickness (t<sub>Cu2O</sub>), N:Cu<sub>2</sub>O contact layer thickness (t<sub>N:Cu2O</sub>), N<sub>2</sub> gas flow, and post-contact anneal (PCA) condition (N=no, Y=yes). Samples S#4 and S#5 are Cu<sub>2</sub>O TFTs with no N:Cu<sub>2</sub>O contact layer. Sample S#5 was treated with PCA and S#4 was not. Samples S#6, S#7, S#8 are Cu<sub>2</sub>O TFTs with N:Cu<sub>2</sub>O contact layers of various thickness, and were all treated with PCA.

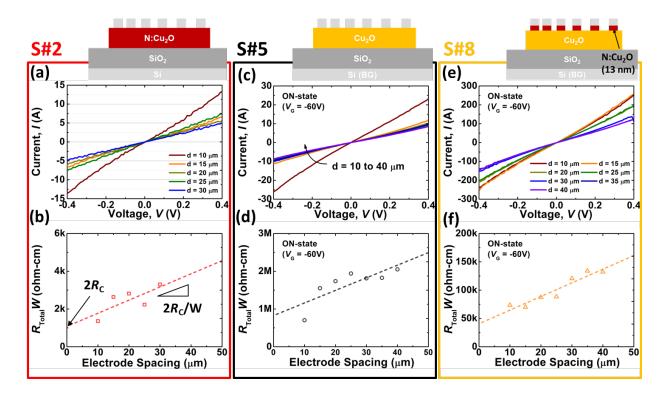

Figure 5.5 (a, c, e) Current–voltage (I–V) curves and (b, d, f) transfer length measurement (TLM) plots. TLM resistance values were extracted for the voltage region ranging from -0.2 V to +0.2 V. Sample S#2 is the room temperature N:Cu<sub>2</sub>O thin film, measured with no gate voltage

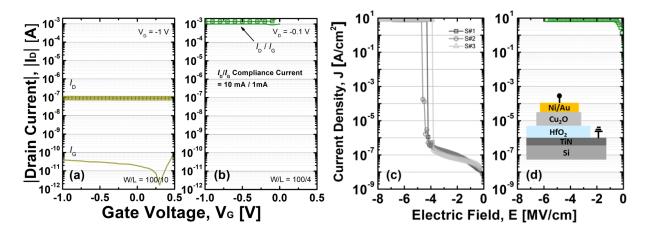

Figure 6.2 Back-gate HfO<sub>2</sub> thin film transistor  $I_D$ -V<sub>G</sub> curves for (a) as-deposited CuO<sub>x</sub> and (b) 600 °C-annealed Cu<sub>2</sub>O. The compliance current of the drain (gate) current is 10 mA (1 mA). Capacitor J-E measurements for (c) a metal-HfO<sub>2</sub>-metal (MIM) structure and (d) a metal-Cu<sub>2</sub>O-HfO<sub>2</sub>-metal (MIS) structure. For all devices, the HfO<sub>2</sub> thickness is 10 nm and the Cu<sub>2</sub>O thin film thickness is 20 nm.

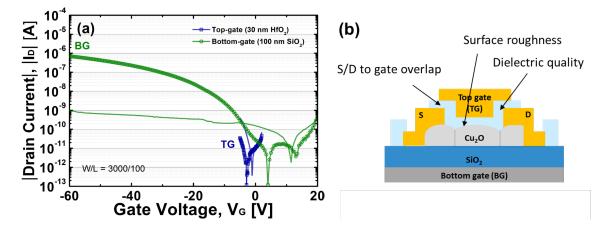

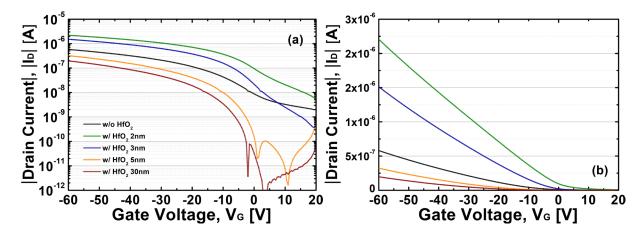

Figure 6.7 I-V curves for 600 °C-PDA Cu<sub>2</sub>O thin film transistors without a passivation layer and with different HfO<sub>2</sub> passivation layer thickness: 2 nm, 3 nm, 5 nm, and 30 nm. Drain current

| versus gate voltage (I <sub>D</sub> vs. V <sub>G</sub> ) curves are shown (a) on a semi-log scale and (b) using a linear |   |

|--------------------------------------------------------------------------------------------------------------------------|---|

| scale. The drain voltage (V <sub>D</sub> ) for all measurements is -1 V                                                  | ; |

Abstract

Today we are living through the fourth industrial revolution with new innovative technologies such as artificial intelligence, internet of things, autonomous robots, and other technologies. With the advent of these new technologies, the development of hardware needed to support them becomes ever more important. It requires not only the continuous advancement of conventional Si-based computing technology but also the flexibility to support novel technologies. To enable the continuous development of hardware technology, thin film electronics – especially, thin film transistors or TFTs – that are characterized by large area deposition, low temperature processing, as well as low complexity and cost are being actively investigated. Oxide semiconductors are a promising material for these TFT applications. Their unique properties such as wide bandgap, which leads to low leakage current, high breakdown voltage, and optical transparency, enable them to be used in new application areas. While n-type oxide semiconductors have been commercialized in display backplanes and are a quite mature technology, the absence of p-type oxide semiconductor TFTs with performance equivalent to n-type TFTs limits the further development of oxide semiconductor technology. Cuprous oxide (Cu<sub>2</sub>O) is a well-known p-type oxide with high mobility up to  $100 \text{ cm}^2 \text{V}^{-1}\text{s}^{-1}$  and wide bandgap of ~2.6 eV. Building on this context, in this thesis p-type Cu<sub>2</sub>O thin film transistors were investigated for complementary metaloxide semiconductor device technologies.

In general, TFT performance can be improved by reducing the TFT non-idealities and making the thin film itself have high mobility. Using RF-sputtered Cu<sub>2</sub>O, I first investigated device-level issues to understand what limits device performance. The Cu<sub>2</sub>O TFT performance

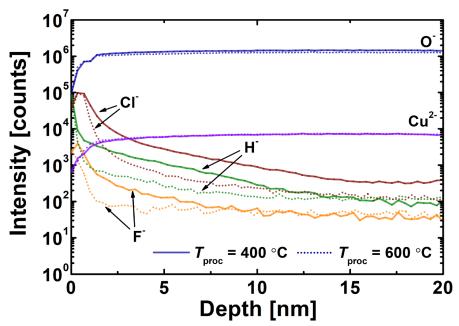

was limited by high contact resistance and high interface traps/bulk defects. Second, to increase the mobility of the Cu<sub>2</sub>O thin film itself, the hole scattering mechanisms were studied. I found that in polycrystalline Cu<sub>2</sub>O thin films, the hole mobility is mainly limited by neutral impurity and grain boundary scattering. Third, since process temperature is an important factor in determining the film's electrical properties, I studied the effect of various Cu<sub>2</sub>O thin film processes on the electrical properties, given a constrained thermal budget.

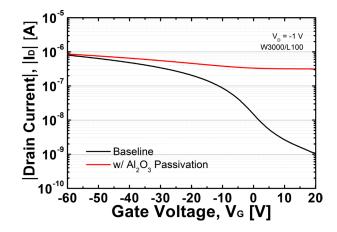

Finally, since the Hall mobility of the Cu<sub>2</sub>O thin film is already  $\sim 10 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$  while field effect mobility is  $\ll 1 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$ , I proposed methods to address the device issues identified earlier. To reduce the ohmic contact resistance to p-type Cu<sub>2</sub>O, a nitrogen-doped Cu<sub>2</sub>O source/drain interlayer was introduced. Since nitrogen is a p-type dopant in Cu<sub>2</sub>O, the addition of this layer alleviates Fermi-level pinning. In addition, dielectric engineering was performed to evaluate the interface trap density with high-*k* dielectrics, using both bottom gate and top gate TFT architectures. Furthermore, the effect of passivation of the Cu<sub>2</sub>O TFT on back-channel defects and device stability was investigated.

## **Chapter 1 Introduction**

#### 1.1 Past, current, and future of computing technology

Today we are living in the era of the fourth industrial revolution, called Industry 4.0 [1]. It is characterized by artificial intelligence (AI), internet of things (IoT), autonomous robots, augmented/virtual reality, big data, 3D printing, and other technologies. These technologies enable cyber-physical systems by blurring the boundaries between the physical and digital worlds. Different from the first, second, and third industrial revolutions, which were characterized by a certain technology such as steam power, electricity, and computers/the internet, the fourth industrial revolution is based on the achievements of the previous industrial revolutions. It is especially based on the third industrial revolution, i.e., the computer or digital revolution. The computer revolution, which started in the 1960s, was enabled by the continuous successful "miniaturization" of transistors. Today, the world is radically changing through use of varied technologies that require continuous advances in semiconductor technology. Functional diversification in hardware technology to support these innovative technologies is becoming more and more important in this era.

Computing technology using complementary metal-oxide-semiconductor (CMOS) logic has dramatically grown over many decades since the early 1960s. By adhering to the oft-quoted scaling "rule" called Moore's law, the silicon industry advanced to successfully demonstrate transistors with feature sizes below 100 nm by 2003. However, since that time, the transistor scaling mechanisms that have enabled this exponential increase in the number of transistors per

chip have started to confront difficulties, as transistor dimensions approach the few-nanometer scale. Due to these physical limits, the scaling strategy was changed from conventional geometrical scaling to equivalent scaling by introducing innovative technologies such as strain [2], high*k*/metal-gate [3], and FinFET [4]. Although today the semiconductor industry has reached sub-10 nm technology nodes [5], scaling has slowed down due to increasing process complexity and cost. Thanks to the introduction of extreme ultraviolet (EUV) lithography, semiconductor industry is anticipated to be able to carry on scaling for a few more generations. Nonetheless, it is predicted that in the near future the continued down-scaling of silicon-based transistors will be no longer possible due to quantum effects [6].

Figure 1.1 Silicon microprocessor trend data. Adapted from [7].

In addition, ever-increasing power density (Figure 1.1) is a critical issue in modern integrated circuits (ICs). As two-dimensional scaling approaches the physical limit, the incommensurate scaling of the power supply voltage ( $V_{DD}$ ) has become a critical issue. Until the early-2000s, constant field scaling [8] enabled transistors to continuously improve their switching speed, allowing microprocessors to operate at higher and higher frequencies. This led to the

improvement of IC performance by enabling an increase in the number of computing steps performed in a certain amount of time. However, MOS transistors require a certain minimum change in gate voltage to increase the source-to-channel current by a factor of 10 due to the Boltzmann distribution of electrons at source/drain [9]: the subthreshold slope of the transistor cannot be lower than 60 mV·dec<sup>-1</sup> at 300K. Due to the Boltzmann limit,  $V_{DD}$  could no longer by scaled linearly as dimensions were scaled down. This resulted in a dramatic increase in power density and associated self-heating. Constant- $V_{DD}$  scaling also made it difficult to continue increasing the operating frequency of new technology nodes. To control the power density and the corresponding heat emission, the operating frequency of CMOS has been stuck at a few GHz since the mid-2000s. This has limited the further performance improvement of the microprocessor, pushing vendors to adopt multi-core systems, instead of single core, to compensate for this frequency limitation.

Figure 1.2 International roadmap for devices and systems (IRDS): More Moore and More than Moore. Adapted from [10]

As Moore's law reaches its twilight, the semiconductor industry has adopted two forwardlooking strategies (Figure 1.2): "More Moore" and "More than Moore" [10]. The term "More Moore" focuses on continuous miniaturization with novel device architectures such as nanowire and nanosheet. Its goal is the continuous improvement of CMOS-based system-on-chip (SoC) technology. Beyond-CMOS devices and systems are also being actively explored for the future. Here, the idea is to exploit new concepts based on novel materials and physics to solve the fundamental issues described above. Such novel approaches include beyond-Boltzmann/steepslope devices (with subthreshold slope <  $60 \text{ mV} \cdot \text{dec}^{-1}$ ) such as negative capacitance FET [11] and tunnel FET [12], as well as beyond-von Neumann systems such as neuromorphic computing [13] and quantum computing [14].

The second strategy is "More than Moore", which implies the addition of non-CMOSbased technologies to CMOS-based technologies in order to achieve functional diversification [10]. Such non-digital functionalities could include RF communication, power control, passive components, and sensors. This is based on die-level integration, e.g. system-in-package (SiP), which means placing multiple dice with different functionalities in a single package. Since it is hard to encompass multiple functionalities at the wafer level, SoC and SiP technologies can be complementary to each other, while at the same time each technology can continue to evolve independently. To support this new approach, the International Technology Roadmap for Semiconductors (ITRS) [15], which has guided the semiconductor industry for many years, evolved in 2016 to become the International Roadmap for Devices and Systems (IRDS) [10] by expanding the focus from the individual device to the system. In line with Industry 4.0, the expanded approach of adding new functionalities to conventional digital devices is expected to support emerging technologies to connect the digital and physical worlds.

The 3D integration technology landscape

Figure 1.3 The 3D integration technology landscape. Adapted from [16].

Three-dimensional (3D) heterogeneous integration is the key to effectively combine nondigital devices with digital components. Diverse approaches (Figure 1.3) to combine these functionalities with digital components are being explored, ranging from package-level and waferlevel integration, to monolithic 3D integration (3D-IC) [17]. These 3D technologies have the ability to reduce interconnect resistance and parasitic capacitance to achieve high speed and low power. For 3D-SiP, package-on-package (PoP) is a common method to achieve system-level miniaturization. At the early stages in developing these 3D technologies, functional diversification was achieved by vertical package stacking using wire bonding. In addition, technologies for integrating multiple dice in a single package using an interposer, known as 2.5D integration, was also developed. As through-Si vias (TSV) and micro-bump technology become mature, 3D integration technologies are moving toward stacked-IC (3D-SIC) and 3D-SoC. In addition, waferto-wafer bonding or sequential process (i.e., transferring a BEOL semiconductor layer onto an already-patterned wafer) enables 3D integration with high interconnect density. Today 3D integration research is starting to move toward monolithic 3D integration (3D-IC). Although these technologies are still at the research stage, diverse attempts to demonstrate 3D-ICs have been made using a wafer without additional process (e.g., bonding, thinning, and TSV). Although additional restrictions (e.g., process temperature limits) exist for back-end-of-line (BEOL) processes to protect front-end-of-line devices and the metal interconnect underneath the BEOL devices, 3D-IC is anticipated to enable continuous improvement in microprocessor performance and diverse functional integration.

#### 1.2 Motivation for oxide-semiconductor thin film electronics

Thin film electronics, especially the thin film transistor (TFT), is a promising technology to support Industry 4.0 devices from IoT to wearable applications [18]. When compared to the traditional CMOS ICs, TFT technology is suitable for being fabricated on large area substrates at low cost, with low process complexity, and with low process temperature. The low thermal budget is key factor that enables flexible, foldable, and stretchable electronics by allowing the use of diverse substrates, as well as BEOL device fabrication for monolithic 3D integration. Many circuits based on thin film technology already have been demonstrated, ranging from near-field communication tags [19] and analog-to-digital converters [20], to flexible microprocessors [21]. These show the possibilities of TFT-based electronics. Today mainstream materials [22] that support TFT technology are amorphous silicon (a-Si), low-temperature polysilicon (LTPS), and amorphous oxide semiconductors, especially, amorphous indium-gallium-zinc-oxide (a-IGZO). Furthermore, novel materials such as carbon nanotubes [23] and 2D materials [24] are also being investigated for future flexible electronics.

Oxide semiconductors, that is, metal oxides, offer many advantages for thin film transistors. They can be realized using low temperature processing, can be fabricated on large area substrates, and have good mobility of  $1 - 20 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$  [22]. The conduction band of n-type oxides is formed by overlapped *s*-orbitals, which enables high electron mobility even when the film is amorphous in structure [25]. This feature makes these materials favorable for large area deposition with good uniformity. These advantages have enabled the growth of the display industry using a n-type oxide semiconductor, a-IGZO, in the display backplane [22]. Furthermore, the wide bandgap property of amorphous n-type oxides, with optical transparency, high breakdown voltage, and low leakage current have allowed researchers to explore new application areas, ranging from transparent electronics to BEOL memory/power control applications [9], [26]. However, currently oxide semiconductor technology relies on n-type unipolar devices, due to lack of high-performance p-type oxide semiconductors. The absence of p-type thin film semiconductors with performance similar to that of the n-type materials is the one of the biggest obstacles that limit the further development of thin film semiconductor technology.

# 1.3 Opportunities in p-type oxide semiconductor thin film transistors

Development of p-type oxide semiconductor TFTs [27] that perform as well their n-type counterparts could unambiguously enable a significant advance in oxide technology. It would enable oxide semiconductor technology to demonstrate more efficient and complex circuits [28], building on the long history of Si CMOS technology, as well as to find new application areas. While conduction band formation is favorable due to the overlapped *s*-orbitals, the formation of the valence band maximum (VBM) is fundamentally difficult due to the localized oxygen *p* orbital. This causes most p-type oxides to have a flat VBM with a large hole effective mass and low hole

mobility. For example, while indium oxide (In<sub>2</sub>O<sub>3</sub>), a common n-type oxide [29], has an electron effective mass of ~0.3 $m_0$ , its hole effective mass is ~38 $m_0$ . This discrepancy illustrates the challenges in realizing p-type oxides [30]. Although there have been enormous efforts to achieve p-type doping with well-known n-type oxides such as zinc oxide (ZnO) and In<sub>2</sub>O<sub>3</sub>, there has not been any significant success [30]. To achieve high mobility p-type oxides, a chemical design concept to alleviate VBM localization was proposed in 1997 [31]. The chemical design concept and following study [32] showed that using metal cations with occupied *d* or *s* states near the VBM can effectively improve hybridization with oxygen 2*p*. Using these guidelines, many researchers have worked to demonstrate p-type oxides.

Figure 1.4 (a)  $Cu_2O$  crystal structure and (b) schematic illustration of valence band formation in  $Cu_2O$ . © 2016 John Wiley & Sons, Inc. Reprinted, with permission, from [33].

Today Cu-based oxides and Sn-based oxides are the most well-known p-type oxides [27], [30], [33]. Binary copper oxide, specifically cuprous oxide (Cu<sub>2</sub>O), has been extensively explored due to its special orbital structure (Figure 1.4). Since the energy level of the copper cation with closed shell configuration (*i.e.*,  $d^{10}s^0$ ) is similar to that of the oxygen anion, it is favorable to form the valence band due to hybridization between the O 2*p* orbitals and the closed shell Cu 3 $d^{10}$ orbitals, thereby enabling a reasonably high hole mobility. In addition, to improve the optical transparency, Cu-based ternary oxides with delafossite structure, which have the form of CuMO<sub>2</sub> (where M = Al [31], Ga [34], In [35], etc.), also have been studied. Another promising p-type option is thin monoxide (SnO) with a pseudo-closed ns<sup>2</sup> orbital of the metal cation, in which the valence band maximum is formed by hybridization of the Sn 5*s* and oxygen 2*p* orbitals. The strong interaction between the cation *s* orbitals, which are spatially more extended than *d* orbitals, with oxygen 2*p* orbitals [30], [36], [37] enables SnO to have a relatively low effective hole mass. Furthermore, to achieve even stronger hybridization of VBM, there have been attempts to use chalcogens such as S, Se, and Te to replace oxygen in both Cu- and Sn-based oxides [38]–[40]. In addition, other p-type oxides [30] such as spinel oxides, Cr-based oxides, and nickel oxide (NiO) also have been studied, and there are ongoing efforts to identify promising p-type oxides using advanced computational methods [41]. Among the p-type options, Cu<sub>2</sub>O has a record high mobility of > 100 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> [42] with low effective hole mass =  $0.58m_0$  [43] (Table 1.1). Due to these excellent electrical properties, there have long been efforts to explore the use of Cu<sub>2</sub>O in high performance TFTs [33] and solar cells [44], [45].

Table 1.1 Comparison of p-type oxides, from ref. [30], [33]

| Material Properties                                                                   | Cu <sub>2</sub> O | SnO                           | NiO         |

|---------------------------------------------------------------------------------------|-------------------|-------------------------------|-------------|

| Effective mass, $m^*(m_0)$                                                            | 0.58              | 2.05                          | -           |

| Band gap, $E_{\rm g}$ (eV)                                                            | 2.1 - 2.6         | 0.7                           | 3.6 - 4.0   |

| Reported Hole mobility, $\mu_p$<br>(cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ) | Up to > 100       | Up to ~19<br>(Typically, 1–5) | Up to > ~29 |

To demonstrate high performance p-type oxide semiconductor thin film transistors, there are two strategies. One is choosing a high mobility p-type oxide. For TFT applications, transparency is not always required (*e.g.*, BEOL devices on Si MOSFET). It was observed that, although materials with the CuMO<sub>2</sub> structure can have a larger bandgap and thus better transparency, they also tend to have a larger hole effective mass and thus lower hole mobility than

$Cu_2O$  [30]. In addition, in contrast with transparent conducting oxides that require high carrier concentration to achieve low resistivity, a high carrier concentration is detrimental for TFT applications since it hinders on/off switching. Thus, I focus on materials with high hole mobility and non-degenerate carrier concentrations, over materials with wideband optical transparency. The second, complementary strategy is to address device issues to enable the TFT field effect mobility to be close as possible to the intrinsic hole mobility.

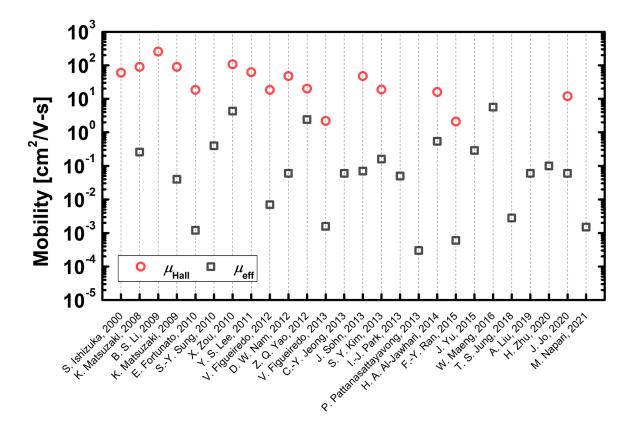

Since Cu<sub>2</sub>O exhibits a high intrinsic mobility with a hole carrier concentration of  $\sim 10^{15}$  cm<sup>-3</sup> [44], it satisfies the first condition. However, there remain several challenges to using Cu<sub>2</sub>O in p-type TFTs. First, the reported field effect mobility in TFTs is typically much lower than the Hall mobility. Second, a wide range of mobility values for p-type Cu<sub>2</sub>O thin film have been reported. In many cases, the reported mobility was lower than the theoretically-estimated mobility value. Third, the Cu<sub>2</sub>O mobility has been observed to be strongly influenced by the process temperature. Therefore, to utilize the intrinsic advantages of Cu<sub>2</sub>O, a fundamental understanding is needed of the factors limiting both the Hall mobility (which represents the maximum achievable performance) as well as the field effect mobility that can be practically achieved in TFTs.

## **1.4 Thesis Objectives**

Figure 1.5 Thesis objective and overview

The overarching objectives of this thesis (Figure 1.5) are to make advances in p-type Cu<sub>2</sub>O thin film semiconductors and identify the key challenges that limit TFT performance, in order to ultimately achieve high performance p-type TFTs. The p-type Cu<sub>2</sub>O layers are fabricated using RF magnetron sputtering. First, I investigate device-level methods to reduce the mobility gap between field effect mobility ( $\mu_{FE}$ ) and Hall mobility ( $\mu_{Hall}$ ). To address this, I focus on comprehensive studies of contact resistance and interface traps in Cu<sub>2</sub>O thin film transistors. Second, I seek to understand why the measured Hall mobility is less than the theoretically-predicted hole mobility. I perform temperature-dependent Hall measurements to investigate and compare hole scattering mechanisms in Cu<sub>2</sub>O thin film and bulk substrates, and compare the results with first-principles theory performed by a collaborator. Third, I explore the effect of process temperature on  $\mu_{FE}$  and

$\mu_{\text{Hall}}$ . Cu<sub>2</sub>O TFTs with various process temperatures and conditions were investigated to correlate the thermal budgets and electrical properties.

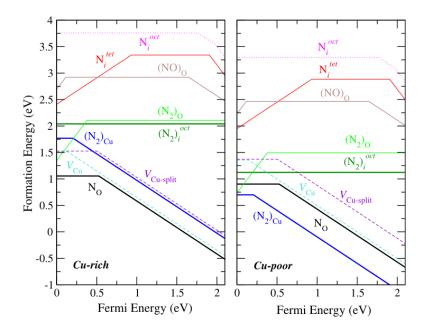

Based on these studies, I identify several possible solutions to improve Cu<sub>2</sub>O TFT performance. My analysis shows that device-level problems are the most critical since the  $\mu_{\text{Hall}}$  of my thin films is already  $\geq 10 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$ . To reduce the high contact resistance and reduce the number of interface traps in my p-type Cu<sub>2</sub>O TFTs, I pursue two novel approaches: (1) the insertion of a nitrogen-doped Cu<sub>2</sub>O between the source/drain metal and the Cu<sub>2</sub>O semiconductor to reduce contact resistance, since my collaborator has predicted that nitrogen-doping can increase the hole concentration in Cu<sub>2</sub>O; and (2) the modification of the dielectric/semiconductor interface at both the front and back channel to address interface trap issues.

## 1.5 Thesis Overview

In Chapter 2, I demonstrate deposition of p-type Cu<sub>2</sub>O thin films using RF magnetron sputtering. Thin film properties were investigated using diverse techniques such as electron beam and X-ray diffraction. P-type Cu<sub>2</sub>O thin film transistors were fabricated. Then, to understand the mobility gap between the field effect mobility and Hall mobility of Cu<sub>2</sub>O, device characterization was performed to analyze the impact of contact resistance and interface traps on TFT performance. In Chapter 3, I investigate hole scattering mechanisms by performing temperature-dependent Hall measurements on my RF-sputtered polycrystalline Cu<sub>2</sub>O thin film and compare with a naturally-formed single crystalline bulk Cu<sub>2</sub>O substrate. To understand why the Hall mobility is lower than the theoretically-predicted value, my measured hole mobility in Cu<sub>2</sub>O was compared to analytical models of phonon, grain boundary, ionized impurity, and neutral impurity scattering, and compared to the results to first-principles theory performed by my collaborator. In Chapter 4, I

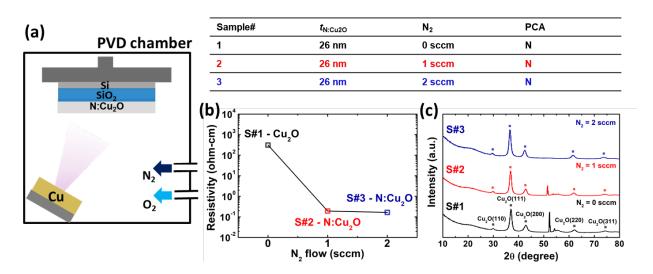

explore the effects of process temperature on Cu<sub>2</sub>O thin films and their TFT performance. The required thermal budgets are different for the diverse applications. Since the process temperature is a critical factor that determines TFT performance, the material, electrical, and optical properties were investigated for Cu<sub>2</sub>O thin films processed at room temperature, 400°C, and 600°C. In Chapter 5, building on my collaborator's prediction of degenerate doping of Cu<sub>2</sub>O using nitrogen, I develop a deposition process for nitrogen-doped Cu<sub>2</sub>O (N:Cu<sub>2</sub>O) and characterize the films. By using a heavily-doped N:Cu<sub>2</sub>O S/D interlayer, I reduce the contact resistance of my p-type Cu<sub>2</sub>O thin film transistors. In Chapter 6, I explore high-*k* dielectric to alleviate the high trap density at the dielectric-to-channel interface of Cu<sub>2</sub>O TFTs. A HfO<sub>2</sub> dielectric layer was tested as a gate dielectric in both the bottom-gate and top-gate TFT structures. In addition, a high-*k* passivation layer was introduced to the Cu<sub>2</sub>O TFT to understand its effect on back-channel defects. The thesis concludes with Chapter 7, which summarizes the contributions to date and recommends future research directions.

# Chapter 2 Causes of the Difference between Hall mobility and Field Effect Mobility for p-type RF Sputtered Cu<sub>2</sub>O Thin Film Transistors

# **2.1 Introduction**

With the successful development of n-type oxide semiconductor thin film transistors (TFTs), many researchers are extensively exploring their counterpart, p-type TFTs, for complementary metal oxide semiconductor (CMOS)-based applications [27], [33], [46]. CMOS integrated circuits (ICs) have many advantages over unipolar (i.e., n-type only) circuits. Their merits include lower power consumption and heat dissipation, reduced circuit complexity, as well as increased immunity to noise [47]. In addition, the development of p-type oxide semiconductors will enable oxide semiconductor technology for new applications beyond commercial display backplanes [48], such as flexible/foldable electronics and back-end-of-line devices on Si-based ICs [49], [9], [50]–[52], [42], [53]–[61].

Cuprous oxide (Cu<sub>2</sub>O) has p-type properties that originate primarily from Cu simple vacancies acting as acceptors [62]–[64], and its Cu 3*d* orbital can favorably form a delocalized valence band maximum with the O 2*p* orbital because they have comparable energy levels [31], [33]. Furthermore, the abundant availability, low price, non-toxic nature, and direct band gap (2.1 – 2.6 eV [33], [65], [66]) of Cu<sub>2</sub>O are desirable. With these advantages, Cu<sub>2</sub>O has been explored using diverse deposition methods [33]. In particular, dc/RF magnetron sputtering is considered to be one of the most promising thin-film deposition methods, since its cost-effective process and its capability for large area deposition make it suitable for manufacturing.

Previous studies have confirmed the p-type properties and TFT performance of Cu<sub>2</sub>O deposited by sputtering [54]–[57], [67]. It has been observed that there is a huge difference between a film's Hall mobility ( $\mu_{\text{Hall}}$ ) and the field effect mobility ( $\mu_{\text{FE}}$ ) achieved within a TFT. For example, while  $\mu_{\text{Hall}}$  values ranged from 16 to 256 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> for poly-crystalline films [54]–[56], [68]–[70],  $\mu_{\text{FE}}$  values ranged from 0.0023 to 0.54 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> [54]–[56], [67] for poly-crystalline films and  $\mu_{\text{FE}} = 2.4 \text{ cm}^2 \text{V}^{-1}\text{s}^{-1}$  for nano-crystalline film [57]—much lower than the values of  $\mu_{\text{Hall}}$ . Films deposited by other methods, such as pulsed laser deposition and atomic layer deposition [33], [42], [58], have reported  $\mu_{\text{FE}} > 1 \text{ cm}^2 \text{V}^{-1}\text{s}^{-1}$ . However, the  $\mu_{\text{FE}}$  values are still much lower than the reported  $\mu_{\text{Hall}}$  values. To address this fundamental knowledge gap, I performed a comprehensive study to determine the factors that limit the  $\mu_{\text{FE}}$  values achieved in p-type Cu<sub>2</sub>O TFTs.

In this chapter, using copper oxide films of different thicknesses, I correlate the CuO<sub>x</sub> material properties with electrical characteristics. With electrical measurements, I analyzed the factors that can cause a gap between  $\mu_{\text{Hall}}$  and  $\mu_{\text{FE}}$  in Cu<sub>2</sub>O TFTs. I determined that the dominant limiting factors in the TFTs are dielectric-semiconductor interface traps ( $D_{\text{it}}$ ) and contact resistance ( $R_{\text{C}}$ ), both of which can be improved in the future to achieve high-performance p-type Cu<sub>2</sub>O TFTs. Note that I have published the results described in this chapter (except for section 2.3.4) in reference [71].

## **2.2 Experimental Methods**

To fabricate p-type copper oxide (CuO<sub>x</sub>) TFTs with different film thicknesses, a 100-nm SiO<sub>2</sub> layer was thermally grown on a heavily-doped Si wafer in a furnace. Then, using RF magnetron sputtering (RFMS), CuO<sub>x</sub> was deposited on top of the SiO<sub>2</sub>/Si. For the RFMS process, a 3-inch Cu (99.99%) metal target was used in a Kurt J. Lesker PRO Line PVD 75 with a targetto-substrate distance of  $\sim 16$  cm. The deposition conditions were as follows: RF power of 300 W, process pressure of  $5 \times 10^{-3}$  Torr, O<sub>2</sub>:Ar ratio of 0.2 (O<sub>2</sub> = 5.35 sccm and Ar = 26.75 sccm), and deposition at room temperature with deposition times of 20 s, 39 s, 79 s, and 158 s. Following thin film deposition, a post-deposition anneal (PDA) was performed at 600 °C in vacuum (~ $1 \times 10^{-5}$ Torr) for 10 mins. After PDA, ellipsometry measurements showed that the film thicknesses were approximately 10 nm, 20 nm, 40 nm, and 80 nm. To form active layer islands, the CuO<sub>x</sub> films were patterned via photolithography and wet etching. Before contact formation, an O<sub>2</sub> plasma descum process was performed. To form source/drain contacts, 20 nm Ni followed by 80 nm Au were deposited and patterned using an e-beam evaporator and photolithography. In addition to TFTs, sheet resistance  $(R_{sh})$  patterns (cloverleaf shape) were made for van der Pauw (vdP) measurement and transmission line method (TLM) test structures were included to extract contact resistance [72]. These test structures were fabricated at the same time as the TFTs, on the same samples. For Hall measurements, a separate sample was fabricated using the same process on a glass substrate, using the *vdP* configuration (cloverleaf pattern).

Metal-oxide-semiconductor capacitors (MOSCAPs) were also fabricated with the  $CuO_x$  films. First, 100 nm Mo was deposited on glass wafers by RFMS. Next, a 120-nm SiO<sub>2</sub> layer was deposited by plasma-enhanced chemical vapor deposition at 200 °C, followed by rapid thermal

annealing at 520 °C for 3 min to densify the  $SiO_2$ . Then,  $CuO_x$  film deposition and Ni/Au contact formation were performed using the processes described above.

Material properties of the CuO<sub>x</sub> films were investigated by grazing incidence X-Ray diffraction (GIXRD), X-ray absorption near-edge structure (XANES) analysis, scanning electron microscopy (SEM), transmission electron microscopy (TEM), high-angle annular dark-field scanning transmission electron microscopy (HAADF-STEM), energy dispersive X-ray spectroscopy (EDS), and conductive atomic force microscopy (C-AFM).<sup>1</sup> For the XANES analysis, Cu(I) and Cu(II) fractions were obtained from X-ray absorption spectroscopy (XAS) at the copper K-edge. The spectra were fit by linear combination fitting method (R-factor < 0.0007 and Chi-squared < 0.022) using the XAS Athena software [73].<sup>2</sup> For electrical measurements, an HP4156A semiconductor parameter analyzer, an HP4284A LCR meter, and an Accent HL5500PC Hall measurement system were used in air, at room temperature, in the dark.

<sup>&</sup>lt;sup>1</sup> C-AFM was performed by EAG Labs, and Dr. Adedapo A. Oni at Intel (the sponsor of this work) performed transmission electron microscopy (TEM) and energy dispersive X-ray spectroscopy (EDS).

<sup>&</sup>lt;sup>2</sup> The XANES data and analysis were performed by my collaborator, Julia D. Lenef, a doctoral student at UM in Materials Science and Engineering working with Prof. Neil Dasgupta. The XANES data was taken at the Advanced Photon Source, a U.S. Department of Energy (DOE) facility using beamline 20-ID-B, C at Argonne National Laboratory, proposal ID 66474. We thank Dr. David Mandia at ANL for his assistance with XANES.

## 2.3 Results and Discussion

#### 2.3.1 Material properties of RF-sputtered CuO<sub>x</sub> thin films

Figure 2.1 GIXRD data for (a) as-deposited films and (b) films after post-deposition annealing (PDA), for films with different thickness: 10 nm, 20 nm, 40 nm, and 80 nm. (c) Fractions of Cu(I) and Cu(II) obtained from XANES data shown in (d), for films after PDA. The dotted lines in (d) show XANES data from Cu<sub>2</sub>O and CuO powder references with Cu(I) and Cu(II) oxidation states, respectively. © 2020 IEEE. Reprinted, with permission, from [71].

The film phase and composition of the post-annealed  $CuO_x$  films with different thicknesses (*i.e.*, 10 nm, 20 nm, 40 nm, and 80 nm) were analyzed using GIXRD and XANES. As shown in Figure 2.1, different thickness films showed different  $CuO_x$  phase after PDA at 600 °C in vacuum. As-deposited films all showed  $Cu_4O_3$  phase, regardless of thickness (Figure 2.1(a)). After PDA, the phase transformed to  $Cu_2O$  (10 and 20 nm films) or a  $Cu_2O + CuO$  mixed phase (40 and 80 nm films) (Figure 2.1(b)). Specifically, GIXRD of the 40 nm film showed  $Cu_2O$  peaks with minor CuO peaks while the 80 nm film showed  $Cu_2O + CuO$  mixed phase peaks.

The Cu(I)/Cu(II) fraction of each film was also quantitatively evaluated (Figure 2.1(c)) by linear combination fitting within the XANES region (Figure 2.1(d)). The 20 nm film showed the highest Cu(I) fraction of 87.2%. As the film thickness increased to 80 nm, the Cu(I) fraction decreased from 87.2% to 66.1%, while the Cu(II) fraction increased from 12.8% to 33.9%. These trends are well matched with the GIXRD results. The difference in phase after PDA is likely due to the following reactions, as explained in a study on the copper oxide phase [74]: oxygen reduction,

i.e.,  $2 \operatorname{Cu}_4\operatorname{O}_3 \rightarrow 4 \operatorname{Cu}_2\operatorname{O} + \operatorname{O}_2$ , and oxidation, i.e.,  $2 \operatorname{Cu}_4\operatorname{O}_3 + \operatorname{O}_2 \rightarrow 8 \operatorname{CuO}$ . For thinner films (10–20 nm), during vacuum annealing, the O<sub>2</sub> released by Cu<sub>4</sub>O<sub>3</sub> reduction may be able to entirely escape from the film, allowing a nearly complete reduction to the Cu<sub>2</sub>O phase. On the other hand, for thicker films (40–80 nm), O<sub>2</sub> may not be able to fully escape from the thick layer, causing oxidation of some of the Cu<sub>4</sub>O<sub>3</sub> to CuO. These competing oxidation and reduction processes, combined with O<sub>2</sub> diffusion, may lead to the observed Cu<sub>2</sub>O + CuO mixed phase.

Figure 2.2 SEM images of  $Cu_2O$  films with different film thickness: (a) 10 nm, (b) 20 nm, (c) 40 nm, and (d) 80 nm films on SiO<sub>2</sub>/Si. (e), (f) TEM images of the 20 nm  $Cu_2O$  film on SiO<sub>2</sub>/Si. (g) HAADF-STEM image and EDS mapping (Cu, O, Si, and C) of the 20 nm  $Cu_2O$  film on SiO<sub>2</sub>/Si. (h) Surface topography (left) and vertical current (right) in a 20 nm  $Cu_2O$  film deposited on Si, obtained by C-AFM. © 2020 IEEE. Reprinted, with permission, from [71].

The morphology of the different thickness films was investigated via SEM shown in Figure 2.2(a-d). The 10 nm film has a discontinuous surface. Dense surface morphology was observed for the 20 nm film. The 40 nm and 80 nm films had different surface morphologies, likely due to the formation of the CuO phase, as shown in the GIXRD and XANES results. Figure 2.2(e-f) present TEM images of the 20 nm Cu<sub>2</sub>O film. The film has a coalesced island-like morphology, with some variation observed in grain size and thickness. For this Cu<sub>2</sub>O film, it appears that

individual grains are vertically homogenous (Figure 2.2(f)). Based on the HAADF-STEM image and EDS mapping results (Figure 2.2(g)), there was no apparent segregation of Cu metal, carbon, or silicates that might limit or interrupt hole transport within the grains or at the grain boundaries/surface.

Figure 2.2(h) shows C-AFM scans for the 20 nm Cu<sub>2</sub>O film. The film has a root mean square surface roughness of 3.23 nm. From the C-AFM measurement of vertical current, I observe that the Cu<sub>2</sub>O grains are more conductive than the grain boundaries. The insulating nature of the grain boundaries may limit hole current flow due to grain boundary scattering and/or formation of electrical potential barriers at the grain boundaries, as has been found in other polycrystalline films [75], [76].

#### 2.3.2 Electrical properties of RF-sputtered CuO<sub>x</sub> thin films

The sheet resistance ( $R_{sh}$ ) of each film was measured using van der Pauw (vdP) method. The measured  $R_{sh}$  values varied with film thickness, as shown in Table I. For thin films (10 nm – 20 nm),  $R_{sh}$  decreased from  $8.5 \times 10^{10} \Omega/\Box$  to  $3.2 \times 10^9 \Omega/\Box$  as the film thickness increased. Since both films have the same Cu<sub>2</sub>O phase, and the decrease in  $R_{sh}$  is much greater (1/27×) than that predicted solely by the change in film thickness (1/2×), I postulate that the high  $R_{sh}$  of the 10 nm film is likely caused by the discontinuous film morphology. As the film thickness increased from 20 nm to 40 nm, a further significant reduction in  $R_{sh}$  (1/38×) was observed as the Cu(II) fraction increased from 12.8% to 26.5%.

It has been previously shown for sputtered, unintentionally doped CuO<sub>x</sub> films that Cu<sub>2</sub>O<sub>1±δ</sub> films have hole carrier concentrations (*p*) of ~10<sup>15</sup>–10<sup>17</sup> cm<sup>-3</sup> while CuO<sub>1±δ</sub> films have significantly greater hole concentrations of  $p \sim 10^{17}$ –10<sup>21</sup> cm<sup>-3</sup> [44]. Thus, the increase in CuO content in the

40-nm film compared to the 20 nm film may lead to a dramatic reduction in  $R_{\rm sh}$ . In addition, the larger grain size observed in SEM (Figure 2.2(c)) may also contribute to the lower  $R_{\rm sh}$  by reducing grain boundary scattering. As the film thickness increased from 40 nm to 80 nm,  $R_{\rm sh}$  increased. The CuO phase is known to have a higher hole effective mass ( $m^*$ ) than the Cu<sub>2</sub>O phase (and therefore a lower hole mobility). For Cu<sub>2</sub>O, the calculated and experimentally-obtained light hole  $m^*$  are 0.36–0.5 $m_0$  [63], [77] and 0.58 $m_0$  [43], respectively. For CuO, the reported average hole  $m^*$  is 1.87 $m_0$  [78] from theory and 7.9 $m_0$  [79] from experiments. It has also been shown that RFMS CuO films have relatively low Hall mobility of 0.05–6 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> [80], [81]. Thus, the increased CuO composition of the 80-nm film may cause an overall increase in resistivity, which is observed as an increase in  $R_{\rm sh}$ . Finally, when comparing to n-type thin film oxides such as amorphous indium-gallium-zinc-oxide (*a*-IGZO), which has an electron  $m^*$  of 0.2 $m_0$  [22], it is clear that Cu<sub>2</sub>O

Figure 2.3 (a) Schematic of the p-type  $Cu_2O$  thin film transistor with back-gate structure. (b) Drain current, gate current versus gate voltage ( $I_D$ ,  $I_G$  vs.  $V_G$ ) with different film thickness: 10 nm, 20 nm, 40 nm, and 80 nm. The measured TFTs have  $W/L = 3000 \ \mu m/100 \ \mu m$  and 100 nm SiO<sub>2</sub> dielectric layer. The dashed line indicates behavior of a 40 nm thick TFT in vacuum. For this measurement, the roughing pump was run for approximately 24 hr before measurement. The drain voltage,  $V_D$ , is  $-10 \ V$  for all TFTs. (c)  $I_D \ vs. \ V_D$  curves of the 20-nm and 40-nm TFTs. © 2020 IEEE. Reprinted, with permission, from [71].

|                                                | 10 nm                 | 20 nm                 | <b>40 nm</b>          | <b>80 nm</b><br>Cu <sub>2</sub> O+CuO |  |

|------------------------------------------------|-----------------------|-----------------------|-----------------------|---------------------------------------|--|

| Film phase                                     | Cu <sub>2</sub> O     | Cu <sub>2</sub> O     | Cu <sub>2</sub> O+CuO |                                       |  |

| Cu(I) (%)                                      | 82.3                  | 87.2                  | 73.5                  | 66.1                                  |  |

| Cu(II) (%)                                     | 17.7                  | 12.8                  | 26.5                  | 33.9                                  |  |

| $\mu_{FE} ({ m cm}^2 { m V}^{-1} { m s}^{-1})$ | 0.013                 | 0.059                 | 0.107                 | 0.005                                 |  |

| Ion/Ioff ratio                                 | ×3388                 | ×5469                 | ×49                   | ×6.1                                  |  |

| SS <sub>min</sub> (V/dec)                      | 9.29                  | 8.05                  | 29.51                 | 65.34                                 |  |

| $R_{sh}\left(\Omega/\Box\right)$<br>from $vdP$ | $8.5 \times 10^{10}$  | 3.2×10 <sup>9</sup>   | 8.3×10 <sup>7</sup>   | 1.5×10 <sup>8</sup>                   |  |

| $D_{it} ({\rm cm}^{-2}{\rm eV}^{-1})$          | 3.34×10 <sup>13</sup> | 2.89×10 <sup>13</sup> | -                     | -                                     |  |

Table 2.1 Material properties and electrical characteristics of p-type  $CuO_x$  thin film transistor with different film thickness. @ 2020 IEEE. Reprinted, with permission, from [71].

*Table 2.2 Contact resistance measured by transmission line method (TLM).* © 2020 IEEE. Reprinted, with permission, from [71].

|                                                                                                                                 | 10 nm                 | 20 nm                | <b>40 nm</b>         | 80 nm                |

|---------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------|----------------------|----------------------|

| $2R_{C}W (\Omega-cm) (@ V_{G} = 0V) (@ V_{G} = -40V)$                                                                           | 165M<br>(847k)        | 16M<br>(82k)         | 32k<br>(4k)          | 99k<br>(44k)         |

| $\rho_{c} \left( \Omega \text{-cm}^{2} \right)$                                                                                 | 354k                  | 26k                  | 6.29                 | 18                   |

| $R_{sh}\left(\Omega/\Box\right)$ from TLM                                                                                       | 1.92×10 <sup>10</sup> | 2.32×10 <sup>9</sup> | 3.97×10 <sup>7</sup> | 1.33×10 <sup>8</sup> |

| $\begin{array}{l} 2R_{C}/R_{T} \ \% \ for \ W/L \\ = 3000/100 \ \mu m/\mu m \ @ \ V_{G} = 0V \\ (@ \ V_{G} = -40V) \end{array}$ | 46.2%<br>(40.1%)      | 40.0%<br>(32.9%)     | 7.4%<br>(5.3%)       | 6.9%<br>(7.0%)       |

Thin film transistors (TFTs) were fabricated with  $CuO_x$  films of different thicknesses. The electrical test results are shown in Figure 2.3. In the TFTs, a patterned channel layer was used to minimize the impact of fringing current and gate leakage current, which can lead to overestimation of  $\mu_{FE}$  [76]. The TFTs have  $\mu_{FE}$  of 0.005 – 0.1 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, as listed in Table 2.1. The linear  $\mu_{FE}$  was calculated using the following equation:  $\mu_{\rm FE} = g_{\rm m} (C_{\rm OX} V_{\rm DS} W/L)^{-1} = (\partial I_{\rm D} / \partial V_{\rm GS}) (C_{\rm OX} V_{\rm DS} W/L)^{-1}$ where  $g_m$  is the transconductance,  $I_D$  is the drain current in linear region,  $C_{OX}$  is gate oxide capacitance per unit area, and W/L is the channel width/length ratio. Among the different devices, a maximum on/off current ( $I_{on}/I_{off}$ ) ratio of ~5 × 10<sup>3</sup> and a  $\mu_{FE}$  mobility of 0.059 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> were observed for the 20 nm Cu<sub>2</sub>O TFT, which also has the highest Cu(I) fraction. Across devices tested on five different samples, the field-effect mobility for 20-nm Cu<sub>2</sub>O TFTs varied between 0.032 and 0.059 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, indicating the good repeatability and consistency of my results. As discussed above, since Cu<sub>2</sub>O has more attractive p-type properties, a higher Cu(I) fraction should correlate with better TFT performance, as observed here. While thin Cu<sub>2</sub>O films (10–20 nm) showed  $I_{on}/I_{off}$ ratios higher than those of thicker films, a large off-current was still observed. The relatively large off current may be due to minority carrier accumulation [53] and/or minority carrier injection from S/D to channel enabled by Fermi level pinning [59]. Although the phase of both the 10 nm and 20 nm films is Cu<sub>2</sub>O, the 40 nm TFT has the highest on-current, possibly due to the more dense and continuous film, as observed in SEM (Figure 2.2(c)). The 40 nm TFT also has the highest  $\mu_{FE}$  of  $0.1 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$ , which may originate from the larger grain size and/or decrease of contact resistance (see Table 2.2). In the case of the 80 nm film with an increased CuO composition, the TFT has lower  $\mu_{\rm FE}$  and  $I_{\rm on}$ . The high off-current level for these thick films may be due to current flowing through an additional, parallel conduction path.

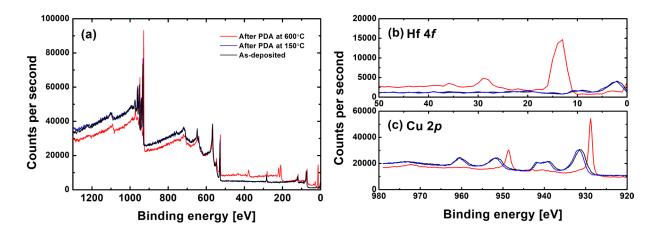

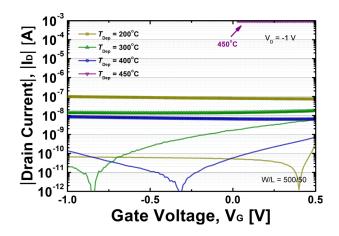

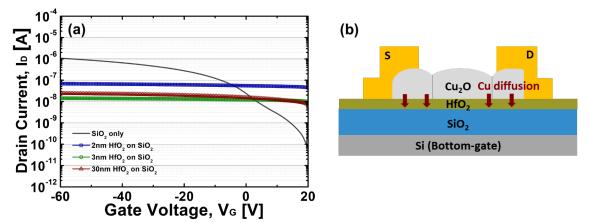

Figure 2.4 (a) Illustration of the possible current flow paths in (a) thin (10 nm–20 nm)  $CuO_x$  TFTs with high contact resistance and interface scattering and (b) thick (40 nm–80 nm)  $CuO_x$  TFTs with vertically non-homogenous films. © 2020 IEEE. Reprinted, with permission, from [71].