# **Cross-Coupled Noise Propagation in VLSI Designs**

# VLADIMIR ZOLOTOV,1 DAVID BLAAUW,2 RAJENDRAN PANDA1 AND CHANHEE OH1

<sup>1</sup>Motorola Inc. Austin, TX <sup>2</sup>University of Michigan, Ann Arbor, MI

Abstract. Signal integrity has become a critical issue in the design of high-performance circuits. Noise on a net arises both through propagation of noise from previous stages through the driver gate of the net and through injection of new noise through coupling capacitance with neighboring nets. Typically, propagated noise and injected noise are added linearly to simplify the analysis and increase its efficiency. In this paper, we show that this linear assumption results in a significant underestimation of the noise, due to the non-linear behavior of the driver gate, and hence can lead to many undetected noise failures in the design. Since complete non-linear simulation is too slow for large cell-based designs, we propose a new linear model that accurately captures the non-linear behavior of the driver gate. We propose three iterative methods for computing the model parameters of this linear model. Results are presented to demonstrate the accuracy of the proposed approach on several industrial designs.

**Key Words:** noise analysis, signal integrity, capacitive cross-talk, circuit stability

# 1. Introduction

With the advance of process technology, cross-coupled noise in digital designs has greatly increased. Especially in high performance designs that employ fast signal transition times and noise sensitive circuit families noise has become a critical design issue. This trend has lead to the need for accurate noise analysis tools [1–4]. In noise analysis, the net under consideration is commonly referred to as the victim net, while the nets that inject noise are referred to as aggressor nets. A victim net with its associated aggressor nets is referred to as a noise cluster. Typically, two types of noise are distinguished. Functional noise occurs when the victim net is in a stable state and the aggressor nets switch. In this case, a noise pulse occurs on the victim net that can change the state of a storage element, such as a latch, and can cause a functional failure. Delay noise occurs when the victim net transitions simultaneously with the aggressor nets that inject noise upon it. In this case, the delay of the net is modified leading to performance violations. Extensive research has been performed on delay noise analysis [5,6]. In this paper, we focus on functional noise analysis.

Functional noise analysis tools must perform a conservative analysis to ensure that no possible noise

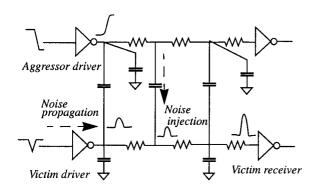

problems remain undetected in the design. Noise injected by the aggressor nets combines with noise propagated from the input of the victim driver gate, as illustrated in Fig. 1. The combined noise pulse at the victim receiver is compared against a so-called noise rejection curve [1,4] to determine if the particular noise pulse height and width results in a failure. In order to perform a conservative noise analysis, the noise peaks of the propagated noise and the injected noise are aligned to create a noise pulse with a maximum possible noise pulse height. In some noise analysis approaches, the propagated noise is treated as DC noise [7], which eliminates the problem of alignment, but results in a more pessimistic analysis.

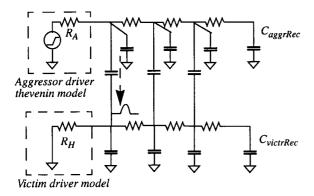

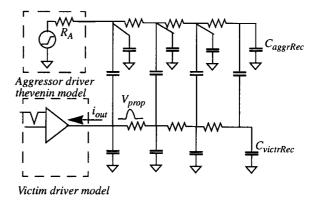

To efficiently compute the injected noise, analysis tools typically use linear models for the victim and aggressor driver gates, as shown in Fig. 2. The aggressor driver is represented with a Thevenin model, consisting of a ramp voltage source and Thevenin resistance  $R_A$ , providing the same signal slope as the original aggressor driver. The victim driver gate is modeled with a grounded resistance, called the holding resistance  $R_H$ . This resistance is computed using a small signal analysis of the driver with both driver input and output biased at stable supply voltages, i.e.,  $V_{dd}$  (GND) at the driver input and GND ( $V_{dd}$ ) at the driver output). The use

Fig. 1. Noise due to propagation and injection.

Fig. 2. Linear model for injected noise

of such a linear model has several advantages. First, the entire circuit can be analyzed using efficient linear methods, such as reduced order modeling [8]. Second, superposition can be used to sum the noise injected from each individual aggressor, making it simple to align the noise pulse peaks from each aggressor.

The propagated noise through the victim driver is typically computed using pre-characterized tables. The driver gate is simulated under a number of different noise pulse heights, pulse widths and loading conditions. For each condition, propagated noise is computed using non-linear simulation and stored in a table. During noise analysis, the propagated noise is determined from this table based on the noise pulse height and width at the victim driver input and is added to the injected noise from aggressor nets. Since the injected and propagated noise pulses are added linearly, their worst-case alignment is again easily determined. In certain approaches [1], a pre-determined worst-case propagated noise is used for each gate, instead of the actual propagated noise. The worst-case propagated noise is defined as the maximum noise at the output of the driver in response to any input noise that does not cause a noise failure of the gate. This simplification improves the efficiency of the analysis while increasing its pessimism.

Due to the use of linear addition of the injected and propagated noise pulses, propagated and injected noise can be computed independently, allowing for very efficient and simple analysis. This explains the wide spread use of this approach in the literature [1,7,9] as well as in commercial tools. It is based on an underlying assumption that the victim driver gate is linear and the approach is similar to noise analysis in analog circuits, where noise sources are small and devices exhibit relatively linear behavior. In digital circuit, on the other hand, noise can be quite large (due to its inherent robustness), and the devices are constructed to have a very high gain and exhibit highly non-linear behavior. Therefore, the linear addition of propagated and injected noise is not valid and can result in a significant error in the computed noise.

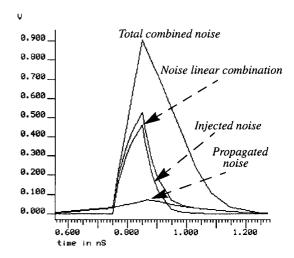

Figure 3 shows the simulation results of a typical noise cluster from an industrial 0.13 micron design. The propagated noise pulse has a height of 70 mV and the injected noise pulse a height of 453 mV. Therefore, the linear combination of the propagated and injected noise has a height of 523 mV. However, non-linear simulation of the noise cluster results in a noise pulse with a height of 900 mV. This is due to the fact that the holding resistance of the victim driver is not constant during the noise propagation. Even though the propagated noise was small (70 mV), the holding resistance of the

Fig. 3. Comparison of combined propagated and injected noise with its linear combination.

driver gate was significantly increased due to the noise at the driver input and output. In fact, it is possible that the input noise at the victim driver is sufficiently small such that it does not yield any propagated noise, while still significantly modulating the holding resistance and increasing the injected noise on the victim net.

It is clear that the linear combination of the propagated noise and injected noise used in existing analysis tools results in a significant underestimation of the actual noise. The straightforward approach to solving this problem is to perform non-linear simulation of the entire coupled interconnect and driver network. However, this approach has two serious difficulties. First, non-linear simulation is too slow for analysis of large design, even though the linear portion of the network can be represented with a reduced order model. Second, determining the worst-case alignment between the propagated noise and the injected noise is difficult in non-linear simulation, and typically involves expensive iterative search.

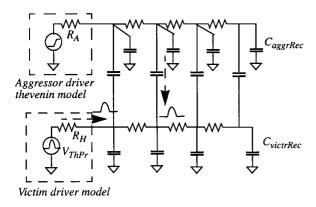

In this paper, we therefore propose a new linear model, shown in Fig. 4 for accurate computation of the combined injected and propagated noise. In this model, the victim driver is represented with a Thevenin model consisting of a pulsed voltage source  $V_{ThPr}$  and resistance  $R_H$ . These model parameters depend on the victim driver input noise  $v_{in}$ , as well as the total combined output noise  $v_o$ , in order to capture non-linearity of the victim driver. The criteria under which the linear model is exact (i.e., identical to the non-linear gate) is first formulated. Three approaches using least square iterative techniques are then presented to compute parameters that minimize the error of the linear model. The proposed methods use the DC-operating characteristics of the driver gate which is easily pre-computed

Fig. 4. Linear model of noise cluster.

and stored in a compact table. The approach therefore lends itself well for use in a pre-characterized cell based design flow. To validate the accuracy of the proposed methods, we present results on a number of nets from industrial designs.

The reminder of the paper is organized as follows: In Section 2 we present the models and algorithms of the proposed approach. In Section 3 we present 3 different model fitting methods. In Section 4 we present our results and in Section 5 we draw our conclusions.

#### 2. Linear Model and Approach

Our goal is to compute the total combined noise at the victim driver output due to a given noise pulse at the victim driver input and coupling with switching aggressor nets, while taking into account the non-linear effects of the victim driver. We assume that a linear aggressor driver model is computed using traditional methods [1,5] and the victim and aggressor receivers are modelled by simple grounded capacitances. The victim and aggressor wires and represented with their lumped RC models as depicted in Fig. 1 and Fig. 4. For simplicity, we assume that noise is applied to only one input of the victim driver though the proposed technique can be generalized for noise propagated from several inputs as well.

# 2.1. Noise Computation Algorithm

The non-linear model of the noise cluster is depicted in Fig. 5. Transforming the Thevenin models of the aggressor drivers into Norton equivalents, the nodal

Fig. 5. Non-linear model of noise cluster.

equations for the noise cluster can be written as follows:

$$\left(C \cdot \frac{d}{dt} + G\right) \cdot V = J \tag{1}$$

where C is the capacitance matrix, G is the conductance matrix, V is the vector of nodal voltages, and J is the vector of current sources. All the equations are linear except the one with the victim driver output current  $i_{out}$  which is non-linear and time dependent. The victim driver output current is expressed as a function of the victim input and output voltages,  $v_{in}$  and  $v_{out}$ , where the victim input voltage  $v_{in}(t)$  is a function of time t.

$$i_{out} = f_{load}(v_{in}, v_{out}) \quad v_{in} = f_{noise}(t)$$

(2)

Since solving equations (1) and (2) simultaneously as a non-linear system is very expensive and takes away the benefits of the linear models such as superposition and model order reduction, we propose to solve equations (1) and (2) separately and iteratively improving the solution. Note that equations (1) and (2) considered separately are indefinite and have many solutions. So they cannot be solved straight forward. We construct a parametrized victim driver Thevenin model  $M_{Victim}(p_1, p_2, ...)$  and add the equations describing this model to equation (1) to make it linear and definite. The resulting system corresponds to the linear model of the noise cluster depicted in Fig. 4. The parameters of this model can be, for example, Thevenin resistance, propagated noise height, etc. We give below some examples of the parametrized Thevenin model for the victim driver. The resulting linear circuit can be solved using reduced order model techniques and superposition principle. Exploiting its linearity we can easily find the worst noise alignment. Its solution is a linear estimation of the victim output voltage  $v_{lin}(t)$ and current  $i_{lin}(t)$ . Substituting the estimation  $v_{lin}(t)$ into equation (2), we compute non-linear estimates of the victim output current  $i_{nonlin}(t)$ . Comparing the linear and non-linear victim output current estimates, we then correct the parameters  $p_1, p_2, \ldots$  of the victim model to improve current estimation. With these refined parameters we repeat our iteration till convergence. It is obvious that if the linear and non-linear current estimates converge to be equal, they provide the exact solution of the original system of equations. Simultaneously we find the parameters of the victim driver linear model. Of course achieving complete coincidence between linear and non-linear solution is the ideal case. In reality, we only minimize the difference between the linear and non-linear estimates of the victim output current. The quality of approximation depends on the structure of the selected victim model.

The proposed approach can be implemented in various ways that differ in the models for the victim driver, the comparison criterion for the victim driver current estimates, and the procedure of correcting victim model parameters. In our experiments we tried two comparison criteria.

The first one is the integral of the difference between the linear and non-linear current estimates:

Minimize

$$\int_{0}^{T} (i_{lin}(t) - i_{nonlin}(t)) dt$$

(3)

The above expresses the difference between charges accumulated up to time T at the victim output in linear and non-linear models. Unfortunately, in practice this criterion is rather unstable. While it works satisfactorily in some cases affects convergence in many. The reason is that the victim output current may change its direction resulting in instability.

The other criterion is the integral of squared difference between linear and non-linear current estimates:

Minimize

$$\int_0^T (i_{lin}(t) - i_{nonlin}(t))^2 dt$$

(4)

The above least squares error based approach is seen to be stable and reliable based on our experiments.

The procedure correcting the victim model parameters is rather obvious. If our model depends on parameters  $p_1, p_2, \ldots, p_n$ , we can use a cost function that we want to minimize:  $F(p_1, p_2, \ldots, p_n)$ . Then at each iteration we can compute the parameter values that minimizes the cost. We can find them by equating partial derivatives of the cost to 0 and solving the resulting system of equations.

$$\frac{dF(p_1, p_2, \ldots)}{dp_i} = 0 \tag{5}$$

Using these parameters we can recompute the current estimations and iterate till convergence. The overall algorithm is given in Fig. 6. As convergence criterion, we use the relative least square error of current estimates.

$$\sqrt{\frac{\int_0^T (i_{lin}(t) - i_{nonlin}(t))^2 dt}{\int_0^T i_{nonlin}^2(t) dt}}$$

(6)

- 1. Compute initial values of victim model parameters  $p_1, p_2, \ldots$

- 2. Build linear system by combining equations (1) and victim model equations

- Find linear estimations of the victim output voltage v<sub>out</sub>(t) and current i<sub>lin</sub>(t) by solving the built system using the worst alignment.

- 4. From nonlinear victim model equation (2) find nonlinear estimations of the victim output current inonlin(t)

- 5. Find the values of the victim model parameters  $p_1, p_2, ..., p_r$  viding the minimum of the criterion  $F(p_1, p_2, ..., p_n)$  by solving equations (5).

- 6. If the value of the criterion F(p<sub>1</sub>, p<sub>2</sub>, ..., p<sub>n</sub>) is more than desired accuracy and the number iterations done is less than the limit repeat step 2.

Fig. 6. Combined noise computation algorithm.

# 2.2. Simplified Non-Linear Victim Driver Model

In our approach above we assume that we can compute victim output current  $i_{out}(t)$  as function of time. Of course it can be done by transient simulation of the victim driver but it is slow. So we propose to compute it approximately but more efficiently.

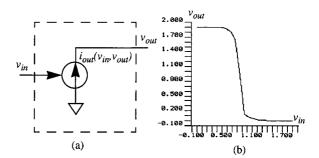

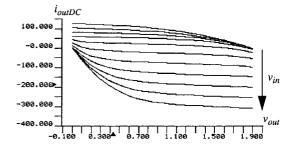

Let us consider the victim drive gate as a black box described by its direct current (DC) characteristics. That is, we model the victim driver as a nonlinear current source (Fig. 7 (a)). Its current  $i_{outDC}$ depends on both its input and output voltages:  $i_{outDC} =$  $f_{load}(v_{in}, v_{out})$ . Graphically this dependence is represented by a family of gate load curves (Fig. 7(c)). For our noise computations, victim driver output current  $i_{outDC} = f_{load}(v_{in}, v_{out})$  is represented by a two dimensional table and computed by DC simulations sweeping a range of input and output voltages. Also, we use DC victim driver voltage transfer characteristic expressing its output voltage as a function of the input voltage:  $v_{out} = v_{out}(v_{in})$ . This is given in a one dimensional table and is also computed by DC simulations sweeping the input voltage range. An example of the DC transfer curve is shown in Fig. 7(b). The family of load curves and the transfer curve are computed only once at the precharacterization stage and do not require recomputing at the time of noise analysis. Using input and output noise waveforms  $v_{in}(t)$ ,  $v_{out}(t)$  and DC characteristics of the victim driver we compute  $i_{out}(t)$ .

We should point out that the above non-linear model neglects the influence of victim driver gate's internal capacitances on noise computation. For nets with long interconnects (which are also significant for noise) this

Fig. 7. Non-linear victim driver model. (a) non-linear victim driver model, (b) victim driver transfer curve.

influence is not significant. The transistor drain capacitances associated with the victim driver output can be easily taken into account by adding it to other parasitic capacitances.

## 3. Victim Gate Models

We investigated three victim driver models that are based on the Thevenin model with resistance and pulse voltage source. These models differ in their parameters and the shape of the propagated noise pulse.

# 3.1. Holding Resistance Adjustment

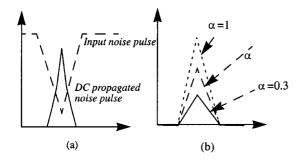

The simplest model is one that is parametrized with the victim holding resistance  $R_H$ . The Thevenin propagated noise pulse is considered constant and equal to the DC propagated input noise pulse shown in Fig. 8(a). The linear estimate of the victim output current in this case is simply  $(v_{out} - V_{ThPr})/R_H$ . Substituting this into equation (4) we obtain the objective:

Minimize

$$\int_{0}^{\infty} \left( \frac{v_{out} - V_{ThPr}}{R_{H}} - i_{nonlin}(t) \right)^{2} dt$$

(7)

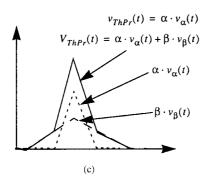

Fig. 8. Propagated noise pulses for victim models. (a) victim input and DC propagated noise pulses, (b) noise pulses parametrized with their height, (c) noise combined of two pulses with different width and height.

We find the value of  $R_H$  by differentiating equation (7) with respect to  $R_H$  and equating it to 0:

$$R_{H} = \frac{\int_{0}^{T} (v_{out} - V_{ThPr})^{2} dt}{\int_{0}^{T} (v_{out} - V_{ThPr}) \cdot i_{nonlin} dt}$$

(8)

Here we neglect with dependence of  $v_{out}$  on  $R_H$  and the corresponding dependence of  $i_{nonlin}$  on it. This leads to inaccuracy in the holding resistance estimation. Therefore in our experiments, we have to restrict variation of  $R_H$  for convergence. This problem could be solved by computing  $\partial v_{out}/\partial R_H$  and  $\partial i_{nonlin}/\partial R_H$  but this will make the technique more expensive. According to our experiments this model has two drawbacks:

- each iteration requires recomputing the reduced order models that could be slow. By the technique proposed in [10] this calculation can be speeded up.

- adjusting only holding resistance often does not provide good accuracy. A circuit with constant holding resistance cannot accurately model noise pulse in a real nonlinear circuit. A small resistance cannot give high enough noise pulse but a high one results in too wide a noise pulse with very long tail.

## 3.2. Propagated Voltage Height Adjustment

Another victim driver model is parametrized with the height of the Thevenin propagated noise pulse  $V_{ThPr}$  which is assumed to be equal to a predetermined voltage pulse  $v_{\alpha}(t)$  scaled by a parameter  $\alpha$ , i.e.,  $V_{ThPr}(t) = \alpha \cdot v_{\alpha}(t)$ . We show such a parameterized noise pulse in Fig. 8(b). The holding resistance  $R_H$  is considered fixed in this case. For this model the criterion equation (4) can be rewritten as:

Minimize

$$\int_0^T \left( \frac{v_{out} - \alpha \cdot v_{\alpha}}{R_H} - i_{nonlin}(t) \right)^2 dt$$

(9)

The victim output noise voltage  $v_{out}$  can be represented as a sum of total injected and propagated noise  $v_{out} = v_{inj} + v_{prop}$ . As our circuit for noise propagation is linear, we can express the propagated noise as  $v_{prop} = \alpha \cdot v_{prop,\alpha}$  where  $v_{prop,\alpha}$  is the solution of the linear model for noise propagation when the Thevenin propagated noise pulse is  $v_{\alpha}(t)$ . Substituting all these into our criterion, differentiating it with respect to  $\alpha$ , and solving the resulting equation, we find  $\alpha$ :

$$\alpha = \frac{\int_0^T \Delta v_\alpha \cdot \Delta v_i \, dt}{\int_0^T \Delta v_\alpha^2 \, dt} \tag{10}$$

where:  $\Delta v_{\alpha} = v_{\alpha} - v_{prop,\alpha}$ ,  $\Delta v_i = v_{inj} - R_H \cdot i_{nonlin}$ .

Here again we neglect the dependence of  $i_{nonlin}$  on  $v_{out}$  and respectively on  $\alpha$ . This results in some inaccuracy in estimating the scale factor and worsens convergence though not as severely as the previous model.

This model does not require recomputation of the reduced order model because we vary only the scale factor of the input voltage. So the iterations are faster. Besides, the Thevenin propagated noise pulse  $V_{ThPr}$  mimics non-linear effects not captured by constant holding  $R_H$ . If we could guess the right shape of the Thevenin propagated noise pulse  $V_{ThPr}$  this model will be able to find its magnitude. This model may compute non-zero propagated noise pulse even if input noise pulse is less than victim driver switching level. This fictitious propagated noise mimics holding resistance increase because of its modulation by the input pulse.

It is easy to combine the previous model with this one but our experiments showed no significant increase in accuracy because the capability of this model is restricted by the fixed pulse shape.

# 3.3. Propagated Voltage Height and Shape Adjustment

The drawback of the previous model is the fixed shape of the propagated noise pulse. It is overcome by representing the Thevenin propagated noise pulse  $V_{ThPr}$  as a combination of two pulses of different width. Their heights  $\alpha$  and  $\beta$  are considered as model parameters. So the total propagated noise pulse is represented as  $V_{ThPr}(t) = \alpha \cdot v_{\alpha}(t) + \beta \cdot v_{\beta}(t)$ . This is shown in Fig. 8(c). Substituting this expression into our criterion we obtain the function to minimize:

Minimize

$$\int_{0}^{T} \left( \frac{v_{out} - \alpha \cdot v_{\alpha} - \beta \cdot v_{\beta}}{R_{H}} - i_{nonlin}(t) \right)^{2} dt$$

(11)

As with the previous model we represent output victim voltage as a sum of injected noise and noise due to propagation  $v_{\alpha}$  and  $v_{\beta}$ ,  $v_{out} = \alpha \cdot v_{prop,\alpha} + \beta \cdot v_{prop,\beta}$ . Substituting it into equation (11) and finding values of  $\alpha$  and  $\beta$  that minimize it we obtain:

an input voltage equal to half the input noise level. Then, using this initial estimation we improve it by computing the total noise and then recomputing the holding resistance from the load curve at the operation point of half the input noise level and half the output noise level. Using of this factor is an attempt to average our estimation because in reality, the holding resistance varies during noise propagation.

Integral Computation. We compute all the integrals by trapezoidal integration formula. The upper integration limit is the time of the combined noise peak. This selection provides better accuracy of noise height estimation because we do not minimize the error of victim current after noise peak.

Parameter Variation. In order to avoid convergence problem we change the adjusted parameters at each iteration by not more than 20%. This restriction is necessary because in computing new values of parameters we partly ignore dependence of victim current on parameters variation.

$$\alpha = \frac{\int_{0}^{T} \Delta v_{\alpha} \cdot \Delta v_{i} dt \cdot \int_{0}^{T} \Delta v_{\beta}^{2} dt - \int_{0}^{T} \Delta v_{\beta} \cdot \Delta v_{i} dt \cdot \int_{0}^{T} \Delta v_{\alpha} \cdot \Delta v_{\beta} dt}{\int_{0}^{T} \Delta v_{\alpha}^{2} dt \cdot \int_{0}^{T} \Delta v_{\beta}^{2} dt - \left(\int_{0}^{T} \Delta v_{\alpha} \cdot \Delta v_{\beta} dt\right)^{2}}$$

$$\beta = \frac{\int_{0}^{T} \Delta v_{\beta} \cdot \Delta v_{i} dt \cdot \int_{0}^{T} \Delta v_{\alpha}^{2} dt - \int_{0}^{T} \Delta v_{\alpha} \cdot \Delta v_{i} dt \cdot \int_{0}^{T} \Delta v_{\alpha} \cdot \Delta v_{\beta} dt}{\int_{0}^{T} \Delta v_{\alpha}^{2} dt \cdot \int_{0}^{T} \Delta v_{\beta}^{2} dt - \left(\int_{0}^{T} \Delta v_{\alpha} \cdot \Delta v_{\beta} dt\right)^{2}}$$

$$(12)$$

where:  $\Delta v_{\alpha} = v_{\alpha} - v_{prop,\alpha}$ ,  $\Delta v_{\beta} = v_{\beta} - v_{prop,\beta}$  and  $\Delta v_i = v_{inj} - R_H \cdot i_{nonlin}$ . Here we again neglect with dependence of  $i_{nonlin}$  on  $\alpha$  and  $\beta$ .

Our experiments show that this third approach gives the best trade-off between the computational cost and accuracy. It does not require recomputing the reduced order model and captures non-linear effects by adjusting both the magnitude and shape of the propagated noise pulse.

## 3.4. Implementation Issues

Holding Resistance Estimation. The proposed technique requires the estimation of the victim driver holding resistance  $R_H$ , which we compute from gate load curves in two steps. First we compute the holding resistance at the assumption of zero output noise and

#### 4. Results

The proposed approach was implemented in an industrial noise analysis tool called Clarinet [1] in place of the existing linear approach. Experiments were performed on net clusters from a high performance microprocessor, implemented in a 0.13 micron process and operating at a supply voltage of 1.9 volts. The results of noise estimations are presented in Table 1. Each noise cluster was analyzed with three different input noise pulse heights at the victim driver input. Since the method using both noise voltage height and width adjustment, presented in Section 3.3, was found give the best accuracy, we only show results for this method.

In Table 1, we demonstrate that the proposed approach provides good accuracy for both small and very

Table 1. Results of combined noise calculation.

| Net | #Input Noise | Output Noise |       |        |       |                          |

|-----|--------------|--------------|-------|--------|-------|--------------------------|

|     |              | New Approach |       | SPICE  |       |                          |

|     |              | Height       | Width | Height | Width | Error (%) (Height/Width) |

| 1   | 0.38         | 0.34         | 0.39  | 0.40   | 0.44  | 9.5/6.3                  |

|     | 0.76         | 0.37         | 0.43  | 0.41   | 0.55  | 9.7/21                   |

|     | 1.14         | 0.48         | 0.48  | 0.51   | 0.60  | 6.3/20                   |

| 2   | 0.38         | 0.32         | 0.35  | 0.31   | 0.45  | 3.2/20.6                 |

|     | 0.76         | 0.32         | 0.35  | 0.33   | 0.47  | 2.5/25                   |

|     | 1.14         | 0.392        | 0.36  | 0.399  | 0.48  | 1.7/25                   |

| 3   | 0.38         | 0.12         | 0.45  | 0.13   | 0.46  | 2.1/2.4                  |

|     | 0.76         | 0.13         | 0.46  | 0.14   | 0.50  | 3.6/8.2                  |

|     | 1.14         | 0.23         | 0.45  | 0.24   | 0.49  | 4.8/8.3                  |

| 4   | 0.38         | 0.14         | 0.27  | 0.13   | 0.26  | 7.6/2.2                  |

|     | 0.76         | 0.16         | 0.28  | 0.17   | 0.31  | 7.1/9.3                  |

|     | 1.14         | 0.32         | 0.30  | 0.39   | 0.32  | 17.8/6.2                 |

| 5   | 0.38         | 0.12         | 0.32  | 0.11   | 0.32  | 10/0.01                  |

|     | 0.76         | 0.14         | 0.32  | 0.15   | 0.34  | 7.6/4.2                  |

|     | 1.14         | 0.32         | 0.32  | 0.39   | 0.33  | 19.5/3.9                 |

high input and output noise. It also demonstrates that the accuracy of the noise height is higher that noise width. This results from the fact that our integral criterion is only computed till the noise pulse peak. Increasing the integration time improves the accuracy of noise width estimation at the expense of the noise height accuracy.

Comparing with the traditional linear approach, the proposed technique usually requires 2–3 times more computation time. However, run time impact can be minimized by applying the proposed method only to critical nets.

#### 5. Conclusions

In this paper we investigated combined noise due to noise propagation and injection. We showed that nonlinear effects in noise propagation and combination are very significant and ignoring them leads to high error in noise estimation even for relatively small noise signals.

We developed a new iterative approach for computing the combined noise due to propagation and injection. The proposed approach takes into consideration the non-linear characteristic of the victim driver. We showed implementation of the proposed approach for three different models of the victim driver using least square criterion of computation accuracy. The proposed

approach gives better accuracy than the traditional one. It still allows to use superposition principle, reduced order model, and easy computation of worst alignment of noise pulses, which features are very important for the speedy analysis of a large number of chip level global nets. The accuracy and convergence of the proposed approach can be increased further by using more sophisticated models and more accurate computation of the derivatives for minimizing cost function. The new approach can be used both for noise calculation and for finding the worst noise alignment for transient noise simulation by Spice.

The proposed approach was tested on noise clusters of high speed microprocessor designs. The results show very good accuracy of noise computation even for noise of high magnitude.

## References

- Levy, R., Blaauw, D., Braca, G., Dasgupta, A., Grinshpon, A., Oh, C., Orshav, B., Sirichotiyakul, S. and Zolotov, V., "Clarinet: A noise analysis tool for deep submicron design," in *Proceedings IEEE/ACM Design Automation Conference*, pp. 233–238, June 2000.

- Chen, P. and Keutzer, K., "Towards true crosstalk noise analysis." ICCAD-99, pp. 132–137.

- Glebov, A., Gavrilov, S., Blaauw, D., Sirichotiyakul, S., Oh, C. and Zolotov, V., "False noise analysis using logic implications." *ICCAD 2001*, pp. 515–521, November 2001.

- Shepard, K. L., "Design methodologies for noise in digital integrated circuits," in *Proc.*, *DAC*, pp. 94–99, 1998.

- Dartu, F. and Pileggi, L. T., "Calculating worst-case gate delays due to dominant capacitance coupling," in *Proc. DAC*, pp. 46–51, June 1997.

- Sirichotiyakul, S., Blaauw, D., Chanhee, Oh, Levy, R., Zolotov, V. and Jingyan, Z., "Driver modeling and alignment for worstcase delay noise," in *Proc. DAC 2001*, pp. 720–725, 2001.

- Shepard, K. L. and Narayanan, V., "Noise in deep submicron digital design." ICCAD 1996, pp. 524–553.

- Odabasioglu, A., Celik, M. and Pileggi, L. T., "PRIMA: passive reduced-order interconnect macromodeling algorithm," in *Proc. ICCAD-97*, pp. 58–65, 1997.

- Shepard, K. L., Narayanan, V., Elementary, P. C. and Zheng, G., "Global harmony: Coupled noise analysis for full-chip RC interconnect networks," in *Proc. ICCAD*, pp. 139–146, 1997.

- Levy, H., Scott, W., MacMillen, D. and White, J., "A rank-one update method for efficient processing of interconnect parasitics in timing analysis." DAC-2000.

**Vladimir Zolotov** (M'96) received M.S. degree in electrical engineering from Moscow Institute of Electronics, Russia and Ph.D. in electrical engineering from Scientific Research Institute of Micro Devices, Moscow, Russia.

He has been with Advanced Tools group, Motorola Inc., Austin, TX since 1998, where he is currently a Senior Staff Engineer/Scientist involved in the development of EDA tools and methodology for high performance VLSI designs.

Previously V. Zolotov was with Scientific Research Institute of Micro Devices, Moscow, Russia and then with Moscow Research Laboratory, Motorola, Inc., Moscow, Russia.

His research interests include signal integrity, reliability, on chip inductance, SOI circuits, timing analysis and optimization of VLSI.

**David Blaauw** received his B.S. in Physics and Computer Science from Duke University in 1986, his M.S. in Computer Science from the University of Illinois, Urbana, in 1988 and his Ph.D. in Computer Science from the University of Illinois, Urbana, in 1991.

He worked at the Engineering Accelerator Technology Division, IBM Corporation, Endicott, as a Development Staff Member, until August 1993. From 1993 till August 2001, he worked for Motorola, Inc. in Austin, TX, where he was the manager of the High Performance Design Technology group. Since August 2001, he has been on the faculty at the University of Michigan as an Associate Professor.

His work has focussed on VLSI design and CAD with particular emphasis on circuit analysis and optimization problems for high performance and low power designs. He was the Technical Program Chair and General Chair for the International Symposium on Low Power Electronic and Design in 1999 and 2000, respectively, and was the Technical Program Co-Chair and member of the Executive Committee the ACM/IEEE Design Automation Conference in 2000 and 2001.

**Rajendran Panda** (S'94, M'96) received the B.E. (Honors) degree in Electrical Engineering from Madurai University in 1978, the LL.B. (Bachelor of Laws) degree from Bangalore University in 1984, and the Ph.D. degree in Computer Science from the University of Illinois at Urbana-Champaign in 1996. From

1978 to 1991, he was with the Bharat Heavy Electrical Industries, Bangalore.

He is currently with Motorola, Austin, managing the High Performance Design Technology group. His work has focussed on low power design, power supply and signal integrity issues, and circuit optimization. He has published extensively and holds many patents in these areas.

**Chanhee Oh** (S'87—M'95) received the B.S. degree from Seoul National University, Korea and the

M.S. and the Ph.D. degrees in electrical engineering from the University of Texas at Austin.

He has been with Advanced Tools group, Motorola Inc., Austin, TX since 1997, where he is currently a Distinguished Member of Technical Staff. He is involved in the development of EDA tools and methodology for high performance VLSI designs. Previously, Dr. Oh was with a microprocessor development group at Advanced Micro Devices, Austin, TX.

His research interests include signal integrity, reliability, timing analysis and optimization of VLSI.