# THE DEVELOPMENT AND CHARACTERIZATION OF SELF-PACKAGES USING MICROMACHINING TECHNIQUES FOR HIGH FREQUENCY CIRCUIT APPLICATIONS

# by Rhonda Franklin Drayton

A dissertation submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

(Electrical Engineering)

in The University of Michigan

1995

#### **Doctoral Committee:**

Professor Linda P. B. Katehi, Chair Assistant Professor Diann Brei Associate Professor Khalil Najafi Associate Professor Gabriel M. Rebeiz Research Scientist Jack East

© Rhonda Franklin Drayton 1995 All Rights Reserved

## The Serenity Prayer

God.

Grant me the Serenity

to Accept the Things that I cannot Change,

The Courage,

to Change the Things that I Can,

And the Wisdom to know the Difference.

Author Unknown

To my loving husband, Marcus My inspiring parents, Elvin and Ann Franklin and In memory of my grandmother, Yolande.

#### **ACKNOWLEDGEMENTS**

First, I would like to thank God for giving me the strength, courage, and means to pursue this endeavor and for this wonderful growth experience. My sincerest and greatest appreciation goes to my advisor and mentor, Linda P. B. Katehi, who has shown utmost faith in my abilities from the very beginning of my graduate school career. Her foresight and confidence in my potential has given me the opportunity to make this goal a reality. Mere words can ever describe the valuable lessons I have learned through my interactions with her. Finally, finishing this degree would not be possible without the time and effort my committee members have extended and the opportunities they've given toward technical and professional discussions over the years. I thank each of you.

I am especially grateful for the financial assistance provided through the Graduate Consortium for Minorities in Engineering (GEM) and the Fellowship Office at The Rackham School of Graduate Studies at the University of Michigan. In particular, I thank Dr. Howard Adams, Former Director of the GEM program, for pursuing his vision to increase the number of underrepresented groups in engineering and science with graduate degrees and my corporate sponsor, Lawrence Livermore National Laboratory, for providing the opportunity for me to participate in the world of research. Lastly, this work would not exist without the financial support of the Army Research Office, Office of Naval Research, and the Nasa Center for Space Terahertz Technology which provides the resources to explore basic research in this area.

The graduate school experience would not be complete without the presence of other peers who suffer, struggle, and explore in the name of knowledge. I would like to extend a thank you to the all of those whose names may not be mentioned, but who have influenced my graduate school experience either technically or personally. In particular, I would like

to thank Dr. Jose E. Roman for being a wonderful friend and for sharing his experiences while in pursuit of a similar goal, and Dr. Andy Engel for the many discussions in the early years that shaped my future research perspective. In the Department and College, thanks to all of the faculty, staff, and colleagues, especially to those in the Professor Rebeiz' group who took the time to share their tribal knowledge and to those in the Solid State Area who were very willing to share their processing expertise. Special thanks goes to Mr. Chen-Yu Chi and Mr. Sanjay Raman for the many open discussions both technically and personally. And it goes without saying, many thanks over and over again to my group members who have made my time here the most pleasant due to the comradry and diversity that exist within and specifically to Dr. Nihad Dib, who's theoretical work provided the means to validate much of my research effort. On the experimental side, I thank Dr. Thomas M. Weller and Messr. Stephen V. Robertson and George Ponchak for their insight, technical dialogues and friendship. Best wishes to the new coming experimentalists and much appreciation to my office mates, Ms. Rashaunda M. Henderson and Mr. Ionnis Papapolymerou for their good company, assistance and patience during the last year. Lastly, a special thanks goes to Ms. Anne Monterio, Ms. Shirley McDavid and Dr. Leo McAfee for the countless discussions and endless encouragement sessions they have given me throughout this process. To my friends and family members, who have practically pursued this degree with me as I have dragged them through my many trials and tribulations, thanks.

On a more personal note, no words can express my lasting appreciation and love for my husband, Marcus, who has stood by me through thick and thin to achieve this endeavor. His constant encouragement and love have it made possible for my dream to become a reality. Many thanks and much appreciation go to my parents for their constant support and teachings by example. It is through their unlimited love and faith, and lack of placing boundary conditions on my capabilities that have made the struggles of obtaining a Ph.D. somewhat bearable. And last but not least to my brother, Fred, and his wonderful

family for being a source of strength and joy to me during the many year I have been in school. This achievement will forever be a memorable event in my life and it is my hope that it is only the beginning as I go forth and give back to society what so many have graciously extended to me along the way. I thank you all and may God Bless you as much as He has Blessed me.

#### **PREFACE**

This thesis presents with the development and characterization of a novel packaging structure that is realized for high frequency circuit applications using silicon micromachining techniques. This self-packaged topology results from the merger of two technologies, silicon micromachining and high frequency circuit design techniques used in microwave and millimeter wave applications. Extensions of the technology have been used to explore its potential to improve the performance of microstrip antennas, such as the rectangular patch, in order to provide an alternative means for reducing surface wave excitation in high index materials. The design, fabrication and testing procedures are discussed herein, and measured results are shown for representative planar circuits and antenna elements typically used in high frequency applications.

# TABLE OF CONTENTS

| DEDICATION.  |                                                            | ii    |

|--------------|------------------------------------------------------------|-------|

| ACKNOWLED    | GEMENTS                                                    | iii   |

| PREFACE      |                                                            | vi    |

| TABLE OF CO  | NTENTS                                                     | . vii |

| LIST OF FIGU | RES                                                        | x     |

| LIST OF TABL | ÆS                                                         | xv    |

| LIST OF APPE | NDICES                                                     | xvi   |

| CHAPTER      |                                                            |       |

| I. INTR      | ODUCTION                                                   | 1     |

|              | Packaging in High Frequency Applications  Overview         |       |

| II. DEV      | ELOPMENT OF MICROMACHINED PACKAGES                         | 6     |

| 2.1          | Introduction                                               | 6     |

| 2.2          | Motivation and Objectives                                  | 9     |

| 2.3          | General Fabrication Methodology                            | 12    |

|              | 2.3.1 Air-Filled Upper Shielded Circuits                   | 13    |

|              | 2.3.1.a Version One: Basic Cavity                          | 15    |

|              | 2.3.1.b Version Two: Cavity with Access Windows            | 20    |

|              | 2.3.1.c Version Three: Cavity with Access Windows based of | n a   |

|              | Double Side Etch                                           |       |

|              | 2.3.2 Self-Packaged Circuits                               | 26    |

|              | 2.3.3 Conformally Packaged Circuits                        |       |

| 2.4          | Conclusions and Future Work                                | 30    |

|              | EORETICAL AND EXPERIMENTAL CHARACTERIZATION CHNIQUES       | 33    |

|              |                                                            |       |

| 3.1          |                                                            |       |

| 3.2          | Circuit Design and Analysis Tools                          | 35    |

|      |      | 3.2.1 Design Procedures                                    | 35  |

|------|------|------------------------------------------------------------|-----|

|      |      | 3.2.2 Theoretical Model Techniques                         |     |

|      |      | 3.2.2.a Space Domain Integral Equation Method              |     |

|      |      | 3.2.2.b Finite Difference Time Domain Method               |     |

|      | 3.3  | High Frequency Measurement Techniques                      |     |

|      |      | 3.3.1 Test Set-Up and Measurement Probes                   |     |

|      |      | 3.3.2 Calibration Methods                                  |     |

|      |      | 3.3.3 Measurement Errors                                   |     |

|      | 3.4  | Summary                                                    |     |

| IV.  | CHA  | RACTERIZATION OF MICROMACHINED PACKAGES                    | 55  |

|      | 4.1  | Introduction                                               | 55  |

|      | 4.2  | Micromachined Package and Circuit Evaluation               | 58  |

|      |      | 4.2.1 Micromachined Circuit Modelling Issues               |     |

|      |      | 4.2.2 Existing Machine-Milled Circuits                     |     |

|      |      | 4.2.2.a Motivation                                         |     |

|      |      | 4.2.2.b Circuit Design and Fabrication Considerations      | 62  |

|      |      | 4.2.2.c Microwave Model Measurements                       |     |

|      |      | 4.2.2.d Summary and Conclusions                            | 67  |

|      |      | 4.2.3 Micromachined "In-Line" Packaged Circuits            |     |

|      |      | 4.2.3.a Self-Packaged Circuit Characterization             | 69  |

|      |      | 4.2.4 High Frequency Circuit Designs with In-Line Packages | 75  |

|      |      | 4.2.4.a Short-End Tuning Stubs                             | 75  |

|      |      | 4.2.4.b Open-End Tuning Stubs                              | 75  |

|      |      | 4.2.4.c Stepped Impedance Filter                           |     |

|      |      | 4.2.5 Micromachined Conformally Packaged Circuits          | 86  |

|      |      | 4.2.5.a Microwave Detector Mount                           | 87  |

|      |      | 4.2.5.b Double Right-Angle Bends                           | 95  |

|      | 4.3  | Summary and Conclusions                                    |     |

| V. N | MICI | ROMACHINED MICROSTRIP ANTENNAS                             | 102 |

|      | 5.1  | Introduction                                               | 102 |

|      | 5.2  |                                                            |     |

|      |      | 5.2.1 Transmission Line Model                              |     |

|      |      | 5.2.2 Modal-Expansion Cavity Model                         |     |

|      | 5.3  | Antenna Characterization                                   |     |

|      |      | 5.3.1 Low Frequency Antenna Design                         |     |

|      |      | 5.3.2 High Frequency Antenna Design                        |     |

|      | 5.4  |                                                            |     |

| VI.  | CON  | ICLUSIONS AND FUTURE WORK                                  | 124 |

|      | 6.1  | Conclusions                                                | 124 |

|      |      | Future Work                                                | 126 |

| APPENDICES   | 130 |

|--------------|-----|

| BIBLIOGRAPHY | 143 |

# LIST OF FIGURES

# <u>Figure</u>

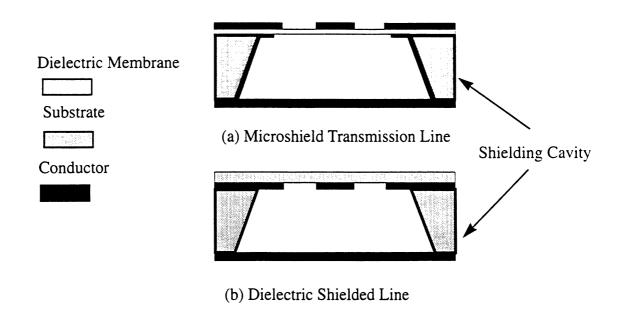

| 2.1  | Novel Geometries for Microwave and Millimeter-wave Technology. (a) Dielectric membrane supported transmission line, called the microshield. The metal conductors are supported by the membrane and a lower shielding cavity is below the conducting line. (b) Dielectric shielded line has conductors supported by the substrate while a shielding cavity is mounted above the conducting line. | 8  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

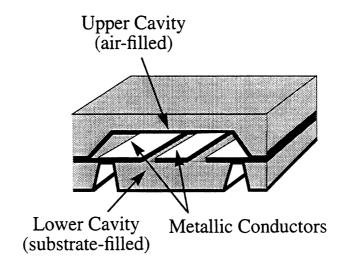

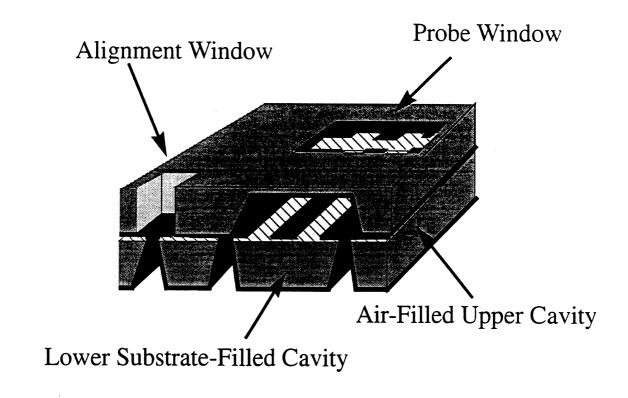

| 2.2  | Self-Packaged Circuit Topology. Constructed out of two silicon substrate wafers. The upper wafer has an air-filled cavity that is mounted over the metallic conductors. The bottom wafer has a silicon-filled cavity is defined by the sidewalls of the v-grooves below the outer conductors.                                                                                                   | 8  |

| 2.3  | The probe window needed to measure a circuit on-wafer.                                                                                                                                                                                                                                                                                                                                          | 14 |

| 2.4  | Photograph of the circuit with the single-strip cavity over the circuits                                                                                                                                                                                                                                                                                                                        | 17 |

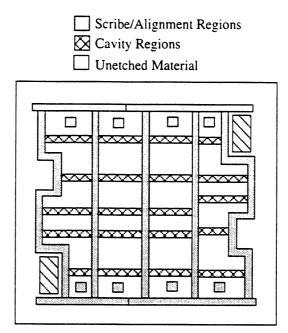

| 2.5  | This represents the upper cavity wafer for the single strip cavity approach shown in Figure 2.4. The Crossed areas represent the region where the cavity is formed. The Hatched are is where the etch rulers are incorporated. Finally the dark regions are where the cavity strip it detached from the larger wafer area using chemical scribing.                                              | 18 |

| 2.6  | Completely shielded micropackaged circuit with lower and upper wafer alignment                                                                                                                                                                                                                                                                                                                  | 21 |

| 2.7  | Etching profile of the probe window area and the cavity region                                                                                                                                                                                                                                                                                                                                  | 23 |

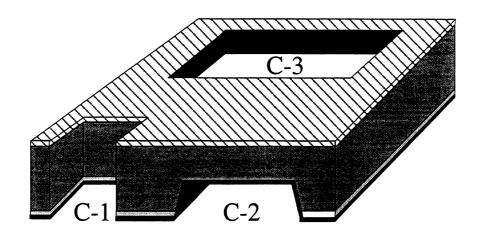

| 2.8  | Upper Wafer Development. A. Probe windows and alignment marks (A-1) are etched from both sides while the upper cavity (A-2) is etched from one side only. B. The upper cavity is then metallized. C. The upper wafer sectional view after processing with the alignment marks (C-1), upper cavity (C-2) and the probe window (C-3).                                                             | 25 |

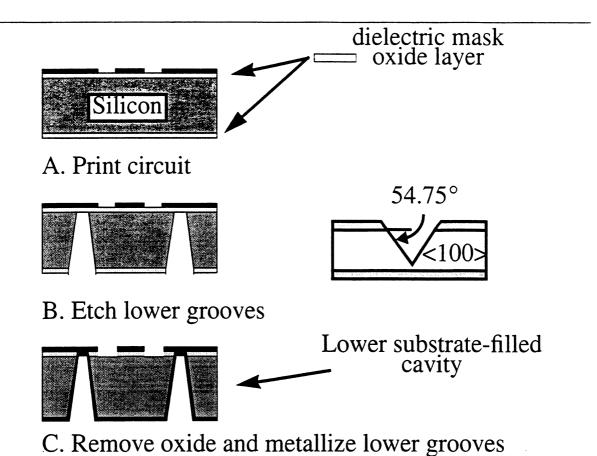

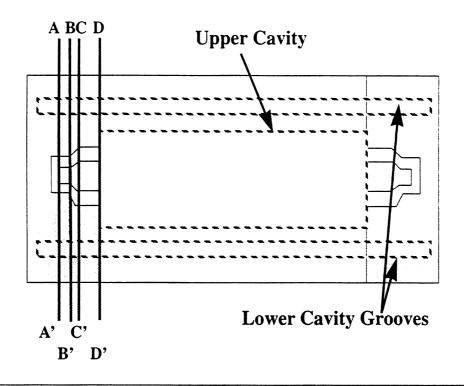

| 2.9  | Lower Wafer Development. A. Transmission lines are printed on the top surface. B. Lower cavity is formed by etching v-grooves. C. Lower cavity grooves are metallized below the line forming direct contact to the upper ground planes.                                                                                                                                                         | 27 |

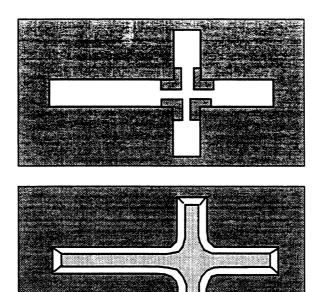

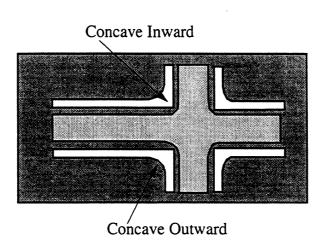

| 2.10 | Cross-Tee Fabrication Layout for Conformal Package Development. The top View shows the effect of etching the upper cavity with compensation. The etched depth is 350 microns and the corners are slightly curved. Bottom                                                                                                                                                                        |    |

|     | View shows the lower wafer where the white slots represent the section that is opened on top for the dc contact and the dashed line is the section that is etched underneath. The curvature in both of the view result from the concave outward corners                        | 31 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

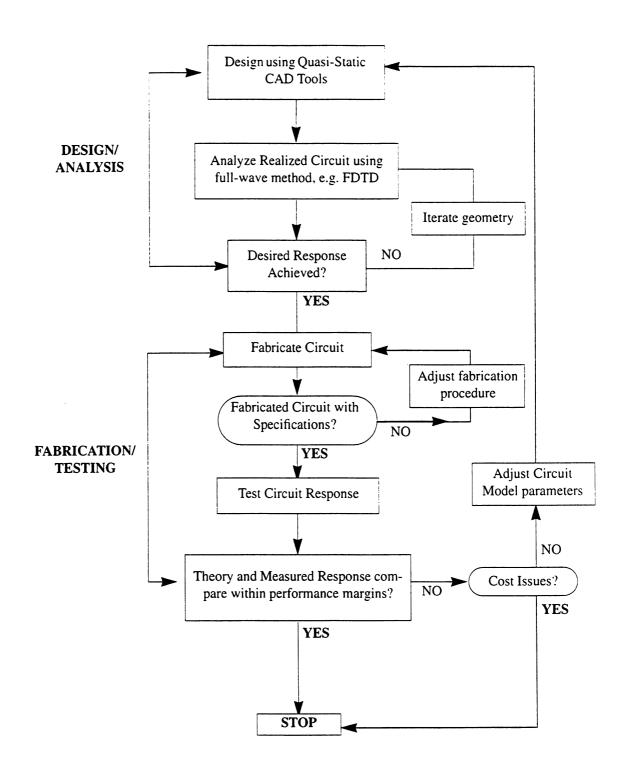

| 3.1 | Design Procedure for Micromachined Circuits                                                                                                                                                                                                                                    | 36 |

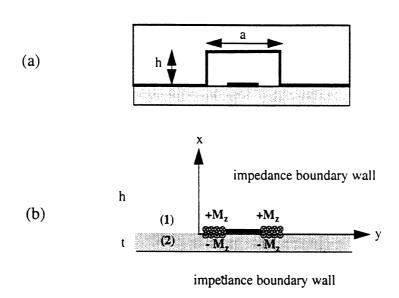

| 3.2 | Half-Shielded geometry of Coplanar Waveguide Circuit and the Equivalent current representation for modeling using Space Domain Integral Equation.                                                                                                                              | 39 |

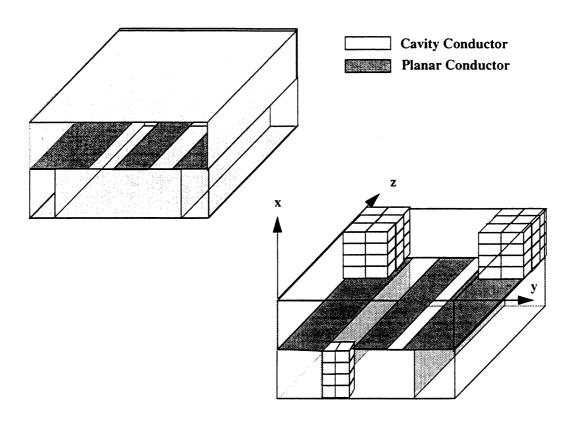

| 3.3 | Illustration of the discretization of a shielded circuit using finite difference time domain method. The top view shows the side walls for the self-packaged circuit and the lower view shows random discretizations of with in x, y, and z directions with the cube elements. | 41 |

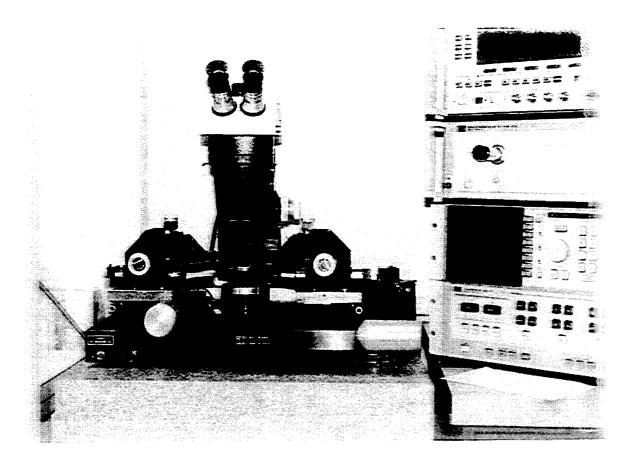

| 3.4 | Photograph of the Network Analyzer and Probe Station                                                                                                                                                                                                                           | 45 |

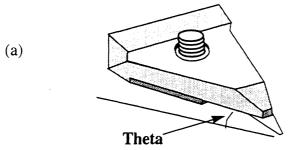

| 3.5 | Cascade Microtech and GGB High Frequency Coplanar Waveguide On-Wafer Probes. (a) Model WPH-150-K with Theta of 11 degrees and probe widest width, w= 4 mm (b) Model 40A-GSG-150-C with Theta of 30 degrees and probe widest width, w= 1.5 mm.                                  | 46 |

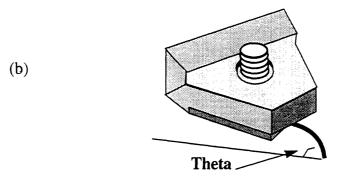

| 3.6 | Thru-Reflect-Line calibration standards for coplanar waveguide based circuit designs.                                                                                                                                                                                          | 49 |

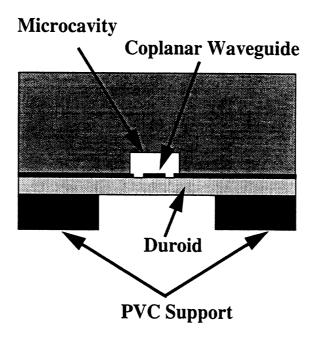

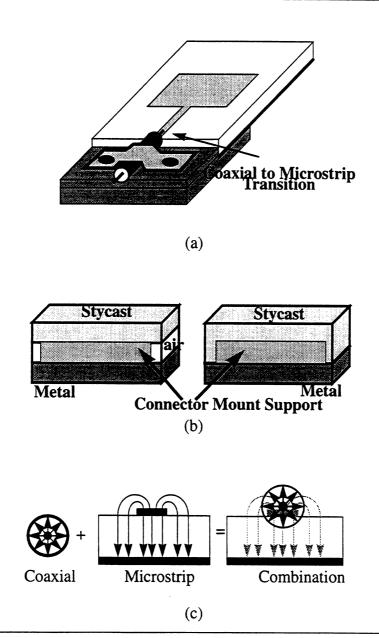

| 4.1 | Microwave Shielded Transmission Line Structure made of an aluminum block mounted over the planar circuit on duroid substrate having er = 2.2. The substrate is supported by a PVC block that has been cored out in the middle.                                                 | 61 |

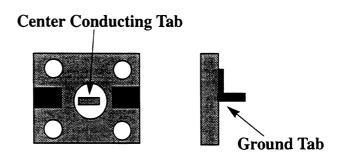

| 4.2 | Illustration of the modified conducting tab to connect the coaxial connector to the coplanar waveguide transmission line.                                                                                                                                                      | 64 |

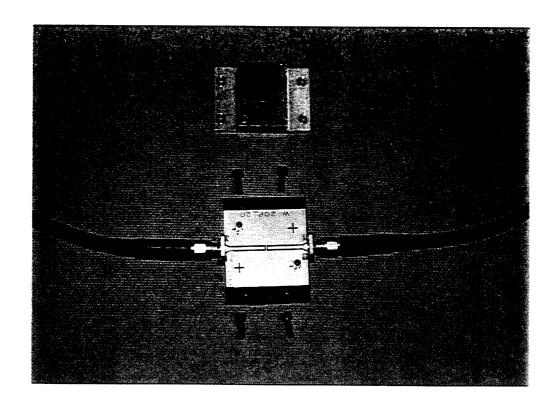

| 4.3 | Photograph of the Microwave Model of the Half Shielded Transmission Line                                                                                                                                                                                                       | 65 |

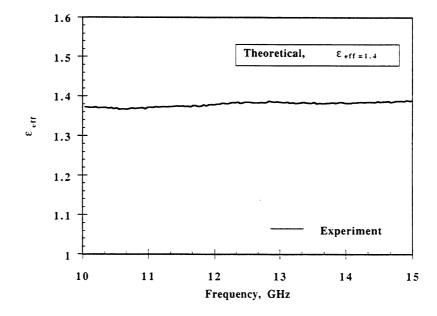

| 4.4 | Effective Dielectric Constant of the Microshield Microwave Model. Graphs shows the calculated effective dielectric constant which was determined theoretically to be 1.4                                                                                                       | 66 |

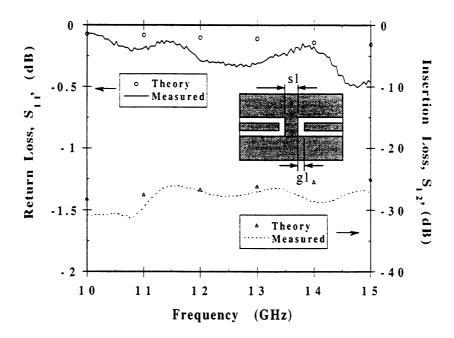

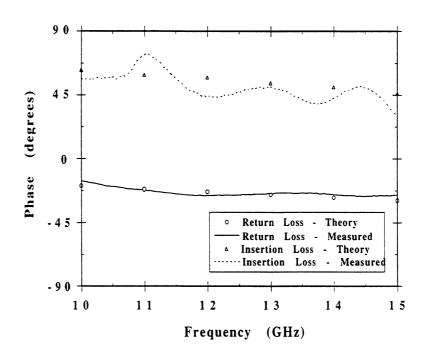

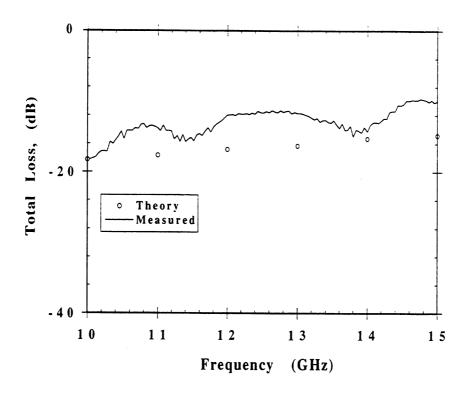

| 4.5 | Two Coupled Open End Line Scattering Parameter Magnitude and Phase (S1=20 mils and g = 10 mils)                                                                                                                                                                                | 68 |

| 4.6 | Two Coupled Open-End Line Radiation Loss Factor, (S1=20 mils and g = 10 mils)                                                                                                                                                                                                  | 69 |

| 4.7 | Dimensions for the completely shielded micropackaged circuit in microns                                                                                                                                                                                                        | 70 |

| 4.8 | Various transitions of a completely shielded micropackaged circuit used for on-wafer robing calibration                                                                                                                                                                        | 71 |

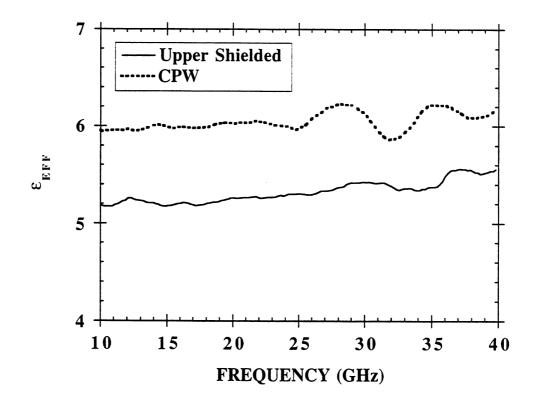

| 4.9 | Effective dielectric constant for an upper shielded and open CPW through line                                                                                                                                                                                                  | 72 |

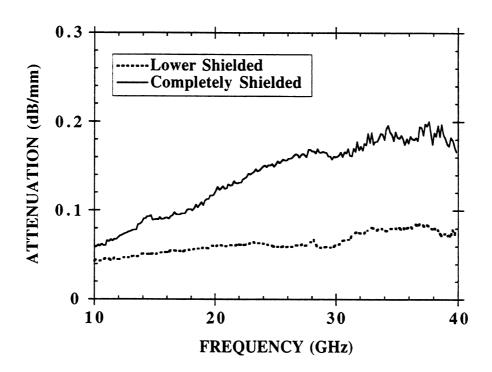

| 4.10 | Attenuation constant for a completely shielded and lower shielded through line                                                                                                                                                                                                                           | 73 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

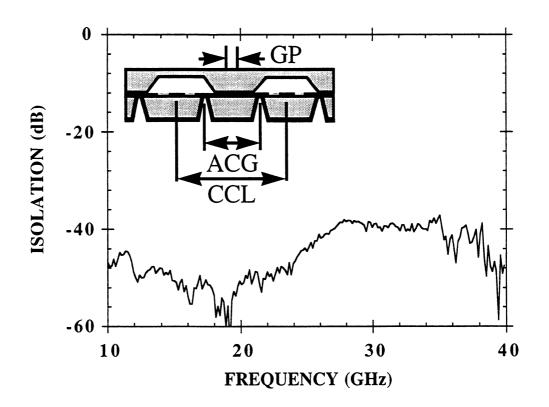

| 4.11 | Isolation response between two completely shielded delay lines, where delay lines 1 and 2 are 3732 and 3242 microns, respectively. These lines have adjacent ground planes (GP), adjacent channel grooves (ACG) and center conducting lines (CCL) separated by 836, 1330 and 2546 microns, respectively. | 74 |

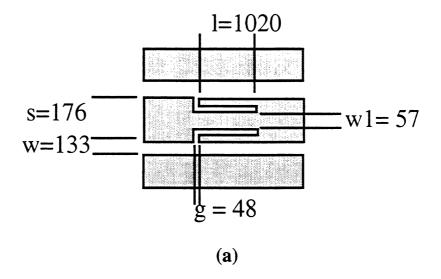

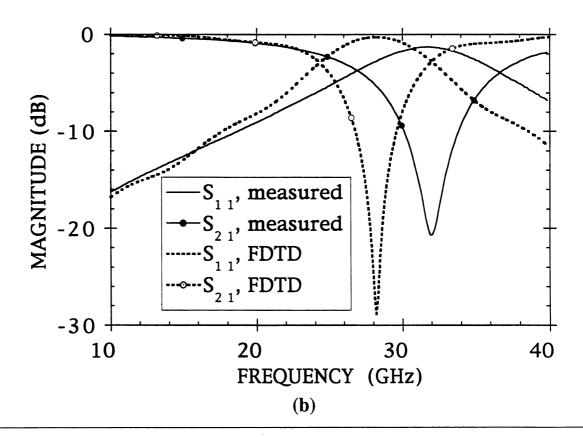

| 4.12 | (a) Series short-end tuning stub dimensions in microns. (b) Comparison between FDTD model and measured results for reflection (S11) and transmission (S21) coefficients of a completely shielded short-end tuning stub in the lower view.                                                                | 76 |

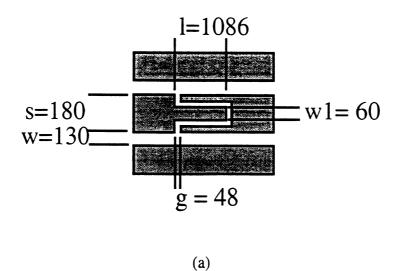

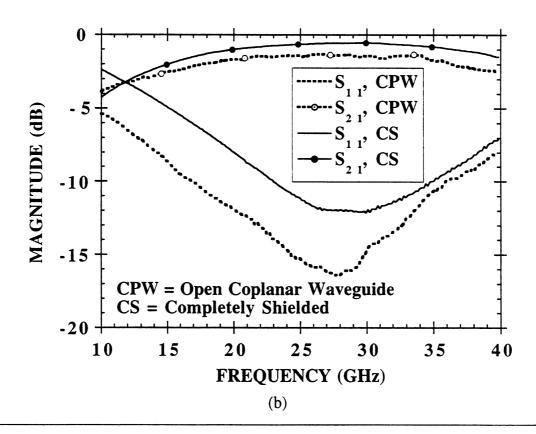

| 4.13 | (a) Series open-end tuning stub circuit with dimensions in microns. (b) Comparison of reflection (S11) and transmission (S21) coefficients between open and completely shielded CPW environments of an open-end series stub. in the bottom view.                                                         | 77 |

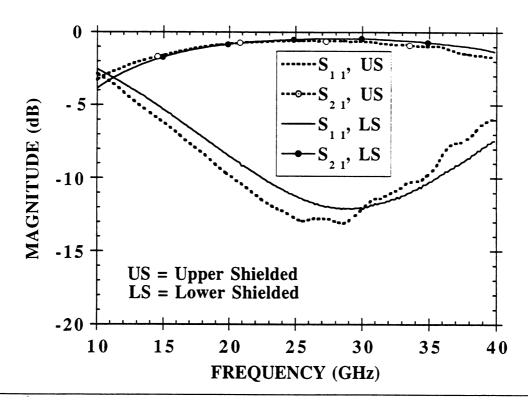

| 4.14 | Comparison of reflection (S11) and transmission (S21) coefficients between upper and lower shielded CPW environments for an open-end series stub.                                                                                                                                                        | 79 |

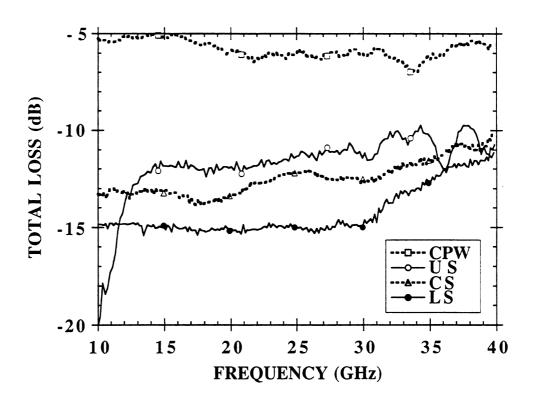

| 4.15 | Loss comparison of an open-end series stub in open (CPW), upper (US), lower (LS) and completely shielded (CS) environments                                                                                                                                                                               | 80 |

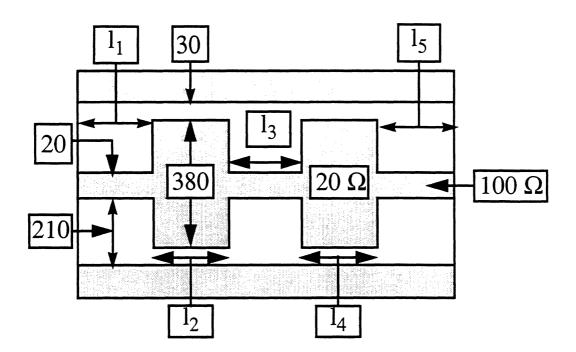

| 4.16 | Dimensions of a 5-section stepped impedance lowpass filter having low impedance sections of 20 ohms and high impedance sections of 100 ohms                                                                                                                                                              | 81 |

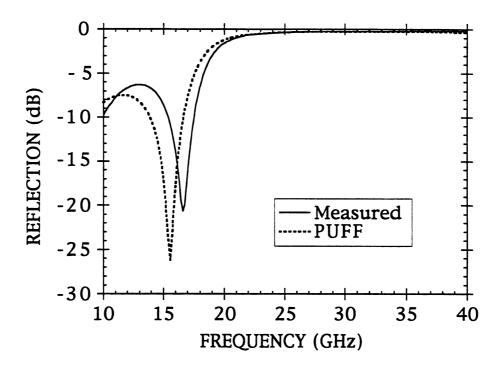

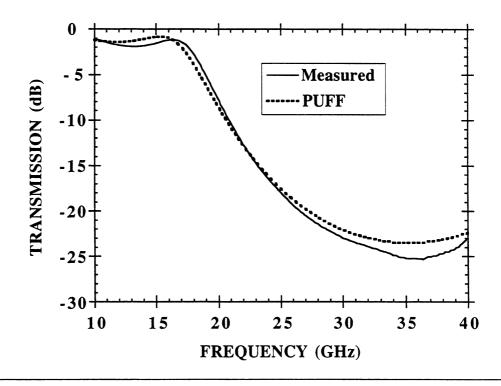

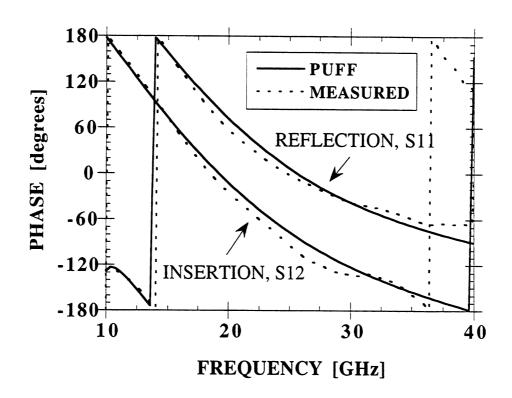

| 4.17 | Comparison of reflection and transmission coefficient between the PUFF model and measured results for a 5-section stepped impedance lowpass filter.                                                                                                                                                      | 82 |

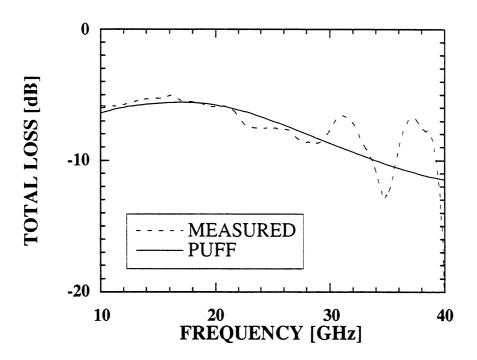

| 4.18 | Loss comparison between the PUFF model and measured response for a 5-section stepped impedance lowpass filter.                                                                                                                                                                                           | 83 |

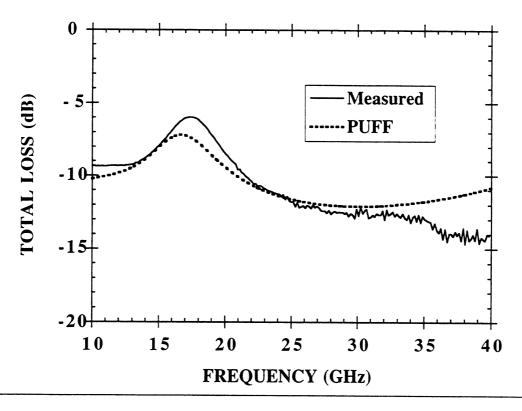

| 4.19 | Seven-section stepped impedance filter where all dimension are in microns                                                                                                                                                                                                                                | 84 |

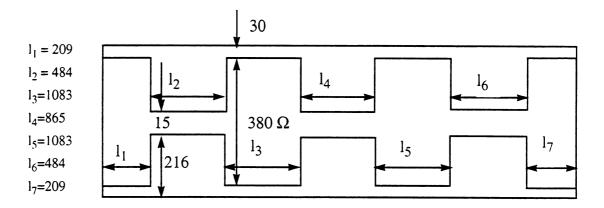

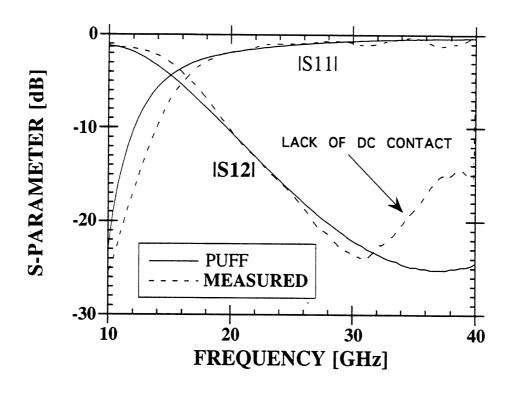

| 4.20 | Performance of a seven-section stepped impedance filter without dc contact                                                                                                                                                                                                                               | 85 |

| 4.21 | Loss Performance for the seven-section stepped impedance filter without dc contact between the planar line ground and the lower shield.                                                                                                                                                                  | 86 |

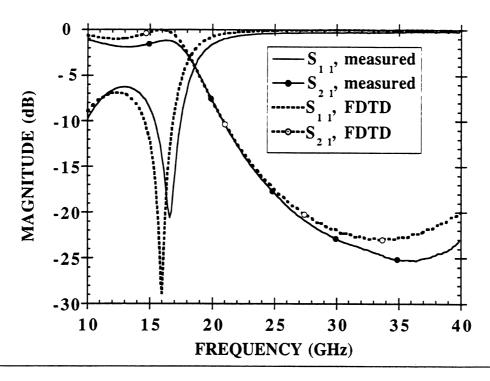

| 4.22 | Comparison between the FDTD model and measured results for reflection (S11) and transmission (S21) coefficients of a 5-section stepped impedance lowpass filter.                                                                                                                                         | 87 |

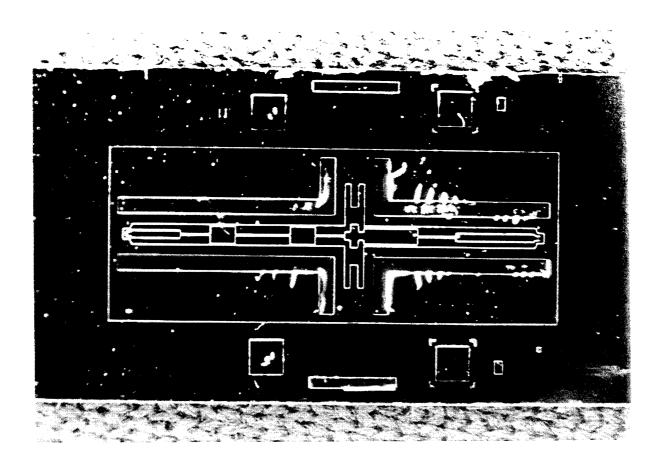

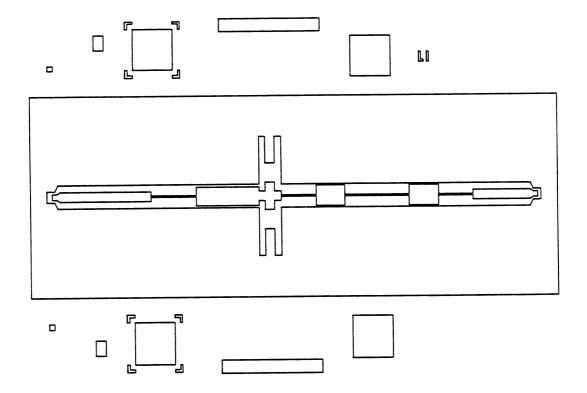

| 4.23 | Picture of the micromachined diode mounting planar circuit                                                                                                                                                                                                                                               | 89 |

| 4.24 | Photograph of the micromachined detector circuit                                                                                                                                                                                                                                                         | 91 |

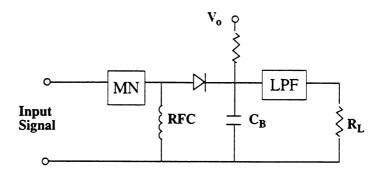

| 4.25 | General design scheme for a detector circuit, where MN is the matching                                                                                                                                                                                                                                   |    |

|      | blocking capacitor.                                                                                                                                                                                                                                                                                                                                              | 92  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.26 | Top view of the planar circuit layout of the detector mounting structure                                                                                                                                                                                                                                                                                         | 93  |

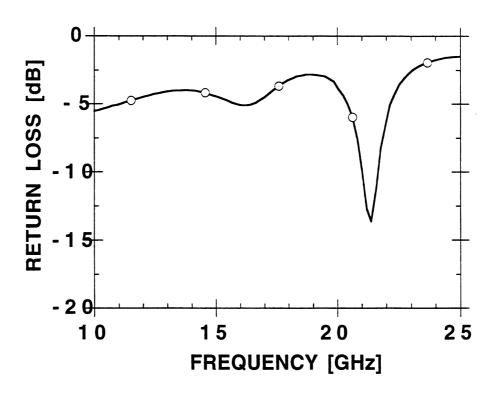

| 4.27 | Passive circuit response of the detector mounting structure                                                                                                                                                                                                                                                                                                      | 94  |

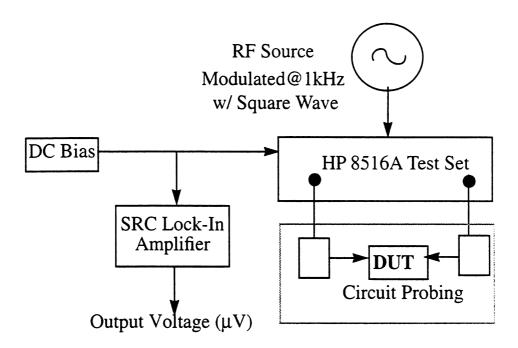

| 4.28 | Measurement System for the Detector Mounting structure                                                                                                                                                                                                                                                                                                           | 95  |

| 4.29 | Predicted versus computed responsivity of the micromachined detector circuit. The individual data points represent the measured results for the lower half-shielded and completely shielded structure                                                                                                                                                            | 96  |

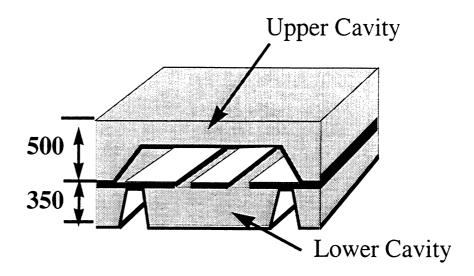

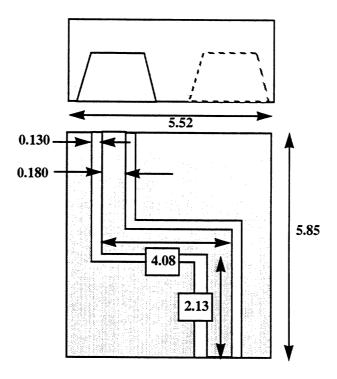

| 4.30 | Illustration of the double right angle bend. Top drawing shows a front view of the cavity region. Bottom view shows a top view of the circuit geometry. All dimensions are in millimeters.                                                                                                                                                                       | 97  |

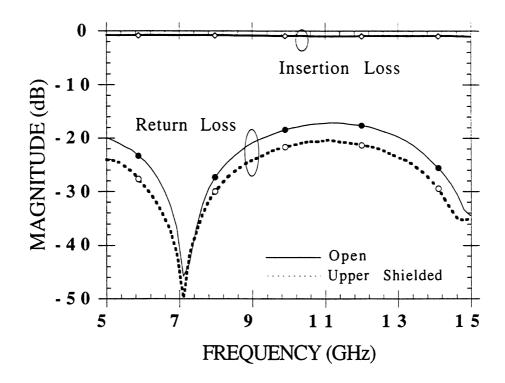

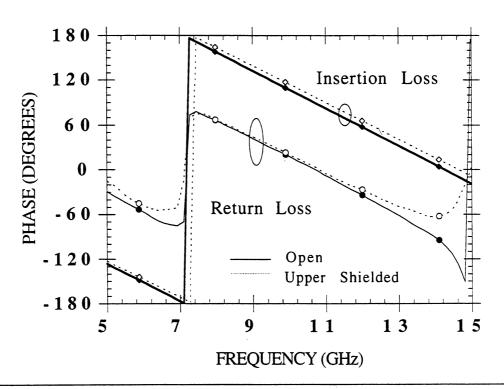

| 4.31 | Performance of the double right angle bend for the open and upper shielded geometry.                                                                                                                                                                                                                                                                             | 98  |

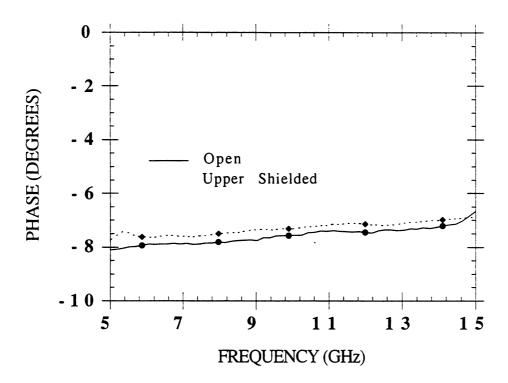

| 4.32 | Computed Total Loss for the double right angle bend shown in Figure 4.26.                                                                                                                                                                                                                                                                                        | 99  |

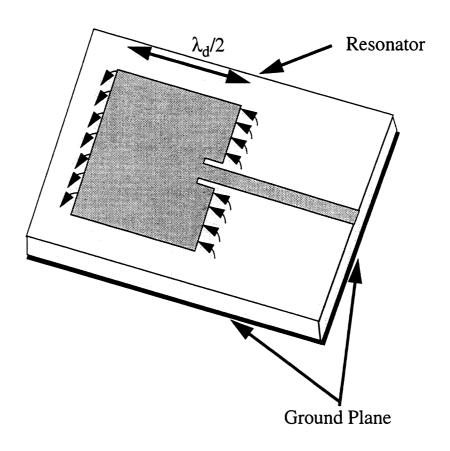

| 5.1  | Microstrip Patch Antenna.                                                                                                                                                                                                                                                                                                                                        | 104 |

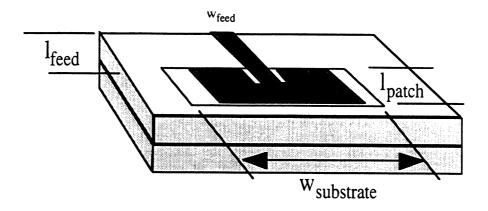

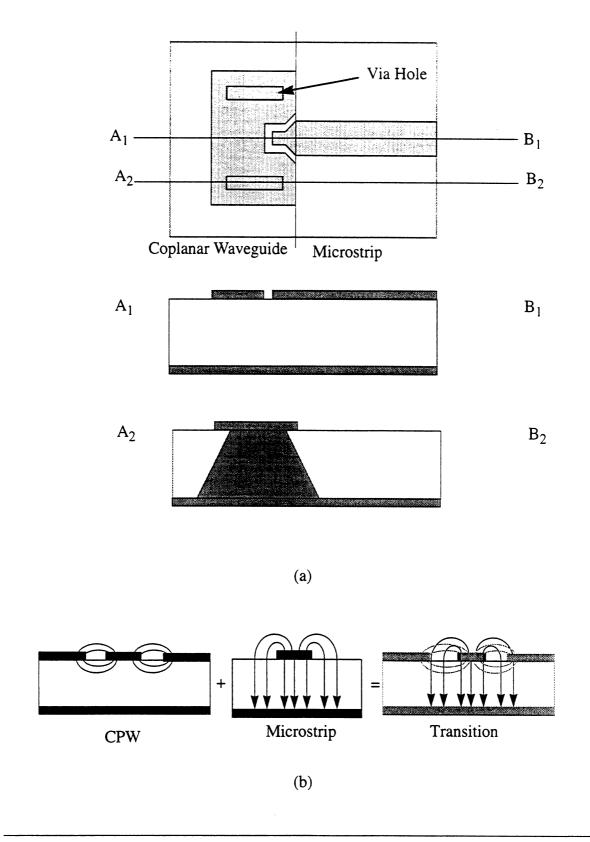

| 5.2  | Illustration of the micromachined patch antenna configuration. (a) The micromachined patch configuration where the specific parameters are defined in Figure 2. (b) The area below the patch shows where the material has been removed laterally to form an air/dielectric cavity                                                                                | 109 |

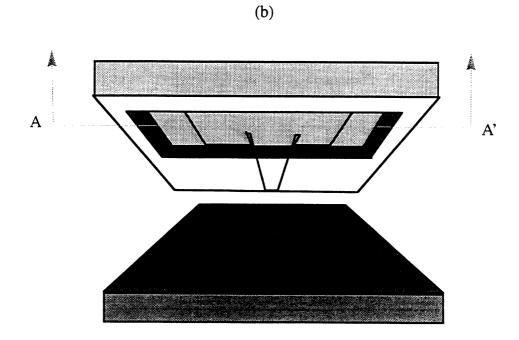

| 5.3  | Microwave Model circuit dimensions for the Microstrip Patch Antenna on Stycast, dielectric constant =12.                                                                                                                                                                                                                                                         | 110 |

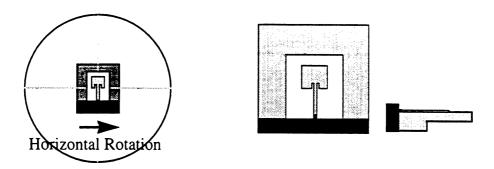

| 5.4  | Microwave Model Measurement apparatus                                                                                                                                                                                                                                                                                                                            | 111 |

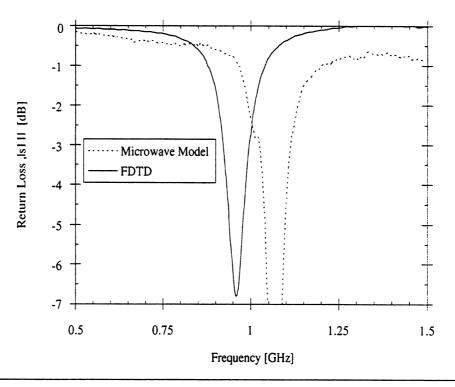

| 5.5  | Microwave model results.                                                                                                                                                                                                                                                                                                                                         | 112 |

| 5.6  | The diagram is a side view of the patch cross-sectional area and the table shows the circuit dimensions of the patch antenna shown in Figure 1                                                                                                                                                                                                                   | 113 |

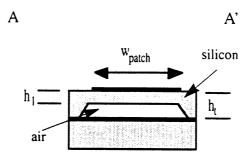

| 5.7  | Transition from cpw to microstrip. (a) Top view of CPW transition to microstrip. (b) Field distribution between two planar circuits                                                                                                                                                                                                                              | 115 |

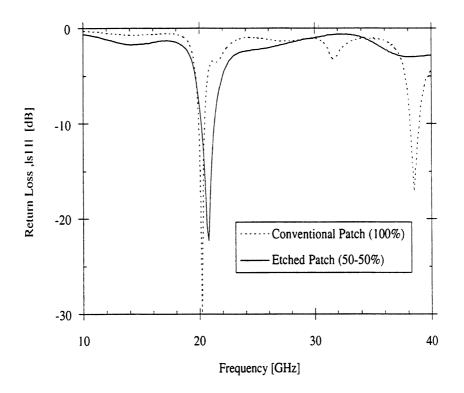

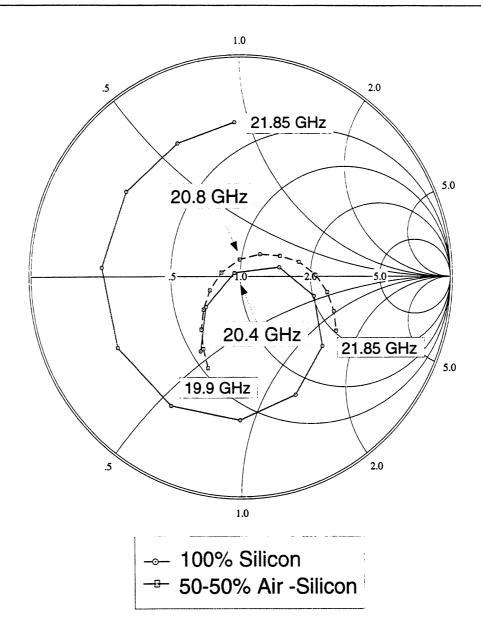

| 5.8  | Measured results for the patch antenna on conventional 100% silicon and 50-50% silicon-air substrate.                                                                                                                                                                                                                                                            | 116 |

| 5.9  | The Smith Chart illustrates the improved bandwidth between the micromachined antenna and the conventional one.                                                                                                                                                                                                                                                   | 117 |

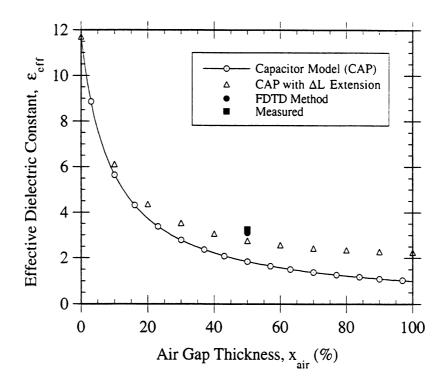

| 5.10 | Plot of the effective dielectric constant for mixed substrates.                                                                                                                                                                                                                                                                                                  | 118 |

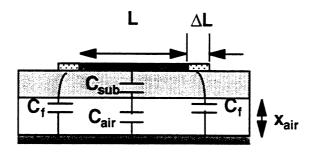

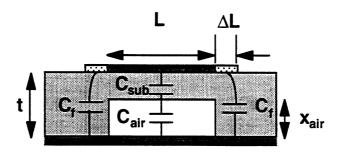

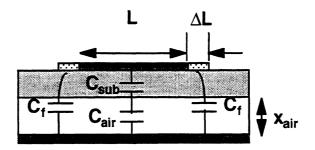

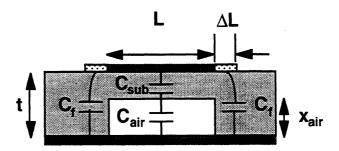

| 5.11 | The patch antenna and equivalent circuit model used in the capacitor model. Cf is the fringing capacitance, Csub is the substrate capacitance, Cair is the capacitance due to the air, t is the total distance between the plates, xair is the height of the air region, L is the resonant length of the antenna and DL is the open end effect extension length. | 119 |

| 5 12 | Test Fixture apparatus for the pattern measurements.                                                                                                                                                                                                                                                                                                             |     |

| 5.13 | Radiation Pattern of the Micromachined antenna                                                                                                                                                                                                                                                                                                                   | 122 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

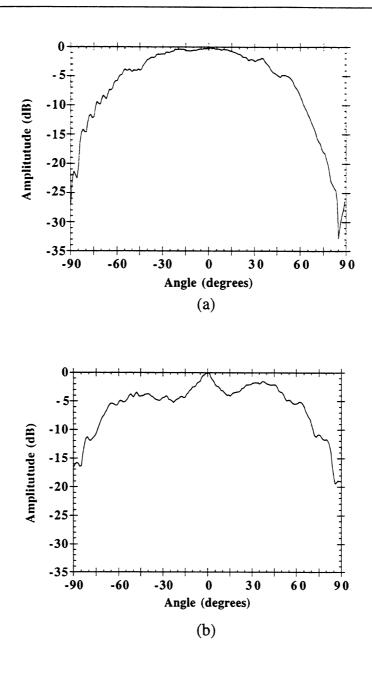

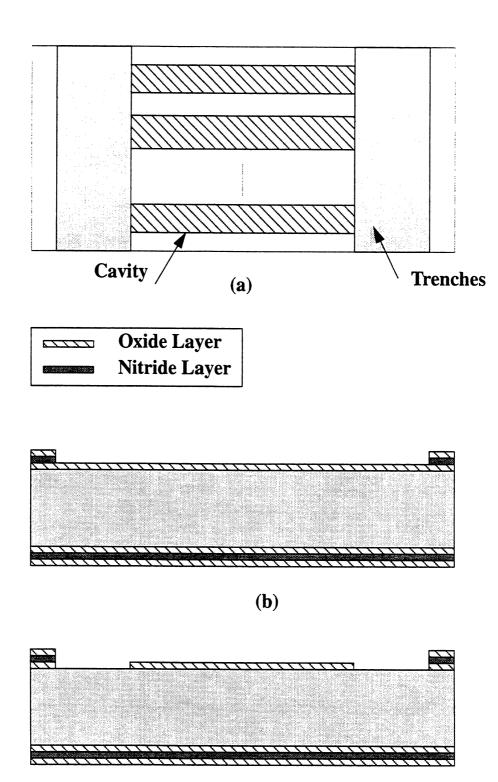

| A.1  | (a) Top View of the cavity wafer layer scheme. (b) The removal of the oxide and nitride dielectrics to transfer the mask pattern onto the wafer. (c) Lower oxide removed from the trench regions while the oxide remains in the cavity region.                                                                                                                   | 132 |

| A.2  | (a) Top view of a section of the upper cavity wafer where the shaded sections correspond to the cavity and trench regions labeled. (b) The etch profile for the trench region, partly through the wafer. (c) The etched region completely through the wafer with the cavity region etch to the desired depth.                                                    | 134 |

|      | •                                                                                                                                                                                                                                                                                                                                                                | 134 |

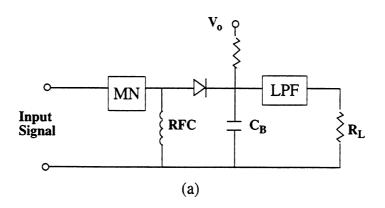

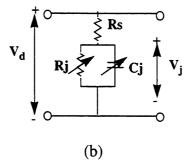

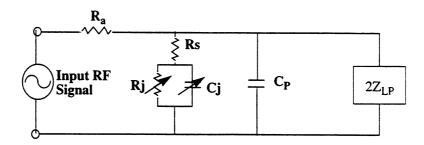

| C.1  | General design scheme for a detector circuit, where MN is the matching network, LPF is a lowpass filter, RFC is the RF choke, and CB is the blocking capacitor. (b) The diode equivalent circuit.                                                                                                                                                                | 136 |

| C.2  | Equivalent circuit the detector circuit for a single diode elements.                                                                                                                                                                                                                                                                                             | 137 |

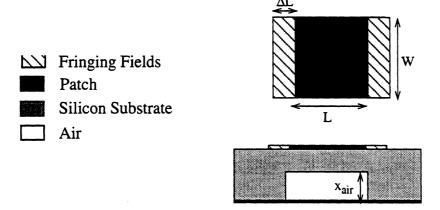

| D.1  | Micromachined Patch Antenna used in the capacitor model                                                                                                                                                                                                                                                                                                          | 139 |

| D.2  | The patch antenna and equivalent circuit model used in the capacitor model. Cf is the fringing capacitance, Csub is the substrate capacitance, Cair is the capacitance due to the air, t is the total distance between the plates, xair is the height of the air region, L is the resonant length of the antenna and DL is the open end effect extension length. | 140 |

# LIST OF TABLES

| т | ah | ما |

|---|----|----|

|   | aυ | 10 |

|   |    |    |

| 4.1 | Cross Sectional Dimensions of Shielded Circuits | 70  |

|-----|-------------------------------------------------|-----|

| 4.2 | Actual Circuit Dimensions                       | 81  |

| 5.1 | Microwave Model Dimensions                      | 110 |

| 5.2 | Dimensions                                      | 113 |

# LIST OF APPENDICES

# <u>Appendix</u>

| A. FABRICATION OF MICROMACHINED CIRCUITS                  | 131 |

|-----------------------------------------------------------|-----|

| B. BILAYER METALLIZATION PROCESS                          | 135 |

| C. DERIVATION OF SYSTEM RESPONSIVITY                      | 136 |

| D. EFFECTIVE DIELECTRIC CONSTANT DETERMINATION BASED ON A |     |

| CAPACITOR MODEL FOR MIXED SUBSTRATES                      | 139 |

#### **CHAPTER I**

## **INTRODUCTION**

## 1.1 PACKAGING IN HIGH FREQUENCY APPLICATIONS

Since the 1950's, packaging has played an increasing important role in the advancement and direction of circuit designs in the electronics industry. Packaging for low frequency (LF) circuit applications have advanced significantly to accommodate high volume cost effective circuits used in commercial applications below 1 GHz. On the other hand, packaging for high frequency (HF) applications has experienced limited growth due to high performance, low volume design requirements. Electrical performance improvements are significantly impacted by the present limitations in HF package development. Processing technologies used to make LF circuits and design/analysis (D/A) techniques used in HF circuits can be combined to realize novel packaging concepts for planar monolithic and microwave integrated circuits (MICs and MMICs). At high frequencies, research on optimum device and component performance were given the highest priority. This resulted in the development of sophisticated D/A tools and an extensive circuit design library. In the last few years, packaging effects are now identified as one of the most important parameters affecting substantial performance improvements in many HF circuits.

Several packaging approaches have been implemented thus far in high frequency applications. Multi-function circuits and arrays use STRATEDGE<sup>TM</sup> [1] and WAFFLE-LINE [3] for example to accommodate MIC and MMIC designs. Quartz hermetic pack-

ages have been successfully developed for multi-chip-modules (MCM) at millimeter wave frequencies [2]. Common to each of the aforementioned approaches is the incorporation of packages at the last phase of product development. Since package integration does affect circuit performance, several design iterations are usually implemented before design requirements are satisfied. Monolithic packaging is a novel approach that provides integration at the circuit design level which offers several advantages. First, the packaging parameters extend the number of design variables to enhance design flexibility. Second, circuit evaluation is inclusive since the package has been integrated simultaneously in the fabrication procedure.

Silicon micromachining techniques can be used toward the development of monolithic packages. To date several micromachined circuits which consist of antenna elements, TM<sub>01</sub> waveguide structures, and planar designs have been implemented using this technique. Rutledge et. al [5] introduced a pyramidal horn antenna with a planar dipole integrated monolithically onto a thin membrane dielectric in the millimeter-wave region. Soon thereafter, one waveguide structure was developed using similar techniques [10] for W-band applications. Since that time, high performance planar transmission lines such as the microshield have been investigated [6] using membrane supported technology.

The planar circuits can be improved significantly by reducing loss mechanisms common to many planar topologies: (a) dielectric and (b) radiation loss. Complete elimination of dielectric losses is achieved through substrate removal that produces planar lines supported on membranes. Demonstrations have been shown for components that include filters to power dividers for frequencies between tens of gigahertz (X-Band) to hundreds of gigahertz (above W-Band). In fact, an extensive collection of planar lowpass to bandpass filters exist based on tuning stubs [6], couples lines [7-8], and lumped elements[9]. An alternative that reduces the loss mechanisms associated with the dielectric can be achieved

<sup>1.</sup> Membrane is a tri-dielectric layer consisting of silicon dioxide/ silicon nitride/ silicon dioxide having thicknesses of 7500Å/3500Å/4500Å.

by controlling the excitation of substrate modes in the form of surface waves and higher order modes.

Both radiation and dielectric loss are addressed in the development of self-packages that incorporate a monolithic shielding package around planar circuit elements using micromachining techniques. Typical to many planar circuits are the excitation of substrate modes, parasitic radiation and package resonances. Together, each of these mechanisms can severely degrade the electrical performance of planar circuits. As the frequency of operation increases to millimeter waves and above, the use of conventional planar transmission lines is diminished since the losses are very high in comparison to the signal strength propagating though the circuit. In order to benefit from existing circuit designs to develop high frequency systems, novel solutions are required to minimize the aforementioned unwanted properties that are inherit to conventional planar designs.

To reduce substrate modes effects, the formation of the lower cavity regions isolates the dielectric medium propagating the undesired mode from the continuity in the substrate Once metallized this shielding can reduce or eliminate unwanted electromagnetic effects that oftentime decreases the amount of useful power available in the circuit. This dimension can be chosen such that any resonance occurs outside of the desired frequency range of operation. Since this type of excitation is detrimental for both planar circuit and antennas elements, use of silicon micromachining technology can open an entirely new arena in high frequency design with an unlimited number of potential applications. To address radiation issues, individual shielding to circuits can offer improved circuit performance by isolating the circuit from neighboring circuits and by reducing interference of random electronic signals.

In addition to decreasing radiation, this approach addresses a number of problems associated with high frequency package design. There are a number of problems that arise from poorly designed electronic packages at high frequencies. One of them, mentioned above, is caused from parasitics in planar transmission lines while the other is associated

with the package layout and configuration. Planar circuits are lightweight, low cost, and conformal and many are easily integrable with active elements. Unwanted parasitics, however, are the cause of many problems in circuit performance and occur whenever discontinuities arise in a circuit design to cause radiation. Package layout and the configuration issues on the other hand influence proximity (or near neighbor) coupling and package resonances that also contribute to performance degradation. Resolution to these problems can be addressed in a variety of ways, either through improved circuit designs or though packaging. The investigation of this novel packaging concept is the subject of the work presented herein.

#### 1.2 OVERVIEW

In this work, a novel approach is proposed that considers the package as an additional parameter to the circuit design and allows monolithic integration with the circuit. This approach presents for first time a monolithic package that has been extensively characterized for microwave and millimeter wave applications. With the use of advanced processing techniques that have been traditionally associated with sensor technology and high frequency circuit design techniques, this packaging concept can be realized and applied to a number of basic circuits that are commonly used in many high frequency applications.

This dissertation is organized into two main sections, the development/characterization and evaluation of the micromachined self-package and circuits. The packaged configuration is described by its cross-sectional geometry and categorized as partial or completely shielded. Next, extensions of this two dimensional topology can be in a straight (linear) or bending (non-linear) direction which is referred to as "in-line" or "conformal" packaging. The conformal package can also be used with multiple input paths to a circuit. Three techniques are required to completely develop and characterize the structure: fabrication, measurement and theoretical.

Chapter 2 presents the fabrication techniques required to develop this structure and various phases of the self-packaged circuit topology are discussed with the merits and problems associated with each design. In Chapter 3, the measurement and theoretical techniques utilized to characterize the package and circuit are discussed with a summary of the factors contributing to measurement error. Next, demonstrations of the concept is applied for various packaging configurations.

The results presented in Chapter 4 indicate the performance of stubs and filters indeed show improved performance over conventional open structures of similar design due to the reduction of parasitic radiation. Basic designs such as a detector circuit and double right angle bend have also been evaluated to show the flexibility of using micromachining as a conformal package. While many issues of planar circuit performance are significantly impacted by the excitation of substrate modes, this packaging approach has been extended to include planar radiating elements such as the microstrip patch. In Chapter 5, the micromachining approach is applied to an antenna problem where the effective dielectric constant is reduced underneath the antenna while maintaining the feeding networks on high index substrates for design compactness. Chapter 6 concludes this work with a summary and suggestions for future work in this area.

#### **CHAPTER II**

### DEVELOPMENT OF MICROMACHINED PACKAGES

#### 2.1 INTRODUCTION

For millimeter and sub-millimeter wave applications, system development is required with transmission and radiating elements as well as sources and respective circuitry in order to communicate with existing hardware. Waveguide and aperture based systems have been successfully implemented at these frequencies since these structures only require scaling of dimensions and rely on existing manufacturing technologies. An alternative approach for an aperture-based system that was observed in the late eighties were a monolithic integrated horn array [5] and a monolithic waveguide structure [10]. At that time, one of the main limiting factors in the realization of high frequency systems was the availability of adequate planar transmission line geometries. Since loss mechanisms found in traditional planar circuits in the form of radiation and parasitic coupling cause extreme performance degradation at higher frequencies, a need existed for exploration and development of novel circuit geometries that overcome these mechanisms. This motivated a large scale investigation into alternative methods that offer improved characteristics. One approach focuses on the use of silicon micromachining techniques to provide an alternative method for the development of such geometries and is the topic of this work.

In many circuit and array applications, design flexibility is extremely important therefore novel transmission line geometries that offer generic shapes and an increase design parameters are desirable in order to develop circuits with optimum performance. Many limitations observed in specific circuit designs can be attributed to the inherit behavior of a planar line along with those effects caused by the surrounding environment. Existing planar lines, such as microstrip and stripline, have well known electromagnetic behavior. As a result, extensive geometry libraries are currently available for circuit realization. In recent years, however, monolithic integration of active and passive elements motivated interest in the use of coplanar waveguide lines since these provide more flexibility in accommodating design requirements. While each of the above lines provides certain advantages to high frequency applications, all of these suffer from losses associated with the dielectric and conductor, which ultimately limits their use for frequencies at and above the millimeter wave region. In addition, external factors associated with proximity coupling to neighboring circuits and electronic package resonances can also result in detrimental effects on electrical performance.

Circuits that geometrically and physically resemble coplanar transmission line technology and have cavity shielding on one side of the circuit were first proposed by Katehi and Dib [10-12] in 1991. In a comparison to the conventional coplanar waveguide (CPW) in an open medium, these geometries, which can exist with or without the substrate underneath the conducting line (Figure 2.1a), offer the advantage of lower radiation, thereby providing an alternative topology with improved performance. Of the two proposed solutions, one performs optimally as a result of the removal of material underneath the conducting line. This eliminates dielectric loss such that a membrane-supported line propagates a purely TEM mode and offers a non-dispersive behavior up to the terahertz frequency range [13]. The other solution is a topology that results in improved performance by providing shielding around the transmission line to form a microcavity (Figure 2.2). This reduces the radiation effects caused by parasitic coupling and substrate mode excitation while providing additional design parameters that can used to enhance circuit design flexibility.

Figure 2.1 Novel Geometries for Microwave and Millimeter-wave Technology. (a) Dielectric membrane supported transmission line, called the microshield. The metal conductors are supported by the membrane and a lower shielding cavity is below the conducting line. (b) Dielectric shielded line has conductors supported by the substrate while a shielding cavity is mounted above the conducting line.

Figure 2.2 Self-Packaged Circuit Topology. Constructed out of two silicon substrate wafers. The upper wafer has an air-filled cavity that is mounted over the metallic conductors. The bottom wafer has a silicon-filled cavity is defined by the sidewalls of the v-grooves below the outer conductors.

In planar circuit designs, this micromachining technology has provided a flexible approach to the development of very low loss transmission lines [13] as well as micropackages that provide self-packaging to individual planar circuit components. Investigation of the latter novel structure, the micropackage, is the primary focus of this dissertation which is intended to address the requirements of low-cost lightweight circuits in applications such as communication systems. In this study of an alternative packaging approach, the following topics are of interest in order to evaluate its potential to high frequency design. The primary issues include:

- characterization of micromachined topologies on CPW based circuits,

- demonstration of the shielding effects on simple high frequency planar elements,

- realization of a package that conforms to the shape and path of the electrical signal line, and

- integration capability with designs that include active elements integrated either hybridly or monolithically.

Before addressing the above topics, however, this chapter will present the evolution of the "self-packaged" circuit shown in Figure 2.2 and will discuss the critical factors associated with the development and fabrication of micropackaged topologies using silicon micromachining.

#### 2.2 MOTIVATION AND OBJECTIVES

In the past, machine milling technology has been the primary method for developing metallic structures such as waveguides and test fixtures. To date, the smallest standard rectangular waveguide produced is WR <sup>1</sup>-3 while custom designs can be as small as WR-1 [13]. While this represents one approach for the development of small cavities that can be

<sup>1.</sup> Rectangular waveguide is denoted WR by the Electronic Industry Association (EIA) and represents the inside width of the rectangular waveguide dimension in english units of mils.

used to shield individual circuit components, there are fundamental limitations to this method regarding product development. As applications require size and space reduction. these metallic structures can add considerably to the overall weight and volume. The fabrication of specific circuit designs using this approach may be limited to low-volume applications, however it requires the cavity and planar circuit to be manufactured then tested separately, followed by additional re-evaluation. This method is extremely time intensive and costly in the fabrication and testing of prototype designs. An alternative approach will be presented in this chapter that addresses the need to develop low-cost lightweight circuits that exhibit improved performance over conventional planar circuits. This exploration focuses on the use of silicon micromachining to implement multiple package topologies that address the requirements of high frequency planar circuit designs.

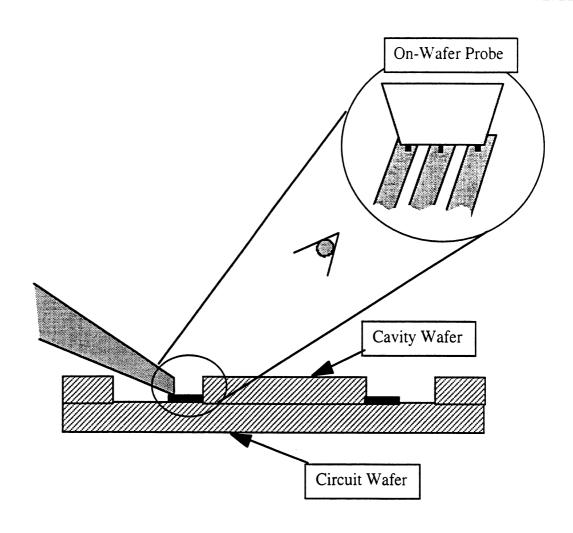

While several factors motivated the investigation of high frequency packaging techniques, planar designs for use in millimeter and submillimeter applications will be tremendously impacted by the outcome. The investigation depends on identifying and addressing fabrication issues as well as circuit performance characterization which must be considered during the initial planning phases of this study. Moreover, accurate evaluation of circuit performance is best obtained using high performance circuits and testing methods. In order to achieve such accuracy, a state of the art on-wafer probing measurement system for high frequency characterization will be employed. The various calibration techniques available will be discussed in Chapter 3, however, it is important to introduce the subject of the measurement tool at this time since it has an essential role in the geometrical evolution of the packaged topologies discussed herein.

High frequency planar circuit characterization results from a combination of good design techniques and accurate measurement techniques. Since many calibration methods rely on the use of several circuit elements which vary in line lengths, a flexible measurement apparatus must be employed. While commercially available test fixtures can be used, the flexibility to measure novel complex three-dimensional structures such as planar cir-

cuits with shielded environments becomes more challenging. Custom-made fixtures may be designed to measure the specific circuit topologies of interest, however this may require additional time for test fixture development and evaluation. This may ultimately impact overall cost depending on the number of design modifications required to meet the circuit requirements. If separate fixtures are needed to accommodate each circuit, for example, many coaxial connectors may be required which can introduce measurement inaccuracies due to unreliable connector repeatability and increased cost.

One simple solution that is both cost effective and very accurate is to use measurement techniques such as on-wafer probing [14] which allow for testing of many circuits on a single wafer. This probing technique is the most accurate method for evaluating large numbers of planar circuits and can accommodate a variety of planar line geometries that have operating frequencies from dc to W-band [15]. Finally, testing time requirements are reduced significantly since the measurements can be made manually or automatically in industrial testing facilities.

Alternative methods for development of potentially inexpensive packaging schemes for high frequency circuits are discussed using fabrication techniques that are standard monolithic and microwave integrated circuits (MICs and MMICs) processing. The following sections highlight the evolution of the "self-packaged" circuit shown in Figure 2.2 starting with the first version of the upper shielded cavity, which is a monolithic version of the machine-milled cavity mount, used to provide an initial understanding of the shielding effects on planar circuits [16]. This micromachined version addresses the monolithic integration of a multiple cavity wafer that is mounted over several circuits. Since the upper shielded circuits exhibit reduced radiation, additional minimization of other unwanted electromagnetic effects, mainly those observed in circuits measured on ground planes, is needed. This reduction of substrate mode excitation occurs with the development of lower shielded circuits that provides isolation between neighboring circuits residing in the same substrate material. Integration of both upper and lower shielded circuits result in the for-

mation of the first "self-packaged" circuit. The discussions will include specifications for each package design and measurement condition requirements, as well as, detailed discussions of the fabrication processes employed to realize the specific three-dimensional geometry. Lastly, current self-packaged configurations [17-18] will be discussed and extensions for the development of simple conformal packages are highlighted. Realization of simple basic planar circuit components that are based on these fabrication procedures are described in the following section and measured data will be presented in Chapter 4 on electrical performance.

## 2.3 GENERAL FABRICATION METHODOLOGY

The micromachined packaged circuits are comprised of a two-silicon (Si) wafer system having a <100> orientation and rely primarily on silicon micromachining processes. In sensor applications, this process is well-established and is frequently utilized in MEM structure development, however, these processes are relatively new to high frequency circuit design. Therefore, a discussion of the fabrication procedures required for the development of micromachined packaged circuits as it pertains to the planar circuit realization and specific cavity formation will be given.

While a variety of transmission line configurations can be used, the circuits in this work are based on coplanar waveguide (CPW) lines since these offer the advantage of having the signal and ground lines on the same plane. The shielding of the circuit is attained by miniature cavities that have been developed monolithically to reside in either or both upper and lower surrounding regions. In general the cavity geometry may consist of air or any dielectric material, however the standard convention used in this work will have air-filled upper cavities located above the planar geometry and substrate filled ones below. Typically high frequency circuits are developed on materials that provide reasonably low loss, therefore the following planar circuits are printed on high resistivity n-type silicon,  $\varepsilon_r = 11.7$ , with resistivity values in the range of 2000-3000 ohm-cm which is ade-

quate to achieve minimal loss effects in the substrate [19]. Since the upper cavity provides grounding to the circuit described, the value of resistivity is less important and are in the range of 6-10 ohm-cm.

While most of the discussions that follow involve the fabrication procedures employed, the factors associated with the testing apparatus will be commented on next since this ultimately influences the circuit design. There are three primary factors, illustrated in Figure 2.3, that influence the accuracy and physical measurement of these circuits in a probe station environment. The first deals with construction of the planar geometry with the shielding cavity while the second and third address excitation of the circuit on the probe station set-up. Configurations having an upper and/or lower cavity region must provide ground plane equalization between the shield and the CPW circuit. As a result the incorporation of mechanisms for the alignment of several wafers is required. In order to measure the circuits, however, access to the shielded region is necessary and achieved by incorporating windows that allow entry of the high frequency probe to the circuit input line. Lastly, transitions between the open and shielded region, which will be discussed in more detail in Chapter 3, are needed for appropriate excitation of the shielded geometry.

The remaining sub-sections concentrate on the evolution of the various packaging configurations and are organized into three main parts: (1) half shielded, (2) self, and (3) conformal packaging. The development of half-shield circuits with upper or lower cavities has produced fundamental knowledge for package development. Packages (2) and (3) are based on a combinations of upper and lower cavity sections and are modified to accommodate the appropriate design requirements while providing the basic foundation for extensions to a variety of complex circuit designs that may be used in high frequency designs.

## 2.3.1 Air-Filled Upper Shielded Circuits

There were many fundamental concerns regarding fabrication and construction of shielded circuits initially; therefore a review of some of the issues pertaining to substrate

Figure 2.3 The probe window needed to measure a circuit on-wafer.

material selection and appropriate fabrication technique identification is given. Although high frequency devices and MMICs are usually realized on GaAs substrates, the vision of this work is to provide packaging alternatives for dense complex circuit layouts that produce improved electrical characteristics using reliable fabrication techniques. Therefore compatibility to existing MMIC processes and cost effective solutions are important goals. Silicon substrates have become an essential part of the microelectronics industry and a wealth of knowledge is available that can be used in the development of novel solutions to packaging high frequency circuits. Sensor applications, which rely heavily on silicon micromachining, make extensive use of advanced etching techniques. With the availabil-

ity of high resistivity substrates at reasonably low cost, Si invariably is the first choice in which these novel packaging schemes will be explored. In addition, planar circuit designs and high power devices, currently being developed with Si-germanium technology, show promise in high frequency circuits applications. Silicon substrates are used here, even though these topologies can be developed in other materials such as GaAs so long as appropriate modifications are used to realize the appropriate cavity geometry and similar electrical behavior.

Two main issues that were considered carefully are the etchant type and selectivity between wet and dry etches and its respective isotropic or anisotropic behavior. Repeatability and consistent process control are typically achieved using dry etchants, however, high selectivity between metal and dielectric masks is difficult [20]. On the other hand, certain wet anisotropic etchants used in micromachining are quite successful since selectivity ratios between specific crystal plane orientations depend on the anisotropic etch chosen. From research, etch rates have been determined for bulk silicon that are reliable for micromachining using well-controlled bath conditions for potassium hydroxide (KOH) and Ethlylenediamine pyrocatechol (EDP) wet etchants. With appropriate masking dielectrics, such as silicon dioxide and silicon nitride combinations, cavity configurations can be formed which have an etch profile of 54.75° with respect to <100> plane.

## 2.3.1.a Version One: Basic Cavity

The primary objective in the development of the first generation of air-filled shielding cavities is to produce a micromachined version of a machined-milled cavity. A planar circuit shielded by a machine milled cavity has produced a desired circuit response for coplanar based lines and has shown reduced losses for discontinuities after careful determination of the planar line geometry and cavity dimensions [16]. Since many circuits can be realized on a single substrate sample, batch processing techniques are employed to produce a variety of circuits that have consistent physical similarities. The circuit layout

consists of at least three calibration standards and a variety of circuit elements which occupy at most one-quarter of a three inch section wafer in the approach used in this methodology. The cavities are included in the layout to correspond to the various circuits and have been oriented to form vertical column alignment. Each column contains cavities that have been separated with similar spacing to the circuits on which they are to be aligned. Since the cavity lengths vary in some cases, one edge has been held constant for each cavity while the other edge accounts for the length variation (Figure 2.5). The cavity depths in this design are approximately 200 microns and are determined so that they provide appropriate shielding to each circuit while maintaining a 50 ohm impedance for the coplanar line. If the cavity shield is placed in close proximity to the transmission line, disturbances to the electric field distribution in the slots of the coplanar waveguide will occur, causing undesired line characteristics.

To facilitate the placement of the cavities over the lines, alignment of the cavities to the circuit wafer is achieved by including rectangular window openings. Each window is aligned to the metallic marks on the circuit surface and as shown in Figure 2.4 in the final version of the cavities shown mounted over the various planar circuits. To produce the design, a two-step etch procedure is employed and requires a layout that requires the inclusion of alignment windows, scribing marks, and cavity regions as shown in Figure 2.5. The following section will focus more on the general procedures used to fabricate the cavity structure.

1. A three dielectric layer consisting of silicon dioxide/silicon nitride/silicon dioxide (SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub>) has thicknesses of 4500 Å /3500 Å / 7500 Å and each layer functions as a mask. Using standard optical lithography processing techniques to pattern the wafer, the two outer dielectrics are removed from all regions to be etched using buffered hydrofluoric acid (BHF) for the oxide (SiO<sub>2</sub>) layers and CF<sub>4</sub>+O<sub>2</sub> in the plasma etcher for the nitride (Si<sub>3</sub>N<sub>4</sub>) layer.

Figure 2.4 Photograph of the circuit with the single-strip cavity over the circuits.

- 2. After repatterning to protect the lower oxide in the cavity area, the sample is placed into the KOH bath solution where the alignment windows are etched approximately half way through the wafer.

- 3. The sample is then removed from the bath and the silicon surface in the cavity region is exposed using BHF etchant and returned to the KOH etch to remove the desired cavity depth of 200 microns. For the KOH recipe used in this process, the etch rate was approximately 29.6 microns/hour, which required approximately 13 hours to etch completely through a 390 micron wafer in this process.

Figure 2.5 This represents the upper cavity wafer for the single strip cavity approach shown in Figure 2.4. The Crossed areas represent the region where the cavity is formed. The Hatched are is where the etch rulers are incorporated. Finally the dark regions are where the cavity strip it detached from the larger wafer area using chemical scribing.

4. Since the scribe lines are completely etched through, each vertical column section will be separated. The cavity structure is then cleaned and metallized with evaporated Cr/Al/Cr/Au to achieve a thickness of 1.5 microns.

This procedure proved to be the best method even though many other approaches were investigated. Initially a 1.2 micron oxide layer was used as a mask, however, this thickness is insufficient to accommodate the extremely long etch times. The thickness issue is compounded by the post-KOH oxide etch, which removes additional dielectric from the other masked areas leaving an inadequate amount of oxide for remainder of the cavity etch time. To overcome this problem, several other approaches were implemented to provide an additional masking layer as protection during the removal of the material in the cavity region. Alternatives masking layers based on metal systems such as chrome-gold (Cr/Au)

and chrome-aluminum (Cr/Al) were tested, however these also produced poor results. The main reason is due to adhesion problems associated at the metal/oxide interface since thin metal layers of approximately 2000Å are thermally evaporated on to the surface. These adhesion problems were not noticeable during the first etching step, however after the second oxide etch small pockets of solution were observed on the surface of the wafer in the metal areas after the samples where submersed into the KOH bath. These problems are related to thermal issues as a result of long etch times in temperatures ranging from 55° to 60° C. Problems in adhesion can result from metallic pinholes which become noticeable after the oxide etchant since the bare silicon surface is exposed and subjected to the KOH. Other adhesion metals such as titanium were investigated, however similar results were also observed which motivated modification of the process and selection of a different masking material.

The tri-layer dielectric materials mentioned above, sometimes referred to as a membrane, allow for successful development of the cavity structure in the KOH solution. The nitride layer in particular is very resistent to many acidic solutions therefore it provides additional protection to the wafer surface during the removal of the lower oxide layer in the cavity regions. This resulted in good masking capabilities, and the problem of metal adhesion is now eliminated since it is no longer required as an additional mask. There is, however, another problem that arose regarding the use of membrane which impacts the successful reliability of the above process. Membranes have been successfully etched in KOH solutions at the University of Michigan by Ling [21] and Ali-Ahmad [23], however a varnish is applied to the front side of the dielectric to serve as a protective layer for the upper surface since backside wafer processing is required to make free-standing membranes. In this case a protective layer is not compatible with the desired design requirements and cannot be used. The nitride tensile stress can be counter balanced by adding even though oxides layers unless low-stress nitrides are used. In long continuous etching cycles, this problem seldom occurs since a photoresist mask protects the entire wafer dur-

ing the dielectric removal. Even though these cracks may be present, the outer oxide layer is protected by the resist during the dielectric removal. On the other hand, when this procedure requires an additional oxide etch after the Si material has been partially removed by the KOH etchant, any imbalance of stress in the dielectric layer will produce membranes in compression or with low grade stress cracks that become more pronounced as in the process described above. These cracks allow for severe surface damage from the KOH across the entire surface of the wafer. Therefore, since a testing procedure and calibration on the appropriate membrane tensile stress compositions was not available, other etchant solutions were investigated.

To summarize the above discussion, the first generation of upper cavities are realized using tri-layer dielectric combinations as masking layers in a KOH chemical solution. The procedure works in general even though there are some issues regarding membrane tensile stress which can be alleviated with the appropriate choice of dielectric layer thicknesses. Tensile stress tests are described in the appendix of Ling's thesis [21] and can aid in the determination of the appropriate thickness needed for a given wafer size.

## 2.3.1.b Version Two: Cavity with Access Windows

In this phase, the issue of aligning multiple cavities with more reliability is addressed along with minimizing the sensitivity of the dielectric masks in the etching solution. The shielding cavity structure in the first version was developed where single strips are used to represent cavities having similar or varying lengths. This arrangement validated the realization of the micromachined structures, however it has limited alignment repeatability since the cavities are not mounted simultaneously. To alleviate this problem, large windows have been incorporated that attach the various cavity columns in order to align all of the cavities to the circuit wafer. The requirements for the windows are to provide probe entry access to each circuit while concurrently providing a mechanism for alignment of all

Figure 2.6 Completely shielded micropackaged circuit with lower and upper wafer alignment.

cavities in the same relative position of each circuit. Any misalignment at this point can be accounted for in the calibration which improves the accuracy of the characterization.

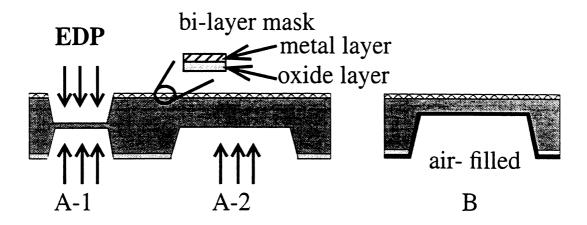

Initially, KOH solution was investigated, however, due to the long etch time requirements and problems discussed above in the first version, EDP anisotropic etch is used the remainder of this work. Probe and alignment windows are incorporated and etched entirely through the wafer while the cavities are etched partially. The use of EDP in this case has reduced the etch time to about 5 hours for a 390 micron thick wafer and the issue of tensile stress has been eliminated. The following description highlights the fabrication procedures implemented:

1. The first two dielectric layers, silicon dioxide and silicon nitride, are removed from all areas to be etched as before.

- 2. The wafer is then repatterned to protect the cavity region and the lower oxide layer is removed in the probe and alignment windows.

- Since the desired cavity depth is approximately 200 microns, all windows are etched to ≈150 microns before the last layer of the oxide is removed from the cavity region.

- 4. The oxide is then removed using buffered hydrofluoric acid (BHF) and the sample is returned to the EDP solution to remove the additional 200 microns of silicon in the remaining areas and the cavity region.

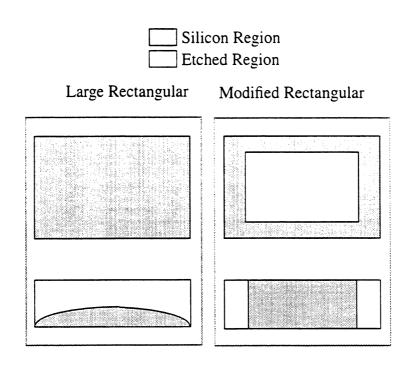

Although the above procedures represent the general form of the process, some concerns did arise regarding the realization of the geometry. While attempting to achieve the desired cavity formation, severe lateral etching was observed in the cavity region as a result of the rapid etch. This is a problem since the etch depth and cavity upper wall depend on the etch used in the fabrication procedure. Many alternatives were investigated to reduce this effect of lateral etching at the entrance of the cavity. The first objective is to determine the difference between the EDP and the KOH used previously. Since all of the probe windows are etched entirely, removing large cross-sectional areas produces uneven etching across the surface due to the selectivity of the etch ratio between <111> and <100> plane. In a large rectangular area, the centers of the surface are not removed at the same rate as the sidewall and result in the inverted bowl profile shown in Figure 2.7. In order to completely remove this material from the center region, etching continues along the cavity edge which causes lateral etching in the cavity upper roof. This results in a narrow horseshoe shaped openings in the upper surface of the cavity entrance regions compared to the straight edge obtained in the KOH etch. To minimize this effect, a channel is etched along the perimeter of the desired rectangular window completely through. Once the channels are etched entirely, the center sections separate apart from the remaining wafer which reduces the edge exposure of the cavities and results in less sever overetching.

Figure 2.7 Etching profile of the probe window area and the cavity region.