# A STUDY OF INFORMATION IN MULTIPLE-COMPUTER AND MULTIPLE-CONSOLE DATA PROCESSING SYSTEMS

K. B. IraniI. S. UppalJ. W. Boyse et al

The University of Michigan

Approved for public release; distribution unlimited.

#### FOREWORD

This report was prepared by Messrs. K.B. Irani, I.S. Uppal, J.W. Boyse, D.M. Coleman, D.L. Hinshaw, G.A. McClain, L.S. Randall, and A.M. Woolf of the University of Michigan, Systems Engineering Laboratory, Ann Arbor, Michigan, under contract F30602-69-C-0214, Job Order Number 55810000. Rome Air Development Center Project Engineer was Rocco F. Iuorno (ISIS).

The period of time covered in this report is April 1970 to March 1971. Contractor's identification number is Annual Report No. 4.

This report has been reviewed by the Information Office, OI, and is releasable to the National Technical Information Service.

This Technical Report has been reviewed and is approved.

Approved:

ROCCO F. IUORNO Project Engineer

Information Processing Branch

Approved:

FRANK J. TOMAINI

Chief, Information Processing Branch

Information Sciences Division

## ABSTRACT

This report documents the achievements from April 1970 to March 1971 of continuing research into the development and application of mathematical techniques for the analysis and optimization of multiple-computer, multiple-user systems. A summary of the theoretical investigations conducted, the major conclusions reached, and some typical applications are included.

# TABLE OF CONTENTS

| Section |                 | <u>-</u>                                   | Page       |

|---------|-----------------|--------------------------------------------|------------|

| 1       | INTRO           | DUCTION                                    | 1          |

|         | 1.1             | Contract Objectives                        | 1          |

|         | 1.2             | Contract Requirements                      | 1          |

|         | 1.3             | Progress Toward Contract Objectives        | 3          |

| 2       | MESSA<br>SYSTEN | GE PROCESSING AND COMMUNICATION MS         | 6          |

|         | 2.1             | Introduction                               | 6          |

|         | 2. 2            | Some Problems in Computer Message          | •          |

|         |                 | Processing and Communication System Design | 9          |

|         | 2.3             | A CMPC System Synthesis Procedure          | 22         |

|         | 2.4             | Example                                    | <b>2</b> 8 |

|         | 2.5             | Conclusion                                 | 45         |

| 3       | MULTI           | PROGRAMMED AND MULTIPROCESSOR              |            |

|         |                 | UTER SYSTEMS                               | 51         |

|         | 3.1             | Multiprogrammed Systems Using              |            |

|         |                 | Storage Hierarchies                        | 52         |

|         | 3.1.1           | The Nature of the Problem                  | 55         |

|         | 3.1.2           |                                            | 56         |

|         |                 | The Model                                  | 57         |

|         | 3.1.4           |                                            | 66         |

|         | 3.2             | Optimum Task Scheduling                    | 72         |

|         | 3.2.1           |                                            | 72         |

|         | 3.2.2           | Data Collection and Analysis               | 80         |

|         | 3.3             | Selection of Optimal Sets with Application |            |

|         |                 | to Computer Programming                    | 89         |

|         | 3.3.1           | Selection of Optimal Program Pages in      |            |

|         |                 | Multiprogramming System                    | 90         |

|         | 3.3.2           | Paging                                     | 91         |

|         | 3.3.3           | Model                                      | 92         |

|         | 3.3.4           | Solution Technique for Grahpical           | <b>.</b> - |

|         |                 | Partitioning                               | 92         |

| Section |                           |                                                                     | Page |

|---------|---------------------------|---------------------------------------------------------------------|------|

|         | 3.3.4.1                   | Optimal Systems                                                     | 92   |

|         | 3.3.4.2                   | Knowing Optimal Procedures                                          | 93   |

|         | 3.3.4.3                   | Heuristic Procedures                                                | 93   |

|         |                           | Multiprocessor Scheduling                                           | 96   |

|         | 3.4.1                     | Multiprocessor Scheduling - Assignment                              |      |

|         |                           | and Scheduling                                                      | 99   |

|         |                           | Hard Real-Time Environment                                          | 103  |

|         | - •                       | Soft Real-Time Environment                                          | 109  |

|         | 3.4.2.2                   | Scheduling Parallel Processes - A Zero-<br>One Programming Approach | 111  |

|         | 3.4.2.1                   | Model and Notation                                                  | 113  |

|         | 3.4.2.2                   | Assumptions and Limitations                                         | 114  |

|         | 3.4.2.3                   | Formulation of the Optimization                                     |      |

|         |                           | Problem                                                             | 116  |

|         | 3.4.2.4                   | Objective Functions                                                 | 116  |

|         | 3.4.2.5                   | Constraints                                                         | 119  |

| 4       | CENTRA                    | AL PROCESSOR DESIGN                                                 | 1 25 |

|         | 4.1                       | Data Path Optimization                                              | 125  |

|         | 4.1.1                     | Example                                                             | 126  |

|         | 4.1.2                     | Model for the Study                                                 | 130  |

|         | 4.1.2.1                   | Model Language                                                      | 132  |

|         | 4.1.2.2                   | Model Architecture                                                  | 133  |

|         | 4.1.2.3                   | Hardware Unit Library                                               | 134  |

|         | 4.1.2.4                   | Algorithm Library                                                   | 135  |

|         | 4.1.2.5                   | Model of the Data Path                                              | 135  |

|         | 4.1.2.6                   | Optimization Criteria                                               | 136  |

|         |                           | Generality of the Model                                             | 137  |

|         | 4.1.3                     | Progress Toward a Solution                                          | 137  |

|         | 4.2                       | Microprogram Control                                                | 139  |

|         | 4.2.1                     | The General Design Method                                           | 139  |

|         | 4.2.2                     | PTL an Intermediate Language                                        | 144  |

|         | 4.2.3                     | Optimization                                                        | 149  |

| 5       | DATA STRUCTURES AND THEIR |                                                                     |      |

|         |                           | SENTATION                                                           | 151  |

|         | 5.1                       | Computer Memory Data Representation                                 | 151  |

|         | 5.1.1                     | Development of a Model                                              | 153  |

|         | 5.1.2                     | Optimization                                                        | 158  |

|         | 5. 2                      | Computer Graphics Systems                                           | 160  |

| Section |                                           | Page |

|---------|-------------------------------------------|------|

|         | 5.2.1 The General Approach                | 161  |

|         | 5.2.1.1 Topological Structure             | 163  |

|         | 5. 2. 1. 2 The Picture Generator          | 170  |

|         | 5.2.1.3 Representation of the Topological |      |

|         | Structure                                 | 172  |

|         | 5.2.1.4 The Optimum Implementation        | 172  |

# LIST OF FIGURES

| Figure |                                                                                                                       | Page   |

|--------|-----------------------------------------------------------------------------------------------------------------------|--------|

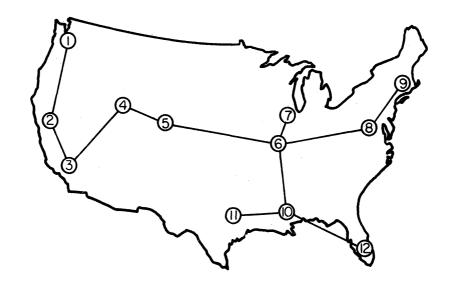

| 2.1    | CMPC System Configuration                                                                                             | 8      |

| 2.2    | Offices and Branches of a Large Banking System                                                                        | 11     |

| 2.3    | File Request Origin Probabilities for Two Example Files                                                               | 13     |

| 2.4    | Variation in Processing Cost, Communication Cost and Total System Cost with Degree of Centralization                  | l      |

| 9 5    | of File Assignments                                                                                                   | 15     |

| 2.5    | Comparison of Point-to-Point and Multi-Point Segments                                                                 | 15     |

| 2.6    | Illustration of Changes in Edge Traffics and<br>Total Traffic When File is Moved from One Node<br>to an Adjacent Node | 10     |

| 2.7    | Average Message Delay in a Communication                                                                              |        |

|        | Channel                                                                                                               | 21     |

| 2.8    | Feasible Values of Channel Capacity in Two                                                                            |        |

|        | Channel Communication System with Performance                                                                         |        |

| 2.0    | Constraint                                                                                                            | 21     |

| 2.9    | A Methodology for Computer Message Processing and Communication Design System                                         | 23     |

| 2.10   | Modified Topologies Resulting from Tree Topology                                                                      | 20     |

|        | by Deletion of One Edge and Insertion of Another                                                                      | 24     |

| 2.11   | CMPC System Design Methodology                                                                                        | 25     |

| 2.12   | Terminal Locations and File Parameters for                                                                            |        |

|        | Design Examples                                                                                                       | 29     |

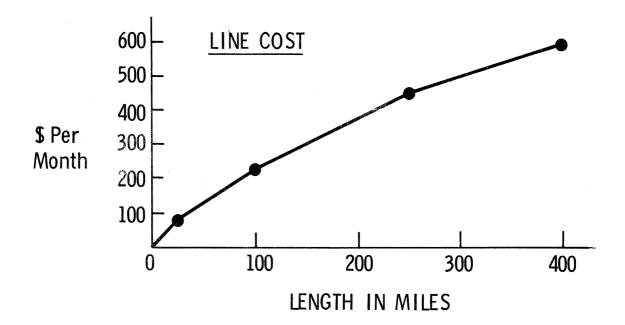

| 2.13   | Line Cost Function                                                                                                    | 30     |

| 2.14   | CMPC System Designs Selected by Each Successive                                                                       | 0000   |

| 2.15   |                                                                                                                       | ,32,33 |

| 2.16   | Non-Optimal System Design Example<br>System Design Example with Network Topology                                      | 36     |

| 20.10  | Selection                                                                                                             | 37     |

| 2.17   | System Design Example with Optimal File                                                                               | 0,     |

|        | Assignments and Network Topology Selection                                                                            | 38     |

| 2.18   | System Design Example with Optimal File                                                                               |        |

|        | Assignment, Tree Segmentation, and Network                                                                            |        |

|        | Topology Selection                                                                                                    | 39     |

| 2.19   | System Design with Optimal File Assignment,                                                                           |        |

|        | Optimal Edge Capacity Allocation and Network                                                                          | 40     |

|        | Topology Selection                                                                                                    | 40     |

| <u>Figure</u> |                                                                                          | Page      |

|---------------|------------------------------------------------------------------------------------------|-----------|

| 2. 20         | System Design Example with Optimal File                                                  |           |

|               | Assignment, Tree Segmentation, Optimal Segment Capacity Allocation, and Network Topology |           |

|               | Selection                                                                                | 41        |

| 2. 21         | Comparison of Several CMPC System Design Pro                                             |           |

|               | Procedures                                                                               | 44        |

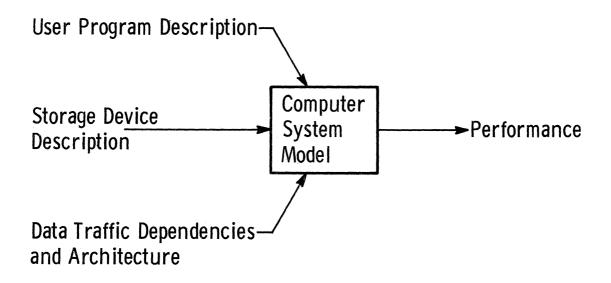

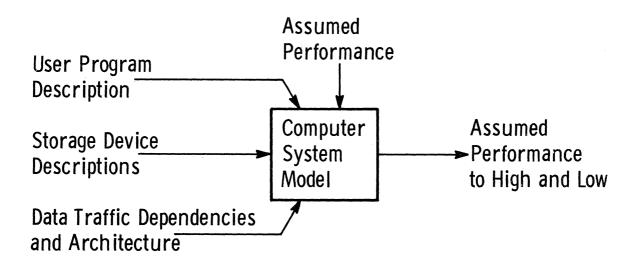

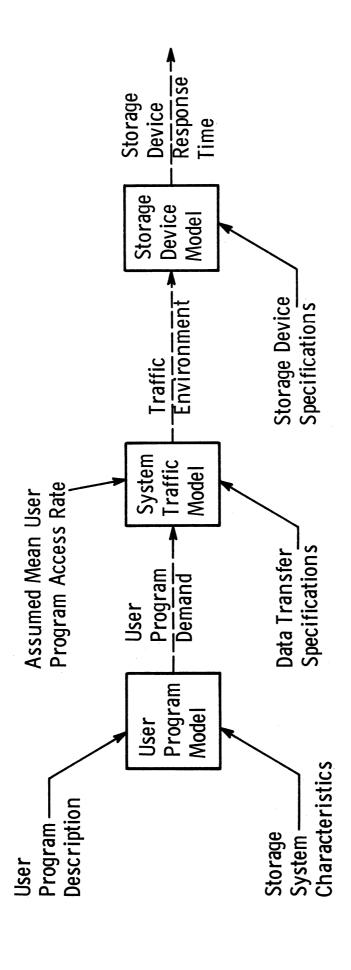

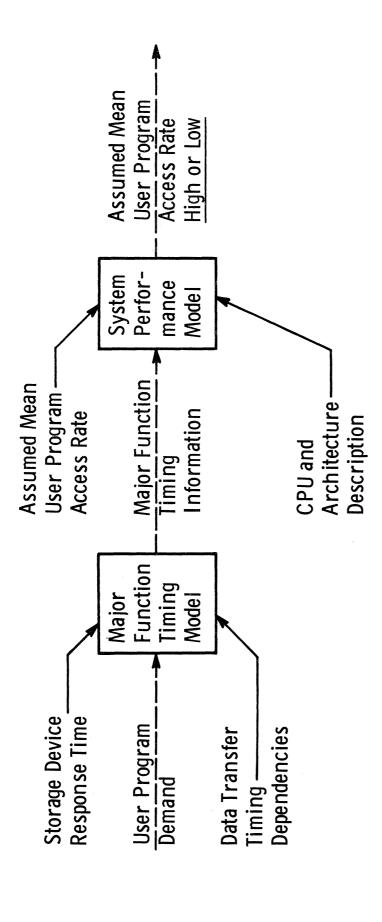

| 3.1           | System Analysis Model                                                                    | 59        |

| 3.2           | System Model                                                                             | 59        |

| 3.3           | Detailed System Model, Part 1                                                            | 60        |

| 3.4           | Detailed System Model, Part 2                                                            | 61        |

| 3.5           | System Diagram                                                                           | 67        |

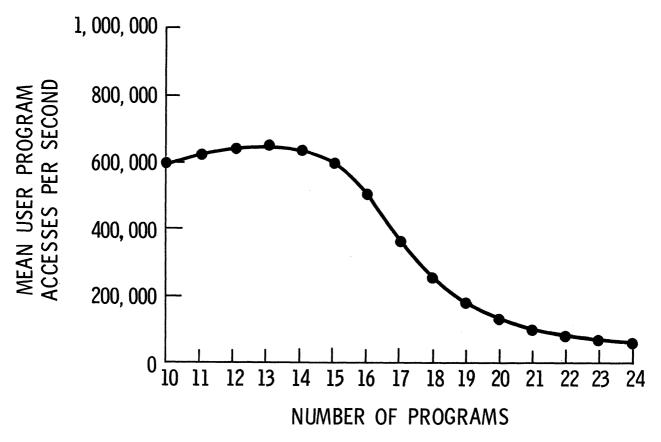

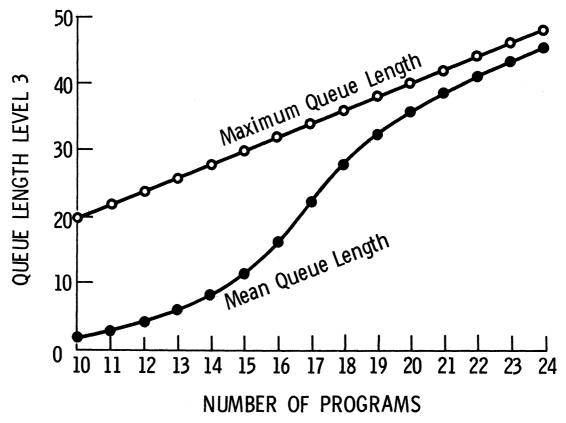

| 3.6           | Performance Versus Number of Programs                                                    | 68        |

| 3.7           | Queue Length Versus Number of Programs                                                   | 68        |

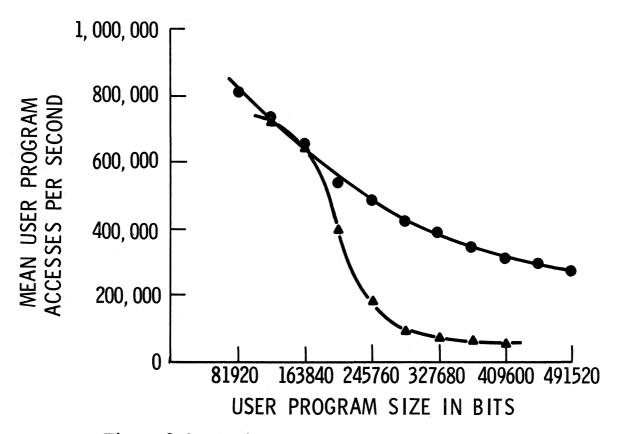

| 3.8           | Performance Versus User Program Size                                                     | 69        |

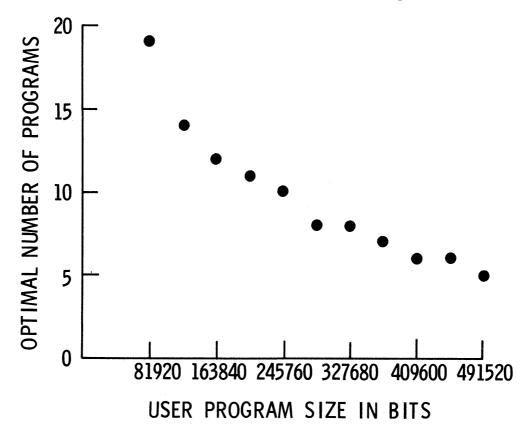

| 3.9           | Optimal Number of Programs Versus Program Size                                           | 69        |

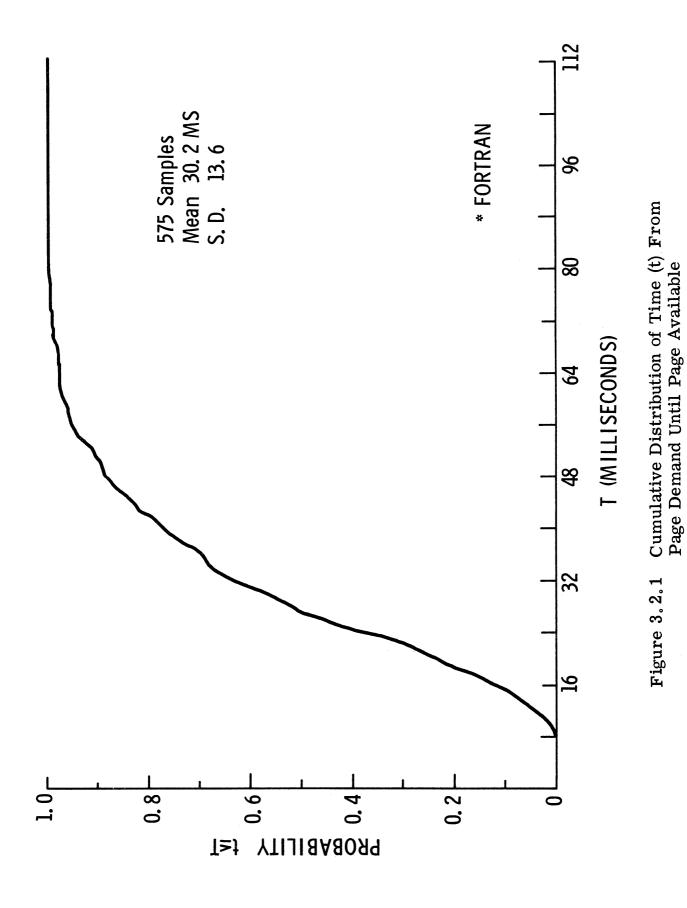

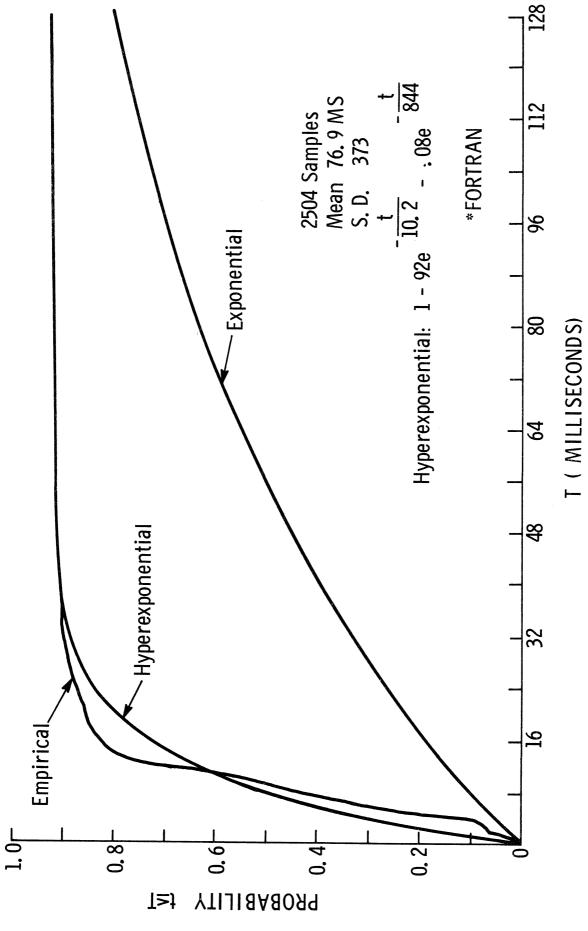

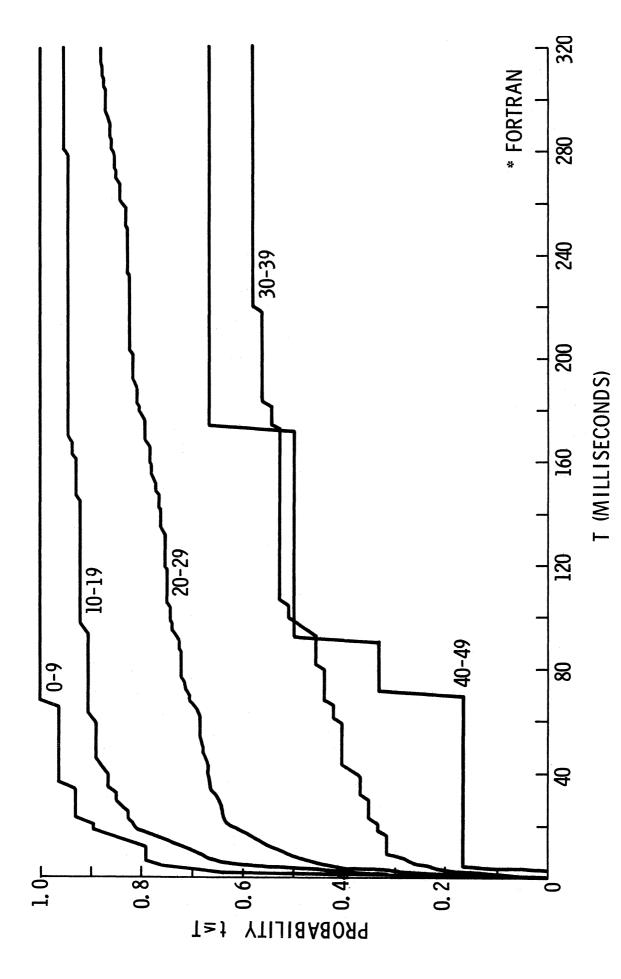

| 3.2.1         | Cumulative Distribution of Time (t) from Page                                            |           |

|               | Demand Until Page Available                                                              | <b>82</b> |

| 3.2.2         | Cumulative Distribution of CPU Time (t) Used                                             |           |

|               | Between I/O During Fortran Compilations                                                  | 83        |

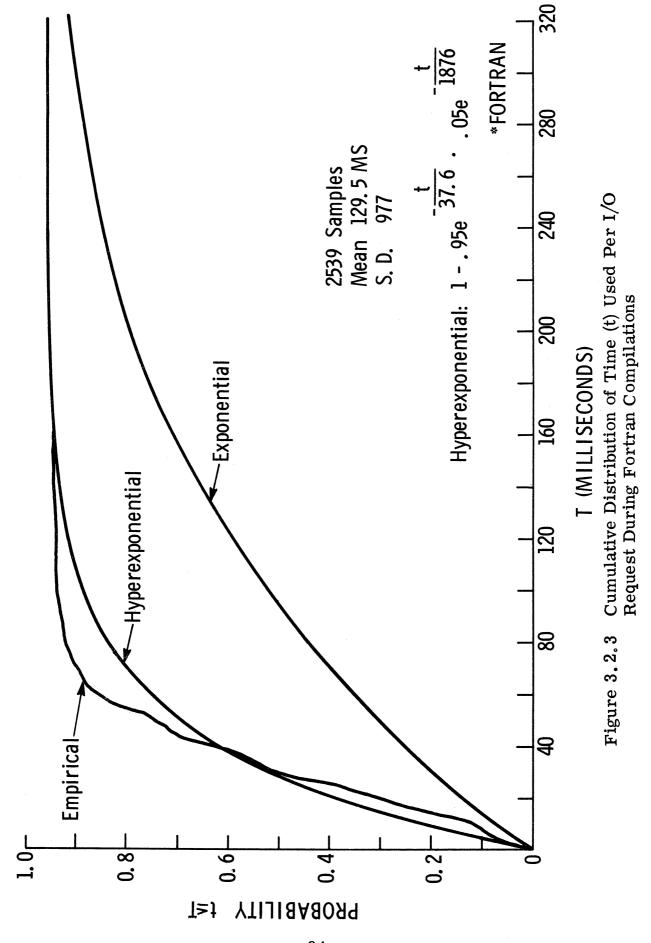

| 3.2.3         | Cumulative Distribution of Time (t) Used Per I/O                                         |           |

|               | Request During Fortran Compilations                                                      | 84        |

| 3.2.4         | Cumulative Distribution of CPU Time (t) Used                                             |           |

|               | Between Page Faults During Fortran Compilations                                          | 85        |

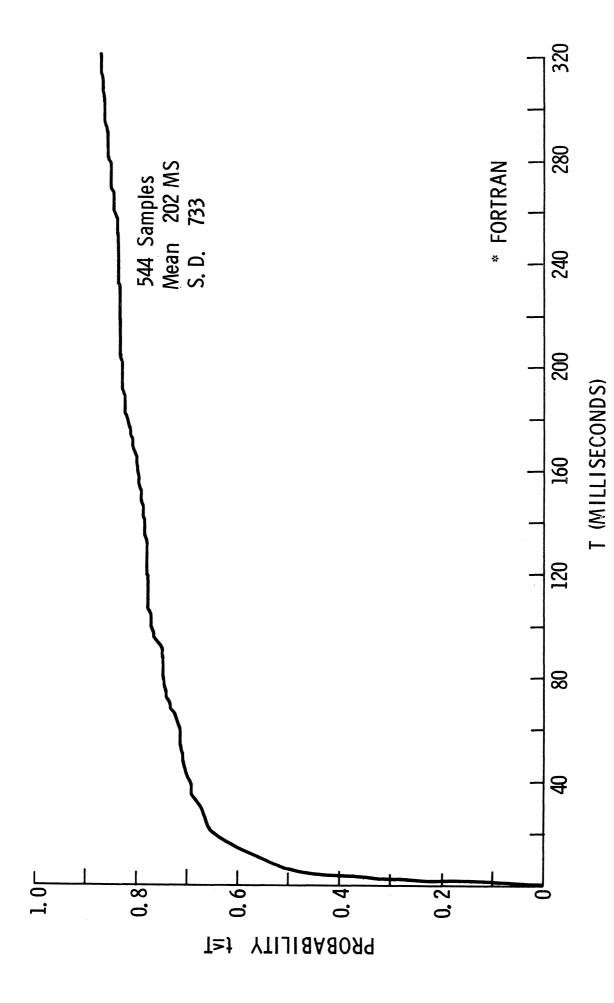

| 3.2.5         | Cumulative Distribution of CPU Time (t) Used                                             |           |

|               | Between Page Faults as a Function of the Number                                          |           |

|               | of Pages in Core for Fortran Compilations                                                | 85        |

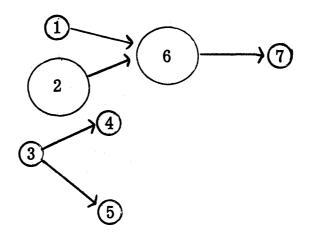

| 3.4.1         | A Typical Task Set                                                                       | 104       |

| 3.4.2         | Initial Configuration of Task List                                                       | 105       |

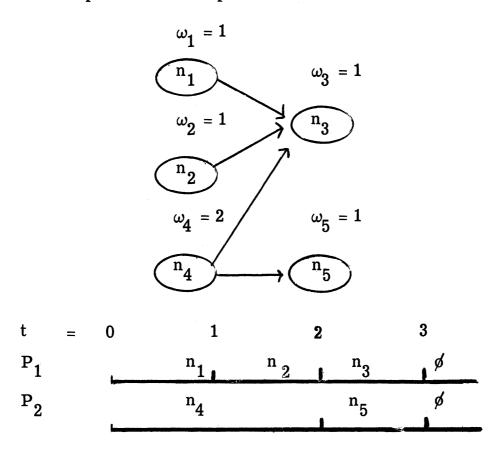

| 3.4.3         | An Example Graph and Schedule                                                            | 108       |

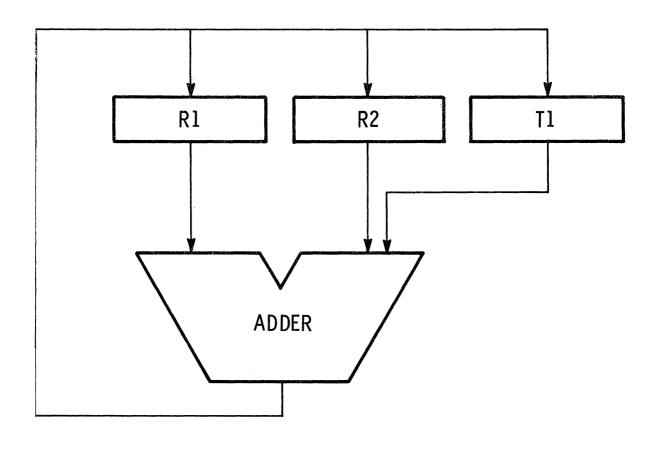

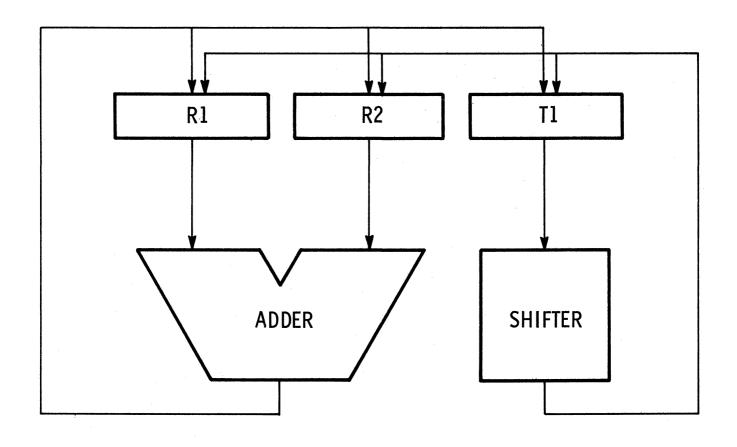

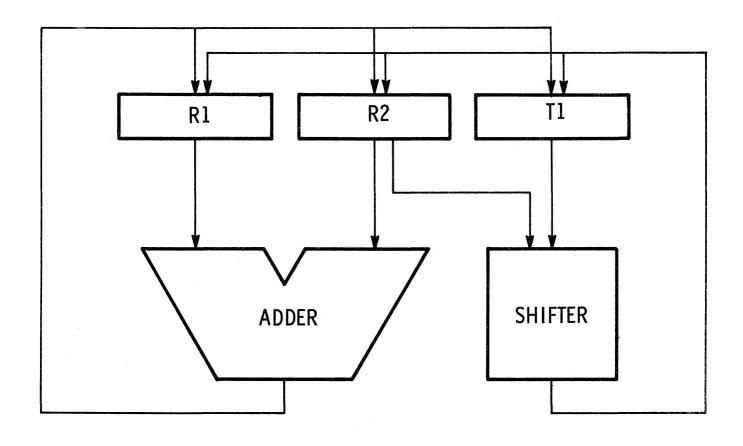

| 4.1           | CPU Data Path I                                                                          | 127       |

| 4.2           | CPU Data Path II                                                                         | 128       |

| 4.3           | CPU Data Path III                                                                        | 1 29      |

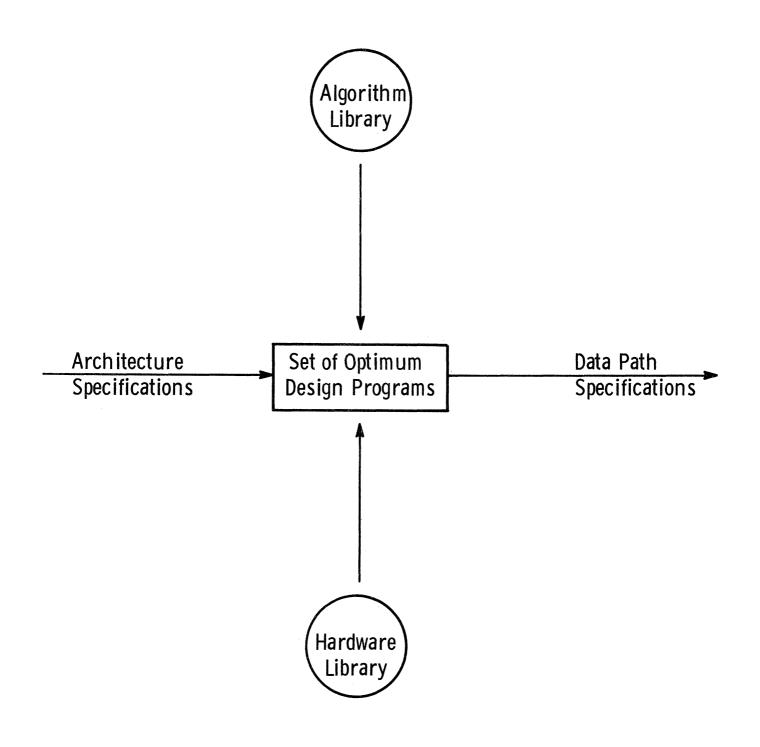

| 4.4           | Overall Structure of Model                                                               | 131       |

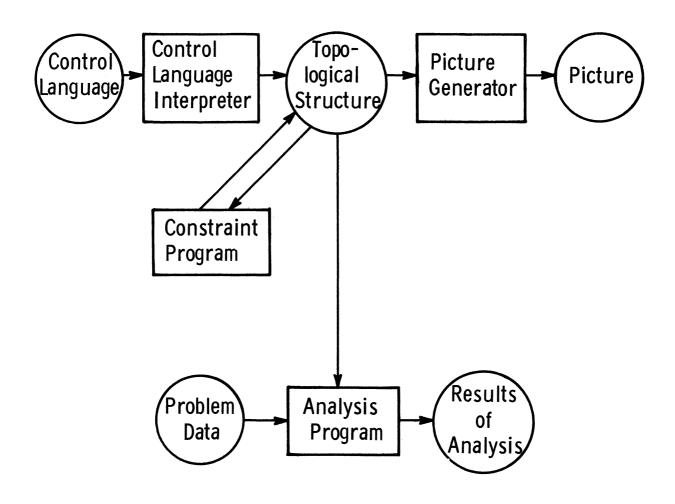

| <b>5.2.1</b>  | Interactive Display Program as Described                                                 |           |

|               | by W. R. Sutherland                                                                      | 162       |

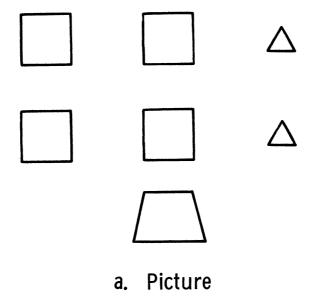

| 5. 2. 2       | A Picture and a Representation of Its Topology                                           | 164       |

| 5.2.3         | Eamples of Pictures for which the Topology of                                            |           |

|               | Each Picture Facilitates Response to Control                                             |           |

|               | Language Inputs                                                                          | 167       |

#### 1. INTRODUCTION

### 1.1 Contract Objective

This effort is for applied research in the area of mathematical techniques for analyzing multiple computer, multiple console, real-time on-line data processing systems, and for analytical techniques and hypothesis to assist system designers and users in determining the optimum configuration, most complete utilization, and most efficient scheduling of this type of system.

The main objective of this work is to make it possible, through development and application of new mathematical techniques, to more optimally design and control computer systems. A computer system consists of a collection of electronic data processing machines, data transmission channels, and multiple user terminals, organized to efficiently service the computational needs of a geographically or functionally diverse population of users. Such systems permit: remote communication and manipulation of shared data bases; cooperative operations between user and computer (symbiosis); an immediate access to a high-capability facility for problem solving and data manipulation.

# 1.2 Contract Requirements

1) Exploration of Queueing Theory to enable the analysis of more general models of computer utilities and their subsystems.

Emphasis shall be concentrated on numerical techniques, and

- shall include extension of earlier work on quasi-birth-and-death (QBD) models and the Recursive Queue Analyzer.

- 2) Collection and analysis of statistical data from existing systems to determine the validity of the mathematical models developed, and to isolate problem areas in need of attention.

The techniques of computer data collection shall be studied.

- 3) Application of new mathematical techniques in conjunction with those previously available, to the analysis and optimization of hardware and software configurations of general purpose computers. These techniques shall be applied to typical systems in order to test the analytical methods and provide specific analyses/recommendations concerning the effectiveness of these systems.

- 4) Continued development of general design guidelines for timeshared computer systems with distributed processing capabilities. Distributed processing has become economically feasible

because of rapidly decreasing small computer costs. This

task shall extend previous investigations of remote display

terminal structures.

- 5) Continued development of mathematical models for the optimal structuring of communication networks associated with computing systems.

- 6) Continued development of optimal design of storage systems and data base strucutres.

- 7) Continued exploration of Discrete Optimization Theory and Graph Theory in relation to application concerning the scheduling of programs in multi-processor systems. Also to investigate the use of these theories in relation to problems of program organization.

- 8) Development of new conclusions and rules which can be used by persons performing initial designs of real-time computer systems having a large number of user consoles. Such rules shall allow system designers to more rapidly choose the type of hardware/software system needed to fit a particular organization or problem.

- 9) Application of statistical analysis to data collected from various computing systems in order togain an understanding of user demand structures and their effects on systems performance. A search for other theoretical approaches to the analysis of multiple computer systems shall be pursued.

#### 1.3 Progress Toward Contract Objectives

The following sections details the progress made during the second year of this contract. Section 2 reports progress in the area of design of message processing and communications systems. In Section 3 we report research into the application of optimization theory to the problems

of program organization and program scheduling. Section 4 reports on efforts to apply mathematical techniques to the analysis and optimization of the hardware configuration of the central processor. Finally Section 5 concentrates on data structures and their representation in the computer memory.

During the past year Systems Engineering Laboratory Technical Reports Nos. 48[1] and 51[2] were published. The other four reports [3,4,5,6] are in the final stages of completion.

#### References for Section 1

- 1) V.K.M. Whitney, "A Study of Optimal File Assignments and Communication Network Configuration in Remote Access Computer Message Processing and Communication System", SEL Tech. Report No. 48, The University of Michigan, Ann Arbor, Jan. 1971.

- 2) J. H. Jackson, 'Optimum Implementation of Topological Structure for Interactive Computer Displays,' SEL Tech. Report No. 51, the University of Michigan, Ann Arbor, Jan. 1971.

- 3) A. M. Woolf, "Analysis and Optimization of Multiprogrammed Computer Systems Using Storage Hierarchies", SEL Tech. Report No. 53, The University of Michigan, Ann Arbor, April, 1971.

- 4) J.W. Boyse, "Solutions of Markov Renewal Decision Process with Application to Computer System Scheduling", SEL Tech. Report No. 52, The University of Michigan, Ann Arbor, to be be published.

- 5) L. S. Randall, "A Relational Model and its Optimization for the Representation of Structured Data Within a Random-Access Computer Memory", SEL Tech.Report No. 54, The University of Michigan, Ann Arbor, to be published.

- 6) D. Coleman, 'On Binding Groups A Quadratic Programming Approach in Zero/One Variables with Applications,' SEL Tech. Report No. 56, The University of Michigan, Ann Arbor, to be published.

#### 2. MESSAGE PROCESSING AND COMMUNICATION SYSTEMS

In this section we report research into the solution of several problems involved in the optimal design of computerized message processing and communication systems. The class of systems studied includes airline and hotel reservation systems, and time-shared computer systems. After a brief description of the general characteristics of the class of systems to which this research is pertinent in Section 2.1, the various subproblems encountered in the design of computer message processing and communication systems are presented in Section 2.2. The various subproblems and their solution techniques are then integrated into a comprehensive design procedure illustrated in Section 2.3. An example of a complete system design using the techniques of the previous sections is given in Section 2.4, and finally a summary of the specific contributions of this research is presented in Section 2.5. The details of the research reported in this section can be found in the report entitled. "A Study of Optimal File Assignment and Communication Network Configuration in Remote Access Computer Message Processing and Communication Systems" [5], which was published during the last year.

## 2.1 Introduction

This work is concerned with the design of large on-line real-time computer communication systems. Both the size and the number of

such systems are rapidly increasing today. Three such systems are the Barcleys Bank Ltd. on-line banking system serving 4,500,000 customers through more than 2500 terminals [1], the American Airlines SABRE reservation system [2], and the General Electric Corporation nationwide order processing system [3].

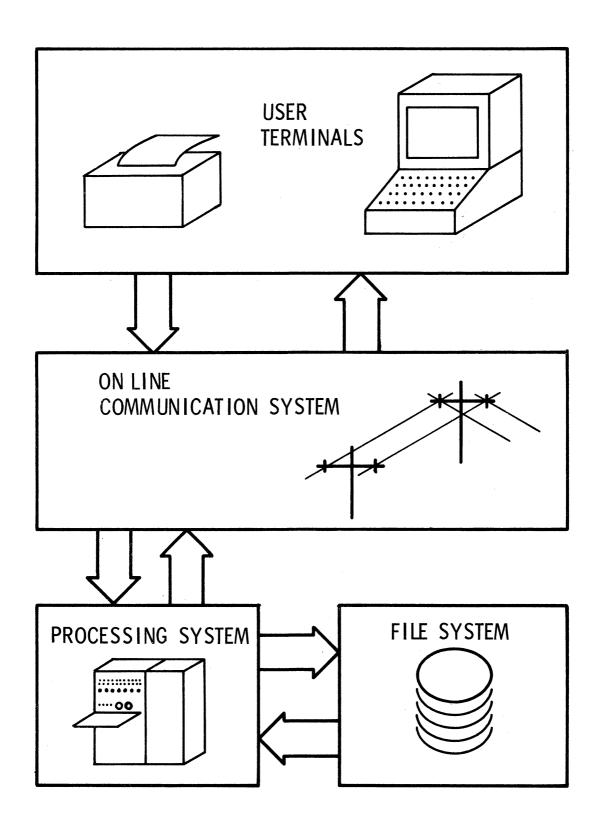

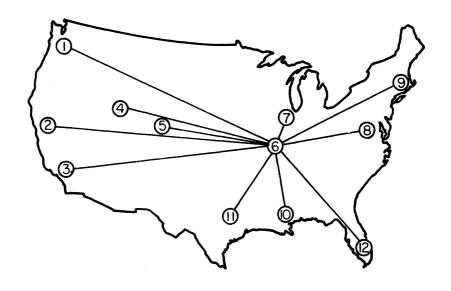

The computer-communication systems studied will be composed of the four basic sub-systems illustrated in Figure 2.1., the user terminal system, an on-line communication system, a message processing system, and a file system. The user terminals are connected by a large telecommunication network to one or more processing facilities. Each processing facility may have its own data files or fetch the necessary data located at the other processing sites through a telecommunication network. Certain properties are common to all of these systems:

- Many users at widely separated geographic locations randomly requesting records of a sizable data base.

- A large data base consisting of files of homogeneous records.

- One or more processing facilities which select, process, and answer the user requests for information.

- An on-line real-time communication system linking the user to the processing facilities.

- Quantitative measures of system performance such as average message delay time, average line utilization, and

Figure 2.1 CMPC System Configuration

- maximum hourly throughput.

- Performance constraints on the system, such as the requirement that the average message delay not exceed 3 seconds.

The goal of this research is the development of a comprehensive realistic optimal design procedure for these computerized message processing and communication (CMPC) systems. While this ambitious goal has not been completely attained, considerable progress has been achieved. A mathematical model of CMPC systems has been constructed and studied to identify the important design variables and to isolate specific problems for analysis and solution. Several of these specific design problems have been solved and the solution techniques organized into a unified system design procedure.

# 2.2 Some Problems in Computer Message Processing and Communication System Design

Since the installation of a large computer system requires a great initial investment of capital and time as well as substantial operating expense, it is desirable to design the least expensive system which will satisfy the system specifications and performance constraints. In this section, several problems arising in the design of these large systems will be discussed.

At the commencement of a system design certain information will be assumed known. The location of the users, the records of the

system data base, the probabilities that individual users' requests will be for specific records, and the rates at which users request records from the data base must be known before the design procedure begins.

In addition to this factual data, certain decisions must be fixed before the design can proceed. A measure of system performance — mean message delay, for example — and the value corresponding to the worst acceptable system performance must be selected. Often, additional constraints on the types of equipment to be used in the system are decided before the system begins. Many such possible constraints will become evident in the following description of the system design procedure.

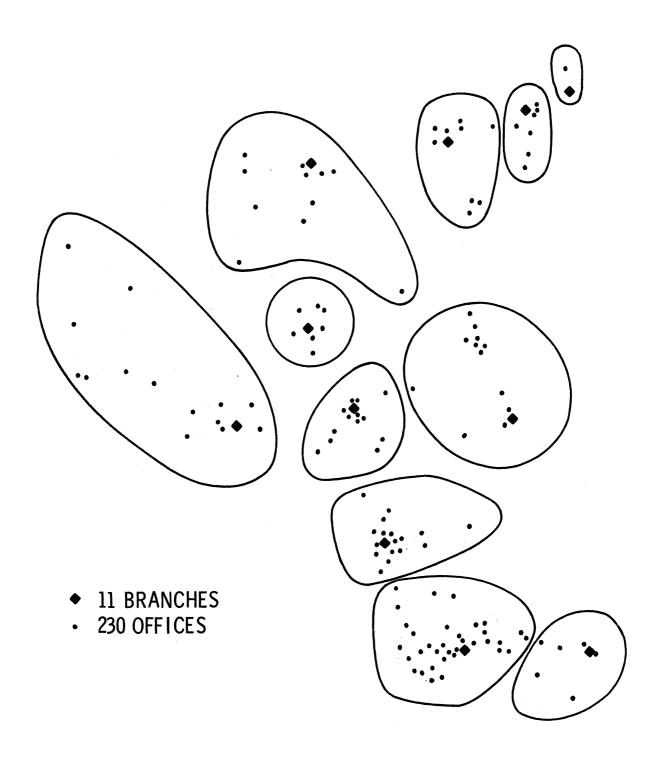

Designing a communication system linking thousands of users to files containing billions of records is a very difficult problem. The first step of the design procedure is to reduce the problem to a more manageable size. The users of the system are gathered into a moderate number of terminal user groups, with one user location in each group serving as a communications terminal. Each user can communicate with his terminal, and each terminal can communicate with the other terminals. Users in distinct terminal user groups may communicate only by using their terminals as relay stations. The partitioning of 230 users into 11 terminal user groups for a banking system example is illustrated in Figure 2.2. Since the selection of terminal locations and the users connected to each is often a political or managerial decision rather than a technical decision, and since the user population of a system may change rapidly, a stable basis for system de-

Figure 2.2 Offices and B ranches of a Large Banking System (from  $\{4\}$ )

sign has been assumed by fixing in advance the terminal locations.

A second reduction in system complexity results from partitioning the records of the data base into individual files of similar records. All record of a single file are assumed equally likely to be requested by the users at a specific terminal. Of course, the likelihoods of a record's being requested by users at different terminals may be different. Sometimes the grouping of files will be done by fiat or will be obvious. In the banking system, for example, each file could contain the savings account records for customers of a particular branch.

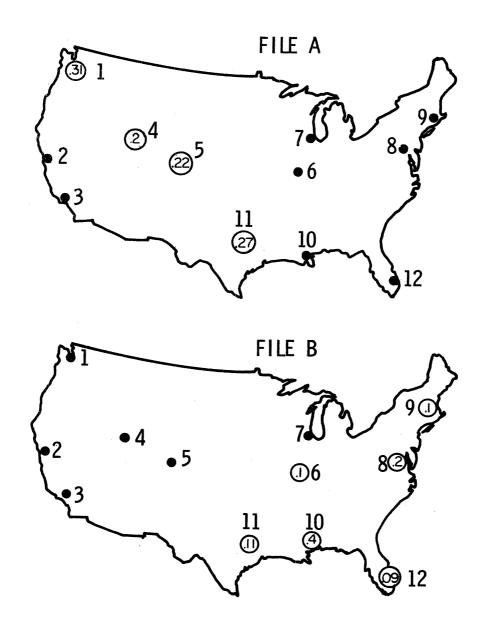

The file access request origin probabilities for two files are illustrated in Figure 2.3. At each of the twelve terminals is a number specifying the probability that a request for a record of that file originated with a user at that terminal. For file A nearly all request are from users in the west; for file B most requests are from the east.

A major problem in CMPC system design is the selection of the proper sites at which to store the files of the system data base. If the cost of communication for a file is proportional to the product of the number of requests made by the distance those requests must travel, we can calculate the communication cost induced by locating the example files at each of the terminals. When cost is the product of traffic rate by distance, the least costly location for file A is terminal 4 (cost 1, 92) and for file B is terminal 10 (cost 1, 30). If, however, it is necessary to locate both files at the same terminal, then the optimal location is terminal 6 with cost 3, 70. Note that

Figure 2.3 File Request Origin Probabilities for Two Example Files

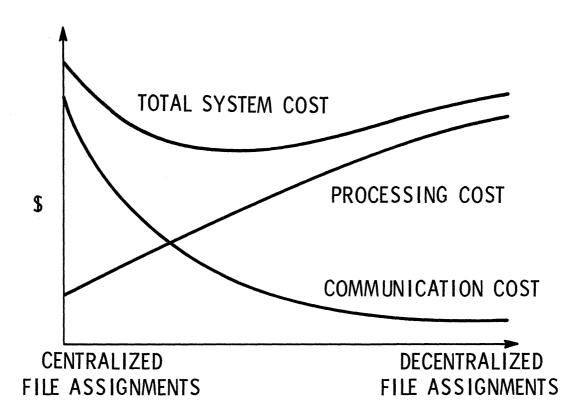

er than the cost of locating each file at its optimal site since then both are located at nonoptimal sites. This example illustrates a problem in file site assignment represented more generally in Figure 2.4. There it is pointed out that while a centralized file site assignment results in lowest storage or processing cost, a decentralized file site assignment results in lowest communication cost. Hence neither a fully centralized nor a fully decentralized file site assignment results in results in lowest communication cost.

It is appropriate to be concerned with this problem of file site assignment, even though most existing computer communication systems are centralized. The number of multiple location computer systems is rapidly increasing; as the communication facilities become more readily available and less expensive, this increase will continue. Careful consideration of the potential savings resulting from partial or full decentralizations should be taken in the early phases of system design. If indeed, the results of such a study for a particular system indicate that a centralized configuration is most economical, that does not necessarily indicate that a decentralized configuration should never have been considered in the first place. Even though they are later rejected, as many options should be left open to the system designer as possible.

Although the problem of file assignment is important for the design of all message processing and communication systems, the other problems studied in this work relate more directly to systems in which the commun-

Figure 2,4 Variation in Processing Cost, Communication Cost, and Total System Cost with Degree of Centralization of File Assignments

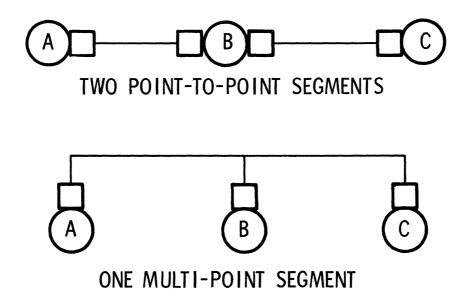

Figure 2.5 Comparison of Point-toPoint and Multi-Point Segments

ication facility is composed of leased private lines configured with a tree topology. This restriction of attention to tree networks deserves a word of justification. Although network reliability is an important consideration in system design, the additional cost of a redundant topology may not be justifiable. The many corporate communication networks operating today with a tree topology indicate a conscious decision that network reliability is not worth the additional cost. But even if redundancy is essential, the design of tree networks is important for cost minimization. One of the largest airline reservation systems has a communication network consisting of a basic tree network used during normal operation together with a minimal spanning tree used as a backup system when one of the links of the basic system fails. Further considerations explored in this research suggest that the random nature of message traffic is most economically handled with as few channels as possible. Hence, in many situations where there are alternate routes for message traffic, the system will be least expensive when only one route is used and the other closed down completely.

The cost of a private leased line network consists of two basic components, the line costs and the line interface costs. The line cost depends on the lengths of the lines leased and their bandwidth or maximum information transfer rate. The line interface costs depend on the actual transfer rate or capacity at which the lines are operated. By using different line interfaces, the same physical line may be operated at a variety of

capacities. Since higher capacity interfaces cost more, the system designer must choose interfaces to minimize cost but still satisfying the performance constraint.

The non-centralized leased line networks for inter-terminal communication facility have also been studied. The notion of multi-point segments is formulized and methods of finding segments which satisfy specified performance constraints are introduced. Multi-point segmentation is a technique used to reduce the number of line interfaces required for a communication facility. The basic technique is illustrated in Figure 2.5. In the upper diagram terminals A, B, and C communicate with the aid of two point-to-point communication lines which require four line interfaces. Traffic from terminal A to terminal C must be relayed through terminal B. In the lower diagram the three terminals are joined with a single multi-point line requiring only three line interfaces. In this case, each pair of terminals may communicate directly, but only one pair at a time. With certain traffic patterns, multi-point lines may be significantly less expensive than point-to-point line configurations.

When network traffics are low, interface costs are sufficiently smaller than line costs that the least expensive line configuration, the minimal spanning tree, is the optimal network topology. For higher traffics, the interface costs increase, and the selection of the optimal topology becomes a much more difficult problem. Methods for selecting inexpensive networks subject to a performance constraint are studied. These will be explained

Figure 2.6 Illustration of Changes in Edge Traffics and Total Traffic When File is Moved from One Node to an Adjacent Node

after a discussion of file assignment on trees and channel capacity allocation.

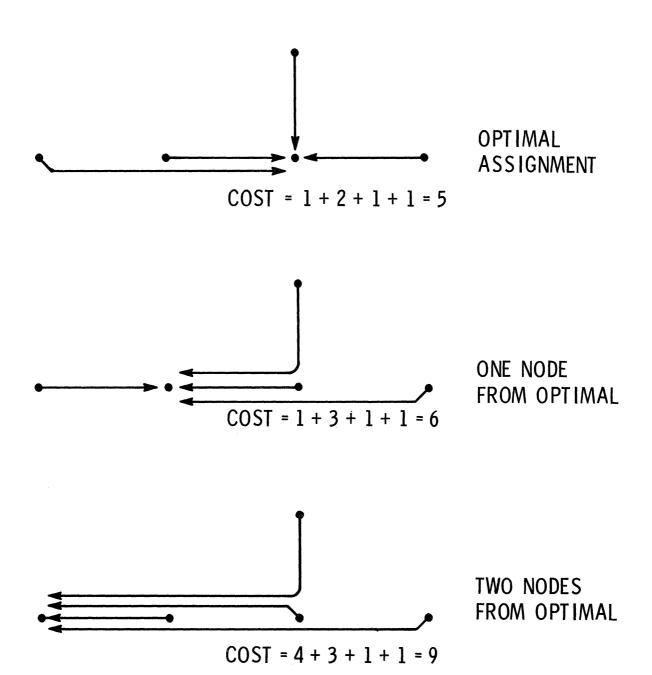

For a fixed tree topology, efficient methods of assigning files to optimal nodes have been developed. A single procedure is vaild for a wide variety of possible communication cost functions. The essential idea underlying this assignment procedure is illustrated in Figure 2. 6. In that Figure are shown the individual edge traffics and total edge traffic for a file with requests equally likely to come from any terminal assigned to or located at three different nodes. As the file is moved away from the optimal (lowest total traffic) terminal node, the traffics in certain edges of the tree increase, but none may decrease. Hence any cost function which is an increasing function of each of the edge traffics must increase too. In this manner, assigning files to minimize total traffics also minimizes any increasing function of the edge traffics. Many possible cost functions satisfy this condition, including some which accurately incorporate the stochastic nature of message flow.

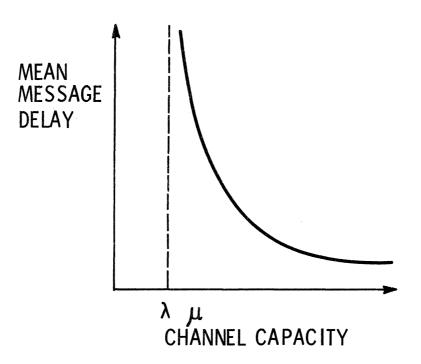

In the design of communication systems which must satisfy performance constraints on the delay of individual messages, such as the requirement that the average message delay be three seconds or less, it is impossible to ignore the randomness of message arrivals and lengths. Rather it is necessary to allocate additional communication channel capacity to reduce the expected additional communication channel capacity to reduce the expected delays, and to provide storage for messages when several arrive almost simultaneously. A graph of the reduction in message delay with an

increase in channel capacity is shown in Figure 2.7. As the capacity is increased, the delay decreases, but a point of diminishing returns is reached.

A number of other methods for reducing message delay besides additional capacity are also explored. Here we are concerned with the design of the message switching computers which would be placed at the nodes of a network of store-and-forward communication links. Borrowing heavily from the literature of queueing theory developed for scheduling jobs in computer central processors, a number of interesting message delay reducing schemes are evaluated. In general these message switching computers result in more efficient utilization of communication lines than simple fixed subchannel multiplexers.

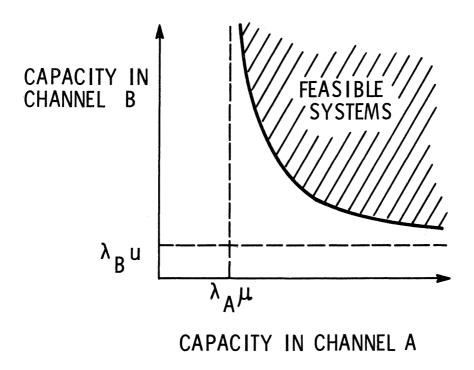

Another method used to reduce total capacity allocation in communication channels is possible when the measure of network performance is an average of performance measures on channels of the network. Such averaged measures are often appropriate for evaluating the performance of CMPC inter-terminal networks. Averaging channel responses allows the delay in one channel to be large while the delay in another is small, while keeping the average at an acceptable level. This is useful since the effect-iveness of additional capacity and the cost of additional capacity vary from channel to channel. This is illustrated in Figure 2.8 for a two channel case. In that figure is shown a curve of pairs of possible channel capacities which yield the same performance for the system. Since the cost of capacity is

Figure 2.7 Average Message Delay in a Communication Channel

Figure 2.8 Feasible Values of Channel Capacity in Two Channel Communication System with Performance Constraint

likely to be different in the two channels, it is necessary to find the least expensive point on the curve of constrant performance. In a simple two channel case, the selection of the most economical system satisfying the performance constraint is easy. For systems with many channels the problem is much more difficult. Several of these optimal channel capacity allocation problems have been solved.

#### 2. 3 A CMPC System Synthesis Procedure

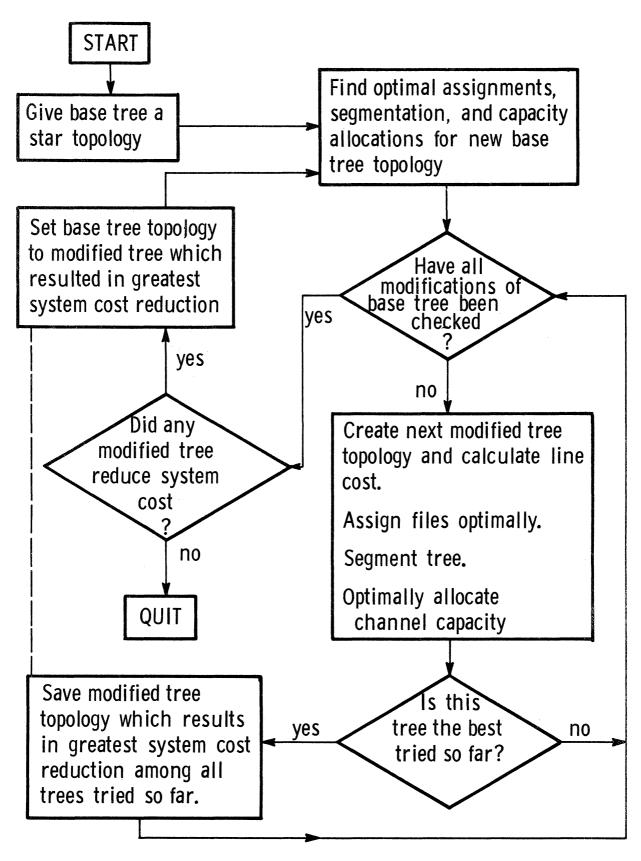

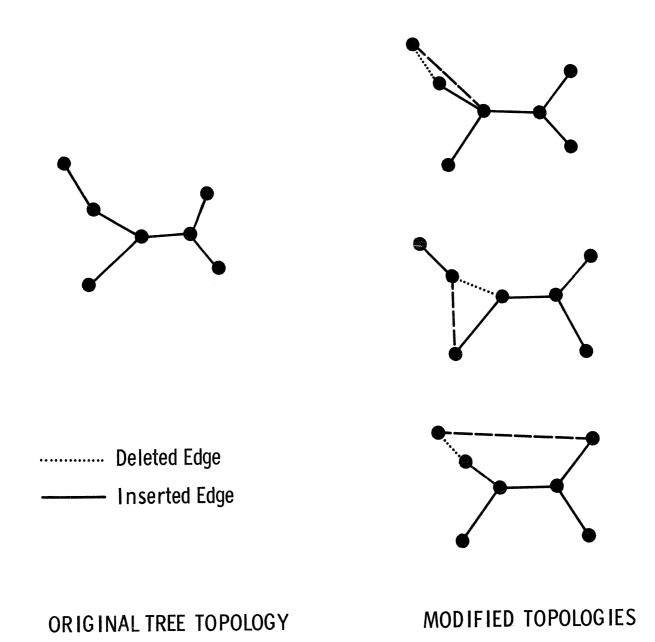

All of the design problems discussed so far are parts of a general design procedure for CMPC systems. This system design procedure separates a computationally infeasible problem into sub-problems amenable to optimal or efficient sub-optimal solutions and combines the solution of those subproblems into a solution to the original problem. The design procedure follows the methodology of Figure 2. 9. An initial configuration consisting of a star tree of leased lines, files assigned optimally, and channel capacity chosen optimally is selected. Then other configurations based on topologies which can be obtained from the base topology by the replacement of a single edge are constructed and the optimal system cost for each of these modified systems is calculated. A typical tree topology and several one edge modifiations are illustrated in Figure 2. 10. That modified topology which results in greatest reduction in system cost is selected as the new base topology. This iterative process of topology improvement continues until no further feasible cost reductions are possible.

Figure 2.9 A Methodology for Computer Message

Processing and Communication Design System

Figure 2.10 Modified Topologies Resulting from Tree Topology by Deletion of One Edge and Insertion of Another

Figure 2.11 CMPC System Design Methodology

The heuristic nature of the solution procedure and the lack of comparable procedures make the evaluation of this total system design procedure difficult. Several points of non-optimality are evident, but the degree of non-optimality introduced is difficult to estimate or bound. Since the procedure follows steps similar to those of a human system designer, and performs some of these steps optimally, it can be expected to produce better solutions than seat-of-the-pants design procedures. In general, as CMPC systems become larger and more complex, the ability of the human designer to cope with the design problems will decrease. The availability of comprehensive procedures such as the one developed here, which handle large systems as well as small systems can contribute to the development and feasibility analysis of such large systems.

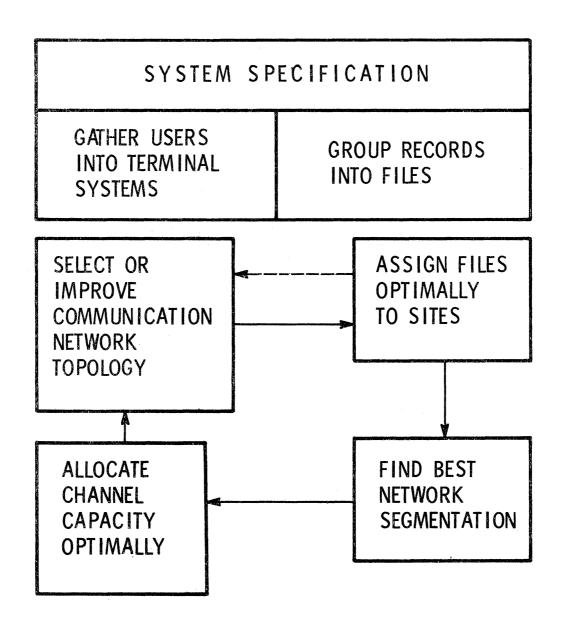

A sequence of steps used by a CMPC system designer is shown in Figure 2. 11. The system design may be conveniently separated into two basic activities, the system specification and the system design itself.

The activities that comprise system specification usually involve non-technical inputs or constraints. For our purposes, according to the problem types studied, these basic inputs and constraints include the terminal systems, the file system, and the performance constraint. Other real inputs are the cost functions for the various communication and processing system structures allowable in the system design.

The problem of gathering the users into terminal systems and locating the terminals for each group of users is a difficult and interesting one,

which has not been addressed in this work. When complete freedom is given to the designer, this problem may be formalized and an optimal solution sought. More often, however, the user groups and terminal locations are specified by non-technical considerations, and therefore are not appropriate topics for research of academic interest.

Another important phase of system specification is the construction and organization of the file system whose records are to be made accessible by the CMPC system to the users. Here too, decisions are often made administratively and not subject to engineering design considerations. It should be noted, however, that were better design tools more widely available, there would be more dependence on the system analysts in these decisions.

Once the terminal systems and file systems have been fixed, the design of the inter-terminal CMPC system may begin. At this point the design procedure specified earlier begins. This system design procedure attempts to find the jointly optimal choice of file site assignment, communication network topology (restricted to trees), tree network segmentation, and segment channel capacity allocation while guaranteeing an acceptable measure of system performance. This problem is very difficult. Straightforward design techniques are computationally infeasible for even the fastest computers.

The validation of such a comprehensive and complex design procedures is a difficult problem, because of the lack of theoretical guidelines or solutions known to be optimal. This total design procedure serves both as a

useful design tool and as a frame work illustrating the relationship among the subproblems discussed earlier. Each step of the procedure is important in the overall design process. One evidence of this, explored in the example of the next section, is that more costly solutions are obtained when one or more of the optimization steps is deleted. These studies also relate the procedure to manual design techniques, since often system designers omit one or more of these steps attempting to achieve computational feasibility. In particular, the optimal file assignment and optimal segment channel capacity allocation are often entirely ignored. In other cases where these problems are not ignored entirely, only partially optimal or very crude design procedures may be used for their solution.

### 2.4 Example

In this section a CMPC system design for a specific problem is presented. Several other system designs are also presented to illustrate the effect of ignoring some of the problem variables. Although the entire design procedure is of interest because of the complex problems it solves, the basic emphasis of this section will be relating the separate steps of the general optimization procedure, and showing their effect on the total system design. With other cost functions than used in this example, the relative importance of the steps of the design procedure might be different. Where possible, however, general guidelinges will be drawn.

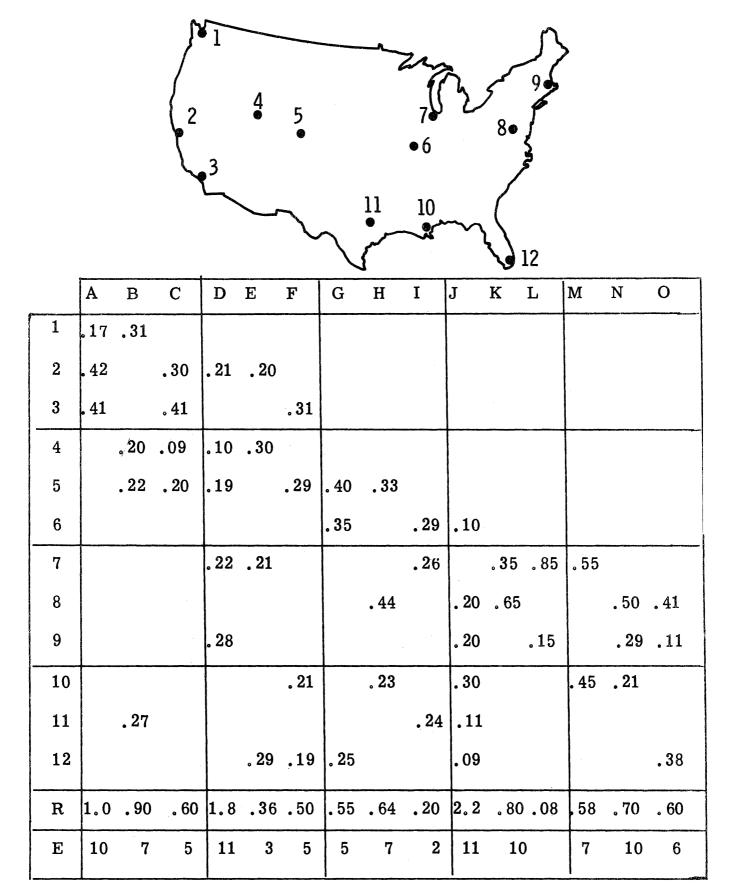

The system to be designed in this section represents a small airline reservation system. The terminal locations and files are specified by the

Figure 2.12 Terminal Locations and File Parameters for Design Example

Figure 2.13 Line Cost Function

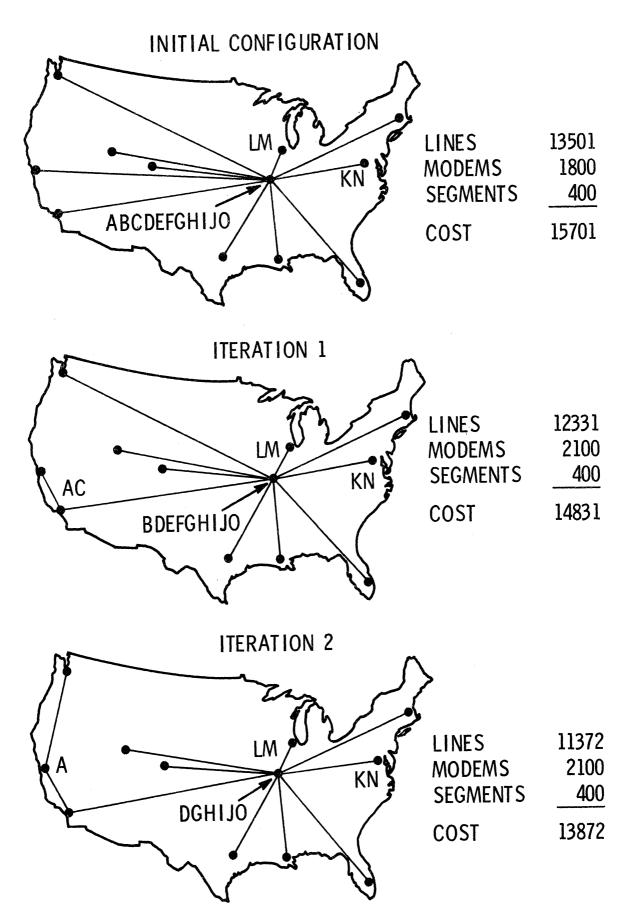

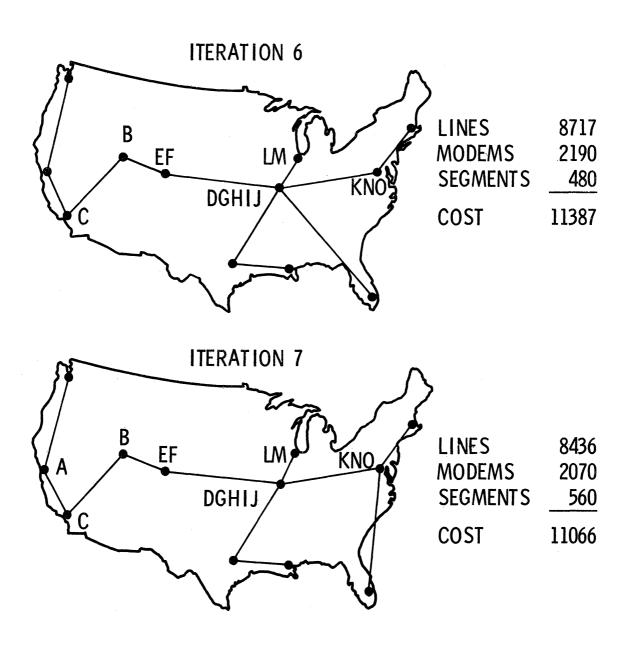

Figure 2.14 (Continued on the following page)

Figure 2.14 (Continued on following page)

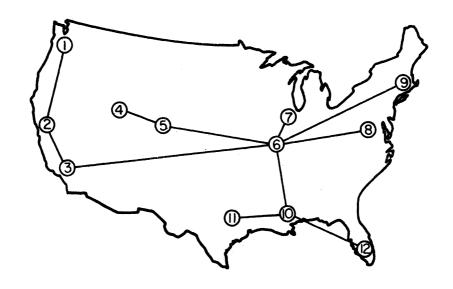

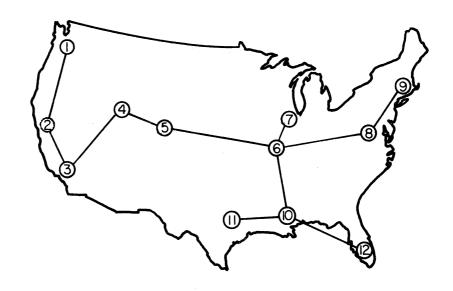

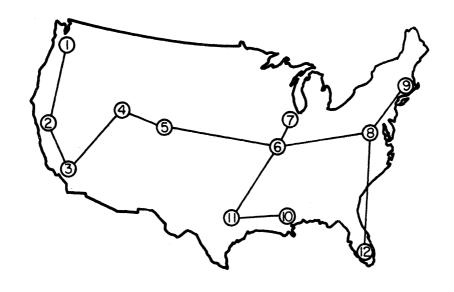

Figure 2.14 CMPC System Designs Selected by Each Successive Improvement Step

parameters of Figure 2. 12. The inter-terminal communication system will consist of store-and-forward concentrators joined by multipoint segments. Line interface speeds are available only in the values 500, 1000, 1500, 3000, 3500, 4000 and 5000 bps. These values correspond to higher actual transmission rates with redundancy for error correction and line control taken into account in the lower TRIB values given. Modems for these lines cost respectively 15, 30, 45, 90, 105, 120, 150 dollars/month rent. In addition, each segment requires a single line control unit leasing for \$80/month. Line costs are given by the graph of Figure 2. 13. No consideration of processing cost is given in this example, because maintaining message switching computers at each terminal accounts for the fixed cost, and the processing and file costs are assumed to be independent of file locations. The three variable costs of the problem are the line cost, the modem cost and the segment control cost.

The initial configuration and the system design after each iterative improvement step with these costs constraints are shown in Figure 2.14. At each step of the procedure all possible single edge replacements are examined with optimal file assignments on the new tree, segmentation to reduce network traffic, and optimal segment capacity allocation. The tree yielding maximal cost reduction is chosen and the next iteration begun. The final system design is illustrated in Figure 2.20 with all segment traffics and capacities indicated. The basic pattern of the iterative improvement is to reduce the line cost as much as possible; as the line cost decreases,

however, network traffics increase, and modem costs increase. In the example, modem costs and segment costs both increase with the reduction in line costs. The procedure terminates when the next line cost reduction exceeds the increase in modem cost, or when no additional line cost reductions can be made.

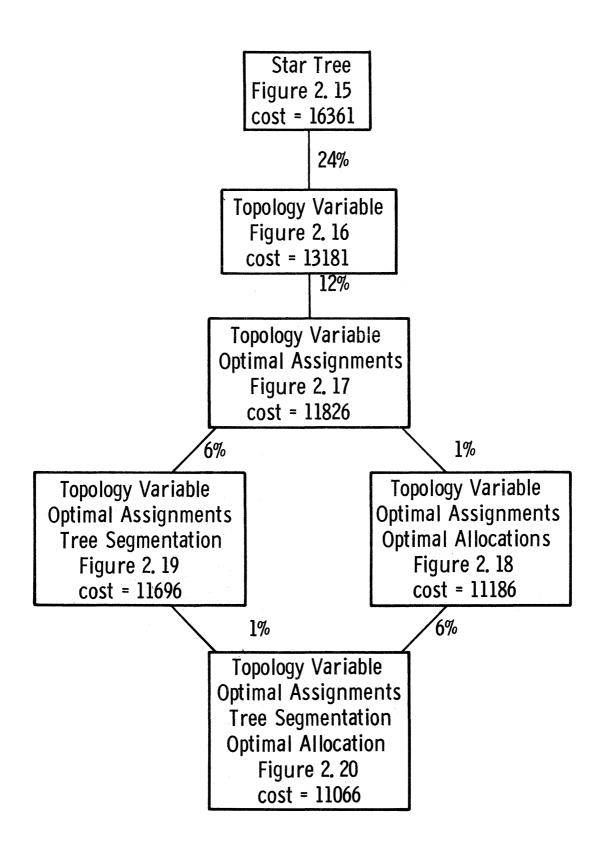

This solution will be compared to five alternatives, exhibited in Figures 2. 15 through 2. 20. In each of these five designs one or more steps of the procedure has been omitted or replaced by a non-optimal design technique.

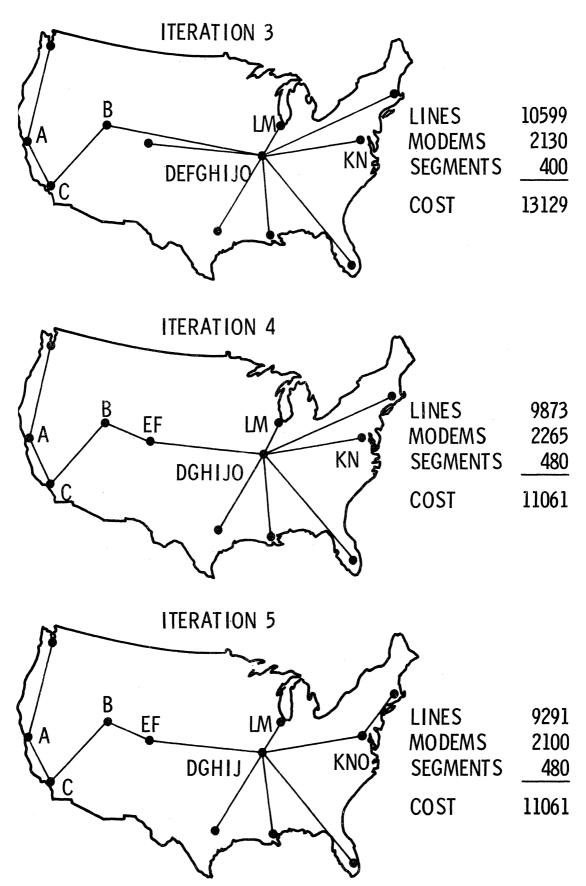

Figure 2. 15 exhibits the least sophisticated design for the MPC system example. In this system, all files are located at a single terminal, modems are chosen to have the same transmission rate (the lowest possible), each link is a separate segment, and no attempt to minimize line cost other than the selection of the central node is made. The solution cost is high, but the design is simple enough to be performed manually without the aid of computers.

Figure 2. 16 exhibits the system design when there is an iterative tree improvement selection, but no additional attempts at optimization are made. All files are located at the single best node, and each link is an individual segment. The tree improvement continues to reduce total link cost until a constraint on the maximal link traffic (necessary because modem capacity is limited) is broken.

| SEGMENT<br>NUMBER | NODE<br>SET | TRAFFIC      | CAPACITY     | MODEM<br>COST |

|-------------------|-------------|--------------|--------------|---------------|

| 1                 | 1,6         | 673          | 2000         | 120           |

| 2                 | 2,6         | 1575         | 3000         | 180           |

| 3                 | 3,6         | <b>121</b> 6 | <b>2</b> 500 | 150           |

| 4                 | 4,6         | 783          | 2000         | 120           |

| 5                 | 5,6         | 1849         | 3000         | 180           |

| 6                 | 7,6         | 1833         | 3000         | 180           |

| 7                 | 8,6         | 2837         | 4000         | 240           |

| 8                 | 9;6         | 1900         | 3000         | 180           |

| 9                 | 10,6        | 1976         | 3000         | 180           |

| 10                | 11,6        | 799          | 2000         | 120           |

| 11                | 12,6        | 1144         | 2500         | 150           |

|                   | •           |              |              |               |

$\begin{array}{ccc} \text{MODEM} & \text{COST} & 1800 \\ \text{SEGMENT} & \text{COST} & 880 \\ \text{LINE} & \text{COST} & \underline{13501} \\ \\ \text{TOTAL} & \text{COST} & 16181 \\ \end{array}$

Figure 2.15 Non-Optimal System Design Example

| SEGMENT<br>NUMBER | NODE<br>SET | TRAFFIC    | CAPACITY | COST |

|-------------------|-------------|------------|----------|------|

| 1                 | 1,2         | 673        | 4000     | 240  |

| 2                 | 2,3         | 2248       | 4000     | 240  |

| 3                 | 3, 6        | 3465       | 4000     | 240  |

| 4                 | 4,5         | <b>783</b> | 4000     | 240  |

| 5                 | 5,6         | 2623       | 4000     | 240  |

| 6                 | 6,7         | 1833       | 4000     | 240  |

| 7                 | 8,6         | 2837       | 4000     | 240  |

| 8                 | 9, 6        | 1900       | 4000     | 240  |

| 9                 | 10,6        | 3920       | 4000     | 240  |

| 10                | 10,11       | 799        | 4000     | 240  |

| 11                | 10,12       | 1144       | 4000     | 240  |

|                   |             |            |          |      |

| MODEM   | COST | 2640  |

|---------|------|-------|

| SEGMENT | COST | 880   |

| LINE    | COST | 9661  |

| TOTAL   | COST | 13181 |

Figure 2.16 System Design Example with Network Topology Selection

| SEGMENT<br>NUMBER | NODE<br>SET | TRAFFIC              | CAPACITY | MODEM<br>COST |

|-------------------|-------------|----------------------|----------|---------------|

| 1                 | 1,2         | 673                  | 4000     | 240           |

| 2                 | 2,3         | 1978                 | 4900     | 240           |

| 3                 | 3,4         | 1587                 | 4000     | 240           |

| 4                 | 4,5         | 2181                 | 4000     | 240           |

| 5                 | 5,6         | <b>2</b> 926         | 4000     | 240           |

| 6                 | 6,7         | <b>1</b> 66 <b>2</b> | 4000     | 240           |

| 7                 | 6,8         | 3602                 | 4000     | 240           |

| 8                 | 8,9         | 1900                 | 4000     | 240           |

| 9                 | 10,6        | 3920                 | 4000     | 240           |

| 10                | 10,12       | 1144                 | 4000     | 240           |

| 11                | 10,11       | 799                  | 4000     | 240           |

|                   |             |                      |          |               |

| MODEM   | COST | 2640  |

|---------|------|-------|

| SEGMENT | COST | 880   |

| LINE    | COST | 8306  |

|         |      |       |

| TOTAL   | COST | 11826 |

Figure 2.17 System Design Example with Optimal File Assignments and Network Topology Selection

| SEGMENT<br>NUMBER | NODE<br>SET | TRAFFIC | CAPACITY | MODEM<br>COST |

|-------------------|-------------|---------|----------|---------------|

| 1                 | 1,2,3,4     | 2727    | 5000     | 600           |

| 2                 | 4,5,6       | 3905    | 5000     | 450           |

| 3                 | 6,7         | 1622    | 5000     | 300           |

| 4                 | 6,8         | 4062    | 5000     | 300           |

| 5                 | 8,9         | 1900    | 5000     | 300           |

| 6                 | 12,8        | 1144    | 5000     | 300           |

| 7                 | 10,11,6     | 2776    | 5000     | 450           |

|                   | • •         |         |          |               |

| MODEM   | COST | 2700  |

|---------|------|-------|

| SEGMENT | COST | 560   |

| LINE    | COST | 8436  |

| TOTAL   | COST | 11696 |

Figure 2.18 System Design Example with Optimal File Assignment, Tree Segmentation, and Network Topology Selection

| SEGMENT | NODE  | TRAFFIC | CAPACITY | MODEM |

|---------|-------|---------|----------|-------|

| NUMBER  | SET   |         |          |       |

| 1       | 1,2   | 673     | 1000     | 60    |

| 2       | 2,3   | 1978    | 3000     | 180   |

| 3       | 3,4   | 1587    | 3000     | 1:80  |

| 4       | 4,5   | 2181    | 3000     | 180   |

| 5       | 5,6   | 2926    | 3500     | 210   |

| 6       | 7,6   | 1662    | 3000     | 180   |

| 7       | 8,6   | 3602    | 5000     | 300   |

| 8       | 9,8   | 1900    | 3000     | 180   |

| 9       | 10,6  | 3920    | 5000     | 300   |

| 10      | 11,10 | 759     | 1500     | 90    |

| 11      | 12,10 | 1144    | 1500     | 90    |

|         | •     |         |          |       |

|         |       |         |          |       |

| MODEM   | COST | 1950  |

|---------|------|-------|

| SEGMENT | COST | 880   |

| LINE    | COST | 8306  |

| mom A r | COCT | 11100 |

| TOTAL   | COST | 11136 |

Figure 2.19 System Design with Optimal File Assignment Optimal Edge Capacity Allocation and Network Topology Selection

| SEGMENT<br>NUMBER | NODE<br>SET | TRAFFIC | CAPACITY     | MODEM<br>COST |

|-------------------|-------------|---------|--------------|---------------|

| 1                 | 1,2,3,4     | 2727    | 3500         | 420           |

| 2                 | 4,5,6       | 3905    | 5000         | 450           |

| 3                 | 7,6         | 1622    | 3000         | 180           |

| 4                 | 11,10,6     | 2776    | 4000         | 360           |

| 5                 | 8,6         | 4062    | <b>5</b> 000 | 300           |

| 6                 | 9,8         | 1900    | 3000         | 180           |

| 7                 | 12,8        | 1144    | 3000         | 180           |

| 7                 |             | 1144    | 3000         | 180           |

| MODEM COST   | 2070  |

|--------------|-------|

| SEGMENT COST | 560   |

| LINE COST    | 8436  |

| TOTAL COST   | 11066 |

Figure 2.20 System Design Example with Optimal File Assignment,

Tree Segmentation, Optimal Segment Capacity Allocation,

and Network Topology Selection

The system design of Figure 2. 17 improves the solution of Figure 2. 16 by assigning each file to its optimal site. This reduces traffic in the links so that additional iterative steps reduce total line cost as well. No attempts at segmentation or optimal channel capacity allocation are made.

The system design of Figure 2. 18 considers tree segmentation to reduce system traffic, resulting in a further reduction in total system cost. It can be seen, by comparing Figure 2. 18 with 2. 17 that considerations of tree segmentation may alter the final system topology. Hence it is important to consider the segmentation of each possible tree improvement, rather than simply adding the segmentation procedure to the system design obtained by selecting a topology on the basis of line lengths alone

The system design procedure whose final design is exhibited in Figure 2. 18 adds optimal segment capacity allocation to the procedure resulting in Figure 2. 19, but does not perform a segmentation on each tree alteration in the iterative improvement step. In this example, adding this optimal capacity allocation does not change the final system topology, because the total cost of the modems is considerably less than the cost of the topology alterations. For systems with higher traffics, capacity allocation might also affect the system topology.

Figure 2. 20 is the result of the most comprehensive design procedure of this section. Each new tree in the iterative improvement steps is given optimal file assignments, a segmentation to reduce system traffics, and optimal segment capacity allocation.

These six design procedures are compared for the airline example in Figure 2.21, showing the cost savings and percentages resulting from the consideration of more design variables in the system selection procedures. Although these exact reductions cannot be expected for another system, there are some general conclusions to be drawn for systems using the same cost functions, but possibly different file and terminal systems. It is clear that segmentation does not result in such a large reduction as does optimal channel capacity allocation. This would be reversed if the fixed cost associated with individual system segments were higher. Optimal assignment also resulted in an improvement in the system cost, both by its effect on feasible topologies and for the actual reduction in link traffics (and total modem capacity).

It would be unfair to claim now that the comprehensive procedure has been shown universally valid, or even useful. Rather this example is intended to demonstrate that many different system designs can be evaluate quickly and the least costly chosen, that the procedure of Figure 2.9 provides a convenient framework for evaluating various types of systems, and that for this example the most general design was significantly less costly than the most restricted design. Note that system design tools such as this procedure are most useful for the very large systems which are the most difficult to analyze by hand, and that a small percentage improvement may represent a very considerable cost savings in a large and expensive system.

Figure 2.21 Comparison of Several CMPC System Design Procedures

#### 2. 5 Conclusion

A precise mathematical model of the systems being studied is formulated to draw attention to the fundamental subsystems and to clarify the basic independent variables of the design processes. Systems considered must have a large data base organized into record files, widely distributed users, an on-line communication network joining users to data base sites, a quantitative performance measure and specified performance constraints. The most general system model studied uses a queuing model for individual communication channels, with the channel interconnections specified by a weighted linear graph. The data base is assumed to be organized into files of homogeneous records, and the processing costs are specified by a single function of the number of messages processed.

One major problem area studied is the determination of the optimal number and locations of sites for the system files. Several basic properties of file site assignment on linear graphs are demonstrated and used in efficient procedures for file assignment.

When the file locations are specified, the communication requirements of the system are known. A second major problem area considered is the optimal design of communication channels and networks of these channels. A through study of stochastic message transmission channels has been undertaken. The effects of channel capacity with one or more channels, message length distributions, message retransmission order, and departures from the model assumptions on message delay are studied, both analytically and

by simulation. Several channel and network performance measures are defined and compared. The problem of the optimal allocation of channel capacity among the channels of a network is solved for several important system models. A complete set of guidelines is given to aid the designer of communication systems and channels.

The third major problem area studied is the optimal design of communication network topologies. Several previously available techniques for the design of centralized networks are critically evaluated. New techniques for the design of centralized and non-centralized networks are presented. These new procedures more faithfully model communication networks than the other procedures by including more realistic cost considerations, and yield more general solutions.

Finally the solution procedures of these problems are integrated into a systematic design procedure for a general class of computer message processing and communication systems. An example of a complete system design is given.

Some specific contributions of this research, arranged in no particular order, are listed below.

- 1. A comprehensive model of on-line Message Processing and Comm unication Systems has been developed which explicitly considers each of the following

- a) Communication network line topology

- b) Communication network tree segmentation into multi-point

segments

- c) Optimal allocation of communication channel capacity to minimize cost while maintaining acceptable system performance

- d) Variation in inquiry origins for separate files and its effects on optimal file assignment

- e) Processing cost for messages and storage cost for files

- f) The stochastic nature of message requests

- g) One or more copies of each file

The model allows the introduction of very general cost structures

in each of the basic sub-systems.

- 2. A procedure for the design of Computer Message Processing and Communication systems has been devised which allows effective consideration of each of the design variables included in the CMPC model. While not necessarily yielding optimal system designs, this procedure yields designs of lower cost and greater generality than those generated by other currently available design procedures.

- 3. Hakimi's theorem [4] that optimal assignments of files lie at nodes of a linear graph has been extended with a simplier proof to a much more general class of communication cost functions.

- 4. Optimal assignments of files on a tree graph are shown to be independent of the edge traffics. Hence, optimal assignment to minimize induced traffic also minimizes a wide class of other

- cost functions, namely those monotone non-descreasing in each edge traffic.

- 5. A careful derivation of the mean message delay in a network of Poisson queues has been given. This exhibits clearly the underlying assumptions necessary to the use of this model for communication networks.

- 6. Efficient procedures for allocating channel capacity in a Poisson message network have been developed and its validity proved carefully. These procedures use a variety of response functions, both continuous and discrete.

- 7. A careful study of store-and forward message transmission channels has been made. The effects of message length distribution, retransmission order, buffer size, and channel capacity allocation upon mean message delay have been studied by numeric, simulation, and analytic techniques. A comprehensive set of channel design guidelines is presented.

- 8. The concept of segmentation of a tree and ite relationship to non-centralized network design has been formalized and studied.

Efficient procedures for the selection of good segmentations of a fixed tree have been developed.

- 9. Procedures for the synthesis of centralized networks of multipoint and multiplexed segments have been developed which yield designs superior to any procedures currently available.

10. A method of calculating the mean waiting time of and mean number in system for Poisson S-server queues with non-homogeneous service rates has been devised. This method uses a combination of analytic and numeric techniques.

#### References For Section 2

- 1) "Look Ahead" Datamation, April 1968, p. 53.

- 2) James Martin, Design of Real-Time Computer Systems, Prentice-Hall, Inc., Englewood Cliffs, N.J., 1967, p. 629.

- 3) C. DeGabrielle, "Design Criteria for an On-Line Nationwide Order Processing System", pp. 71-75 in Disk File Applications, American Data Processing, Inc., 1964, Detroit, Michigan.

- 4) S. L. Hakimi, "Optimum Distribution of Switching Centers in a Communication Network and Some Related Graph Theoretic Problems", Operations Research vol. 13, no. 3, 1965.

- 5) V. K. M. Whitney, "A Study of Optimal File Assignment and Communication Network Configuration in Remote-Access Computer Message Processing and Communications Systems", SEL Technical Report no. 48, The University of Michigan, Ann Arbor, Sept. 1970.

# 3. MULTIPROGRAMMED AND MULTIPROCESSOR COMPUTER SYSTEMS

In this section we discuss research into problems related to the operational optimization of multiprogrammed and multiprocessor computer systems. We first present (3.1) a very comprehensive mathematical model of complex computing systems using storage hierarchies and multiprogramming order to predict and control the behavior of such systems. This model has been implemented in the form of a fast and highly interactive computer program which leads easily to an incremental optimization of the computer systems under study by providing the user with comprehensive performance measures as model parameters are varied. The research outlined in section 3.2 uses queuing theoretic approach to investigate optimal task scheduling rules in heavily loaded multiprogrammed computer systems. The effects of reentrant procedures and sharing of information in such systems is also investigated. Section 3.3 is concerned with the problem of breaking up programs into pages in such a way as to minimize the number of page faults. Using an algorithm developed for the solution of a particular quadratic programming problem efficient solution technique for the above partitioning problem is presented. Finally the scheduling of programs in a multiprocessor computer system is investigated in section 3.4.

# 3.1 Multiprogrammed Systems Using Storage Hierarchies

The design and application of large computing systems involves considerable risk. One can draw a parallel between those who have designed and applied today's computing systems and those who, in the early days of flight, strapped wings to their backs and jumped from the roofs of barns. Neither had adequate methods of predicting system performance. The work reported here attempts to contribute to computer system technology through the development of improved methods of predicting system performance.

Throughout the development of computing systems there has been an effort to make a given hardware technology perform better as a system. The primary emphasis in the early days of development was on hardware technology, However, as computing systems have progressed, there has been a continued and growing interest in the design of system which makes the best and most efficient use of a given hardware technology.

One important method of achieving efficient use of a given hardware technology has been the use of storage hierarchies. Storage hierarchies are not unique to computer systems. Your pocket, your desk or dresser drawer and your basement represent a storage hierarchy. The basic idea is simply to store those items used most frequently in as easily accessible location. Those items seldom used may be stored

in less accessible and correspondingly less costly locations.

The storage hierarchy was first implemented in a computing system developed at the University of Manchester in England in 1949. As computer systems have progressed, two things have happened.

First, the complexity of the hierarchy itself has increased. We can easily locate systems with 5,6 or more different kinds of storage hardware capability. For instance, registers, cores, drums, disks, data cells, magnetic tapes, punched cards, and punched paper tape. A second and very important change has occurred in the management responsibility of the hierarchy.

The gains achieved by the storage hierarchy have imposed considerable burden upon the programmer. At the outset the programmer was responsible for deciding what information should be stored on what device at each instant of time. In addition the programmer was responsible for carrying out the necessary operations required to move the information about as required. Lastly and very important, the programmer was responsible for keeping track of how and where everything was stored as it was moved about in the system. As we have progressed and hierarchies have become more complex the operating systems and hardware have assumed these responsibilities in varying degrees. In some case all responsibilities for management of a hierarchy have been assumed by the operating system and/or hardware and the hierarchy is invisible to the programmer.

Another area of computer systems development has been in the use of multiprogramming. A computer is often limited by its slowest (or most overworked) component, often the IØ device. One of the methods used to alleviate this problem has been multiprogramming or the practice of working with more than one user program at a time.

One of the effects of multiprogramming is to provide the system with a more balanced workload. If a system processes one program at a time, it will find some programs using a great deal of CPU resources and leaving the IØ devices idle, while others leave the CPU idle and do voluminous IØ. On the other hand, if a system is processing 10 or 20 programs at once, it is unlikely that the system will see this group of programs exhibit the wide variations in resource demand exhibited by the individual programs in the group. In other words system loading is more consistent and predictable when the sample space grows larger.

The second effect of multiprogramming is to introduce parallel paths in the workload as seen by the computing system. If a computing system must follow a single thread of execution, a delay in any part of the system holds up the entire system. Multiprogramming is one way of providing the necessary parallel paths of execution, which if properly used, can increase resource utilization.

The difficulty with multiprogramming is complexity. The problems of resource scheduling are difficult. The problems of protecting one user from another, protecting the operating system itself, and charging for resource

use become most complex. However, the rewards for efficient resource utilization can be great. There has been considerable motivation for complexity in the effort to better utilize computing system resources. This has been added to by the response requirements of time-sharing and real-time systems.

This need for complexity has placed the modern computing system outside the capability of man's unaided intuition.

#### 3.1.1 The Nature of the Problem

In very few words the problem is that of predicting and controlling the behavior of complex computing systems using storage hierarchies and multiprogramming.

A computing system using a storage hierarchy generally involves 2 or more different types of storage devices. Different device types have widely varying performance characteristics. Drums, cores and disks all behave differently under load. A system's performance may be determined by a complex balance of workload throughout the system of devices, or may be determined by the performance characteristics of a single overworked device.

User programs can be big or small. They can access data in a serial or random manner. They can do large quantities of I0 or almost none at all.

The data paths and routing of information influences the load seen by storage devices. The logical record sizes throughout the system also influence the load seen by storage devices and in turn their response times.

The number of programs running in a multiprogrammed system effects the storage allocations of user programs. This in turn influences the demands placed on the system by user programs.

All of these factors and many others combine to create an enormously complex and remarkably difficult analysis problem. It is simply difficult to determine what a given system will and will not do in a given circumstance. It is even more difficult to design such systems especially if some kind of optimal or near optimal design is required.

# 3.1.2. Objectives

The specific objective of this research is to develop and demonstrate a mathematical model of a computing system. The computing systems in question here fall into the class of those systems using storage hierarchies of 2,3 or more levels and multiprogramming. The model developed exhibits the following characteristics:

- 1. The model includes the effects of user program behavior, operating system characteristics and hardware performance.

- 2. The model is versatile and easily applied to a wide range

of system configurations. The model is useful as a tool for the investigation of computing systems in general as well as applicable to the detailed investigation of a particular system.

- 3. The model is useful as a tool for both analysis and optimization.

- 4. The results obtained from the model approach the accuracy and realism of those obtained from simulation models.

# 3.1.3. The Model

At this point we will attempt a broad preview of the model which has been developed.

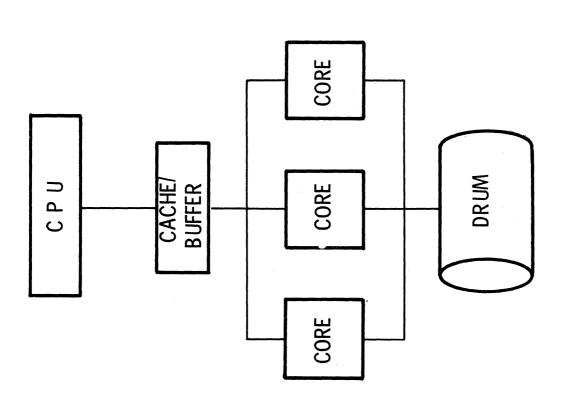

The overall model for computer system analysis is shown in Figure 3.1. On the left we see 3 categories of independent variables. First we have the user program description. This includes independent variables such as the size of the user programs and other characteristic of the user program behavior. Next there is storage device description. This includes such items as drum RPM, disk seek time and variables relevant to storage device performance. Last we have data traffic dependencies and architecture. This includes CPU performance characteristics, logical record size, data transfer timing dependencies and other global system characteristics. As an output for the model we show performance. In the narrow sense,

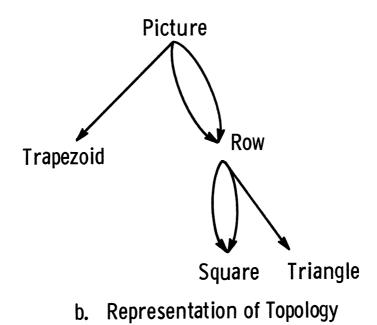

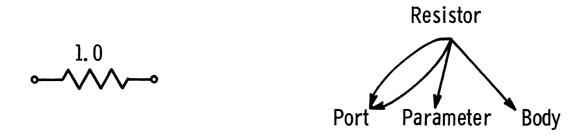

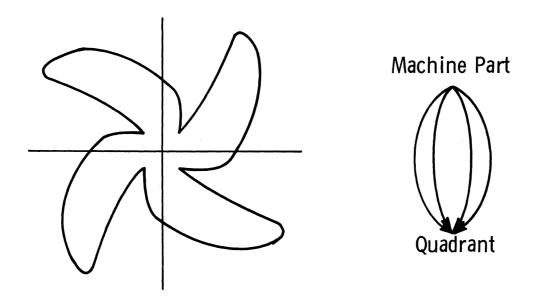

performance is defined as the mean rate at which the collection of user programs running on the system make reference or access to data and instructions. In the broad sense the performance also includes many details such as mean queue lengths at various devices in the storage system and CPU utilization.