# DESIGN TECHNIQUES FOR ON-CHIP GLOBAL SIGNALING OVER LOSSY TRANSMISSION LINES

by

Jun Young Park

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctoral of Philosophy (Electrical Engineering) in The University of Michigan 2008

#### **Doctoral Committee:**

Associate Professor Michael Flynn, Chair Professor Amir Mortazawi Professor Kim A. Winick Associate Professor Dennis M. Sylvester

To Mom and Dad

#### Acknowledgements

Any single work was impossible without the invaluable support of many people. I am especially very grateful to my research advisor Prof. Michael Flynn for his encouragement and support. I am so lucky that I had a chance to work with him. I really learned a lot to be a good student and a good person even though not enough yet. I also thank all the other committee members, Prof. Amir Mortazawi, Prof. Dennis M. Sylvester, and Prof. Kim Winick for their invaluable suggestions and time.

I thank all former and current members of Prof. Flynn's group for their assistance with their friendship: Dr. Fatih Kocer, Dr. Jia-yi Chen, Paul Walsh, Dr. Sunghyun Park, Ivan Bogue, Dan Shi, Jaeyoung Kang, Mark Ferriss, Jongwoo Lee, Shahrzad Naraghi, Andres Tamez, Chun Lee, Jorge Pernillo, David Lin, LiLi Lim, and Hyo-Gyuem Rhew.

I am very grateful to my mother, father, my sister, and my brother for their love, encouragement, and support.

### **Table of Contents**

| Dedicati  | ion                                 | ii    |  |  |

|-----------|-------------------------------------|-------|--|--|

| Acknow    | ledgements                          | iii   |  |  |

| List of F | List of Figuresvii                  |       |  |  |

| List of T | List of Tablesxvii                  |       |  |  |

| Abstract  | t                                   | xviii |  |  |

| Chapter   | ·                                   |       |  |  |

| I.        | Introduction                        | 1     |  |  |

|           | 1.1. On-chip wires                  | 3     |  |  |

|           | 1.2. Termination                    | 5     |  |  |

|           | 1.3. Pre-emphasis and pulse shaping | 7     |  |  |

|           | 1.4. Modulation                     | 9     |  |  |

|           | 1.5. Skewed Pulsed Buses            | 10    |  |  |

|           | 1.6. Dual VDD buffer                | 11    |  |  |

|           | 1.7. Dissertation outline           | 12    |  |  |

| II.       | On-chip parallel and serial links   | 13    |  |  |

|           | 2.1. Bus bases global link          | 14    |  |  |

|           | 2.2. Serial global link             | 20    |  |  |

|           | 2.3. 20mm link design example       | 27    |  |  |

| III. | Multi-stage LC oscillators with capacitive coupling          | 38    |

|------|--------------------------------------------------------------|-------|

|      | 3.1. Phasor diagram                                          | 38    |

|      | 3.2. Capacitive coupling                                     | 48    |

|      | 3.3 Two stage oscillator with capacitive coupling            | 56    |

|      | 3.4 Prototype circuits                                       | 57    |

|      | 3.5 Conclusion                                               | 59    |

| IV.  | High-speed clock generation with a low-jitter PLL with capac | itive |

|      | coupling                                                     | 60    |

|      | 4.1. PLL Fundamentals                                        | 60    |

|      | 4.2. A low-jitter PLL with capacitive coupling               | 80    |

|      | 4.3. Image rejection ratio(IRR)                              | 85    |

|      | 4.4. Measurement                                             | 92    |

|      | 4.5. Conclusion                                              | 96    |

| v.   | On-chip serial signaling                                     | 97    |

|      | 5.1. Overall block diagram                                   | 98    |

|      | 5.2. TX (transmitter)                                        | 99    |

|      | 5.3. RX (receiver)                                           | 106   |

|      | 5.4. Error-check                                             | 114   |

|      | 5.5. Measurements of Prototype                               | 119   |

|      | 5.6. 20Gbps On-chip Serial Signaling                         | 127   |

|      | 5.7. Conclusion                                              | 132   |

| VI.  | Summary and Future Work                                      | 133   |

|      | 6.1. Summary                                                 | 133   |

| 6.2. Future work | 13 |

|------------------|----|

|                  |    |

| Bibliography     |    |

## **List of Figures**

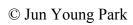

| Figure 1.1: Physical structure of wires; (a) is designed based on the RLC                       |

|-------------------------------------------------------------------------------------------------|

| model[12] (s is the space between signal lines and w and t are width and thickness of the       |

| signal lines respectively.) (b) is designed based on the LC model[10]                           |

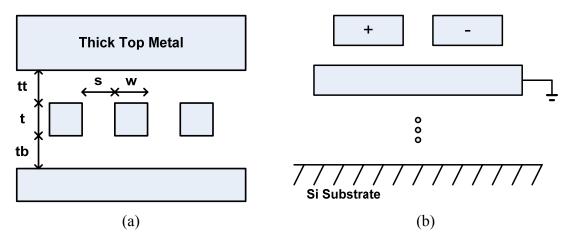

| Figure 1.2: Twisted differential bus; This is effective to cancel neighbor-to-                  |

| neighbor crosstalk                                                                              |

| Figure 1.3: Differential line with distributed equalization[13]; When clock signal              |

| is high, both lines are set to same voltage (pre-equalizing), so data can be sent only          |

| during half the period of the clock cycle.                                                      |

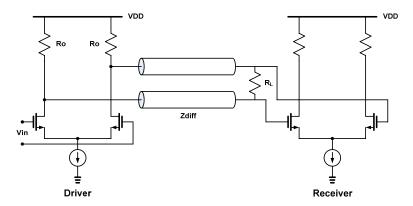

| Figure 1.4: A simple configuration for the driving and termination[14]; Since the               |

| input differential pair in the data driver is operating at either off or saturation region, the |

| output impedance of the data driver is approximately equal to the impedance of the load         |

| resistors. Therefore, same impedance for $R_o$ and $Z_{diff}$ allows impedance matching at the  |

| data driver                                                                                     |

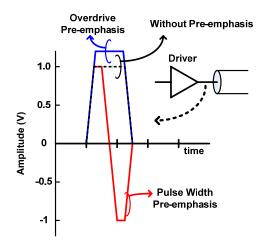

| Figure 1.5: Pre-emphasis at the transmitter; overdrive buffering[13] and pulse-                 |

| width pre-emphasis[12]                                                                          |

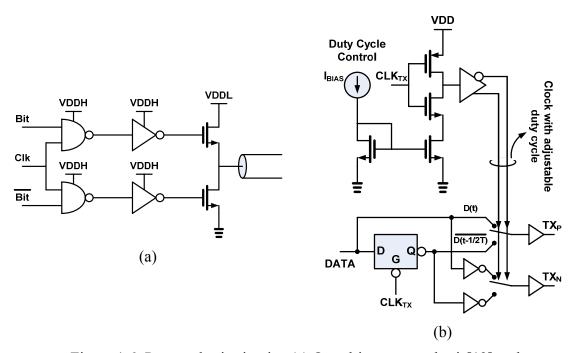

| Figure 1.6: Pre-emphasis circuits; (a) Overdrive pre-emphasis[13] and (b) pulse                 |

| width pre-emphasis[12]                                                                          |

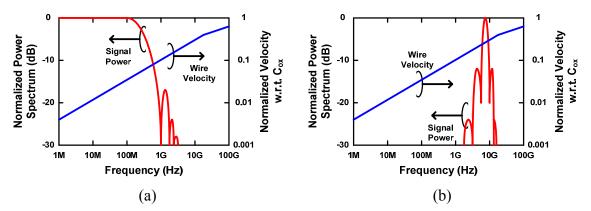

| Figure 1.7: Frequency characteristics of conventional digital pulse (a) and                     |

| modulated pulse (b) [10]9                                                                       |

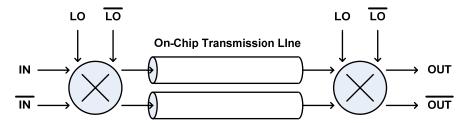

| Figure 1.8: Simplified block diagram for the transceiver with direct                          |

|-----------------------------------------------------------------------------------------------|

| conversion[10]; The transceiver has two mixers, one at the transmitter for the frequency      |

| up conversion and the other at the receiver for the frequency down conversion                 |

| Figure 1.9: Skewed pulsed buses[15]                                                           |

| Figure 1.10: Dual-VDD buffer[15]                                                              |

| Figure 2.1: Propagation delay for different M1 wire widths versus length in (a)               |

| and M2 wire widths versus length in (b)                                                       |

| Figure 2.2: Minimum propagation time for different lengths, with smallest                     |

| inverter from standard cell library, and metal wire, M1 in (a) and M2 in (b)                  |

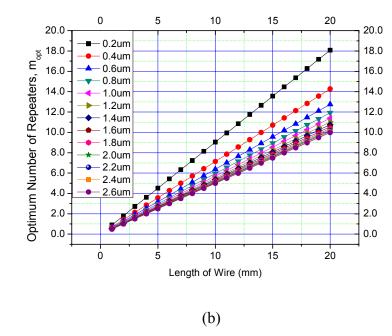

| Figure 2.3: Optimum number of minimum-sized standard-cells repeaters for                      |

| different widths metal wire M1 versus length in (a) and for different widths metal wire       |

| M2 versus length in (b).                                                                      |

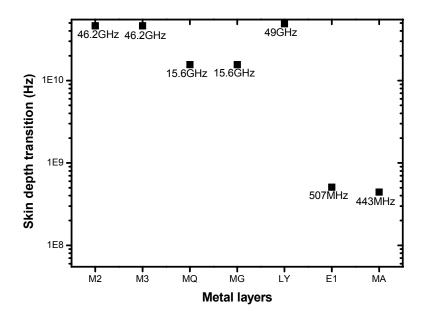

| Figure 2.4: Skin depth transition                                                             |

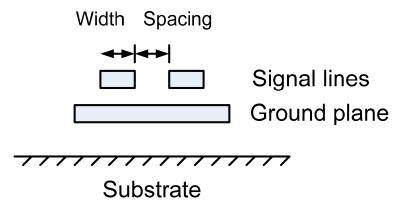

| Figure 2.5: On chip transmission line structure                                               |

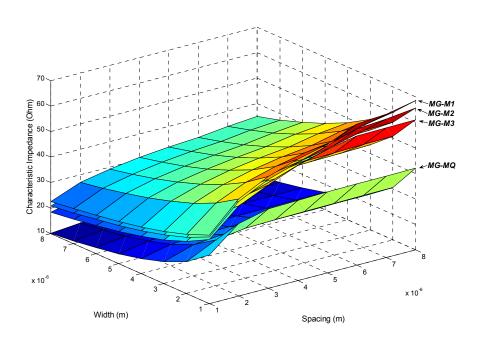

| Figure 2.6: Characteristic impedance for MG transmission line with different line             |

| widths and line spacing                                                                       |

| Figure 2.7: Length of transmission line at different widths and spacing with                  |

| signal line MG (M5)                                                                           |

| Figure 2.8: Step response of a lossy transmission line; <i>outA</i> is output at the end of   |

| a short transmission line and <i>outB</i> is output at the end of a long transmission line 25 |

| Figure 2.9: Width of transmission line for different widths and spacing with                  |

| signal line MG (M5)                                                                           |

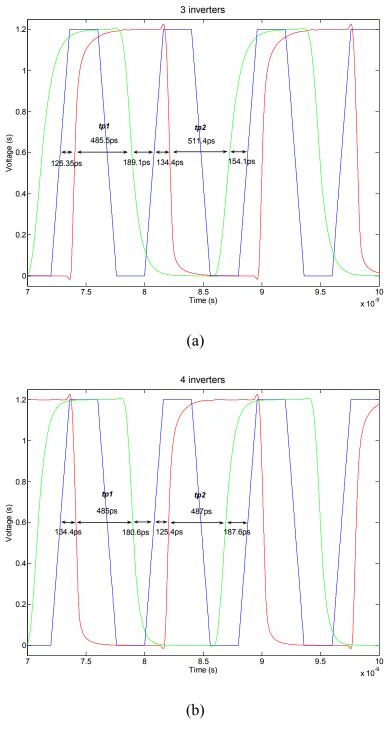

| Figure 2.10: Parallel bus designs;(a) 4 inverters and (b) 3 inverters between flip-                              |

|------------------------------------------------------------------------------------------------------------------|

| flops                                                                                                            |

| Figure 2.11: Spice simulations with (a) 3, (b) 4 inverters between flip-flops 29                                 |

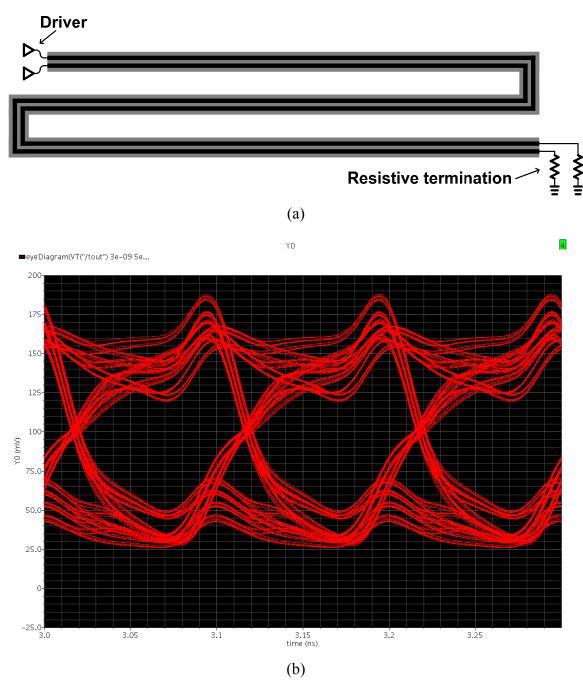

| Figure 2.12: Serial link; (a) schematic, (b) eye diagram at the end of 20mm                                      |

| transmission line. 32                                                                                            |

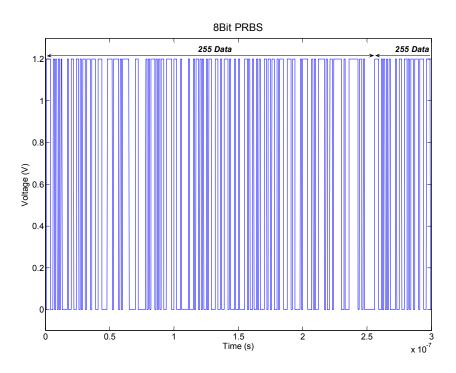

| Figure 2.13: One of outputs of 8bit PRBS generator                                                               |

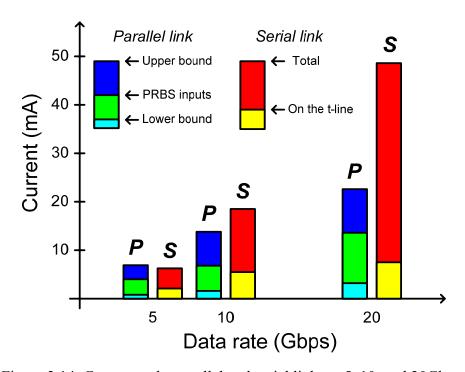

| Figure 2.14: Current at the parallel and serial links at 5, 10, and 20Gbps 36                                    |

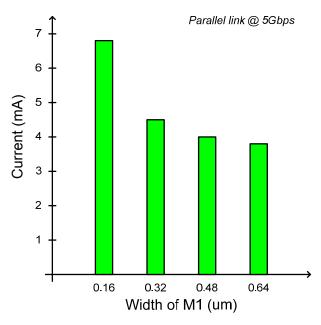

| Figure 2.15: Current at the parallel links with different widths of M1 with the                                  |

| PRBS input at 5Gbps                                                                                              |

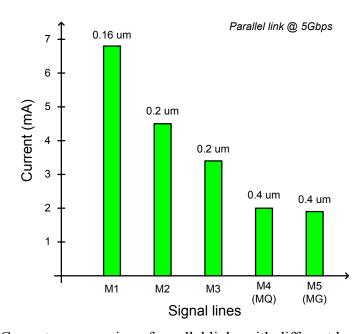

| Figure 2.16: Current at the parallel links with different signal lines with the                                  |

| PRBS input at 5Gbps; minimum width of the metal layers are listed on top of each bar                             |

| graph                                                                                                            |

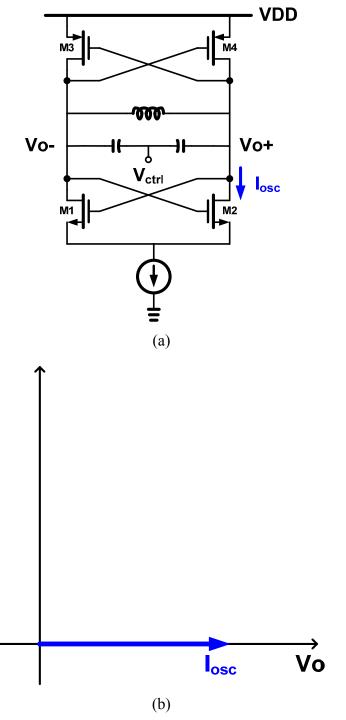

| Figure 3.1: (a) Single stage LC oscillator (b) Phase relationship; Voltage, $V_o$ , and                          |

| current, $I_{osc}$ , are in phase.                                                                               |

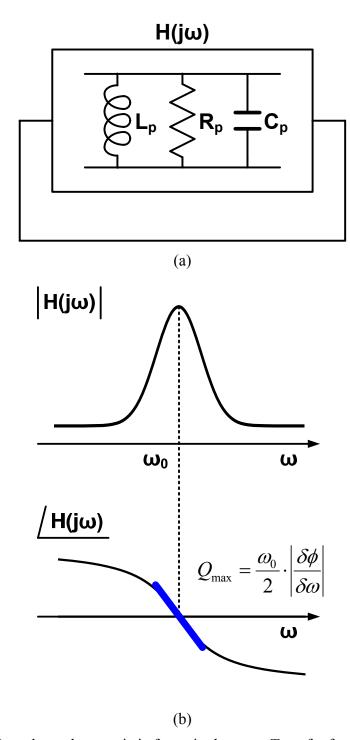

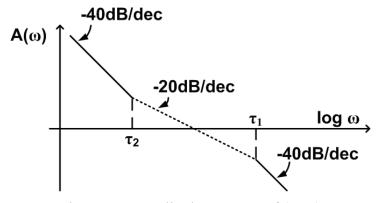

| Figure 3.2: Open loop characteristic for a single stage; Transfer function in (a)                                |

| and magnitude and phase response in (b); Operating point is where the slope of phase is                          |

| maximum, so the single stage oscillator achieves maximum quality factor                                          |

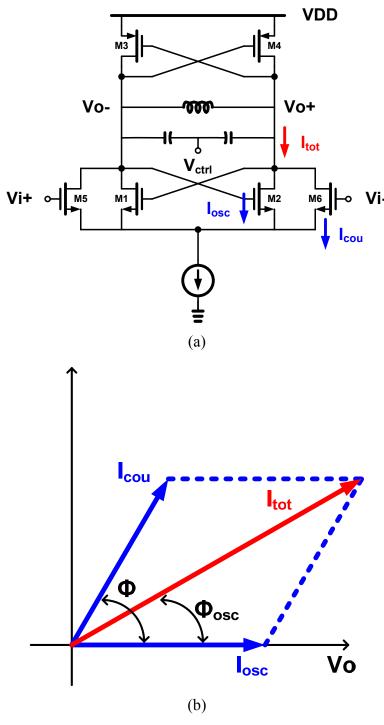

| Figure 3.3: (a) Basic cell of three stage LC oscillator (note that there are coupling                            |

| transistors, M5 and M6, in this case) and (b) Phase relationship; coupling current, $I_{cou}$ , is               |

| out of phase with the oscillation current, $I_{osc}$ , and the total current, $I_{tot}$ , has $\Phi_{osc}$ phase |

| difference with the voltage, $V_o$                                                                               |

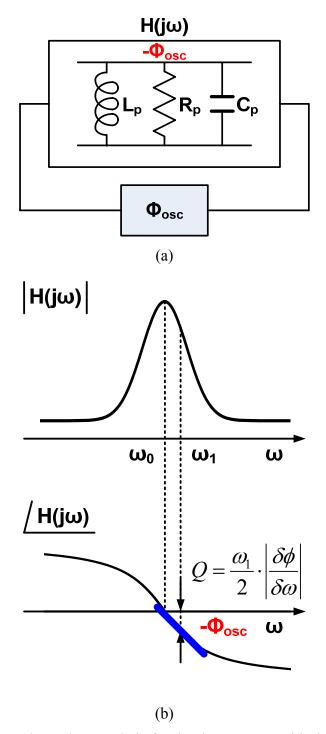

| Figure 3.4: Open loop characteristic for the three stage multi-phase oscillator;                      |

|-------------------------------------------------------------------------------------------------------|

| Transfer function (a) and magnitude and phase response (b); The multi stage oscillator is             |

| no longer operate at the point of maximum slope and maximum quality factor 45                         |

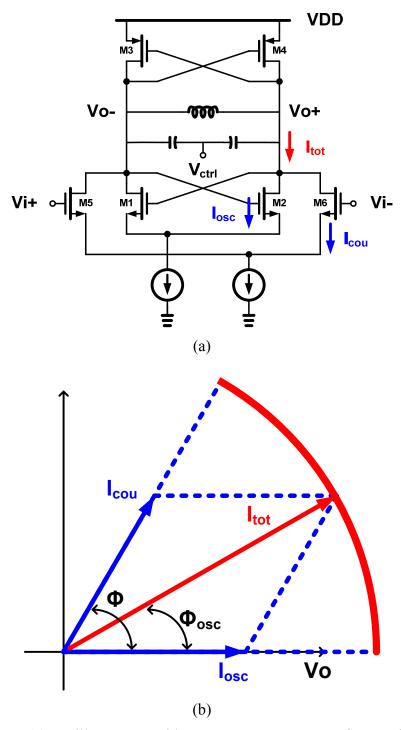

| Figure 3.5: (a) Oscillator stage with separate current sources for coupling and                       |

| cross-coupled transistors (b) Phase relationship; With changing coupling current, $I_{cou}$ , and     |

| oscillation current, $I_{osc}$ , we can have different phase difference, $\Phi_{osc}$ , between total |

| current, $I_{tot}$ , and the voltage, $V_o$                                                           |

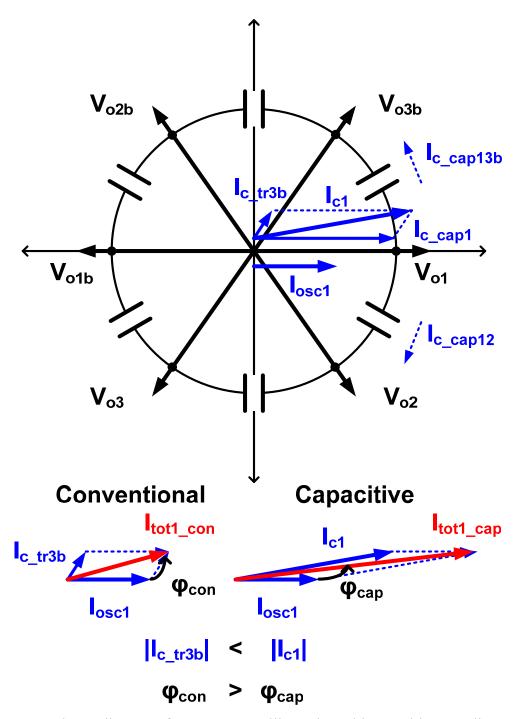

| Figure 3.6: Phase relationship in a 3 stage LC oscillator ring. Coupling capacitors                   |

| are shown with dashed line (coupling capacitors form a ring of capacitors) 49                         |

| Figure 3.7: Phasor diagram of 3 stage LC oscillator ring with capacitive coupling;                    |

| With the capacitive coupling there is another path for the current flowing from the ring of           |

| capacitors. The coupling current with the ring of capacitors introduces in-phase coupling             |

| current, therefore, the coupling strength is much bigger but with much smaller phase                  |

| difference between total current, $I_{tot1\_cap}$ , and the oscillation current, $I_{osc1}$           |

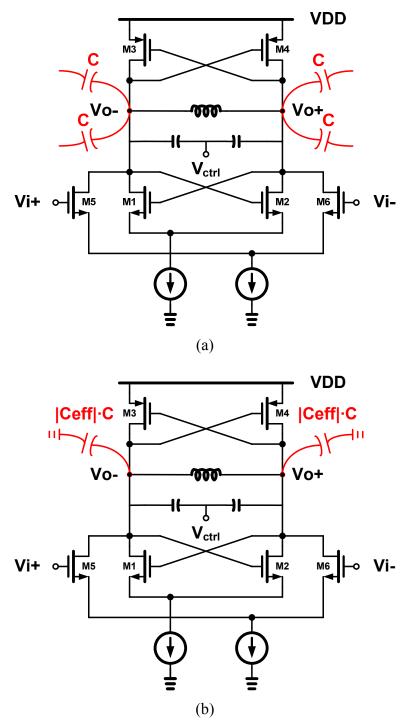

| Figure 3.8: Three stage LC oscillator ring (a) with capacitive coupling (b)                           |

| without capacitive coupling but with same capacitive loading; Both oscillators are                    |

| operating at the same frequency, but the oscillator with capacitive coupling has capacitive           |

| coupling effect, so there is in-phase coupling current                                                |

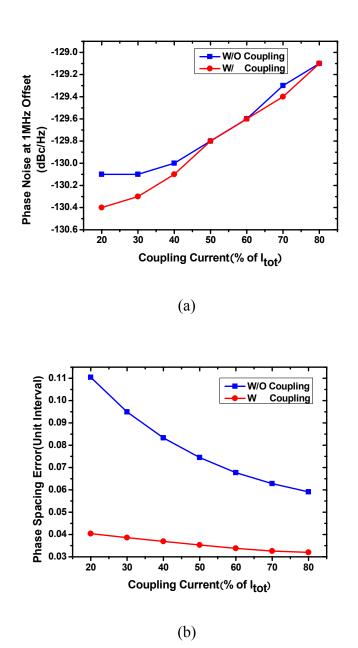

| Figure 3.9: Comparison with/without capacitive coupling (a) Phase noise (b)                           |

| phase spacing error; the oscillator with capacitive coupling shows slightly better phase              |

| noise performance over all, but when we look at the phase spacing error, the oscillator               |

| with capacitive coupling shows much better phase spacing error performance                            |

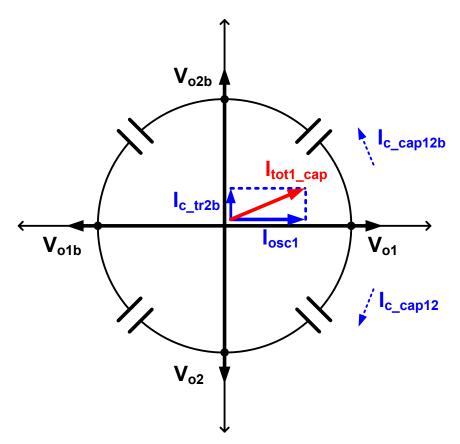

| Figure 3.10: Phasor diagram of 2 stage LC oscillator ring with capacitive                          |

|----------------------------------------------------------------------------------------------------|

| coupling; in case of two stage LC oscillator the sum of two coupling currents, $I_{c\_cap12b}$ and |

| $I_{c\_cap12}$ , is zero, so there is no contribution from the capacitive coupling in this case 56 |

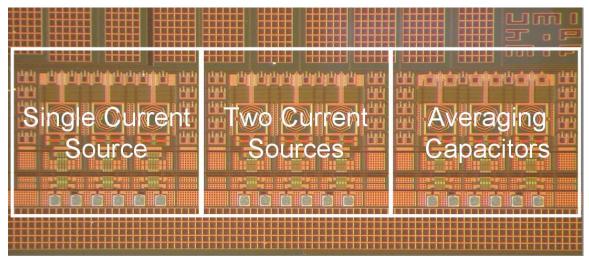

| Figure 3.11: Die photograph of the 3 oscillator rings; all three oscillators take                  |

| same power and same area                                                                           |

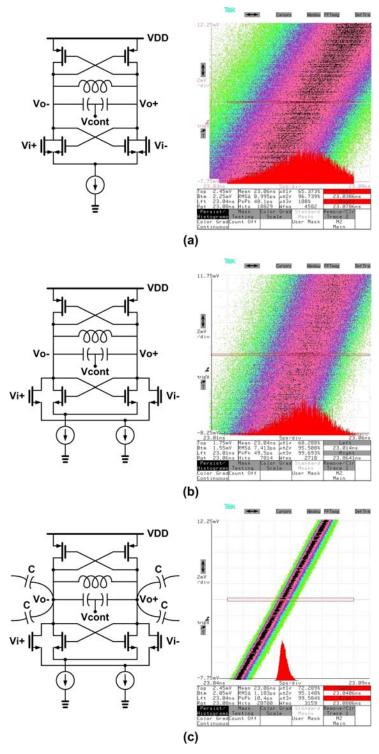

| Figure 3.12: RMS and pk-pk jitter of three three-stage LC oscillators (a)                          |

| Conventional Cell; RMS 8.995ps, pk-pk 40.1ps @ 4.537GHz (b) With separate current                  |

| sources; RMS 7.413ps, pk-pk 49.5ps @ 4.588GHz (c) With Capacitive Coupling; RMS                    |

| 1.183ps, pk-pk 10.4ps @ 4.011GHz                                                                   |

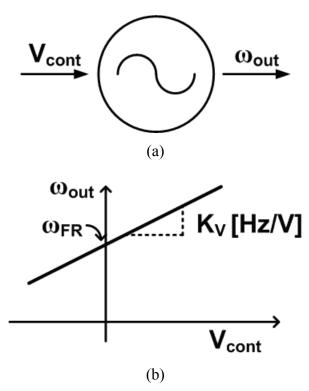

| Figure 4.1: Voltage controlled oscillator (VCO); (a) input and output of VCO and                   |

| the relationship between phase and frequency in (b)                                                |

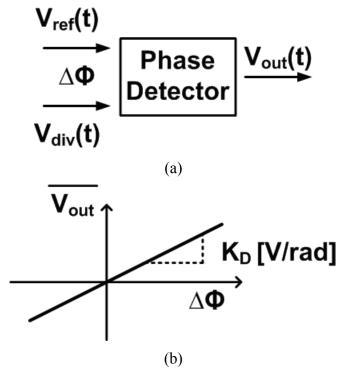

| Figure 4.2: Phase detector; (a) input and output of PD and their relationship in (b)               |

| 63                                                                                                 |

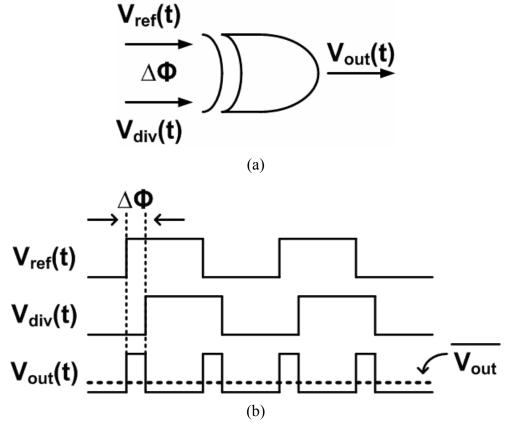

| Figure 4.3: XOR as a PD; (a) input and output of PD and waveforms (b) 64                           |

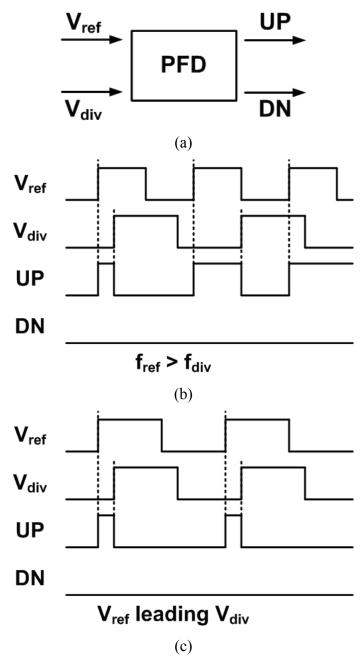

| Figure 4.4: (a) Symbol of a PFD, (b) UP and DN signals when the input                              |

| frequencies are different, and (c) input phases are different                                      |

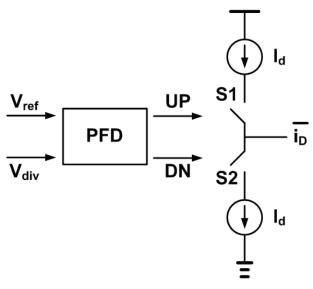

| Figure 4.5: PFD and charge pump                                                                    |

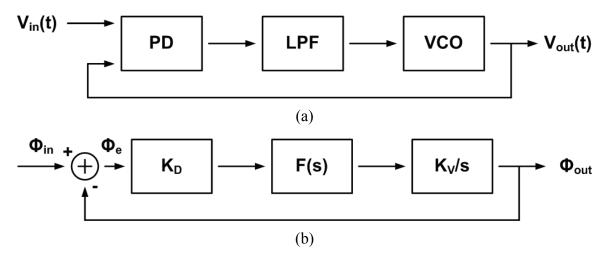

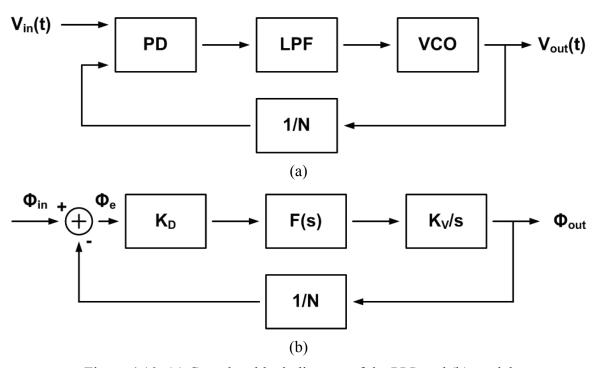

| Figure 4.6: Block diagram of PLL in (a) and the model of PLL in (b)                                |

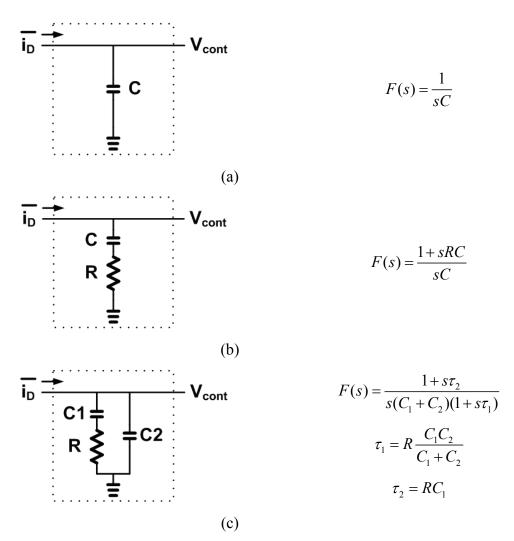

| Figure 4.7: Filters in PLL; (a) single pole filter, (b) single pole and single zero                |

| filter, (c) two poles and one zero filter                                                          |

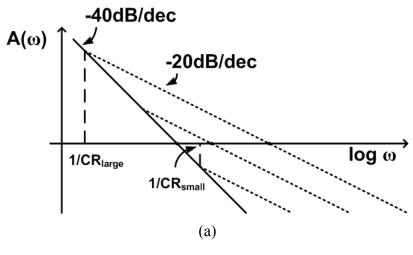

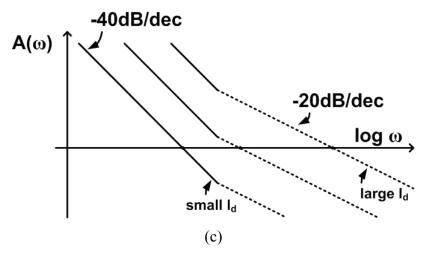

| Figure 4.8: Amplitude response of $(4.34)$ : (a) changing $R$ , (b) chaging $C$ , and (c)          |

| changing $I_d$                                                                                     |

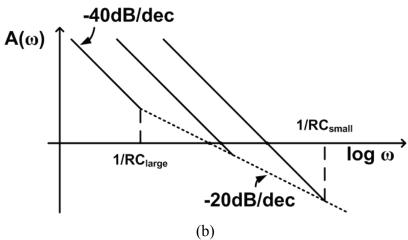

| Figure 4.9: Amplitude response of (4.35)                                                           |

| Figure 4.10: (a) Complete block diagram of the PLL and (b) model                                              |

|---------------------------------------------------------------------------------------------------------------|

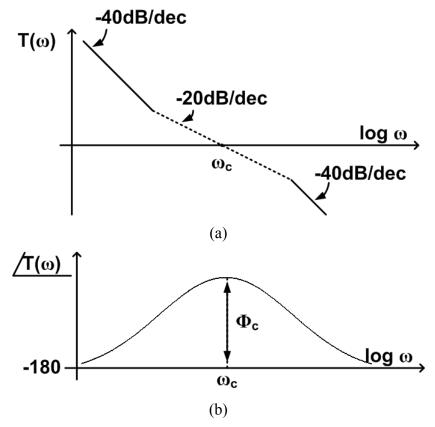

| Figure 4.11: Design goal of loop filter is to have the maximum phase margin at                                |

| the unit gain frequency.; (a) amplitude response and (b) phase response of loop gain $T(\boldsymbol{\omega})$ |

|                                                                                                               |

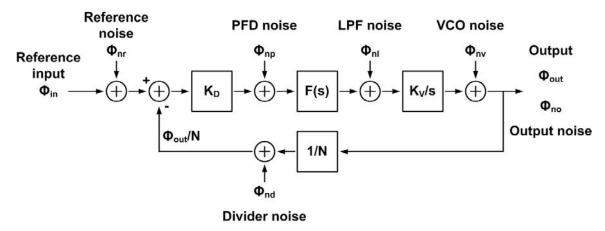

| Figure 4.12: PLL with output-referred noise for each block                                                    |

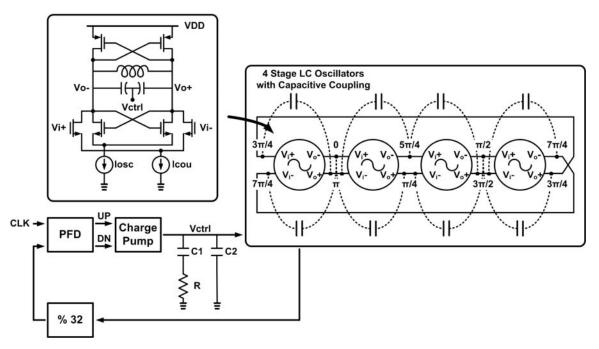

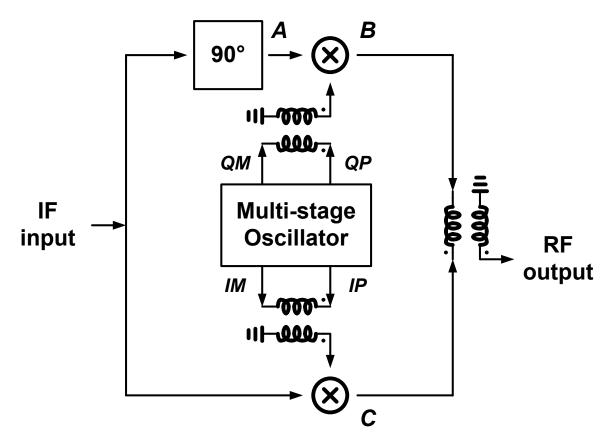

| Figure 4.13: PLL with capacitive coupling                                                                     |

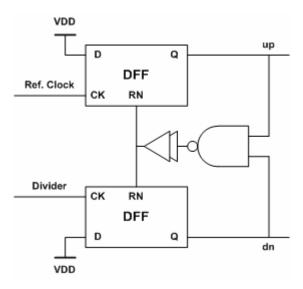

| Figure 4.14: Phase frequency detector(PFD)                                                                    |

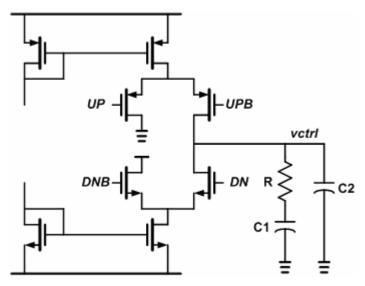

| Figure 4.15: Charge pump and filter                                                                           |

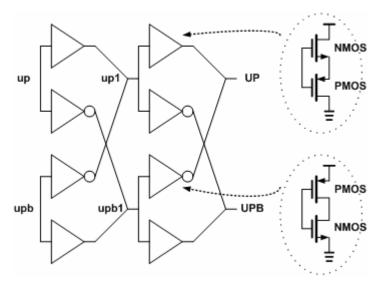

| Figure 4.16: Edge match circuit                                                                               |

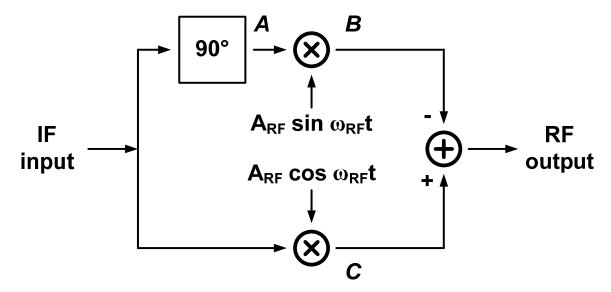

| Figure 4.17: Hartley image-reject transmitter                                                                 |

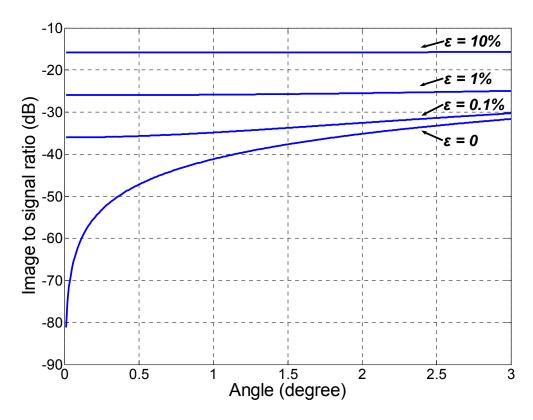

| Figure 4.18: Image to signal ratio with amplitude and phase mismatches 88                                     |

| Figure 4.19: Schematic to measure the image rejection ratio                                                   |

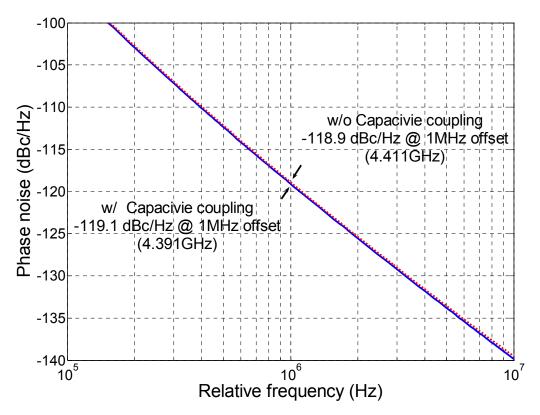

| Figure 4.20: Phase noise of the four stage coupled oscillators with deliberate                                |

| mismatch; w/ capacitive coupling shows -119.1 dBc/Hz at 1MHz offset and w/o                                   |

| capacitive coupling shows -118.9 dBc/Hz at the same offset                                                    |

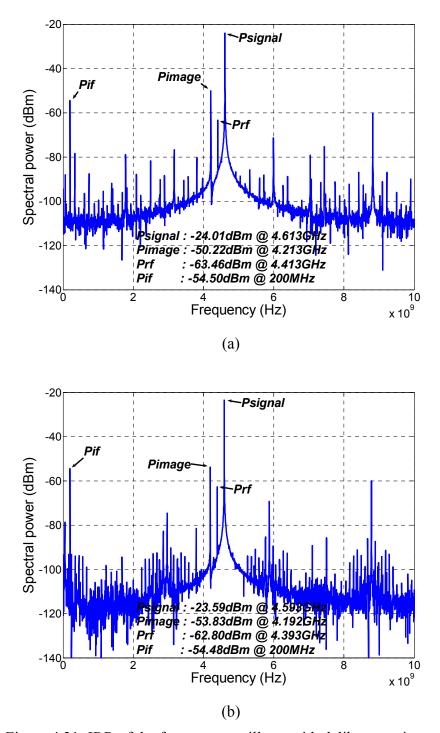

| Figure 4.21: IRR of the four stage oscillator with deliberate mismatch; (a) IIR of                            |

| 26.21dB with capacitive loading (b) IIR of 30.24dB with capacitive coupling                                   |

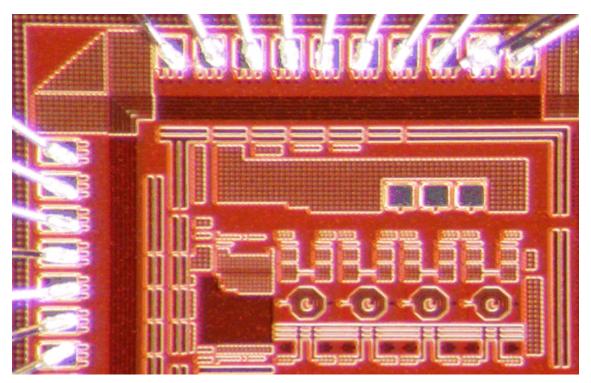

| Figure 4.22: Chip microphotograph of PLL                                                                      |

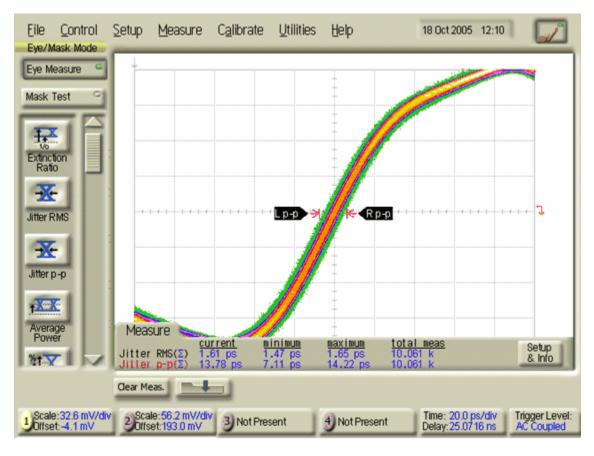

| Figure 4.23: 1.61 ps RMS jitter and 13.78 ps pk-pk jitter of the digital output of                            |

| the PLL at 3.47 GHz                                                                                           |

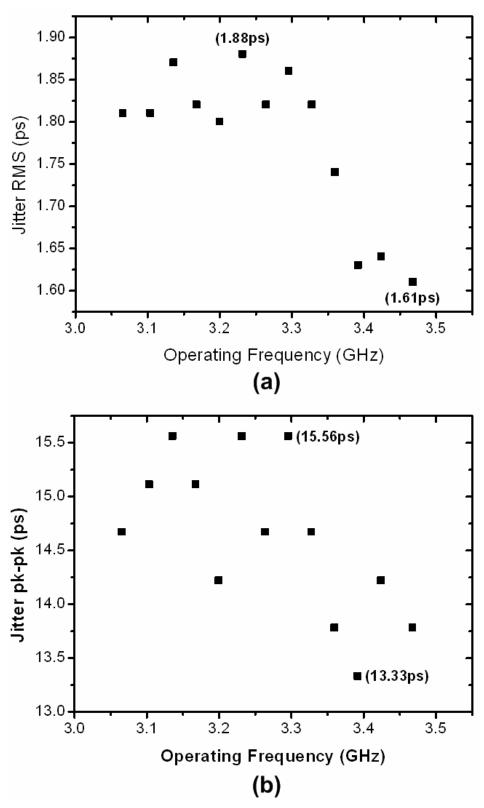

| Figure 4.24: (a)Measured RMS jitter and (b) measured pk-pk jitter                                             |

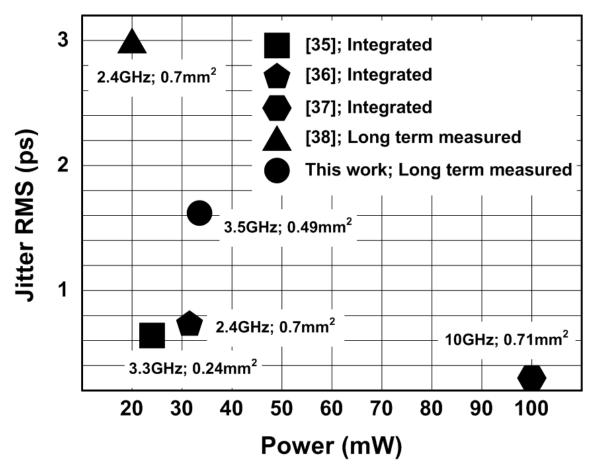

| Figure 4.25: Jitter and power dissipation of published CMOS LC-PLLs and this                    |

|-------------------------------------------------------------------------------------------------|

| work; [35-37] got their RMS jitter from the phase noise measurement, and [38] and this          |

| work got the RMS jitter from the long term measurement with the oscilloscope 95                 |

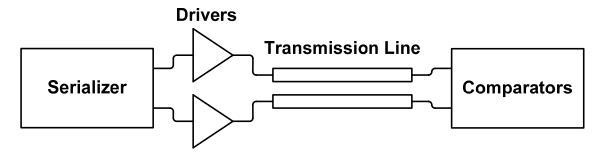

| Figure 5.1: Main functional blocks for serial data communication; serializer, data              |

| driver, on-chip transmission line, and comparators                                              |

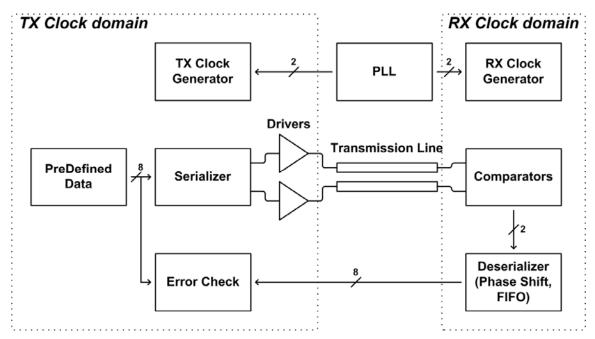

| Figure 5.2: Block diagram of on-chip serial link; Serial link consists of two clock             |

| domains, TX and RX clock domains. Since both TX and RX share single PLL, their                  |

| operating frequency is same, but their clock phases are different in order to compensate        |

| the delay from the long on-chip transmission line                                               |

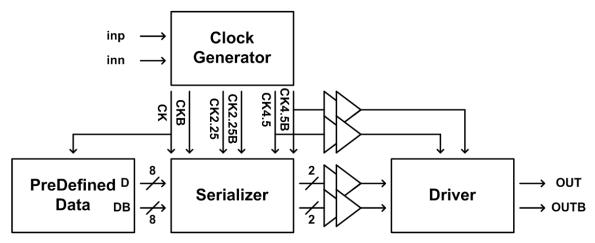

| Figure 5.3: Block diagram of the TX (transmitter); transmitter serializes pre-                  |

| defined data, 8bit 1.125GHz, to 9Gbps and drives long transmission line                         |

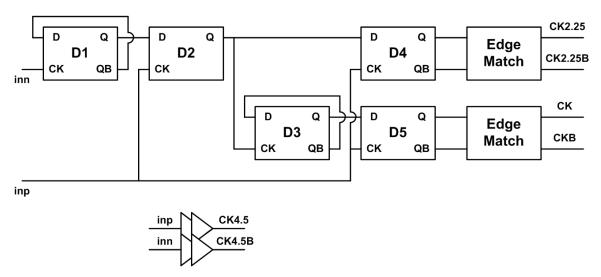

| Figure 5.4: Clock generator; inn is divided by two and divided by two again at D1               |

| and D3 respectively. The divided signals are clocked by the other 4.5GHz signal, inp, and       |

| aligned                                                                                         |

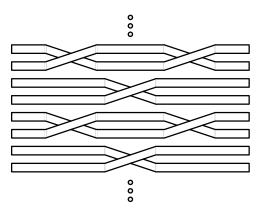

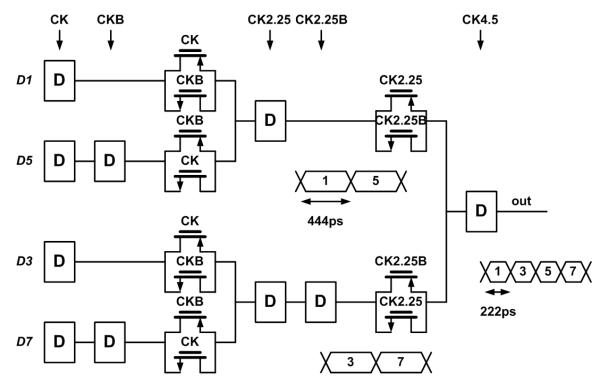

| Figure 5.5: A 4-bit serializer[42]; serialization is accomplished by sampling                   |

| original data at low frequency with high frequency clock signals                                |

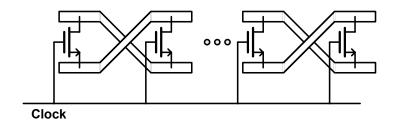

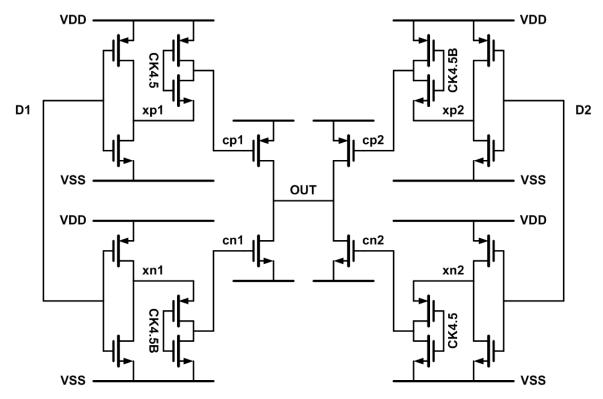

| Figure 5.6: Line driver[43]; two identical circuits only one of which is active at a            |

| time during half period of 4.5GHz clock signal generates 9Gbps serialized data 104              |

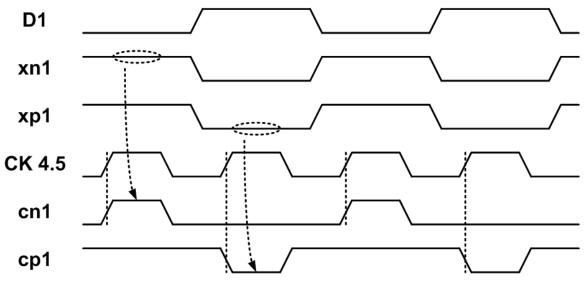

| Figure 5.7: Example waveforms for the line driver; input data ,D1, sets up                      |

| voltages at internal nodes, $xn1$ and $xp1$ , and clock signal, $CK4.5$ , makes short pulses on |

| cn1 and cp1 nodes based on the voltage at xn1 and xp1                                           |

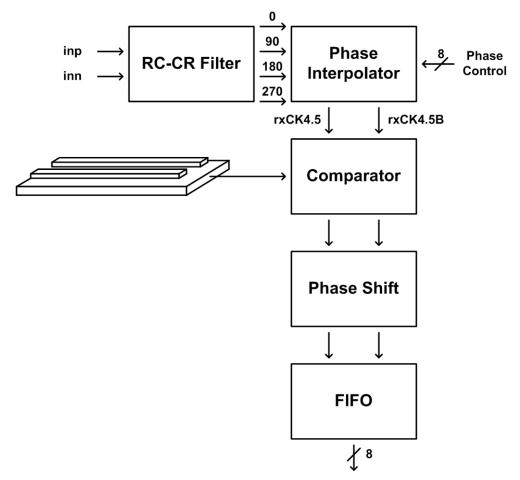

| Figure 5.8: Block diagram of the RX; receiver samples the serialized data, 9Gbps,                  |

|----------------------------------------------------------------------------------------------------|

| and de-serializes down to 8bit 1.125GHz. It requires clock phase tuning to compensate              |

| the delay from the long transmission line.                                                         |

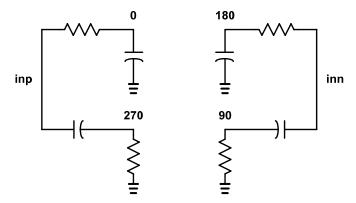

| Figure 5.9: A RC-CR filter[28]; four phases, 0, 90, 180, and 270, are generated                    |

| from the original two phases, <i>inp</i> and <i>inn</i>                                            |

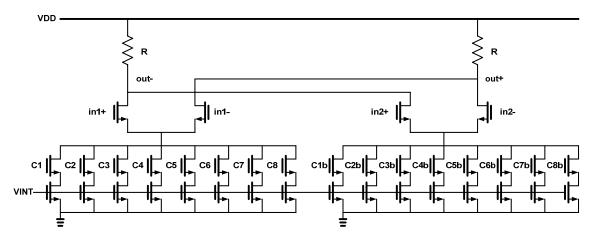

| Figure 5.10: Interpolator; the output phases, out+ and out-, from the two input                    |

| differential pairs can be modulated by changing the amount of the current in each side.            |

|                                                                                                    |

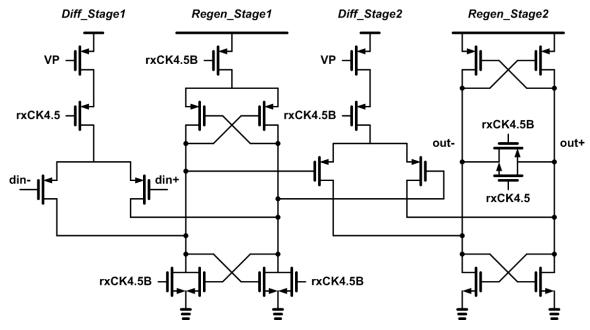

| Figure 5.11: Comparator; it samples the difference of input signals, <i>din+</i> and <i>din-</i> , |

| and regenerates the small voltage difference to the CMOS voltage level                             |

| Figure 5.12: Comparator output phase alignment at 4.5GHz; since the outputs of                     |

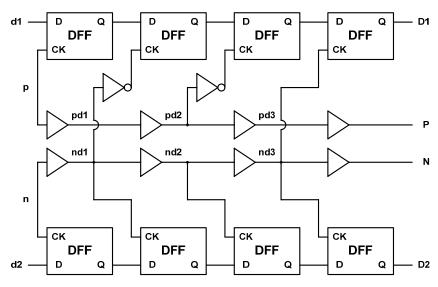

| the comparators, $d1$ and $d2$ , are out of phase, they need to be aligned to single clock         |

| phase (D1 and D2) for the further digital processing.                                              |

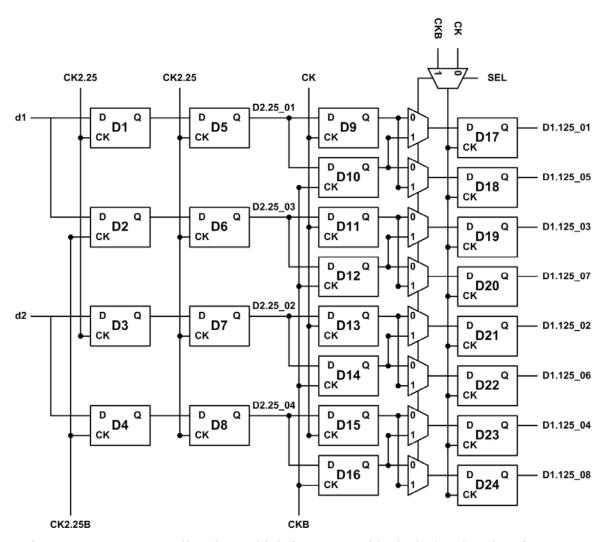

| Figure 5.13: FIFO; sampling data at high frequency with clock signals at low                       |

| frequency allows de-serialization from 2bit 4.5GHz to 4bit 2.25GHz and then to 8bit                |

| 1.125GHz. 113                                                                                      |

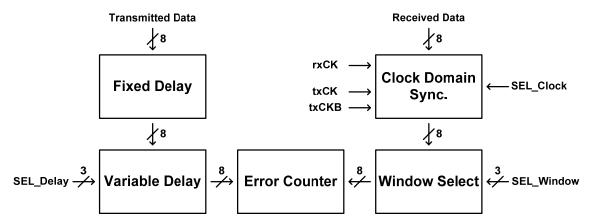

| Figure 5.14: Block diagram of the error-check block; error-check block compares                    |

| two data patterns, transmitted data and received data, and counts the number of errors             |

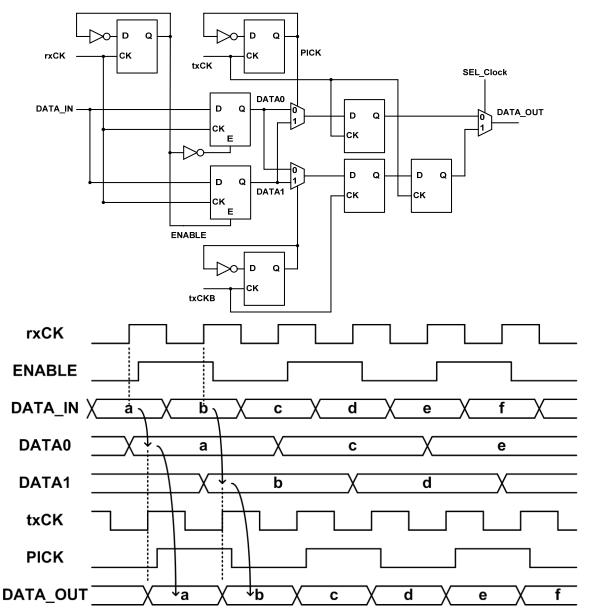

| when there is a discrepancy.                                                                       |

| Figure 5.15: Clock domain synchronization[43]; since the recovered data are at                     |

| the clock domain of the receiver, they need to change their clock domain to that of the            |

| transmitter in order to be compared with the original data at the transmitter 116                  |

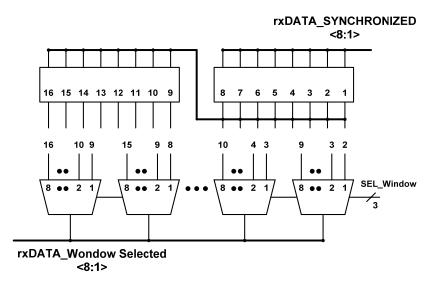

| Figure 5.16: Data window selection; it stores 8 bit recovered data for two clock          |

|-------------------------------------------------------------------------------------------|

| cycles and allows 16 bit data for the final 8 bit data selection                          |

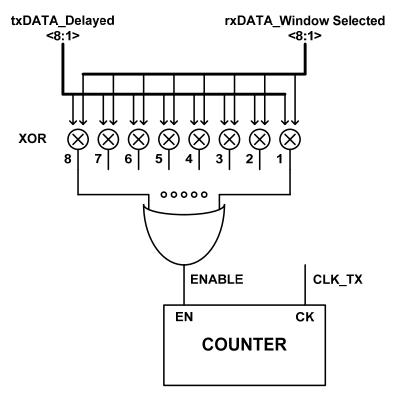

| Figure 5.17: Error counter; It receives two data patterns, original data and              |

| recovered data, and XORing those two patterns and then ORing the outputs of XORs          |

| becomes ENABLE signal. It becomes high and allows counting the number of errors at        |

| every clock cycle when there is a discrepancy between two input patterns                  |

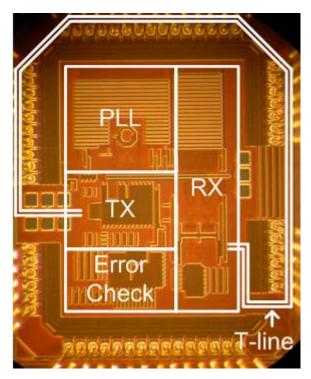

| Figure 5.18: Chip micrograph; transmission lines are laid out outside of the              |

| bonding pads. 119                                                                         |

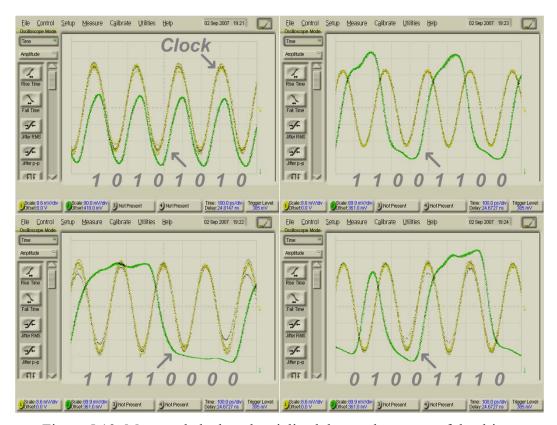

| Figure 5.19: Measured clock and serialized data at the output of the driver for the       |

| 10101010, 11001100, 11110000, 01001110 patterns                                           |

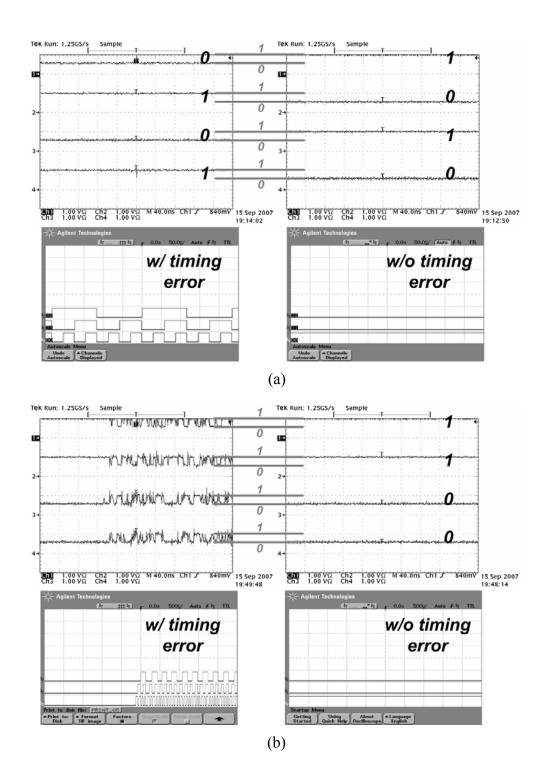

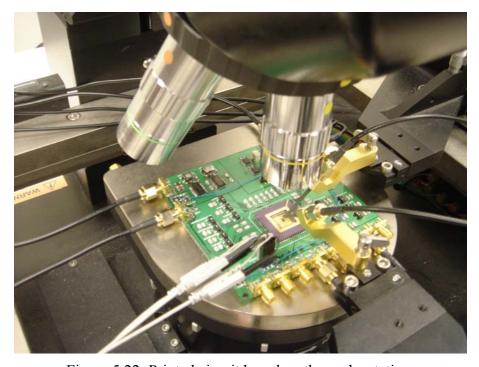

| Figure 5.20: Output of the self checking logic with (left) and without (right)            |

| deliberate timing error for the (a) 10101010, (b) 11001100, (c) 11110000, and (d)         |

| 01001110 patterns; when there are mismatches between the original data and the            |

| recovered data, error counter increases the number of errors at every clock cycles, but   |

| when those two data patterns are perfectly matched, the output of the error counter stays |

| at the same value.                                                                        |

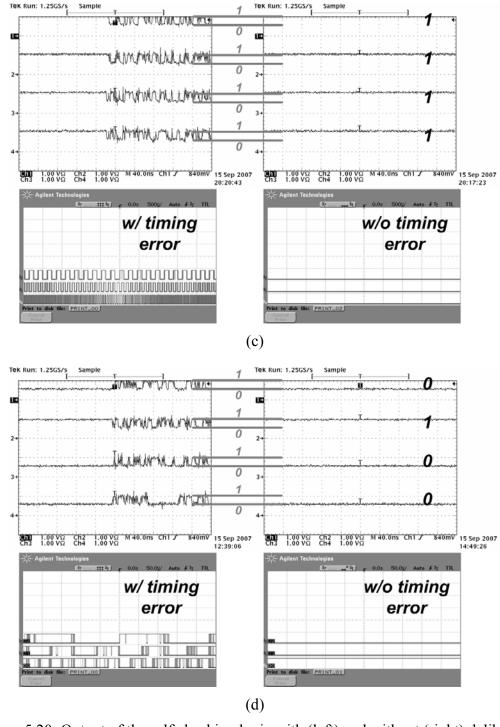

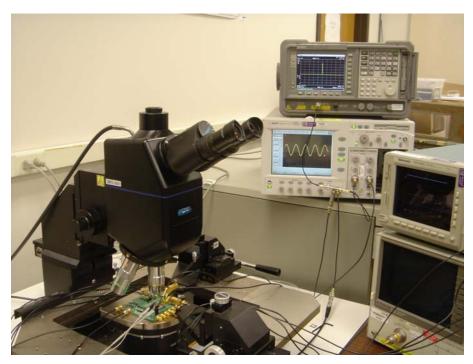

| Figure 5.21: Measurement setup; Cascade GSG probes are used to measure the                |

| operating frequency, RMS jitter, and the serialized data                                  |

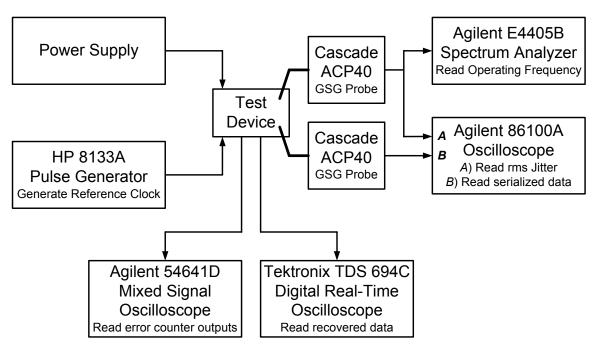

| Figure 5.22: Printed circuit board on the probe station                                   |

| Figure 5.23: Test setup to measure the clock signal and its frequency 126                 |

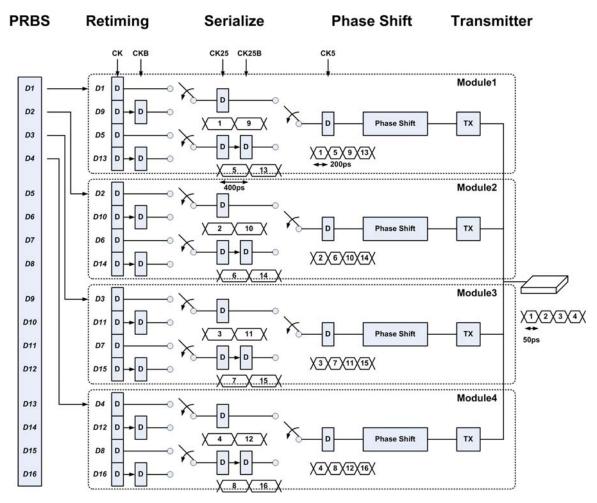

| Figure 5.24: System diagram of the transmitter(TX); TX consists of four identical         |

| functional blocks. Each block receives original data from the PRRS and does retimina      |

| for the proper sampling, serialization to the high frequencies, and phase shifting to       |

|---------------------------------------------------------------------------------------------|

| guarantee timing requirment for the following data driver                                   |

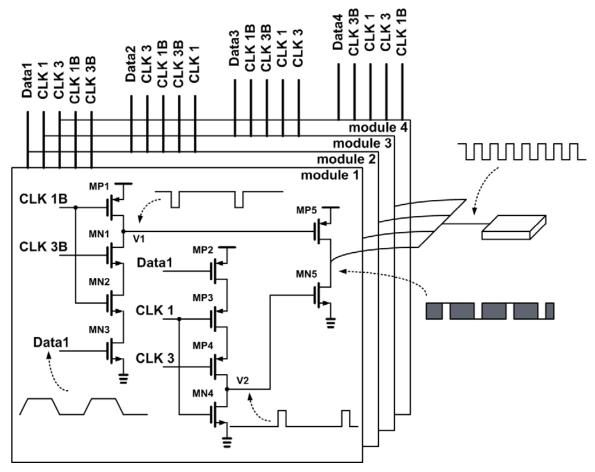

| Figure 5.25: Driver for 20Gbps serialization; it consists of four identical modules,        |

| and only one module is active at a time. Therefore, the outputs of the driver are the       |

| serialized data of the original data in four modules                                        |

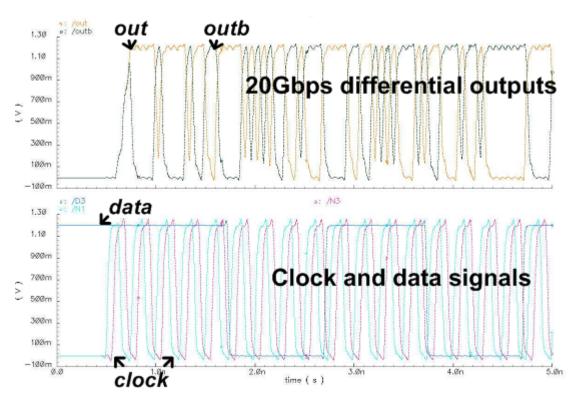

| Figure 5.26: 20Gbps serialized data at the output of an unloaded driver is shown            |

| at top and clock and data signals for the driver are shown at bottom                        |

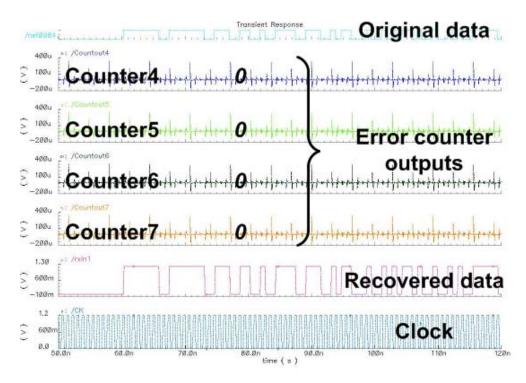

| Figure 5.27: Input and output signals of the error check block; Since the recovered         |

| data perfectly match with the original data, the outputs of the error counter stay at zero. |

|                                                                                             |

| Figure 6.1: Simulated eye diagram of 1 cm link with 40 Gb/s PRBS (2 <sup>32</sup> -1) data. |

|                                                                                             |

### **List of Tables**

| Table 2.1 Propagation delay and total current of parallel buses | 30  |

|-----------------------------------------------------------------|-----|

| Table 2.2 Current on the serial link                            | 31  |

| Table 2.3 Compare serial and parallel links                     | 34  |

| Table 3.1 Effective capacitance                                 | 54  |

| Table 6.1 FO4 delay of an inverter                              | 136 |

#### **Abstract**

This thesis describes techniques for global high-speed signaling over long (~10mm) lossy chip-serial transmission lines. With the increase in clock frequencies to multi-GHz rates, it has become impossible to move data across a die in a single clock cycle using conventional parallel bus-based communication. There are also reliability problems due to timing errors, skew, and jitter in fully synchronous systems. Noise, coupling, and inductive effects become significant for both intermediate length and global routing.

A new on-chip lossy transmission line technique is developed and new driver and receiver circuitry for on-chip serial links are described. High-speed long-range serial signaling is best done over transmission lines. However, because of the relatively high sheet resistance of metal interconnect layers, on-chip transmission lines tend to be lossy. Matched termination with resistors and the proper selection of the characteristic impedance of the transmission line structure can effectively suppress ISI. Fast digital CMOS technology allows pulsed mode data drivers to operate at multi-GHz rates. A phase-tuned receiver samples and de-serializes the received signal. Since the sampling instant is tuned to match the received signal eye, there is no requirement to match the clock and signal routing or clock and signal delays. A complete self-testing on-chip transceiver communicating over a 5.8mm on-chip transmission line is implemented in 0.13µm CMOS and tested. The measured BER at 9Gbps is less than 10<sup>-10</sup>.

Interleaving is usually necessary in high serial data rate serializer and de-serializer circuits. Multi-stage LC oscillators can be used to generate low phase noise multi-phases clocks required for interleaving. Conventional coupling between oscillators introduces out of phase currents, and this out of phase current causes a lower effective quality factor for each oscillator stage. However, capacitive coupling, a new technique, introduces in phase coupling between stages. Increased coupling with a ring of capacitors decreases phase spacing error dramatically and, in addition, the phase noise of multi-stages is also decreased thanks to in-phase coupling.

#### Chapter I

#### Introduction

The current globally synchronous clocking and signaling paradigm will fail as the number of transistors on an IC reaches the 1 billion mark. Although transistor feature size is expected to continue to scale for at least the next decade, power consumption, global signaling, and clocking have become critical problems that now prevent improvements in system performance, efficiency, and integration. The globally asynchronous locally synchronous (GALS) scheme within a *network-on-chip* paradigm is one of the long-term solutions, but this communications-centric methodology can only succeed with a fundamentally new approach to on-chip signaling.

According to the International Technology Roadmap for Semiconductors (ITRS), the rising integration levels and corresponding system complexity lead to "fundamental walls of performance, power consumption and heat dissipation" [1]. The current globally-synchronous signaling and clocking paradigm is largely responsible for an ever increasing portion of the total power consumption. The power consumed by synchronous global clocking has continually grown as integration levels increase and in some applications clocking alone already consumes 33-70% of the total power [2-4]. With multi-GHz clock frequencies, it has become impossible to move data across the die in a single cycle. In addition to these problems, there are also reliability problems due to timing errors, skew, and jitter in fully synchronous systems. Noise, coupling, and

inductive effects become significant for both intermediate and global routing. Buses are taking too much area, yet interconnect is reverse scaling [5] while the required communication bandwidth on an IC is growing exponentially.

The modular [6] or network-on-chip [7-9] approach advocated by the ITRS and others as a long term solution, is the one of the real alternatives. However, the ITRS also concedes that this *communications-centric* approach requires a significant change in communication architecture. In contrast to the traditional globally synchronous approach, the system is divided in GALS functional blocks or modules. The problems of global clocking are eliminated. Since the IC is now comprised of standalone modules, design complexity is reduced and IP reuse is facilitated. Substantial power savings can be achieved by independently setting (and adjusting) the power supply voltage and clock frequency to the modules. Despite these advantages, the modular approach places a far greater burden on communication. Robust communication between asynchronous network components is difficult using present techniques. Modern techniques will also be stretched to their limits to provide adequate local communication.

This chapter summarizes some of the work that has been done by others to mitigate the problems of on-chip signaling. Much of the research in this area has been focused on the analysis and design of on-chip wires. Differential signaling structures are an attractive solution at high frequency. Work has been done to minimize the area and maximize the bandwidth of differential structures. It has been shown that resistive termination extends the bandwidth to three times that compared to the case with capacitive termination. Pre-emphasis is another way to increase the bandwidth of on-chip wires.

A recently proposed architectural approach that uses modulation techniques for on-chip data transmission is described. Skewed pulsed buses and the use of dual VDD buffers, introduced to save power in conventional bus based links, are presented.

#### 1.1. On-chip wires

On-chip wires can be modeled as distributed RC or RLC networks depending on the operating frequency, or as distributed LC networks at high frequency[10] if the wires are constructed with low resistivity, thick top metal. Since differential signaling is noise insensitive and shows better performance than conventional single-ended signaling, as the sensitivity of the receiver becomes smaller[11], differential signaling is attractive for long distance high frequency data transmission. Even though most long distance, on-chip, communication schemes employ differential signaling, the physical structure of differential wires varies greatly, depending on the operating frequency and the mode of operation.

The structure in Figure 1.1(a) [12] was designed based on an RLC model to transmit data at 3Gbps signals, over a 10mm long link. Both pre-emphasis and resistive termination are employed. Both the width, w, and the space, s, between lines are 0.4 $\mu$ m, the bandwidth achieved for the cross section area is at it's maximum(t is the thickness of the signal lines, tt is the space between signal lines and thick top metal, and tb is the space between signal lines and bottom plane). An on-chip transmission line structure, Figure 1.1(b) [10] based on an LC model allows transmission of a 7.5GHz signal over a 20mm long link. The line width is 16 $\mu$ m and the space between lines is 2.1 $\mu$ m. The characteristic impedance,  $Z_0$ , of the transmission line in Figure 1.1(b) is proportional to

the (L/C)<sup>0.5</sup>, and for a given distance between two lines, increasing the width of the lines decreases the characteristic impedance while, on the other hand, increasing the space between two lines with fixed metal width increases the characteristic impedance. Due to the low inductance and high capacitance of on-chip wires the characteristic impedance tends to be far less than 50 ohm.

Figure 1.1: Physical structure of wires; (a) is designed based on the RLC model[12] (s is the space between signal lines and w and t are width and thickness of the signal lines respectively.) (b) is designed based on the LC model[10].

In a bus structure similar to that shown Figure 1.1(a) where the space between lines is not large, twists can be inserted in the differential links to cancel neighbor-to-neighbor crosstalk as shown in Figure 1.2. However, this scheme has the disadvantage of having extra series resistance because of the via connections, and the resistive loss can be problematic for data transmission at very high frequencies.

Figure 1.2: Twisted differential bus; This is effective to cancel neighbor-to-neighbor crosstalk.

With differential signaling, latency can be reduced by a factor of 2 by preequalizing the differential wires as shown in Figure 1.3 [13]. When clock is high, the charge on differential lines recycles between them, and when clock is low, the transmitter can send data to the receiver. Even though pre-equalizing the lines can save some time for the signal flight, the transmitter can only send data during half the period of the clock cycle, and pre-equalizing can also cause significant clock loading.

Figure 1.3: Differential line with distributed equalization[13]; When clock signal is high, both lines are set to same voltage (pre-equalizing), so data can be sent only during half the period of the clock cycle.

#### 1.2. Termination

Since the effect of inductance is negligible for long and narrow interconnects, the transfer function can approximate with a first-order RC model, and with low ohmic

termination instead of conventional capacitive termination, three times more bandwidth is achieved[12].

The characteristic impedance of the differential line is:

$$Z_{diff} = 2\sqrt{\frac{L - L_m}{C + C_m}}, \qquad (1.1)$$

where L, C,  $L_m$ , and  $C_m$  are the inductance, capacitance, mutual inductance, and mutual capacitance per unit length, respectively.  $Z_{diff}$  is exactly twice the characteristic impedance of a single line,  $Z_0$ , if there are no mutual inductance and mutual capacitance. Figure 1.4 [14] shows a simple configuration for the driver and termination. A resistively loaded transmitter drives a long line which has characteristic impedance  $Z_{diff}$ , and there is a termination resistor connecting the two ends of the differential line. In order not to have reflection at both transmitter and receiver, the resistors should meet the following conditions.

$$Z_{diff} = R_L = 2Z_0 \tag{1.2}$$

If two resistors are used for termination at the receiver (one port of the resistor is connected to the end of the line and the other port is connected to the ground), the resistor value for each should be half of  $Z_{\text{diff}}$ , and this is the same value which is used for the load resistors at the transmitter. If there is a mismatch at the receiver, the reflected signal can be observed at the transmitter requiring source matching. However when the attenuation of interconnect is large, a large resistance can be used to improve output gain at the driver.

Figure 1.4: A simple configuration for the driving and termination[14]; Since the input differential pair in the data driver is operating at either off or saturation region, the output impedance of the data driver is approximately equal to the impedance of the load resistors. Therefore, same impedance for  $R_o$  and  $Z_{diff}$  allows impedance matching at the data driver.

#### 1.3. Pre-emphasis and pulse shaping

Pre-emphasis can be used to extend the bandwidth of the wire and reduce inter symbol interference (ISI). Figure 1.5 shows two schemes, overdrive buffering [13] and pulse-width pre-emphasis[12]. The signal with overdrive buffering has a faster pulse rise time allowing higher data transfer rates to the receiver, while pulse-width pre-emphasis uses negative amplitude to reduce ISI. Both methods require extra circuitry for pulse shaping. Schematics of the two pre-emphasis schemes are shown in Figure 1.6. Figure 1.6(a)[13] was designed to generate low swing signals at the output and uses NMOS transistor for the pull-up to take advantage of faster speed compared to the case with a PMOS transistor pull-up. By using the high supply voltage for the logic circuits right before the drivers, the overdrive signals are generated. Figure 1.6(b)[12] is a circuit for the pulse width pre-emphasis signal generation. Sampling clocks, where the duty cycle can be controlled with bias current, generate a pulse width pre-emphasis signal by

sampling data and half period delayed inverted data at rising and falling edges alternatively.

Figure 1.5: Pre-emphasis at the transmitter; overdrive buffering[13] and pulse-width pre-emphasis[12]

Figure 1.6: Pre-emphasis circuits; (a) Overdrive pre-emphasis[13] and (b) pulse width pre-emphasis[12]

#### 1.4. Modulation

Modulation techniques [10] can be employed to send high speed data along the line. With conventional signaling a digital pulse at the end of a line has the power spectrum similar to that shown in Figure 1.7(a). Most of the signal power is concentrated at low frequency. However, because of the RC characteristic of a long line low frequency components travel slowly and the signal experiences frequency dispersion. At high frequency, the inductance of the wire dominates over the resistance, and the wire behaves like a waveguide (which can be modeled as distributed LC structure) allowing electromagnetic wave propagation. The wire velocity in Figure 1.7(a) and (b) increases with increasing frequency. Although conventional digital data has the spectrum power at all frequencies, the signal power can be restricted in a certain frequency range by using modulation and signals can take advantage of fast wire velocity and limited dispersion at high frequency.

Figure 1.7: Frequency characteristics of conventional digital pulse (a) and modulated pulse (b) [10]

Figure 1.8 shows a simplified block diagram for a transceiver employing direct conversion. A differential input data signal is mixed with the local oscillator signal, and

the up-converted differential signal is driven onto the on-chip transmission line. There is another mixer at the receiver, to down-convert to the original input signal. 1GHz data were transmitted and received using a 7.5GHz local oscillator over 20mm long on-chip transmission line[10]. In this case, the speed for the data transmit was limited by the local oscillator frequency. Analog circuits such as mixers and LC oscillators can cause reliability problem in the presence of substrate and supply noise from digital circuitry.

Figure 1.8: Simplified block diagram for the transceiver with direct conversion[10]; The transceiver has two mixers, one at the transmitter for the frequency up conversion and the other at the receiver for the frequency down conversion.

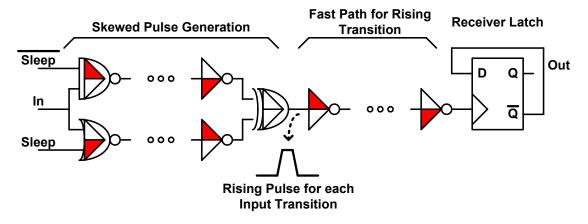

#### 1.5. Skewed Pulsed Buses

Skewed pulsed buses[15] are designed to lower standby and active mode leakage power without any performance degradation. Non-critical paths in a circuit module are suited to this method. By using the high threshold (HVT) and low threshold (LVT) devices alternately and properly encoding the data pulses, the circuit can be designed to pass rising edges with fast LVT devices. During standby mode, leakage is only through HVT devices. As shown in Figure 1.9, a skewed pulse generator makes rising pulses for each input transition at the output of the XOR gates, and the rising pulses only follows fast LVT devices. During standby mode, the output of the XOR remains high, reducing the standby leakage power of the repeater chain since the leakage is only through HVT

devices. Simulations of a 2GHz, 8mm long, 8bit data bus, implemented in partially-depleted SOI 90nm technology with repeaters every 0.5mm, show the skewed pulsed bus has 20% less active mode leakage and 85% less standby mode leakage compared to a traditional bus structure.

Figure 1.9: Skewed pulsed buses[15]

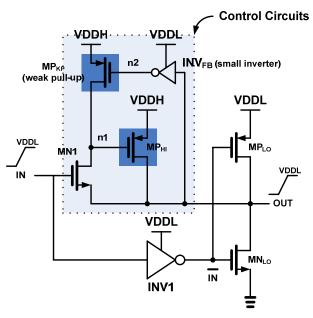

#### 1.6. Dual VDD buffer

In dual VDD digital circuits, the repeaters in non-critical paths are designed with low VDD, which sometimes requires a large repeater size in order to meet the delay requirement. If the power consumption of a path is excessive due to the large size of the repeaters, it is better to use high VDD repeaters than to increase the size of the repeaters. Figure 1.10 [15] shows a low VDD buffer which has control circuits generating short pulses at the rising edge at the output port to help small sized PMOS, MP<sub>LO</sub>, pull up. With a control circuit which has only two high VDD transistors, dual VDD buffers can use less area and less power than low VDD only buffers. With the same delay for both

the dual VDD buffer and low VDD buffer, the dual VDD scheme consume 16% less power, and the size of the dual VDD is 56% smaller than low VDD buffer.

Figure 1.10: Dual-VDD buffer[15]

#### 1.7. Dissertation outline

Some of the techniques suggested by others to improve the performance of on chip global links have been introduced. In the next chapter new techniques to increase the bandwidth of on-chip transmission lines are introduced. Techniques to generate multiple clock phases with low phase noise and low phase-spacing error are presented in Chapter III respectively. The design of an LC oscillator based PLL is explained in chapter IV. In chapter V the building blocks of a 9Gbps on chip transceiver are covered in detail. The design of a 20Gbps on-chip serial link is also presented. The thesis concludes in chapter VI with a summary and suggestions for future works.

#### **Chapter II**

#### On-chip parallel and serial links

Metal resistivity in conventional CMOS, poses significant challenges to implementing transmission lines for long range (~1 cm), on-chip, digital communication. Series resistance causes dispersion, leading to considerable inter-symbol interference (ISI). Dispersion is caused by differing propagation velocities for the low frequency slow-wave (i.e. RC) propagation mode and higher frequency TEM mode [16]. For an onchip 1cm link, the breakpoint between these two modes can be as high as several GHz. Others have avoided this problem by up-converting to a limited frequency band within the high frequency TEM region [17]. Significant dispersion is avoided by utilizing only a narrow band at high frequency; however, this approach adds complexity to the link and utilizes only a fraction of the potential bandwidth. Another solution is to use very thick, non-standard, metal interconnect lines. In [18], a 50 GHz bandwidth is achieved over a 20 mm link implemented as a coplanar transmission line, formed with a very thick (5 μm) non-standard metal layer. We compare a standard parallel-bus design scheme for a conventional 130nm CMOS process and an on-chip transmission line scheme. With same throughput, parallel and serial links are compared in terms of area and power.

#### 2.1. Bus bases global link

#### 2.1.1 Propagation delay, $t_p$

The propagation delay,  $t_p$ , for a step response is defined as the time for the voltage to rise from 0 to 50% of the final level. Depending on the model used for the RC network, the delay is 0.69RC with a lumped RC model and 0.38RC for a distributed RC model, where R and C are total resistance and capacitance respectively[19].

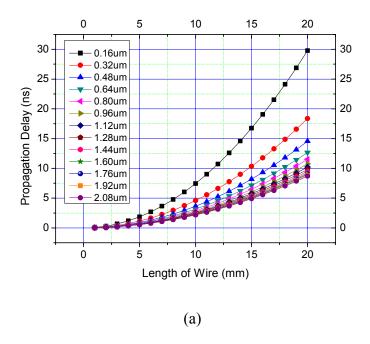

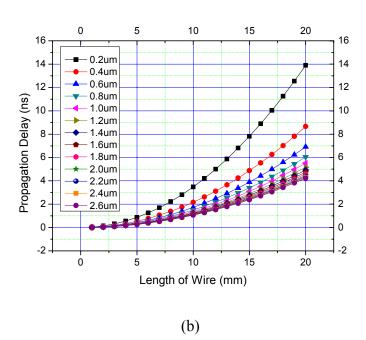

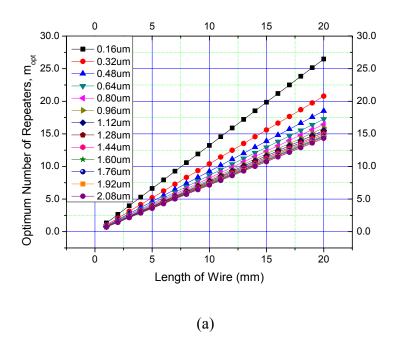

The resistance, r, per micron length of a minimum width wire M1 in 0.13 $\mu$ m CMOS is  $\sim 3\Omega/\mu$ m, while the capacitance, c per micron length, of the same metal is  $60aF/\mu$ m. The propagation delay of the wire is  $t_p=0.38RC=0.38rcL^2$  and is proportional to the square of the length. Figure 2.1(a) shows the propagation delay of M1 metal for different lengths and widths. For the minimum width, the propagation delay is about 30ns for a 20mm long line. For a line of twice the minimum width, the delay falls to 16ns for the same length. Figure 2.1(b) shows the propagation delay of over M2 metal lines for different line lengths and widths. For the minimum M2 line width, 0.20 $\mu$ m, the propagation delay is about 14ns for a 20mm long line. This delay is approximately the same as the delay for an M1 line with a width of 0.48 $\mu$ m. Using top metal layers has advantage of reducing the propagation delay dramatically, but without using large area since top metal has low resistance due to its increased thickness and lower capacitance due to the increased distance between metal layer and the substrate. However the resistance of vias should be considered when higher metal layers are used.

Figure 2.1: Propagation delay for different M1 wire widths versus length in (a) and M2 wire widths versus length in (b)

# 2.1.2 Optimum number of repeaters, $m_{\text{opt}}\,,$ and minimum propagation time, $t_{\text{p,\,min}}$

From Spice simulation, the intrinsic delay of a minimum sized inverter,  $t_{p0}$ , is 21ps. If  $R_d$  and  $C_d$ , are the equivalent on-resistance and input capacitance of a minimum sized repeater, then the optimum number of repeaters to achieve minimum delay, and minimum propagation time is given by the following equations[19]:

$$m_{opt} = L \sqrt{\frac{0.38rc}{0.69R_dC_d(\gamma + 1)}} = \sqrt{\frac{t_{pwire(unbuffered)}}{t_{p1}}}$$

(2.1)

$$t_{p,min} = (1.38 + 1.02\sqrt{1 + \gamma})L\sqrt{R_d C_d r c}$$

(2.2)

where L is the length of the wire, r is the resistance per micron, and c is the capacitance per micron.  $t_{p1} = 0.69R_dC_d(\gamma + 1) = t_{p0}(1 + 1/\gamma)$  represents the delay of an inverter for a fan-out of 1 and  $\gamma$  is the ratio of intrinsic output capacitance and input gate capacitance of the inverters,  $C_{int}/C_g$  ( $\approx$ 1).

With  $\gamma = 1$ ,  $t_{p1}$  becomes  $2t_{p0}$ , 42.5ps, and  $t_{p, min}$  becomes

$$t_{p,min} = 3.42L\sqrt{R_d C_d rc} \approx 3.42\sqrt{t_{pwire(unbuffered)} t_{p0}}$$

(2.3)

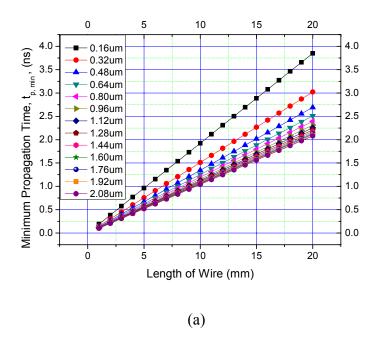

The minimum propagation time,  $t_{p, min}$ , in (2.3) with the 21ps of the intrinsic delay of a minimum sized inverter,  $t_{p0}$ , from Spice simulation and with the unbuffered propagation delay time,  $t_{pwire(unbuffered)}$  in Figure 2.1(a) and (b) are shown in Figure 2.2(a) and (b) respectively.

The minimum propagation time for an M1 wire with an optimum number of inverters and with a minimum width, 0.16µm, is about 4ns in Figure 2.2(a), while the original propagation time for the same line without inverters is about 30ns (Figure 2.1(a)). As shown in Figure 2.2(b) the minimum propagation time for an M2 wire with an

optimum number of inverters and with a minimum width, 0.2µm, is about 2.7ns, while the original propagation time for the same line without inverters is about 14ns (Figure 2.1(b)).

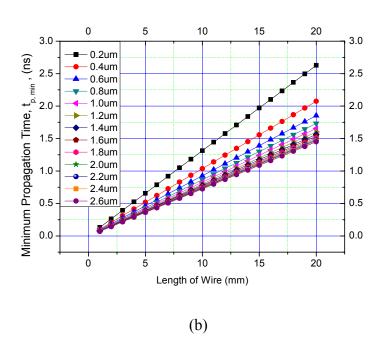

The number of repeaters for the minimum propagation time with 0.16µm M1 wire and 0.2µm M2 wire are 27 and 18 respectively from (2.1) as shown in Figure 2.3(a) and (b). Since the number of repeaters with 0.48µm M1 wire is 18 in Figure 2.3(a) which is equivalent to the number of repeaters with 0.2µm M2 wire, using a higher metal is more efficient in terms of area and power.

Figure 2.2: Minimum propagation time for different lengths, with smallest inverter from standard cell library, and metal wire, M1 in (a) and M2 in (b)

Figure 2.3: Optimum number of minimum-sized standard-cells repeaters for different widths metal wire M1 versus length in (a) and for different widths metal wire M2 versus length in (b).

#### **2.1.3 Sizing**

Sizing the repeaters is essential to reduce the delay. The optimum repeater sizing factor,  $S_{opt}$ , is defined as [19]

$$S_{opt} = \sqrt{\frac{R_d c}{C_d r}} \ . \tag{2.4}$$

For an M1 wire 0.16 $\mu$ m wide, r is 3.2 $\Omega/\mu$ m and c is 60aF/ $\mu$ m. Since the input capacitance of minimum inverter,  $C_d$ , is 1.4fF, the equivalent on resistance of the minimum sized inverter,  $R_d$ , can be derived from  $t_{p0} = 0.69R_dC_d$  and becomes 22kOhm. Therefore, the sizing factor,  $S_{opt}$ , is 17.14, and inserting 27 of these sized inverters achieves the minimum delay for the 20mm M1 link.

#### 2.2. Serial global link

#### 2.2.1 Skin depth

At high frequencies the effective resistance of metal wires becomes frequency dependent due to the skin effect. The skin depth,  $\delta$ , is defined as the depth where the current density falls to a value of  $e^{-I}$  of its nominal value, and is given by

$$\delta = \sqrt{\frac{\rho}{\pi f \,\mu}} \tag{2.5}$$

where f is the frequency of the signal, and  $\mu$  is the permeability of the surrounding dielectric. Due to the small thickness of on-chip metal wires, the skin effect is an issue only for wider, thicker wires. Also better conductors such as copper tend to suffer from the skin effect at lower frequencies. Figure 2.4 shows the frequency of each metal wire

where the skin effect starts to appear. In a 130nm CMOS technology two copper wires such as E1 and MA show skin depth transition points of only 507MHz and 443MHz respectively.

Figure 2.4: Skin depth transition

#### 2.2.2 Characteristic impedance

The characteristic impedance of a transmission line [20] is

$$Z_0 = \sqrt{\frac{R + j\omega L}{G + j\omega C}} \tag{2.6}$$

$$\approx \sqrt{\frac{L}{C}} \tag{2.7}$$

$$\approx \sqrt{\frac{R + j\omega L}{j\omega C}} \tag{2.8}$$

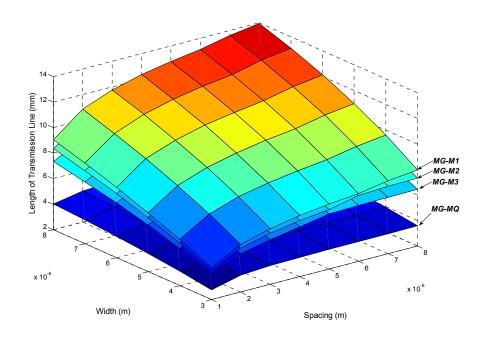

where R, L, G, C are series resistance, series inductance, parallel conductance, and parallel capacitance per unit length respectively. If the line is low-loss we can assume that  $R << \omega L$  and  $G << \omega C$ , and the characteristic impedance is given by the equation (2.7) approximately. In the case of a lossy on-chip transmission line, equation (2.8) is more appropriate for the characteristic impedance, since R is comparable or even larger than  $\omega L$ , but often equation (2.7) is still used for simplicity. The differential on-chip transmission line structure used in this investigation is shown in Figure 2.5. A strip-line rather than a coplanar structure gives better isolation from crosstalk. Figure 2.6 shows the characteristic impedance for various configurations of transmission line - the signal line is implemented on the MG layer and the ground plane is implemented with the M1, M2, M3, and MQ layers. The characteristic impedance is given for different line widths and line spacings and ranges from  $10\Omega$  to  $70\Omega$ . Implementing the ground plane with the M1 layer tends to give the largest characteristic impedance due to the reduced capacitance between signal lines and ground plane. Either decreasing the width of signal lines or increasing the space between signal lines increases the characteristic impedance, but decreasing the width of signal lines also increases the resistance of the metal wires.

Figure 2.5: On chip transmission line structure

Figure 2.6: Characteristic impedance for MG transmission line with different line widths and line spacing

# 2.2.3 Length of the transmission Line with matched termination

Due to resistive losses, the response of a lossy transmission line shows both wave propagation and diffusion. A step input propagates as a wave through the line, and the

amplitude of this traveling wave is attenuated along the line with a value at x given by:

[19]

$$V_{step}(x) = V_{step}(0)e^{-\frac{r}{2Z_0}x}$$

(2.9)

The arrival of the wave is followed by a diffusive relaxation to the steady-state value at point x:[21, 22]

$$V_{steady-state}(x) = \frac{Z_0}{rx + Z_0}$$

(2.10)

Figure 2.7 shows the point where the initial step voltage is same as the steady-state voltage. Increasing the characteristic impedance by widening the space between signal lines allows a longer transmission line due to the decreased total line resistance, but on the other hand increasing the characteristic impedance by reducing the width of signal lines (this is a way to increase total line resistance) reduces the length of transmission line.

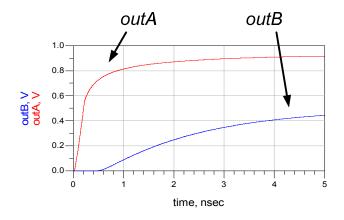

Figure 2.8 shows the step response of two lossy transmission lines where *outA* is the output of short transmission line, while *outB* is the output of a very long transmission line. The amplitude of the step due to the wave propagation in Figure 2.8 decreases exponentially along the line, and so that the effect of wave propagation cannot be observed with the very long lossy transmission line. *outA* shows step due to wave propagation followed by a diffusion component, but *outB* shows only a diffusion component since the wave propagation is not apparent due to the large resistance of the line. A transmission line only can be used properly if it shows wave propagation. Since a serial link using a transmission line takes advantage of wave propagation, the maximum

allowable length of transmission line is where the voltage level of the wave propagation equals the minimum allowable voltage level at the receiver.

Figure 2.7: Length of transmission line at different widths and spacing with signal line MG (M5)

Figure 2.8: Step response of a lossy transmission line; *outA* is output at the end of a short transmission line and *outB* is output at the end of a long transmission line

#### 2.2.4 Area

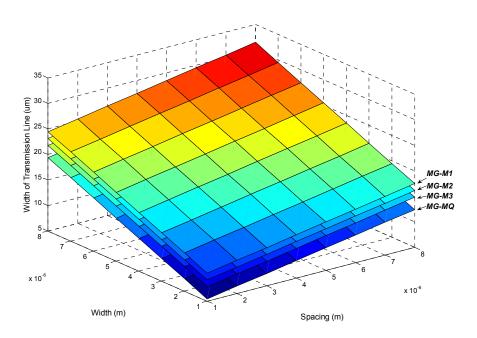

Using a lower metal layer as a ground plane increases the characteristic impedance due to the reduced self capacitance. However, the increased space between signal lines and ground planes requires a wider ground plane in order to contain electric fields; therefore, the widths of both the transmission line and the ground plane becomes larger. Figure 2.9 shows the overall width of the transmission line for different line widths and spacings.

Figure 2.9: Width of transmission line for different widths and spacing with signal line MG (M5)

# 2.3. 20mm link design example

## 2.3.1 Parallel bus design

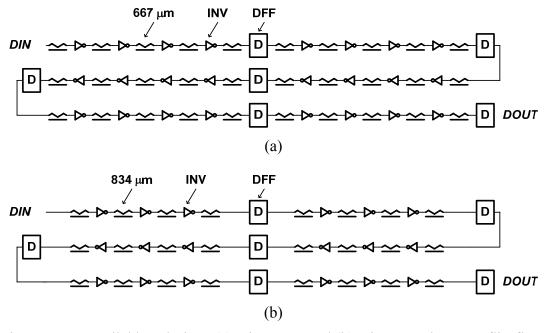

For simplicity, a 20mm long M1 bus with minimum width wires (0.16µm) is used in the parallel bus design. The propagation delay without repeaters is about 30ns as shown in Figure 2.1, but with 27 repeaters the total delay is reduced to 4ns as shown in Figure 2.2 and Figure 2.3. For a 1.25GHz operating frequency the signal cannot reach the end of the line in one clock cycle. Therefore flip-flops are required to retime the signal. Considering the setup time and the internal time delay of the flip-flops we can allow 650ps of propagation time between flip-flops. 6 clock cycles are required for the signal to travel the entire length of the line. Two designs are shown in Figure 2.10. Four inverters are inserted between flip-flops in Figure 2.10(a), and three inverters are inserted in Figure 2.10(b). Since the length of line between flip-flops is same for both designs, the inverters in Figure 2.10(a) and Figure 2.10(b) drive 667µm and 834µm long lines respectively. Spice simulation results of the design of Figure 2.10 are shown in Figure 2.11. Figure 2.11 shows the clock signal, the output of first flip-flop, and the input to the second flipflop for each case. In the case of 3 inverters (Figure 2.11(a)) the internal delays from the flip-flop are 125.4ps and 134.4ps for the rising and falling output signals respectively, and the average propagation time between flip-flops is 498.45ps ((485.5ps + 511.4ps)/2).

Figure 2.10: Parallel bus designs;(a) 4 inverters and (b) 3 inverters between flip-flops

Table 2.1 summarizes the average propagation delay time and total current for the 8bit parallel bus. A range of currents is given for no bus activity to full activity. Although there is not much difference in the delay time with different numbers of inverters between flip-flops, the minimum average propagation time is achieved with 5 inverters between the sets of flip-flops. Calculations show the optimum number of repeaters for the minimum delay is 27, or just over 4 inverters between flip-flops. As the numbers of inverters between the flip-flops grows, the total current also increases accordingly. However, the current for zero activity is almost the same for all designs since in this case most of the current is consumed by the flip-flops which are still active at every clock edges (each design has the same number of flip-flops).

Figure 2.11: Spice simulations with (a) 3, (b) 4 inverters between flip-flops

Table 2.1 Propagation delay and total current of parallel buses

| Number of inverters | Average propagation delay time between flip flips; (tp1+tp2)/2 | Total current of 8 bit parallel buses (VDD=1.2V, F=1.25G) |

|---------------------|----------------------------------------------------------------|-----------------------------------------------------------|

| 3                   | 498.45ps                                                       | 1.587mA ~ 13.778mA                                        |

| 4                   | 486ps                                                          | 1.599mA ~ 14.622mA                                        |

| 5                   | 484.3ps                                                        | 1.581mA ~ 15.458mA                                        |

| 6                   | 488.75ps                                                       | 1.600mA ~ 16.292mA                                        |

## 2.3.2 20mm serial link design

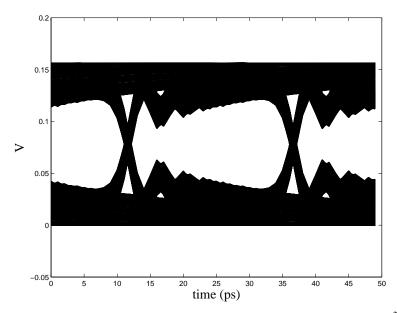

In order to minimize the skin effect and to save area, the MG layer is selected as signal line. For the transmission line the bottom metal layer M1 is selected as ground plane. With a 6 $\mu$ m line width and 3 $\mu$ m space between signal lines, the initial step voltage due to wave propagation is same amplitude as the steady-state voltage around 10mm from the transmitter. However, actual signal can propagate much further than that point. A 20mm long transmission line is terminated with 33 $\Omega$  resistors as shown in Figure 2.12(a). A pulsed mode transmitter in chapter V is used to transmit 10 Gbps signals, and the eye diagram at the end of the transmission line is shown in Figure 2.12(b).

Using a characteristic impedance of 33.4  $\Omega$  and 1.2 V signaling, the upper limit of the power delivered to each half line is given by (2.11):

$$P_{in} = \frac{1}{2} \frac{V_{S,rms}^2}{Z_o} = \frac{1}{2} \frac{0.849^2}{33.4} = 10.79 mW$$

(2.11)

And the lower limit of the power is given by (2.12):

$$P_{in} = \frac{1}{2} \frac{V_{S,rms}^2}{R_{line,total} + R_L} = \frac{1}{2} \frac{0.849^2}{167.4 + 33.4} = 1.795 mW$$

(2.12)

The total supply current consumption of the serial line driver and the current delivered to the transmission line are summarized in the Table 2.2. All three line drivers

are pulsed mode type, and drive 20mm transmission lines. The drivers at 10Gbps and 20Gbps have extra circuitry to generate 10Gbps and 20Gbps pulses respectively since the original data generated at 1.25GHz can only be serialized up to the 5Gbps with standard digital cells. The total current is 6.239mA, 18.45mA, and 48.556mA for the 5Gbps, 10Gbps, and 20Gbps serial links, respectively. Compared to the increase of the current on the transmission line at high frequencies, the current increase for the driver is extremely large since it requires additional circuitry to generate high frequency pulses.

The simulated power consumption of the transmission line lies between the upper and lower boundary values in (2.11) and (2.12).

**Table 2.2 Current on the serial link**

| Serial link | Total current | Current delivered to the transmission line |

|-------------|---------------|--------------------------------------------|

| 5Gbps       | 6.239mA       | 2.092mA                                    |

| 10Gbps      | 18.45mA       | 5.514mA                                    |

| 20Gbps      | 48.556mA      | 7.499mA                                    |

Figure 2.12: Serial link; (a) schematic, (b) eye diagram at the end of 20mm transmission line.

#### 2.3.3 Comparison

Table 2.3 compares a 10Gbps serial link and an equivalent 8-bit-wide parallel bus. The area of the parallel bus, based on the size of standard cells, is 0.688mm<sup>2</sup>. The area of the serial link at 0.449mm<sup>2</sup>, is about 0.24mm<sup>2</sup> smaller than that of the parallel link.

For the power consumption comparison, both a parallel link with three inverters between each set of retiming flip-flops and serial link are driven by same 8bit PRBS generator. Since an N-bit PRBS generator generates a 2<sup>N</sup>-1 long data sequence, the 8bit PRBS generator generates a repeating 255 bit data pattern. One of the eight bit outputs is shown in Figure 2.13. The average data transition rate is 4.016 bits out of 8 bits, corresponding to a 50.2 % activation rate.

Figure 2.13: One of outputs of 8bit PRBS generator

The total supply current for the serial link is 18.45mA at 1.2V, with only 5.514mA used for the data transmission while the remaining current is for the serialization of two 5GHz data patterns to a single 10GHz data pattern.

The supply current for the parallel link is 6.806mA with the same PRBS input as used to test the serial link. The supply total current ranges from 1.587mA with a zero activation to 13.778mA with full data activity for the link with three inverters between flip flops. The relatively high current for a static input is due to the power consumption of the retiming flip-flips, which are continuously clocked.

With the serial link taking advantage of wave propagation, data can reach the end of the 20mm line only in 150.7ps, compared to 6 clock cycles (4.8ns) for the parallel link. The clock driver for the parallel link is not considered in this comparison. For the serial link the current consumption of the serializer (i.e. total current) is also given in the table.

Table 2.3 Compare serial and parallel links.

|                          | Serial link (10Gbps)                                                              | Parallel bus (8bit 1.25Gbps)                                         |

|--------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------|

| Link Area                | 22.48µm X 20mm                                                                    | 34.4μm X 20mm                                                        |

| Current                  | Total Current : 18.45mA @ 1.2V  Current on the transmission line : 5.514mA @ 1.2V | 3 Inverters between DFFs : 6.806mA @ 1.2V (1.587mA ~ 13.778mA @1.2V) |

| Time delay for 20mm link | 150.7ps                                                                           | 4.8ns<br>6 clock cycles (800ps X 6)                                  |

#### 2.3.4 Conclusion

This chapter compares the power consumption, area and delay of an on-chip transmission line based serial link with that of a conventional, parallel bus link. Prototype 20mm 10Gbps links are designed with both approaches for 130nm CMOS.

The serial link requires a lower signaling power than the parallel bus except at low data activation rates. However, serialization adds considerably to the power required for serial signaling. Figure 2.14 compares the power required for a parallel and serial links designed for data rates of 5Gbps, 10Gbps, and 20Gbps. When the extra power required for serialization is considered the power consumptions are similar at 10Gbps. At 5Gbps the serial approach is more energy efficient, indicating a breakpoint somewhere between 5Gbps and 10Gbps. We expect this breakpoint to be larger in more advanced technology nodes since serialization becomes much more efficient in faster CMOS technology.

This study is not exhaustive since there are still some additional factors that might be considered. A parallel link using a wider or higher metal layer would most likely be more energy efficient. The current consumption required for a 20mm data transmission with the different M1 metal wire widths are shown in Figure 2.15. The widths of M1 are multiples of 0.16µm. The current decreases from 6.8mA at the minimum width to 3.8mA with the 0.64µm wide metal wire. However, increasing wire width also increases capacitance, limiting the improvement in power consumption.

The use of higher level minimum width M5(MG)metal wires decreases current consumption to 2mA as shown in Figure 2.16. The use of higher metal layers decreases not only resistance but also capacitance because of the increased distance between the

metal layer to the substrate. However, on the other hand the clock power dissipation for the parallel link was not considered in those figures. Furthermore, the use of a pseudodifferential serial signaling scheme could significantly reduce the power required for serial signaling.

Since a serial link takes advantage of wave propagation, a serial link has a much shorter propagation delay than an optimally designed parallel bus. Our simulations show that the propagation delay for the serial link is more than an order of magnitude lower that of the parallel link. This could be a key advantage in high performance applications, such as microprocessors and graphics processors. The area required for a serial link is slightly less than for an equivalent parallel link.

Figure 2.14: Current at the parallel and serial links at 5, 10, and 20Gbps

Figure 2.15: Current consumption of a parallel links for different widths of M1 with 5Gbps PRBS data

Figure 2.16: Current consumption of parallel links with different layer signal lines.

#### **Chapter III**

## Multi-stage LC oscillators with capacitive coupling

Multi-stage oscillators[23] not only provide multiple phases, but also generate low phase noise clock signals, since the overall phase noise in a multi-stage oscillator is inversely proportional to the number of stages[24, 25]. Therefore, as the number of stages increases we can get lower noise, but at the expense of large area and power. Much research has been done to decrease the phase noise without further increasing the number of stages[25, 26]. Capacitive coupling for multi-stage LC oscillators, introduced here, is an efficient and simple method to decrease phase noise in multi-phase oscillators since unlike other forms of coupling it does not introduce an out-of-phase coupling current which can decrease phase noise, yet capacitively coupling is very effective in reducing phase spacing error [27]. The phasor diagram in multi-stage oscillators is first presented to explain the variation of the quality factor in multi-stages. Capacitive coupling is explained in detail.

#### 3.1. Phasor diagram

#### 3.1.1 Single stage LC oscillator

The voltage and current phase relationship for a single stage LC oscillator oscillating in steady-state is shown in Figure 3.1[28, 29]. Once oscillation starts, it takes some transient time to reach steady-state, and for the voltage and current phases in LC

tank to become in-phase as shown in Figure 3.1(b). The steady-state phase relationship also can be explained from an open loop model. The open loop model in the case of a single stage LC oscillator is shown in Figure 3.2(a). One of the oscillation conditions is a zero phase shift (or equivalently 360 degree phase shift) in the loop which includes the LC tank. Since LC tank is the only component contributing the phase in the loop, the total phase is same as the phase of the LC tank. Therefore, in order to achieve zero total phase in the loop the phase of the LC tank should be zero. From the amplitude and phase response of the transfer function of the LC tank in Figure 3.2(b) the operating point which satisfies zero phase in the loop can be decided. So, for a single stage LC oscillator, the steady-state oscillation stays at the point of zero phase with the oscillation frequency of  $\omega_0$ ,  $1/(LC)^{0.5}$ .

The LC tank achieves its maximum effective quality factor in case of single stage LC oscillator, since the effective quality factor is proportional to the slope of the phase and the operating point of zero phase is where the derivative of the phase over the frequency is maximum.

Figure 3.1: (a) Single stage LC oscillator (b) Phase relationship; Voltage,  $V_o$ , and current,  $I_{osc}$ , are in phase.

Figure 3.2: Open loop characteristic for a single stage; Transfer function in (a) and magnitude and phase response in (b); Operating point is where the slope of phase is maximum, so the single stage oscillator achieves maximum quality factor.

## 3.1.2 Three stage coupled LC oscillator

Multi-stage coupled oscillators are usually designed with the basic cell shown in Figure 3.3(a), which is exactly same as the basic cell for the single stage LC oscillator, but with two more transistors, M5 and M6, for coupling with other oscillator stages. Unlike a single-stage LC oscillator, multi-stage oscillators have an additional current component in each basic cell due to the coupling between oscillators. Transistors M5 and M6 in Figure 3.3(a) introduce a coupling current between each stage. The phasor diagram with this coupling current is shown in Figure 3.3(b). Assuming that the magnitude of the coupling current,  $I_{cou}$ , is same as that of the oscillation current,  $I_{osc}$ , then in case of three stage LC oscillators we have a 60 degree phase difference,  $\phi$ , between the coupling current and the oscillation current. For a given stage, the introduced coupling current from an adjacent stage alters the total current which has phase difference of  $\Phi_{osc}$  with the voltage at the LC tank. Since the zero-phase between the voltage and the current in the LC tank is the oscillation condition at the steady-state as shown in Figure 3.1(b), this requirement forces the LC tank to have  $-\Phi_{osc}$  phase with changing the operating frequency slightly. This can be understood more easily from the open loop model in Figure 3.4. In multi-stage coupled oscillators phase shifting is introduced in the loop due to the out of phase coupling current. In order for the sum of phases around the loop to be zero, the LC tank should have same phase but with opposite polarity. This is the steady state condition for oscillation in multi-stage coupled oscillators. Due to the introduced phase component in the LC tank the oscillators do not operate at the same frequency as the single stage oscillator.

The operating frequency can be estimated from the magnitude and phase response

of the transfer function of the tank in Figure 3.4(b). At the operating frequency of the multi-stage oscillator, the derivative of the phase is not the maximum value we get from the single stage oscillator. Therefore, the effective quality factor of the tank is smaller in this type of coupled multi-stage oscillator. As the introduced phase due to increased coupling gets bigger, the effective capacitance of the tank becomes smaller.

Figure 3.3: (a) Basic cell of three stage LC oscillator (note that there are coupling transistors, M5 and M6, in this case) and (b) Phase relationship; coupling current,  $I_{cou}$ , is out of phase with the oscillation current,  $I_{osc}$ , and the total current,  $I_{tot}$ , has  $\Phi_{osc}$  phase difference with the voltage,  $V_o$ .

Figure 3.4: Open loop characteristic for the three stage multi-phase oscillator; Transfer function (a) and magnitude and phase response (b); The multi stage oscillator is no longer operate at the point of maximum slope and maximum quality factor

## 3.1.3 Three stage coupled LC oscillator with separate current sources

In the case of a three-stage LC oscillator, built with the basic stage shown in Figure 3.5(a), there are separate current sources for the coupling transistors and for the cross-connected regenerative transistors. For a fixed total current, increasing the coupling current moves the phase of the total current closer to that of the coupling current,  $I_{cou}$ , in Figure 3.5(b). With stronger coupling, the phase accuracy of the multiple phases is improved, but there is also increasing the phase difference,  $\Phi_{osc}$ , between total current  $I_{tot}$  and  $I_{osc}$ . Because of the phase difference  $\Phi_{osc}$ , the effective quality factor of the each stage is degraded and, thus, the oscillator phase noise increases. On the other hand, increasing the current to the cross coupled transistors,  $I_{osc}$ , and decreasing the coupling current,  $I_{cou}$ , reduces the phase difference,  $\Phi_{osc}$ , and decreases the phase noise but also increasing the phase spacing error. Therefore, with the separate current sources we can increase the current for coupling between oscillators or increase the current for the cross coupled transistors. In other words, we cannot decrease the phase spacing error and phase noise at the same time.

Figure 3.5: (a) Oscillator stage with separate current sources for coupling and cross-coupled transistors (b) Phase relationship; With changing coupling current,  $I_{cou}$ , and oscillation current,  $I_{osc}$ , we can have different phase difference,  $\Phi_{osc}$ , between total current,  $I_{tot}$ , and the voltage,  $V_o$ .

# 3.2. Capacitive coupling

Introducing capacitive coupling to a conventional multi-stage oscillator is a simple method to reduce both phase-spacing-error and phase noise. Unlike conventional coupling with coupling transistors, capacitive coupling introduces an in-phase coupling current whose phase is same as that of the oscillation current and the coupling strength is much larger than the coupling power with a conventional coupling connection. Another benefit is that the in-phase coupling power increases with the operating frequency.

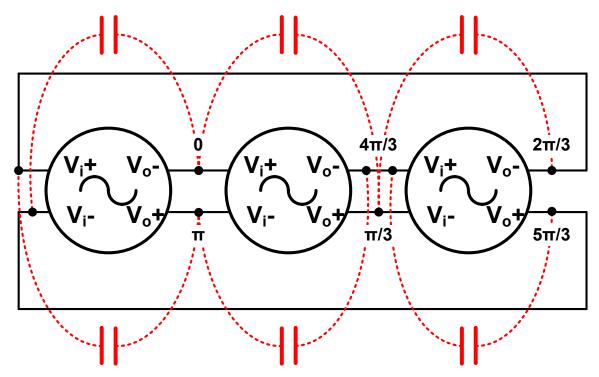

# 3.2.1 Architecture

Capacitive coupling can be used along with the conventional coupling with the coupling transistors. It cannot be used as a stand alone coupling method, since capacitive coupling alone cannot define the oscillation direction properly. Capacitive coupling can be accomplished with a ring of capacitors as shown in Figure 3.6. It also shows the phase relationship for a 3 stage LC oscillator ring. The connections of the coupling capacitors are shown with a dashed line. The capacitors connect the oscillator nodes in the order of the phases (i.e. 0°, 60°, and 120° and so on) forming a ring.

Figure 3.6: Phase relationship in a 3 stage LC oscillator ring. Coupling capacitors are shown with dashed line (coupling capacitors form a ring of capacitors)

#### 3.2.2 Phasor diagram