# DESIGN AND ANALYSIS OF POWER DISTRIBUTION NETWORKS IN VLSI CIRCUITS

#### by

# Sanjay Pant

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 2008

#### **Doctoral Committee:**

Professor David Blaauw, Chair Professor John P. Hayes Associate Professor Igor L. Markov Associate Professor Dennis M. Sylvester Eli Chiprout, Intel © <u>Sanjay Pant</u>

All Rights Reserved

2008

To my Parents

#### **ACKNOWLEDGEMENTS**

Looking back at my stay in Ann Arbor, I see a number of people who have helped me in this endeavor. I would like to take this opportunity to express my sincere gratitude to all of them.

First of all I would like to thank my advisor Professor David Blaauw. I have always considered myself to be very fortunate to have had him as my advisor. I have learnt a lot from him. His enthusiasm and energy has been the source of my motivation and inspiration all throughout my journey through graduate school. This work would not have been possible without his guidance and encouragement.

I am thankful to Professor Hayes, Professor Markov, Professor Sylvester and Dr. Chiprout for serving on my committee and for their valuable feedback. I would also like to acknowledge all my co-authors who have helped me grow professionally.

I thank Edward Chusid, Bertha Wachsman, Amanda Brown, Denise DuPrie and Beth Stalnaker for the help provided in managing a lot of different things. Special thanks to Amanda for the cookies during paper-submission and tapeout deadlines.

Finally, I would like to thank my family and friends. My family has been a constant source of support and encouragement, and all credit goes to them for whatever I accomplish. Thanks to Visvesh, Ashish, Shidhartha, Sarvesh, Kavi, Ravi, Manav, Carlos, Rajeev and other friends who made my stay in Ann Arbor, some of the best years of my life.

# **TABLE OF CONTENTS**

| DEDICATION | ON                                                                | ii  |

|------------|-------------------------------------------------------------------|-----|

| ACKNOWL    | LEDGEMENTS                                                        | iii |

| LIST OF FI | GURES                                                             | vii |

| LIST OF TA | ABLES                                                             | xii |

| CHAPTER    | I                                                                 |     |

| INTRO      | DDUCTION                                                          | 1   |

|            | 1.2 Power-grid modeling and voltage-drop analysis                 | 6   |

|            | 1.3 Impact of supply noise on circuit performance                 | 11  |

|            | 1.4 Decoupling-capacitance modeling and allocation                | 12  |

|            | 1.5 Ringing in power supply networks                              | 17  |

|            | 1.6 Active supply-voltage regulation and supply-noise measurement | 21  |

|            | 1.7 Contributions of this work and organization                   | 23  |

|            |                                                                   |     |

| CHAPTER    | II                                                                |     |

|            | ORLESS ANALYSIS OF SUPPLY-NOISE INDUCED DELAY                     |     |

|            | ATION                                                             |     |

| •          | 2.1 Introduction                                                  | 28  |

|            | 2.2 Delay model for supply fluctuations                           | 31  |

|            | 2.3 Voltage-drop sensitivity computation                          | 38  |

|            | 2.4 Block-current constraints                                     | 42  |

|            | 2.5 Overall path-based delay-maximization formulation             | 46  |

|            | 2.6 Block-based circuit-delay model                               | 49  |

| ,          | 2.7 Experimental results                                          | 55  |

|       | 2.8 Conclusions                                                   | 63  |

|-------|-------------------------------------------------------------------|-----|

| СНАРТ |                                                                   |     |

| PC    | OWER-SUPPLY-DROP ANALYSIS                                         |     |

|       | 3.1 Introduction                                                  |     |

|       | 3.2 Constraint-based early supply-drop analysis                   |     |

|       | 3.3 Statistical supply-drop analysis                              | 68  |

|       | 3.4 Experimental results                                          | 79  |

|       | 3.5 Conclusions                                                   | 85  |

|       | ER IV MING-AWARE DECOUPLING-CAPACITANCE ALLO DWER SUPPLY NETWORKS |     |

|       | 4.1 Introduction                                                  | 86  |

|       | 4.2 Proposed global-optimization approach                         | 89  |

|       | 4.3 Greedy path-based approach                                    | 100 |

|       | 4.4 Experimental results                                          | 101 |

|       | 4.5 Conclusions                                                   | 104 |

|       | ER V<br>DUCTANCE, LOCALITY AND RESONANCE IN POW<br>ETWORKS        |     |

|       | 5.1 Introduction                                                  | 105 |

|       | 5.2 Full-wave on-die inductive effects                            | 107 |

|       | 5.3 Mid-size model and capacitive effects                         | 112 |

|       | 5.4 Complete package-die model                                    | 117 |

|       | 5.5 Conclusions and CAD implications                              | 121 |

|       | N ANALOG ACTIVE DECAP CIRCUIT FOR INDUCTIV                        |     |

| N(    | DISE SUPPRESSION                                                  |     |

|       | 6.1 Introduction                                                  | 123 |

| 6.2 Proposed active decap circuit                                    | 125 |

|----------------------------------------------------------------------|-----|

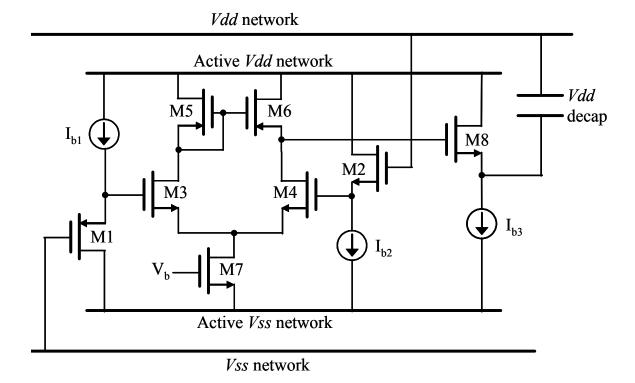

| 6.3 Opamp design                                                     | 133 |

| 6.4 Simulation results                                               | 136 |

| 6.5 Conclusions                                                      | 143 |

| CHAPTER VII                                                          |     |

| DIGITAL CIRCUIT-TECHNIQUES FOR ACTIVE INDUCTIVE-SUINOISE SUPPRESSION |     |

| 7.1 Introduction                                                     | 144 |

| 7.2 Charge-injection-based active decoupling circuit                 | 146 |

| 7.3 High-voltage charge-pump-based active decoupling circuit         | 165 |

| 7.4 High-voltage shunt-supply-based active decoupling circuit        | 170 |

| 7.5 Digital on-chip oscilloscope for supply-noise measurement        | 174 |

| 7.6 Conclusions                                                      | 177 |

| CHAPTER VIII                                                         |     |

| CONCLUSIONS AND FUTURE DIRECTIONS                                    | 179 |

| 8.1 Contributions                                                    | 179 |

| 8.2 Future directions                                                | 183 |

| BIBLIOGRAPHY                                                         | 185 |

# **LIST OF FIGURES**

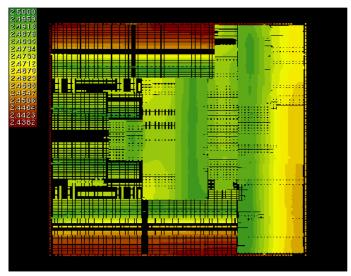

| Figure 1.1: | On-die IR voltage map of the PowerPC® microprocessor (source: Motorola)                                                             |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------|

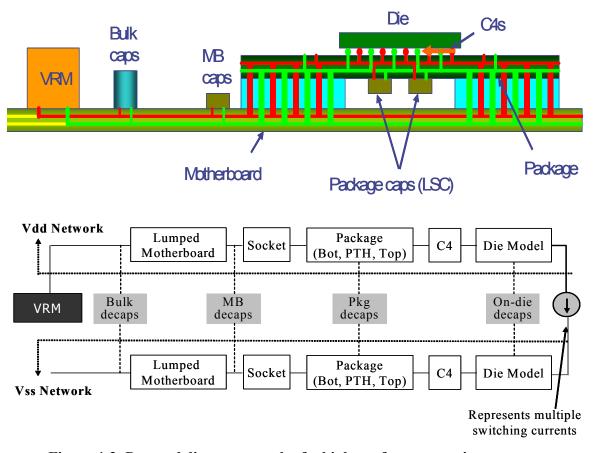

| Figure 1.2: | Power delivery network of a high-performance microprocessor (source:Intel)                                                          |

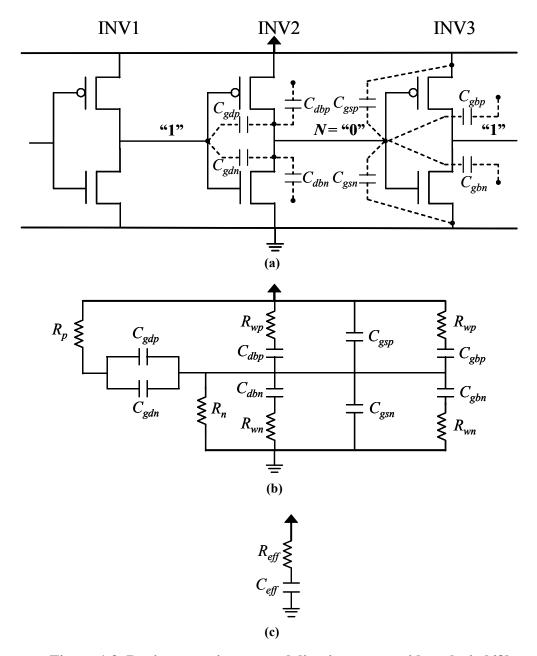

| Figure 1.3: | Device-capacitance modeling in power-grid analysis [68]                                                                             |

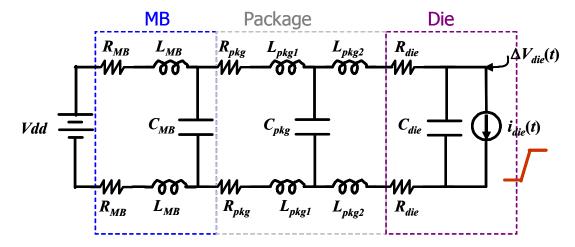

| Figure 1.4: | Simplified model of a power supply network18                                                                                        |

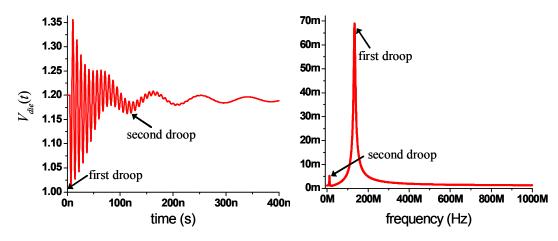

| Figure 1.5: | Transient and frequency response showing first and second droops                                                                    |

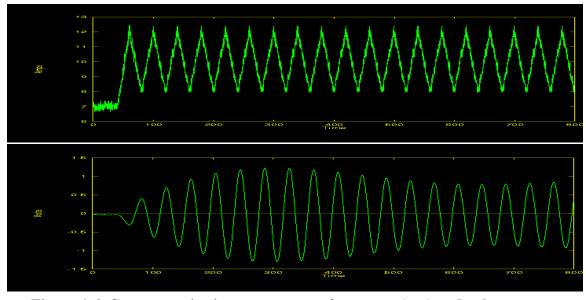

| Figure 1.6: | Current excitation at resonance frequency (top) and voltage response (bottom) (source: Motorola)                                    |

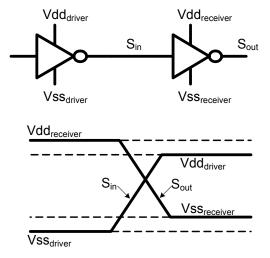

| Figure 2.1: | A driver-receiver pair in a non-ideal supply network                                                                                |

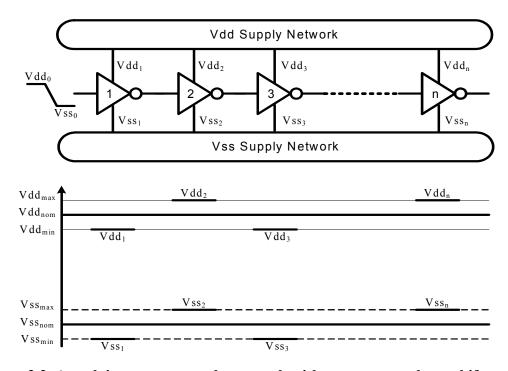

| Figure 2.2: | A path in a power supply network with worst-case voltage shifts causing the maximum path delay                                      |

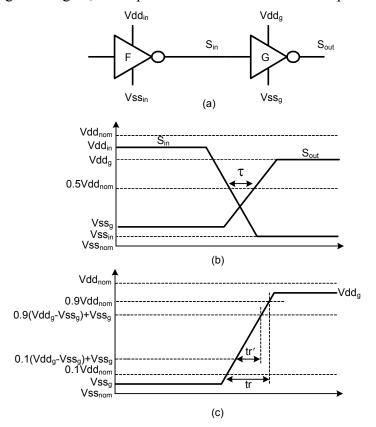

| Figure 2.3: | A driver-receiver pair in a non-ideal supply network (a), propagation delay (b) and output transition time (c)                      |

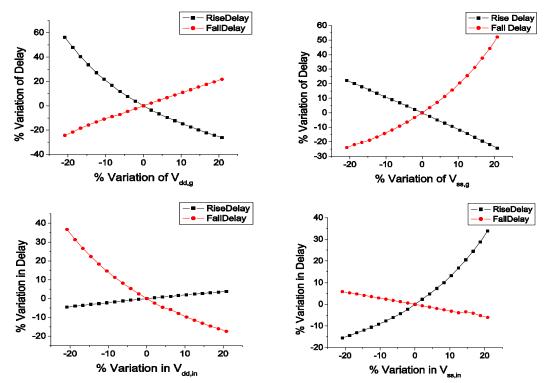

| Figure 2.4: | Variation of rise/fall propagation delays of a gate with respect to Vddg, Vssg, Vddin and Vssin                                     |

| Figure 2.5: | Library-characterization error for delay and transition time for more than 35,000 sample points                                     |

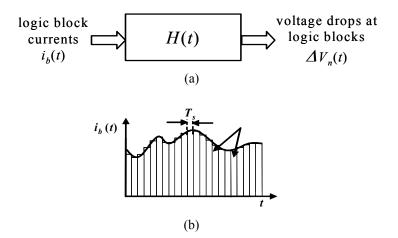

| Figure 2.6: | (a) Power grid as a linear system and (b) Time-varying block-current discretization into time-steps                                 |

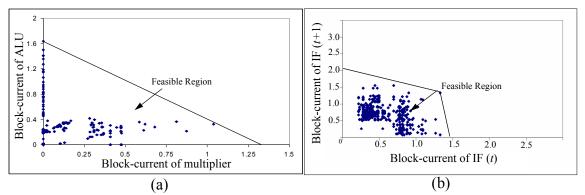

| Figure 2.7: | Correlation between Multiplier and ALU block-currents (a) and correlation between IF-stage in cycle t and ID-stage in cycle t+1 (b) |

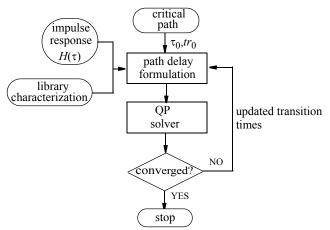

| Figure 2.8. | Path-based delay-maximization accounting for transition-time variations 48                                                          |

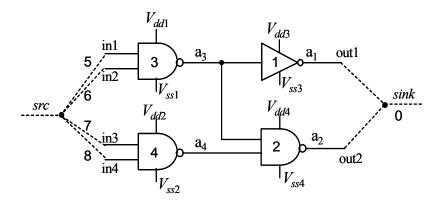

| Figure 2.9: An example of a combinational circuit                                                   | 19             |

|-----------------------------------------------------------------------------------------------------|----------------|

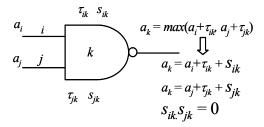

| Figure 2.10: Illustration of the removal of the max function                                        | 51             |

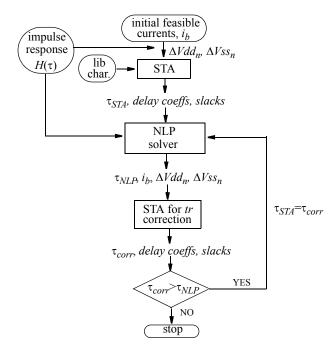

| Figure 2.11: Overall block-based circuit-delay-maximization flow                                    | 53             |

| Figure 2.12: An illustration of delay-based circuit pruning to reduce the problem size5             | 55             |

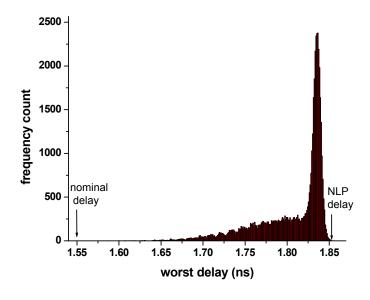

| Figure 2.13: Comparison of block-based NLP with random runs for c880                                | 59             |

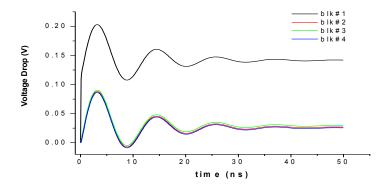

| Figure 2.14: Step response at a node due to different blocks (resonance frequency = 50MHz)          | 50             |

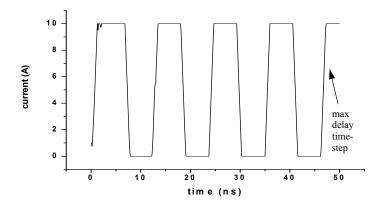

| Figure 2.15: Time-varying total chip-current obtained from the block-based delay maxim zation       |                |

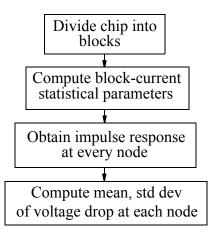

| Figure 3.1: Flow diagram of proposed statistical approach                                           | 58             |

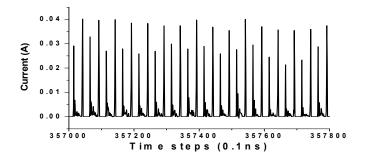

| Figure 3.2: Variation of a block-current with time                                                  | 72             |

| Figure 3.3: PDF (a) and auto-correlation (b) of a block-current                                     | 73             |

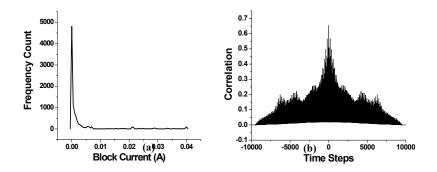

| Figure 3.4: Probability distribution of the overall worst-case drop                                 | 31             |

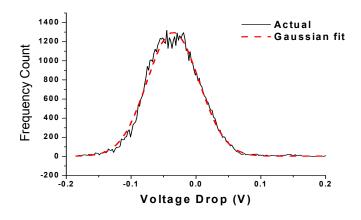

| Figure 4.1: A combinational circuit in a power distribution network                                 | 39             |

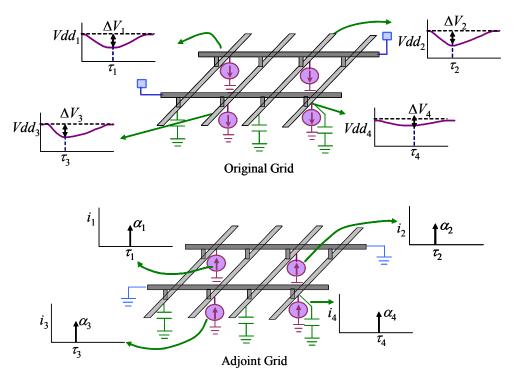

| Figure 4.2: Illustration of gradient computation using the modified adjoint-sensitivity method.     | €7             |

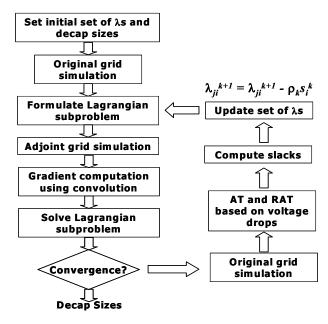

| Figure 4.3: Overall global-optimization flow                                                        | <del>)</del> 9 |

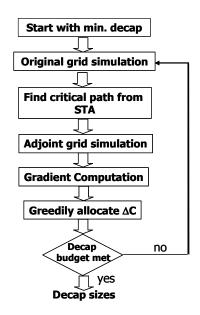

| Figure 4.4: Optimization flow of path-based greedy algorithm                                        | )0             |

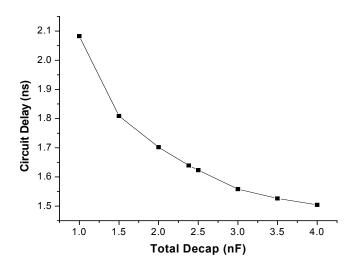

| Figure 4.5: Decap area vs circuit-delay trade-off curve for c432                                    | )2             |

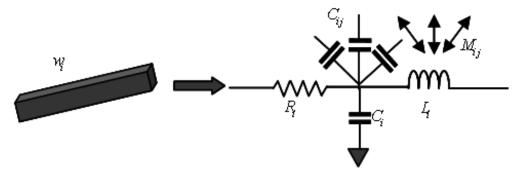

| Figure 5.1: Illustration of the PEEC model of a wire segment                                        | )8             |

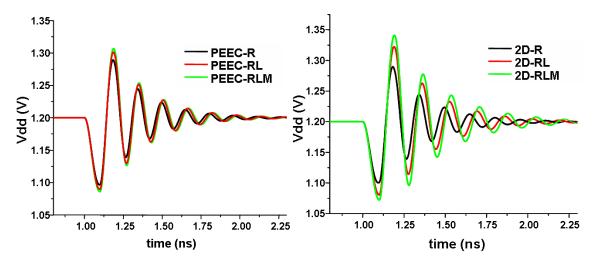

| Figure 5.2: A 3D PEEC simulation of 500mx500m grid (left) compared to a 2D-modelin approach (right) | _              |

| Figure 5.3: Voltage map generated due to high-frequency current transients                          | 11             |

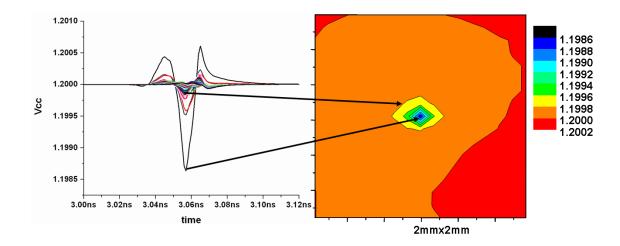

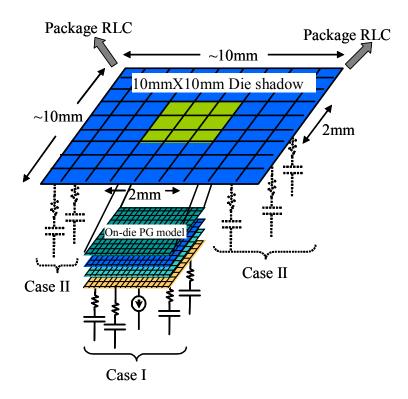

| Figure 5.4: A 2mm X 2mm section of on-die grid attached to the middle of package sharow             |                |

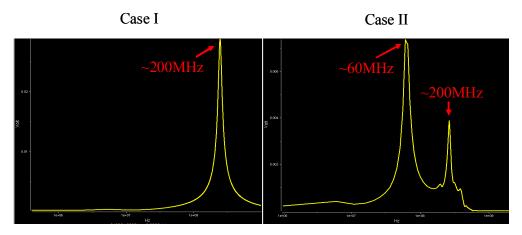

| Figure 5.5: Supply drop frequency response showing resonance frequencies for Case I an              | ıd             |

|             | Case II illustrated in Table 5.4                                                                        | 14 |

|-------------|---------------------------------------------------------------------------------------------------------|----|

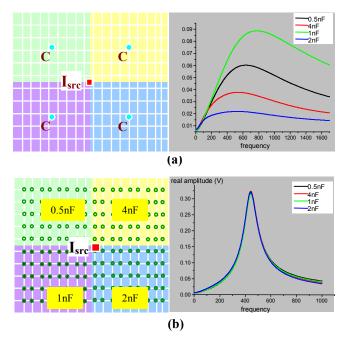

| Figure 5.6: | A 2mm X 2mm section of the grid with lumped (a) and distributed decouplin capacitors (b)                |    |

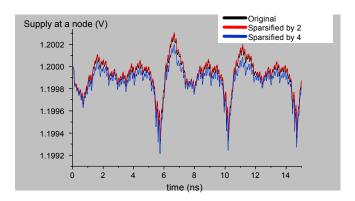

| Figure 5.7: | Voltage response of a 2mm X 2mm with 2x- and 4x-reduced grids for identic current excitation            |    |

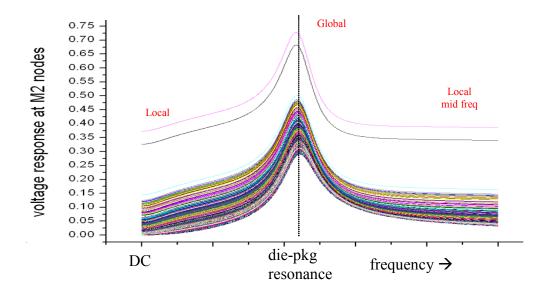

| Figure 5.8: | Frequency response at all the M2 supply nodes illustrating locality as function of excitation frequency |    |

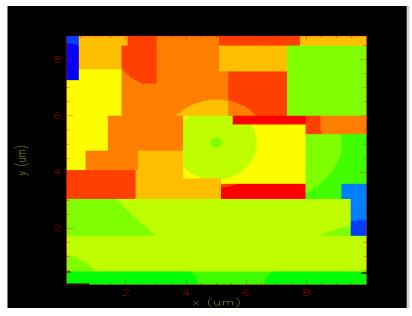

| Figure 5.9: | The non-uniform block-based on-die decap distribution in the microprocessor                             |    |

| Figure 5.10 | D: Transient current response of non-uniform decaps (left) and the magnified pl<br>(right)              |    |

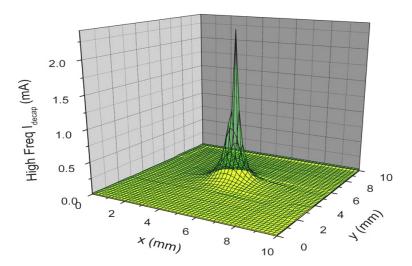

| Figure 5.11 | 1: Locality of high-frequency currents provided by decaps                                               | 19 |

| Figure 5.12 | 2: Distribution of mid-frequency decap currents which are strongly correlated decap distribution map    |    |

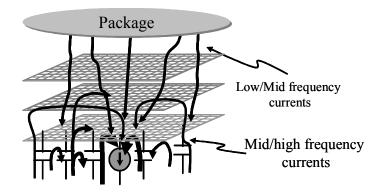

| Figure 5.13 | 3: A visualization of the flow of currents on die                                                       | 20 |

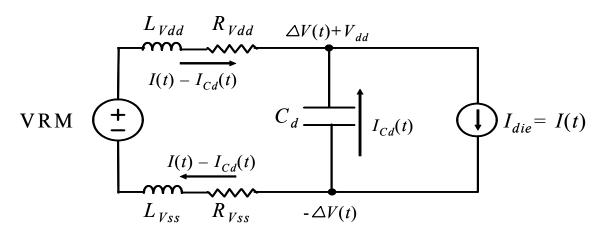

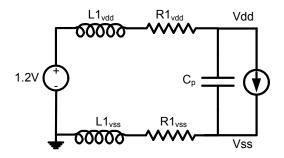

| Figure 6.1: | Model of a power delivery network                                                                       | 25 |

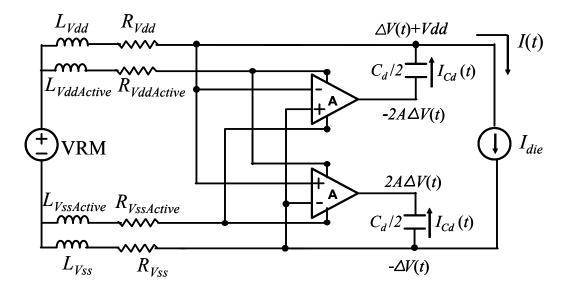

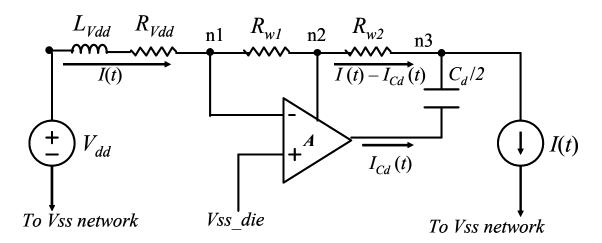

| Figure 6.2: | Proposed active decoupling capacitance circuit                                                          | 28 |

| Figure 6.3: | Need for external active supply for operational amplifiers                                              | 29 |

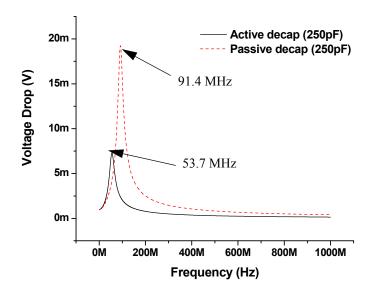

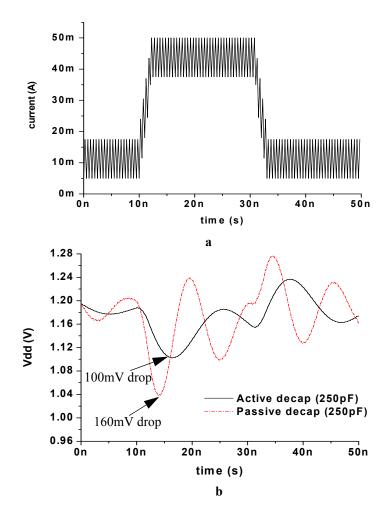

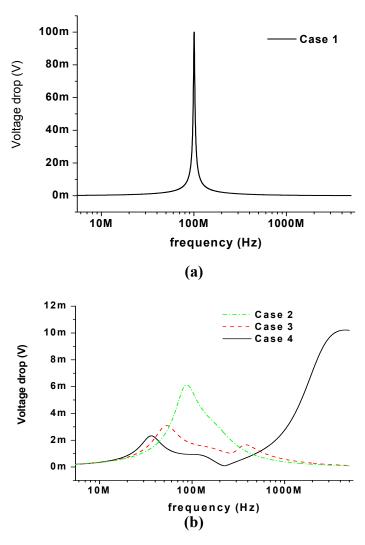

| Figure 6.4: | Comparison of frequency response with active and passive decaps                                         | 31 |

| Figure 6.5: | Transient current profile (a) and voltage response (b) using active and passive decaps                  |    |

| Figure 6.6: | Operational amplifier schematic                                                                         | 34 |

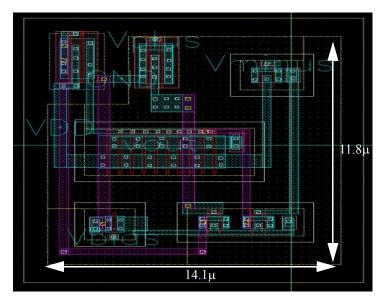

| Figure 6.7: | Layout of the opamp with drive strength of 5pF                                                          | 37 |

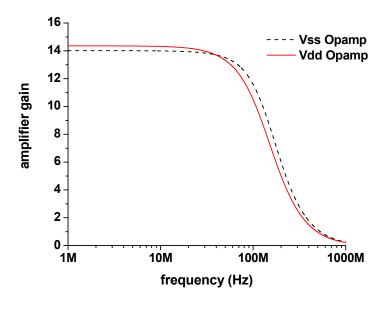

| Figure 6.8: | Gain of the opamp                                                                                       | 37 |

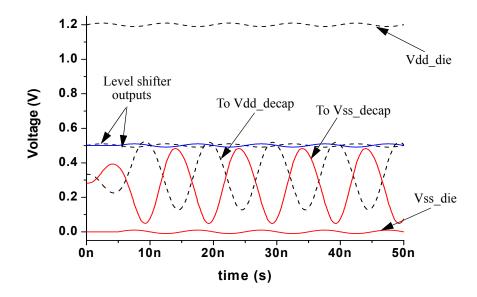

| Figure 6.9: | Transient response of the opamp                                                                         | 38 |

| Figure 6.10 | 0: Comparison of frequency response of power grid with different decap sizes                            | 39 |

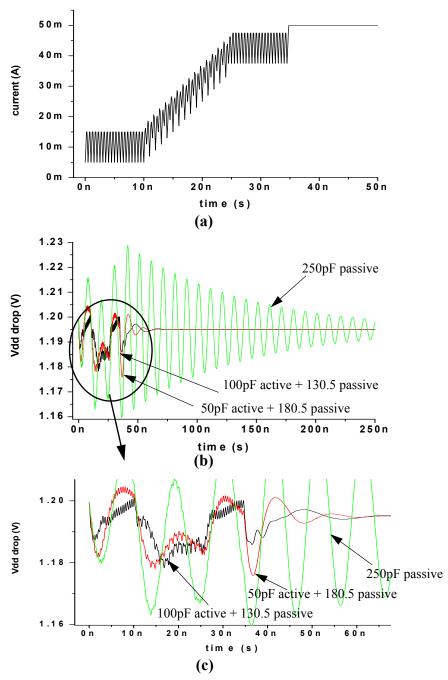

| Figure 6.11: Comparison of transient response of power grid with different decap sizes                   |       |

|----------------------------------------------------------------------------------------------------------|-------|

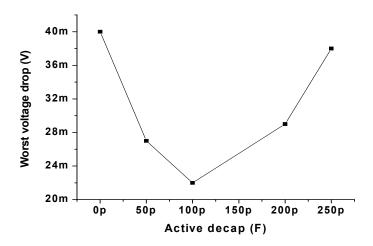

| Figure 6.12: Worst-case voltage-drop variation with decap allocation                                     | . 142 |

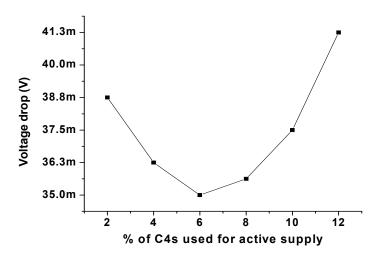

| Figure 6.13: Impact of C4 distribution on worst-case voltage drop                                        | . 143 |

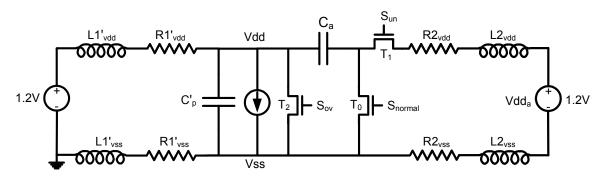

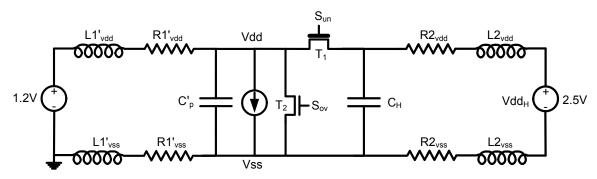

| Figure 7.1: A simplified power distribution model and the proposed regulation technique                  | . 147 |

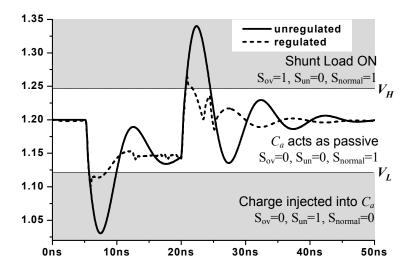

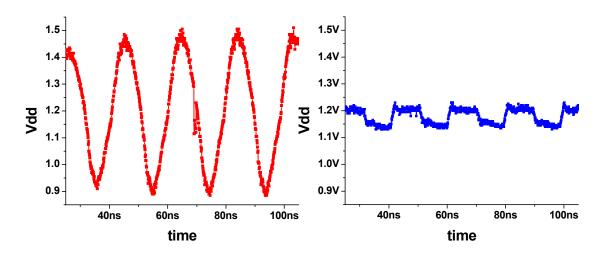

| Figure 7.2: Simulated unregulated and regulated supply waveforms and safety bounds                       | s148  |

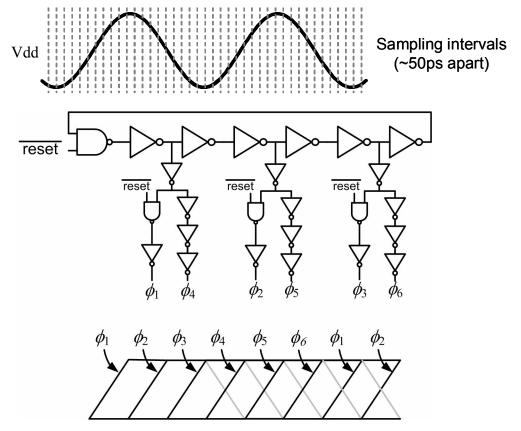

| Figure 7.3: Sampling clock generator                                                                     | . 150 |

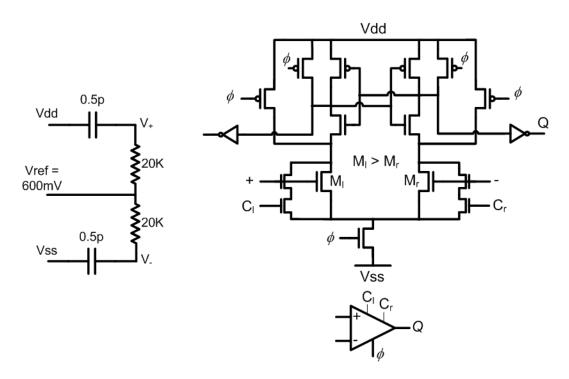

| Figure 7.4: Vdd/Vss level shifter and clocked-comparator schematics                                      | . 150 |

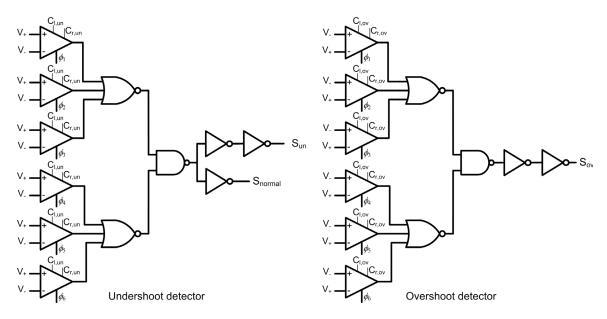

| Figure 7.5: Comparator banks and generation of normal, undershoot and overshoot signals                  |       |

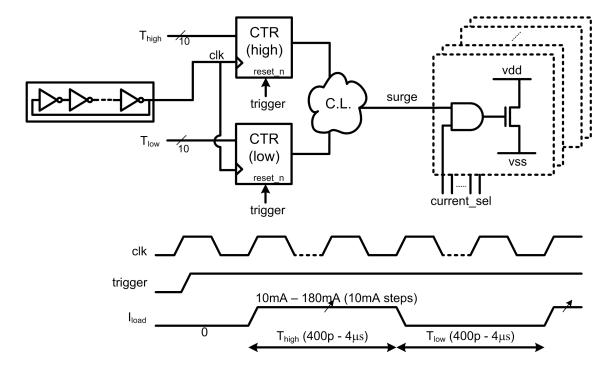

| Figure 7.6: Synthetic load-current generator                                                             | . 152 |

| Figure 7.7: V-I converter-based drop-detector circuit                                                    | . 153 |

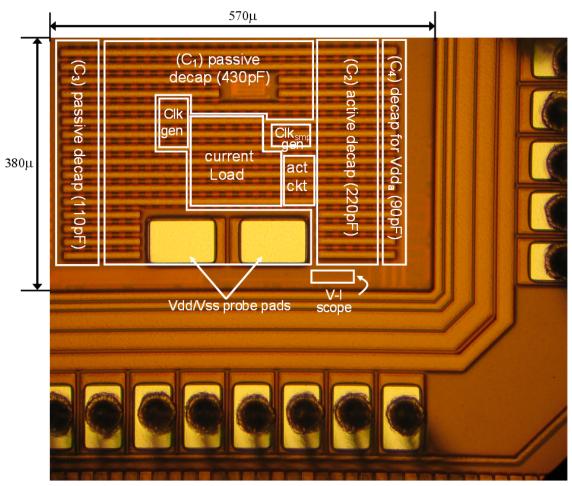

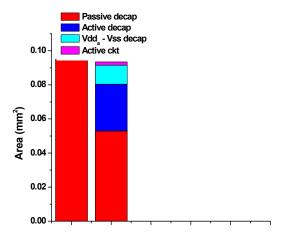

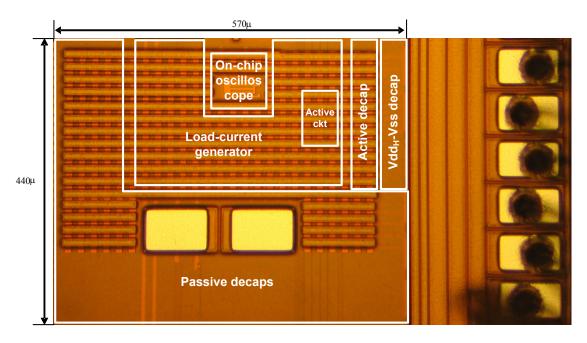

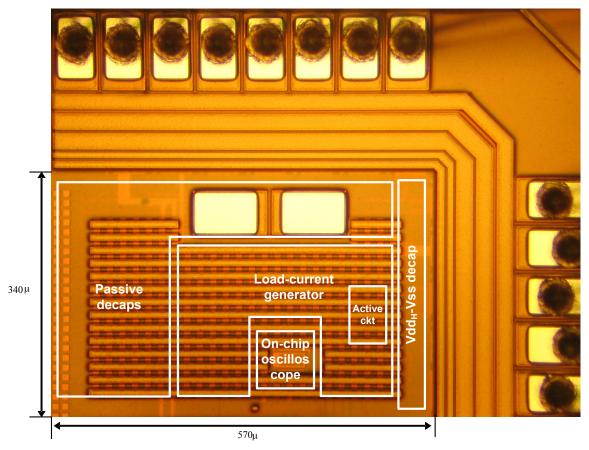

| Figure 7.8: Die micrograph and implementation details of the test chip                                   | . 154 |

| Figure 7.9: Area breakdown in unregulated and regulated test-cases                                       | . 155 |

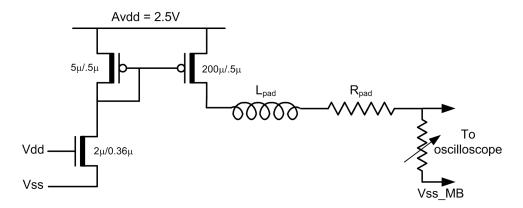

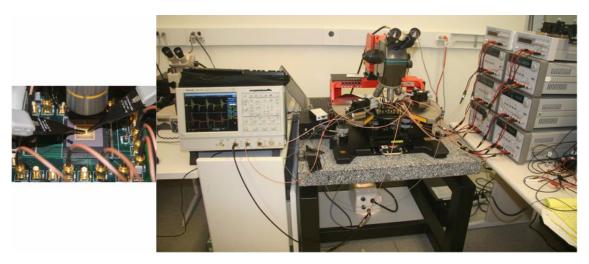

| Figure 7.10: Measurement setup                                                                           | . 156 |

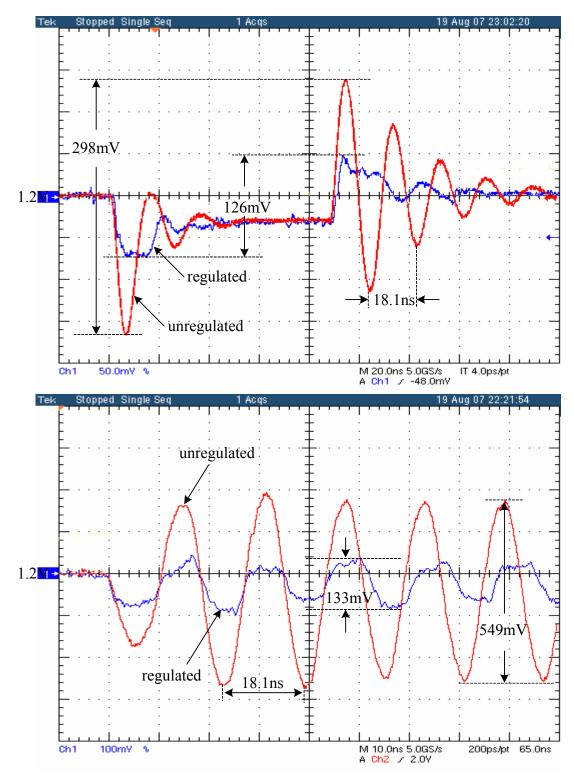

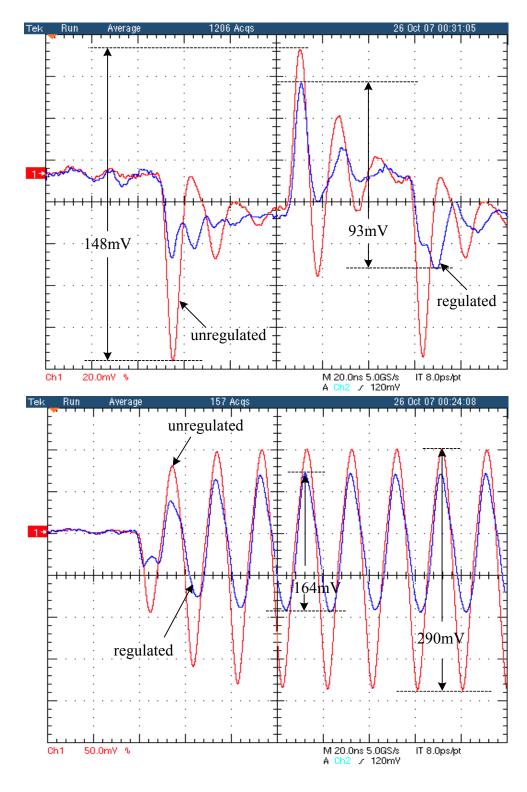

| Figure 7.11: Measured unregulated and regulated supply noise waveforms for ramp loand during resonance   |       |

| Figure 7.12: Measured unregulated and regulated supply waveforms as a function of trip signal            |       |

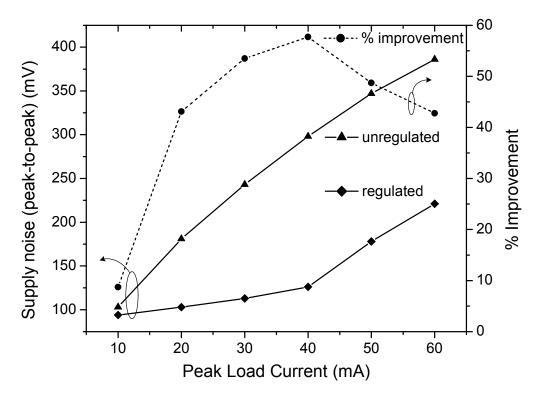

| Figure 7.13: Measured unregulated and regulated peak-to-peak supply noise for varying peak load-currents | _     |

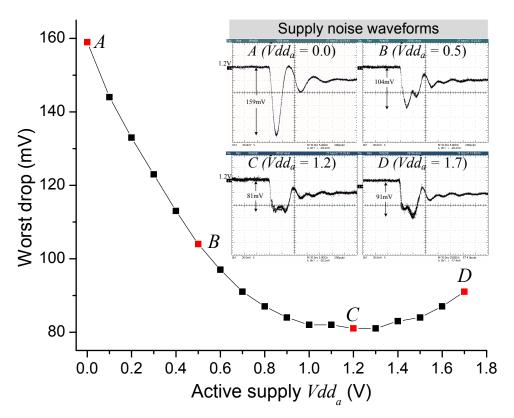

| Figure 7.14: Measured worst supply drop as a function of the active supply voltage                       | . 160 |

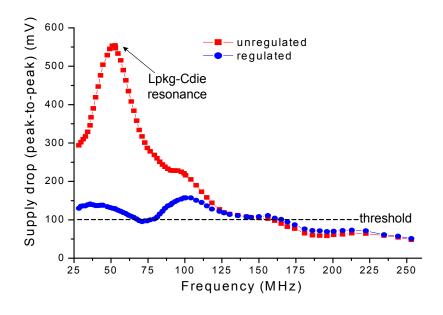

| Figure 7.15: Comparison of measured frequency responses with and without active supregulation            |       |

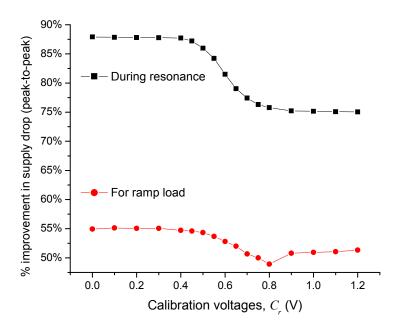

| Figure 7.16: Measured worst regulated supply drop as a function of calibration voltages                  |       |

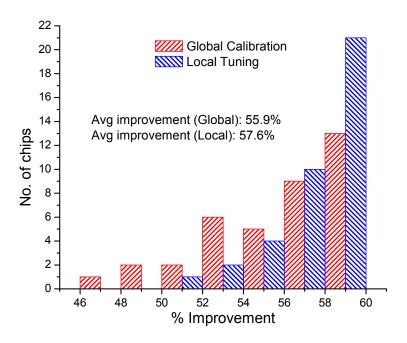

| Figure 7.17: Statistical analysis across 38 chips showing the affect of a global calibration vs. individual die-tuning |

|------------------------------------------------------------------------------------------------------------------------|

| Figure 7.18: Measured supply waveforms with on-chip V-I detector and active on-chip probing164                         |

| Figure 7.19: Proposed high-voltage charge-pump-based regulation circuit technique 166                                  |

| Figure 7.20: Die micrograph and implementation details of the test chip                                                |

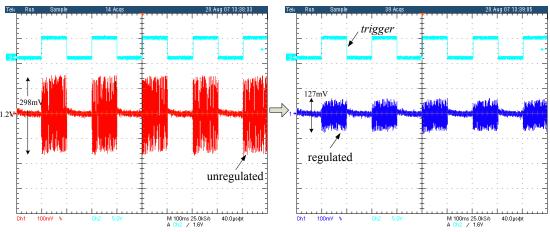

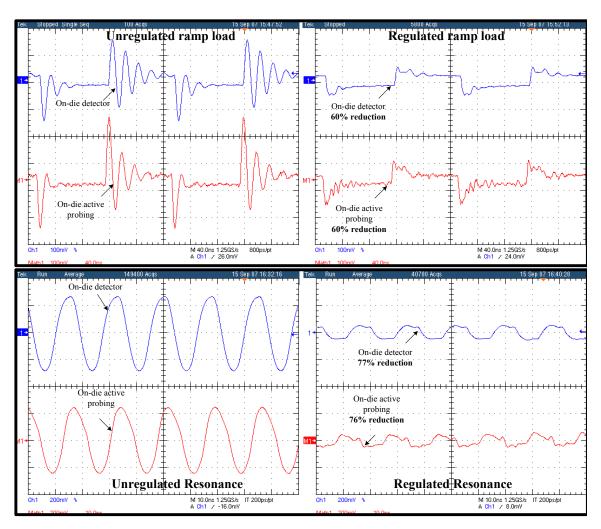

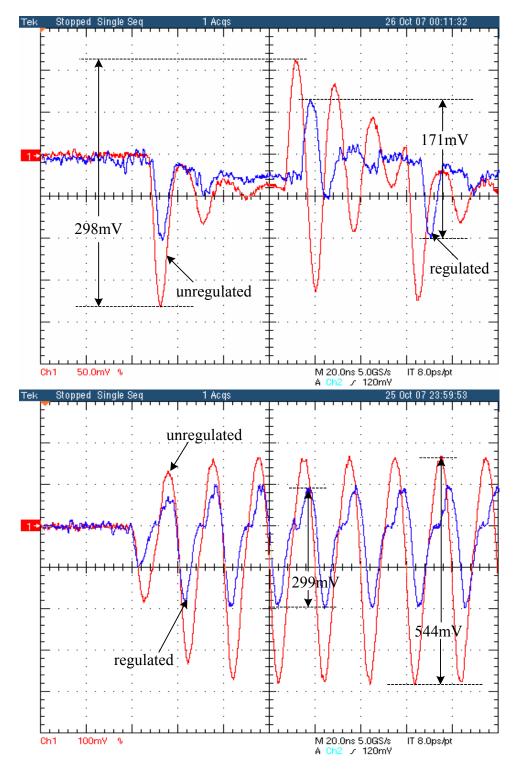

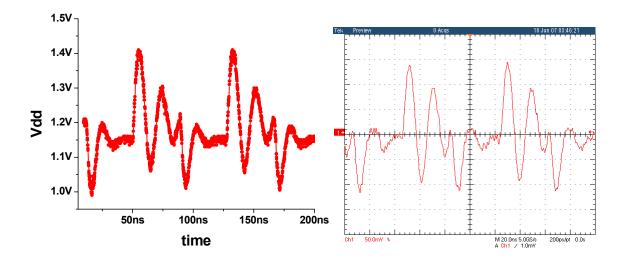

| Figure 7.21: Measured unregulated and regulated supply noise waveforms for ramp load and during resonance              |

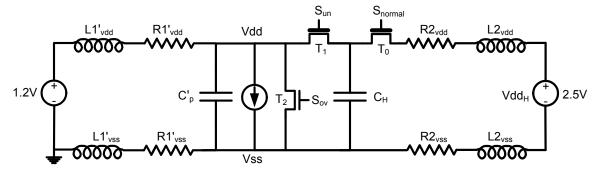

| Figure 7.22: Schematic of the proposed high-voltage shunt-supply-based regulation technique                            |

| Figure 7.23: Die micrograph and implementation details of the test chip                                                |

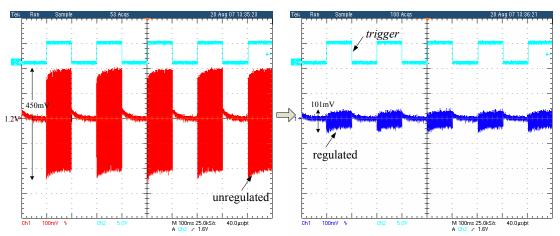

| Figure 7.24: Measured unregulated and regulated supply noise waveforms for ramp load and during resonance              |

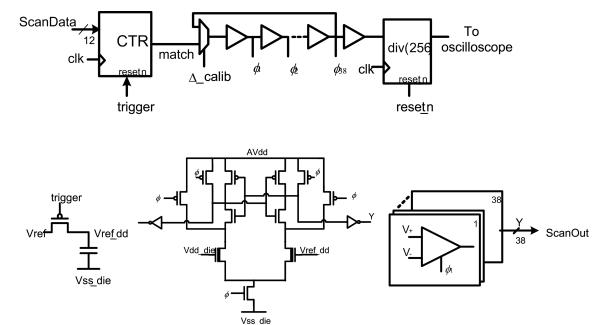

| Figure 7.25: Schematic of the proposed on-chip oscilloscope for supply-noise measurement                               |

| Figure 7.26: Unregulated (left) and regulated (right) resonance waveforms measured using the on-chip oscilloscope      |

| Figure 7.27: Measured supply waveform using the on-chip oscilloscope (left) and the V-I converter (right)              |

# LIST OF TABLES

| Table 1.1: Summary of the key contributions                                                                 | 23  |

|-------------------------------------------------------------------------------------------------------------|-----|

| Table 2.1: Experimental results for DC current constraints                                                  | 56  |

| Table 2.2: Random-run comparison with NLP                                                                   | 59  |

| Table 2.3: Experimental results for AC (time-varying) current constraints                                   | 61  |

| Table 2.4: Run-time reduction due to circuit pruning                                                        | 63  |

| Table 3.1: Comparison of worst-case voltage drops                                                           | 80  |

| Table 3.2: Mean, standard deviation and 95% interval of the voltage drops                                   | 82  |

| Table 3.3: Comparison with HSPICE                                                                           | 83  |

| Table 3.4: Effect of correlations on accuracy and run-time                                                  | 84  |

| Table 4.1: Experimental results showing delay reduction for a given decap budget                            | 103 |

| Table 4.2: Experimental results showing reduction in decap area for specified timing straint                | •   |

| Table 5.1: Run-time and peak memory-usage of the 2mm X 2mm model before and multi-grid-based sparsification |     |

#### CHAPTER I

#### Introduction

#### 1.1 Overview and motivation

Power distribution networks deliver the power and the ground voltages from pad locations to all devices in a design. Shrinking device dimensions, faster switching frequency and increasing power consumption in deep submicron technologies cause large switching currents to flow in the power and ground networks. Rapidly switching currents cause spatial and temporal fluctuations in the supply voltage which may cause functional failures in a design, degrade circuit performance and create reliability concerns. A robust power distribution network is essential to ensure reliable operation of circuits on a chip. Power-supply integrity verification is, therefore, a critical concern in high-performance designs.

Due to the resistance of the interconnects constituting the network, there occurs a voltage drop across the network, commonly referred to as the IR drop. IR drop is predominantly caused by the parasitic resistance of metal wires constituting the on-chip power distribution network. The package supplies currents to the pads of the power grid either by means of package leads in wire-bond chips or through C4 (controlled collapsed chip connection) bump-array [26][78] in flip-chip technology. Although the resistance of package is quite small, the inductance of package leads is significant which causes a voltage drop at the pad locations due to time-varying currents drawn by devices on the die. This voltage

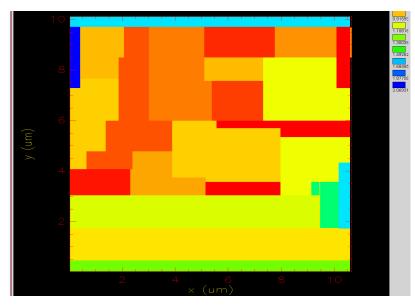

Figure 1.1. On-die IR voltage map of the PowerPC® microprocessor (source: Motorola)

drop is referred to as the di/dt drop or Ldi/dt drop. Therefore, the voltage seen at the devices is the supply voltage minus the IR drop and the Ldi/dt drop. Figure 1.1 shows the voltage map of a high-performance microprocessor [27] illustrating the spatial variation in supply drop at the on-die devices.

Excessive voltage drops in the power grid reduce switching speeds [16][66][79] and noise margins of circuits, and inject noise which may lead to functional failures. High average-current densities can also lead to undesirable wear-out of metal wires due to electromigration(EM) [7]. Therefore, the challenge in the design of a power distribution network is in achieving excellent voltage regulation at the consumption points notwithstanding the wide fluctuations in power-demand across the chip, and to build such a network using minimum area of the metal layers. These issues are prominent in high-performance chips such as microprocessors, since large amounts of power, in the order of hundreds of Watts, have to be distributed through a hierarchy of metal layers. A robust

power distribution network is vital in meeting performance guarantees and in ensuring the reliable operation of a chip.

Capacitance between power and ground distribution networks, referred to as the decoupling capacitance or *decap*, acts as local charge storage and is helpful in mitigating the voltage drop at supply points. Parasitic capacitance between metal wires of supply lines, device capacitance of the non-switching devices, and capacitance between N-well and substrate, occur as implicit decoupling capacitance in a power distribution network. Unfortunately, this implicit decoupling capacitance is not enough to constrain the voltage drop within safe bounds and designers have to often add intentional explicit decoupling-capacitance structures on the die at strategic locations [15]. These explicitly added decoupling capacitances are not free and increase the area and the leakage-power consumption of the chip. Parasitic interconnect resistance, decoupling capacitance and package/interconnect inductance form a complex RLC network which has its own resonance frequency [47][59]. If this resonance frequency lies close to the operating frequency of the design, large voltage drops can develop in the grid.

Figure 1.2 shows the power distribution network of a typical high-performance microprocessor in detail. The voltage regulator module (VRM), located on the motherboard (MB), provides the nominal supply voltage to the die through wire-bond pads or C4 bumps. Decoupling capacitances are inserted at various levels (on-die, package, motherboard and VRM) in order to suppress the Ldi/dt noise in the supply.

The crux of the problem in designing a power grid lies in the fact that there are many unknowns until the very end of the design cycle. Nevertheless, decisions about the structure, size and layout of the power grid have to be made at very early stages when a large

Figure 1.2. Power delivery network of a high-performance microprocessor (source:Intel)

part of the chip design has not even begun. Unfortunately, most commercial tools focus on post-layout verification of the power grid when the entire chip design is complete and detailed information about the parasitics of the power and ground lines and the currents drawn by the transistors are known. Power grid problems revealed at this stage are usually very difficult and/or expensive to fix. Also, due to the growth in power consumption and switching speeds of modern high-performance microprocessors, the di/dt effects are becoming a growing concern in these designs. Clock-gating or power-gating, which is a preferred scheme for power management in high-performance designs, can cause rapid surges in current demands of macro-blocks and increase di/dt effects. Designers rely on the on-chip parasitic capacitances and intentionally added decoupling capacitors to coun-

ter the Ldi/dt variations in the supply voltage. It is necessary to accurately model the inductance and capacitance of the package and chip in detail and then analyze the power grid to avoid any underestimation/overestimation in the amount of added decap. Also, it is necessary to maintain the efficiency of the analysis after including these detailed models.

A critical issue in the analysis of power grids is the large size of the network (typically millions of nodes in a state-of-the-art microprocessor). Simulating all the non-linear devices in the chip together with the power grid is computationally infeasible. To make the model-size manageable, the simulation is done in two steps. First, the non-linear devices are simulated assuming ideal supply voltages and the currents drawn by the devices are measured. Next, during power grid simulation, the non-linear devices are replaced by the measured time-varying current sources. Note that the non-linear simulation to generate the time-varying currents is performed assuming a nominal supply and does not account for any drops in the supply voltage. However, since the voltage drops are typically less than 10% of the nominal supply voltage, the error incurred by ignoring the interaction between the device currents and the supply voltage is small.

The circuit-currents are not independent because of signal correlations between different logic blocks. This has traditionally been addressed by deriving the inputs for individual blocks of the chip from the results of logic simulation using a common set of chip-wide input vectors. An important issue in power-grid analysis is to determine what these input vectors should be. For IR-drop analysis, patterns that produce maximum instantaneous currents are required, whereas for the verification of electromigration issues, patterns producing large sustained (average) currents are of interest. For Ldi/dt-drop analysis, input-vector search is even more challenging because the worst Ldi/dt drop at a particular point

in time is dependant on the previous history of currents. Maximizing Ldi/dt drop thus requires simulation of a long pattern of input vectors spanning multiple clock cycles.

In this chapter, we will present in detail the traditional methods for addressing the above-mentioned power-ground signal integrity issues, and will discuss their strengths and shortcomings. This chapter is organized as follows. Section 1.1 presents some popular power grid modeling and analysis techniques. Section 1.2 provides an overview of the impact of supply noise on circuit performance. Section 1.3 explains some commonly used decap modeling and optimization methodologies while Section 1.4 discusses the transient response and resonance in power grids. In Section 1.5, we present some prior-proposed circuit techniques for measurement and suppression of resonance and Ldi/dt noise in supply networks. The research contributions of our work are summarized in Section 1.6.

# 1.2 Power-grid modeling and voltage-drop analysis

Modeling of power distribution networks depends on the accuracy and run-time efficiency tradeoff in the required analysis. Although a purely resistive model of the power distribution network may be sufficient for IR drop computation, a more detailed model including the network capacitances, device parasitic capacitances, explicit decoupling capacitors and the inductance of the package is necessary when analyzing the network with time-varying currents. Due to the increasing switching speeds, the Ldi/dt drop is becoming a significant part of the total voltage drop [69]. Therefore, it has become crucial to model the effect of package inductance. Additionally, the impact and the significance of on-chip inductance on the di/dt effects need to be studied, which requires detailed 3-D inductance models [35][65] of the on-die power supply network. Finally, it is imperative

to accurately model the amount of implicit non-switching decaps and explicitly added decaps. An analysis of the inductance effects without accurately modeling the decoupling capacitance will provide pessimistic results since the high fluctuation of currents at the pads will cause very large voltage swings.

Methods for power-grid analysis can be broadly classified into *input-vector-dependent* methods and *vectorless* methods. The input-vector-dependent methods employ search techniques to find a set of input patterns which cause the worst drop in the grid. A number of methods have been proposed in literature [20][40][46] which use genetic algorithms or other search techniques to find vectors or a pattern of vectors that maximize the total current drawn from the supply network. Input-vector-dependent approaches are computationally intensive and are limited to circuit-blocks rather than full-chip analysis. Furthermore, these approaches are inherently optimistic, underestimating the voltage drop and thus allowing some of the supply noise problems go unnoticed. The vectorless approaches [45][43][61], on the other hand, aim to compute an upper bound on the worst-case drop in an efficient manner. These approaches have the advantage of being fast and conservative, but are sometimes too pessimistic and may therefore lead to over-design. Also, these approaches are limited to static power-supply analysis since they can only account for IR drop.

Most of the above discussed approaches model the power supply network as a linear system and rely on a fast and accurate solution of a linear system of equations. The next subsection describes a few linear system solution techniques which are commonly employed in supply-drop analysis.

#### 1.2.1 Linear-system solution techniques

With the increasing number of devices on a chip, the size of power network has grown so large as to make the power-supply integrity verification very challenging. Several methods have been proposed in the literature to reduce the run-time and memory requirements of power grid simulation. Power grid simulation involves solving the following system of differential equations:

$$Gx(t) + C\dot{x}(t) = b(t)$$

(EQ 1.1)

where G is the conductance matrix; C is the matrix resulting from capacitive and inductive elements; x(t) is the vector of time-varying voltages at the nodes, currents through the inductors and currents through the ideal voltage sources; and b(t) is the vector of the time-varying current sources and the ideal voltage sources.

A method known as Modified Nodal Analysis (MNA) [38][60] transforms the above system of differential equations into the following linear algebraic system which can be solved very efficiently in time-domain:

$$\left(G + \frac{C}{h}\right)x(t) = b(t) + \frac{C}{h}x(t-h)$$

(EQ 1.2)

MNA uses the Backward Euler (BE) technique with a small fixed time-step, h. The BE reduction with a fixed time-step is advantageous for transient simulation since the left hand side (LHS) matrix  $\left(G + \frac{C}{h}\right)$ , referred to as the coefficient matrix, does not change during simulation, allowing for preprocessing or factoring of the matrix for a one-time cost and reusing the factors efficiently to solve the system at successive time points.

Several *direct* [60] and *iterative* [33] approaches are available to solve the linear system of equations as in EQ 1.2. Direct techniques rely on factoring the LHS matrix once into a

product of lower and upper triangular matrices (LU factors) and then using them repeatedly in a simple backward and forward substitution procedure [60] to solve the system at every time-step. Iterative methods, on the other hand, rely on efficient convergence techniques to steer the iterations from an initial guess to the final solution.

The size and structure of the conductance matrix of the power grid is important in determining the type of linear-solution technique (direct or iterative) that should be used. Although, the power grid consists of millions of nodes, the conductance matrix is very sparse (typically, fewer than 5 entries per row/column). Sparsity favors the use of iterative methods, but convergence is slowed down by ill-conditioning and can be accelerated to some extent by preconditioning methods [17]. Iterative methods do not suffer from size limitations so long as the (sparse) matrix and some iteration vectors can fit into the memory. Although the conductance matrix itself is sparse, its LU factors are extremely dense. The number of non-zero entries in the LU factors is of the order  $O(N^2)$ , where N is the number of rows/columns in the coefficient matrix. The single biggest problem with direct methods is the need for large amounts of memory to store the LU factors of the coefficient matrix. However, if only fixed time steps are used for transient analysis, then the initial factorization can be reused with subsequent current vectors, thus amortizing the large decomposition time. Iterative methods do not have this feature of reusability and the linear system needs to be solved iteratively from scratch at every new time step. Iterative methods are best suited for IR-drop analysis which requires simulation of only one time step, or for solving large systems using limited memory resources.

When the vector x(t) in EQ 1.2 consists only of node voltages (power grid network of RC elements and current sources), the coefficient matrix,  $\left(G + \frac{C}{h}\right)$  can be shown to be symmetric and positive-definite [32]. The symmetric-positive-definiteness of the coefficient matrix, which is also very sparse, is especially attractive since the system can now be solved very efficiently using specialized linear system solution techniques, such as Cholesky factorization (direct method) and conjugate gradient (iterative method) techniques. The Modified Nodal Analysis circuit formulation is no longer guaranteed to be positive-definite when inductance is included in the power grid model. However, using a simple nodal formulation or mesh current formulation [24], the RLC model of the power distribution network can also be converted into a symmetric-positive-definite system and above techniques can be used effectively. To further speedup the simulation by exploiting the hierarchy in the supply distribution network, a hierarchical macromodeling-based approach was presented in [87], where the power-grid analysis is performed based on a divide-and-conquer approach by splitting the supply network into a global grid and multiple local grids.

Several other approaches have also been proposed to compute the supply drop. The work in [44] proposes a multigrid-like method [10] for the simulation of large power grids. This method, which is particularly attractive for regular meshes, reduces the size of the network by solving several coarser meshes and interpolating the results to the original fine mesh However, this method has been shown to be error-prone while handling *via* resistances and after a certain level of grid-reduction of the original network. The approach in [43] formulates the IR-voltage-drop maximization problem as a linear optimi-

zation formulation with constraints on block-currents while [61] formulates the IR-drop computation as an integer linear programming (ILP) problem to estimate the worst case switching activity based on working modes of macro-blocks. Recently, a statistical approach [62] based on random walks [29] has been proposed which exploits the spatially localized nature of supply drop in power grids to achieve speed-up in simulation. This approach is very efficient for IR-drop computation but the convergence may be slow in transient Ldi/dt-drop computation. A part of this dissertation is dedicated to finding efficient vectorless approaches which can account for both IR and Ldi/dt drops. The approaches should be useful in the early design phase, when there is limited information about currents of the logic blocks, as well as with detailed simulation models during sign-off.

# 1.3 Impact of supply noise on circuit performance

The voltage fluctuations in a supply network can inject noise in a circuit, leading to functional failures of the design. Extensive work has therefore been focused on modeling and efficient analysis of the worse-case voltage drop in a supply network as discussed in the previous section. Also, with decreasing supply voltages, the gate delay is becoming increasingly sensitive to supply-voltage variation as the difference between the supply voltage and the threshold voltage is consistently getting reduced. With ever-diminishing clock-cycle times, accurate analysis of the supply voltage impact on circuit performance has therefore also become a critical issue.

Power-supply variation can impact the circuit delay in two ways: First, a reduced supply voltage lessens the gate drive strength, thereby increasing the gate delay. Second, a differ-

ence in the supply voltage between a driver and receiver pair creates an offset in the voltage with which the driver/receiver gates reference the signal transition. This has the effect of creating either a positive or negative time shift in the signal transition perceived at the receiver gate. This dual nature of the impact of supply voltage on circuit delay was observed in [16], and complicates the generation of simulation vectors that maximize the delay along a particular circuit path. Increasing the voltage drop at a particular location may worsen the delay of one gate while improving the delay of another. Therefore, determining the path with worst-delay under these often conflicting goals is a complicated task.

Traditionally, the impact of supply noise on delay has been accounted for by reducing the operating voltage of all library cells by the worst-case supply-voltage drop during library characterization. The library cells are characterized at the worst-case supply variation (which is assumed to be around 10% - 15%) and static timing analysis is performed at this worst supply voltage. However, this approach may be extremely pessimistic since it assumes the occurrence of worst-case voltage drop at all the gates in the design at the same point of time. Also, the traditional approach ignores any supply-voltage shifts between adjacent gates. In this dissertation, we will present approaches for accurate estimation of supply noise induced circuit-delay variation.

## 1.4 Decoupling-capacitance modeling and allocation

Decoupling capacitance acts as local charge storage and is helpful in attenuating fast transients in supply drop. In this section, we discuss some of the traditional methods for modeling and optimization of on-die decoupling capacitance. The following three sources of capacitances affect the supply voltages in a power grid:

- (1) parasitic wire capacitances between power/ground wires, substrate, or signal nets,

- (2) parasitic capacitance of transistors, and

- (3) explicitly placed decoupling capacitors.

Parasitic wire capacitances can be extracted using either approximate formulae, which use the width and spacing between wires, or by using a commercial parasitic-extraction tool. A difficult issue is the analysis of the wire capacitances coupled to signal nets. The effect of these capacitors on the voltage in the power grid depends on the state of the signal net. For example, coupling from a power network to a signal net that is high, simply couples the power network to itself, with little or no effect on the voltage drop. Unfortunately, due to prohibitively large number of signal nets in a design, it is infeasible to model the signal nets and power grid simultaneously [13]. Therefore, a statistical approach for modeling of the coupling capacitance between the power grids and signal nets has been proposed in [13].

The switching activity of signals is determined by calculating the average number of signal nets that switch in a clock cycle. If the low-to-high and high-to-low switching probabilities of a signal are equal, their effects cancel each other out and therefore, switching nets can be ignored in the analysis. Of the remaining (non-switching) nets, half may be considered to be in stable high state and half in stable low state. Each coupling capacitance is replaced by an effective capacitance to ground, in series with a resistor. The effective value of the coupling capacitor [68] is

$$C_{eff} = \frac{1}{2}C_{coupling}(1 - P_{active})$$

(EQ 1.3)

where  $P_{active}$  is the average switching activity.

Device capacitances attenuate the voltage drop in the power grid and have a larger effect on the voltage in the power grid as they are much larger than the wire capacitances. The effect of device capacitances also depends on the state of the signal. This is explained with the help of an inverter chain in Figure 1.3, where we compute the implicit decoupling capacitance of inverters INV2 and INV3 based on their input and output states. Each transistor has 5 device capacitances,  $C_{sb}(source\ to\ bulk)$ ,  $C_{db}(drain\ to\ bulk)$ ,  $C_{gs}(gate\ to\ source)$ ,  $C_{gs}(gate\ to\ drain)$  and  $C_{gb}(gate\ to\ bulk)$ . The  $C_{sb}$  can be ignored since the source and bulk for both the pmos and nmos are always at the same potential  $^1$ . Figure 1.3(a) shows the remaining 4 device capacitances for an inverter. In Figure 1.3(b), the capacitances are arranged across three inverters to make the analysis more convenient. Capacitances of switching devices contribute to the current drawn from the grid, which is already modeled by the time varying current source in the power-grid analysis. Therefore, in power-grid analysis, we need to consider the device capacitances of only those gates that do not switch.

We first look at the case where net N in Figure 1.3(a) is in a low state. The device capacitances shown in Figure 1.3(a) can be modeled by the equivalent RC circuit shown in Figure 1.3(b). The resistance  $R_p$  corresponds to the effective pull-up resistance of inverter 1, the resistance  $R_n$  corresponds to the effective pull-down resistance of inverter 2, and the resistance  $R_{wp}$  and  $R_{wn}$  correspond to the P and N well resistances, respectively. Since net N is low, capacitances  $C_{dbn}$ ,  $C_{gsn}$ , and  $C_{gbn}$  are discharged and do not contribute to the

1. This assumption is not valid in gates with series stacks of transistors.

Figure 1.3. Device-capacitance modeling in power-grid analysis [68]

decoupling between the power and ground grid. Furthermore, since  $R_{wp}$  is a relatively high resistance and since  $C_{dbp}$  and  $C_{gbp}$  are small, they can be ignored without a significant loss in the accuracy. An analogous analysis can be made for the decoupling capacitances when the state of signal N is high. This state is assumed to have equal probability of

being high or low when the gate is not switching, although a different ratio of high-to-low signal states could easily be incorporated in the analysis. An approximate model of the device capacitances for power-grid analysis is shown in Figure 1.3(c). The effective decoupling capacitance in this simplified model is the sum of the effective high and low decoupling capacitances weighted by the probability of the gate being in either state:

$$C_{eff} = (1 - P_{active})(C_{gdp} + C_{gdn}) + \frac{1}{2}((1 - P_{active})(C_{gsp} + C_{gsn}))$$

(EQ 1.4)

Similarly, the effective resistance is approximated by the sum of the high and low resistance of the gates:

$$R_{eff} = R_p + R_n \tag{EQ 1.5}$$

The intrinsic N-well capacitance is also modeled as a series RC whose time constant and capacitance per unit well area are characterized using a process simulator. The intrinsic as well as the explicit decoupling capacitances are distributed either according to the layout or, when a layout is not available (as during the early design stage), uniformly across the power rails.

The intrinsic decoupling capacitance is usually not enough to confine the voltage drop within safe bounds and designers have to add specific (explicit) decoupling-capacitance structures on the chip. Several methods [72][73][88] have been proposed for optimal explicit decoupling-capacitance allocation. These methods formulate the decoupling-capacitance allocation as an optimization problem with the objective of decoupling-capacitance area minimization and constraints on the worst voltage drop. However, in high-performance designs, circuit performance is a more pressing concern and the above approaches, although optimal for supply-noise reduction, may not be optimal for best circuit performance. For instance, in a logic block, only the delay of gates on the critical and

near-critical paths are of concern and the gates having larger timing slacks can afford relatively higher voltage drop. In this dissertation, we will present an approach for decoupling-capacitance minimization with the objective of optimizing the circuit performance.

## 1.5 Ringing in power supply networks

Intrinsic and extrinsic on-die decoupling capacitances interact with package inductance and may cause power supply resonance, where even small changes in the load-current can cause excessive supply-voltage fluctuations in the power distribution network. Also, the decoupling capacitances present at the other levels of the power distribution network (Figure 1.2) interact with parasitic inductances to form a multiple LC system with multiple resonance frequencies. In this section, we explain the transient response and various resonance frequencies of a power supply network. Figure 1.4 shows a simplified model with parasitics and decoupling capacitances at various levels of the power supply network. In this simplified model, all the on-chip decoupling capacitances have been lumped into a single capacitor  $C_{die}$  and all the switching devices have been modeled by a single timevarying current,  $I_{die}$ . The Ldi/dt drop occurring in the supply network can be classified as zeroth droop, first droop, second droop and third droop. The third droop occurs at the node between the voltage regulator module (VRM) and the motherboard and at the node between the motherboard and the microprocessor socket. The third droop is controlled by the motherboard inductance  $(L_{MB})$  and motherboard capacitors  $(C_{MB})$ . The second droop, which takes place at the node between the microprocessor's socket and the microprocessor's package, is controlled by the partial package inductance leading from the motherboard upto the package capacitors  $(L_{pkgl})$  and package capacitors  $(C_{pkg})$ . The first droop

occurs at the node between the microprocessor's package and the chip itself. The first droop is controlled by partial package inductance leading from the package capacitors to I/O pads ( $L_{pkg2}$ ) and on-chip decoupling capacitance ( $C_{die}$ ).  $L_{pkg2}$  also consists of the inductance of wire-bonds or C4 bumps. Lastly, a zeroth droop can occur on the die if there is significant amount of on-die inductance in the power grid. Figure 1.5 shows the first and the second droop in the transient response for a step load-current and the ac frequency response of the supply voltage. The third drop is very small in magnitude as well as frequency than the first and the second droops. The expression for the first droop (supply drop and ground bounce combined) due to a step load-current of peak amplitude  $I_{max}$  is given as follows:

$$\Delta V_{die}(t) \cong 2I_{max}R + I_{max}\sqrt{\frac{2L_{pkg2}}{C_{die}}} \cdot e^{-\frac{R}{2L_{pkg2}}t} Sin(\omega_r - \theta)$$

(EQ 1.6)

where,  $R = R_{pkg} + R_{MB} + R_{die}$ ;  $\omega_r$  is the resonance frequency of the first droop given by:

Figure 1.4. Simplified model of a power supply network

Figure 1.5. Transient and frequency response showing first and second droops

$$\omega_r = \frac{1}{\sqrt{L_{pkg2}C_{die}}}$$

(EQ 1.7)

and  $\theta$  is the phase difference given by,

$$\tan \theta = \frac{\sqrt{R^2 C_{die}^2 - 4L_{pkg2} C_{die}}}{RC_{die} - 2L_{pkg2}/R}$$

(EQ 1.8)

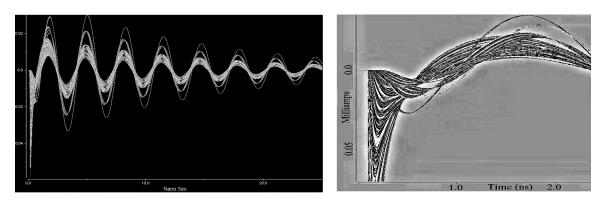

Any current excitation which is centered at the resonance frequency,  $\omega_r$  for a sufficient amount of time can create excessive voltage swings in the power grid as shown in Figure

Figure 1.6. Current excitation at resonance frequency (top) and voltage response (bottom) (source: Motorola)

1.6. Due to the presence of decoupling capacitance at multiple locations (die, package and motherboard), there are multiple resonance frequencies in the supply network: the  $L_{MB}$ - $C_{MB}$  combination causes a resonance at a few hundred kHz; the  $L_{pkg1}$ - $C_{pkg}$  combination causes a resonance at a few MHz; and the  $L_{pkg2}$ - $C_{die}$  causes a resonance of the order of a few hundred MHz. The goal of a power grid designer is to minimize package inductance  $(L_{pkg2})$ , allocate on-die decaps  $(C_{die})$  and sufficient C4s in the pads, so as to minimize the first droop and to create the largest possible gap between the highest resonance frequency and the operating frequency of the design. Care should also be taken to ensure that the operating frequency does not directly coincide with the higher harmonics of the resonance frequencies [11]. The advent of C4 flip-chip technology, which have much smaller inductance than that of bond-wires, and advances in package technology have led to a significant decrease in package inductance. The impact of package inductance on the first droop can be further reduced by placing the package decaps  $(C_{pkg})$  as close to the die as possible. Intelligent allocation and placement of explicit on-die decaps is also helpful in reducing the first droop as shown in [47][59][73][88]. Explicit decaps are, therefore, often added near regions with severe supply drops.

However, these explicit decaps result in area overhead and hence directly increase the cost of the chip. In addition, explicit decaps increase the leakage power consumption of the chip due to their gate-leakage current. With technology scaling, gate leakage has become a significant percentage of the overall leakage which places a significant limitation on the maximum amount of decap that can be introduced [9]. Several circuit techniques have, therefore, been proposed to actively regulate the on-die supply voltage. The next section provides an overview of some of the previously proposed active circuits.

# 1.6 Active supply-voltage regulation and supply-noise measurement

Active supply voltage regulation techniques employ circuits to enhance the amount of charge transfer to-and-from the power supply network during a supply-voltage fluctuation. The objective of these approaches is to reduce the supply drop for the same amount of explicit decoupling capacitance or to minimize decoupling-capacitance area for the same worst-case supply drop.

Active guard-ring circuits, based on the use of active decaps, were proposed in [51] and [82] to suppress substrate noise. In [77], a Miller-coupling based capacitance enhancement technique was proposed to reduce crosstalk between digital and analog regions on a die. A switched-capacitor based circuit technique with two decap banks switched between series and parallel configurations was proposed in [4]. The same switched capacitor was used for suppressing resonance in [36]. In [84], a band-pass filter is used to detect supply noise resonance and an artificial shunt load, connected between Vdd and Vss, is periodically switched on and off with 180° phase shift to dampen the resonance. In [56], a shunt high voltage supply is connected to the regular power grid when power-gated logic blocks wake up from the sleep state. A linear regulator with a specific goal to source or sink large transients of current was proposed in [83]. Recently, several adaptive frequency-management techniques [30][76] have also been proposed to compensate for supply transients. These techniques employ supply-drop monitors at various locations on the die and the frequency of operation is altered to compensate for fluctuations in the power supply. In [37], the use of controlled incremental frequency changes to alleviate inductive noise in dynamically voltage scaled microprocessors was explored. In addition to these, several microarchitectural control techniques such as selective issue, pipeline throttling and selective wake-up of clock-gated modules have been proposed in [34] and [41]. A major portion of this dissertation is devoted to exploring power efficient active circuit techniques for suppression of Ld*i*/d*t* drop and supply resonance.

Several circuits have been proposed to monitor the on-die supply noise. Circuits proposed in [31][42][54][55][74] constitute a sample-hold circuit to sample the supply voltage and a V-I converter circuit. The V-I converter circuit consists of a high-conductance transistor to convert the supply voltage samples into current. The current is then amplified using a current mirror and is transmitted out of the chip using a transmission line. Currentbased sensing is particularly attractive due to its robustness to coupling noise. However, the use of an analog V-I converter with high gain, followed by current amplifiers makes this technique power inefficient. An A-D converter has been proposed to convert the analog samples of supply noise into a digital code [89] which is then transmitted off-chip. This approach requires a lot of area, making it less effective for fine-grained supply noise measurement. [53] presents an analog circuit that reports whether power supply or ground voltage at the location of comparators within a microprocessor core crosses a pre-defined threshold voltage in every clock cycle. [2] and [39] use repetitive time-shifted sampling of on-chip supply noise. In this dissertation, we propose a low-power, all-digital on-chip oscilloscope for measuring supply noise and compare its performance with that of the V-I converter based supply drop monitor. The proposed on-chip oscilloscope can also be used for measuring coupling noise in critical signals and clock jitter.

# 1.7 Contributions of this work and organization

This dissertation focuses on developing algorithms and circuit techniques to analyze and suppress the supply noise related signal integrity issues. While we do not purport to present complete solutions to these problems, we aim to provide state-of-the-art CAD tools and active circuit techniques to estimate and combat supply noise in modern high-performance VLSI systems. Table 1.1 summarizes the key problems, the prior-proposed solutions and the solutions proposed in this dissertation. The first half of this dissertation presents CAD approaches for modeling, analysis and optimization of power supply net-

|   | Problem Statement                                                                                                                                | Prior Works                             | Proposed Solutions                                                                                         | Chapter            |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------|

| 1 | Analysis of supply noise induced circuit delay variation                                                                                         | [1][16][66]                             | Path-based and block-based approaches for accurate analysis of delay variation under IR and Ldi/dt drops   | Chapter II         |

| 2 | Early-mode power-grid analysis                                                                                                                   | [19][43][44][61]<br>[87]                | A constraint-based and a<br>statistical approach for<br>power-grid analysis in early<br>design phase       | Chapter III        |

| 3 | Timing-aware passive decoupling-capacitance allocation                                                                                           | [12][48][73][88]<br>[86]                | An exact optimization<br>approach and a heuristic-<br>based approach for timing-<br>aware decap allocation | Chapter IV         |

| 4 | Detailed study of the impact<br>of inductance, resonance<br>and locality in power distri-<br>bution network of an indus-<br>trial microprocessor | [15][27][52]                            | A detailed full-die dynamic<br>model of a 90nm Intel Pen-<br>tium®-class microproces-<br>sor design        | Chapter V          |

| 5 | Active circuit techniques for<br>the suppression of induc-<br>tive-supply-noise                                                                  | [4][36][37][51][56]<br>[76][77][82][83] | Analog and fully-digital circuit techniques for inductive-supply-noise suppression                         | Chapters<br>VI,VII |

| 6 | On-die supply-noise mea-<br>surement                                                                                                             | [2][31][39][42][53]<br>[54][55][74][89] | A power-efficient, fully-<br>digital on-chip oscilloscope<br>for on-die probing of high-<br>speed signals  | Chapter VII        |

Table 1.1. Summary of the key contributions

works. In the later half of the dissertation, we present circuit techniques for measurement and suppression of supply noise. The dissertation is organized as follows:

In Chapter II, we propose a path-based and a block-based analysis approach for computing the maximum circuit delay under power-supply fluctuations. The analyses are based on the use of superposition, both temporally and spatially across different circuit blocks. The approaches are vectorless and take both IR drop as well as Ldi/dt drop into account. The path-based approach computes the maximum possible delay of a given critical path in the presence of supply variations, while the block-based approach does not require apriori knowledge of the critical paths in a circuit and can be, therefore, effectively incorporated into an existing static timing analysis framework. The delay maximization problem is formulated as a non-linear optimization problem with constraints on currents of macros or circuit-blocks in the design. We show how correlations between currents of different circuit-blocks can be incorporated in the formulations using linear constraints. The proposed methods were validated on ISCAS85 benchmark circuits and an industrial power-supply grid, and demonstrate accurate worst-case circuit-delay computation.

In Chapter III, we propose two new approaches for analyzing the power-supply drop. The first approach conservatively computes the worst-case supply drop, early in the design flow when detailed information of the design is not available. The second approach computes the statistical parameters of supply-voltage fluctuations with variability in block currents. The proposed statistical analysis can be used to determine the portions of the grid that are most likely to fail. The analyses consider both IR drop and Ldi/dt drop in a power supply network and can take into account spatial and temporal correlations among block-currents. We show that the run-time is linear with the length of the current waveforms

allowing for extensive vectors, up to millions of cycles, to be analyzed. We implemented the approaches on a number of grids, including a grid from an industrial microprocessor to demonstrate their accuracy and efficiency.

In Chapter IV, we propose an approach for timing-aware decoupling-capacitance allocation which uses timing slacks to drive the optimization. Non-critical gates with larger timing slacks can tolerate a relatively higher supply-voltage drop as compared to the gates on the critical paths. The decoupling-capacitance allocation is formulated as a non-linear optimization problem using Lagrangian relaxation and a modified adjoint sensitivity method is used to obtain the sensitivities of objective function to decap sizes. A fast path-based heuristic is also implemented and compared with the global optimization formulation. The approaches have been implemented and tested on ISCAS85 benchmark circuits and grids of different sizes. Compared to uniformly allocated decaps, the proposed approach utilizes 35.5% less total decap to meet the same delay target. For the same total decap budget, the proposed approach is shown to improve the circuit delay by 10.1% on an average.

In Chapter V, we describe the first detailed full-die dynamic model of a 90nm Intel Pentium®-class microprocessor design, including package and non-uniform decap distribution. This model is justified from the ground up using a full-wave model and then increasingly larger but less detailed models with only the irrelevant elements removed. Using these models, we show that there is insignificant impact of on-die inductance in such a design, and that the package is critical to understanding the resonant properties of the grid. We also show that transient effects are sensitive to non-uniform decap distribu-

tion and that locality is a function of the excitation frequency and of the package-die resonance frequency.

In Chapter VI, we present an analog active decap circuit that significantly increases the effectiveness of decap in suppressing power supply fluctuations. The proposed circuit senses the supply drop and drives an amplified and inverted voltage fluctuation on the decap. The active decoupling circuit is powered by a separate power supply and we study the optimal allocation of the total C4s/pads between this second power supply and the regular supply, as well as the optimal allocation of the total decoupling capacitance between actively switched and traditional static decap. Finally, we demonstrate that the overhead of the proposed method is small compared to the area of the decaps. Simulations in a 0.13µm CMOS process demonstrate that the maximum supply drop is reduced by 45% compared to the use of only traditional decap, corresponding to an increase in the effective decap of approximately 8X.

In Chapter VII, we present three digital circuit techniques for inductive supply-noise suppression. The presented techniques effectively suppress supply noise caused by rapid current transients or due to resonance. The charge-injection-based active decoupling technique uses a nominal active supply and an active decap bank to inject extra charge into the power grid in case of an undershoot. This technique provides as effective decap of 10.5X (for a 10% supply regulation tolerance), does not require any high-voltage supplies and obviates the need for thick oxide (thick-ox) devices. Furthermore, the active decap acts as passive when the supply voltage is within the pre-specified safety bounds. The high-voltage charge pump based active circuit uses a high-voltage charge pump to dump extra charge into the power grid during excessive undershoots. The high-voltage shunt supply

based active circuit connects the regular nominal-supply power grid directly to an external high-voltage supply whenever an undershoot is detected, thus damping the transient response of the supply network. We also present a fully-digital on-chip oscilloscope which is more power efficient than a conventional supply drop monitor. All of the proposed circuits were implemented in a test-chip, fabricated in a 0.13μm, triple-well CMOS process. Measurement results demonstrate that the three active supply-noise suppression techniques suppress the inductive supply fluctuation by 57%, 33% and 43%, respectively for a step load-current. During resonance, the supply fluctuation is suppressed by 75%, 43% and 45%, respectively by the three proposed circuit techniques. The performance of the proposed active circuit techniques was validated with the V-I converter-based drop detector circuit, the proposed on-chip oscilloscope and by direct on-chip probing of Vdd and Vss metal lines.

In Chapter VIII, we summarize our contributions and discuss the future work.

## **CHAPTER II**

# VECTORLESS ANALYSIS OF SUPPLY-NOISE INDUCED DELAY VARIATION

#### 2.1 Introduction

Power supply networks are essential in providing the devices on a die with a reliable and constant operating voltage. Due to the resistance and inductance of the on-chip and package supply networks, the supply voltage delivered to various devices on a die is non-ideal and exhibits both spatial and temporal fluctuations. In today's high-end designs, it is not uncommon for the supply network to conduct hundreds of Amperes of total current [75]. As semiconductor technology is scaled down and the supply voltage is reduced, the total current that must be supplied by the power network is expected to increase even further, making it more difficult to meet stringent supply-integrity constraints. In particular, the Ldi/dt voltage drop is expected to become more prominent as it increases with both increasing current demand and higher clock frequency [69]. Furthermore, IR drop and Ldi/dt drop interact in a non-trivial manner and total maximum drop is not always the sum of the two individual maximum voltage drops. With decreasing supply voltages, the gate delay is becoming increasingly sensitive to supply-voltage variation as the difference between the supply voltage and the threshold voltage is consistently reduced. With ever

diminishing clock-cycle times, accurate analysis of the impact of supply voltage on circuit performance has, therefore, become a critical issue.

Power supply variation can impact the circuit delay in two ways: First, a reduced supply voltage lessens the gate drive strength, thereby increasing the gate delay. Second, a difference in the supply voltage between a driver/receiver pair creates an offset in the voltage with which the driver/receiver gates reference the signal transition. This has the effect of creating either a positive or negative time shift in perceived signal transition at the receiver gate. This dual nature of the impact of supply voltage on circuit delay was observed in [16], and complicates the generation of simulation vectors that maximize the delay along a particular circuit path. Increasing the voltage drop at a particular location may worsen the delay of one gate while improving the delay of another. Therefore, a vector must be determined that results in an optimal combination of these often conflicting goals of introducing both reduced drive strengths and supply voltage shifts such that overall circuit delay is maximized.

Traditionally, the impact of supply noise on delay has been accounted for by reducing the operating voltage of all library cells by the worst-case supply-voltage drop during library characterization. This assumes that the expected worst-case voltage drop occurs at all places in the design. This yields a very conservative analysis since, in practice, the worst drop is localized to a small region at any one point in time. On the other hand, this approach ignores the impact of voltage shifts between driver/receiver pairs, thereby possibly underestimating the worst-case delay in certain situations.

In this chapter, we present two approaches for analyzing the impact of supply variations on circuit delay. The proposed approaches are vector-less, allowing for efficient analysis,

and address both IR drop and Ldi/dt drop effects. The first approach is a path-based approach which computes the maximum possible delay of a path in the circuit in presence of supply variation. The second approach is a block-based method which does not require apriori knowledge and enumeration of the critical paths in a circuit. The proposed approaches use a quadratic gate-delay model. We formulate the task of determining the worst-case impact of supply noise on delay using a constrained non-linear optimization problem where the currents of the different logic-blocks are the optimization variables. Linear constraints on block-currents are then formulated for the total power consumption of the chip and for individual block-currents. Constraints between currents of different blocks or a single block in consecutive clock cycles can be incorporated to account for any spatial or temporal correlations that exist between circuit blocks. The proposed approaches have the advantage that accurate constraints can be extracted from extensive gate level simulation data that is readily available during the design process, thereby significantly improving the accuracy of the analysis while avoiding the need for lengthy and time-consuming power grid simulation. The proposed methods were validated on ISCAS85 benchmark circuits, including a power grid from an industrial processor design, and demonstrate a significant reduction in pessimism during worst-case circuit-delay computation.

The remainder of this chapter is arranged as follows. Section 2.2 describes the gatedelay model for delay variations with respect to supply-voltage fluctuations. Section 2.3 presents the voltage-drop sensitivity computation while Section 2.4 presents the constraints on block-currents and a method to incorporate current correlations. Section 2.5 and Section 2.6 present the path-based and the block-based formulations respectively for maximizing the impact of supply-voltage fluctuations on delay. Section 2.7 presents the experimental validation of the proposed approaches and conclusions are presented in Section 2.8.

## 2.2 Delay model for supply fluctuations

In this section, we model the impact of supply-voltage variations on delay. Since the supply-voltage variations in a power grid are typically very slow compared to the transition time of a switching gate [11], we can make the simplifying assumption that the supply voltages are constant during a switching transition. From the perspective of the circuit delay, we are therefore concerned with the impact of fixed voltage offsets from the nominal *Vdd* and *Vss* voltages on the delay of a circuit. Note however that *dynamic* IR drop and Ld*i*/d*t* drop effects will be the cause of these voltage offsets.

A voltage drop at a power-supply point can impact the delay of a gate through one of the following two mechanisms:

1. A decrease in the *Vdd* voltage or an increase in the *Vss* voltage at the gate under consideration decreases the *locally* observed supply voltage of the gate and will reduce its drive strength and hence increase its delay. The worst-case voltage drop is typically localized to a small region in the chip. Hence, only a few gates in a path will typically be operated with a worst-case drive strength. Gates with higher local supply voltage therefore compensate for the increased delay of gates with reduced local supply voltage in the path, and a global analysis of the impact of supply voltage on the path delay is therefore required.

2. A relative shift in the *Vdd* or *Vss* voltages between the driver and receiver gates of a signal net can introduce a voltage offset that will impact the delay of a gate. This is illustrated in Figure 2.1 where the *Vss* voltage of the receiver gate is increased relative to the *Vss* voltage of the driver gate. Since the input signal has a rising transition, the NMOS transistor of the receiver gate senses the input voltage relative to the local *Vss* voltage level. The shown voltage shift therefore results in an effective (negative) noise voltage at the receiver gate input that increases the delay of the receiver gate. Note that a shift in the supply voltage impacts the rising and falling transitions of a gate in opposite ways, meaning that an increase in the *Vss* voltage from driver to receiver results in an increased delay for a rising input transition while an increase in the *Vdd* voltage improves the delay for a falling input transition.

The relative shift in supply voltage between the driver and receiver gates is likely to be larger if the gates are farther apart. Therefore, nets that transmit signals across the chip will have a higher likelihood of shifts in supply voltage between their driver and receiver pair and hence are more susceptible to power grid noise. The relative magnitude of the

Figure 2.1. A driver-receiver pair in a non-ideal supply network

above two mechanisms depends on the input slope and output loading of a gate. The sensitivity of gate delay to driver-strength reduction will increase with output loading, while the sensitivity to voltage shifts will increase with slower input signal-transition times.

In order to maximize the delay of a path, it is necessary to induce voltage drops in the supply network such that the delay of each gate is increased through both mechanisms: reduction of driver strength and voltage shifts between successive gates in the path. A possible voltage assignment that maximizes the voltage shift between consecutive gates in a circuit path is shown in Figure 2.2. However, this assignment does not reduce the drive strength of each gate by the maximum possible amount. Furthermore, this assignment may not be feasible for grids where Vdd-drop and Vss-bounce are tightly correlated with each other. Maximizing the delay through reduced drive strength and through voltage shifts therefore, requires conflicting voltage assignments that cannot be realized simultaneously.

Figure 2.2. A path in a power supply network with worst-case voltage shifts causing the maximum path delay

A worst-case *realizable* voltage assignment that maximizes the overall path delay will depend on the specific conditions of the gates and their sensitivities to the different voltage-drop phenomena.

We now present our model for the dependence of the delay of a single gate on the voltage drops at that gate and at its preceding gate. We consider the delay of a gate G, shown in Figure 2.3(a), with local supply voltages  $Vdd_g$  and  $Vss_g$  and supply voltages  $Vdd_{in}$ ,  $Vss_{in}$  at the preceding driver gate. As shown in Figure 2.3(b), the propagation delay  $\tau$  between the input and output transitions of a gate is measured at 1/2 the *nominal* supply voltage point to ensure a common reference between successive gates. The delay of the receiver gate depends on the  $Vdd_g$  and  $Vss_g$  voltages at the receiver gate itself, the voltages  $Vdd_{in}$ ,  $Vss_{in}$  at the preceding driver gate, the input transition time and the output load. To provide a

Figure 2.3. A driver-receiver pair in a non-ideal supply network (a), propagation delay (b) and output transition time (c)

common reference for transition time, we again define the transition time tr of a signal as the time between the 10% to 90% crossing of *nominal* supply voltage for an equivalent full-swing transition, as shown in Figure 2.3(c). Given the signal transition at the output of gate G, and given the *local* transition time tr, measured between 10% to 90% of the local supplies  $V_{ss,g}$  to  $V_{dd,g}$ , the equivalent full-swing transition time tr is computed as follows:

$$tr = tr' \cdot \frac{Vdd_{nominal}}{Vdd_g - Vss_g}$$

(EQ 2.1)

For a given input transition time and output slope, the delay and transition time at the output of gate G are expressed as follows:

$$\tau = f(Vdd_o, Vss_o, Vdd_{in}, Vss_{in})$$

(EQ 2.2)

$$tr_{out} = g(Vdd_g, Vss_g, Vdd_{in}, Vss_{in})$$

(EQ 2.3)

where,  $\tau$  and tr are the propagation delay and output transition time of gate G.

In general, f and g are non-linear functions of their variables. However, the voltage drop in a power grid network is restricted and is typically within the range of  $\pm 10\%$  of the *nominal* supply voltage. It was observed in [1] that within this range, the delay of a gate is close to a second degree polynomial. Figure 2.4 shows the rise and fall delays of an inverter in  $0.13\mu$  technology as  $Vdd_g$ ,  $Vss_g$ ,  $Vdd_{in}$  and  $Vss_{in}$  vary by  $\pm 20\%$ . The delay curves in Figure 2.4 show that functions, f and g can be accurately modeled as second degree polynomials for reasonable supply voltage variations. We therefore express the delay,  $\tau$ , and output transition time, tr of a gate as follows: