# THE FAST, EFFICIENT, AND REPRESENTATIVE BENCHMARKING OF FUTURE MICROARCHITECTURES

by Jeffrey Stuart Ringenberg

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in The University of Michigan 2008

# Doctoral Committee:

Professor Trevor N. Mudge, Chair Associate Professor Steven K. Reinhardt Associate Professor Dennis M. Sylvester Assistant Professor Scott Mahlke

To Bridgette For understanding.

# **ACKNOWLEDGEMENTS**

My path to graduation took many different routes, some longer than others, and I owe much of my success to several, very important people.

My advisor, Trevor Mudge, started my journey in 1995 by granting me a summer undergraduate research position working with one of his graduate students, Nomik Eden. From our first Friday meetings at Ashley's to future lunches at Casey's, I enjoyed the freedom, flexibility, and guidance that I was given to pursue both my research and my teaching interests. Although I may have stayed around longer than usual, I would never have learned or discovered all that I have about my career, and myself, if not for the time that I was given. I will forever be indebted to them both for getting me started and to Trevor, especially, for all that he has done in keeping me on the path.

Another person of equal importance, David Oehmke, provided me with an incredible amount of assistance and guidance. How he managed to graduate so much earlier than I, I cannot fully comprehend. This may be due, quite possibly, to his wonderful wife, Cathy, and a desire to return to the real world. In the years that we worked together, he provided me with an incredible amount of insight and, more importantly, friendship. I, too, will always remember our culinary tour of San Diego. He is responsible for the original idea behind this dissertation and if it were not for this, you would soon be reading a completely different dissertation.

I would also like to thank my committee: Scott Mahlke, Steve Reinhardt, and

Dennis Sylvester. Their guidance following my thesis proposal helped me to focus my research and their comments refined my work.

Quite a few graduate students were pivotal in the successful completion of my work. Thanks to Ali Saidi, Geoff Blake, and Ron Dreslinski for providing me with several "eleventh hour" insights and suggestions that greatly impacted the usefulness of my research. In addition, thanks to Chris Pelosi for helping me create some of the tools that were used early in my work.

Several other people in the CSE department are deserving of my thanks. Denise DuPrie, Dawn Freysinger, Karen Liska, Stephen Reger, and Bert Wachsman all provided me with the inside information necessary to navigate the CSE, EECS, and Rackham buildings and bureaucracy. Were it not for them, I would still be figuring where to apply for positions, how to fill out the right information, and who I can talk to in order to stay employed and/or enrolled.

In addition to those people who helped with my research, there are many people I would like to thank in conjunction with my teaching at the University of Michigan. The first is my original inspiration, Elliot Soloway. His EECS Senior Design Projects course was a joy to behold and I was honored to be his Graduate Student Instructor for two years. I also whole-heartedly thank Dave Chesney for his guidance in teaching me how to handle a more traditional course and for introducing me to pedagogical research. I learned a great deal as his GSI in his software engineering course and I will always remember our dinner and conversation in Hawaii. Thanks also to Susan Montgomery for teaching her course on engineering education and for giving me a formalized introduction to the area. She was an excellent instructor and helped me to crystallize my decision to continue in teaching. Finally, I owe a great deal of gratitude to James Holloway and Toby Teory for continuing to give me the opportunity to teach

at the University. They have allowed me to pursue my true passion and this is a gift that I will forever cherish.

I also must thank my family and friends for always trusting that I made the right decision and never asking "So when are you going to graduate?" more than was absolutely necessary. To my parents, Joe and Diane Ringenberg, thank you for giving me the opportunity to start this whole journey back in 1996 and for always being interested and supportive of everything that I have done. Even though you never really understood what I was talking about, at least you listened. To my sister, Marta Ringenberg, thanks for the great conversations and for being who you are. Also, thanks for going into teaching. Maybe some day I will get one of your students in my class. To my friends, Pete Driver and Chris Rowland, thanks for the great lunches at Qdoba and for keeping the laughing to a minimum when I was still able to legally order the student drink. While I enjoyed sitting idly by, seeing Chris make the big bucks and Pete fly the friendly skies, I finally realized that I needed to join the World of Work too.

Finally, thank you to my partner, wife, and altogether better half, Bridgette Carr. She has supported me in more ways than I can describe and I will be forever indebted to her. From our first encounter on the sand courts of Slauson Middle School, her understanding nature, spirited conversation, and constant "encouragement" has provided me with a new perspective on life that reaches far outside the lab. We have literally traveled the world together and I don't ever plan to stop. I only hope that she is ready to continue that ride with me. Something tells me that she is...

# TABLE OF CONTENTS

| DEDICATIO   | N                                           | 11         |

|-------------|---------------------------------------------|------------|

| ACKNOWLE    | EDGEMENTS                                   | iii        |

| LIST OF FIG | GURES                                       | ix         |

| LIST OF TA  | BLES                                        | xi         |

| CHAPTER     |                                             |            |

| I. Intro    | duction                                     | 1          |

| 1.1         | Motivation                                  | ]          |

| 1.2         | Thesis Overview                             | 2          |

| 1.3         | Thesis Organization                         | 4          |

| II. Back    | ground                                      | 6          |

| 2.1         | Overview                                    | $\epsilon$ |

| 2.2         | Benchmark Suite Reduction                   | 8          |

|             | 2.2.1 Dataset Reduction                     | 8          |

|             | 2.2.2 Benchmark Subsetting                  | 8          |

| 2.3         | Statistical Simulation                      | 10         |

|             | 2.3.1 Trace-Based Simulation                | 11         |

|             | 2.3.2 Testcase Program Synthesis            | 13         |

| 2.4         | Instruction Sampling                        | 14         |

| 2.1         | 2.4.1 SMARTS                                | 15         |

|             | 2.4.2 SimPoint                              | 16         |

|             | 2.4.3 Improving Sampled Simulation          | 19         |

| 2.5         | Techniques for Checkpointing and Warmup     | 20         |

| 2.0         | 2.5.1 Direct Execution Checkpointing        | 21         |

|             | 2.5.2 Simulator-Derived Checkpointing       | 23         |

|             | 2.5.3 Reuse Latency Warmup                  | 24         |

| 2.6         | Summary                                     | 25         |

| III. Intrin | nsic Checkpointing with Binary Modification | 27         |

| 9.1         |                                             | 0.5        |

| 3.1         | Overview                                    | 27         |

| 3.2         | Register Checkpointing                      | 29         |

| 3.3         | Memory Checkpointing                        | 29         |

| 3.4         | System Call Checkpointing                   | 30         |

| 3.5         | Interval Execution                          | 30         |

| 3.6         | Exit Handling                               | 31         |

| 3.7         | Implementation Issues                       | 32         |

|              | 3.8    | Validation                                                    |

|--------------|--------|---------------------------------------------------------------|

|              | 3.9    | Alpha Example                                                 |

|              | 3.10   | Summary                                                       |

| IV.          | Intrin | sically Checkpointed Assembly Code                            |

|              | 4.1    | Overview                                                      |

|              | 4.2    | Simulation Interval Selection                                 |

|              | 4.3    | ITCY Code Generation                                          |

|              | 4.0    | 4.3.1 Overview                                                |

|              |        | 4.3.2 Initial State Intrinsic Checkpointing                   |

|              |        | 1 0                                                           |

|              |        | 4.3.3 Ensuring Valid Memory Accesses                          |

|              |        | 4.3.4 Preserving Dynamic Instruction Stream Execution Order 4 |

|              |        | 4.3.5 Preserving Cache Access Patterns                        |

|              |        | 4.3.6 Exit Handling                                           |

|              | 4.4    | 4.3.7 System Call Emulation                                   |

|              | 4.4    | ITCY Code Compilation                                         |

|              | 4.5    | ITCY Code Execution                                           |

|              | 4.6    | Validation                                                    |

|              | 4.7    | Additional Features                                           |

|              |        | 4.7.1 Intrinsic Warmup                                        |

|              |        | 4.7.2 Multi-suite Benchmarks 60                               |

|              |        | 4.7.3 Fine-grained Statistics Control 60                      |

|              | 4.8    | Summary                                                       |

| v.           | Exper  | imental Framework                                             |

|              | 5.1    | Target Architecture                                           |

|              | 5.2    | Code Compilation                                              |

|              | 5.3    | Benchmarks Used                                               |

|              | 5.4    | SimPoint Intervals                                            |

|              | 0.1    |                                                               |

| VI.          | Resul  | ts and Analysis                                               |

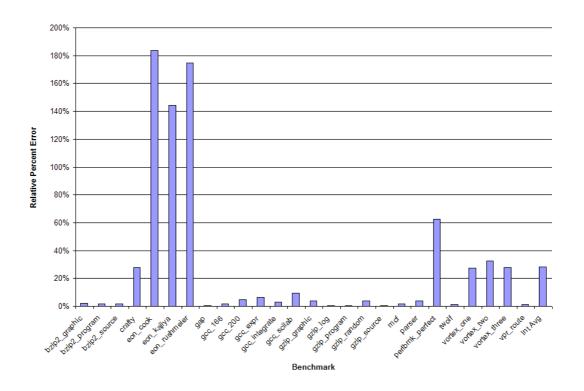

|              | 6.1    | Intrinsic Checkpointing with Binary Modification              |

|              |        | 6.1.1 Code Overhead                                           |

|              |        | 6.1.2 Performance Modeling                                    |

|              |        | 6.1.3 Effects on File Size                                    |

|              |        | 6.1.4 Simulation Speedup                                      |

|              | 6.2    | Intrinsically Checkpointed Assembly Code                      |

|              |        | 6.2.1 Code Overhead                                           |

|              |        | 6.2.2 Required Pre-Interval Instructions                      |

|              |        | 6.2.3 Required Intra-Interval Instructions                    |

|              |        | 6.2.4 Cache Performance Modeling                              |

|              |        | 6.2.5 Branch Prediction Performance Modeling 97               |

|              |        | 6.2.6 CPI and IPC Performance Modeling                        |

|              |        | 6.2.7 Tracking Design Changes                                 |

|              |        | 6.2.8 Effects on File Size                                    |

|              |        | 6.2.9 Simulation Speedup                                      |

|              | 6.3    | Discussion                                                    |

| 7 <b>T</b> T | Ca1    | usion 111                                                     |

| V 11.        | Concl  | usion                                                         |

|              | 7 1    | Thoras Summary 111                                            |

| 7.2       | Future Directions |  |  |  |  |  |  |  |  |  |  |  |  |  | 116 |

|-----------|-------------------|--|--|--|--|--|--|--|--|--|--|--|--|--|-----|

| BIBLIOGRA | PHY               |  |  |  |  |  |  |  |  |  |  |  |  |  | 119 |

# LIST OF FIGURES

| Fi | gure |                                                                                  |    |

|----|------|----------------------------------------------------------------------------------|----|

|    | 2.1  | Summary of Simulation Time Reduction Techniques                                  | 7  |

|    | 2.2  | Sampleing Intervals for SMARTS                                                   | 16 |

|    | 3.1  | ICBM Process Flow Diagram                                                        | 27 |

|    | 3.2  | ICBM Interval Selection and Creation                                             | 28 |

|    | 3.3  | Pseudo-Assembly Template for ICBM code                                           | 32 |

|    | 3.4  | Anatomy of an ICBM Binary                                                        | 33 |

|    | 3.5  | Pseudo-Assembly for Pre-Interval Syscall Checkpointing                           | 36 |

|    | 3.6  | Pseudo-Assembly for Register and Memory Restoration                              | 36 |

|    | 3.7  | Converting Pseudo-Assembly to Alpha Machine Instructions                         | 38 |

|    | 4.1  | ITCY Code Generation Diagram                                                     | 39 |

|    | 4.2  | ITCY Interval Selection and the Creation of a SuiteSpot or SuiteSpecks           | 41 |

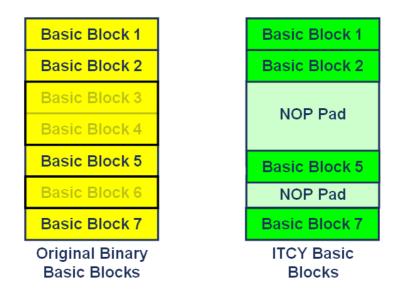

|    | 4.3  | Original and New Binary Memory Layouts                                           | 45 |

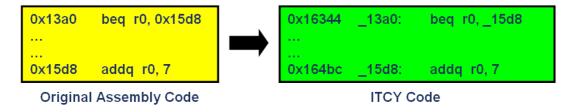

|    | 4.4  | Retargeting Direct Branches to Maintain Proper Execution Order                   | 45 |

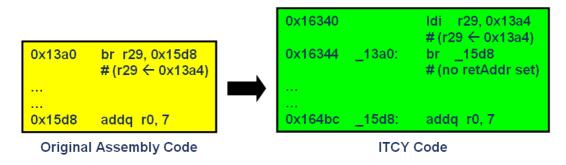

|    | 4.5  | Explicitly Setting a Branch's Old Return Address Register                        | 46 |

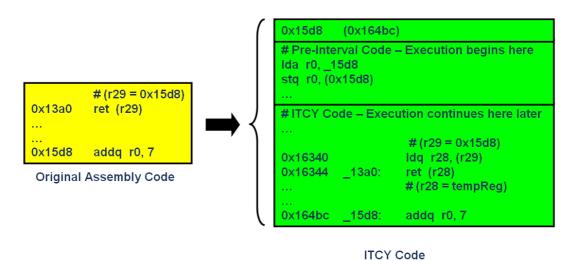

|    | 4.6  | Using the Original Memory Location of an Indirect Branch to Store its New Target | 47 |

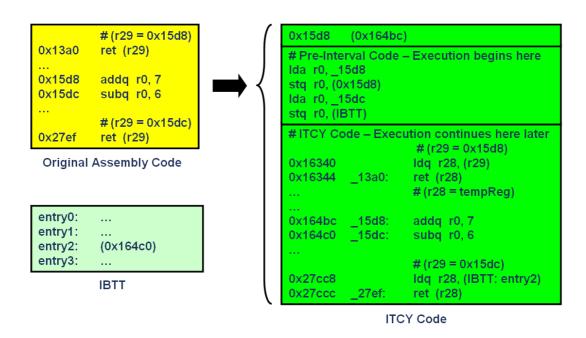

|    | 4.7  | Using the IBTT to Handle Special Indirect Branch Targets                         | 49 |

|    | 4.8  | Using Instruction Pads to Recreate the Original Interval's Memory Footprint $$   | 50 |

|    | 4.9  | Special Exit Handling Control Code                                               | 53 |

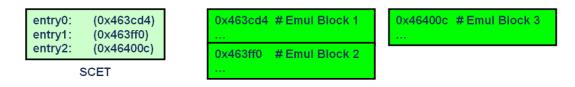

|    | 4.10 | Using the SCET to Store the Starting Addresses of System Call Emulation Blocks   | 54 |

|    | 4.11 | System Call Emulation Code Sample                                                | 55 |

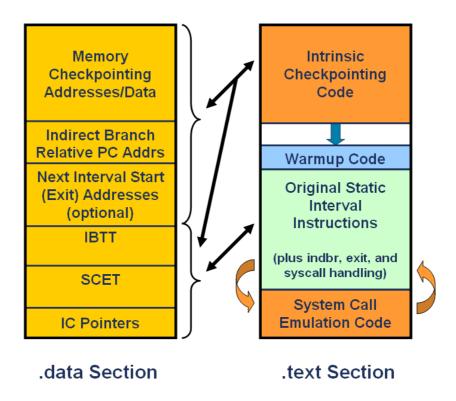

|    | 4.12 | Anatomy of an ITCY Binary                                                        | 56 |

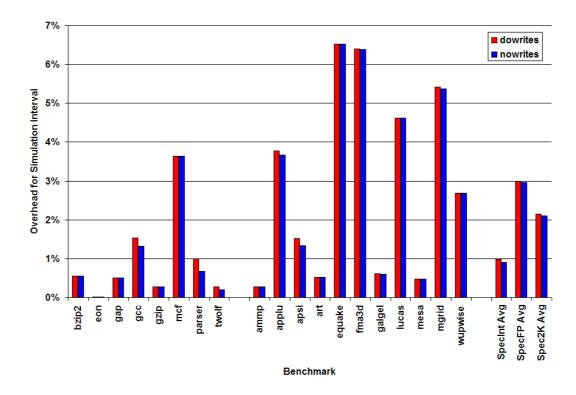

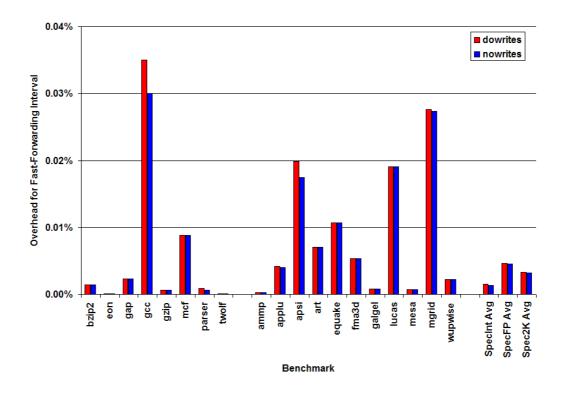

| 6.1  | Overhead of ICBM Checkpointing Code Compared to Simulation Interval                       | 69  |

|------|-------------------------------------------------------------------------------------------|-----|

| 6.2  | Overhead of ICBM Checkpointing Code Compared to Fast-Forward Interval                     | 70  |

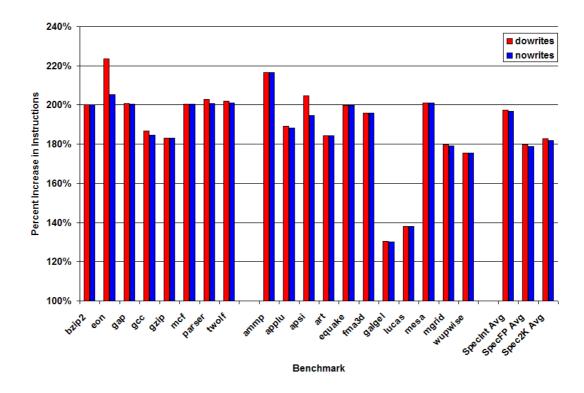

| 6.3  | Increase in Number of Instructions when Converting to Alpha Code $\ \ldots \ \ldots$      | 71  |

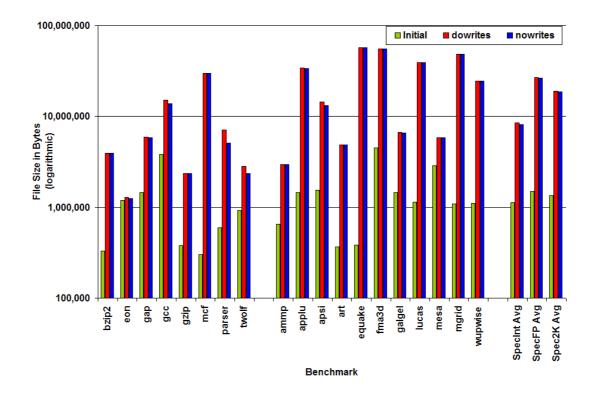

| 6.4  | Increase in ICBM File Size (measured in bytes) Overall                                    | 72  |

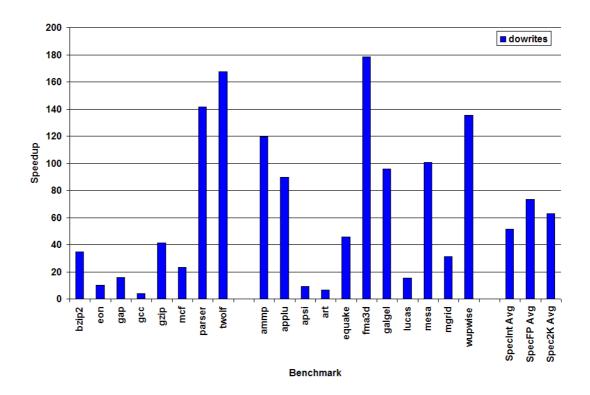

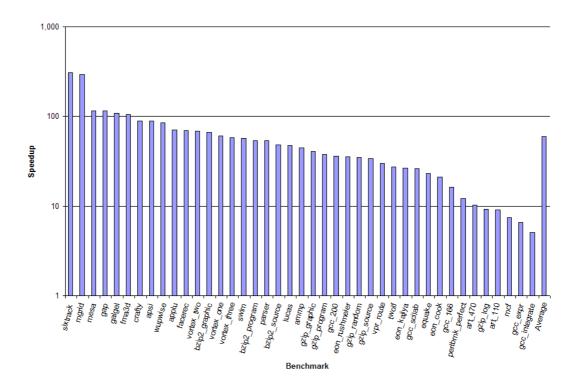

| 6.5  | Speedup of ICBM Code over Initial Benchmark                                               | 73  |

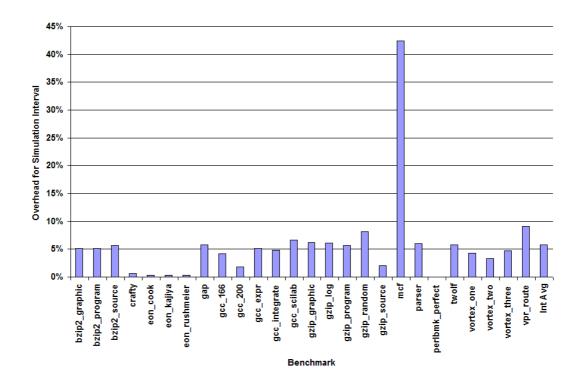

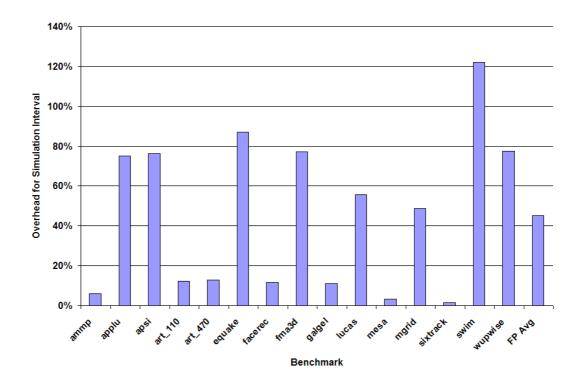

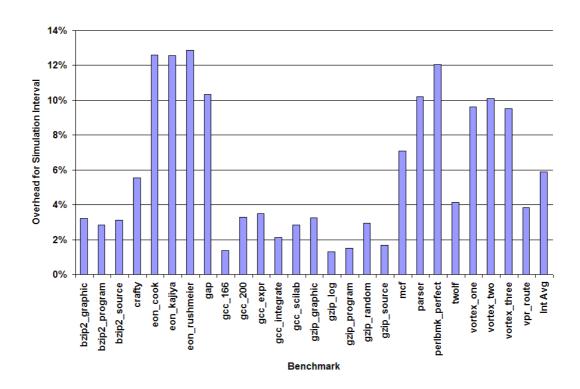

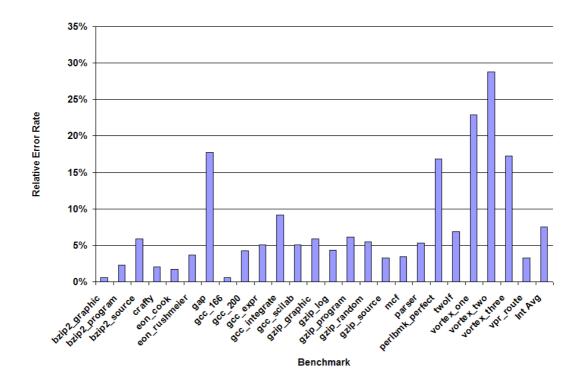

| 6.6  | Overhead of ITCY Pre-Interval Code Compared to Simulation Interval: INT $$                | 78  |

| 6.7  | Overhead of ITCY Pre-Interval Code Compared to Simulation Interval: FP $$                 | 79  |

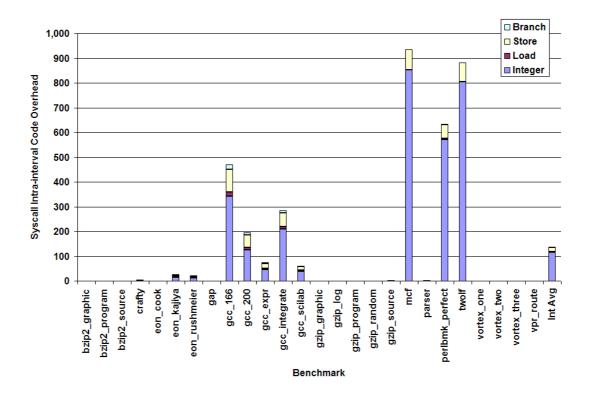

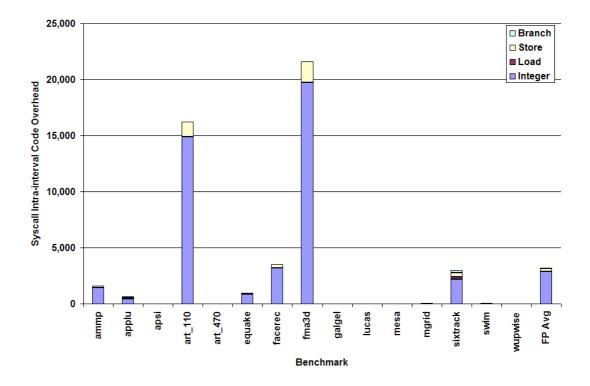

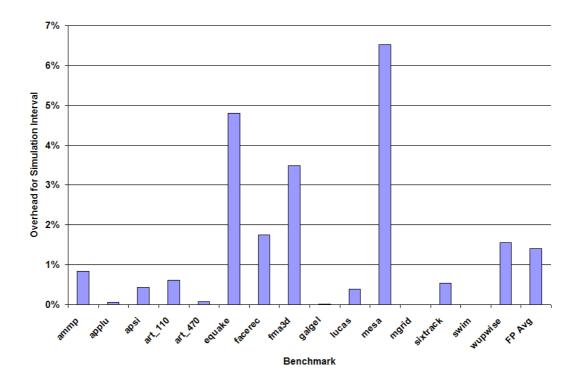

| 6.8  | Overhead of ITCY Intra-Interval Syscall Emulation Code: INT benchmarks                    | 85  |

| 6.9  | Overhead of ITCY Intra-Interval Syscall Emulation Code: FP benchmarks                     | 85  |

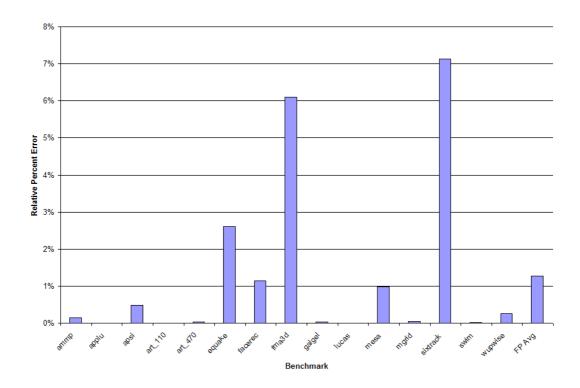

| 6.10 | Overhead of ITCY Intra-Interval Code Compared to Simulation Interval: INT                 | 87  |

| 6.11 | Overhead of ITCY Intra-Interval Code Compared to Simulation Interval: FP $$               | 88  |

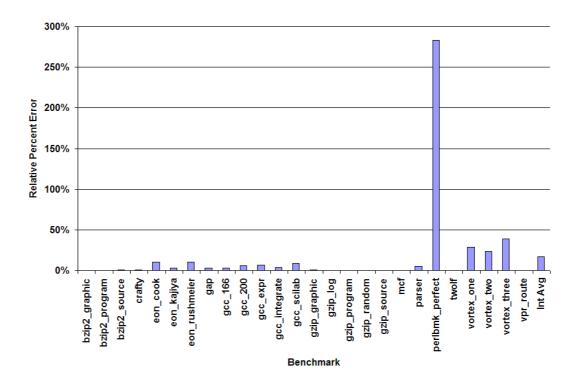

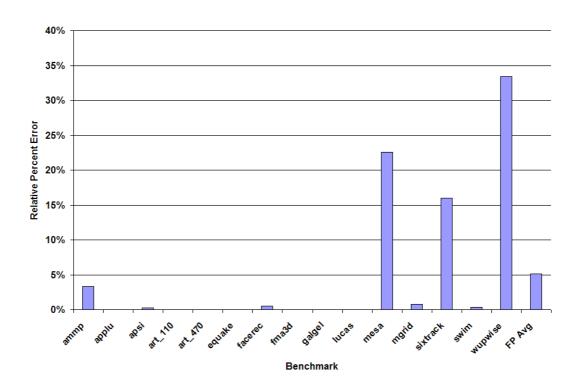

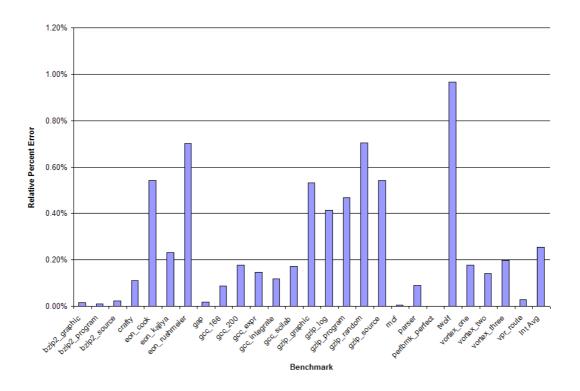

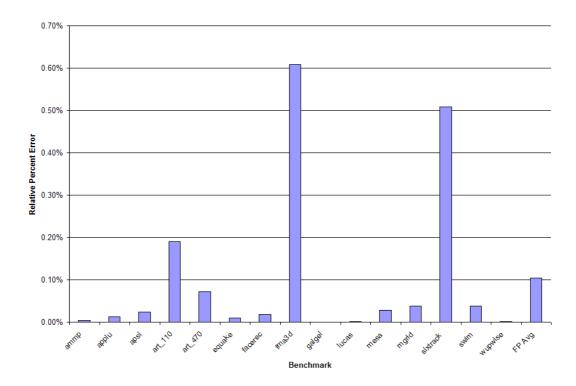

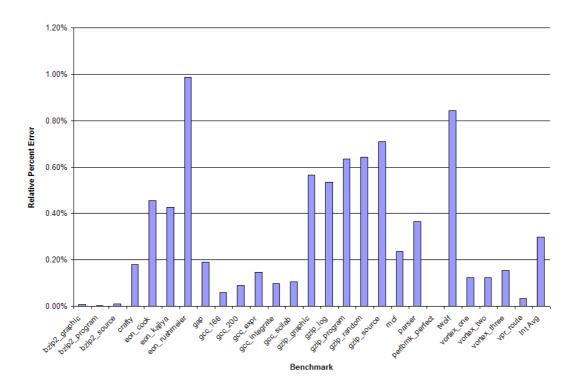

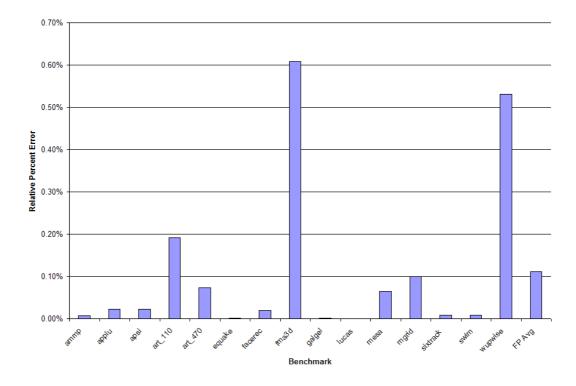

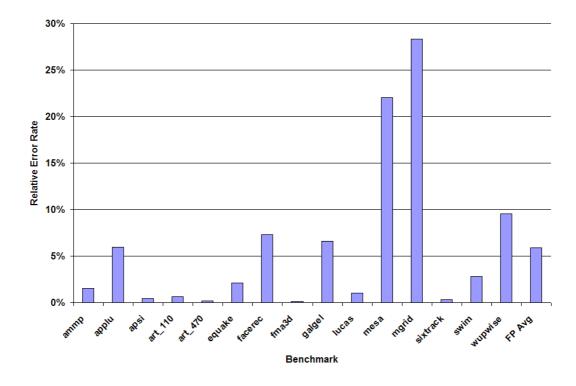

| 6.12 | L1 D-Cache Miss Rate of ITCY Code - Integer Benchmarks                                    | 94  |

| 6.13 | L1 D-Cache Miss Rate of ITCY Code - Floating Point Benchmarks                             | 94  |

| 6.14 | L2 Cache Miss Rate of ITCY Code - Integer Benchmarks                                      | 96  |

| 6.15 | L2 Cache Miss Rate of ITCY Code - Floating Point Benchmarks                               | 96  |

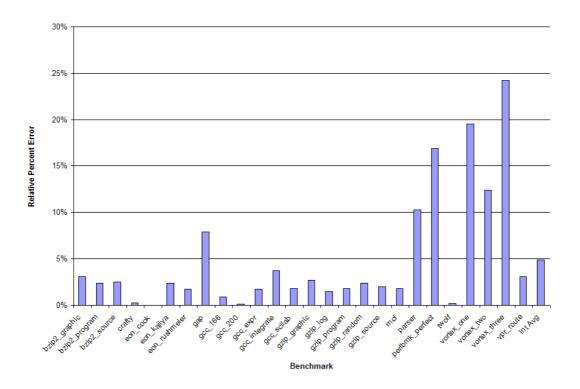

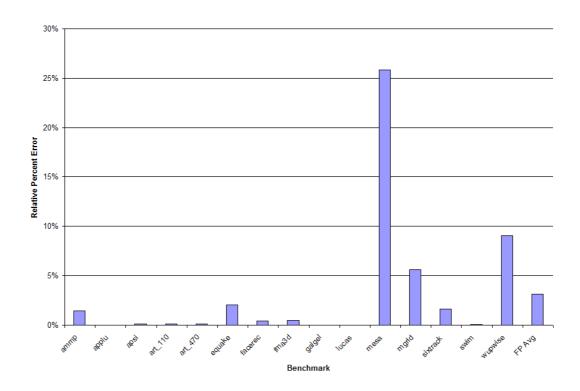

| 6.16 | Branch Direction Prediction Rate of ITCY Code - Integer Benchmarks                        | 98  |

| 6.17 | Branch Direction Prediction Rate of ITCY Code - Floating Point Benchmarks                 | 98  |

| 6.18 | Branch Address Prediction Rate of ITCY Code - Integer Benchmarks                          | 99  |

| 6.19 | Branch Address Prediction Rate of ITCY Code - Floating Point Benchmarks $$                | 99  |

| 6.20 | CPI of ITCY Code - Integer Benchmarks                                                     | 101 |

| 6.21 | CPI of ITCY Code - Floating Point Benchmarks                                              | 101 |

| 6.22 | IPC of ITCY Code Compared to Detailed Simulation - Integer Benchmarks $\ \ldots \ \ldots$ | 103 |

| 6.23 | IPC of ITCY Code Compared to Detailed Simulation - Floating Point Benchmarks              | 103 |

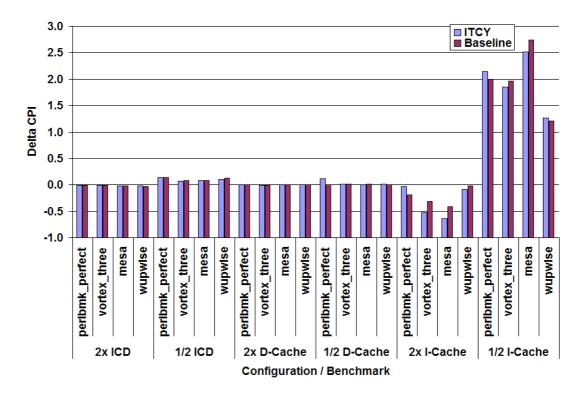

| 6.24 | Tracking Design Changes using Delta CPI - ITCY versus Baseline                            | 105 |

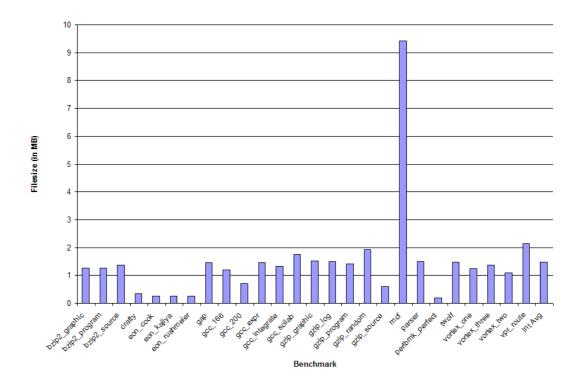

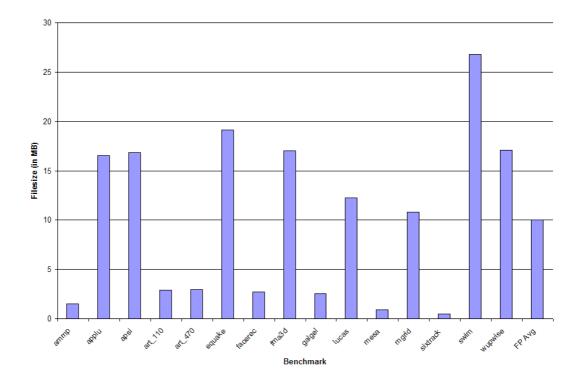

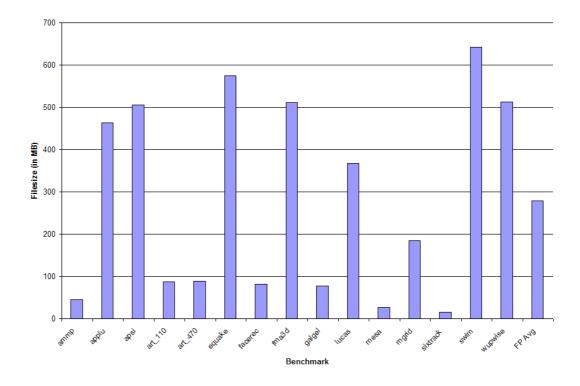

| 6.25 | File Size of ITCY Code (per Interval Average) - Integer Benchmarks                        | 107 |

| 6.26 | File Size of ITCY Code (per Interval Average) - Floating Point Benchmarks                 | 107 |

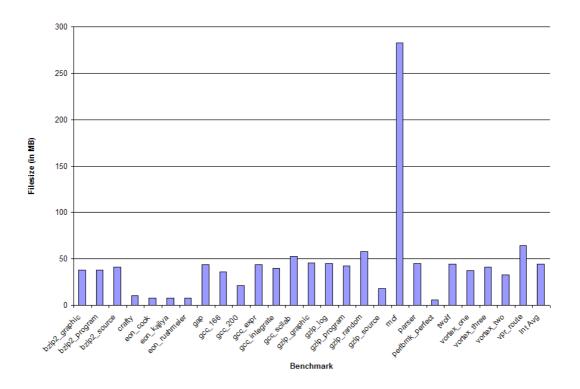

| 6.27 | File Size of ITCV Code (all Intervals Totaled) - Integer Banchmarks                       | 108 |

| 6.28 | File Size of ITCY Code (all Intervals Totaled) - Floating Point Benchmarks | 108 |

|------|----------------------------------------------------------------------------|-----|

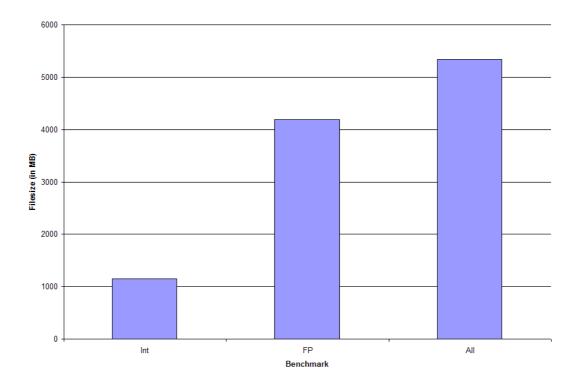

| 6.29 | File Size of ITCY Code - All Benchmarks Totaled                            | 109 |

| 6.30 | Speedup of ITCY Code Executed Serially                                     | 111 |

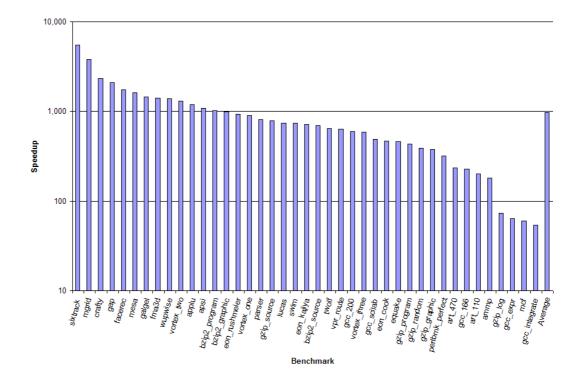

| 3.31 | Speedup of ITCY Code Executed in Parallel                                  | 111 |

# LIST OF TABLES

| 1 | <u> Cable</u> |                                                                                 |     |

|---|---------------|---------------------------------------------------------------------------------|-----|

|   | 2.1           | List of Benchmark Subsets for SPEC2006, SPEC2000, and MiBench/MediaBench .      | 10  |

|   | 2.2           | Comparison of Several Popular Simulation Time Reduction Techniques              | 26  |

|   | 6.1           | Benchmarks used for ICBM Results                                                | 66  |

|   | 6.2           | Baseline Configuration for ICBM Results                                         | 67  |

|   | 6.3           | Breakdown of ICBM Pseudo-Assembly Checkpointing Instructions                    | 67  |

|   | 6.4           | Increase in ICBM File Size (measured in bytes) for INT, FP, and SPEC2000        | 71  |

|   | 6.5           | Benchmarks used for ITCY Results                                                | 75  |

|   | 6.6           | Baseline Configuration for ITCY Results                                         | 76  |

|   | 6.7           | Breakdown of ITCY Pre-Interval Instructions                                     | 77  |

|   | 6.8           | 8-byte .data Entries Needed for ITCY Code                                       | 79  |

|   | 6.9           | Number of Syscalls and Indirect Branches Seen in ITCY Interval                  | 80  |

|   | 6.10          | Intra-Interval Indirect Branch ITCY Code Overhead Breakdown                     | 81  |

|   | 6.11          | Intra-Interval Unconditional Branch ITCY Code Overhead                          | 82  |

|   | 6.12          | Average Syscall Emulation Block Size (in Instructions)                          | 86  |

|   | 6.13          | Instruction Pads Needed for ITCY Code                                           | 87  |

|   | 6.14          | I-Cache Miss Rate Performance of ITCY Code Compared to Baseline                 | 91  |

|   | 6.15          | I-Cache Accesses and Misses of ITCY Code Compared to Baseline                   | 92  |

|   | 6.16          | Comparing ICBM and ITCY to Several Popular Simulation Time Reduction Techniques | 113 |

#### CHAPTER I

# Introduction

## 1.1 Motivation

Methods for properly simulating and testing new microarchitectural concepts have been proposed ever since computers were first designed. Most techniques require a large number of benchmark programs be run with many different input datasets for an equally large number of sample configurations of the design. Unfortunately, these requirements create a burdensome number of simulations that can significantly increase the design time of a product. For example, if 30 benchmarks were used with an average of five datasets per benchmark and there were 20 different configurations to be tested, this would require a total of 3,000 individual simulation runs. With each simulation potentially taking days or even weeks to complete, this amount of simulation quickly becomes a serious bottleneck. Compounding this problem is the fact that the most important and representative phases of a benchmark's code usually execute in the middle of the simulation and there is no easy way to execute only this portion without additional support.

Many different methods have been proposed to help alleviate these burdens; however, these methods often lead to decreased accuracy in the simulation or require that the simulator have additional functionality. For instance, if benchmarks or their respective datasets are shortened or removed, the new set of benchmark and dataset combinations might no longer represent a proper workload profile for the design. In addition, methods such as checkpointing and fast forwarding meant to enable the simulation of only certain essential parts of the code require that the simulator have these abilities built in. Checkpointing requires the ability to capture the state of the system at some point in the simulation and later simulations then need the ability to load in the state and start again at that point. Fast forwarding requires a simulator to have a separate, faster mode of simulation that ignores many of the details of the design being simulated while at the same time guaranteeing its functional correctness. These features are not always available or may not be economical to implement if the simulator will have limited distribution or is meant for a small amount of use. Therefore, there is a strong need for new techniques that allow for the fast, efficient, and representative benchmarking of future designs.

# 1.2 Thesis Overview

This dissertation describes two different techniques that are targeted at reducing the overall simulation time needed to test a new design while still maintaining an acceptable level of accuracy with respect to performance estimation. The first technique, Intrinsic Checkpointing through Binary Modification (ICBM), augments a benchmarking program by directly inserting checkpointing code into the binary. When the augmented benchmark later executes, it begins with the checkpointing block of code with refreshes the system to a predetermined state, and then begins the execution of the original binary's code at a specific location. The second technique, InTrinsically Checkpointed assembly (ITCY), also inserts checkpointing code into a benchmark. However, instead of modifying the original binary, the ITCY

method writes an entirely new program in assembly code composed of a subset of the static instructions from the benchmark and any necessary checkpointing and control code needed for proper execution. When the ITCY code is re-compiled, it will then only execute the code necessary to simulate a specific range of instructions from the original benchmark's dynamic instruction stream.

This dissertation makes the following contributions:

- The Intrinsic Checkpointing through Binary Modification (ICBM) technique is presented as a methodology that dramatically decreases the amount of time needed for simulation by analyzing and augmenting benchmark binaries to contain intrinsic checkpointing data. The newly modified binaries do not require re-compilation and allow for the rapid execution of only important portions of code thereby removing the need for fast-forwarding or explicit checkpointing support. In addition, the binaries have increased portability across multiple simulation environments and the ability to easily simulate only important parts of code in a highly parallel fashion.

- A technique for emulating the effects of system calls that are seen within an interval of execution is presented. This method inserts system call emulation code into a new benchmark eliminating the need of system call support for a simulator that runs the new program. As a result, the input dataset is effectively embedded in the new benchmark removing the need for file I/O and increasing its portability across multiple simulation environments.

- A method for combining multiple program fragments into one benchmark is presented. This technique can combine pieces of code from one benchmark, or from a variety of different benchmarks, into a single program. This new

program, if properly instrumented, can easily be moved between a variety of simulators and it can quickly simulate a large amount of representative code in a very short period of time.

• The InTrinsically Checkpointed assembly (ITCY) technique is introduced as an additional method for creating fast and portable benchmarks. It extends on the work done with ICBM by extracting a representative portion, or portions, of a benchmarking program's assembly code and creating a new program. It incorporates the system call emulation and interval combining methods to create a new program that, when re-compiled, contains only a fragment of the original binary. When executed, the code fragments within the program run as if they were run from within their original benchmark in a fraction of the time and can serve as a replacement for the original benchmark. Once an ITCY benchmark is created, it does not need to be recreated if there is a change in the underlying microarchitecture since it is based purely on the original assembly code. In addition, the ITCY technique provides the framework for third parties to create microbenchmarks from their own internal benchmark sources. These microbenchmarks can then be released to the public without the concern of releasing any proprietary information since this sensitive information is effectively hidden inside the ITCY code.

# 1.3 Thesis Organization

This dissertation is organized as follows:

Chapter II provides background information on many different simulation techniques that aim to reduce the overall simulation time needed to test a new design.

Chapter III describes the Intrinsic Checkpointing through Binary Modification

technique along with providing an example of its use on the Alpha [13] architecture.

Chapter IV describes the InTrinsically Checkpointed assembly technique and describes the method of system call emulation. It also presents the method for combining multiple intervals of instructions into a single benchmark.

Chapter V explains the experimental framework used to test the ICBM and ITCY techniques.

Chapter VI investigates the ICBM and ITCY techniques with respect to code overhead, performance modeling, effects on file size, and simulation speedup.

Chapter VII concludes the dissertation with a brief overview and a discussion of future directions.

#### CHAPTER II

# Background

#### 2.1 Overview

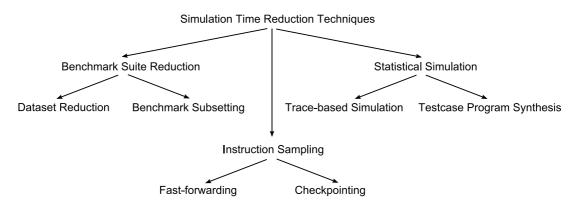

There are many different techniques that can be used to reduce the simulation time of a new design while still maintaining an acceptable level of accuracy. They can be broken down into three main categories: benchmark suite reduction, statistical simulation, and instruction sampling. The first category decreases simulation time by reducing the size of the input data to the benchmarks, by simulating a subset of the original benchmarks, or by doing both. Since the benchmarks subsequently do not execute as many instructions as was originally intended, the overall execution time will be faster. The second category takes each benchmark and runs a set of profiling routines on it to extract its makeup and behavior. Once this information is obtained, a new, smaller benchmark binary or trace is created whose behavior is meant to mimic that of the original benchmark. The third category involves sampling intervals of instructions from the benchmark's dynamic instruction stream and then re-executing the intervals at a later time. The cumulative performance of these samples is intended to represent the overall performance of the benchmark if it were to be executed in its entirety.

A problem with instruction sampling, in particular, is that once the sample inter-

vals of the original benchmark have been identified, they may occur at any point in the benchmark's dynamic instruction stream. Reaching these starting points can be done in several different ways. The entire benchmark can be executed up until the starting point, referred to as fast-forwarding, and then the simulation of the sample can begin. Unfortunately, this method can take a long time to complete if the starting point occurs late in the benchmark's execution. Alternatively, the sample interval can use *checkpointing* to restore the state of the system corresponding to the start of the interval. The data used do to this, referred to as a *checkpoint*, can be used not only to refresh the architectural state of the system such as its memory and registers, but also its microarchitectural state such as its caches and branch predictors. The procedure of refreshing the microarchitectural state is referred to as warmup. Figure 2.1 summarizes these different techniques.

Figure 2.1: Summary of Simulation Time Reduction Techniques

This chapter is organized as follows. Section 2.2 discusses different approaches to benchmark suite reduction. Section 2.3 presents two main types of statistical simulation. Section 2.4 presents several different methods for instruction sampling and section 2.5 discusses a variety of different techniques for adding checkpoint and warmup information to the sample intervals. Finally, section 2.6 concludes with a summary.

#### 2.2 Benchmark Suite Reduction

The techniques in this section reduce simulation time by altering the composition of the original benchmark suite. Even though great care goes into the creation of a benchmarking suite, there can still be a large amount of redundant behavior that is exhibited by its member programs and input datasets. The techniques in this section identify this behavior so that only those programs and input datasets that are necessary to properly represent the benchmarking suite can be simulated.

#### 2.2.1 Dataset Reduction

Dataset reduction reduces the amount of data that a program must process and therefore its execution will finish quicker than if the benchmark had massive amounts of data to handle. This method, when used to create the MinneSPEC [24] workloads, reduces the size of the input datasets to the SPEC CPU2000 benchmarks [23]. It has the advantage that, once the reduced workloads have been characterized, no analysis needs to be done on the program prior to simulation. The workload selection chooses smaller datasets through a process that systematically reduces larger workloads while still maintaining their simulation characteristics, however, this process requires many steps of manual tuning to avoid removing the representative nature of the datasets. In addition, the reduced workloads, if sufficiently small, can fit entirely within a typical cache and no longer test the functionality of the memory subsystem.

## 2.2.2 Benchmark Subsetting

In [48], several different approaches meant to reduce the number of benchmarks that need to be run from a given benchmarking suite are compared. These approaches advocate executing a reduced number of program-input pairs from the suite called a *subset* based upon the similarities between the pairs. Each approach uses a different

method to choose a subset of the suite, however, the method detailed in [36] proves to be the best with respect to accuracy versus cost.

The method in [36] makes use of a multi-step process that first chooses a group of microarchitectural-independent metrics with which to measure the performance of the programs within the benchmarking suite. The programs are run and their results for the chosen metrics are logged. Since this step in the process produces a large number of data points, the next step applies a technique called *Principal Component Analysis* (PCA) to the data points to reduce the dimensionality of the data. After the PCA step is run, a final step, *cluster analysis*, is run on the data to group program-input pairs into clusters that have similar behavior. One benchmark is then selected from each cluster and used to represent all the benchmarks in the cluster for subsequent runs of the suite. Their results show that from an initial set of 26 SPEC CPU2000 benchmarks, they only need to simulate 8 benchmarks to achieve a measure for Cycles Per Instruction (CPI) that is within a 5% error of the actual measurement for the entire suite.

In [37] and [38], the work done in [36] is extended to other benchmarking suites including SPEC CPU2006 [29], MiBench [19], and MediaBench [26]. In [37], performance counters are used to measure a set of metrics for the SPEC CPU2006 benchmarks. The standard PCA and cluster analysis in [36] is then carried out to select a subset of the benchmarks. The analysis identifies a subset of only 6 integer and 8 floating point benchmarks that are needed to represent most of the information found in the 12 integer and 17 floating point benchmarks that comprise the entire suite. In [38], an analysis similar to that proposed in [36] is done and it shows that only 5 benchmarks from the combined set of both MiBench and MediaBench are needed to achieve a measure for Instructions Per Cycle that is within a 5% error of

the actual measurement when both suites are combined. Table 2.1 lists the various subsets of benchmarks that were chosen where each is assumed to use the reference or large datasets.

| SP                           | EC CPU200                                   | 06 Benchmarl                           | κs                                |

|------------------------------|---------------------------------------------|----------------------------------------|-----------------------------------|

| Inte                         | eger                                        | Floating                               | Point                             |

| perlbench                    | mcf                                         | cactusADM                              | leslie3d                          |

| libquantum                   | omnetpp                                     | dealII                                 | soplex                            |

| astar                        | xalancbmk                                   | povray                                 | calculix                          |

|                              |                                             | GemsFDTD                               | lbm                               |

| SP                           | EC CPU200                                   | 00 Benchmarl                           | KS                                |

| Inte                         | eger                                        | Floating                               | Point                             |

| Inte                         | gcc                                         | Floating applu                         | Point equake                      |

|                              | <u> </u>                                    | _                                      |                                   |

| gzip<br>mcf                  | gcc<br>twolf                                | applu                                  | equake<br>mesa                    |

| gzip<br>mcf                  | gcc<br>twolf                                | applu<br>fma3d                         | equake<br>mesa<br>narks           |

| gzip<br>mcf<br>MiBer         | gcc<br>twolf<br>nch/MediaB                  | applu<br>fma3d<br>ench Benchm          | equake<br>mesa<br>narks           |

| gzip mcf  MiBer  MiBerch: su | gcc<br>twolf<br>nch/MediaB<br>san1<br>djpeg | applu fma3d  ench Benchm  MiBench: sus | equake mesa  narks an3 ocm decode |

Table 2.1: List of Benchmark Subsets for SPEC2006, SPEC2000, and MiBench/MediaBench

# 2.3 Statistical Simulation

This section discusses techniques, referred to as statistical simulation, that convert a benchmarking program into a trace or an entirely different program whose execution profile is intended to match that of the original benchmark. This is done first by profiling the original benchmark to ascertain its execution characteristics. These characteristics are then input into algorithms that generate a statistically similar trace or program that will serve as a replacement for the benchmark with an execution time that is far less than the original.

Two types of statistical simulation are discussed below. The first, trace-based simulation, generates a trace of instructions from the initial profile which is run on a

specially instrumented simulator capable of interpreting the trace. The second, testcase program synthesis, generates an actual program binary from the initial profile that can be run on a traditional execution-based simulator.

## 2.3.1 Trace-Based Simulation

In [32], a basic method of trace-based simulation called HLS is proposed. It first executes the benchmark on a pair of simulators that measure several of the program's execution statistics. Statistics such as basic block size and distribution, dynamic instruction distance, instruction mix, cache performance, and branch predictor performance are logged and used to generate a profile of the benchmark. This profile is then input into a symbolic code generator that produces a sequence, or trace, of "instructions". Unlike regular instructions, these symbolic instructions contain special information that dictate their functional unit requirements, expected cache performance, and dynamic instruction distances. The instructions in the trace are then grouped into basic blocks which are linked together into a program flow-control graph. The basic blocks themselves are instrumented such that their branching behavior will produce branch prediction performance similar to that of the original benchmark. The execution of the trace is carried out by a special statistical simulator that is similar to a traditional simulator except that it interprets the statistical information contained inside the trace's symbolic instructions. The final simulation of the trace produced results that were within 5-7% for the SPECint95 benchmarks.

A technique for statistical simulation that is similar to HLS, is proposed in [31]. Unlike HLS, the technique in [31] moves the generation of the instruction trace into the statistical simulator. Therefore, the simulation takes as inputs an instruction profile and the set of cache and branch prediction models. This gives the simulator the flexibility to test different microarchitectural features without having to generate

a new trace of instructions beforehand. Experiments using this technique were carried out with varying levels of complexity with respect to the composition of the basic blocks. The simplest basic block composition that used a global mix of instructions per block and a limited amount of performance information, produced the fastest simulation and results that were within 8% for the SPECint95 benchmark baseline. The more complex basic block composition that incorporated variable basic block sizes, cache and brach prediction miss rates, and dependencies took three times as long to simulate as the simpler method, but produced results that were within 5% of the baseline.

A final technique for synthetic trace generation was first proposed in [16]. Instead of running the benchmark on a simulator to generate the program's profile, a trace of its execution is obtained from real hardware. This initial trace is then input into a set of three profiling tools, two of which model microarchitecture-dependent statistics (i.e. cache and branch performance) and the third which models microarchitectureindependent statistics. Once these statistics are gathered, a synthetic trace is generated. The synthetic trace differs from the other methods discussed above with respect to how it represents instruction dependencies and allocates registers within the trace. Subsequent work done in [15] adds the ability to measure the expected power usage of a design by incorporating a power estimator into the statistical simulator. Results show that this model is capable of identifying a set of energy-efficient architectures that warrant further study. Later work done in [14] and [18] has expanded the capabilities of the method proposed in [16]. Control flow modeling is used in [14] to generate a control flow graph during the microarchitecture-independent profiling stage and improves the accuracy of the overall statistical simulation. Memory data flow modeling is incorporated in [18] for tracking statistics such as cache miss correlations, load forwarding, and delayed hits. This method reduces the average performance prediction error from 10.7% down to 2.3%.

# 2.3.2 Testcase Program Synthesis

As an alternate to creating a synthetic trace, statistical simulation can be performed using a standalone program whose creation and execution profile are also based on statistical analysis. This method is referred to as testcase program synthesis. In [7], the HLS methodology described in section 2.3.1 is modified slightly to include the concept of issue width and to more closely match the execution engine of SimpleScalar [1]. Since the SimpleScalar simulator will ultimately be executing the synthetic testcase, this modification is made to allow for more accurate modeling of program performance. The HLS framework, now referred to as S-HLS, is used to generate a profile of the benchmark. After the profile is generated, it is used to synthesize a program in C-code that is composed primarily of a subset of assembly language calls that map directly to the instructions in the basic blocks of the profile. The technique unfortunately suffers from an inability to properly model branch prediction and cache performance. This problem is reserved for future work and the technique is tested using technical loops as a proof of concept due to their high cache hit rates and high branch prediction rates.

Subsequent work done in [10] and [8] addresses the branch prediction and cache modeling issues in [7]. The difficulty of branch prediction modeling is alleviated by manipulating the branches that exit the basic blocks in the profile. By creating code that dictates whether or not a branch is taken or not taken, the branch prediction rate is able to be modeled effectively. To properly model D-cache behavior, a more detailed memory access model is developed. In addition, I-cache performance is more effectively predicted using a carefully tuned number of synthetic basic

blocks. After these problems were addressed, synthetic testcases for the SPEC2000 benchmarks were successfully generated and measurements for Instructions per Cycle (IPC) within 2.4% of the original benchmarks with similar workload characteristics were obtained. This work was extended further in [9] to do efficient power analysis and in [6] to do performance model validation of a PowerPC processor.

A detailed analysis was done in [5] on the source of the errors in testcase synthesis. Errors in the workload characterization phase were caused by the need to reduce the number of representative basic blocks due to size constraints and also the loss of information by only using a subset of assembly instructions to represent all the original instructions. In addition, small errors that still existed in the cache and branch prediction models were discussed. Other sources of error included problems with instruction dependencies, register assignment, and scaffolding code in the synthetic testcase. A final analysis of the errors showed that, while they do contribute to a loss of accuracy, the effects are small with respect to the performance of the original program with similar workload characteristics. However, it is noted that because of these errors, particularly those regarding cache and branch prediction performance, testcase synthesis should not be used as a replacement to detailed, application simulation. Rather, it should be used early in the design cycle to quickly evaluate the many different design choices that are available and provide insight into what configuration should be looked at more closely with detailed simulation.

## 2.4 Instruction Sampling

The methods in this section reduce simulation by using a technique called instruction sampling. These technique can achieve the highest level of accuracy with respect to performance prediction. However, they oftentimes result in a longer simulation time than benchmark suite reduction and statistical simulation. The basic instruction sampling methods select intervals of instructions from the dynamic instruction stream and then re-execute those intervals at a later time. Depending on the size and location of the intervals, the reduction in simulation time can be quite dramatic.

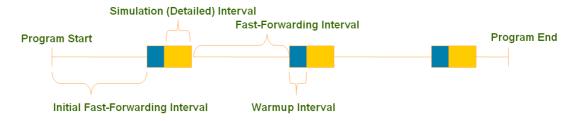

## 2.4.1 SMARTS

The Sampling Microarchitecture Simulation framework (SMARTS) [47] is a simulation tool that provides quick and accurate results while only having to simulate in detail a small portion of the benchmarking program. It relies on strict statistical sampling and selects a subset of the program for detailed simulation whose results will adhere to an expected confidence interval. The program is divided into a series of equal length intervals each of which is further broken into a fast-forward component that stresses speed over accuracy, a warmup component that refreshes certain microarchitectural components such as caches and branch predictor structures that were neglected in prior fast-forwarding segments, and finally a detailed simulation component that runs with the most accuracy. After the user calculates, based on methodologies explained in [47], initial input values for warmup, detailed simulation, and overall interval lengths, SMARTS undergoes a series of tuning steps that refine the length of the fast-forward component to a point that will result in an appropriate amount of confidence for the benchmark being used.

After deriving all the necessary interval values, SMARTS starts the original benchmark binary in fast-forwarding, or functional simulation, mode and runs for an initial number of instructions provided by the user. At this point, the first interval begins the warmup period that updates the state of necessary components mentioned above. After the warmup period finishes, the detailed simulation segment begins and is followed by the fast-forwarding component that finishes the first interval. This system-

atic sampling of warmup, detailed simulation, and then fast-forwarding repeats itself until the benchmark completes. Figure 2.2 depicts this process graphically.

Figure 2.2: Sampleing Intervals for SMARTS

Simulations utilizing SMARTS were run on 8-way and 16-way superscalar processor models meant to represent current and future microarchitectures, respectively, using the SPEC CPU2000 benchmarks. CPI and Energy per Instruction (EPI) can be estimated within 3% with 99.7% confidence while measuring less than 50 million instructions for each benchmark. An additional amount of error, empirically set to roughly 2%, needs to be included due to unknown accuracy in the warmup routines. For the actual simulation runs themselves, SMARTS was able to reach an average error of only 0.64% for CPI and 0.59% for EPI with average speedups over detailed simulation of 35 for the 8-way model and 60 for the 16-way model.

# 2.4.2 SimPoint

Another tool that is useful for fast and accurate instruction sampling is SimPoint [41]. Like SMARTS, SimPoint only simulates in detail small portions of the benchmark leaving the rest for fast-forwarding. However, the methods it uses to decide which portions of the program will be used for the detailed simulation significantly differ from SMARTS. SimPoint makes use of the fact that most programs are comprised of repeated sections of execution referred to as phases. Since some of these phases look very much alike, SimPoint attempts to find them and then simulates only one of them from each set of similar phases. Results are then be extrapolated

based on the frequencies of the different phase sets in the code.

In order to identify phases in the code, the program is executed in a fast and functional manner where only the instructions are analyzed. In other words, it is executed independent of the underlying microarchitecture which allows for the final results to be carried across different microarchitectural configuration boundaries. As the program is being executed, frequency vectors meant to track various program structures are captured for contiguous intervals of size N. After the vectors are obtained for each interval of execution, their dimensionality is reduced, while still preserving commonality, by a process of random linear projection to allow for faster analysis in later steps. The reduced vectors are then input into a k-means clustering algorithm, using various values of k representing the number of clusters, to find a minimum number of clusters that satisfies a "goodness of fit" value calculated using the Bayesian Information Criterion on each clustering that is produced by the k-means algorithm. This final clustering will then contain a grouping of intervals into phases.

Once the clustering is found, it is input into a selection algorithm that will choose a representative interval from each cluster. To do this, the Euclidean distances between the vectors in the cluster are calculated and used to determine the similarity of each interval to one another. The interval that is most like the other intervals, referred to as the centroid, is then chosen as the most representative, assigned to be the simulation point for the cluster, and given a weight that corresponds to the overall number of instructions that it represents in the program. After a simulation point is found for each cluster, all simulation points from each cluster can then be simulated in detail.

When all the simulations have finished, it is a simple matter of multiplying the

metrics gathered from each interval by the weight assigned to that interval. These weighted metrics are then summed together to get the final metric used for the entire program. As an example, if a program consisted of two intervals where the first had a weight of .25 with a measured value of 5 and the second had a weight of .75 with a measured value of 10, the full execution metric would be estimated at .25(5) + .75(10) = 8.75.

Several modifications have been made to SimPoint that address some potential shortcomings of the original implementation. The first modification attempts to make SimPoint faster by introducing an additional variable into the simulation point selection algorithm [35]. Instead of simply using Euclidean distance similarity for selection, intervals are given higher priority if they occur early in the code as opposed to ones that appear later. This early SimPoint method makes it possible for the serial simulation to finish quicker since its points will occur earlier in the code. The second modification removes the restriction that each interval must be of equal length [25]. This allows for a more representative sample to be obtained since the intervals are not constrained to a specific length. Finally, additional improvements are made in the newest release of SimPoint, version 3.0 [21]. These improvements consist of faster and more efficient cluster identification, better clustering in general, the ability to handle large numbers of simulation points, and the ability to output only those clusters that account for the majority of the execution.

The results for SimPoint when run on the SPEC CPU2000 benchmarks show that an average error rate of 2.1% is achieved for the standard SimPoint algorithm and an average error rate of 3.5% is achieved for the early SimPoint algorithm. As expected, the early SimPoint algorithm completed in much less time, finishing 15 times faster than the standard algorithm. If each simulation point were to be

executed independently, the run time of the simulation would further improve and be merely a function of the number of instructions in each interval that are executed in detail combined with the amount of fast-forwarding needed to reach the interval. This amount of time would be orders of magnitude smaller since a typical interval has a length of 10 million instructions while whole programs often run into many billions of instructions.

# 2.4.3 Improving Sampled Simulation

Although SMARTS and SimPoint can greatly reduce the amount of time needed to simulate a new design, work done in [28] contributes several improvements to these and other instruction sampling techniques. First, it is shows that the number of instructions contained in each instruction sample can have an affect on its accuracy. In particular, smaller and more numerous samples lead to more accuracy in general than larger, less frequent samples when the simulation budget remains fixed. Second, the number of instructions necessary to estimate different performance metrics within a certain margin of error is shown to vary based on the metric. For example, if the only requirement for a simulation is to show the expected speedup of a design change, then 9X less instructions need to be sampled in order to remain within the same margin of error that would be required when estimating CPI instead. Finally, for techniques such as SMARTS that require several tuning runs of the benchmark in order to reach a certain confidence interval, it is shown that these tuning runs are no longer necessary when a proposed dynamic stopping technique is used in conjunction with online transactional processing benchmarks due to their unique execution patterns.

# 2.5 Techniques for Checkpointing and Warmup

After sample intervals are identified by methods such as those in section 2.4, they can be executed in a variety of ways. The first, and simplest, method simply runs the benchmark through a functional simulator that only updates the essential state of the system until it reaches the beginning of the interval. Then the interval's execution can begin in detail. Unfortunately, this technique, referred to as fast-forwarding, can take an incredible amount of time if the benchmark occurs late in the dynamic instruction stream of the benchmark. Alternatively, through a process called checkpointing, a copy of the system state, called a checkpoint, is gathered immediately prior to the execution of the interval. Then, instead of fast-forwarding to the start of the benchmark, this checkpoint data can be loaded into the simulator and the interval can immediately begin its execution.

Checkpoint data can be composed of many different elements meant to refresh the state of not only the architectural components of the system, but also its microarchitectural components. At the simplest level, the checkpoint must at least refresh the architectural state (i.e. the main memory and registers) used in the interval. However, if the sampled interval is to be completely simulated in detail on the microarchitectural level, there must be more detailed information contained in the checkpoint to refresh such components as the caches and branch predictor. The process of using this detailed information to update the microarchitectural state of the system is referred to as warmup. This section will describe several different methods of checkpointing and warmup in detail.

## 2.5.1 Direct Execution Checkpointing

The techniques in this section obtain checkpoint and warmup data by directly executing the benchmark on real hardware. This can rapidly provide data, however, a system to directly execute the benchmark may not always be readily available. For systems that are in the early stages of development, a hardware implementation may not even exist. Regardless, they provide a very rapid methodology for obtaining checkpoint and warmup data.

The SimSnap tool [42] is a checkpointing approach that places the location where checkpoint data needs to be obtained directly in the source code of the program. The user has to modify the original source code of the benchmark to include checkpointing routines and also has to supply, on a function level, a location for where the code should be checkpointed. After the benchmark is compiled, it is run and at the predefined location in the code it will output checkpointing data to a separate file. Subsequent runs of the benchmark, when executed in a restore mode, will read in the data from the checkpoint file and resume operation where the benchmark left off.

Because of the fact that SimSnap relies heavily on the compiler and has to checkpoint not only the data required for the proper execution of the simulation interval,

but the entire system state, it has several drawbacks. The first is that the checkpointing files can be quite large since they contain the entire state of the system. A

second drawback is that SimSnap not only requires the user to make changes to the

source code, but also that the source code itself be available. For benchmarks that

do not supply source code, this will prevent them from utilizing the checkpointing

features of SimSnap. A final drawback is that SimSnap will only work if the benchmark's native programming language is supported by a compiler. If the program was

written in a propriety language or one that is no longer heavily used, then SimSnap

would not be able to generate checkpoint code.

In [34] and [40], direct execution is used to obtain instructions from within an instruction interval. In [34], the Pin [27] tool, which relies on direct execution, produces a benchmark profile that is input into SimPoint to identify representative instruction intervals. Once these intervals are identified, they are compared against the original benchmark using Pin and a set of *PinPoints* is generated. The Pin-Points can then either be used as an instruction trace of the interval or to dictate to an execution-driven simulator when it should switch between fast-forwarding and detailed execution modes. In [40], a completely new program is generated. When combined with a pre-loaded memory image, the program executes a set of instructions that represent the original interval of interest.

The Direct SMARTS technique described in [12], uses direct execution to progress the original benchmark between its intervals of detailed simulation. The checkpoint and warmup data that is generated by Direct SMARTS is fed directly into the simulator during the period of direct execution and is not stored for later use. This ability is made possible by running the benchmark inside of the RSIM simulator [33] which has the ability to switch back and forth between modes of direct execution and detailed simulation.

In [30], the Pin tool is again used to directly execute a benchmark. However, the importance of Pin in this technique is that it is modified to capture system effects. These effects are stored in a system effect log and are later used during architecture simulations. This type of checkpointing is different than previous methods since it removes the need for a simulator to support system calls. This is important since popular simulators such as SimpleScalar must emulate the effects of system calls and many applications, particularly applications running in Linux, require system

calls that may not be emulated. Therefore, since the system calls have effectively been checkpointed, SimpleScalar can execute a broad range of applications that it previously could not support.

#### 2.5.2 Simulator-Derived Checkpointing

Work done in [43] directly addresses checkpointing and warmup in SimPoint. It proposes two techniques, the touched memory image (TMI) and the memory hierarchy state (MHS), to refresh the system state prior to the execution of the simulation interval. TMI creates a list of memory addresses and data values that are used to refresh the architectural state of the system. TMI only contains stores to memory locations that are needed within the simulation interval and is, therefore, much smaller than a full system checkpoint. In addition, it uses several data packing strategies to reduce its overall size. MHS stores a cache state that is collected during a simulation of the memory hierarchy prior to the execution of the interval. Later, when the interval is simulated in detail, the microarchitectural information stored by MHS is loaded and used to refresh the state of the cache or any cache with a smaller size or associativity.

Similar to the work done in [43], [44] and [45] propose techniques that are targeted at the rapid checkpointing and warmup of SMARTS. Again, state is only stored for the instructions that will be executed in each SMARTS interval, and since the size of each SMARTS interval is much smaller than the interval size in SimPoint, roughly 1000 instructions, the amount of checkpointing data needed per interval is very small. Unlike [43], however, caches are not the only microarchitectural element that are warmed up. The branch predictor is also warmed by storing a variety of configurations worth of checkpointing data for different branch predictor organizations in the checkpoint. The combination of the checkpoint and warmup data with

the interval of execution is referred to as a live-point and a library of live-points meant to checkpoint the entire SPEC2000 benchmarking suite occupies 12 GB of file space. Since each live-point is an individual simulation element, the live-points that comprise a full benchmark can be executed in parallel and in any order. In addition, if the live-points are randomly executed, then the confidence interval of the simulation can be tracked over time and when it reaches an acceptable level, the simulation can be terminated early. This addition of warmup and checkpointing data and the ability to leave a simulation early makes the live-points technique a fast and accurate simulation technique. Later work done in [46] extends live-points to cover multiprocessor server workloads and creates a very powerful simulation environment for future workloads.

In [4], [3], and [2], several additional methods are described that create checkpoint data that is similar to that generated in [43] and [45]. [4] presents a software structure called a memory timestamp record (MTR) that stores memory access patterns that can be used to refresh the state of a variety of cache configurations in a multiprocessor system. [3] presents a technique called branch predictor based compression (BPC) that creates a highly compressed representation of many different branch predictor configurations that can be used to warmup a variety of different branch predictors. Since MTR and BPC are both microarchitecture-independent methods, they offer a great deal of flexibility when warming up the state of a system.

## 2.5.3 Reuse Latency Warmup

Two techniques that offer very different warmup strategies than those described in the previous sections are MRRL [22] and BLRL [17]. Both techniques are based on what are referred to as *reuse latencies*, the distance in the dynamic instruction stream between two accesses to the same memory location. By analyzing these dis-

tances during an initial functional simulation, MRRL and BLRL identify a starting point in the benchmark that occurs prior to the beginning of a sampled instruction interval. This starting point is where execution should begin in order to effectively warmup the state of the system by the time the interval starts. This starting point identification is different than the previously discussed techniques since it does not require the discovery, storage, and loading of any checkpoint data and it is completely microarchitecture-independent. It simply tells the simulator to start executing the benchmark a certain number of instructions before the interval and then begin gathering statistics once the interval is reached. Since the introduction of MRRL preceded BLRL by several years, BLRL was able to improve upon the work in MRRL and decrease the size of the warmup interval by half over MRRL. Regardless, both are very useful methods for simply and effectively warming a system's state prior to the execution of a simulation interval.

# 2.6 Summary

This chapter presented a variety of techniques targeted at reducing the simulation time of a benchmarking program while still maintaining accuracy. Benchmark suite reduction locates redundancies in benchmarking suites and attempts to find the minimum subset of benchmarks and input datasets that are necessary to represent the entire benchmarking suite. Statistical simulation generates a profile of the original benchmark and then uses this to create a synthetic trace or program that can be used early in the design cycle to quickly sort out viable design choices that should be evaluated in more detail. Instruction sampling can be used to study a benchmark in much more detail by choosing representative intervals of instructions and using only those intervals for simulation. Checkpointing can be used to further decrease

their immediate execution after checkpoint data has been handled. Finally, warmup can help to guarantee that the intervals' results will be as accurate as possible by refreshing the state of not only the system's architecture, but its microarchitecture as well. Table 2.2 compares several of the more popular techniques by contrasting their reported speedup, accuracy with respect to full detailed simulation, representativeness, microarchitecture dependence, storage space requirements, and flexibility with respect to the subsequent simulation environment.

|               | Execution  | CPI        | Representa- | Micro-       | Storage    | Flexi- |

|---------------|------------|------------|-------------|--------------|------------|--------|

| Technique     | Time per   | Prediction | tiveness    | architecture | Req's      | bility |

|               | B-mark     | Accuracy   |             | Dependent    |            |        |

| B-mark Suite  |            |            |             |              |            |        |

| Reduction     | Variable   | Variable   | Low         | No           | N/A        | High   |

| [24]          |            |            |             |              |            |        |

| Statistical   | approx.    |            |             |              |            |        |

| (Trace)       | 1000x      | 2.3%       | Low         | Yes          | negligible | Low    |

| [18]          | speedup    |            |             |              |            |        |

| Statistical   | approx.    |            |             |              |            |        |

| (Testcase)    | 1000x      | 2.4%       | Low         | Yes          | negligible | High   |

| [10]          | speedup    |            |             |              |            |        |

| SMARTS [47]   | 5 hrs      | 0.64%      | High        | No           | N/A        | Medium |

| SimPoint [41] | 2.8 hrs    | 3.7%       | High        | No           | N/A        | Medium |

| SimPoint      | 14 mins    |            |             |              | 4 GB       |        |

| Startup [43]  | (serial)   | 1.2%       | High        | Yes          | for 20     | Low    |

|               | 1 min      |            |             |              | SPEC2K     |        |

|               | (parallel) |            |             |              | b-marks    |        |

| LivePoints    |            |            |             |              | 12 GB      |        |

| [45]          | 91 secs    | 1.6%       | High        | Yes          | compressed | Low    |

|               |            |            |             |              | all SPEC2K |        |

|               |            |            |             |              | b-marks    |        |

Table 2.2: Comparison of Several Popular Simulation Time Reduction Techniques

## **CHAPTER III**

# Intrinsic Checkpointing with Binary Modification

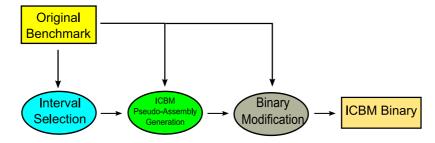

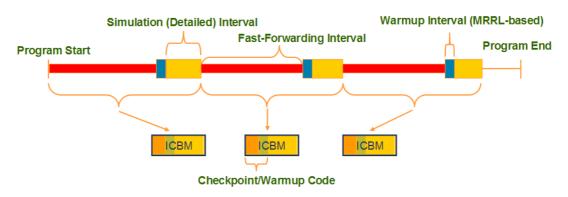

## 3.1 Overview

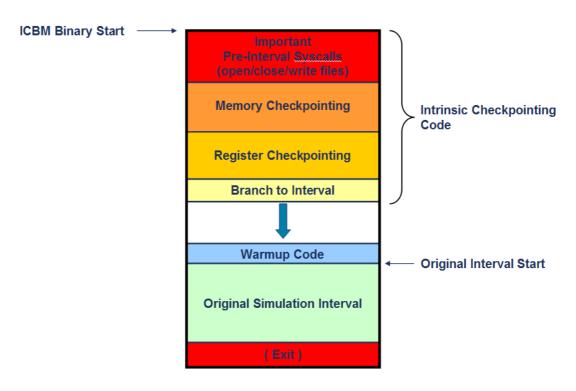

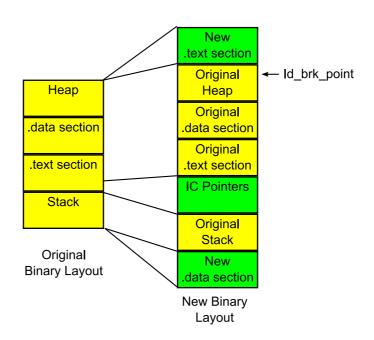

This chapter will present a technique called *Intrinsic Checkpointing through Binary Modification* (ICBM), first published in [39], which modifies a benchmark binary so that it will only execute a certain part of its code. This is done by first analyzing the code within a provided interval of execution and then generating a set of checkpointing and warmup instructions. These instructions, when inserted into the original binary, effectively recreate the system environment that the interval would see at its start had the binary been executed normally. The original binary must then be modified to start its execution at the beginning of these checkpointing instructions and then transfer control to the start of the interval instructions. Figure 3.1 represents these phases pictorially.

Figure 3.1: ICBM Process Flow Diagram

This technique creates a form of intrinsic checkpointing that removes the require-

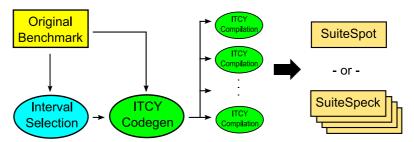

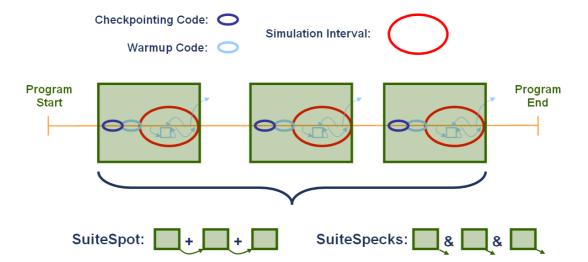

ments of checkpointing and fast forwarding from the simulator and places it into the program itself. When combined with tools such as SimPoint [41] and BLRL [17], it becomes possible to properly benchmark a system in a fraction of the time compared to using the original benchmarking binary. For simulators such as RTL models where checkpointing and fast forwarding may be very difficult to implement, this technique allows for the simulation of benchmarks that in the past were severely hindered by their execution times. Figure 3.2 gives a graphical overview of how the various fast-forwarding, warmup, and detailed simulation intervals are combined into individual ICBM binaries.

Figure 3.2: ICBM Interval Selection and Creation

This chapter is organized as follows. Sections 3.2, 3.3, and 3.4 will discuss how the register file, memory, and system calls are checkpointed, respectively. Section 3.5 with describe how the checkpointing code is inserted into the original benchmark through the binary modification process. Section 3.6 will describe how it is possible for the interval to exit its execution after the appropriate number of instructions and section 3.7 will list several implementation issues that are associated with ICBM. Section 3.8 will describe how the ICBM technique is verified and section 3.9 will illustrate the basic ICBM method with an example. Finally, section 3.10 will conclude with a summary.

# 3.2 Register Checkpointing

In order to create the necessary code to bring the simulation interval up to date, an analysis of the benchmark must be done to find out what system state needs to be restored for the proper execution of the simulation interval. The register file is by far the simplest component whose usage must tracked and restored since it only contains a limited number of architectural elements. To do this, a simple snapshot of the register file is taken immediately before the first instruction in the simulation interval and its current values are noted. These values are then restored with simple load instructions in the checkpoint code to bring the register file up to date.

## 3.3 Memory Checkpointing

Memory, unlike the register file, proves to be a much more troublesome component to intrinsically checkpoint, especially if there are many instructions within the simulation interval that depend on values in memory that were modified before the interval began. To track these modifications, a copy of the initial memory, INIT-MEM, is created when the program first begins its execution and the program is then allowed to fast-forward up to the simulation point in question. At that point, a copy of memory, CHECKMEM, is saved to hold any changes to the memory from the pre-interval code. Next, as the simulation interval progresses, each time a load is encountered within the simulation interval, if the value in INITMEM differs from the value in the current memory, CURRENTMEM, then it is known that some instruction in the pre-interval code stored a value to that memory location. Consequently, the memory location and its value from CHECKMEM are logged so that later it can be turned into a store in the checkpoint code. The memory location in INITMEM is then updated with the value from CURRENTMEM so that this situation will

not occur again. In the case of a store to memory within the simulation interval, the value is simply stored to both CURRENTMEM and INITMEM since this store effectively overwrites any loads that occurred in the pre-interval code.

# 3.4 System Call Checkpointing

System calls (syscalls) also create a rather difficult problem when handling the instructions prior to the interval's execution. File output syscalls are ignored since, unless the output file is used later in the interval as input, they won't affect the results of the program. File input, however, modifies file pointers in the program and the usage of all input files is logged so that all relevant pointers can be updated in the checkpoint code. This is done by noting the work that occurs in the simulation for file handling and keeping track of the various values that control file manipulation. Other system calls, such as those that change directories, modify file permissions, or open/close files also have these types of methods that track their usage. Code is inserted into the system call handlers of the simulator to have their requisite input values loaded using analysis similar to the register and memory analysis discussed above. Then, the actual system call is run from within the checkpoint code. Since there are only a few syscalls that can actually affect the system environment, the generated code for syscall checkpointing is small. The remainder of the syscalls that occur prior to the interval are either ignored or, if they modify memory or register state, the normal simulation interval analysis discovers these changes and generates the corresponding checkpoint code.

#### 3.5 Interval Execution

Once the checkpointing data has been created and saved to a "pseudo-assembly" program, it must be converted into the appropriate machine instructions and inserted

into the original benchmark binary. To do this, the ICBM technique uses a Perl script that converts the pseudo-assembly into machine code, finds a place in the binary to insert the code, and then rewrites the binary. During insertion, it is important that the restoration of the registers occur at the end of the checkpointing code since the operations for restoring the memory need to make use of the registers. After the insertion, the new binary has its starting point set to the beginning of the checkpointing code. Next, at the end of the checkpointing code a final jump is inserted that will move the execution to the beginning of the simulation interval. Depending on the instructions available, this can be done with either an explicit jump to a PC provided in the instruction, or a jump to a PC value that is stored in a register. If a register is needed, as is the case with ICBM, then it will have to be one that is going to be overwritten before it is used inside the interval so that proper execution will be guaranteed. Figure 3.3 shows the instructions in a typical, pseudoassembly checkpoint file prior to being converted into machine code and inserted into the binary. First, any syscalls that must be run prior to the interval are output, followed by the section to restore the memory, and then register restoration occurs. Finally, the jump to the start of the simulation interval is executed.

## 3.6 Exit Handling

A final issue that will need to be dealt with is the method by which the simulation ends following the execution of the interval. In a typical simulator, the preferable method is to simply tell the simulation when to stop by providing a count for the number of cycles to simulate. This, however, requires that the simulator have the ability to track the number of instructions on a per instruction basis from within the simulation. In addition, if the goal of creating a set of microbenchmarks is to

```

# <syscall stores>

st <addr>, <imm>

# store imm value into mem @ addr

# <syscall register loads>