## THE UNIVERSITY OF MICHIGAN COMPUTING RESEARCH LABORATORY<sup>1</sup>

#### DEVELOPMENT AND ANALYSIS OF A GLOBAL COMPACTION TECHNIQUE FOR MICROPROGRAMS

Jehkwan Lah

CRL-TR-40-84

September 1984

Room 1079, East Engineering Building Ann Arbor, Michigan 48109 USA Tel: (313) 763-8000

<sup>&</sup>lt;sup>1</sup>Any opinions, findings, and conclusions or recommendations expressed in this publication are those of the authors and do not necessarily reflect the views of the funding agency.

# DEVELOPMENT AND ANALYSIS OF A GLOBAL COMPACTION TECHNIQUE FOR MICROPROGRAMS

#### by Jehkwan Lah

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 1984

#### **Doctoral Committee:**

Professor Daniel E. Atkins, Chairman Professor Gideon Frieder Associate Professor Trevor Mudge Professor Norman Scott Associate Professor Toby Teorey

#### **ABSTRACT**

## DEVELOPMENT AND ANALYSIS OF A GLOBAL COMPACTION TECHNIQUE FOR MICROPROGRAMS

## by Jehkwan Lah

Chairman: Daniel E. Atkins

The need for a better microprogramming tool has increased considerably as increased demand and support of computer technology has brought about wide use of microprograms. The eventual goal of microprogramming tool development would be to make a high level microprogram language and a compiler to generate minimal-execution-time microcode for a variety of machines. In generating minimal-execution-time microcode, one aspect that differentiates microprogramming languages from macroprogramming languages is the need for compaction in highly horizontal microarchitecture.

Among the proposed microprogram compaction methods, the trace scheduling is the most general and appears to give the fastest execution of compacted microcode. However, the growth of memory size by extensive copying of blocks can be enormous, exponential in the worst case, and the complicated bookkeeping stage of the trace scheduling has been an obstacle to implementation.

A technique called beta compaction, based on trace scheduling, is proposed to mitigate the drawbacks of trace scheduling. Basically, it identifies the junction blocks (the blocks beginning with a join and ending with a conditional branch) as the major source of complication, and cut traces at those junction blocks. It achieves almost all the compaction of the trace scheduling except that which causes copying of blocks. Memory size after the beta compaction is usually smaller than the original. Even when the memory size grows in rare instances, it

is bounded by  $O(n^2)$  in the worst case. And the bookkeeping stage is very much simplified. The compacted microcode size variation as the source microcode changes is also very small.

A loop-free version of both beta compaction and trace scheduling has been implemented. Comparison between the two was done using artificially synthesized microcodes and the above properties of the beta compaction was confirmed.

A simple microprogrammable machine based on AM2900 components was designed and simulated with an interactive user-friendly interface. A realistic application program was written and hand-compiled into microcode. The microcode was executed on the simulator both before and after compaction, which demonstrated the applicability of the compaction technique and the correctness of the implementation.

## TABLE OF CONTENTS

| DEDICATION   |                              | ii       |

|--------------|------------------------------|----------|

| ACKNOWLED    | OGMENT                       | iii      |

| LIST OF FIGU | JRES                         | vi       |

| LIST OF APP  | ENDICES                      | ix       |

| LIST OF ABB  | REVIATIONS                   | X        |

| CHAPTER      |                              |          |

| I. INTR      | ODUCTION                     | 1        |

| П. А МО      | ODEL OF A MICROPROGRAM       | 7        |

| 2.1          | Data Dependency Analysis     | 9        |

| 2.2          | Host Machine Description     | 10       |

| 2.3          | Microprogram Description     | 11       |

| III. PRE     | EVIOUS RESEARCH              | 13       |

| 3.1          | Local Compaction             | 14       |

|              | 3.1.1 First-Come First-Serve | 15       |

|              | 3.1.2 Critical Path          | 17       |

|              | 3.1.3 Branch and Bound       | 20<br>23 |

|              | 3.1.4 List Scheduling        | 23<br>26 |

| 3.2          |                              | 20<br>28 |

| 0.2          | 3.2.1 Wood                   | 29       |

|              | 3.2.2 Tokoro                 | 31       |

|              | 3.2.3 Fisher                 | 33       |

| IV. BET      | ΓA COMPACTION ALGORITHM      | 38       |

| 4.1         | Algorithm Description                | 39         |

|-------------|--------------------------------------|------------|

|             | 4.1.1 Live register analysis         | 42         |

|             | 4.1.2 Pick Trace                     | 43         |

|             | 4.1.3 List Scheduling                | 47         |

|             | 4.1.4 Bookkeeping                    | 54         |

| 4.2         | Simple Illustrative Example          | 58         |

| V. EXPI     | ERIMENTATION AND ANALYSIS            | <b>6</b> 8 |

| 5.1         | Purpose                              | 68         |

| 5.2         | Hypothesis                           | 69         |

| 5.3         | Implementation                       | 69         |

| 5.4         | Comparison against trace scheduling  | 70         |

|             | 5.4.1 Artificial Microcode Model     | 71         |

|             | 5.4.2 Program Structure Model        | 72         |

|             | 5.4.3 Procedure                      | 76         |

|             | 5.4.4 Result and Discussion          | 78         |

| 5.5         | Simulator of an AMD2900-based system | 81         |

|             | 5.5.1 System description             | 82         |

|             | 5.5.2 Functions and human interface  | 85         |

|             | 5.5.3 An Application Program         | 85         |

| 5.6         | Space Complexity Analysis            | 87         |

|             | 5.6.1 Trace Scheduling               | 88         |

|             | 5.6.2 Beta Compaction                | 80         |

| VI. CON     | NCLUSION                             | 95         |

| 6.1         | Summary                              | 95         |

| 6.2         | Future Research                      | 96         |

| APPENDICES  |                                      | 97         |

| BIBLIOGRAPI | HY                                   | 126        |

## LIST OF FIGURES

## Figure

| 3.1  | Data dependency graph of example microcode | 14 |

|------|--------------------------------------------|----|

| 3.2  | The working of first-come first serve      | 16 |

| 3.3  | The working of critical path               | 18 |

| 3.4  | Result of critical path                    | 19 |

| 3.5  | Working of branch and bound exhaustive     | 22 |

| 3.6  | Weight of MO's for list scheduling         | 25 |

| 3.7  | MO's with different data antidependencies  | 27 |

| 3.8  | Wood's compaction heuristic                | 30 |

| 3.9  | Tokoro's MO movement rules                 | 32 |

| 3.10 | Fisher's trace scheduling                  | 34 |

| 3.11 | Copied blocks in the trace scheduling      | 36 |

| 4.1  | Junction block                             | 39 |

| 4.2  | Insertion of dummy blocks                  | 41 |

| 4.3  | Selecting traces                           | 46 |

| 4.4  | Sample data dependency graph               | 48 |

| 4.5  | Example of building DDG                    | 50 |

| 4.6  | Example of assign priority                 | 52 |

| 4.7  | Components of trace                        | 55 |

| 4.8  | Copying MO's                               | 57 |

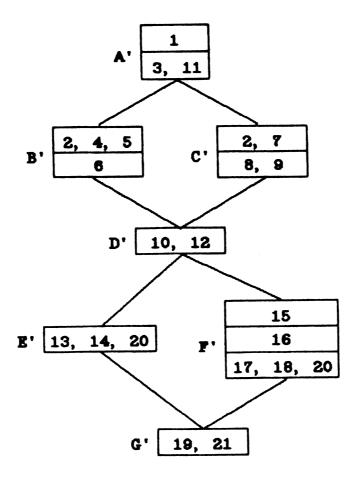

| 4.9  | Sample microprogram                        | 59 |

| 4.10 | List of MO's                               | 60 |

| 4.11 | Live registers                             | 61 |

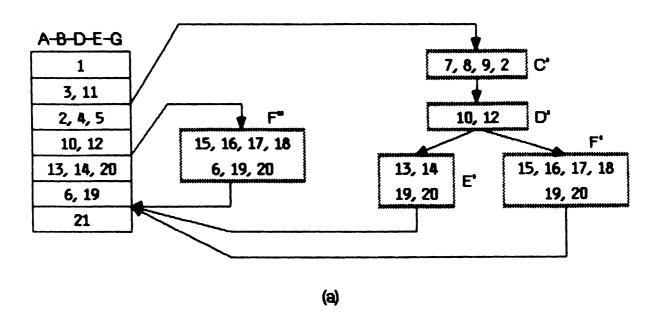

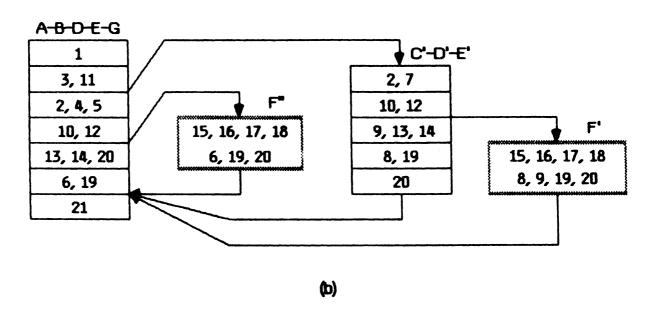

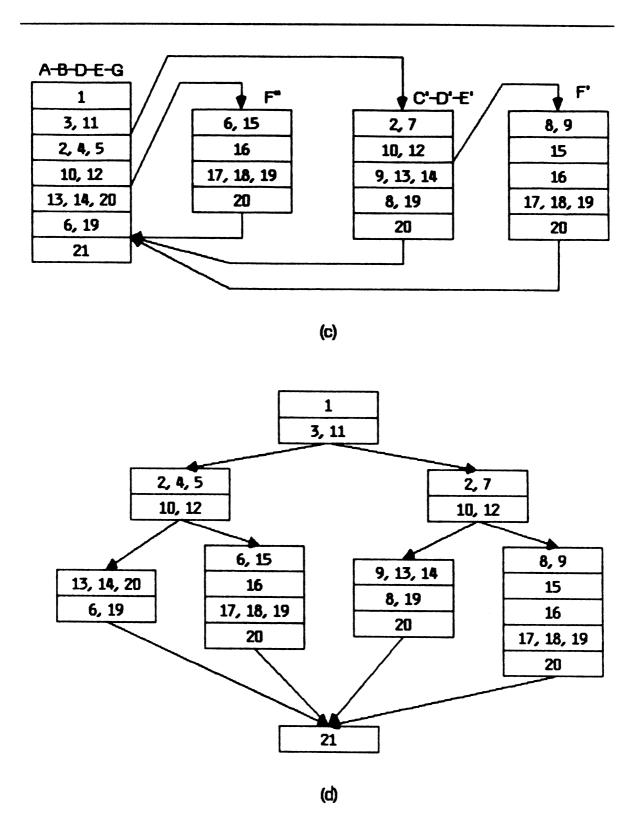

| 1.12        | Data dependency graphs                                      | 62         |

|-------------|-------------------------------------------------------------|------------|

| 1.13        | Intermediate results                                        | 63         |

| 4.14        | Final result                                                | 64         |

| 4.15        | Trace scheduling on the example                             | 65         |

| 4.15        | Trace scheduling on the example (cont'd)                    | 66         |

| 4.16        | Comparison summary                                          | 67         |

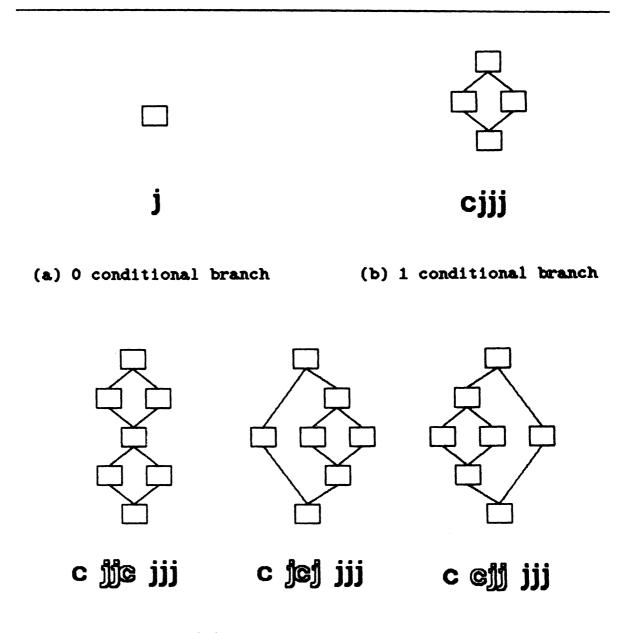

| 5.1         | Program structure model                                     | <b>7</b> 3 |

| 5.2         | Program structure model for 3 conditional branches          | 74         |

| 5.2         | Program structure model for 3 conditional branches (cont'd) | <b>7</b> 5 |

| 5.3         | Example of an artificially synthesized microcode            | 77         |

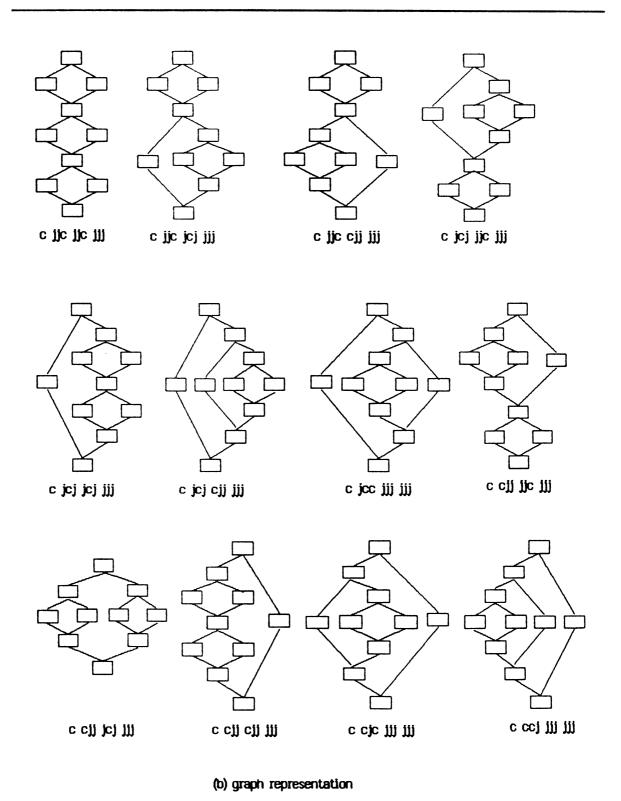

| 5.4         | Summary of experimental result                              | 79         |

| 5.5         | Distribution of the two junction block case                 | 80         |

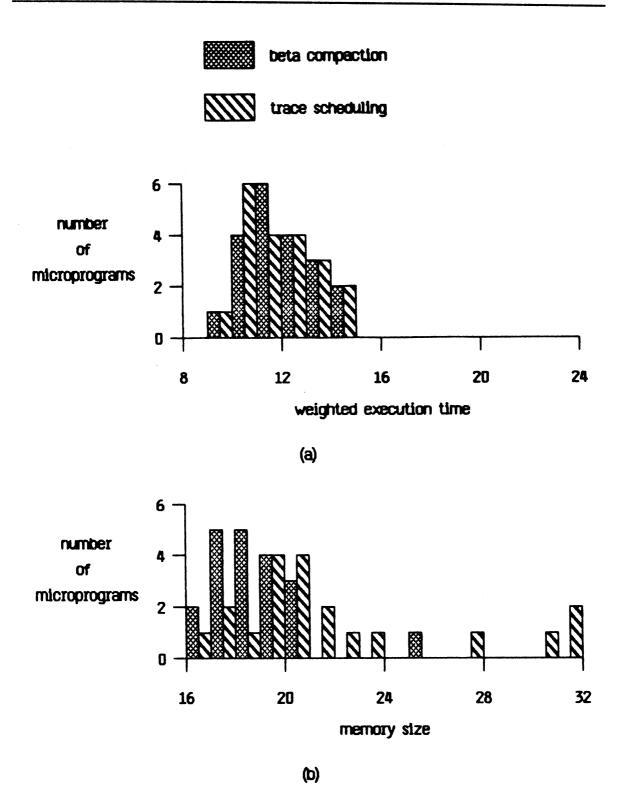

| 5.6         | Block diagram of the simulated system                       | 83         |

| 5.7         | Microinstruction format                                     | 84         |

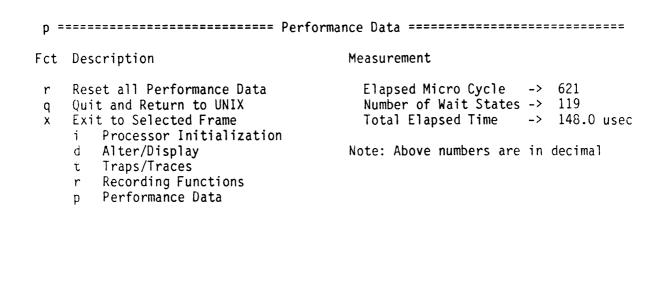

| 5.8         | Summary of 2-3 tree insertion program execution             | 87         |

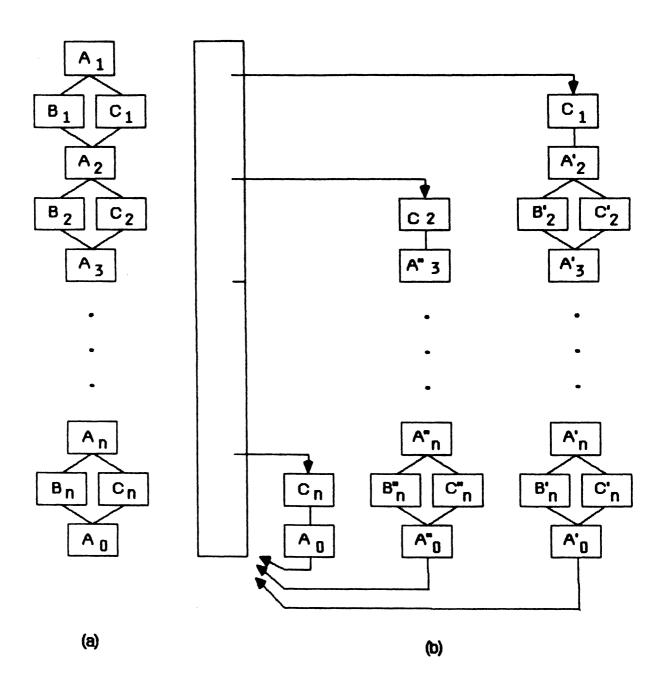

| 5.9         | Exponential memory growth in trace scheduling               | 88         |

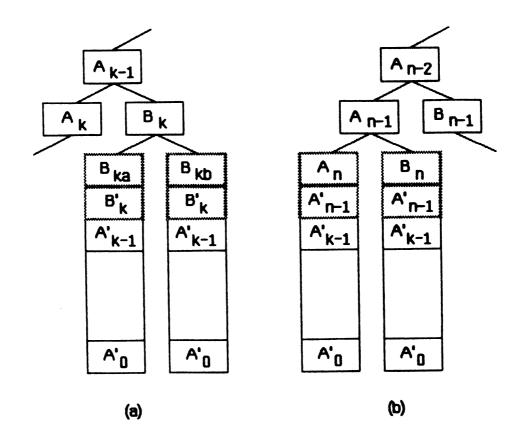

| 5.10        | Worst case in beta compaction                               | 91         |

| 5.11        | Calculation of memory size increase                         | 92         |

| A.1         | Processor initialization frame                              | 100        |

| A.2         | Trap/trace frame                                            | 101        |

| A.3         | Alter/display frame ( datapath subframe )                   | 102        |

| A.4         | Alter/display frame ( pipeline register subframe )          | 103        |

| <b>A</b> .5 | Alter/display frame ( control store subframe )              | 104        |

| A.6         | Alter/display frame ( main store subframe )                 | 105        |

| A.7 | Alter/display frame ( trace table subframe ) | 106 |

|-----|----------------------------------------------|-----|

| A.8 | Recording frame                              | 107 |

| A.9 | Performance data frame                       | 108 |

## LIST OF APPENDICES

## **Appendix**

| A. | The simulator functions and human interface    | 98  |

|----|------------------------------------------------|-----|

| B. | Pascal listing of 2-3 tree insertion algorithm | 109 |

| C. | AMDASM listing of 2-3 tree insertion algorithm | 116 |

## LIST OF ABBREVIATIONS

MO Micro operation

MI Micro instruction

DDG Data dependency graph

SLM Straight line microcode

CI Complete instruction

DRS Date ready set

EP Early partition

LP Late partition

CP Critical partition

#### CHAPTER I

#### INTRODUCTION

Since Maurice Wilkes first introduced the concept of microprogramming in 1951 [WIL51], the use of the microprogram has increased continuously as the demand for and support of computer technology have increased. Increasing complexity of digital systems requires more complex microprograms. Decreasing high speed memory cost and emerging development tools help meet the requirement.

However, until recently microcode was produced with little help of development tools. The only practical tool available to many microprogrammers was an assembly-like bit stuffer using mnemonics. The microcode was written by someone who had a thorough knowledge of the machine to be programmed. The microprogramming was considered a part of the hardware design and so it was often done by the hardware designer. And once developed, the microcode was not touched except to fix bugs. Those microcode developments were manageable by a few specialists with little help from development tools, mainly because the microcode was relatively small in size and less complex.

However, things have changed. With the introduction of writable control store and user microprogramming, the need for better microprogramming tools is higher. And increasingly complex digital systems and the advent of VLSI are increasing the use of microprograms. Design time for VLSI systems depends on sophisticated design aids for hardware and microprogramming. VLSI hardware and microcode design problems are large and technology-dependent; humans alone cannot handle the detail and explore all the alternatives involved in correct

optimal design [PAR81]. VLSI technology has also reduced the cost of high-speed memory available, so the size of micromemory has become less of a constraint and the microprogramming of some special purpose processors involves larger microcodes than conventional macro instruction emulation. All these changes are making it more critical to have better tools in microprogramming.

The eventual goal of microprogramming tool development would be to make a high level language and a compiler to generate minimal-execution-time microcode for a wide variety of machines. There have been various attempts to design and implement higher level languages for microprogramming but none of these has resulted in the production of a generally available compiler. Several proposed high level microprogramming languages are reviewed in [SIN80]. Even though the same pressure that has led to the widespread acceptance of conventional high level languages now applies to microprogramming [DAV78], the development of microprogramming languages lags far behind that of macroprogramming languages. There are a couple of factors which complicate compilation to microcode.

First, the structure of horizontal<sup>1</sup> microcode is much more complicated than that of conventional machine code. In horizontal microarchitecture, a microinstruction contains several microoperations which directly control parallel hardware resources. The microoperations contained in one microinstruction are executed at the same time. Accordingly, the detection of available parallelism and scheduling microoperations are very difficult. Timing can be very complicated. Certain microoperations require different clock phases than others or might take more than one clock cycle. If some degree of ( if not total ) machine independence is sought, generating equally fast-executing microcode for different machines is an extremely different task.

Second, in most microprogramming environments, minimal-execution-time microcode is very important. In particular, when the microprogram is used to

<sup>&</sup>lt;sup>1</sup> See the definition in chapter II.

emulate macroarchitecture, the efficiency of the whole systems ultimately depends on the efficiency of the microprograms implementing the instruction set of the macromachine. The user microprogram (of non-emulation application) may allow less strict efficiency requirements. But the only reason that a user would want to write microcode is to gain speed. If the compiler cannot generate sufficiently fast-executing microcode, it is of no use.

One of the critical issues in developing a high level microprogram language is how to generate minimal-execution-time microcode. As machines have more concurrency available in datapath at the register transfer level, it is particularly important to efficiently control all the available parallel resources. It is a common belief that microcode generated by a machine (or a compiler) cannot be executed faster than one written by a highly skilled microprogrammer, but as the size of microprograms grows, it becomes beyond human intelligence to handle all opportunities to optimize a microprogram [PAT76].

In generating minimal-execution-time microcode, one aspect that differentiates microprogramming languages from macroprogramming languages is the need for compaction in highly horizontal microarchitecture. Microprogram compaction is the process of exploiting parallelism to combine microoperations (MO's) into microinstructions (MI's) to reduce the time and/or space needed for the execution of a microprogram. In solving microprogram compaction problems, optimality is pursued but not necessarily arrived at, since the microprogram optimization (optimal compaction) problem has been proved to be NP-complete both in microword dimension [DEW76] and in bit dimension [ROB79].

The microprogram compaction problem has been approached in two ways: local compaction and global compaction. Local compaction deals only with a straight line microcode (SLM) section also known as a basic block. A SLM is a sequence of MO's with no jump into the microcode except at the beginning, and no jump out except possibly at the end. Global compaction deals with microprograms which have more than one basic block with conditional jumps, joins, and

loops.

Several methods have been proposed to solve the local compaction problem, and they are reviewed in an article by Landskov et al [LAN80]. The same group of people ran some experiments with the methods and reported the results in [DAV81] and claimed that the local compaction problem is considered to be essentially solved. However, Vegdahl presented an algorithm in his thesis [VEG83] which showed that the classical compaction problem, which does not consider reordering of source MO's, can be solved in  $O(n^{v})$ , where v is a bounded number of registers in the machine. And so, Vegdahl conjectures, the problem of finding a semantics-preserving partial ordering which yields optimum compaction is a more difficult problem, because the general compaction problem - that is, the problem that considers all semantics-preserving partial orderings - is still NPcomplete even with the bounded-register assumption. Here we are dealing with the classical compaction problem and do not consider reordering of source MO's. Even though the problem can be solved in polynomial time, the order which is equal to the number of registers in the hardware is, in most cases, so high that one is justified in using heuristics, which has low order (usually  $O(n^2)$ ) polynomial time complexity. Several methods to solve the local compaction problem, including Vegdahl's thesis results, are reviewed in section 3.1.

Four methods have been proposed to solve the global compaction problem [DAS79, WOO79a, TOK78, TOK81, FIS79, FIS81a] as summarized in [FIS81b]. Also, a recent paper by Isoda [ISO83] has proposed another approach, which uses a generalized data dependency graph.

The trace scheduling by Fisher [FIS79, FIS81a] is the most general method and appears to give the fastest execution of compacted microcode. Although Fisher's trace scheduling procedure for global compaction may produce significant reduction in execution time of compacted microcode, the growth of memory size by extensive copying of blocks can be enormous. In the worst case, the memory

size can grow exponentially<sup>2</sup> [FIS81a], and the complex bookkeeping stage of the trace scheduling is an obstacle to implementation.

In [FIS81a], Fisher suggests modifications to mitigate the memory growth effect. These modifications are based upon selection of a probability threshold below which (with some exceptions) MO's are not allowed to move across block boundaries. Both memory size and execution time appear to be very sensitive to changes in the source microcode. See section 3.2.3 for further discussion of the modifications. A few methods to solve the global compaction problem are reviewed in section 3.2.

In this dissertation a technique called beta compaction, based on trace scheduling, is proposed to mitigate the drawbacks of trace scheduling. Basically, it identifies the junction blocks ( the blocks beginning with a join and ending with a conditional branch ) as the major source of complication, divides traces at those junction blocks, and compacts each divided trace separately. It achieves almost all the compaction of the Fisher's trace scheduling except that which causes copying of blocks. An earlier effort to correct the drawbacks of trace scheduling called tree compaction is reported in [LAH83].

A loop-free version of both beta compaction and trace scheduling has been implemented. Comparison between the two was done using some synthesized microcodes and it was confirmed that the beta compaction generates almost as fast-executing microcode as the trace scheduling but with much less memory.

A microprogrammable machine based on AMD2900 components was designed and simulated with an interactive interface. A realistic application programs was written and hand-compiled into microcode. The microcode was executed on the simulator both before and after compaction, to demonstrate the applicability of the compaction technique and the informal correctness of the implementation.

<sup>&</sup>lt;sup>2</sup> One such example is shown in section 5.6.1.

Chapter II presents a simple microprogram model and definitions of the terms which are used throughout the thesis. Chapter III reviews some work done previously in the area of microprogram compaction including local compaction and global compaction. Chapter IV and Chapter V are the core of this thesis. Chapter IV presents a detailed description of the beta compaction which are developed to solve the global compaction problem. It also gives one illustrative example to show the actual working of the heuristic. Chapter V reports two experimental results. First, the comparison of beta compaction against the trace scheduling using an artificial microcode model is presented. Second, compaction of an application program and its execution on a simulated machine is described. At the end of the chapter, exponential memory growth of the trace scheduling and the worst-case space complexity analysis of the beta compaction are shown. Chapter VI summarizes the dissertation and suggests some future research.

Throughout the dissertation a few abbreviations of terms are used to make sentences short and clear. The abbreviations are listed at the beginning of this document.

#### CHAPTER II

#### A MODEL OF A MICROPROGRAM

The purpose of this chapter is to present a microprogram model which will be used in later chapters of the thesis. A part of the model is based on D. Landskov et al [LAN80]. The model is to satisfy the minimum requirement of allowing presentation of the essential concepts of the microprogram compaction heuristics with clarity. Since this is the basic model, many extensions are possible. Some of them will be discussed along with the basic model.

**Definition:** A microinstruction (MI) is an ordered set of all control signals in a machine at a given (quantized) time.

Definition: A microprogram is a time-ordered sequence of MI.

**Definition:** Each separate machine activity specified in an MI is called a microoperation (MO).

Thus an MI can be characterized as a set of MO's and the MO is the basic unit of operation that we are dealing with. In some literature [MAL78,LAN80], microbundle (MB) is defined as a set of MO's, all of which are coupled to one another. Thus every MO in an MB must go into the same MI. The concept of bundling can be useful in dealing with MO's which operate on transitory data storage.

The most common classification applied to microinstruction formats is to describe them as horizontal or vertical [SAL76]. The horizontal and the vertical are relative terms used to indicate the degree of encoding in microinstruction

formats. There are two extremes, totally horizontal and totally vertical, and many variations in between. The highly horizontal microinstruction format would have a sufficient number of separate control fields to exercise simultaneous control over all independent hardware facilities, with encoding limited to mutually exclusive control signals. The highly vertical microinstruction format, on the other hand, would have a high degree of encoding and, in many ways, resembles conventional machine instruction. We will use the terms horizontal and vertical to indicate highly horizontal and highly vertical, which include not only extremes but some neighborhood of the extremes.

**Definition:** Microprogram compaction is the process of exploiting parallelism to combine MO's into MI's to reduce the time and/or space needed for the execution of a microprogram.

The vertical MI's, in a strict sense, specify only a single MO to be performed in each MI. Therefore vertical microprogramming allows no room for microprogram compaction. Horizontal microprogramming is implied throughout the discussion of microprogram compaction.

**Definition:** A straight line microcode (SLM) is an ordered set of MO's with no entry point, except at the beginning, and no branches, except possibly at the end.

Microprogram compaction which deals only with a single SLM at a time is called local compaction. Microprogram compaction which deals with more than one SLM, where SLM's are connected with each other through conditional branches, joins or loops, is called global compaction. In local compaction, the execution time of compacted microcode is reduced by reducing the number of compacted MI's. However, in global compaction, simply reducing the total number of compacted MI's does not necessarily reduce the execution time of the compacted microcode because the probabilities of SLM's being executed are different. It is possible, in global compaction, that a microcode with larger size is executed faster than a microcode with smaller size for some data set.

#### 2.1. Data Dependency Analysis

In the process of microcode compaction, a given sequence of MO's are placed into a sequence of MI's where an MI may contain one or more MO's. Although the original order of MO's is invariably changed, we want the original semantics of the microcode retained and the data integrity not violated after the compaction. To accomplish these we need to analyze data dependency between MO's.

The following definitions about data dependency are made only with respect to a SLM or a trace. A trace is a sequence of blocks and MO's in the blocks are treated as if they form a SLM for the purpose of data dependency analysis. The trace will be defined in sec. 2.3. The definitions of data dependency can be extended to include any program structure [ISO83].

**Definition:** In a given sequence of MO's mo<sub>1</sub>, mo<sub>2</sub>, ..., mo<sub>i</sub>, ..., mo<sub>i</sub>, ..., mo<sub>t</sub>, we say mo<sub>i</sub> and mo<sub>j</sub> have a *data interaction* if they satisfy any of the following conditions.

- (1) An output resource of mo<sub>i</sub> is also an input resource of mo<sub>j</sub>.

- (2) An input resource of moi is also an output resource of moi.

- (3) An output resource of mo; is also an output resource of mo;

To maintain data integrity, the order of any two MO's cannot be changed if they have a data interaction. Using the definition of data interaction, we can define a partial ordering over the MO's.

**Definition:** Given two MO's mo<sub>i</sub> and mo<sub>j</sub>, where mo<sub>i</sub> precedes mo<sub>j</sub> in the original SLM, mo<sub>j</sub> is directly data dependent on mo<sub>i</sub> ( written mo<sub>i</sub>  $\rightarrow$  mo<sub>j</sub> ) if the two MO's have a data interaction and if there is no sequence of MO's, mo<sub>k1</sub>, mo<sub>k2</sub>, ..., mo<sub>kn</sub>,  $n \ge 1$ , such that mo<sub>i</sub>  $\rightarrow$  mo<sub>k1</sub>, mo<sub>k1</sub>  $\rightarrow$  mo<sub>k2</sub>, ..., mo<sub>kn</sub>, mo<sub>kn</sub>, mo<sub>kn</sub>  $\rightarrow$  mo<sub>j</sub>.

The second part of the definition ensures that two directly data dependent MO's will have no other chain of directly data dependent MO's between them.

Data dependency is the transitive closure of the direct data dependency relation.

Definition: The partial ordering over MO's defined by direct data dependency can be represented by a directed acyclic graph. We call this the data dependency graph (DDG). Each node on a DDG corresponds to a MO. An edge on a DDG from a node i corresponding to mo<sub>i</sub> to a node j corresponding to mo<sub>j</sub>, indicates that mo<sub>j</sub> is directly data dependent on mo<sub>i</sub>.

Vegdahl adopted the definition of data antidependency from Banerjee et al. [BAN79] and used that as a basis for his analysis.

**Definition:** If MO may destroy data that is required by another MO, the former is said to be data antidependent on the latter.

This is the case (2) of our definition of data interaction. For further discussion of data antidependency and Vegdahl's analysis, see section 3.1.5.

#### 2.2. Host Machine Description

Besides data dependency among MO's, there is another restriction that has to be considered in microprogram compaction which is imposed by the host machine itself. If two MO's require exclusive use of a single resource, they cannot be placed into the same MI. The situation is called a resource conflict. To handle the resource conflict, we need a model to describe the host machine resources seen by the microprogram. Even though two MO's require separate resources, they may not necessarily be placed in the same MI because, as a result of partial encoding, the two MO's use the same MI field. The situation is called a MI field conflict. In the case of totally horizontal microinstruction, the MI field conflict does not exist because each resource in the hardware has its own control field in the MI. Therefore, the resource conflict and the MI field conflict are equivalent in totally horizontal microcodes. To simplify the discussion, we will assume a

totally horizontal MI format without losing generality. It would then be straightforward to extend our discussion to handle partially encoded microcodes. We now present a model of a machine control word which includes a simple description of the host machine resources.

Definition: An MO is represented by a six-tuple (label, instruction, next-address, destination-registers, source-registers, resource vector). The label is a number to identify each MO, the instruction is a command to the microsequencer (microaddress controller), for example, CONT, CJMP, GOTO, etc., and the next-address is a target address for a branch. The destination-registers and the source-registers are the registers written and read respectively in a given MO. A resource vector is a vector in which each component corresponds to an individual resource available in the hardware. The value of each component is either 1 or 0 depending on whether the corresponding resource is used in a given MO.

The resource vector gives a necessary description of the host machine resources to detect and resolve the resource conflicts.

Other models used in the literature [LAN80, DAV81, TOK81], which were intended for local compaction, do not have sequencer instructions and branch addresses. On the other hand, they have a set of clock phase required for MO execution and a set of all MI fields required by the MO. It would be straightforward to add these attributes to our model as necessary.

**Definition:** A register is alive at some point in a program if its contents will be read in the future prior to being overwritten. Otherwise, the register is dead.

### 2.3. Microprogram Description

A loop-free program can be represented as a connected directed graph with one node of in-degree zero (entrance) and one node of out-degree zero (exit). For programs with multiple entry points, a dummy entry block from which execution is branched to the actual entry points, is added to comply to the above rule. Similarly, a dummy exit block is added for programs with multiple exit points.

**Definition:** A trace is a set of blocks which forms a path of execution and has higher probability of execution than any other path in a given microprogram or a part of it.

Definition: A weighted execution time of a microprogram is the sum of execution time of each block multiplied by the probability of that block executing.

#### CHAPTER III

#### PREVIOUS RESEARCH

Previous research attempts to solve the microprogram compaction problem has been approached in two different ways: local compaction and global compaction. Earlier attempts concentrated on what is now known as local compaction, which schedules MO's within block boundaries. First, it was attempted to find an optimal solution<sup>3</sup> [YAU74] only to find out that the algorithm was exponential in complexity. So efforts were directed to finding reasonable heuristics. It was later proved that the microprogram optimization (optimal compaction) problem is indeed NP-complete both in microword dimension [DEW76] and in bit dimension [ROB79]. Four different heuristics have been proposed to solve the local compaction problem and are reviewed in [LAN80].

More recently, in an effort to get more efficient microcode, the compaction was tried not only among MO's within each block boundary but also among MO's beyond block boundaries. This is now known as global compaction. The global compaction of microprograms has been an active research area for the last five years or so and several heuristics have been proposed.

<sup>&</sup>lt;sup>3</sup>Note that in a straight line microcode, getting the minimum microcode size is equivalent to getting the minimum execution speed of the microcode.

#### 3.1. Local Compaction

In [DAV81], the same group of people who reviewed four local compaction heuristics in [LAN80] reported the experimental result on these heuristics and claimed that the local compaction problem was essentially solved. Based on the experimentation, they recommended first-come first-serve ( see Section 3.1.1 ) with some modification and list scheduling ( see Section 3.1.4 ).

However, Vegdahl revisited the local compaction problem again in his thesis [VEG83] and proved that the *classical* local compaction problem, which does not consider reordering of source MO's, is not NP-complete, but polynomial in complexity. He presented such an algorithm.

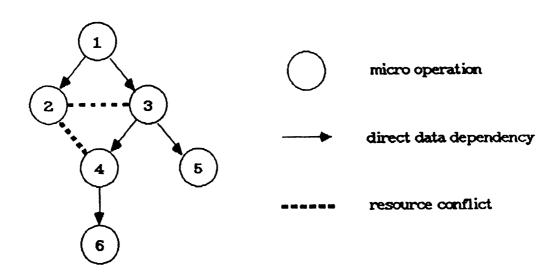

In this section, four local compaction heuristics are briefly reviewed and Vegdahl's thesis results are discussed. In describing the heuristics, we will use one simple example to enhance understanding. The DDG of the example microcode is shown in Figure 3.1. The circled numbers represent microoperations.

Figure 3.1 Data dependency graph of example microcode

The arrows indicate the direct data dependency relation between MO's. The dotted lines are used for convenience to indicate resource conflict between MO's. We will show the working of each heuristic on the same sample microcode along with the description of the heuristic itself.

#### 3.1.1. First-Come, First-Serve

The first-come first-serve heuristic described by Dasgupta and Tartar [DAS76] operates on a straight line microcode (SLM) which is in the form of a list of MO's. MO's from the SLM are added, in the order in which they appear on the list, to an initially empty list of MI's. Here is the outline of the heuristic.

```

for each MO do

{

Determine the rise limit of the MO by searching MI's from bottom to top using data dependency.

Place the MO in the first MI which has no resource conflict with the MO, starting from the rise limit to the last MI

if the MO is not placed, create a MI at the bottom to hold it.

}

```

The detail procedure follows.

The search for an existing MI to which the current MO can be added begins with a data dependency analysis. Starting at the bottom of the MI list and proceeding upward, examine each MI if the MO under current consideration is not data dependent on any MO in that MI. If the current MO is data dependent

on an MO in the *i* th MI, the current MO cannot be placed in any MI earlier than *i* or *i* itself. The object of this search is to find the earliest (highest) MI in which the new MO can be placed without violating the ordering imposed by the data dependencies in the SLM. This MI is called the *rise limit*.

The next step in the search for an existing MI is the examination of resource conflicts. To be placed in a MI, the current MO must not conflict with any MO already in that MI. Assuming that a rise limit i was found, search downward in the list, starting with MI i, for some MI in which the new MO can be placed. When such a MI is found, add the new MO. If no such MI is found, add the new MO to the end of the MI list, thus forming a new MI containing only one MO.

If no rise limit was found, then the current MO was not data dependent on any MO in the MI list, and the MO can be added to any MI with which it has no conflicts. In this case begin the downward search at the top of the MI list. If

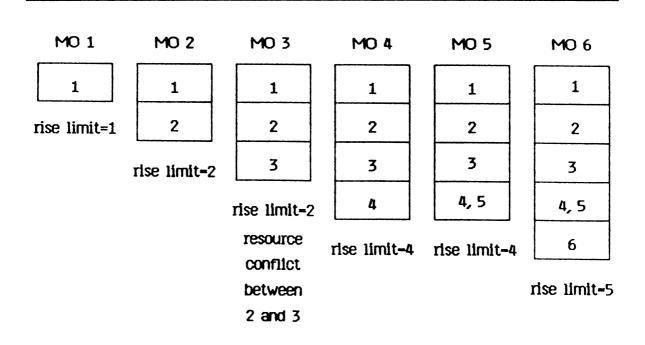

Figure 3.2 The working of first-come first serve

there are no MI's to which the MO can be added without conflict, use the MO to form a new MI at the top of all the other MI's. Placing this MO at the top will keep it from blocking any new MO's that depend on it.

Figure 3.2 shows the working of the first-come first-serve heuristic on the sample microcode. Each column shows the placement of one MO as indicated on top. The boxes represent MI's. The rise limit is shown for each MO. After MO 1 is placed, the rise limit for MO 2 is 2 because of data dependency. Even though the rise limit of MO 3 is also 2, it can not be placed in the same MI with MO 2 because of resource conflict between MO 2 and MO 3. The remaining MO's are placed similarly and the result is five MI's.

#### 3.1.2. Critical Path

The critical path heuristic for microcode compaction was introduced by Ramamoorthy and Tsuchiya [RAM74]. This critical path heuristic attempts to identify MO's that must be executed at a certain time in order for the list of MI's to be optimal. The MO's chosen are those which are on a longest path ( the critical path ) through the DDG. As noted, the minimum possible number of MI's is just the length of the longest path. Here is the outline of the heuristic.

Determine early partition

Determine late partition

Determine critical partition

Revise the critical partition

Place non-critical MO's

The detailed description of each step follows.

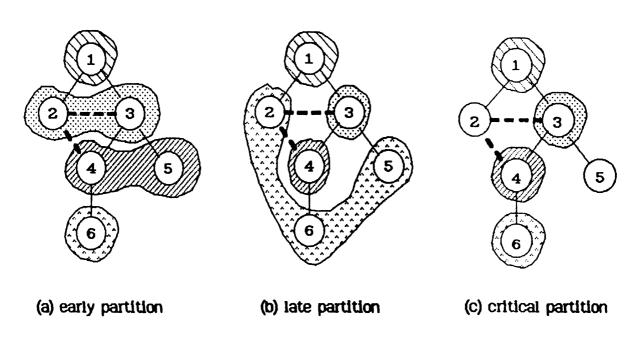

The first step is to create an early partition (EP). Each time frame of the EP contains those MO's that can be executed in that time, at the earliest. So

starting from the first time frame, fill in each time frame with all executable MO's and if there is no more executable MO's, then go on to the next time frame. A MO must be placed in the time frame of the EP after the frame of its latest ancestor. Data dependencies alone determine the placement of MO's in the EP. Conflicts will be resolved later. The early partition of the sample microcode is shown in Figure 3.3(a). Each different shading indicates a separate time frame.

The next step is the creation of a late partition (LP). In the LP the latest possible timings of the MO's are considered. Each time frame of the LP contains those MO's that can be executed in that time, at the latest. It starts from the MO for which no other MO is data dependent and goes on to the one earlier time frame and fills it with all MO's for which no other MO is data dependent but those which are in the later time frame. If the data dependency graph is represented by a matrix, the LP can be created by applying the EP algorithm to the transpose of the graph matrix. The construction of the LP resembles the

Figure 3.3 The working of critical path

construction of the EP in reverse. The late partition of the sample microcode is shown in Figure 3.3(b).

The construction of these partitions facilitates the identification of MO's on the critical path of the DDG. These MO's, called critical MO's, are just those with the same timing in both early partition and late partition. It is called a critical partition (CP). The critical partition of the sample microcode is shown in Figure 3.3(c) by the shaded nodes.

Since the CP was constructed by considering only data dependencies between MO's, two MO's in the same frame of the CP may conflict. And since the frames of the CP will serve as a basis for MI's in the list of MI's, conflicting MO's in a frame must be separated. The result of separating all the conflicting MO's in each frame is called the *revised critical partition* (RCP). The separated frame forms subframes. The revised critical partition of the sample microcode happens to be the same as the critical partition shown in Figure 3.3(c). In other words, in this particular example, the critical partition contains no time frame which contains two conflicting MO's.

Figure 3.4 Result of critical path

The next and final step of the heuristic is to add the noncritical MO's to the RCP, forming the final list of MI's. For each noncritical MO, we search the RCP from the frame containing the MO in the EP to the frame containing the MO in the LP for a MI to which the noncritical MO can be added. If the MO cannot be added to any of the frames within this range, a new subframe is created. The final result of critical path heuristic on the sample microcode is shown in Figure 3.4 after placing non-critical MO's 2 and 5.

#### 3.1.3. Branch and Bound

The third method of solving the local compaction problem is branch and bound (BAB), a general class of tree-searching scheduling algorithms. Yau, Schowe and Tsuchiya [YAU74] were the first to describe the application of this technique to microcode compaction.

In BAB, a tree is built, the nodes of which correspond to microinstructions. A path from the root of the tree to a leaf is an ordering of MI's, and thus a list of MI's. The tree will branch whenever there is more than one MI that can be placed at a point in the list of MI's. A complete tree represents every possible MI ordering.

There are two variants of this algorithm. The first is BAB exhaustive, in which every branch of the tree that can possibly lead to an optimal MO ordering is explored. The other is BAB heuristic, in which pruning is done to the tree. BAB exhaustive is an optimal algorithm, and running in exponential time, while BAB heuristic is not guaranteed optimal and can be made to run in polynomial time.

The growth of the tree can be bounded even in BAB exhaustive. As in the other algorithms, calculate the lower bound on the number of MI's in the best possible ordering. (Remember that this is the longest path through the DDG.)

A path through the BAB tree of this length represents an optimal ordering, and the algorithm can stop once such a path is obtained. The growth of the tree can be further bounded by remembering the length of the best (shortest) path found so far. If the length of an incomplete list of MI's is greater than or equal to this length, the current path needs no further consideration.

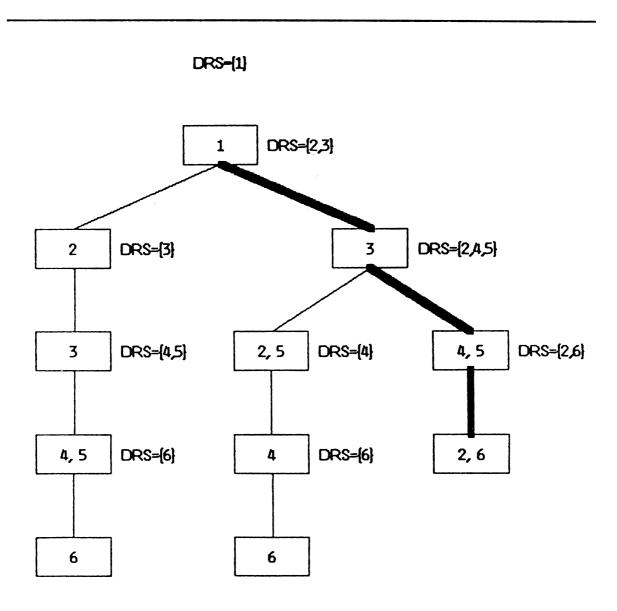

Definition: data ready set (DRS) is the set of all unplaced MO's that are not data dependent on any unplaced MO.

**Definition:** complete instructions (CI's) is defined as an instruction to which no other MO's in the DRS can be added. Thus a CI is not a subset of any other legal MI given a DRS.

The outline of the BAB exhaustive algorithm is presented here using a recursive function.

```

form initial data ready set;

call FormCI;

procedure FormCI

{

form all possible Complete Instructions;

for each Complete Instruction do

{

form new data ready set;

if data ready set is not empty

call FormCI;

}

}

```

A more detailed description of the algorithm follows.

Like the critical path heuristic, the BAB algorithm gets its information on the data dependencies of MO's of an SLM through a DDG. The first step of the BAB exhaustive algorithm is the construction of a DRS. The contents of the DRS change as execution of the algorithm progresses. The initial DRS contains just those MO's not data dependent on any other MO.

Figure 3.5 Working of branch and bound exhaustive

The next step is to form MI's from the MO's in the DRS. We wish to form only the largest possible MI's. These are called CI's. CI's make up the nodes of the BAB tree so that a path through the tree is a list of CI's or a list of MI's. For the detailed algorithm of forming CI's, see [LAN80] Sec. 3.

Now, for each CI, compute a new DRS and form the next CI's which will make branches from the previous node (or CI). Repeat this for all the branches until there is no more MO's left.

Figure 3.5 shows working of the BAB exhaustive algorithm on the sample microcode in Figure 3.1. It starts with the initial DRS which contains just MO 1. So there is only one CI with MO 1, which is shown in the box. The next DRS after the CI is shown on the right side of the CI box. From the DRS of { 2, 3 }, two CI's are formed; namely one with MO 2 and the other with MO 3. The two CI's make two branches in the graph. The process continues similarly until all possible branches are considered. The shortest path from the node to a leaf, which is indicated with thick lines, represents the optimal solution.

#### 3.1.4. List Scheduling

The list scheduling can be considered a special case of the BAB heuristic but it is important in its own right. The heuristic used in the list scheduling is as follows.

Instead of examining every complete instruction generated from a DRS, examine only the best CI, where the best CI is determined by some metric. The outline of the list scheduling, shown below, is very similar to that of the BAB exhaustive shown in Section 3.1.3.

```

form initial data ready set;

call FormCI;

procedure FormCI

{

form best complete instruction;

form new data ready set;

if data ready set is not empty

call FormCI;

}

```

The only difference is that inside the procedure FormCI, one best CI is formed and considered instead of examining all possible CI's. This heuristic requires only an amount of time that grows polynomially with the number of MO's in the SLM. The metric used in forming the CI affects the optimality of the compaction. Extensive test of different metrics were reported by Fisher [FIS79]. In the test, the metric used by Wood [WOO78] was shown to be one of the best and is presented here.

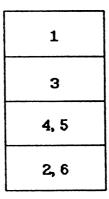

Assign a weight to each MO in the DDG. The weight of an MO is the number of levels of descendants of that MO in the DDG. The execution of the heuristic proceeds as follows. Compute a DRS from the DDG. Find the MO in the DRS with the highest weight. Add it to the MI, which is initially empty. Then find the MO with the second highest weight in the DRS. If this MO does not conflict with any MO already in the MI, add it. Otherwise, consider the MO with the next highest weight. Repeat until all the MO's in the DRS have been examined. The resulting MI is the CI with the highest weight. Add this MI to the list of MI's and compute a new DRS. Repeat until all of the MO's in the SLM have been placed.

Figure 3.6 shows the DDG of the sample microcode with the weight of each MO indicated outside of circles. The working of the list scheduling is the same as

Figure 3.6 Weight of MO's for list scheduling

the optimal path of the BAB exhaustive shown in Figure 3.5 with dark lines. From the DRS of { 2, 3 }, MO 3 is selected since its weight of 2 is higher than the weight of 0 of MO 2. From the DRS of { 2, 4, 5 }, MO 4 is selected for the same reason. Then MO 5 is placed in the same MI while MO 2 is not because of resource conflict with MO 4. The forming of the last MI is obvious.

One last note on this example microcode. Keep in mind that this is just one very specific example. The fact that the first-come first-serve heuristic did not get the optimal solution while the others did does not necessarily indicate inferior performance of first-come first-serve or superior performance of the others. As noted at the beginning, the test result by Landskov et al. [LAN80] recommended first-come first-serve with some modification and list scheduling.

## 3.1.5. Vegdahl's Thesis

One of the contributions of Vegdahl's thesis is that he has shown that the classical microprogram compaction problem, which does not consider semantics-preserving reordering of source MO's, can be solved optimally in time  $O(n^r)$ , where v is the number of registers in the hardware, instead of in exponential time, although the order v of the polynomial may be very high.

**Definition:** A MO may require data that is produced by another MO. If this is the case, then the former is said to be *data dependent* on the latter.

Definition: A MO may destroy data that is required by another MO. If this is the case, then the former is said to be data antidependent<sup>4</sup> on the latter. [BAN79]

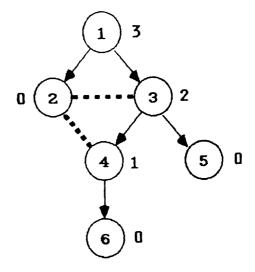

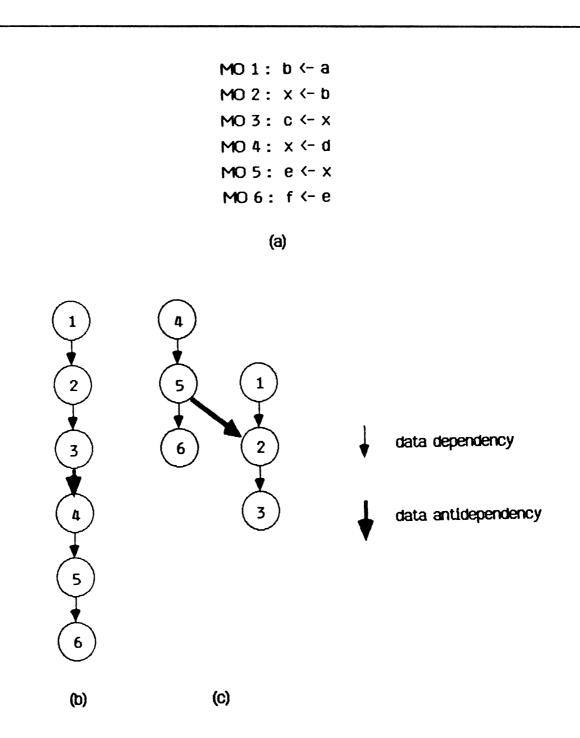

Vegdahl recognized that data antidependency should not be treated as data dependency in solving microprogram compaction problems, as demonstrated by the following example [VEG82]. Figure 3.7(a) shows an example, where register x is twice used as a temporary. Figure 3.7(b) shows one valid partial ordering of the MO's with data dependency and data antidependency among them. However, Figure 3.7(c) shows another valid partial ordering of the MO's with the same data dependency but different data antidependency. Clearly, the partial ordering shown in Figure 3.7(c) can yield less number of MI's when compacted.

Vegdahl contended that the problem of optimally ordering the MO's - and thereby determining the data antidependencies - is a more difficult problem than compaction. He then presented an algorithm, called a chain-matrix compaction algorithm, to optimally solve the compaction problem, once data antidependencies are specified. He concluded that the determination of data antidependencies is likely the more difficult problem, because the general compaction problem is NP-complete.

<sup>&</sup>lt;sup>4</sup> Note that data antidependency was defined as a part of data dependency in chapter II.

Figure 3.7 MO's with different data antidependencies

We now present a summary of the chain-matrix compaction algorithm from [VEG83]. For a complete description with an example, refer to [VEG82].

The MO's are first divided into v chains, each being placed in the chain corresponding to the register it writes. There is a strict ordering on the MO's in any chain - namely the order in which they appear in the source program. Each chain defines one dimension of a directed acyclic graph that is shaped as a v-dimensional matrix. The edges of the graph correspond to MI's; missing edges denote conflicting MI's. Each node in the graph represents a set of MO's; the node corresponding to matrix element <1,2,...> represents the set of MO's containing the first MO of chain 1, the first two MO's of chain 2, etc. Any node whose MO's violate a data dependency is removed. At this point, the problem is reduced to a single-source shortest path problem that can be solved using dynamic programming in time that is linear in the number of nodes.

### 3.2. Global Compaction

While the local compaction problem is concerned only with possible MO movements within each block boundary, methods for solving the global compaction problem attempt to achieve even more compaction by moving MO's over the block boundaries. This widened scope opens up a whole new set of issues. To name a few: When is it legal to move a MO to another block? What kind of provisions have to be made? How far can a MO move: just to adjacent blocks only, or further to over several block boundaries? How do we optimize overall performance, given that some blocks are more frequently executed than others? How much extra space is needed?

The global compaction problem is still considered an active research area. We present some of the previous works here and propose some improvements in the next chapter.

# 3.2.1. Wood [WOO79a, WOO79b]

This is one of the earlier attempts to compact MO's beyond block boundaries. It is an elegant and clean method even if somewhat restrictive. The basic idea is to allow MO movements among the same block level in a block structured microprogram.

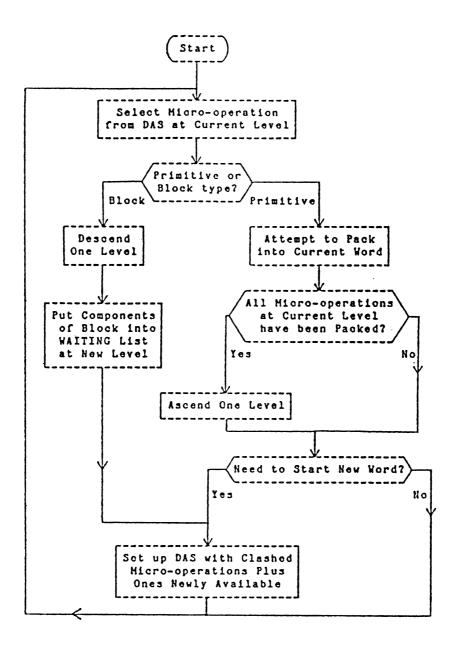

The big precondition of this work is that the source microcode has to be written in a block structured fashion, i.e., only if-then-(else) and (nested) loop structures are allowed. Given a block structured source microcode, the goal is to allow MO's to migrate over a conditional block, but not to let them land inside the block nor to allow any MO to migrate beyond the confines of its own block.

To achieve the goal, a concept of a hierarchy of levels of MO's within the microprogram is introduced. MO's may be of two basic types: a primitive MO which is an atomic entity, or a block-type MO which may be expanded at one level lower to a set of component MO's. These component MO's may, in turn, be either primitive or block type. A block-type MO represents a whole block of MO's which may be an if-then-else block or a loop block.

Using the MO's of these types, data dependency is defined between MO's at the same level as follows.

Multi-level dependency rule: If A and B are primitive MO's with A data dependent on B, then the outermost block containing A but not B should be marked as dependent on the outermost block containing B but not A.

The basic structure of the heuristic can be best described by Wood's own diagram [WOO79a], which is reproduced in Figure 3.8. In the figure, the term DAS (data available set) is used which has the same meaning with the DRS (data ready set). In selecting MO from DRS, block type MO's are selected first before primitive MO's are selected. So, the compaction starts at the lowest level block and works its way up. A separate DRS and waiting list is maintained for

Figure 3.8 Wood's compaction heuristic [WOO79a]

each level of MO's. The waiting list is a list of the MO's at that level which have not yet been made available for packing.

Even though this is a nice clean way of solving the global compaction problem, it is too restrictive and may not perform as well as the other methods. It does not allow many of the legal MO motions which will be discussed in the following sections.

# 3.2.2. Tokoro [TOK81]

Tokoro's approach to solving the global compaction problem is based on his identification of a set of rules of legal MO motions over the block boundaries. It is sometimes referred to as automated menu method. Even though the set of rules is very comprehensive and almost complete,<sup>5</sup> the proposed heuristic procedure to utilize these rules is rather ineffective.

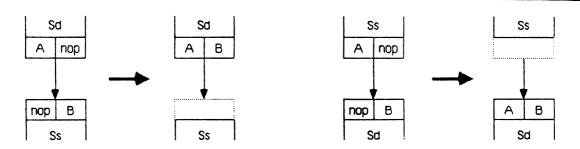

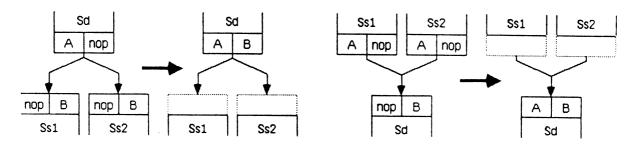

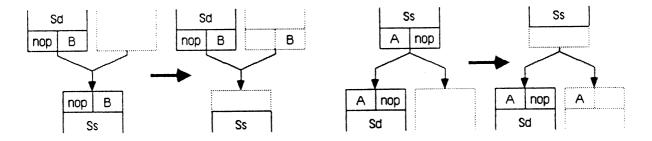

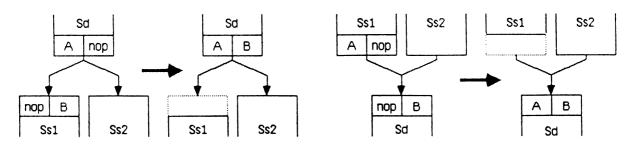

The pictorial representations of Tokoro's MO movement rules are reproduced from his paper [TOK81] in Figure 3.9. Note that the MO's in these figures are drawn at the edges of the blocks just to make the explanation of the concept simpler. In fact, MO's can be transferred from the inside of blocks and/or into MI's within blocks as long as data dependency relations are maintained. In Figure 3.9, A, B and nop (no operation) are MO's and  $S_s$  represents a source block and  $S_d$  represents a destination block. MO's are transferred from source blocks to destination blocks.

The simple transfer type optimization shown in Figure 3.9(a) and the common MO type optimization shown in Figure 3.9(b) are obvious and self-explanatory. A redundant MO is one in which all resources written by the MO are never referenced afterwards. The redundancy reduction type optimization shown in Figure 3.9(c) simply eliminates a redundant MO to save a cycle. The redundancy insertion type optimization shown in Figure 3.9(d) actually adds a redundant MO to one path without adding a cycle to make it possible to save a

<sup>&</sup>lt;sup>5</sup>Since Tokoro's rules deal only with MO motions between adjacent blocks ( he calls it contiguous segments ). MO movements over several blocks, the kind of MO migration described by Wood [WOO79b] ( see sec. 3.2.1 ) for example, are not allowed.

# (a) Simple transfer type optimization

# (b) Common micro-operation type optimization

# (c) Redundancy reduction type optimization

(d) Redundancy insertion type optimization

Figure 3.9 Tokoro's MO movement rules

cycle at the other path.

The detailed procedure to apply these rules, which will not be repeated here, is basically as follows. For each MO in each block, search for a possible move which can save a cycle by checking against all the rules. If such a move can be found, move the MO, otherwise select the next MO and repeat the entire search.

This automated menu method appears to suffer from the following shortcomings [FIS81a]. Each time a MO is moved, it opens up more possible motions. Thus, the automated menu method implies a massive and expensive tree search with many possibilities at each step. Evaluating each move means recompacting up to three blocks, an expensive operation which would be repeated quite often. To find a sequence of very profitable moves, one often has to go through an initial sequence of moves which are either not profitable, or, worse still, actually make the code longer. Locating such a sequence involves abandoning attempts to prune this expensive search tree.

# 3.2.3. Fisher [FIS79, FIS81a]

The trace scheduling appears to be the best proposed method to solve the global compaction problem. Its basic concept is nice and elegant and the available indications show that it gives good speed-up of execution time of compacted microcodes. However, in actual realization of the elegant concept, it gives some undesirable side effects which need to be corrected. And it is this correction process, called bookkeeping, that is nontrivial and complicated as will be described later.

In brief, trace scheduling proceeds as follows.

To schedule a given MO, we repeatedly pick the *most likely* trace from among the uncompacted MO's, build the trace DDG, and compact it. After each trace is compacted, some duplication of MO's into locations off

the trace is done to keep the semantics of the original microprogram unchanged. When no MO's remain, compaction has been completed.

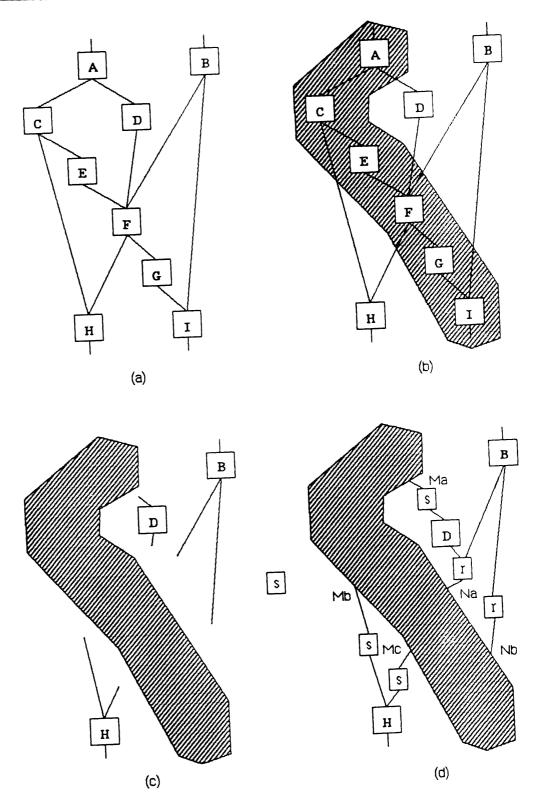

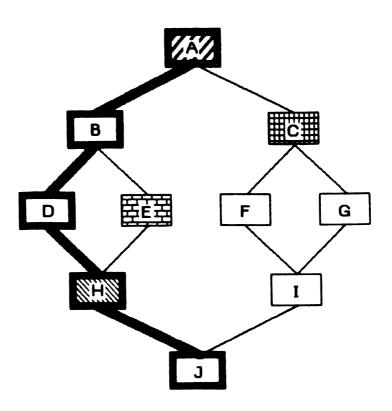

Figure 3.10 shows the basic steps of the trace scheduling. The figures are redrawn from [FIS82] with additional labeling to make it easier to explain. In Figure 3.10(a), each box represents a block of MO's and the lines between blocks indicate possible execution path. So the blocks with more than one line at the bottom are the blocks which end with a conditional branch. In Figure 3.10(b), the blocks covered by the shaded area are assumed to form a path with the highest probability of execution. In other words, the blocks form a trace. In Figure 3.10(c), after some preprocessing, the MO's in the trace are treated as if they belong to a single block and compacted using list scheduling. After the list scheduling is done on the trace, bookkeeping is necessary, which possibly includes massive copying of blocks.

First, let's consider repairing rejoins. Rejoin is a join in a trace to which an execution flow from a non-trace block is reached. When there were joins to the trace, we now must find a location in the new sequence of MI's to join to. MO's may have moved above and below the old join. We may only rejoin to places that have no MO's at or below them which had been above the old join, since we don't want to execute such MO's. When the highest point for rejoin is found, all MO's which had been below the old join but are now above the new rejoin have to be copied into the joining block. In Figure 3.10(d), blocks denoted by "R" are the blocks which contain the copied MO's because of repairing rejoins, and  $N_a$  and  $N_b$  are two newly found rejoining points.

Second, consider conditional jumps. Some MO's which were originally above a conditional jump on the trace may have been scheduled in an MI below the conditional jump. We must copy these MO's to the blocks that the conditional jump jumps to. If all registers written by the MO are dead at the beginning of

<sup>&</sup>lt;sup>6</sup>See conditional source registers

Figure 3.10 Fisher's trace scheduling

the block, then the MO does not need to be copied. In Figure 3.10(d), blocks denoted by "S" are the blocks which contain the copied MO's because of conditional jumps.

Up to this point, the bookkeeping stage is not overly-complicated. But here is the big question.

What if the rejoin  $N_a$  happens to be below the conditional jump  $M_c$  in Figure 3.10(d)?

In the original source microcode, the conditional jump was below the join but if the conditional jump is above the join, for the execution flow coming from the block B, the conditional jump does not exist any more. So the execution path of block B, block F and block H or the semantics of that path of the microprogram cannot be realized after the scheduling. To solve this problem, instead of rejoining block B to the trace, the blocks F, G, H and I are duplicated after the block B, as shown in Figure 3.11. This kind of block copying is the major source of complication and possible memory explosion.

To prevent possibly exponential growth of memory size, Fisher suggested modifications of trace scheduling [FIS81a].

- (1) If the block ends in a conditional jump, we draw a DDG edge to the jump from each MO which is above the jump on the trace and write a register alive in the branch.

- (2) If the start of the block is a point at which a rejoin to the trace is made, we draw DDG edges to each MO free at the top of the block from each MO which is in an earlier block on the trace and has no successors from earlier blocks.

Fisher recommended the above be used if the expected probability of a block's being reached is below some threshold. However, we suspect that there are some difficulties. First, the major source of extensive copying of blocks is

Figure 3.11 Copied blocks in the trace scheduling

from initial long traces which therefore have higher probabilities of being executed. Thus, fixing blocks with lower probability of being executed, after possibly extensive copying has already been done, helps relatively little. If, however, the threshold is raised to include blocks of high probability of execution, then it becomes close to compacting each block separately. Second, in long traces, the memory size growth is so sensitive to minor changes in source code that it is possible for one small change in source code to almost double the size of compacted code. The example microcode in section 5.6.1 has such sensitivity. Third, the bookkeeping stage which is the major source of complication remains to be the same.

#### CHAPTER IV

#### BETA COMPACTION ALGORITHM

Chapter III has reviewed several local compaction and global compaction techniques for microprograms. It is clear that global compaction gives better performance than local compaction, since some extra compaction over the block boundaries is done. Among the heuristics to solve the global compaction problem, trace scheduling appears to be the best proposed method so far. However, the trace scheduling has some serious drawbacks, as described in section 3.2.3. In particular, the kind of block copying shown in Figure 3.11, which can possibly cause memory explosion, may be unacceptable in many applications. Also, the bookkeeping stage of the trace scheduling is so complex that Fisher avoided a formal description of it in his paper [FIS81a] and later found a major bug during verification [NIC84].

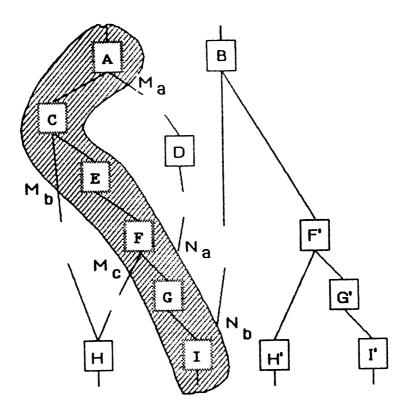

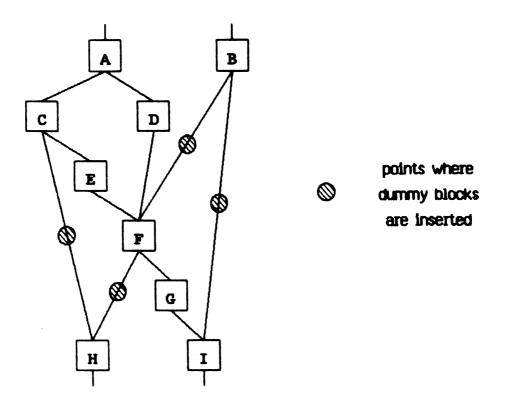

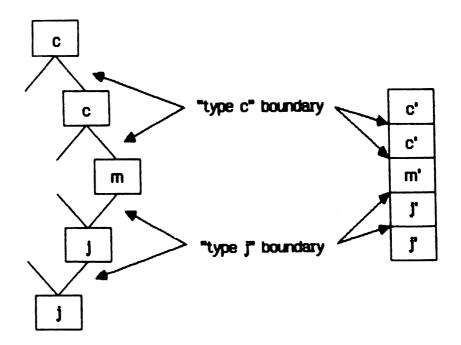

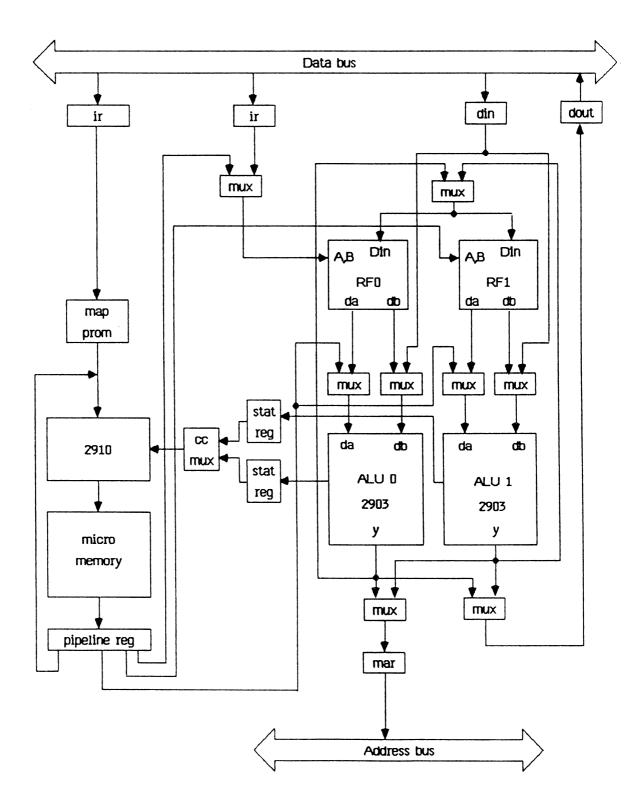

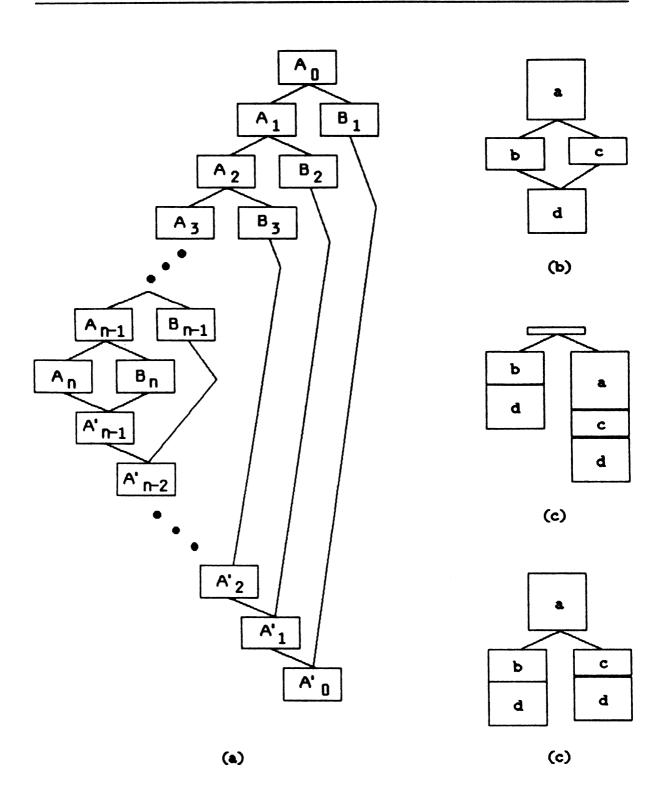

In Figure 3.10 of previous chapter, it can be seen that the reason for all the block copying is the fact that the rejoin  $N_a$  happens to be below the conditional jump  $M_c$  after the compaction of the trace. This can happen only around the block which has a join at the beginning and a conditional jump at the end, as shown in Figure 4.1. We call such block a junction block. Having recognized that junction blocks can cause the serious complication, we propose a modification on the trace scheduling to avoid the complication. The modification is to cut traces at each junction block. By making this modification, we not only prevent the kind of block copying shown in Figure 3.11, but also simplify the bookkeeping stage tremendously. Also, the worst case memory growth is reduced from exponential to  $O(n^2)$ . We call this improved trace scheduling a beta compaction.

Figure 4.1 Junction block

The beta compaction has all the above nice properties with very little trade off in compaction. It performs all the compaction that the trace scheduling does except that it does not allow MO movement across a junction block. MO's may still move into and out of junction blocks but MO's may not migrate across junction blocks. We conjecture that this kind of MO movement, which is allowed by trace scheduling, occurs very rarely, as will be shown experimentally in the next chapter.

## 4.1. Algorithm Description

Informally, the beta compaction algorithm proceeds as follows.

An entry block with highest probability is selected. Starting from the block, a trace is selected by following its descendant block of highest probability until it reaches an exit block or a junction block or an already compacted block. The blocks in the trace are treated as if they are a sin-

gle block, and compacted using list scheduling with copying of MO's as necessary. This process is repeated until all blocks are compacted.

A more detailed description follows. In Section 4.2, a working example of beta compaction is given.

## Input:

Sequence of MO's (label, instruction, next address, destination registers, source registers, resource vector).

## Output:

Sequence of MI's where each MI contains one or more MO's.

#### Procedure:

- (1) Initialization and preprocessing

- (2) Repeat until all blocks are compacted

Pick trace

List scheduling

Bookkeeping

}

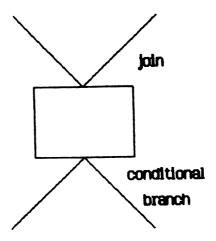

During the initialization and preprocessing, dummy blocks may be inserted wherever a conditional branch and a join directly meet as shown in Figure 4.2. These points are the only places where extra blocks may have to be created to hold copied MO's in the bookkeeping stage. Insertion of dummy blocks at the beginning totally eliminates the need to create blocks later. Empty dummy blocks after the compaction will simply be deleted.

Loops are handled the same way as they are in trace scheduling. The inner most loop is compacted first and the compacted loop is represented as a pseudo MO which contains all the data dependency information and serves as a MO in

Figure 4.2 Insertion of dummy blocks

the compaction of outer loop. Fisher proposed unwinding of loops in [FIS82] as a way to compact loops. In the beta compaction, similar loop unwinding is possible but, except for small inner loops, is probably too costly in space.

The next few sections will describe in detail the major steps of the beta compaction, including live register analysis. Here are a few definitions to help the description.

**Definition:** A tracehead set is a set of blocks in which each element of the set will make the beginning block of a trace.

**Definition:** Off-the-trace blocks are non-trace blocks which are the targets of conditional branches.

### 4.1.1. Live register analysis

The live register analysis is the process of determining which registers are alive at some point in a program. This information is necessary to allow as much compaction as possible without allowing illegal MO movement. Here we are interested in the live register information at the beginning and at the end of each block. The live register analysis is done once at the beginning as a part of the preprocessing and after new block boundaries are identified in the bookkeeping stage. It is also done every time a MO is copied from one block to another in the bookkeeping stage. The following summary is taken from [AHO77].

**Definition:** The depth-first-ordering of the nodes of a graph is the reverse of the order in which we last visit the nodes in the preorder traversal. Depth-first-numbers DFN(n) assigned to each node indicate the depth-first-ordering of the nodes.

**Definition:** IN[n] is the set of registers alive at the point immediately before block n and OUT[n] is the same immediately after the block.

**Definition:** DEF[n] is the set of registers which are assigned values in block n prior to any use of that register in the block n, and USE[n] is the set of registers used in block n prior to any definition thereof.

#### Input:

A set of blocks each containing a sequence of MO's.

## Output:

A list of live registers at the beginning and end of each block.

#### Procedure:

(1) Compute a depth-first ordering of the nodes. Let the nodes be  $n_1$ ,  $n_2$ , ...,  $n_N$ , such that  $DFN[n_i] = i$ .

```

for i := 1 to N do

begin

IN[n] := USE[n];

OUT[n] := empty;

end

while changes occur do

for i := n to 1 by -1 do

/* in reverse depth-first order */

begin

OUT[n<sub>i</sub>] := ∪ IN[s];

iN[n<sub>i</sub>] := (OUT[n<sub>i</sub>] - DEF[n<sub>i</sub>]) ∪ USE[n<sub>i</sub>];

end

end

```

### 4.1.2. Pick Trace

The pick trace routine determines the next set of trace blocks to be compacted. It selects the highest probability block among non-compacted blocks and iteratively selects the highest probability descendant block until it reaches an exit block, or a junction block, or an already compacted block. After selecting the trace blocks, all the MO's from those blocks are converted to a form acceptable to the list scheduling routine which performs local compaction regardless of block boundaries.

#### Input:

A set of blocks where each block is a 2-tuple. The first element is the probability of execution and the second is a flag indicating if the block has been compacted.

### Output:

The set of blocks which forms an execution path.

#### Procedure:

- (1) Delete empty blocks from the tracehead set.

- (2) Initialize the conditional source registers of each MO to empty.

- (3) Select a block with the highest probability of execution in the tracehead set.

Call the selected block the current block and add it to the trace.

- (4) Repeat until the current block is an exit block, a junction block or an already compacted block

{

Update the current block with a block of the highest execution probability among its descendant blocks.

If the new current block is not a compacted block, mark it as compacted and add it to the trace.

(5) Update the tracehead set.

}

(6) Convert the MO's in the trace to the appropriate format for the list scheduling.

The first step of the pick trace procedure is to delete empty blocks from the tracehead set. It is possible that some of the blocks in the tracehead set became empty in the previous bookkeeping procedure. So it is necessary to delete them from the tracehead set and instead add their descendent blocks to the tracehead set.

Search through the blocks in the tracehead set to pick up a block with the highest probability of execution among them. The selected block ( call it start block ) will be the first block in the trace selected.

Starting from the start block, repeatedly select the next block in the trace by picking the block with the highest probability among the descendant blocks of the current trace block. Mark all the blocks selected as trace blocks. The selection is stopped when a program exit block, a junction block or a marked block (already compacted) block is encountered. A program exit block or a junction block is included as a part of the trace but not a marked block. In the process, the descendant blocks of any trace block except the next trace block is collected as the off-the-trace blocks for that trace block. These off-the-trace blocks are necessary to update the tracehead set and to make some necessary copies of MO's in the bookkeeping stage.

Delete the start block from the tracehead set and add all the off-the-trace blocks of each trace block to the tracehead set.

Convert the MO's in the trace to the appropriate format for the list scheduling. Note that the list scheduling does not know about the blocks and our implementation of the list scheduling requires a slightly different MO format, e.g. sequential numbering of MO's. Also, add the live registers at the beginning of the off-the-trace blocks as the conditional source registers of the conditional branch MO in the trace for those off-the-trace blocks. Add a dummy register to all the conditional branch MO's as a conditional source register and destination register to establish a DDG edge between the conditional branch MO's, and thus keep the order of those MO's.

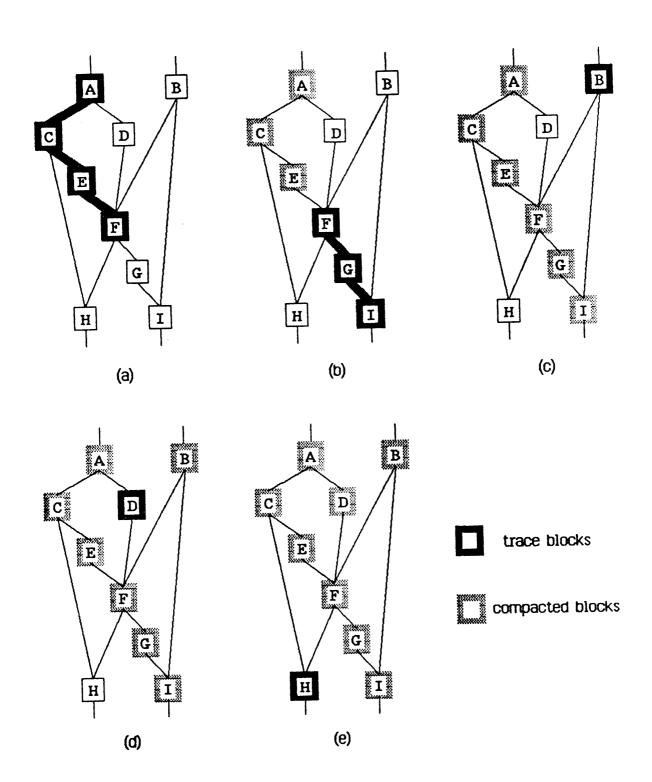

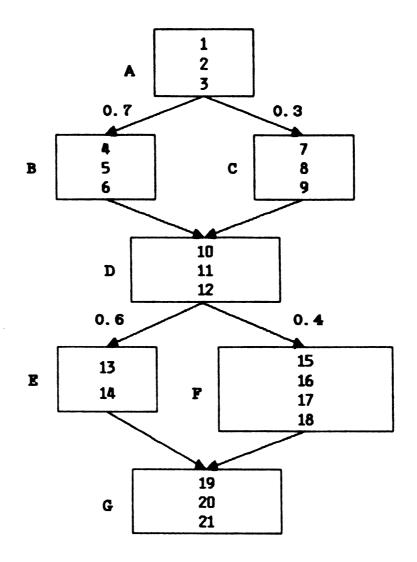

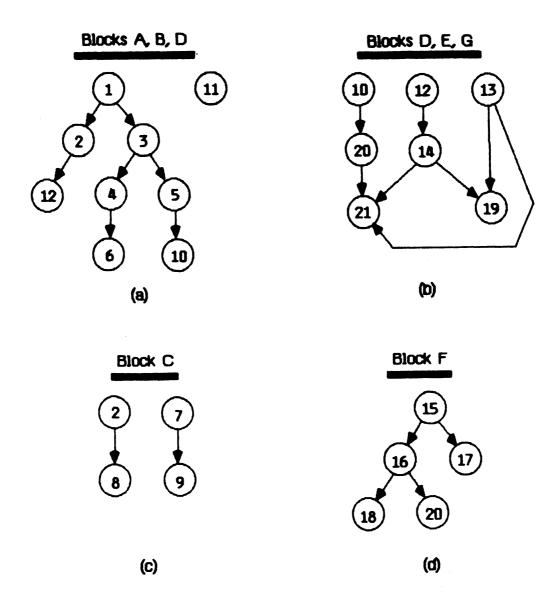

Figure 4.3 shows an example of selecting traces throughout the course of the beta compaction. Each box in the figure represents a block of MO's. Each subfigure shows the result of a call to the pick trace routine, Figure 4.3(a) being the first and Figure 4.3(e) being the last. It is assumed that the execution probability of blocks A, F, C, G, B, D and H are from high to low in the order of listing. Trace blocks are indicated with dark lined boxes and compacted blocks are indicated with shaded boxes.

Figure 4.3 Selecting traces

## 4.1.3. List Scheduling

The list scheduling routine does just local compaction on the list of MO's without any knowledge of block boundaries and generates a list of compacted MI's.

### Input:

The sequence of MO's in a basic block or in a trace

### Output:

The sequence of compacted MI's

#### Procedure:

- (1) Build DDG on MO's starting from the first MO.

- (2) Assign priority value ( number of levels of successors in DDG ) to each MO.

- (3) CYCLE = 0

- (4) Data Ready Set (DRS) is formed from all MO's with no predecessors on the DDG.

- (5) While DRS is not empty, DO {

CYCLE = CYCLE + 1

The MO's in DRS are placed in iteration CYCLE in order of their priority until DRS is exhausted or no more resources are available for CYCLE.

All MO's so placed are removed from DRS.

All unscheduled MO's not in DRS whose predecessors have all been scheduled are added to DRS.

}

The above procedure may be seen as three stages, i.e., build DDG (step 1), assign priority (step 2) and schedule MO's (steps 3, 4 and 5). A more detailed description of each step follows.

## (A) Build DDG

Given a sequence of MO's, a DDG is built based on source and destination registers of the MO's.

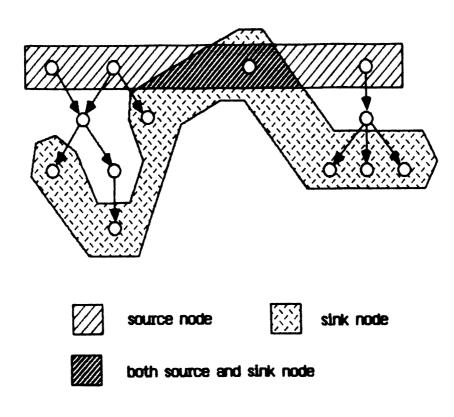

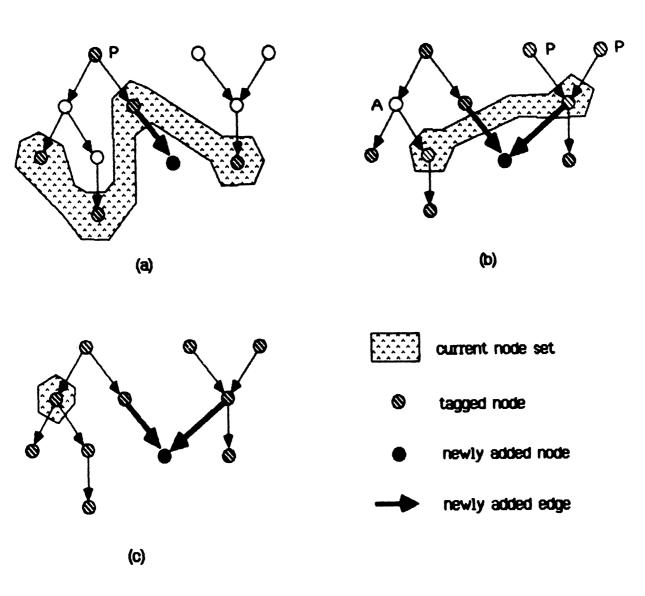

Starting from the second MO ( the first MO forms a single node DDG by itself), add one more node for the MO on the partially built DDG. The DDG is a directed acyclic graph with a set of source nodes and a set of sink nodes as shown in Figure 4.4. The source nodes are the nodes with in-degree zero and the

Figure 4.4 Sample data dependency graph

sink nodes are the nodes with out-degree zero. A single node not connected to the rest of the graph is considered to be both a source node and a sink node. Let us call the MO to be added the *current* MO, and the set of nodes being considered in the partially built DDG the *current node set*. At first the elements of the current node set are the sink nodes of the partially built DDG and are updated as the algorithm progresses.

Now take the current MO and see if there is any data interaction between the current MO and the MO's represented by the current node set. If there is any data interaction, i.e., the current MO is directly data dependent on some MO's represented by the current node set, draw edges from the corresponding nodes in the current node set to the new node representing current MO. Note that since we handle MO's in sequence, the current MO may be data dependent on the MO's of the current node set but the MO's of the current node set can not be data dependent on the current MO. Conditional source registers are used when considering data interaction between a conditional jump MO and the MO's that follow but not the MO's that precede. This constraint is to prevent movement of MO's above a conditional jump which may overwrite live registers at off-the-trace blocks but still allow movement of MO's below a conditional jump. In the case of a join, list scheduling is done on a trace with no constraint and new joining points are identified at the bookkeeping stage.

For all the MO's of the current node set on which the current MO is data dependent, tag all their ancestor nodes so that those ancestor nodes may not be included in the updated current nodes. When all the elements of the current node set are considered, update the current node set and repeat the process until the updated current node set is empty.

To update the current node set, consider each node of the set at a time. First, delete the node from the current node set. If the deleted node is not the source node, add the untagged ancestors of the node to the current node set. And delete any element of the current node set if it is an ancestor of another

node.

An example of building DDG is shown in Figure 4.5. The figure shows the change of the current node set and how edges are drawn to the newly added node. The black circle is the newly added node and it is assumed that one data dependency has been found between the node and current node set in Figure 4.5(a). The node labeled P is tagged because it is the ancestor node of the node

Figure 4.5 Example of building DDG

that the newly added node is data dependent upon. Another data dependency is assumed to be found in Figure 4.5(b) and there are two tagged nodes labeled P for the similar reason. In Figure 4.5(b), the node labeled A is not included in the current node set because it is an ancestor node of another element of the current node set.

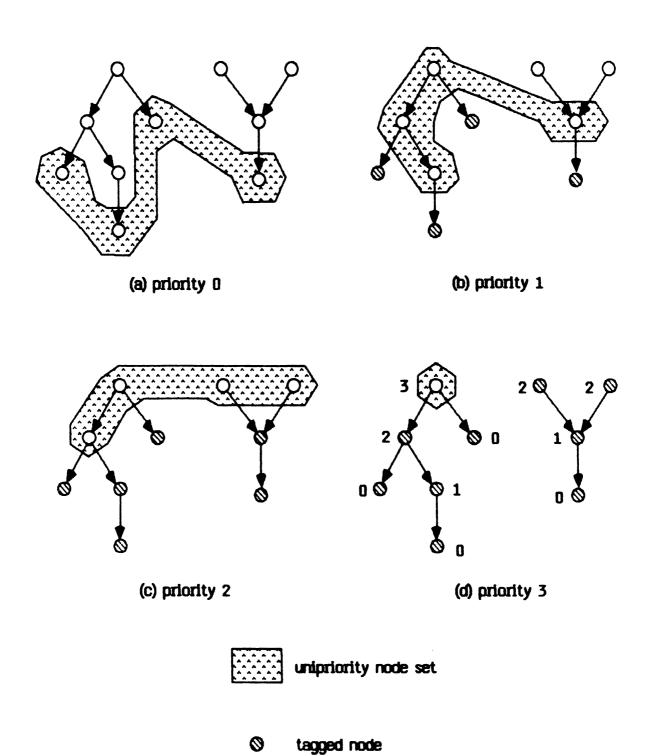

## (B) Assign priority